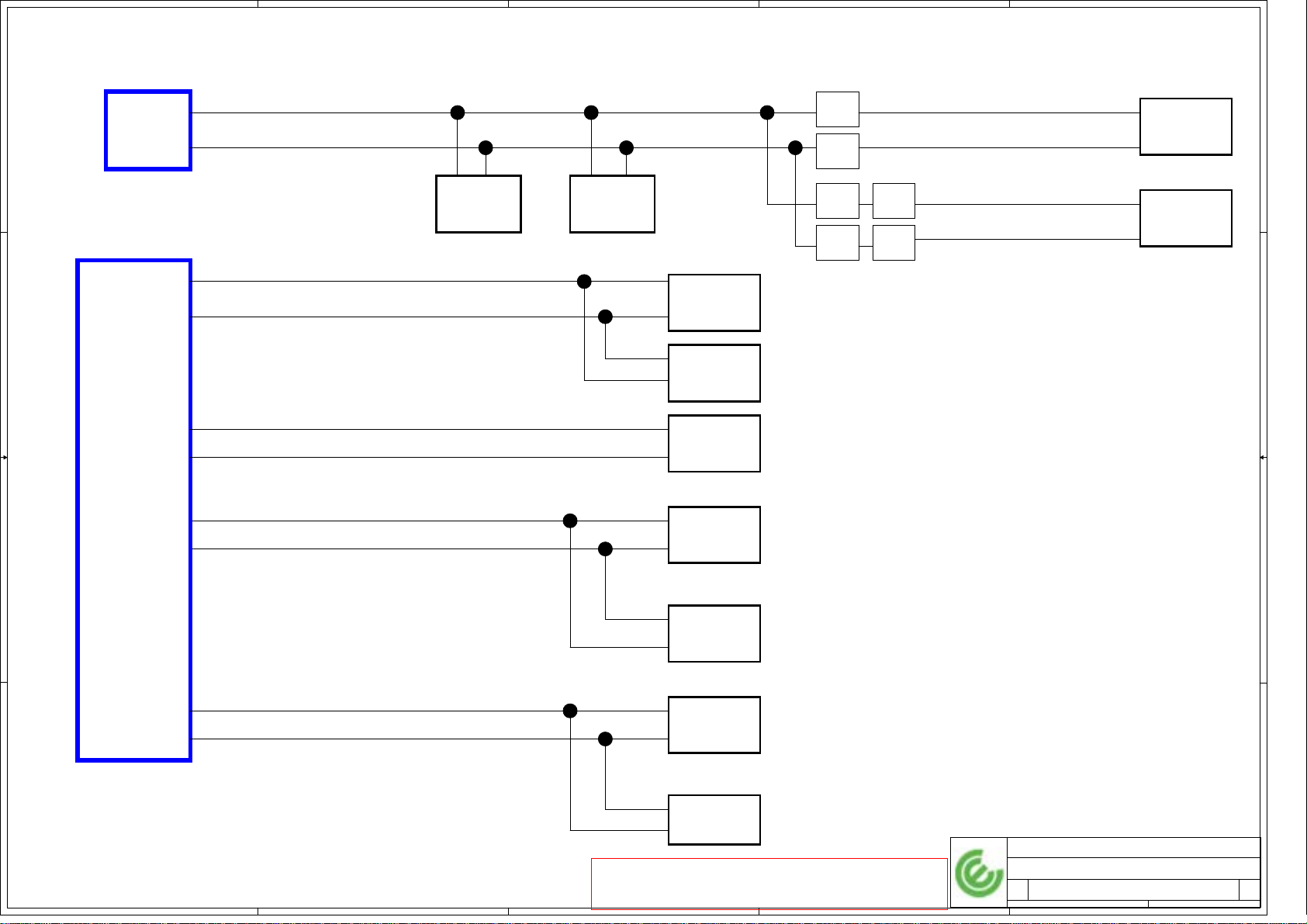

Page 1

5

D D

4

3

2

1

LAGUNA

REV : X00

C C

@ : Depop Component

PRELIMINARY

B B

Dothan Schematic with Capture CIS and Function field

uFCPGA Dothan

A A

02-07-2004

REV: 0.3

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Cover Sheet

Board Number LA2111

161Monday, February 09, 2004

1

of

0.3

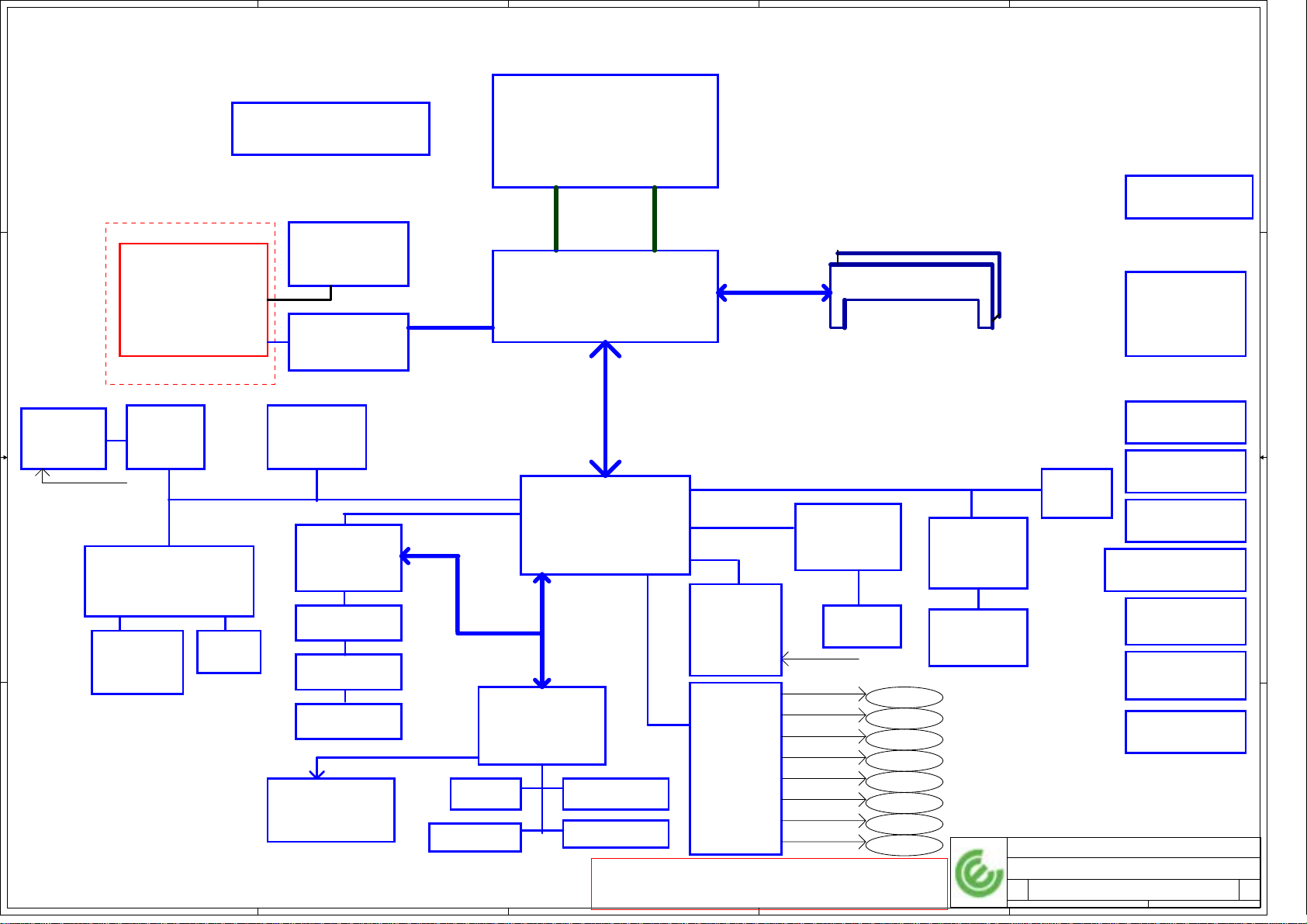

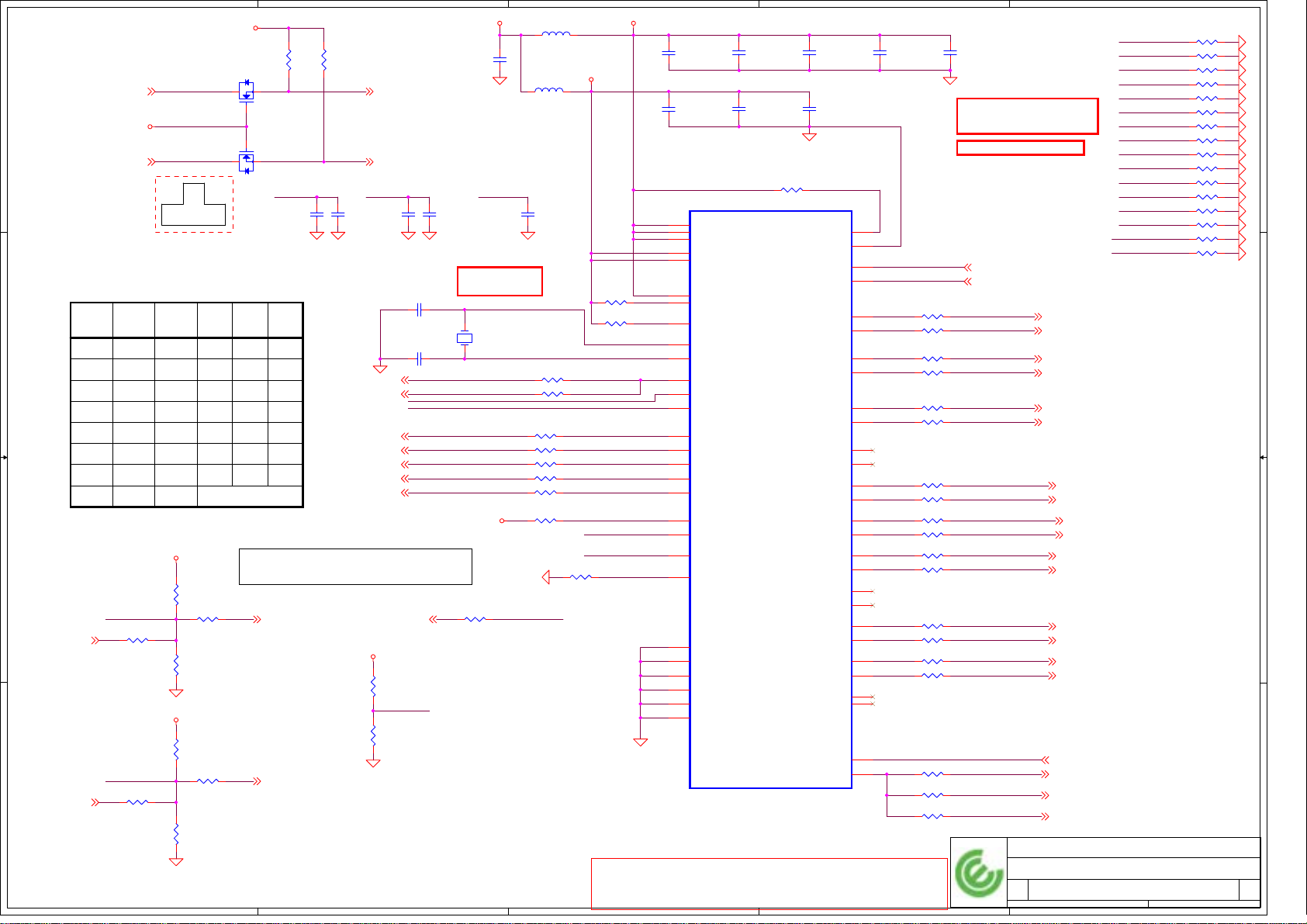

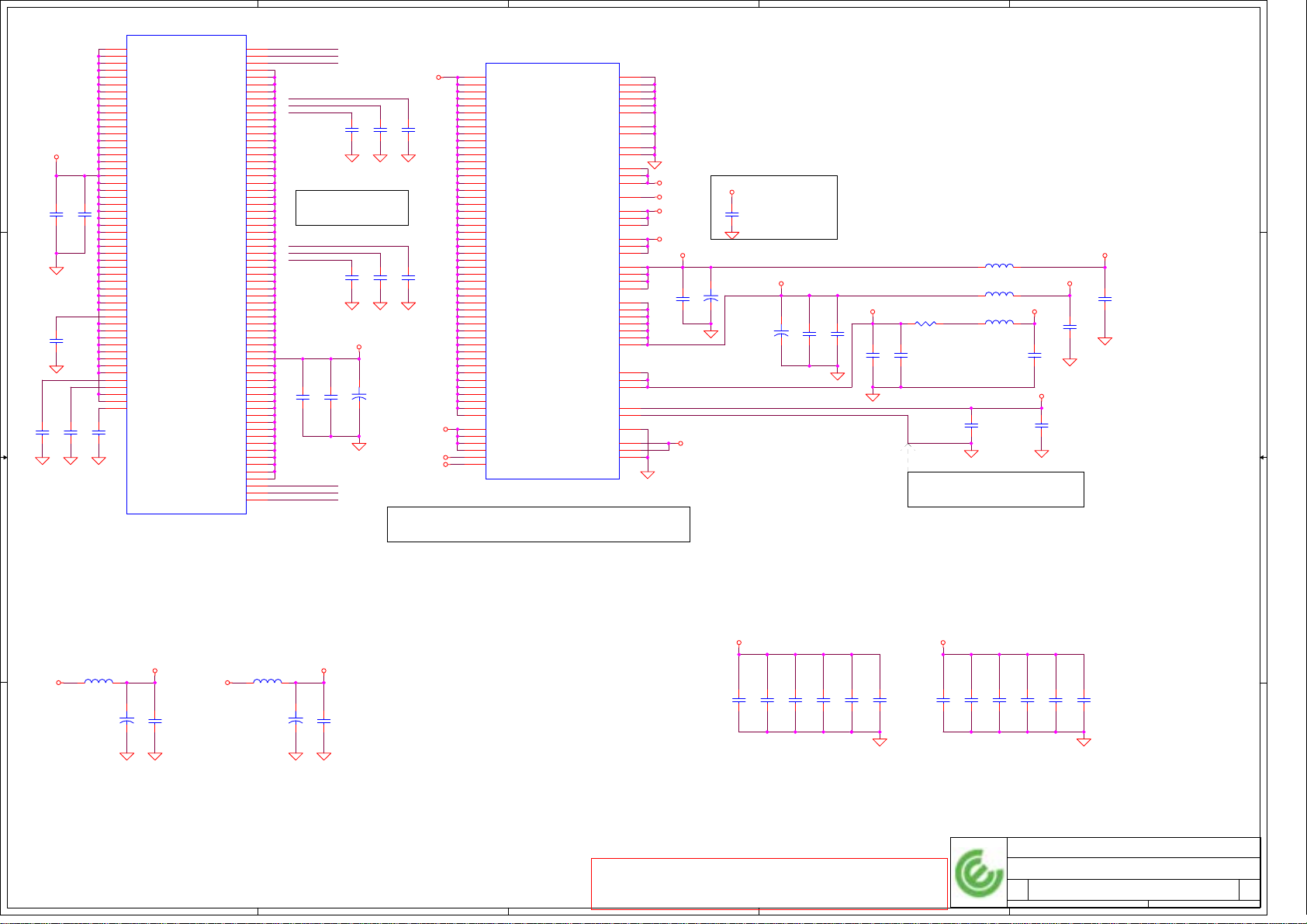

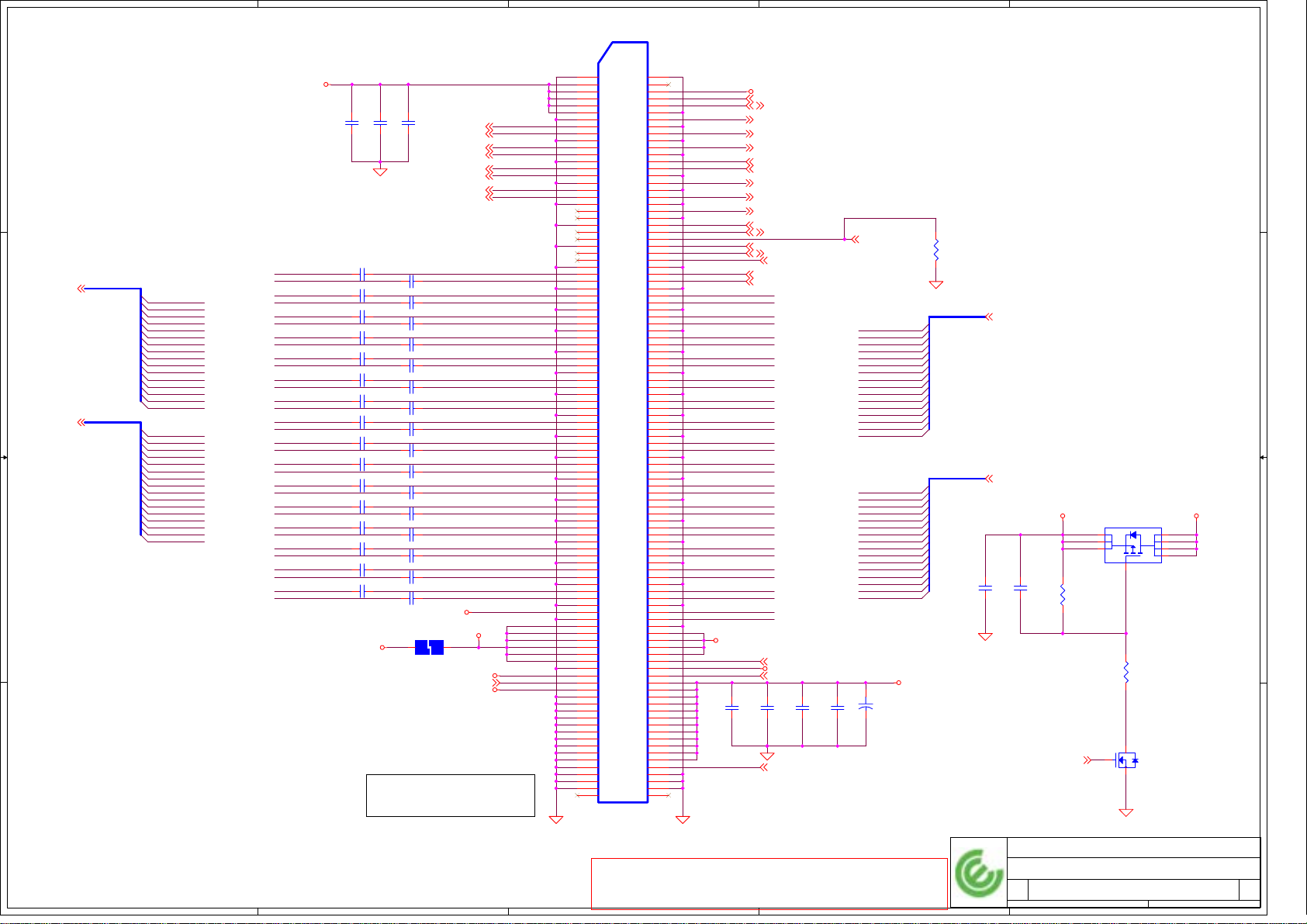

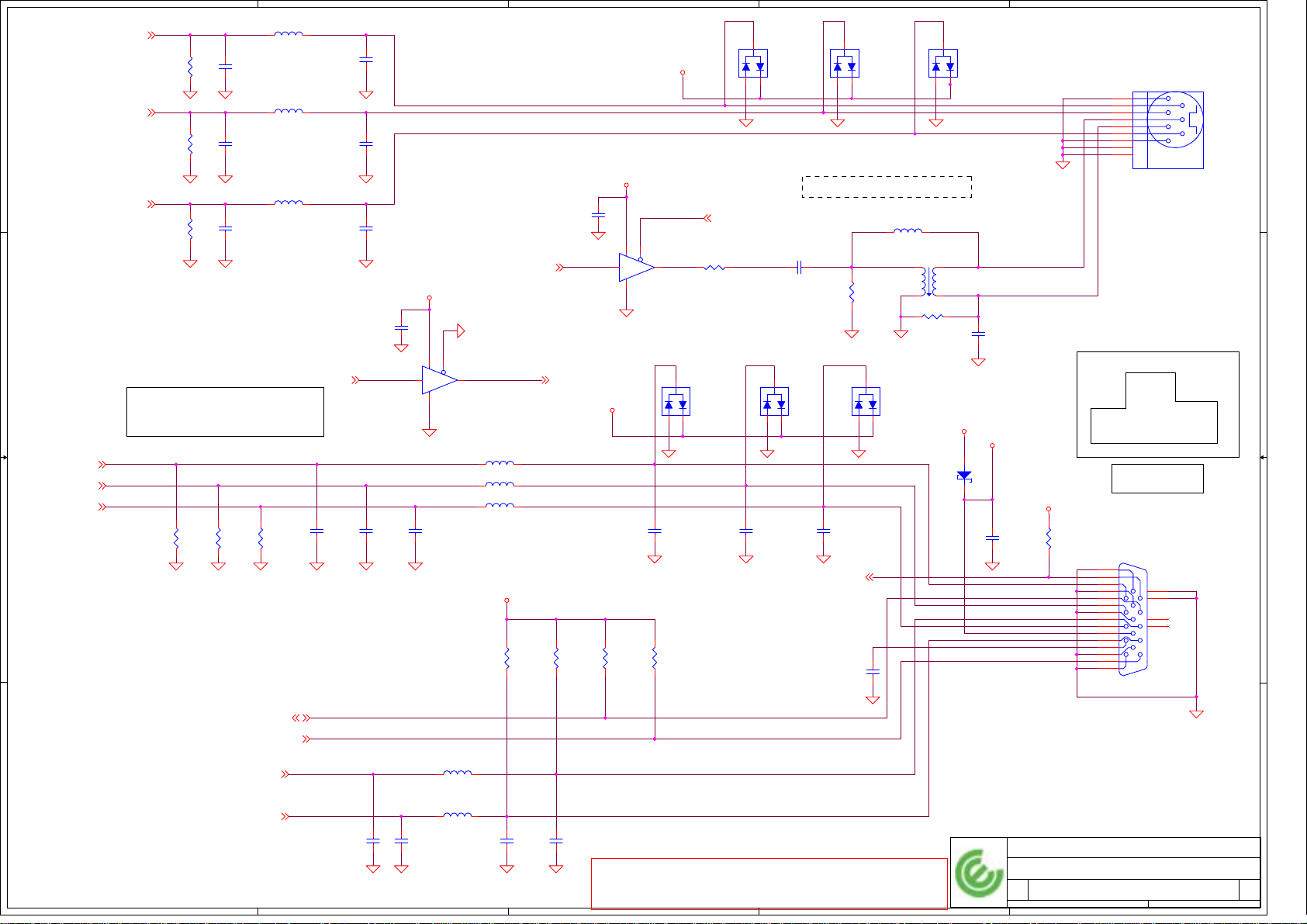

Page 2

5

Compal confidential

4

3

2

1

Block Diagram

D D

GUARDIAN

EMC6N300

page 39

Dothan

uFCPGA CPU

page 7,8,9

Fan Control

HA#(3..31)

CRT CONN.

& TV-OUT

VGA

page 19

Board

PCI-E 16X

VGA CONN.

C C

page 18

System Bus

400 / 533MHz

Alviso

GMCH-M

1257 FC-BGA

HD#(0..63)

page

10,11,12

13,14

Memory

BUS(DDR2)

1.8V 400 / 533MHz

SO-DIMM X2

BANK 0, 1, 2, 3

page16,17

Clock Generator

page 15

CK410M

page 6

DMI

DOCKING

PORT

PAGE 35

DOCKING

BUFFER

PAGE 34

USB

IDSEL:AD20

(PIRQA/B#,GNT#2,REQ#2)

B B

CardBus Controller

PCI6515

Smart card

page31

3.3V 33MHz

page 31,32

Slot 0

page32

MINI PCI

page 33

LAN

BCM5751M

Analog Switch

Transformer

RJ45

page 30

page 30

page 30

PCI BUS

PCI-E BUS

LPC BUS

3.3V 33MHz

Macallen III

X BUS

A A

5

SST39VF080

page 38

4

COM

page 28

Touch Pad

page 38

1.5V

100MHz

LPC to X-BUS

& Super I/O

page

36,37

ICH6

3.3V 24.576MHz

609 BGA

page

20,21,22,23

ATA100 and SATA

SATA

Marvell

SATA to PATA

page 52

PATA

CDROM

USB

FDD

SATA HDD

page 24

48MHz / 480Mb

Int.KBD

FIR (LED/B)

page 38

page 40

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

USB2.0

page 27

HDD

USB

USBPORT 0

USBPORT 1

USBPORT 2

USBPORT 3

USBPORT 4

USBPORT 5

USBPORT 6

USBPORT 7

page 52

FDD

DOCK

BT

Card BUS

JUSB1 U

JUSB1 D

JUSB2 U

JUSB2 D

AC-LINK

MDC

page 28

AC97

Codec

STAC9751

page 25page 29

AMP& Phone

Jack

page 26

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

2

Date: Sheet

Block Diagram

Board Number LA2111

DC IN

BATT

IN

1.8V / 0.9V

page

44

page

45

page

44

1.5V/1.05V(+VCCP)

page 47

VCORE

page 49

5V/3.3V/15V

page 46

CHARGER

1

page

50,51

261Monday, February 09, 2004

of

0.3

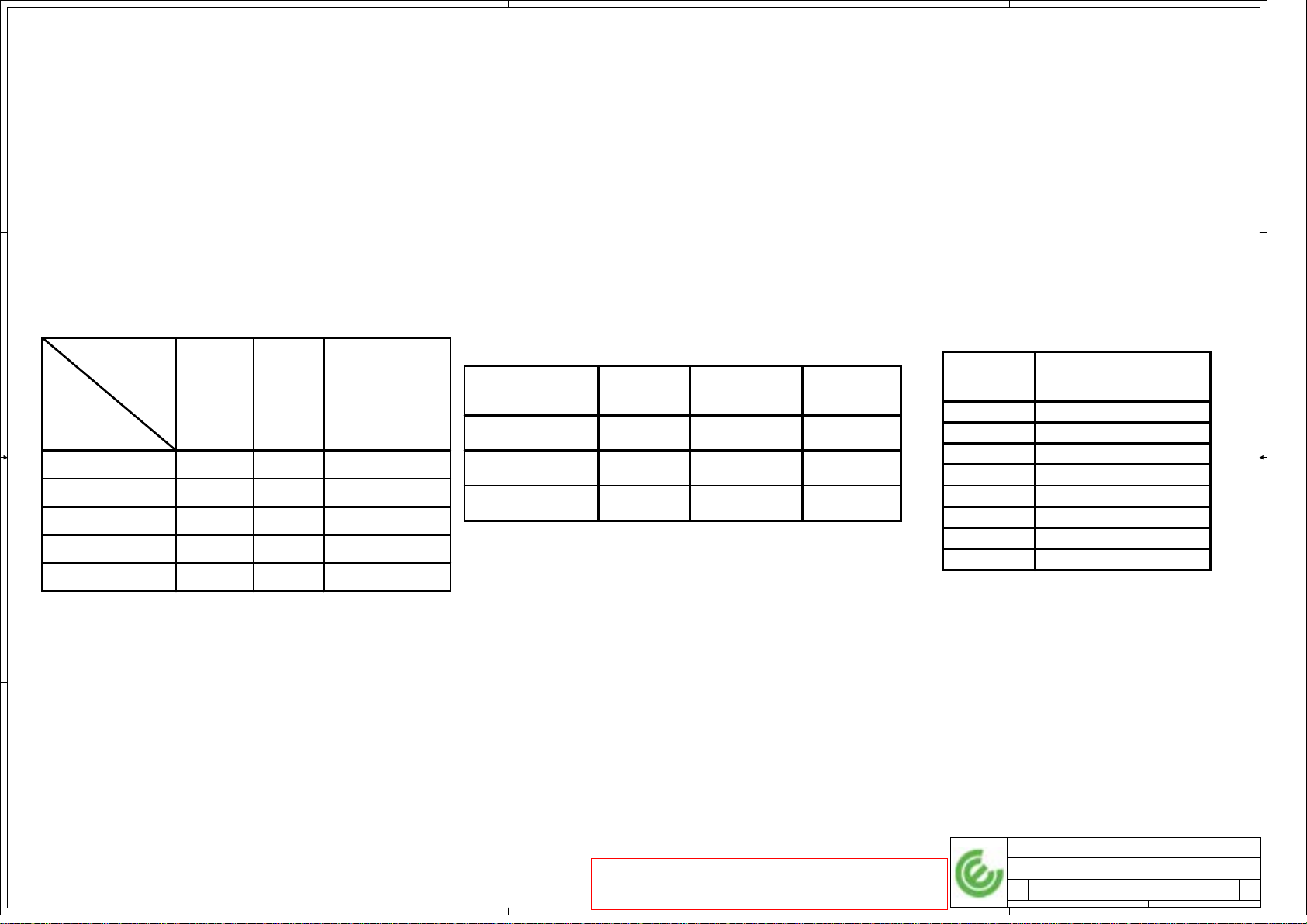

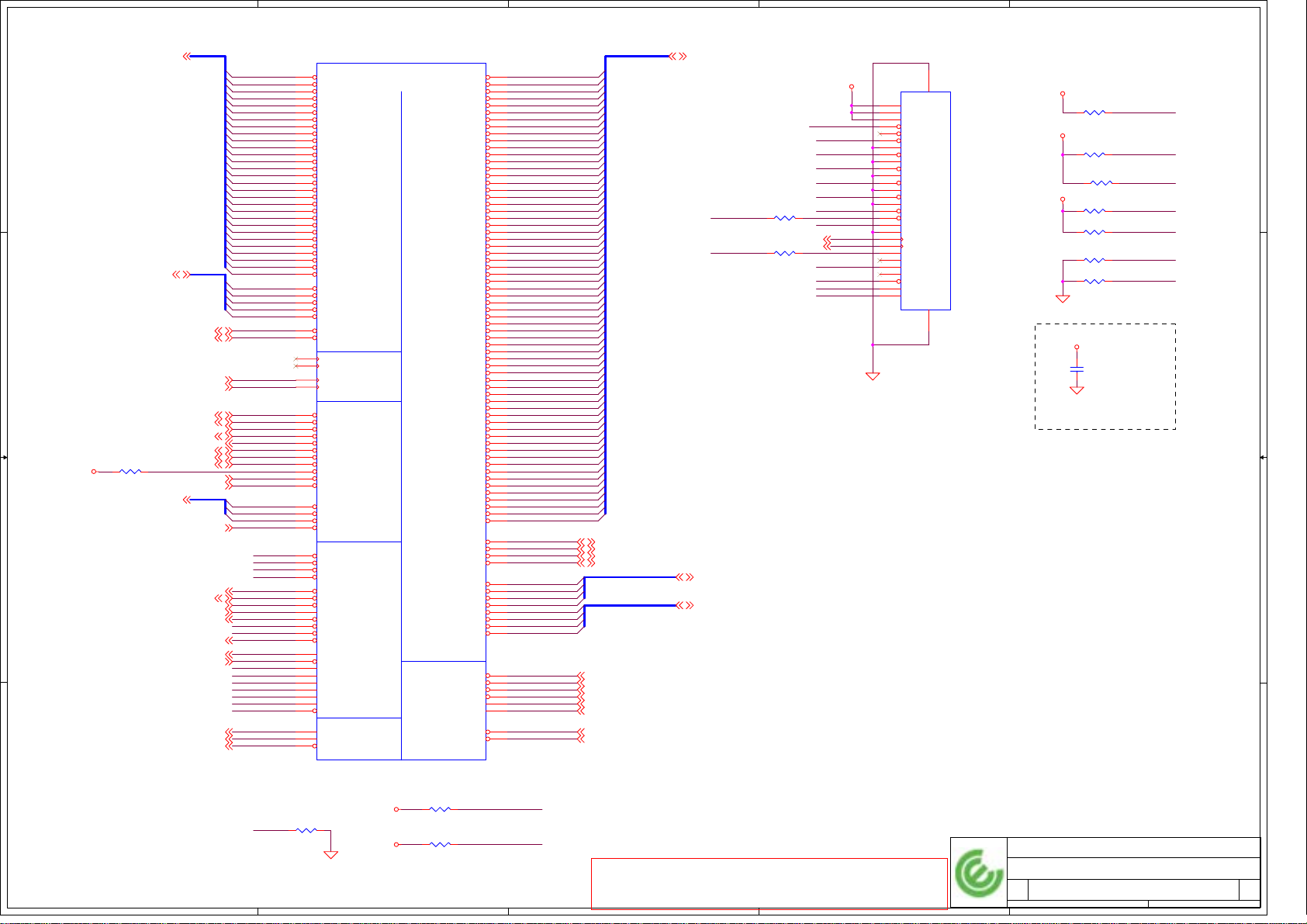

Page 3

5

D D

4

3

2

1

PM TABLE

C C

power

plane

State

S0

S1

S3

S5 S4/AC

B B

S5 S4/AC don't exist

+3VALW

+5VALW

ON

ON

ON

ON

+3VSUS

+5VSUS

+1.8VSUS

+1.5VSUS

ON ON

ON

ON

OFF

OFFOFF

+5VRUN

+3VRUN

+2.5VRUN

+1.8VRUN

+1.5VRUN

+VCC_CORE

+VCCP

+15V

+RTC_CELL

+0.9V_DDR_VTT

ON

OFF

OFF

OFF

PCI TABLE

PCI DEVICE

CARD BUS

DOCK

MINI PCI

IDSEL

AD17

AD24

AD19

REQ#/GNT#

1

0

3

PIRQ

D,C

A

D,B

USB TABLE

USB PORT#0DESTINATION

FDD (module bay)

1

2

MPCI (BlueTooth)

DOCK

3 NEW Connector

4

USB Port 1(Top)

USB Port 1(Bottom)5

6 USB Port 2(Top)

7 USB Port 2(Bottom)

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Index and Config.

Board Number LA2111

361Monday, February 09, 2004

1

of

0.3

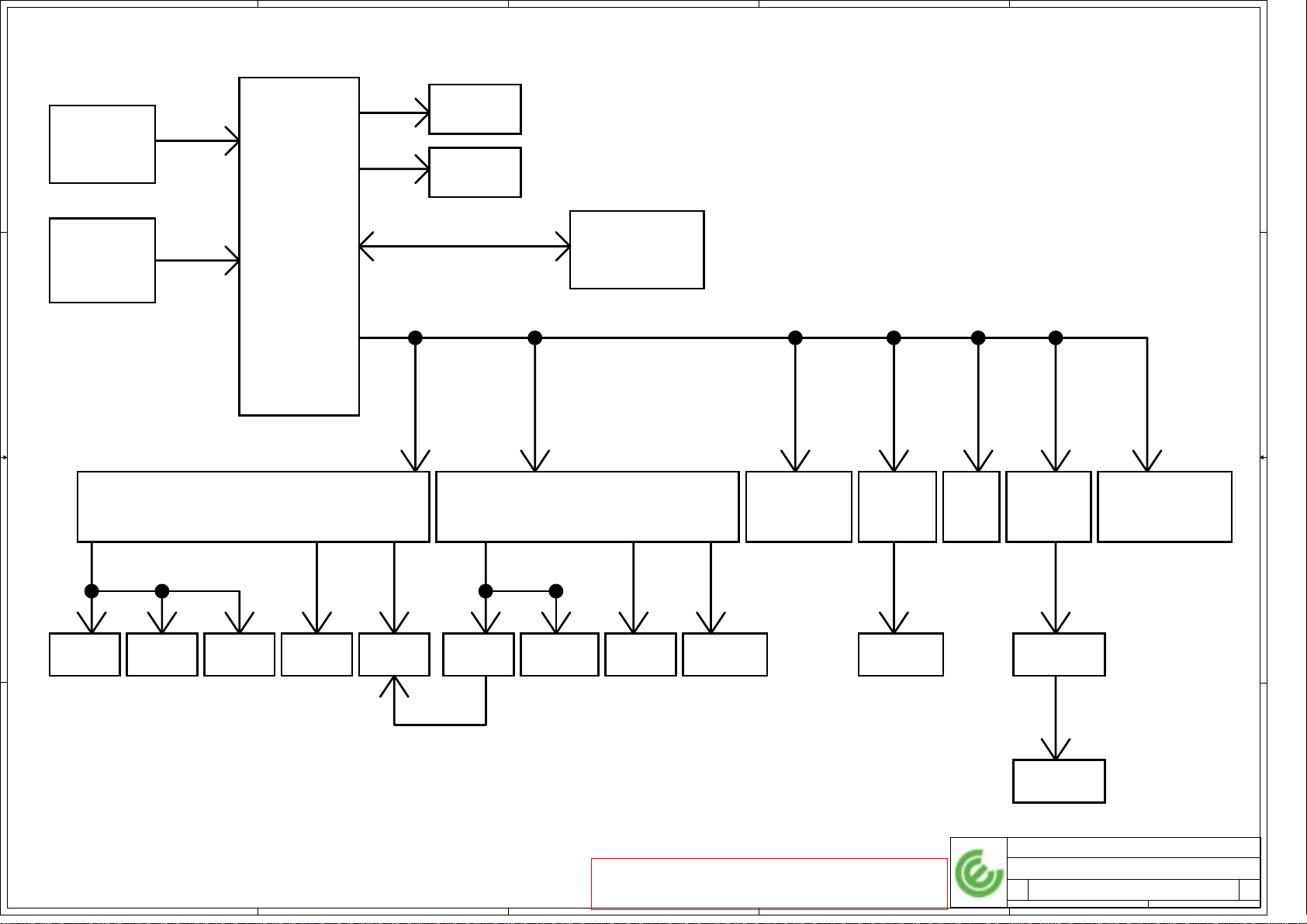

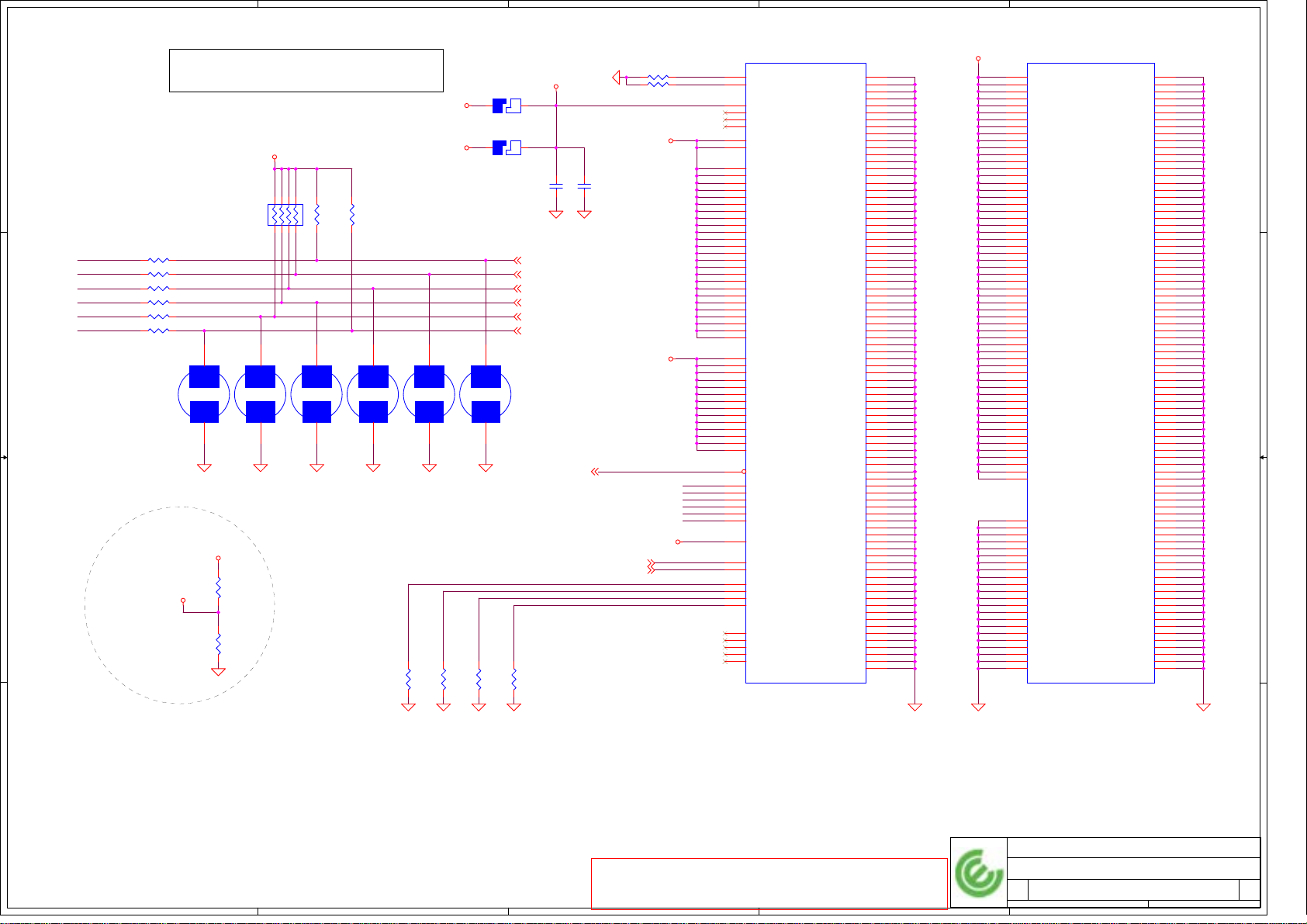

Page 4

5

4

3

2

1

D D

+5VALW

ADAPTER

PWR_SRC

BATTERY

C C

+5VSUS

SUS_ON

+3VALW

SUS_ON

+3VSRC

G_PWR_SRC

RUNPWROK

+VCC_CORE

+1.5VSUS

RUNPWROK

+VCCP

SUSPWROK_5V

+5RUN

+1.8VSUSP +0.9V_DDR_VTT

B B

+5VHDD +5VMOD +5VRUN VDDA

A A

RUN_ON

PL9

+15V +2.5VRUN

(Option)

AUDIO_AVDD_ON

+3VRUN

L10

RUN_ON

V3P3LAN

SUSPWROK_5V

+3VSUS

RUN_ON

RUN_ON SUSPWROK_5V

+1.5VRUN

PJP11,PJP12

+1.8VSUS

RUN_ON

+1.8VRUN

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

Power Rail

Board Number LA2111

461Monday, February 09, 2004

1

of

0.3

Page 5

5

4

3

2

1

+3VRUN

ICH_SMBCLK

D D

ICH6

ICH_SMBDATA

+3VSUS

7002

7002

CK_SCLK

CLK GEN.

CK_SDATA

DIMM0

Address 00 Address 10

DIMM1

7002

7002

LAN_SMBCLK

LOM

LAN_SMBDATA

7002

CLK_SMB

DAT_SMB

C C

+3VALW

GUARDIAN

V_3P3_LAN

7002

24C04

DOCK_SMB_CLK

SIO

DOCK_SMB_DAT

+5VALW

DOCKING

Macallen III

SBAT_SMBCLK

SBAT_SMBDAT

B B

+5VALW

2'nd

BATTERY

VGA

PBAT_SMBCLK

1'st

PBAT_SMBDAT +5VALW

A A

BATTERY

CHARGER

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Size Document Number Rev

Date: Sheet

SMBUS TOPOLOGY

Board Number LA2111

561Monday, February 09, 2004

1

of

0.3

Page 6

5

+3VRUN

ICH_SMBDATA<<22,33>>

D D

ICH_SMBCLK<<22,33>>

ICH_SMBDATA

+3VRUN

ICH_SMBCLK

D

1 3

1 3

D

D

1

3

G

S

2

2N7002

FSC FSB FSA CPU

CLKSEL0 CLKSEL1 CLKSEL2

C C

0

0

0

1

1

1

00

1

0

0

1

11

0

0

0

1

0

1

1

11

MHz

266

133

200

166

333

100

400

SRC

MHz

100 33.30

100

100

100

100

100

100

RESERVED

R57

S

Q6

2N7002_SOT23~D

G

2

2

G

Q8

2N7002_SOT23~D

S

12

100K_0402_5%~D

CK_VDD_A

PCI

MHz

33.3

33.3

33.3

33.3

33.3

33.3

C1247

12

R61

100K_0402_5%~D

CK_SDATA

CK_SCLK

1

2

4.7U_0805_6.3V6K~D

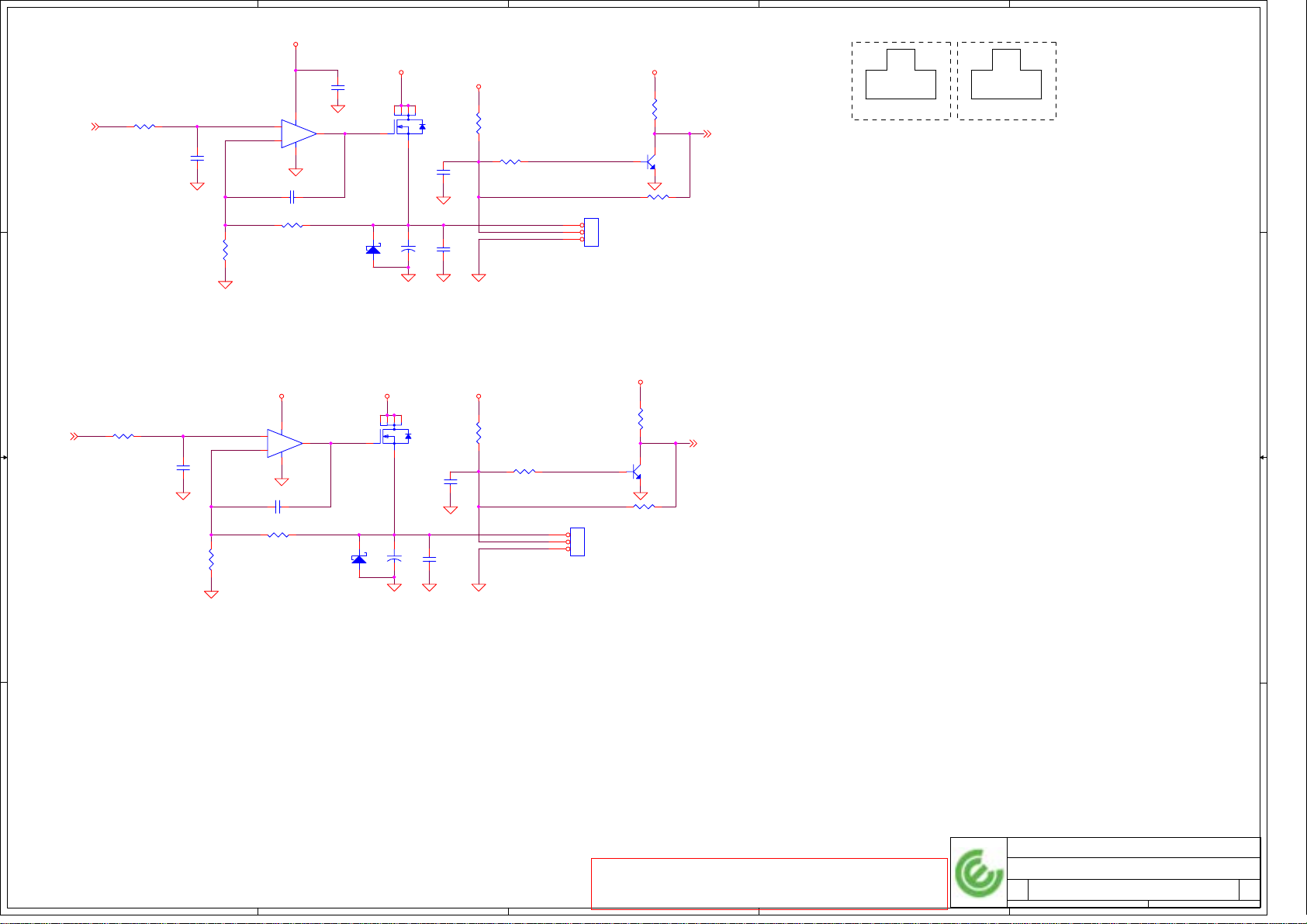

Table : ICS 954201 / Cypress CY28411

+VCCP

B B

CLKSEL0

CPU_BSEL0<<8>>

A A

CPU_BSEL1<<8>>

1 2

R643

0_0402_5%~D@

CLKSEL1

1 2

R641

0_0402_5%~D@

5

+VCCP

R65

1K_0402_5%~D

@

1 2

1 2

R1070

1K_0402_5%~D

R66

0_0402_5%~D

1 2

R95

1K_0402_5%~D

@

1 2

1 2

R1073

1K_0402_5%~D

R90

0_0402_5%~D

1 2

Dothan-A 400MHz, Install R65, No pop. R66, R643

Dothan-A 533MHz, Install R66, No pop. R65, R643

MCH_CLKSEL0 <<10>>

MCH_CLKSEL1 <<10>>

1

2

C1248

0.047U_0402_16V7K~D

CK_48M_SCR<<31>>

CK_33M_CBPCI<<31>>

CK_33M_SIOPCI<<36>>

CK_33M_MINIPCI<<33>>

CK_33M_DOCKPCI<<34>>

CK_33M_ICHPCI<<20>>

4

CK_SDATA <<16,17>>

CK_SCLK <<16,17>>

CK_VDD_48

C1249

4.7U_0805_6.3V6K~D

33P_0402_50V8J~D

33P_0402_50V8J~D

CK_48M_ICH<<22>>

CK_33M_LOMPCI<<29>>

+3VRUN

R96

10K_0402_5%~D

1 2

CLKSEL2

R91

10K_0402_5%~D

@

1 2

4

1

1

2

2

C1251

C90

12

C93

12

CK_48M_SCR

CK_48M_ICH

CLKSEL1

CLKSEL0

CK_33M_CBPCI

CK_33M_SIOPCI

CK_33M_MINIPCI

CK_33M_DOCKPCI

CK_33M_ICHPCI

+3VRUN

1

C992

2

0.1U_0402_16V4Z~D

1 2

BLM21PG600SN1D_0805~D

CK_VDD_REF

0.047U_0402_16V7K~D

Place crystal within

500 mils of CK410

CK_XTAL_IN

X1

12

14.31818MHz_20P_1BX14318CC1A~D

+3VRUN

CK_XTAL_OUT

R59 33_0402_5%~D

R62 33_0402_5%~D

R81 33_0402_5%~D

R83 33_0402_5%~D

R68 33_0402_5%~D

R79 33_0402_5%~D

R88 33_0402_5%~D

1 2

PCICLK4

R1206

33_0402_5%~D

1 2

1 2

L33

BLM21PG600SN1D_0805~D

CK_VDD_MAIN2

L130

1

2

C1252

0.047U_0402_16V7K~D

1 2

1 2

12

CLKSEL2

12

12

12

12

12

12

R177

10K_0402_5%~D

PCICLKF0

1 2

R67 475_0402_1%~D

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

CK_VDD_MAIN

CK_VDD_REF

R1107

1_0402_5%~D

CK_VDD_48

R1108

2.2_0402_5%~D

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLKF1

CK_SCLK

CK_SDATA

CLKIREF

3

CK_VDD_MAIN

2

C89

10U_0805_6.3V6M~D

1

2

C993

10U_0805_6.3V6M~D

1

U8

21

VDD_SRC0

28

VDD_SRC1

34

VDD_SRC2

1

VDD_PCI0

7

VDD_PCI1

42

VDD_CPU

48

VDD_REF

11

VDD_48

50

XTAL_IN

49

XTAL_OUT

12

FSA/USB_48

16

FSB/TEST_MODE

53

FSC/TEST_SEL

5

PCI5

4

PCI4

3

PCI3

56

PCI2

9

PCIF1

8

PCIF0/ITP_EN

46

SCLOCK

47

SDATA

39

IREF

13

VSS_48

29

VSS_SRC

2

VSS_PCI0

45

VSS_CPU

51

VSS_REF

6

VSS_PCI1

CY28411ZCT_TSSOP56~D

1

C94

0.047U_0402_16V7K~D

2

1

C994

0.047U_0402_16V7K~D

2

R1106

2.2_0402_5%~D

1 2

CPU_2_ITP/SRC_7

CPU_2_ITP/SRC7#

VTT_PWRGD#/PD

1

C91

0.047U_0402_16V7K~D

2

1

C995

0.047U_0402_16V7K~D

2

CK_VDD_A

37

VDD_A

38

VSS_A

55

PCI_STOP#

54

CPU_STOP#

41

CPU1

40

CPU1#

44

CPU0

43

CPU0#

36

35

33

SRC6

32

SRC6#

31

SRC5

30

SRC5#

26

SRC4

27

SRC4#

24

SRC3

25

SRC3#

22

SRC2

23

SRC2#

19

SRC1

20

SRC1#

17

SRC0

18

SRC0#

14

DOT96

15

DOT96#

10

52

REF

2

1

C87

0.047U_0402_16V7K~D

2

H_STP_PCI#

H_STP_CPU#

CK_CPU1

1 2

R85 33_0402_5%~D

CK_CPU1#

1 2

R82 33_0402_5%~D

CK_CPU0

CK_CPU0#

CK_CPU2

CK_CPU2#

1 2

R78 33_0402_5%~D

1 2

R71 33_0402_5%~D

1 2

R93 33_0402_5%~D

1 2

R87 33_0402_5%~D

SCR5

1 2

R1040 33_0402_5%~D

SRC5#

1 2

R1041 33_0402_5%~D

SRC4

1 2

R138 33_0402_5%~D

SRC4#

1 2

R143 33_0402_5%~D

SRC3

1 2

R60 33_0402_5%~D

SRC3#

1 2

R148 33_0402_5%~D

SRC1

1 2

R64 33_0402_5%~D

SRC1#

1 2

R63 33_0402_5%~D

SRC0

1 2

R165 33_0402_5%~D

SRC0#

1 2

R166 33_0402_5%~D

CLK_ENABLE#

CLKREF

1 2

R99 12.1_0402_1%~D

1 2

R98 12.1_0402_1%~D

1 2

R551 12.1_0402_1%~D

2

1

C85

0.047U_0402_16V7K~D

2

Place near each pin

W>40 mil

Place near CK410

H_STP_PCI# <<22>>

H_STP_CPU# <<22,49>>

CLK_MCH_BCLK

CLK_MCH_BCLK#

CK_BCLK

CK_BCLK#

CK_ITP

CK_ITP#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_VGA

CLK_PCIE_VGA#

CLK_PCIE_LOM

CLK_PCIE_LOM#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CK_14M_ICH

CK_14M_SIO

CK_14M_CODEC

CLK_MCH_BCLK <<10>>

CLK_MCH_BCLK# <<10>>

CK_BCLK <<7>>

CK_BCLK# <<7>>

CK_ITP <<7>>

CK_ITP# <<7>>

DELL CONFIDENTIAL/PROPRIETARY

Title

Size Document Number Rev

Board Number LA2111

Date: Sheet of

CLK_MCH_BCLK

CLK_MCH_BCLK#

CK_BCLK

CK_BCLK#

CK_ITP

CK_ITP#

CLK_PCIE_SATA

CLK_PCIE_SATA#

CLK_PCIE_VGA

CLK_PCIE_VGA#

CLK_PCIE_ICH

CLK_PCIE_ICH#

CLK_MCH_3GPLL

CLK_MCH_3GPLL#

CLK_PCIE_LOM

CLK_PCIE_LOM#

CLK_MCH_3GPLL <<12>>

CLK_MCH_3GPLL# <<12>>

CLK_PCIE_SATA <<21>>

CLK_PCIE_SATA# <<21>>

CLK_PCIE_VGA <<18>>

CLK_PCIE_VGA# <<18>>

CLK_PCIE_LOM <<29>>

CLK_PCIE_LOM# <<29>>

CLK_PCIE_ICH <<22>>

CLK_PCIE_ICH# <<22>>

CLK_ENABLE# <<49>>

CK_14M_ICH <<22>>

CK_14M_SIO <<36>>

CK_14M_CODEC <<25>>

Clock Generator

1

R92

12

49.9_0402_1%~D

R86

12

49.9_0402_1%~D

R84

12

49.9_0402_1%~D

R80

12

49.9_0402_1%~D

R77

12

49.9_0402_1%~D

R70

12

49.9_0402_1%~D

R146

1 2

49.9_0402_1%~D

R140

1 2

49.9_0402_1%~D

R153

1 2

49.9_0402_1%~D

R154

1 2

49.9_0402_1%~D

R156

1 2

49.9_0402_1%~D

R159

1 2

49.9_0402_1%~D

R114

1 2

49.9_0402_1%~D

R115

1 2

49.9_0402_1%~D

R1038

1 2

49.9_0402_1%~D

R1039

1 2

49.9_0402_1%~D

661Monday, February 09, 2004

1

0.3

Page 7

5

4

3

2

1

H_A#[3..31]<<10>>

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

D D

H_REQ#[0..4]<<10>>

H_ADSTB#0<<10>>

C C

R624

56_0402_5%~D

1 2

+VCCP

B B

H_ADSTB#1<<10>>

CK_BCLK<<6>>

CK_BCLK#<<6>>

H_ADS#<<10>>

H_BNR#<<10>>

H_BPRI#<<10>>

H_BR0#<<10>>

H_DEFER#<<10>>

H_DRDY#<<10>>

H_HIT#<<10>>

H_HITM#<<10>>

H_LOCK#<<10>>

H_RESET#<<10>>

H_RS#[0..2]<<10>>

H_TRDY#<<10>>

ITP_DBRESET#<<42>>

H_DBSY#<<10>>

H_DPSLP#<<21>>

H_DPRSTP#<<21>>

H_DPWR#<<10>>

H_PROCHOT#<<37>>

H_PWRGOOD<<21>>

H_CPUSLP#<<10,21>>

H_THERMDA<<39>>

H_THERMDC<<39>>

H_THERMTRIP#<<39>>

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

CK_BCLK

CK_BCLK#

H_ADS#

H_BNR#

H_BPRI#

H_BR0#

H_DEFER#

H_DRDY#

H_HIT#

H_HITM#

H_IERR#

H_LOCK#

H_RESET#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_DBRESET#

H_DBSY#

H_DPSLP#

H_DPRSTP#

H_DPWR#

ITP_BPM#4

ITP_BPM#5

H_PROCHOT#

H_CPUSLP#

ITP_TCK

ITP_TDI

ITP_TDO

TEST1

TEST2

ITP_TMS

ITP_TRST#

H_THERMDA

H_THERMDC

JCPUA

P4

A3#

U4

A4#

V3

A5#

R3

A6#

V2

A7#

W1

A8#

T4

A9#

W2

A10#

Y4

A11#

Y1

A12#

U1

A13#

AA3

A14#

Y3

A15#

AA2

A16#

AF4

A17#

AC4

A18#

AC7

A19#

AC3

A20#

AD3

A21#

AE4

A22#

AD2

A23#

AB4

A24#

AC6

ADDR GROUP

A25#

AD5

A26#

AE2

A27#

AD6

A28#

AF3

A29#

AE1

A30#

AF1

A31#

R2

REQ0#

P3

REQ1#

T2

REQ2#

P1

REQ3#

T1

REQ4#

U3

ADSTB0#

AE5

ADSTB1#

A16

ITP_CLK0

A15

ITP_CLK1

B15

BCLK0

B14

BCLK1

N2

ADS#

L1

BNR#

J3

BPRI#

N4

BR0#

L4

DEFER#

H2

DRDY#

K3

HIT#

K4

HITM#

A4

IERR#

J2

LOCK#

B11

RESET#

H1

RS0#

K1

RS1#

L2

RS2#

M3

TRDY#

C8

BPM0#

B8

BPM1#

A9

BPM2#

C9

BPM3#

A7

DBR#

M2

DBSY#

B7

DPSLP#

G1

DPRSTP#

C19

DPWR#

A10

PRDY#

B10

PREQ#

B17

PROCHOT#

E4

PWRGOOD

A6

SLP#

A13

TCK

C12

TDI

A12

TDO

C5

TEST1

F23

TEST2

C11

TMS

B13

TRST#

B18

THERMDA

A18

THERMDC

C17

THERMTRIP#

AMP_1473129-1_Dothan~D

Dothan

DATA GROUP

HOST CLK

CONTROL GROUP

MISC

THERMAL

DIODE

LEGACY CPU

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DINV0#

DINV1#

DINV2#

DINV3#

DSTBN0#

DSTBN1#

DSTBN2#

DSTBN3#

DSTBP0#

DSTBP1#

DSTBP2#

DSTBP3#

A20M#

FERR#

IGNNE#

INIT#

LINT0

LINT1

STPCLK#

SMI#

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

A25

A22

B21

A24

B26

A21

B20

C20

B24

D24

E24

C26

B23

E23

C25

H23

G25

L23

M26

H24

F25

G24

J23

M23

J25

L26

N24

M25

H26

N25

K25

Y26

AA24

T25

U23

V23

R24

R26

R23

AA23

U26

V24

U25

V26

Y23

AA26

Y25

AB25

AC23

AB24

AC20

AC22

AC25

AD23

AE22

AF23

AD24

AF20

AE21

AD21

AF25

AF22

AF26

D25

J26

T24

AD20

C23

K24

W25

AE24

C22

L24

W24

AE25

C2

D3

A3

B5

D1

D4

C6

B4

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20H_A#23

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_A20M#

H_FERR#

H_IGNNE#

H_INIT#

H_INTR

H_NMI

H_STPCLK#

H_SMI#

H_DINV#0 <<10>>

H_DINV#1 <<10>>

H_DINV#2 <<10>>

H_DINV#3 <<10>>

H_A20M# <<21>>

H_FERR# <<21>>

H_IGNNE# <<21>>

H_INIT# <<21>>

H_INTR <<21>>

H_NMI <<21>>

H_STPCLK# <<21>>

H_SMI# <<21>>

H_D#0H_A#3

A19

H_D#[0..63] <<10>>

H_RESET#

ITP_TDO

H_DSTBN#[0..3] <<10>>

H_DSTBP#[0..3] <<10>>

R621

22.6_0603_1%~D

1 2

CK_ITP<<6>>

CK_ITP#<<6>>

1 2

R620

22.6_0603_1%~D

+VCCP

ITP_DBRESET#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_RESET#

ITP_TCK

CK_ITP

CK_ITP#

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

29

JITP

28

VTT1

27

GND6

VTT0

26

VTAP

25

DBR#

24

DBA#

23

BPM0#

22

GND5

21

BPM1#

20

GND4

19

BPM2#

18

GND3

17

BPM3#

16

GND2

15

BPM4#

14

GND1

13

BPM5#

12

RESET#

11

FBO

10

GND0

9

BCLKP

8

BCLKN

7

TDO

6

NC2

5

TCK

4

NC1

3

TRST#

2

TMS

1

TDI

GND7

MOLEX_52435-2891_28P~D

30

+3VSUS

+VCCP

+VCCP

+VCCP

R743

150_0603_1%~D

1 2

R622

54.9_0603_1%~D

1 2

R1160

54.9_0402_1%~D

1 2

R618

39.2_0603_1%~D

1 2

R619

150_0603_1%~D

1 2

This shall place near CPU

R615

680_0402_5%~D

1 2

R617

27.4_0603_1%~D

1 2

1

C914

0.1U_0402_10V7K~D

2

ITP_DBRESET#

ITP_TDO

H_RESET#

ITP_TMS

ITP_TDI

ITP_TRST#

ITP_TCK

Place near JITP

A A

5

TEST1

R1120

1K_0402_5%~D@

1 2

+VCCP

+VCCP

R12

56_0402_5%~D

H_THERMTRIP#

1 2

R17

200_0402_5%~D

H_PWRGOOD

1 2

4

Add pullups for PWRGOOD and THERMTRIP per INTEL

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

3

DELL CONFIDENTIAL/PROPRIETARY

Title

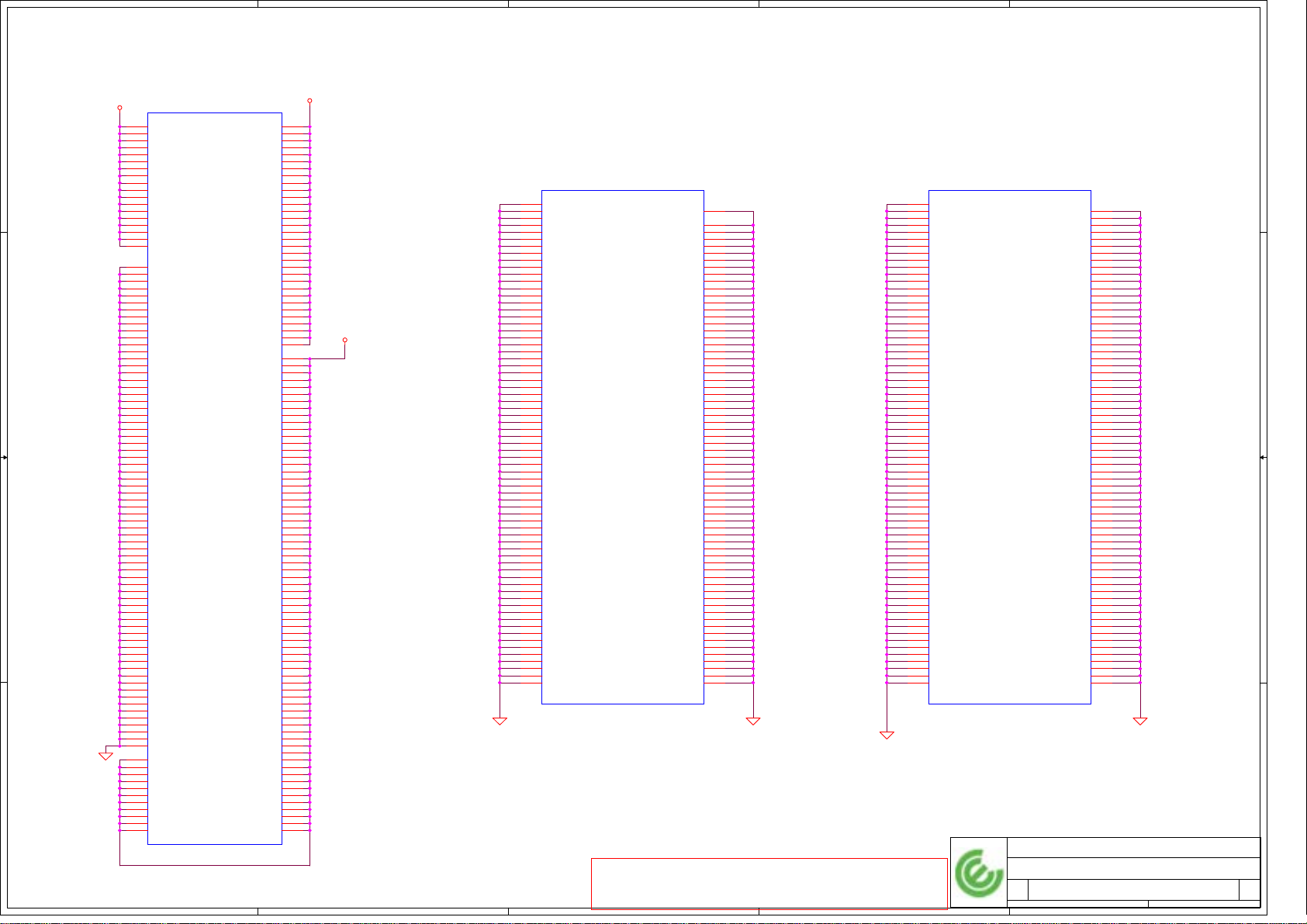

Dothan Processor in mFCPGA479

Size Document Number Rev

Board Number LA2111

2

Date: Sheet of

761Monday, February 09, 2004

1

0.3

Page 8

5

4

3

2

1

Dothan-A2 w/ 533Mhz supports both 1.5V and 1.8V.

Dothan-B step w/533Mhz supports only 1.5V

+1.8VRUN

2 1

+1.5VRUN

12

PAD-OPEN 2x2m~D

2 1

PAD-OPEN 2x2m~D

2

1

12

R646

27.4_0402_1%~D

D D

+VCCP

For test only ,Cmos output

CPU Voltage ID

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

C C

B B

Layout close CPU

12

R341 0_0402_5%~D

12

R337 0_0402_5%~D

12

R338 0_0402_5%~D

12

R339 0_0402_5%~D

12

R340 0_0402_5%~D

12

R747 0_0402_5%~D

V_CPU_GTLREF

2

1

+VCCP

RN9

10K_1206_8P4R_5%~D@

VID0

VID1

VID2

VID3

VID4

VID5

R_A

R50

1K_0603_1%~D

R_B

R51

2K_0603_1%~D

2

2

1

1

B_VID4

OPEN~D

B_VID6

OPEN~D

2

1

OPEN OPEN OPEN OPEN OPEN OPEN

12

12

12

12

1 8

2 7

3 6

4 5

2

2

1

1

10K_0402_5%~D@

R333

B_VID3

OPEN~D

R746

10K_0402_5%~D@

2

2

1

1

B_VID2

OPEN~D

R644

B_VID1

OPEN~D

2

2

1

1

12

R645

54.9_0402_1%~D

27.4_0402_1%~D

OPEN

PJP17

PJP16

SHORT

B_VID5

OPEN~D

2

1

R647

54.9_0402_1%~D

+1.8VS_PROC

1

C997

2

0.01U_0402_16V7K~D

VID0 <<49>>

VID1 <<49>>

VID2 <<49>>

VID3 <<49>>

VID4 <<49>>

VID5 <<49>>

Resistor placed within

0.5" of CPU pin.Trace

12

should be at least 25

miles away from any

other toggling signal.

1

C998

2

10U_0805_6.3V6M~D

H_PSI#<<49>>

54.9_0603_1%~D@

1 2

1 2

54.9_0603_1%~D@

+VCC_CORE

V_CPU_GTLREF

CPU_BSEL0<<6>>

CPU_BSEL1<<6>>

R634

R635

+VCCP

VCCSENSE

VSSSENSE

H_PSI#

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

CPU_BSEL0

CPU_BSEL1

COMP0

COMP1

COMP2

COMP3

AC26

AD26

AE7

AF6

F26

P23

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

F16

L21

M22

N21

P22

R21

T22

U21

D18

D20

D22

E17

E19

E21

F18

C16

C14

P25

P26

AB2

AB1

E26

AF7

AC1

B1

N1

W4

K6

L5

M6

N5

P6

R5

T6

D6

D8

E5

E7

E9

F6

F8

E1

E2

F2

F3

G3

G4

H4

B2

C3

JCPUB

VCCSENSE

VSSSENSE

VCCA0

VCCA1

VCCA2

VCCA3

VCCQ0

VCCQ1

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCCP

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

PSI#

VID0

VID1

VID2

VID3

VID4

VID5

GTLREF

BSEL0

BSEL1

COMP0

COMP1

COMP2

COMP3

RSVD

RSVD

RSVD

RSVD

RSVD

A2

VSS

A5

VSS

A8

VSS

A11

VSS

A14

VSS

A17

VSS

A20

VSS

A23

VSS

A26

VSS

B3

VSS

B6

VSS

B9

VSS

B12

Dothan

AMP_1473129-1_Dothan~D

VSS

B16

VSS

B19

VSS

B22

VSS

B25

VSS

C1

VSS

C4

VSS

C7

VSS

C10

VSS

C13

VSS

C15

VSS

C18

VSS

C21

VSS

C24

VSS

D2

VSS

D5

VSS

D7

VSS

D9

VSS

D11

VSS

D13

VSS

D15

VSS

D17

VSS

D19

VSS

D21

VSS

D23

VSS

D26

VSS

E3

VSS

E6

VSS

E8

VSS

E10

VSS

E12

VSS

E14

VSS

E16

VSS

E18

VSS

E20

VSS

E22

VSS

POWER, GROUNG, RESERVED SIGNALS AND NC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

+VCC_CORE

W21

AA11

AA13

AA15

AA17

AA19

AA21

AB10

AB12

AB14

AB16

AB18

AB20

AB22

AC11

AC13

AC15

AC17

AC19

AD10

AD12

AD14

AD16

AD18

AE11

AE13

AE15

AE17

AE19

AF10

AF12

AF14

AF16

AF18

M21

M24

F20

F22

G5

G21

H6

H22

J5

J21

K22

U5

V6

V22

W5

Y6

Y22

AA5

AA7

AA9

AB6

AB8

AC9

AD8

AE9

AF8

M4

M5

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

R6

R22

R25

T3

T5

T21

T23

JCPUC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

POWER, GROUND

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Dothan

AMP_1473129-1_Dothan~D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Dothan Processor in mFCPGA479

Size Document Number Rev

Board Number LA2111

Date: Sheet of

861Monday, February 09, 2004

1

0.3

Page 9

5

4

3

2

1

+VCC_CORE

1

C415

10U_0805_4VAM~D

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C403

10U_0805_4VAM~D

C404

10U_0805_4VAM~D

C376

10U_0805_4VAM~D

D D

C C

1

C386

10U_0805_4VAM~D

2

1

C418

10U_0805_4VAM~D

2

1

C440

10U_0805_4VAM~D

2

1

C414

10U_0805_4VAM~D

2

1

C412

10U_0805_4VAM~D

2

1

C413

10U_0805_4VAM~D

2

1

C396

10U_0805_4VAM~D

2

1

C445

10U_0805_4VAM~D

2

1

C406

10U_0805_4VAM~D

2

1

C378

10U_0805_4VAM~D

2

1

C387

10U_0805_4VAM~D

2

1

C398

10U_0805_4VAM~D

2

1

C395

10U_0805_4VAM~D

2

1

C405

10U_0805_4VAM~D

2

1

C439

10U_0805_4VAM~D

2

1

C444

10U_0805_4VAM~D

2

+VCC_CORE

1

2

+VCC_CORE

1

2

+VCC_CORE

1

2

C925

10U_0805_4VAM~D

C427

10U_0805_4VAM~D

C441

10U_0805_4VAM~D

1

C926

10U_0805_4VAM~D

2

1

C379

10U_0805_4VAM~D

2

1

C394

10U_0805_4VAM~D

2

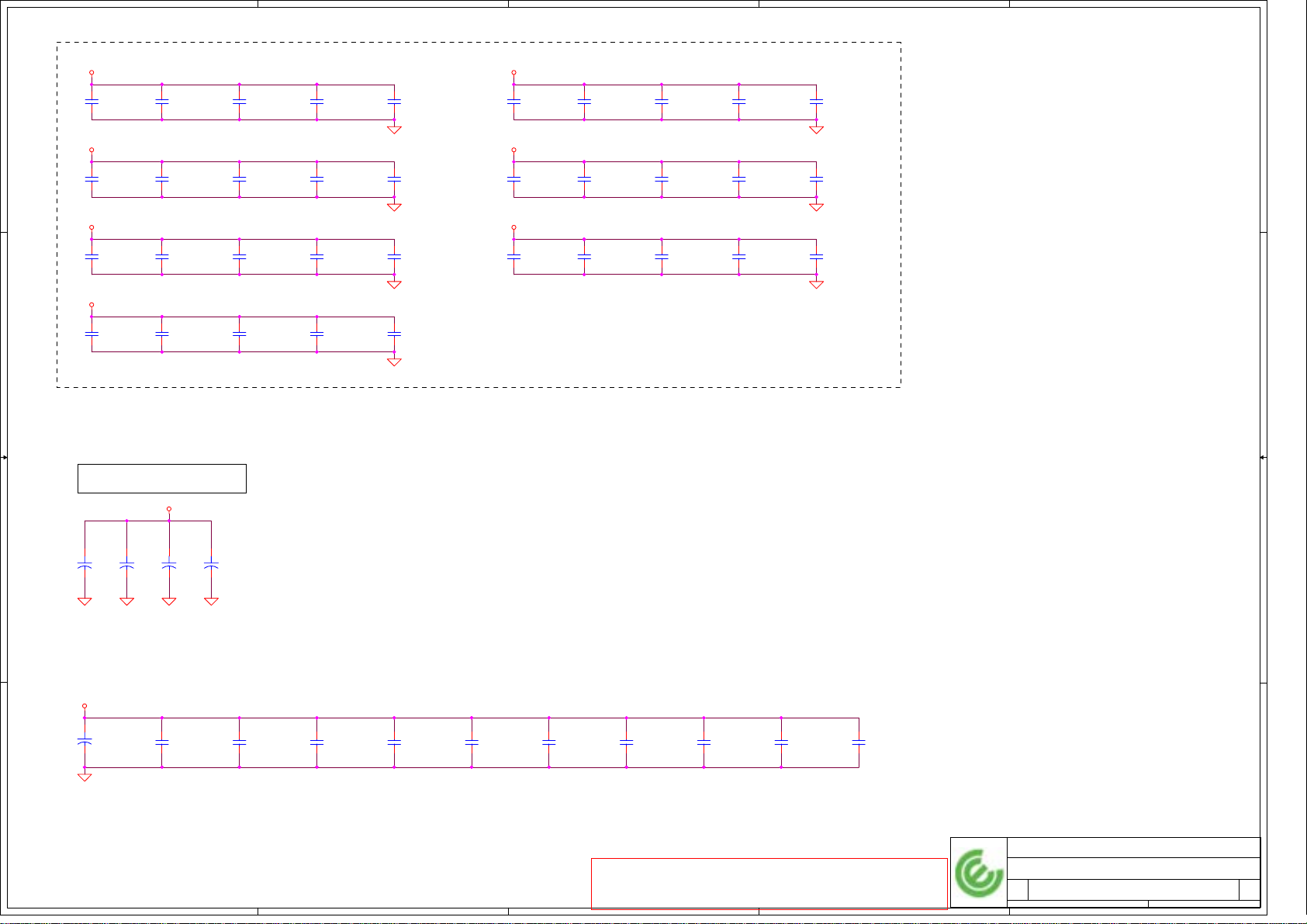

10uF 0805 X6S -> 105 degree

1

C927

10U_0805_4VAM~D

2

1

C373

10U_0805_4VAM~D

2

1

C372

10U_0805_4VAM~D

2

1

C928

10U_0805_4VAM~D

2

1

C438

10U_0805_4VAM~D

2

1

C374

10U_0805_4VAM~D

2

High Frequence Decoupling

1

C929

10U_0805_4VAM~D

2

1

C377

10U_0805_4VAM~D

2

1

C426

10U_0805_4VAM~D

2

Near VCORE regulator.

+VCC_CORE

1

1

+

+

C942

B B

A A

C941

330U_D2E_2.5VM_R9~D

2

9mOhm

7343

PS CAP

+VCCP

1

2

+

C731

150U_D2_4VK~D

2

330U_D2E_2.5VM_R9~D

9mOhm

7343

PS CAP

C943

330U_D2E_2.5VM_R9~D

9mOhm

7343

PS CAP

1

2

1

1

+

C944

2

2

220U_D2_2VM~D

@

C732

0.1U_0402_10V7K~D

+

ESR <= 3m ohm

Capacitor > 880uF

1

C733

0.1U_0402_10V7K~D

2

1

C734

0.1U_0402_10V7K~D

2

1

C735

0.1U_0402_10V7K~D

2

1

C736

0.1U_0402_10V7K~D

2

1

C737

0.1U_0402_10V7K~D

2

1

C738

0.1U_0402_10V7K~D

2

1

C739

0.1U_0402_10V7K~D

2

1

C740

0.1U_0402_10V7K~D

2

1

C741

0.1U_0402_10V7K~D

2

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

CPU Bypass

Size Document Number Rev

Board Number LA2111

Date: Sheet of

961Monday, February 09, 2004

1

0.3

Page 10

5

4

3

2

1

U68B

AA31

DMIRXN0

AB35

DMIRXN1

AC31

DMIRXN2

AD35

DMIRXN3

Y31

DMIRXP0

AA35

DMIRXP1

AB31

DMIRXP2

AC35

DMIRXP3

AA33

DMITXN0

AB37

DMITXN1

AC33

DMITXN2

AD37

DMITXN3

Y33

DMITXP0

AA37

DMITXP1

AB33

DMITXP2

AC37

DMITXP3

AM33

SM_CK0

AL1

SM_CK1

AE11

SM_CK2

AJ34

SM_CK3

AF6

SM_CK4

AC10

SM_CK5

AN33

SM_CK0#

AK1

SM_CK1#

AE10

SM_CK2#

AJ33

SM_CK3#

AF5

SM_CK4#

AD10

SM_CK5#

AP21

SM_CKE0

AM21

SM_CKE1

AH21

SM_CKE2

AK21

SM_CKE3

AN16

SM_CS0#

AM14

SM_CS1#

AH15

SM_CS2#

AG16

SM_CS3#

AF22

SM_OCDCOMP0

AF16

SM_OCDCOMP1

AP14

SM_ODT0

AL15

SM_ODT1

AM11

SM_ODT2

AN10

SM_ODT3

AK10

SMRCOMPN

AK11

SMRCOMPP

AF37

SMVREF0

AD1

SMVREF1

AE27

SMXSLEWIN

AE28

SMXSLEWOUT

AF9

SMYSLEWIN

AF10

SMYSLEWOUT

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

DMIDDR MUXING

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

CFG/RSVD

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

PM

RSTIN#

DREF_CLKN

DREF_CLKP

DREF_SSCLKP

DREF_SSCLKN

CLK

NC1

NC2

NC3

NC4

NC5

NC6

NC7

NC8

NC

NC9

NC10

NC11

ALVISO_BGA1257~D

PM_EXTTS#0

PM_EXTTS#1

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

J23

J21

H22

F5

AD30

AE29

A24

A23

D37

C37

AP37

AN37

AP36

AP2

AP1

AN1

B1

A2

B37

A36

A37

CFG0

MCH_CLKSEL1

MCH_CLKSEL0

CFG5

CFG6

CFG7

CFG9

CFG12

CFG13

CFG16

CFG18

CFG19

THERMTRIP_MCH#

PM_EXTTS#0

PM_EXTTS#1

THERMTRIP_MCH#

IMVP_PWRGD

PLTRST_R#

+1.5VRUN

R898

10K_0402_5%~D

R899

10K_0402_5%~D

CFG0 <<12>>

MCH_CLKSEL1 <<6>>

MCH_CLKSEL0 <<6>>

CFG5 <<12>>

CFG6 <<12>>

CFG7 <<12>>

CFG9 <<12>>

CFG12 <<12>>

CFG13 <<12>>

CFG16 <<12>>

CFG18 <<12>>

CFG19 <<12>>

R1113

56_0402_5%~D

1 2

PM_BMBUSY# <<22>>

THERMTRIP_MCH# <<39>>

IMVP_PWRGD <<22,42,49>>

1 2

R1030 100_0603_1%~D

+2.5VRUN

12

12

+VCCP

PLTRST_MCH# <<20>>

M_ODT0<<16>>

M_ODT1<<16,17>>

M_ODT2<<17>>

M_ODT3<<17>>

M_OCDOCMP0

M_OCDOCMP1

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR3

M_CLK_DDR4

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#3

M_CLK_DDR#4

DDR_CKE0_DIMMA

DDR_CKE1_DIMMA

DDR_CKE2_DIMMB

DDR_CKE3_DIMMB

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_OCDOCMP0

M_OCDOCMP1

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SMRCOMPN

SMRCOMPP

1

C753

C752

2

0.1U_0402_16V4Z~D

1

2

0.1U_0402_16V4Z~D

DMI_TXN0<<22>>

DDR_CKE0_DIMMA<<16>>

DDR_CKE1_DIMMA<<16>>

DDR_CKE2_DIMMB<<17>>

DDR_CKE3_DIMMB<<17>>

DDR_CS0_DIMMA#<<16>>

DDR_CS1_DIMMA#<<16>>

DDR_CS2_DIMMB#<<17>>

DDR_CS3_DIMMB#<<16,17>>

1 2

V_DDR_MCH_REF<<16,17,48>>

12

R699

DMI_TXN1<<22>>

DMI_TXN2<<22>>

DMI_TXN3<<22>>

DMI_TXP0<<22>>

DMI_TXP1<<22>>

DMI_TXP2<<22>>

DMI_TXP3<<22>>

DMI_RXN0<<22>>

DMI_RXN1<<22>>

DMI_RXN2<<22>>

DMI_RXN3<<22>>

DMI_RXP0<<22>>

DMI_RXP1<<22>>

DMI_RXP2<<22>>

DMI_RXP3<<22>>

M_CLK_DDR0<<16>>

M_CLK_DDR1<<16>>

M_CLK_DDR3<<17>>

M_CLK_DDR4<<17>>

M_CLK_DDR#0<<16>>

M_CLK_DDR#1<<16>>

M_CLK_DDR#3<<17>>

M_CLK_DDR#4<<17>>

12

40.2_0603_1%~D

R10

0_0402_5%~D

@

1 2

U68A

G9

HA3#

C9

HA4#

E9

HA5#

B7

HA6#

A10

HA7#

F9

HA8#

D8

HA9#

B10

HA10#

E10

HA11#

G10

HA12#

D9

HA13#

E11

HA14#

F10

HA15#

G11

HA16#

G13

HA17#

C10

HA18#

C11

HA19#

D11

HA20#

C12

HA21#

B13

HA22#

A12

HA23#

F12

HA24#

G12

HA25#

E12

HA26#

C13

HA27#

B11

HA28#

D13

HA29#

A13

HA30#

F13

HA31#

A11

HPCREQ#

A7

HREQ#0

D7

HREQ#1

B8

HREQ#2

C7

HREQ#3

A8

HREQ#4

B9

HADSTB#0

E13

HADSTB#1

AB1

HCLKN

AB2

HCLKIN

G4

HDSTBN#0

K1

HDSTBN#1

R3

HDSTBN#2

V3

HDSTBN#3

G5

HDSTBP#0

K2

HDSTBP#1

R2

HDSTBP#2

W4

HDSTBP#3

H8

HDINV#0

K3

HDINV#1

T7

HDINV#2

U5

HDINV#3

H10

HCPURST#

F8

HADS#

B5

HTRDY#

G6

HDPWR#

F7

HDRDY#

E6

HDEFER#

F6

HEDRDY#

D6

HHITM#

D4

HHIT#

B3

HLOCK#

E7

HBREQ0#

A5

HBNR#

D5

HBPRI#

C6

HDBSY#

G8

HSLPCPU#

A4

HRS0#

C5

HRS1#

B4

HRS2#

ALVISO_BGA1257~D

Alviso

HOST

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HVREF

HXRCOMP

HXSCOMP

HYRCOMP

HYSCOMP

HXSWING

HYSWING

H_D#0

E4

H_D#1

E1

H_D#2

F4

H_D#3

H7

H_D#4

E2

H_D#5

F1

H_D#6

E3

H_D#7

D3

H_D#8

K7

H_D#9

F2

H_D#10

J7

H_D#11

J8

H_D#12

H6

H_D#13

F3

H_D#14

K8

H_D#15

H5

H_D#16

H1

H_D#17

H2

H_D#18

K5

H_D#19

K6

H_D#20

J4

H_D#21

G3

H_D#22

H3

H_D#23

J1

H_D#24

L5

H_D#25

K4

H_D#26

J5

H_D#27

P7

H_D#28

L7

H_D#29

J3

H_D#30

P5

H_D#31

L3

H_D#32

U7

H_D#33

V6

H_D#34

R6

H_D#35

R5

H_D#36

P3

H_D#37

T8

H_D#38

R7

H_D#39

R8

H_D#40

U8

H_D#41

R4

H_D#42

T4

H_D#43

T5

H_D#44

R1

H_D#45

T3

H_D#46

V8

H_D#47

U6

H_D#48

W6

H_D#49

U3

H_D#50

V5

H_D#51

W8

H_D#52

W7

H_D#53

U2

H_D#54

U1

H_D#55

Y5

H_D#56

Y2

H_D#57

V4

H_D#58

Y7

H_D#59

W1

H_D#60

W3

H_D#61

Y3

H_D#62

Y6

H_D#63

W2

H_VREF

J11

H_XRCOMP

C1

H_XSCOMP

C2

H_YRCOMP

T1

H_YSCOMP

L1

H_SWNG0

D1

H_SWNG1

P1

D D

C C

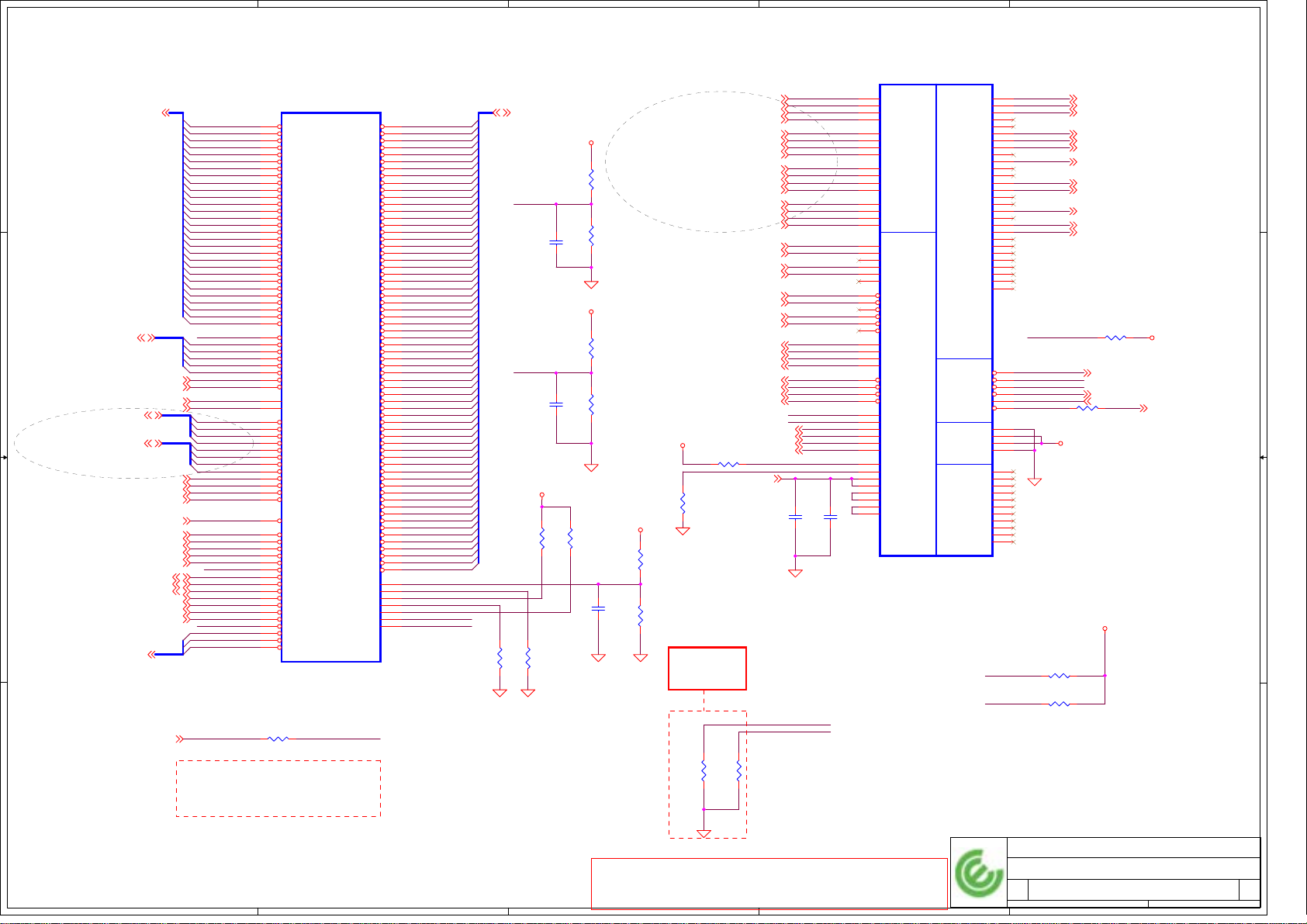

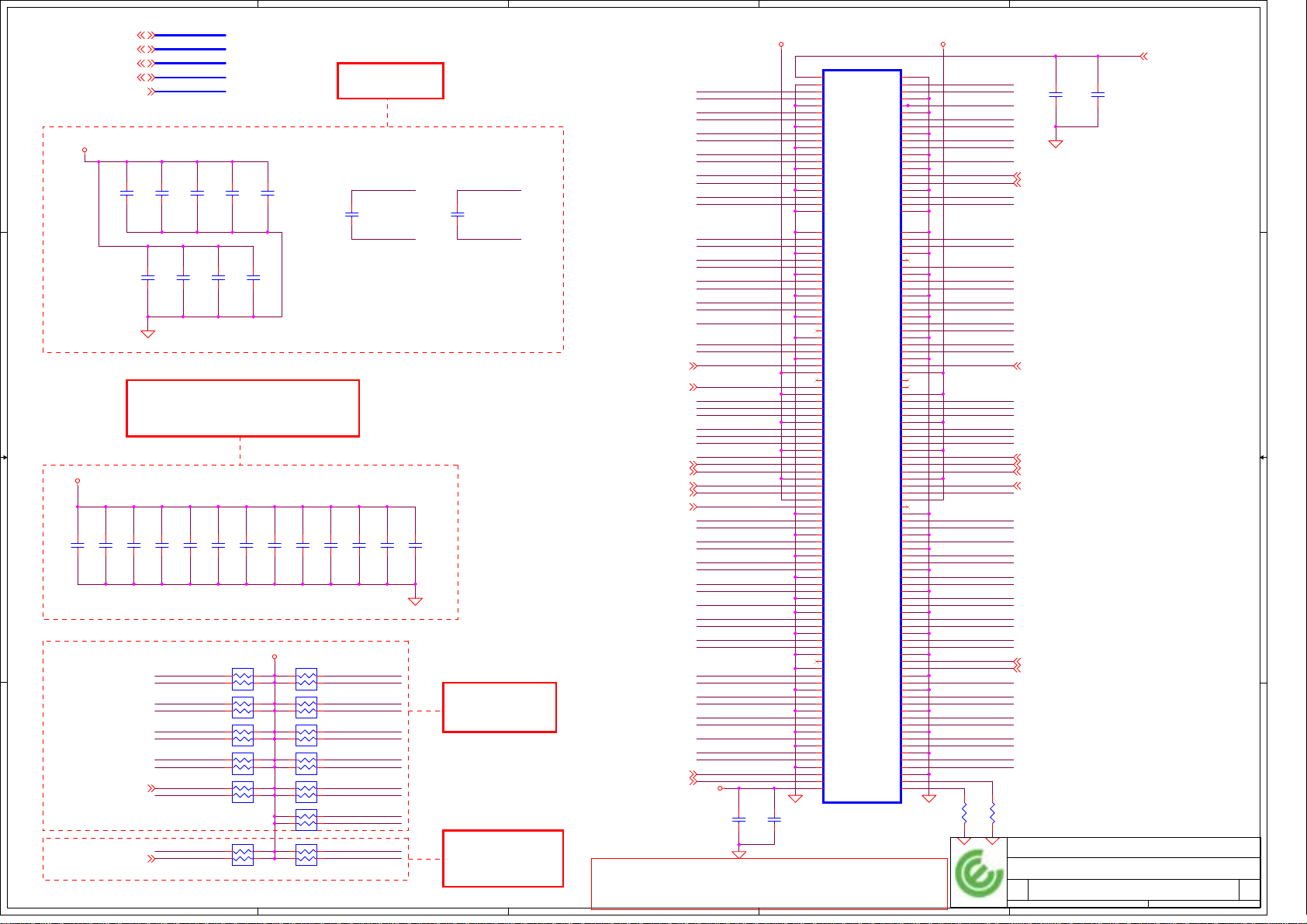

Layout Guide will show

these signals routed

differentially.

B B

A A

H_A#[3..31]<<7>>

H_REQ#[0..4]<<7>>

H_ADSTB#0<<7>>

H_ADSTB#1<<7>>

CLK_MCH_BCLK#<<6>>

CLK_MCH_BCLK<<6>>

H_DSTBN#[0..3]<<7>>

H_DSTBP#[0..3]<<7>>

H_DINV#0<<7>>

H_DINV#1<<7>>

H_DINV#2<<7>>

H_DINV#3<<7>>

H_RESET#<<7>>

H_ADS#<<7>>

H_TRDY#<<7>>

H_DPWR#<<7>>

H_DRDY#<<7>>

H_DEFER#<<7>>

H_HITM#<<7>>

H_HIT#<<7>>

H_LOCK#<<7>>

H_BR0#<<7>>

H_BNR#<<7>>

H_BPRI#<<7>>

H_DBSY#<<7>>

H_RS#[0..2]<<7>>

H_CPUSLP#<<7,21>>

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

TP_H_PCREQ#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_ADSTB#0

H_ADSTB#1

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_RESET#

H_ADS#

H_TRDY#

H_DPWR#

H_DRDY#

H_DEFER#

TP_H_EDRDY#

H_HITM#

H_HIT#

H_LOCK#

H_BR0#

H_BNR#

H_BPRI#

H_DBSY#

H_R_CPUSLP#

H_RS#0

H_RS#1

H_RS#2

H_CPUSLP# H_R_CPUSLP#

Note:

"Do not install R10 for Dothan-A,

Install R10 for Dothan-B"

12

R13

24.9_0603_1%~D

H_D#[0..63] <<7>>

H_SWNG1

1

2

C743

0.1U_0402_16V4Z~D

H_SWNG0

1

2

C744

0.1U_0402_16V4Z~D

+VCCP

12

R661

R660

54.9_0603_1%~D

12

R11

24.9_0603_1%~D

+VCCP

12

R649

221_0603_1%~D

12

R650

100_0603_1%~D

+VCCP

12

R652

221_0603_1%~D

12

R653

100_0603_1%~D

12

54.9_0603_1%~D

C745

0.1U_0402_10V6K~D

1

2

Layout Guide

will show these

signals routed

differentially.

+VCCP

12

R656

100_0402_1%~D

12

R657

200_0402_1%~D

+1.8VSUS

R8 80.6_0603_1%~D

12

R9

80.6_0603_1%~D

Layout Note:

Rote as short

as possible

R648

40.2_0603_1%~D

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Alviso(1 of 5)

Size Document Number Rev

Board Number LA2111

Date: Sheet of

10 61Monday, February 09, 2004

1

0.3

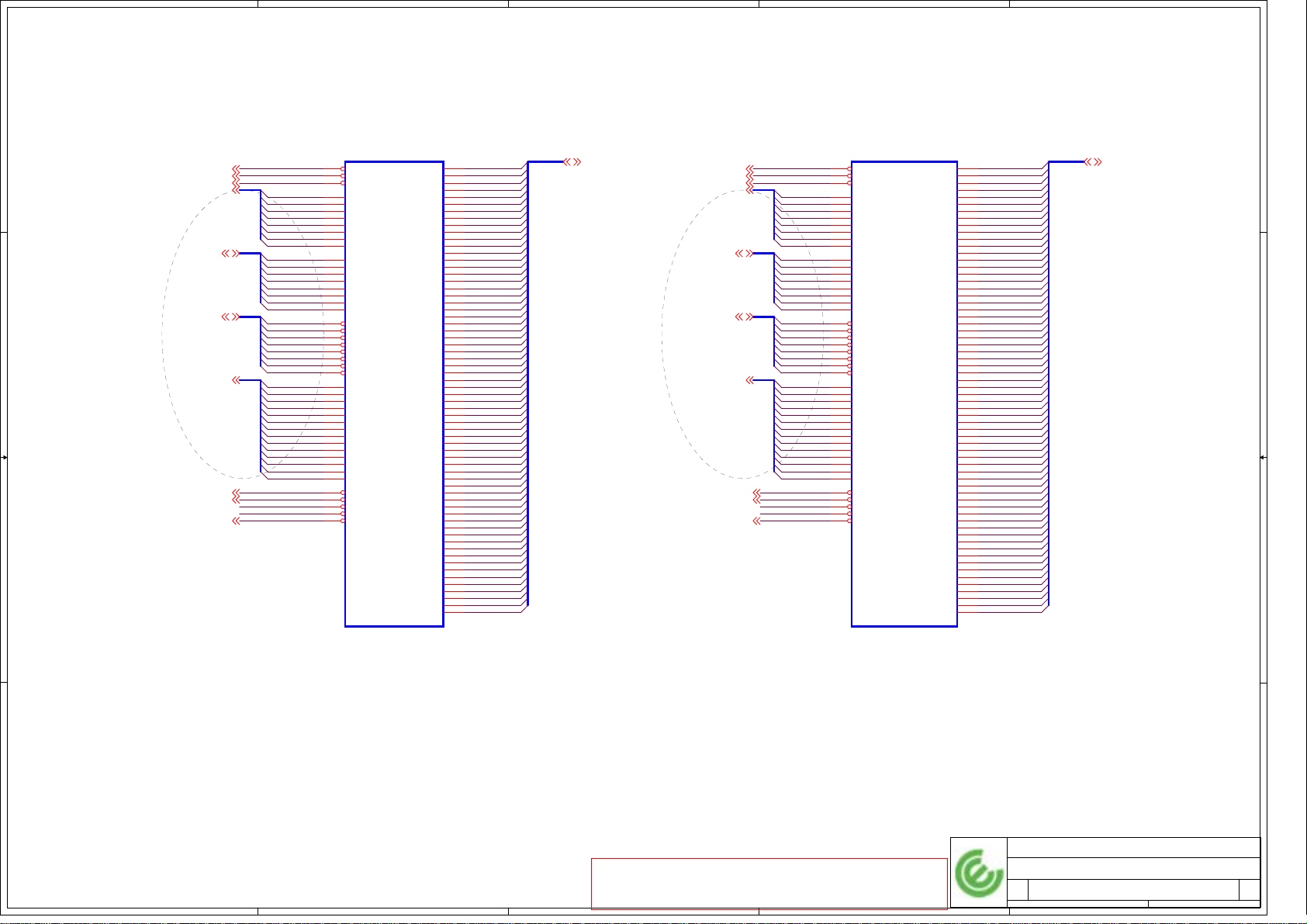

Page 11

5

D D

4

3

2

1

DDR_A_BS#0<<16>>

DDR_A_BS#1<<16>>

DDR_A_BS#2<<16>>

DDR_A_DM[0..7]<<16>>

DDR_A_DQS[0..7]<<16>>

This Symbol as same

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

C C

B B

DDR_A_DQS#[0..7]<<16>>

DDR_A_MA[0..13]<<16>>

DDR_A_CAS#<<16,17>>

DDR_A_RAS#<<16>>

DDR_A_WE#<<16>>

DDR_A_BS#0

DDR_A_BS#1

DDR_A_BS#2

DDR_A_DM0

DDR_A_DM1

DDR_A_DM2

DDR_A_DM3

DDR_A_DM4

DDR_A_DM5

DDR_A_DM6

DDR_A_DM7

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_CAS#

DDR_A_RAS#

TP_MA_RCVENIN#

TP_MA_RCVENOUT#

DDR_A_WE#

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AK36

AP33

AN29

AP23

AM8

AM4

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

AP9

AP4

AJ2

AD3

AJ1

AE5

AE4

U68C

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_RCVENOUT#

SA_WE#

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

SADQ32

SADQ33

SADQ34

SADQ35

SADQ36

SADQ37

SADQ38

SADQ39

SADQ40

SADQ41

SADQ42

DDR MEMORY SYSTEM A

SADQ43

SADQ44

SADQ45

SADQ46

SADQ47

SADQ48

SADQ49

SADQ50

SADQ51

SADQ52

SADQ53

SADQ54

SADQ55

SADQ56

SADQ57

SADQ58

SADQ59

SADQ60

SADQ61

SADQ62

SADQ63

ALVISO_BGA1257~D

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AM9

AL9

AL6

AP7

AP11

AP10

AL7

AM7

AN5

AN6

AN3

AP3

AP6

AM6

AL4

AM3

AK2

AK3

AG2

AG1

AL3

AM2

AH3

AG3

AF3

AE3

AD6

AC4

AF2

AF1

AD4

AD5

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

This Symbol as same

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

DDR_B_BS#0<<17>>

DDR_B_BS#1<<17>>

DDR_B_BS#2<<17>>

DDR_B_DM[0..7]<<17>>

DDR_B_DQS[0..7]<<17>>

DDR_B_DQS#[0..7]<<17>>

DDR_B_MA[0..13]<<17>>

DDR_B_CAS#<<17>>

DDR_B_RAS#<<17>>

DDR_B_WE#<<16,17>>

DDR_B_BS#0

DDR_B_BS#1 DDR_B_D1

DDR_B_BS#2

DDR_B_DM0

DDR_B_DM1

DDR_B_DM2

DDR_B_DM3

DDR_B_DM4

DDR_B_DM5

DDR_B_DM6

DDR_B_DM7

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_CAS#

DDR_B_RAS#

TP_MB_RCVENIN#

TP_MB_RCVENOUT#

DDR_B_WE#

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AF34

AK32

AJ28

AK23

AM10

AF35

AK33

AK28

AJ23

AL10

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

AK5

AE7

AB7

AH6

AF8

AB4

AH7

AF7

AB5

U68D

SB_BS0#

SB_BS1#

SB_BS2#

SD_DM0

SD_DM1

SD_DM2

SD_DM3

SD_DM4

SD_DM5

SD_DM6

SD_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_RCVENOUT#

SB_WE#

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

SBDQ15

SBDQ16

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

SBDQ31

SBDQ32

SBDQ33

SBDQ34

SBDQ35

SBDQ36

SBDQ37

SBDQ38

SBDQ39

SBDQ40

SBDQ41

DDR SYSTEM MEMORY B

SBDQ42

SBDQ43

SBDQ44

SBDQ45

SBDQ46

SBDQ47

SBDQ48

SBDQ49

SBDQ50

SBDQ51

SBDQ52

SBDQ53

SBDQ54

SBDQ55

SBDQ56

SBDQ57

SBDQ58

SBDQ59

SBDQ60

SBDQ61

SBDQ62

SBDQ63

ALVISO_BGA1257~D

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AJ31

AK30

AJ30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AJ22

AK22

AH24

AH23

AG22

AJ21

AG10

AG9

AG8

AH8

AH11

AH10

AJ9

AK9

AJ7

AK6

AJ4

AH5

AK8

AJ8

AJ5

AK4

AG5

AG4

AD8

AD9

AH4

AG6

AE8

AD7

AC5

AB8

AB6

AA8

AC8

AC7

AA4

AA5

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

DDR_B_D0

AE31

SBDQ0

AE32

DDR_B_D[0..63] <<17>>DDR_A_D[0..63] <<16>>

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

Alviso(2 of 5)

Size Document Number Rev

Board Number LA2111

Date: Sheet of

11 61Monday, February 09, 2004

1

0.3

Page 12

5

4

3

2

1

U68G

H24

SDVOCTRL_DATA

H25

SDVOCTRL_CLK

CLK_MCH_3GPLL#<<6>>

D D

C C

B B

CLK_MCH_3GPLL<<6>>

+VCCP

AB29

AC29

A15

C16

A17

J18

B15

B16

B17

E24

E23

E21

D21

C20

B20

A19

B19

H21

G21

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

GCLKN

GCLKP

TVDAC_A

TVDAC_B

TVDAC_C

TV_REFSET

TV_IRTNA

TV_IRTNB

TV_IRTNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

VSYNC

HSYNC

REFSET

LBKLT_CTL

LBKLT_EN

LCTLA_CLK

LCTLB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

EXP_ICOMPO

MISC

TVVGALVDS

PCI - EXPRESS GRAPHICS

EXP_COMPI

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

D36

D34

E30

F34

G30

H34

J30

K34

L30

M34

N30

P34

R30

T34

U30

V34

W30

Y34

D30

E34

F30

G34

H30

J34

K30

L34

M30

N34

P30

R34

T30

U34

V30

W34

E32

F36

G32

H36

J32

K36

L32

M36

N32

P36

R32

T36

U32

V36

W32

Y36

D32

E36

F32

G36

H32

J36

K32

L36

M32

N36

P32

R36

T32

U36

V32

W36

PEGCOMP

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

24.9_0603_1%~D

1 2

PEG_RXN[0..15]

PEG_RXP[0..15]

PEG_TXN[0..15]

PEG_TXP[0..15]

R44

+1.5VRUN_PCIE

PEG_RXN[0..15] <<18>>

PEG_RXP[0..15] <<18>>

This Symbol as same

as Intel CRB

schematic, So Layout

Guide will show these

signals routed

differentially.

PEG_TXN[0..15] <<18>>

PEG_TXP[0..15] <<18>>

CFG[2:0]

CFG5

CFG6

CFG7

CFG9

CFG[13:12]

CFG16

(FSB Dynamic

ODT)

CFG18

(VCC Select)

CFG19

(VTT Select)

Refer to sheet 6 for FSB

frequency select

Low = DMI x 2

High = DMI x 4

Low = DDR-II

High = DDR-I

*

*

Low = DT/Transportable CPU

High = Mobile CPU

Low = Reverse Lane

*

High = Normal Operation

00 = Reserved

01 = XOR Mode Enabled

10 = All Z Mode Enabled

11 = Normal Operation (Default)

Low = Disabled

High = Enabled

Low = 1.05V (Default)

High = 1.5V

*

*

Low = 1.05V (Default)

High = 1.2V

+VCCP

R20 10K_0402_5%~D

CFG0<<10>>

R52 2.2K_0402_5%~D@

CFG5<<10>>

R55 2.2K_0402_5%~D

CFG6<<10>>

R56 2.2K_0402_5%~D@

CFG7<<10>>

R74 2.2K_0402_5%~D@

CFG9<<10>>

R906 2.2K_0402_5%~D@

CFG12<<10>>

R907 2.2K_0402_5%~D@

CFG13<<10>>

R97 2.2K_0402_5%~D@

*

CFG16<<10>>

12

1 2

1 2

1 2

1 2

1 2

1 2

1 2

CFG[17:3] have internal pull-up

*

+2.5VRUN

R118 1K_0402_5%~D@

CFG18<<10>>

CFG19<<10>>

*

1 2

1 2

R125 1K_0402_5%~D@

CFG[19:18] have internal pull-down

ALVISO_BGA1257~D

A A

DELL CONFIDENTIAL/PROPRIETARY

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

5

4

3

2

Title

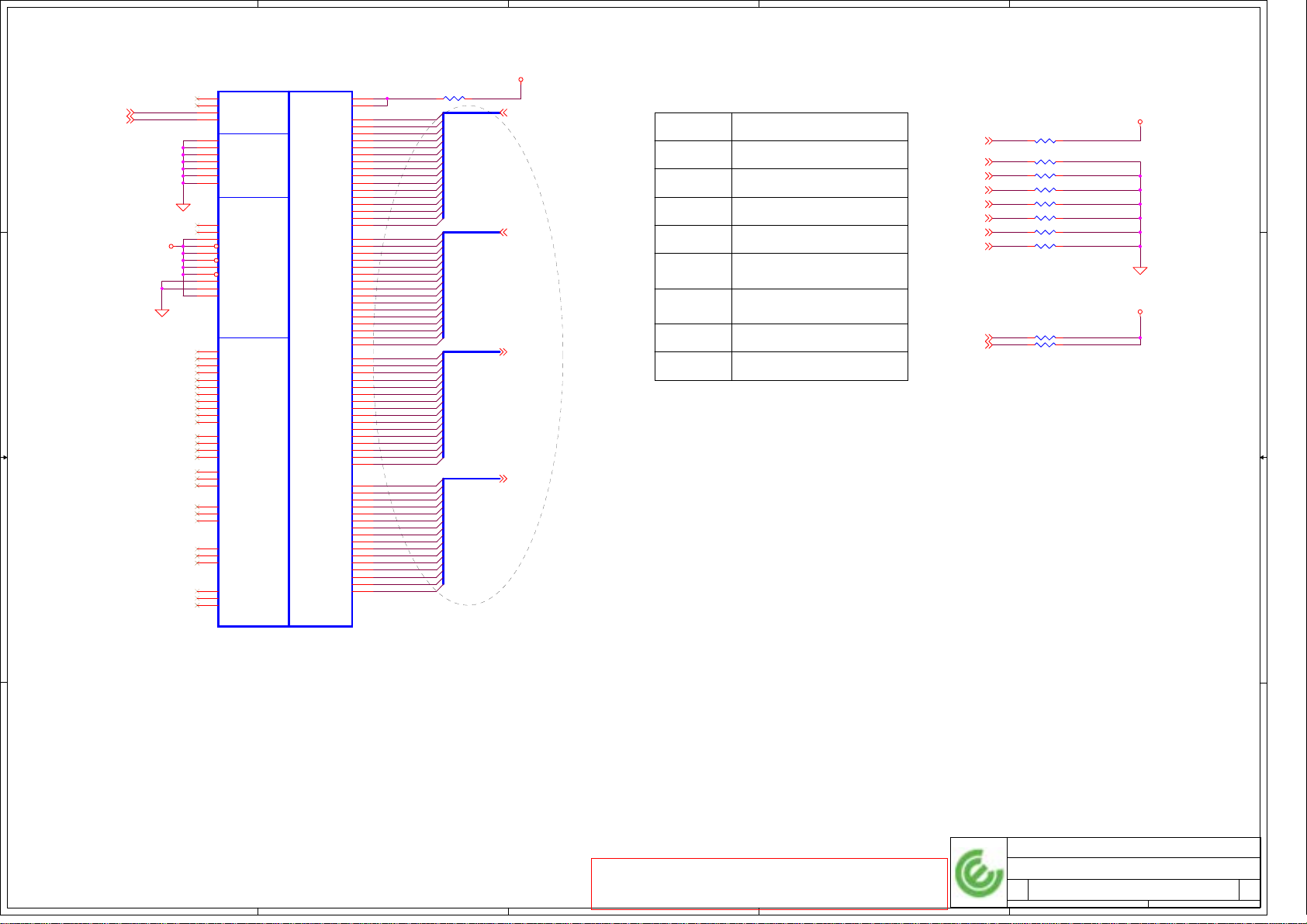

Alviso(3 of 5)

Size Document Number Rev

Board Number LA2111

Date: Sheet of

12 61Monday, February 09, 2004

1

0.3

Page 13

5

4

3

2

1

U68F

K13

VTT0

J13

VTT1

K12

VTT2

W11

VTT3

V11

VTT4

U11

VTT5

T11

VTT6

R11

VTT7

P11

POWER

VTT8

N11

VTT9

M11

1

2

C807

VTT10

L11

VTT11

K11

VTT12

W10

VTT13

V10

VTT14

U10

VTT15

T10

VTT16

R10

VTT17

P10

VTT18

N10

VTT19

M10

VTT20

K10

VTT21

J10

VTT22

Y9

VTT23

W9

VTT24

U9

VTT25

R9

VTT26

P9

VTT27

N9

VTT28

M9

VTT29

L9

VTT30

J9

VTT31

N8

VTT32

M8

VTT33

N7

VTT34

M7

VTT35

N6

VTT36

M6

VTT37

A6

VTT38

N5

VTT39

M5

VTT40

N4

VTT41

M4

VTT42

N3

VTT43

M3

VTT44

N2

VTT45

M2

VTT46

B2

VTT47

V1

VTT48

N1

VTT49

M1

VTT50

G1

VTT51

1

C806

2

0.22U_0603_10V7K~D

0.22U_0603_10V7K~D

D D

+VCCP

1

C805

C1023

2

4.7U_0805_6.3V6K~D

2.2U_0805_6.3V6K~D

1

C810

C C

2

0.47U_0603_16V7K~D

1

1

C808

2

2

0.47U_0603_16V7K~D

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

ALVISO_BGA1257~D

AM37

AH37

AP29

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AP13

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

AN12

AM12

AL12

AK12

AJ12

AH12

AG12

AF12

AE12

AD11

AC11

AB11

AB10

AB9

AP8

AM1

AE1

V1.8_DDR_CAP1

V1.8_DDR_CAP2

V1.8_DDR_CAP5

V1.8_DDR_CAP1

V1.8_DDR_CAP2

V1.8_DDR_CAP5

Note : All VCCSM pin

shorted internally.

V1.8_DDR_CAP6

V1.8_DDR_CAP4

V1.8_DDR_CAP3

1

1

C812

C811

2

2

10U_0805_4VAM~D

10U_0805_4VAM~D

V1.8_DDR_CAP6

V1.8_DDR_CAP4

V1.8_DDR_CAP3

1

2

1

2

+1.8VSUS

1

+

C98

2

330U_D2E_2.5VM~D@

W=20 mils

+VCCP

1

1

C30

C20

2

2

C1219

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

1

1

C37

0.1U_0402_10V7K~D

C45

C38

2

2

0.1U_0402_10V7K~D

0.1U_0402_10V7K~D

+1.5VRUN

+1.5VRUN_HPLL

+1.5VRUN_MPLL

Remove L6, C48, C51, Connect DPLLB directly to +1.5vrun

Remove L29, C47, C8, Connect DPLLA directly to +1.5vrun

Steven-01/09/2004

M29

M28

M27

W20

W18

T29

R29

N29

K29

J29

V28

U28

T28

R28

P28

N28

L28

K28

J28

H28

G28

V27

U27

T27

R27

P27

N27

L27

K27

J27

H27

K26

H26

K25

J25

K24

K23

K22

K21

U20

T20

K20

V19

U19

K19

V18

T18

K18

K17

AC2

AC1

B23

C35

AA1

AA2

U68E

VCC0

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCCD_HMPLL1

VCCD_HMPLL2

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

POWER

ALVISO_BGA1257~D

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCD_TVDAC

VCCDQ_TVDAC

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCCA_TVBG

VSSA_TVBG

VCCA_LVDS

VCCHV0

VCCHV1

VCCHV2

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GBG

VSSA_3GBG

VCC_SYNC

F17

E17

D18

C18

F18

E18

H18

G18

D19

H17

B26

B25

A25

A35

B22

B21

A21

B28

A28

A27

AF20

AP19

AF19

AF18

AE37

W37

U37