Page 1

A

1 1

B

C

D

E

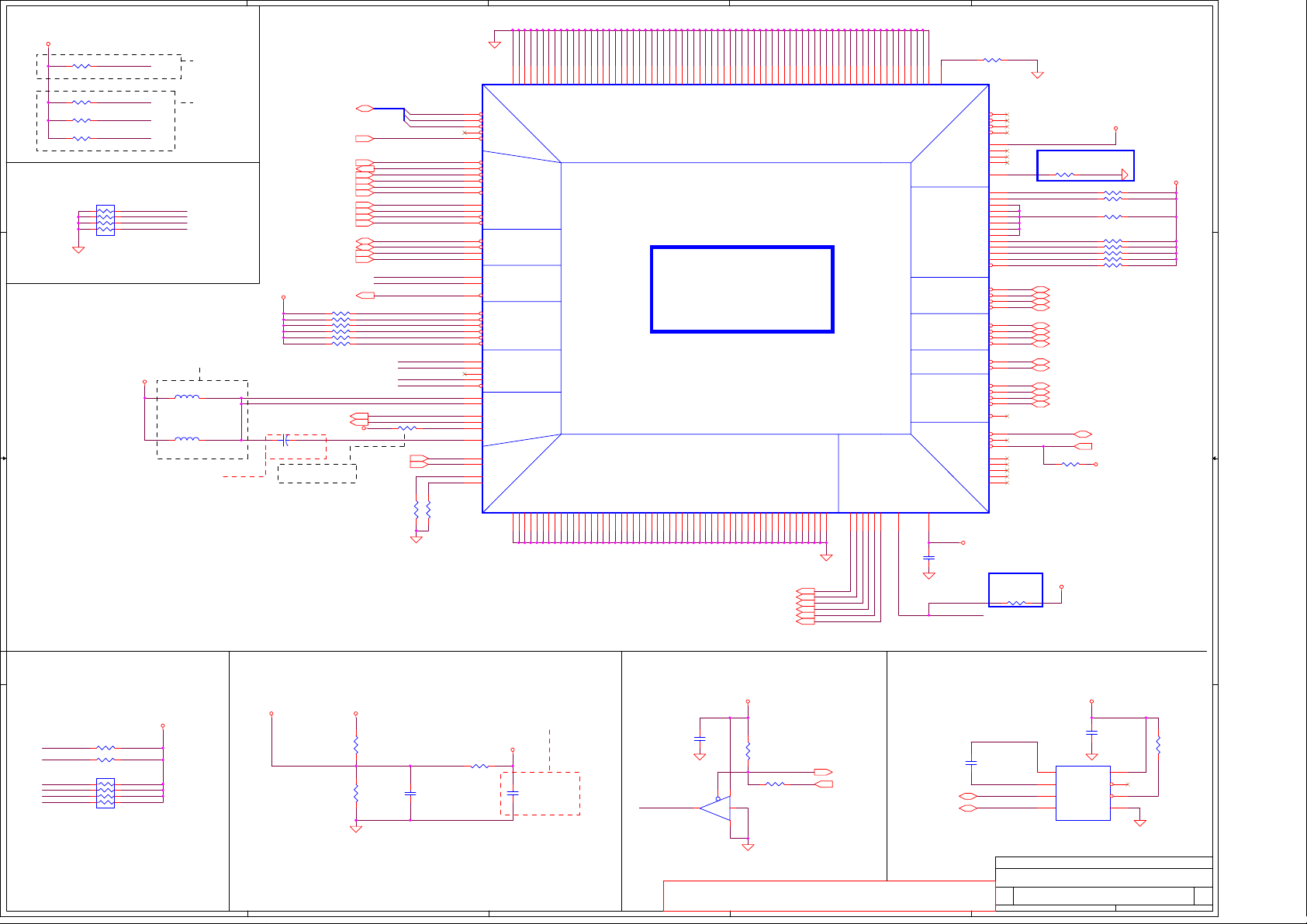

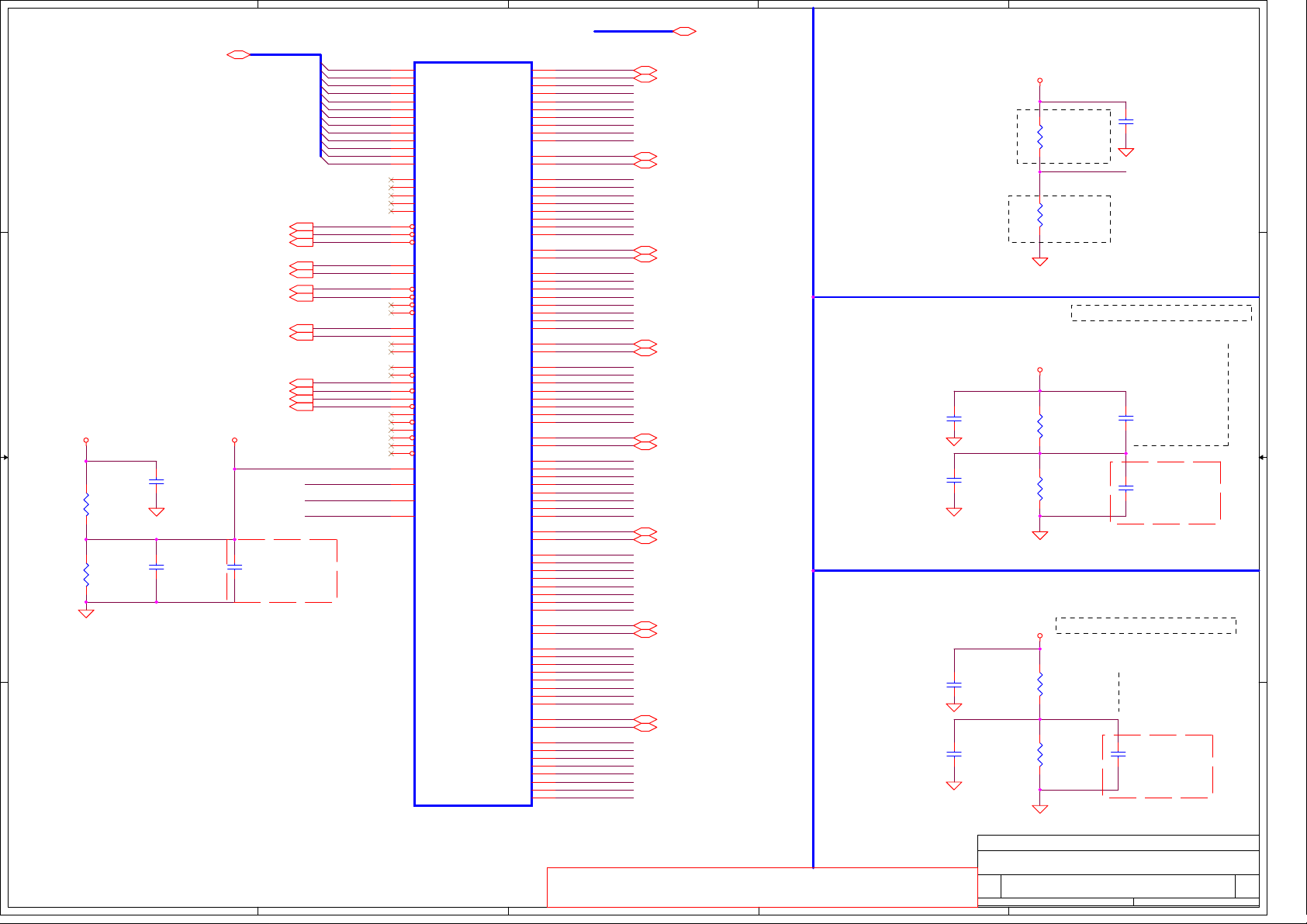

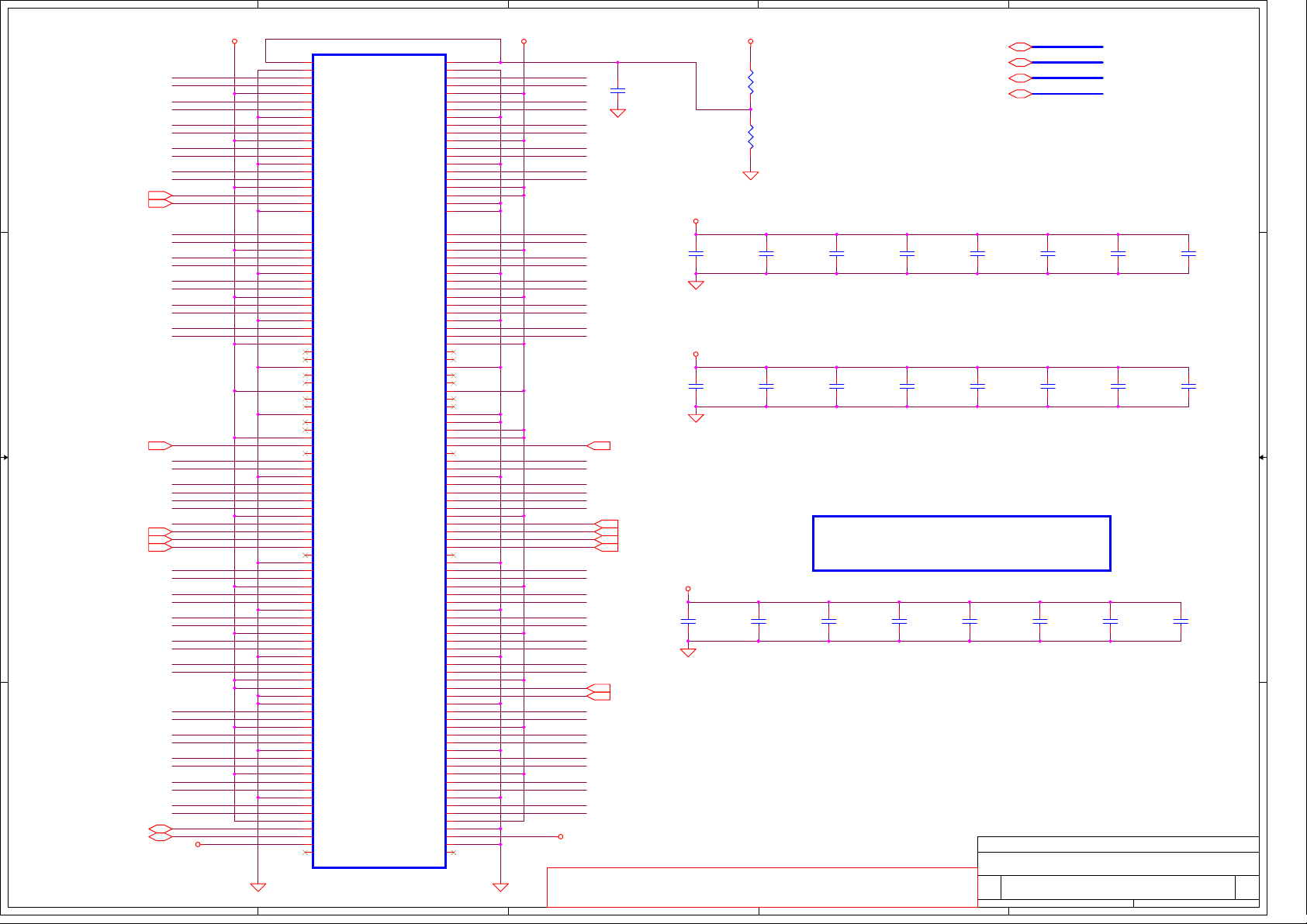

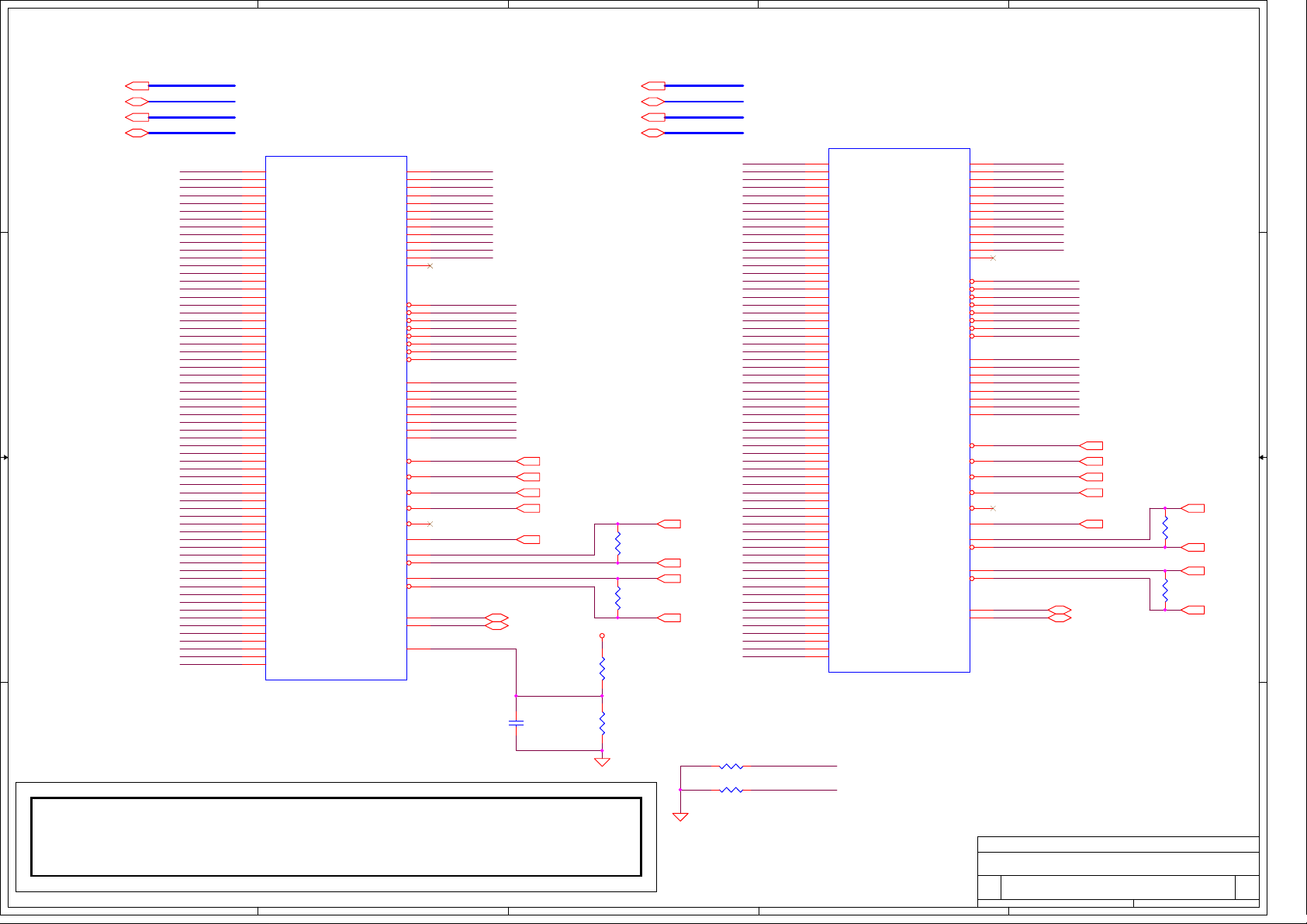

SAPPORO 150 (DAL00)

2 2

LA-1911 REV0.3 Schematic

3 3

Desktop Prescott/Northwood uFCPGA-478 CPU

Springdale(865PE)+ICH5+nVIDIA NV34M(64MB VRAM)

2003-07-14

4 4

Compal Electronics, Inc.

Title

Cover Page

Size Docu ment Number R e v

B

157, 1

星期三 七月

A

B

C

D

Date: Sheet

6, 2003

E

of

0.2

Page 2

A

B

C

D

E

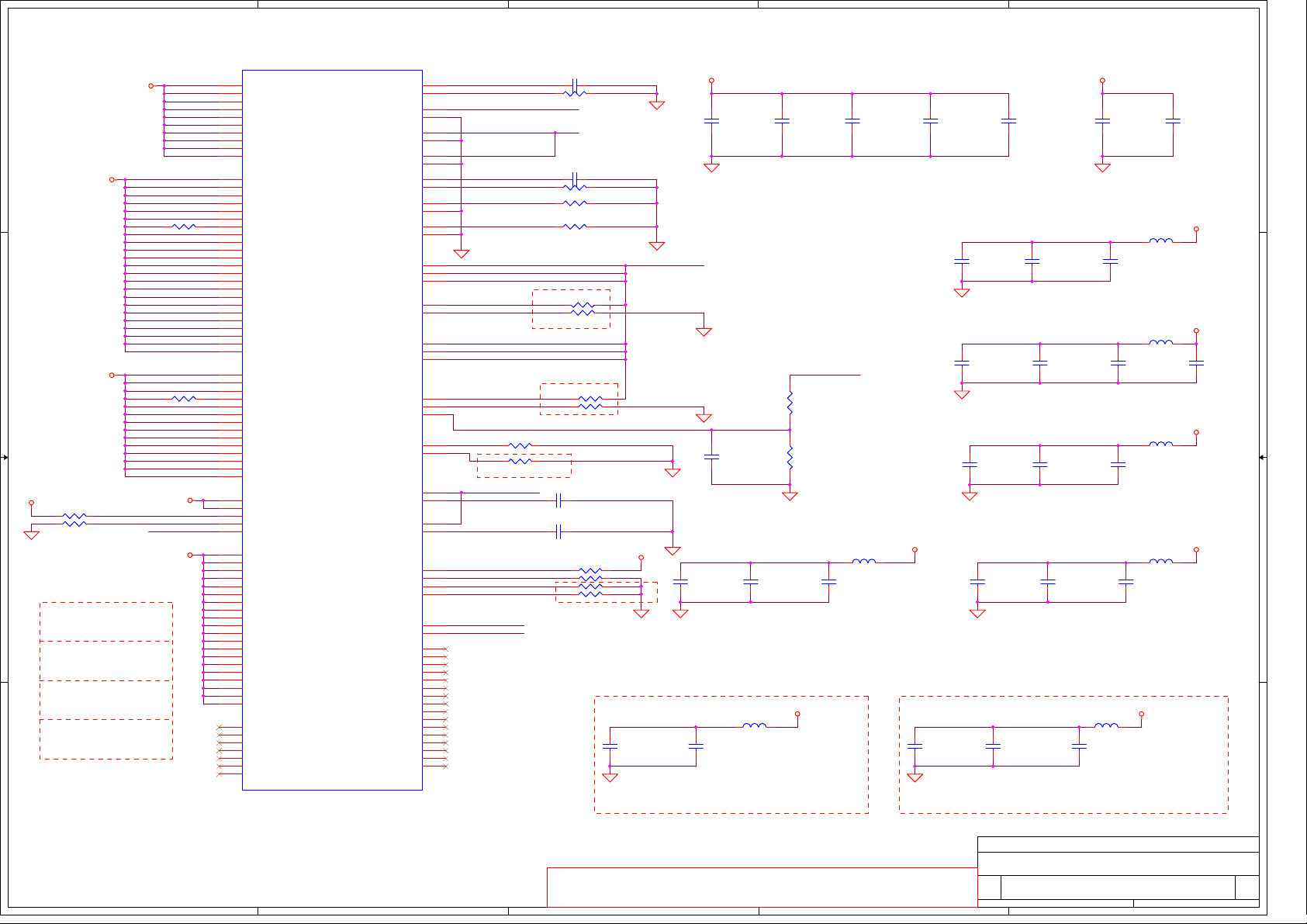

DAL00 LA-1911 BLOCK DIAGRAM

4 4

Desktop Northwood

Deskto p Prescott

(uFCBGA/uFCPGA-478)

PAGE 4,5,6

Thermal S ensor

ADM1032

PAGE 5,16

Clock Generator

ICS952623

PAGE15

CPU VID

PAGE 5

FANController

RTC Battery

PAGE 40

FSB

HUB Interface

ICH5

800MHz

PAGE 7,8,9,10,11

PAGE 23,24,25

480MHz

266/333/400MHz

(2.55V)

Memory Bus

Primary

Secondary

AC-LINK

SO-DI M M x 2(DDR)

BANK 0,1,2,3

Bluetooth

USB 2.0 Port *3

CD-ROM/DVD

AC97 CODEC

IDE HDD

ALC 202

MDC

Connector

PAGE 36

PAGE 35

PAGE 33

PAGE 33

PAGE 31

PAGE 36

PAGE 12,13,14

RJ-11

Aud i o A m p lifier

TPA6011A4

PAGE 26

PAGE 32

DC/DC Interface

PAGE 43

BATTERY

Charger

PAGE 45

Power Interface &

TEMP. sensing circuit

PAGE 46-54

LID/Kill Switch

Power Buttom

PAGE 39

DIRECT BOARD

PAGE 38

CRT&LVDS

Connector

TV-OUT

3 3

4 Pin-Connector

PAGE 22

NVIDIA-NV34M

PAGE 22

AGP

PAGE 16,17,18,19

AGP 8X

AGP Bus

Intel Springdale

MCH 865PE

FCBGA-932

VRAM

2 Channel and 4 sets

RJ-45

PAGE 26

IEEE1394(BTO)

2 2

Slot 0

PAGE 28

SD Conn

PAGE 28

PAGE 20,21

Mini PCI

LAN

RTL8101L

TSB43AB21A

CARDBAY

T7L65XB

PAGE 27,28

PAGE 29

PAGE 26

PAGE 30

PCI BUS

33MHz (3.3V)

LPC BUS 3 3MHz (3.3V)

266MHz

(1.8V)

mBGA-460

VR/CIR BOARD

Super I/O

LPC47N227

REV B

PAGE 34

1 1

Embedded

Controller

NS PC87591L

PAGE 37

CIR

Con t ro ller

PAGE 41

CIR

SW BOARD

PAGE 38

PAGE 38

FIR(BTO)

PAGE 35

A

Parallel

PAGE 36

B

Scan KB

PAGE 37

BIOS(1M)

& I/O PORT

PAGE 38

Compal Electronics, Inc.

Title

Block Digram

Size Docu ment Number Re v

Custom

Date: Sheet

星期三 七月

C

D

16, 2003

257,

E

0.2

of

Page 3

A

B

C

D

E

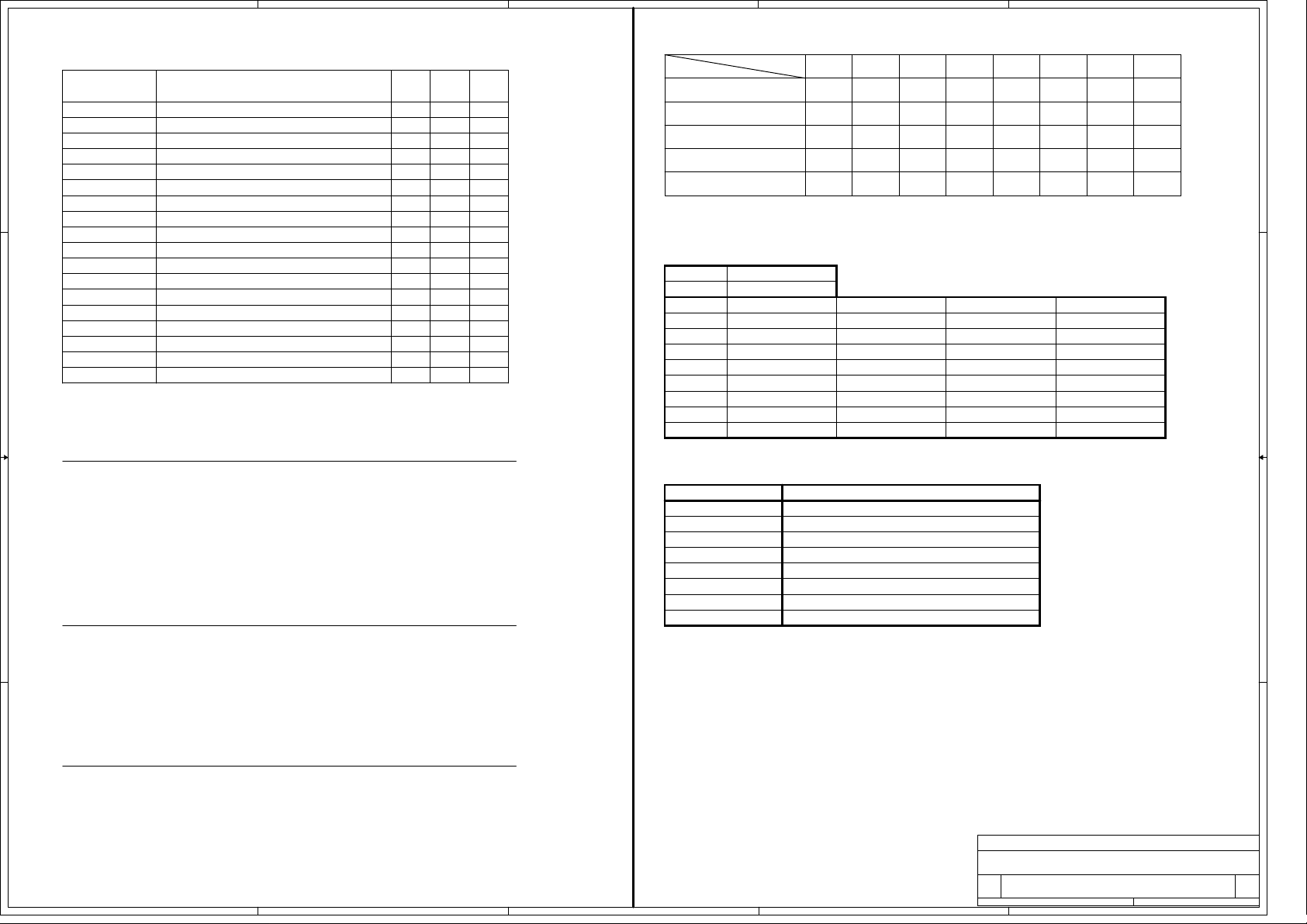

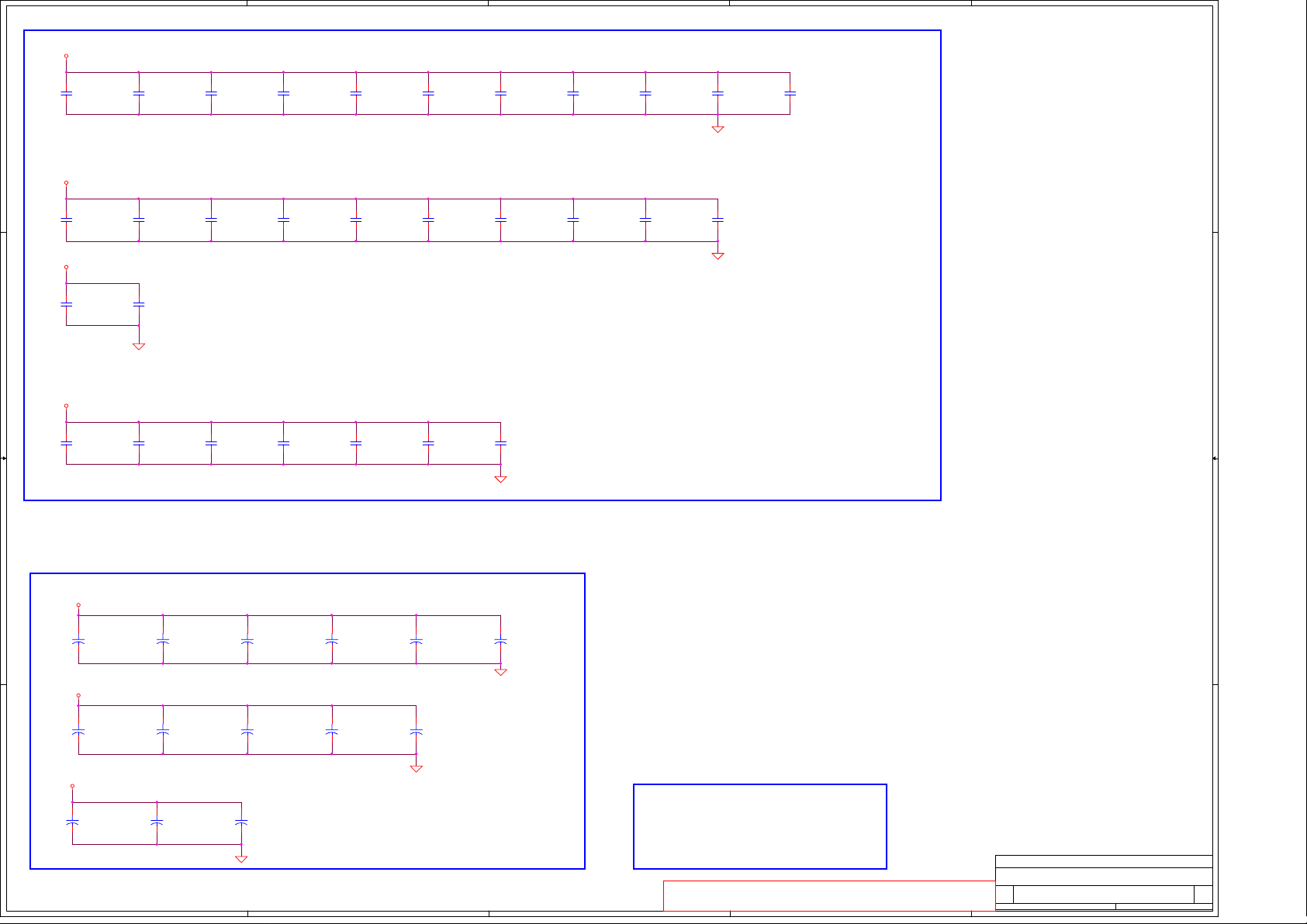

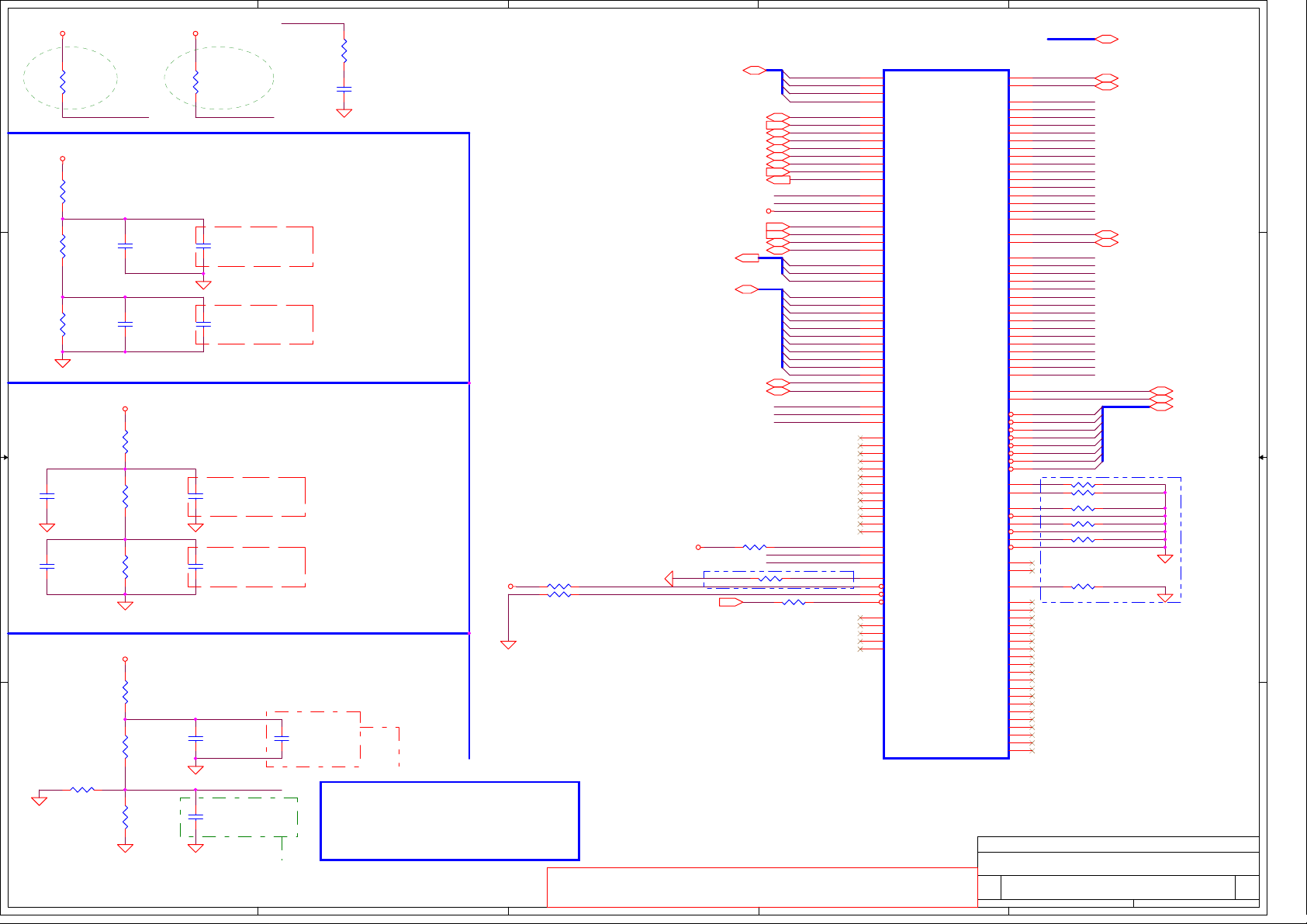

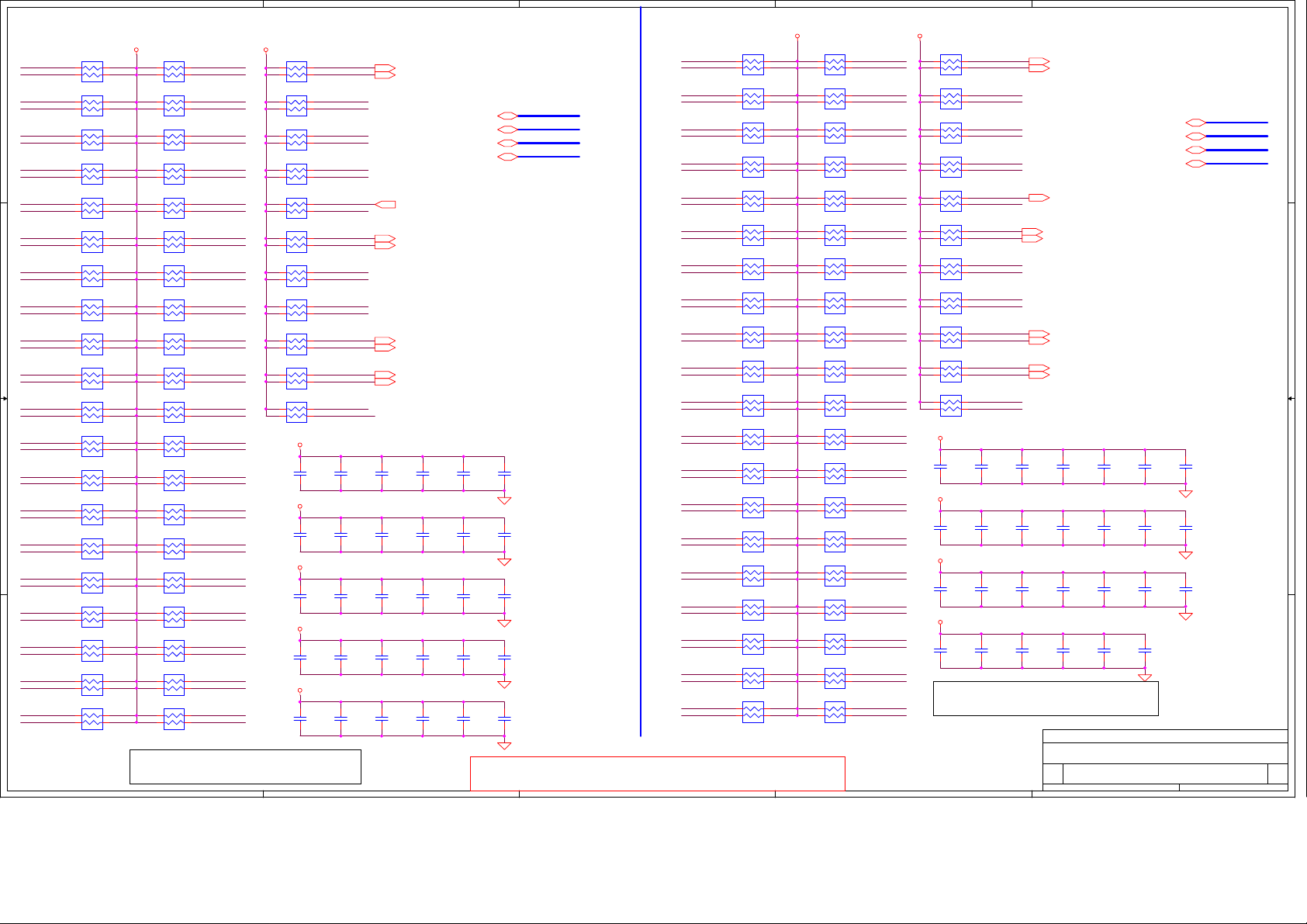

Voltage Rails

STATE

Power Plane Description

1 1

2 2

VIN

B+

+CPU_CORE

+CPU_VID

+V TT_GMCH +1.225V (Prescott) / +1.45V (Northwood)

+VGA_CORE ON OFF OF F1.2V/1.5V switched power rail for VGA chip

+1.25VS 1.25V switched power rail

+1.5VS

+2.5V

+2.5VS 2.5V switched power rail

+3VALW

+3V

+3VS

+5VALW O N

+5V

+5VS

+12VALW

+RTCVCC

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF.

Adapte r power supply (19V)

AC or battery power rail for power circuit.

Core voltage for CPU

1.2V switched power rail for CPU AGTL Bus

AGP 4X/8X

2.5V power rail

3.3V always on power rail

3.3V power rail

3.3V switched power rail

5V always on power rail

5V power rail

5V switched power rail

12V always on power rail

RTC power

S1 S3 S5

N/A N/A N/A

N/AN/AN/A

ON OFF

ON OFF

ON OFF O FF

ON OFF O FF

ON OFF OFF

ON

ON

ON

ON

ON

ON

ON

ON

OFF

OFF

OFFON

ON

OFF

OFF

ON ON*

OFF

ON

OFF

OFF

ON

ON*

OFF

ON

OFF

OFF

ON

ON*

ON

ON

Full ON

S1(Power On Suspend)

S3 (Suspend to RAM)

S4 (Suspend to Disk)

S5 (Soft OFF)

Board I D Ta ble f or AD c hanne l

Vcc 3.3V +/- 5%

Board ID

0

1

2

3

4

5

6

7 NC

SIGNAL

SLP_S1# SLP_S3#

HIGH HIGH HIGH HIGH

LOW

LOW

LOW LOW LOW LOW

100K +/- 5%Ra

Rb V min

0

8.2K +/- 5%

18K +/- 5%

33K +/- 5%

56K +/- 5%

100K +/- 5%

200K +/- 5%

SLP_S4# SLP_S5# +VALW +V +VS Clock

LOW

AD_BID

0 V

HIGH

LOWLOWLOW

ON

HIGHHIGHHIGH

HIGH

HIGH

ON

ON

ON

ON

Vtyp

AD_BID

0 V 0 V

ON

ON

ON

OFF

OFF

V

AD_BID

ON ON

ON

OFF

OFF

OFF

max

0.216 V 0.250 V 0.289 V

0.436 V

0.712 V

1.036 V

0.503 V

0.819 V

0.538 V

0.875 V

1.185 V 1.264 V

1.453 V 1.650 V 1.759 V

1.935 V

2.500 V

2.200 V

3.300 V

2.341 V

3.300 V

LOW

OFF

OFF

OFF

External PCI Devices

Device IDSEL# REQ# / G NT # Interrupts

VGA

CardBus

LAN

Mini-PCI

1394

3 3

SD

EC SM Bus1 address

Device

Smart Battery

EEPROM( 24C16/ 02)

(24C04)

AD16

AD20

AD17

AD18

AD16 0

AD22

2

3PIRQF

1/4

PIRQA

PIRQA/PIRQB/PIRQC/PIRQD

PIRQG/PIRQH

PIRQE

PIRQA/PIRQB/PIRQC/PIRQD

EC SM Bus2 address

Address Address

1010 000X b

1011 000Xb

Device

ADM1032

1001 110X b0001 011X b

Board ID

0

1

2

3

4

5

6

7

PCB Revision

0.1

ICH4 SM Bus address

Device

4 4

Clock Generator

( ICS 952623)

DDR DIMM0

DDR DIMM2

A

Address

1101 001Xb

1010 000Xb

1010 010Xb

Compal Electronics, Inc.

Title

Size Document Number R e v

B

B

C

D

Dat e : Sheet

LA-1911

期三 七月

Notes

0.2

of

357¬P , 16, 2003

E

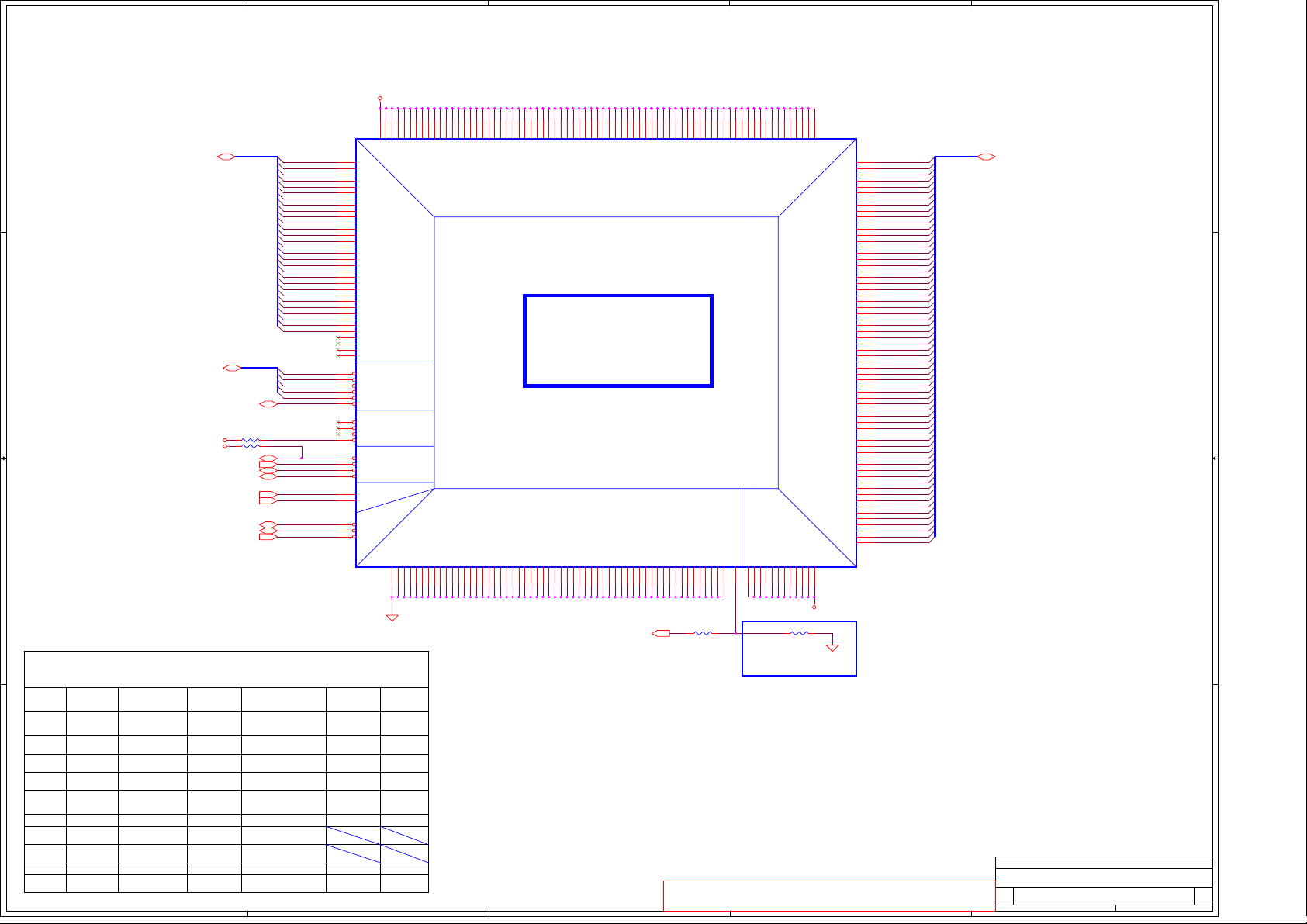

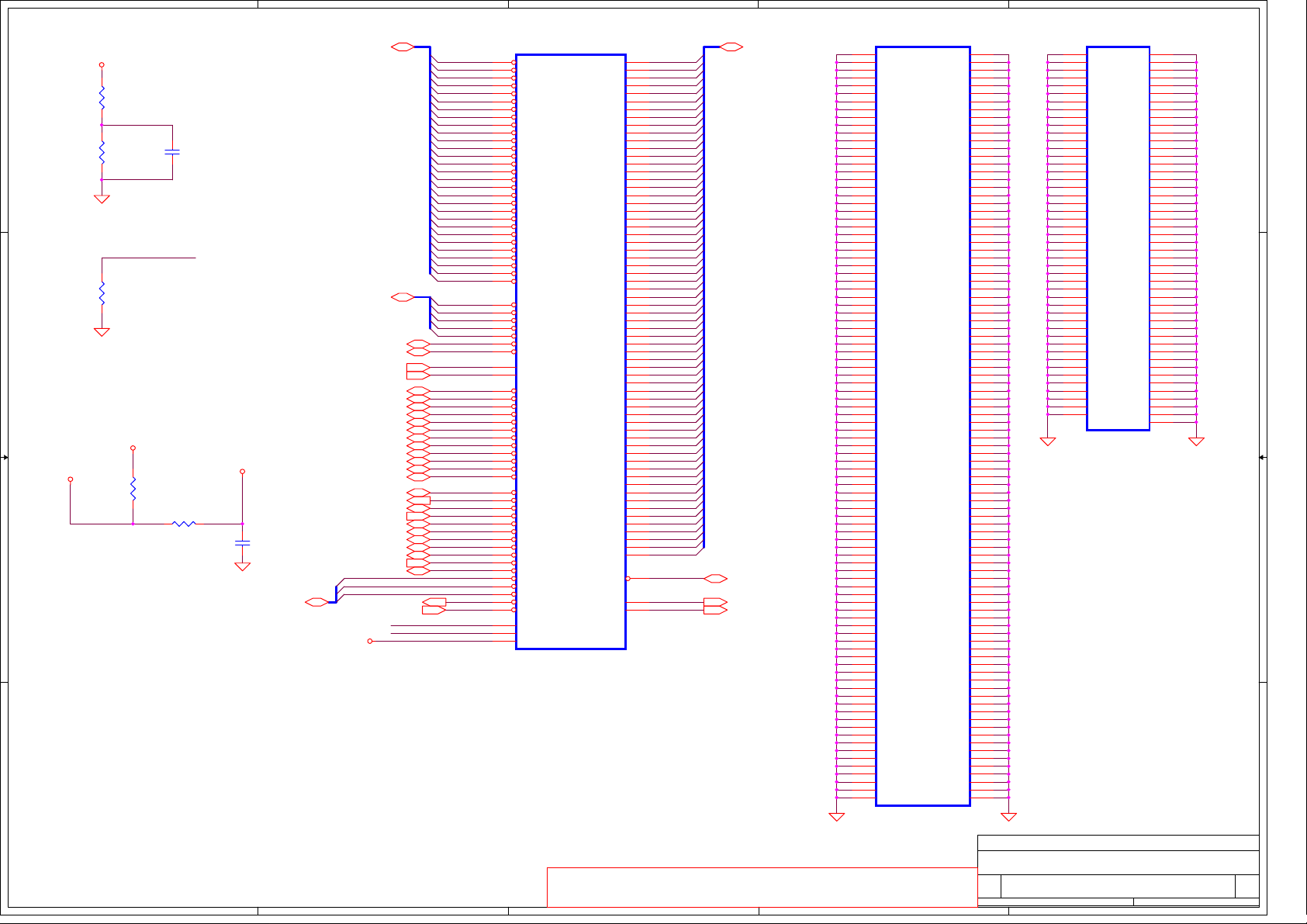

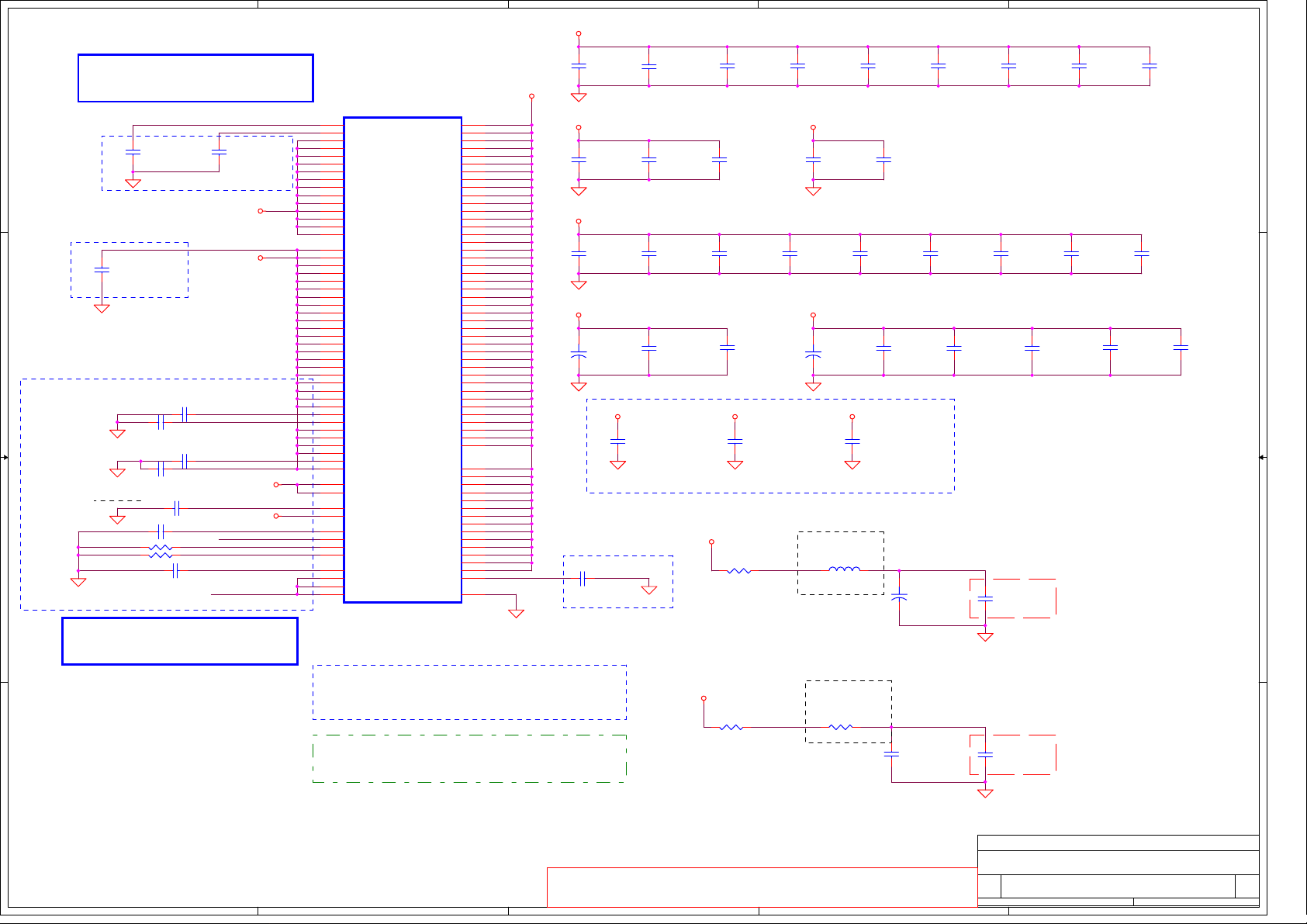

Page 4

5

4

+CPU_CORE

3

2

1

D D

H_A#[3..31]7

C C

H_REQ#[0..4]7

H_ADS#7

R25 62_0402_5%

+CPU_CORE

+CPU_CORE

B B

1 2

1 2

R35 200_0402_5%

H_BR0#7

H_BPRI#7

H_BNR#7

H_LOCK#7

CLK_BCLK15

CLK_BCLK#15

H_HIT#7

H_HITM#7

H_DEFER#7

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_IERR#

CLK_BCLK

CLK_BCLK#

AMP_3 - 1 565030-1_Pres cot t

AF22

AF23

A10

A12

A14

A16

A18

A20

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

D9

VCC_65C8VCC_66

VCC_84

VCC_85

F9

F11

VCC_67

VCC_68

VCC_79E8VCC_80

E20

VCC_69

VCC_78

E18

VCC_70

VCC_77

E16

E10

VCC_71D7VCC_72

VCC_75

VCC_76

E12

E14

VCC_73

VCC_74

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

H_D#0

B21

D#0

H_D#1

B22

D#1

H_D#2

A23

D#2

H_D#3

A25

D#3

H_D#4

C21

D#4

H_D#5

D22

D#5

H_D#6

B24

D#6

H_D#7

C23

D#7

H_D#8

C24

D#8

H_D#9

B25

D#9

H_D#10

G22

H_D#11

H21

H_D#12

C26

H_D#13

D23

H_D#14

J21

H_D#15

D25

H_D#16

H22

H_D#17

E24

H_D#18

G23

H_D#19

F23

H_D#20

F24

H_D#21

E25

H_D#22

F26

H_D#23

D26

H_D#24

L21

H_D#25

G26

H_D#26

H24

H_D#27

M21

H_D#28

L22

H_D#29

J24

H_D#30

K23

H_D#31

H25

H_D#32

M23

H_D#33

N22

H_D#34

P21

H_D#35

M24

H_D#36

N23

H_D#37

M26

H_D#38

N26

H_D#39

N25

H_D#40

R21

H_D#41

P24

H_D#42

R25

H_D#43

R24

H_D#44

T26

H_D#45

T25

H_D#46

T22

H_D#47

T23

H_D#48

U26

H_D#49

U24

H_D#50

U23

H_D#51

V25

H_D#52

U21

H_D#53

V22

H_D#54

V24

H_D#55

W26

H_D#56

Y26

H_D#57

W25

H_D#58

Y23

H_D#59

Y24

H_D#60

Y21

H_D#61

AA25

H_D#62

AA22

H_D#63

AA24

H_D#[0..63] 7

JCPU1A

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6A8VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56B7VCC_57B9VCC_58

VCC_59

VCC_61

VCC_62

VCC_63

K2

A#3

K4

A#4

L6

A#5

K1

A#6

L3

A#7

M6

A#8

L2

A#9

M3

A#10

M4

A#11

N1

A#12

M1

A#13

N2

A#14

N4

A#15

N5

A#16

T1

A#17

R2

A#18

P3

A#19

P4

A#20

R3

A#21

T2

A#22

U1

A#23

P6

A#24

U3

A#25

T4

A#26

V2

A#27

R6

A#28

W1

A#29

T5

A#30

U4

A#31

V3

A#32

W2

A#33

Y1

A#34

AB1

A#35

J1

REQ#0

K5

REQ#1

J4

REQ#2

J3

REQ#3

H3

REQ#4

G1

ADS#

AC1

AP#0

V5

AP#1

AA3

BINIT#

AC3

IERR#

H6

BR0#

D2

BPRI#

G2

BNR#

G4

LOCK#

BCLK0

BCLK1

F3

HIT#

E3

HITM#

E2

DEFER#

VSS_0H1VSS_1H4VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12A3VSS_13A9VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

A11

A13

A15

A17

A19

A21

A24

H23

H26

A26

AA1

AA4

AA11

AA13

AA15

AA17

AA19

AA23

AA26

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

AA7

AA9

AB10

AB12

AB14

AB16

Prescott

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

AB3

AB6

AB8

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

AC19

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

AC2

AC5

AC7

AC9

AC22

AC25

AD10

AD12

AD14

AD16

AD18

AD21

AD23

VCC_64

BOOTSELECT

VSS_54

VSS_55

VCC_81

VCC_82

VCC_83

F13

F15

F17

F19

AD1

AD4

AD8

+CPU_CORE

H_BOOTSELECT52

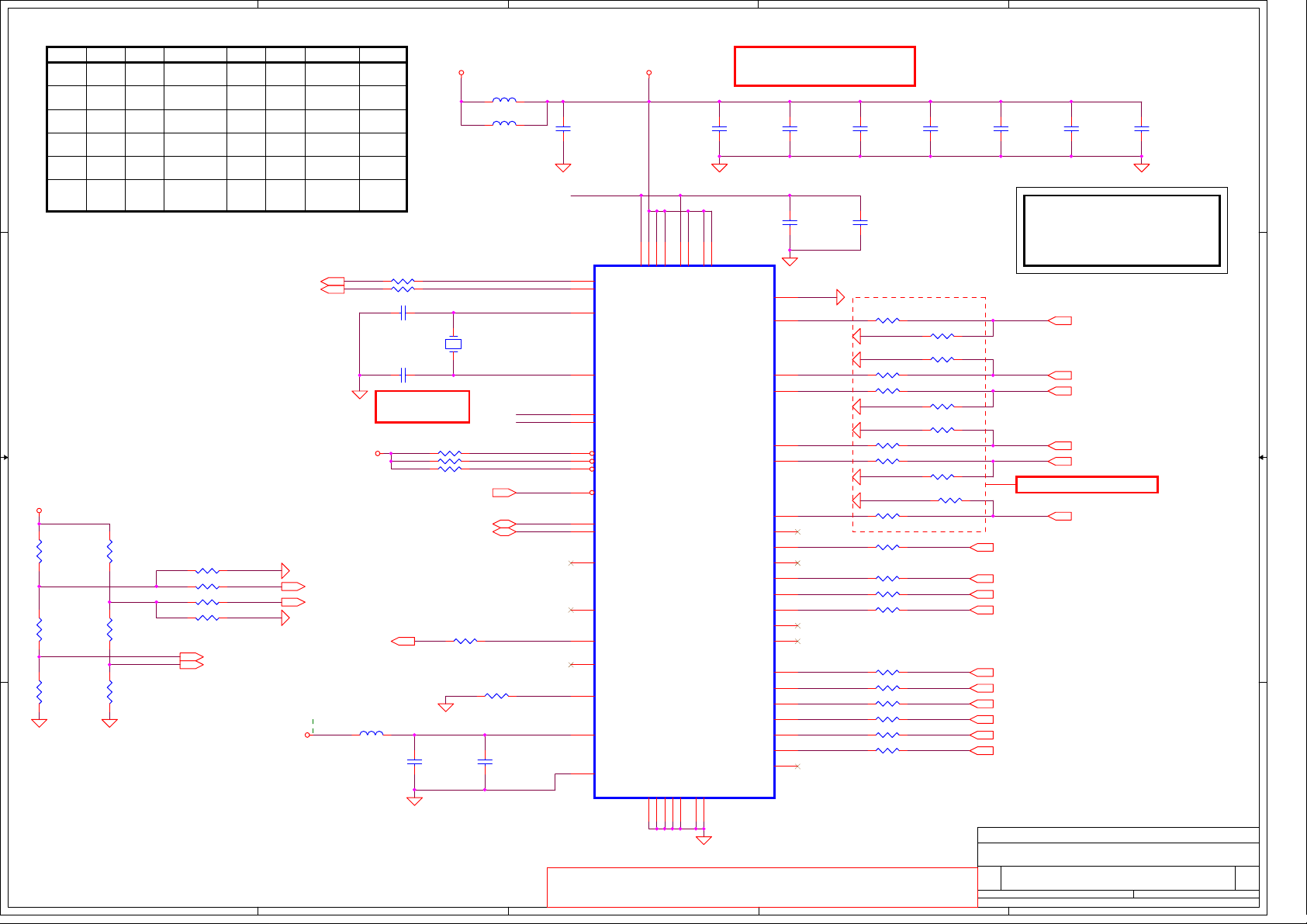

Reference Intel document

Desktop P4 Spec.: 10988 P4 0.13u 512KB L2 EMTS Rev.2.0

Desktop Prescott Spec.: 11910 Prescott EMTS Rev.0.5

Pin number Northwood

Pin name

B6 FERR# FERR#/PBE# Pull-up 62ohm

AA20 ITPCLKOUT0 Pull-up56ohm

AB22 ITPCLKOUT1 Pull-up 56ohm

AD2 NC VIDPWRGD Pull-up 8.2Kohm

AD3 NC float VID5 Pull-up1Kohm to

A A

AF3 NC float VCCVIDLB Connect to +VCCVID

AD20 VCCA VCCIOPLLConnect to CPU

AF23 Connect to CPU

VCCIOPLL VCCA

AD1 VSS BOOTSELECTConnect to GND CPU determine

AE26 VSS Connect to GND OPTIMIZED/

Commend Commend

Pull-up 62ohm

to +VCC_CORE

to +VCC_CORE

to +VCC_CORE

float

Filter

Filter

5

Prescott

Pin name

to +VCC_CORE

TESTHI6 Pull-up 62ohm

TESTHI7 Pull-up 62ohm

to +VCC_CORE

to +VCC_CORE

to +VCCVID

+3VRUN & connect

to PWRIC

Connect to CPU

Filter

Connect to CPU

Filter

COMPAT#

float

Northwood Prescott

Pop Pop

Pop Pop

Pop Pop

PopDepop

Depop

Depop

Pop

Pop

Pop Depop

Pop Depop

4

3

1 2

R12

0_0402_5%

THIS SHEET OF EN G I N EERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONIC S, INC. AND CONTAINS CONFID ENTIAL

AND TRADE SECRET IN F ORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZ ED BY COMP AL ELECTR ONICS, INC. NE ITHER T HIS SHEET NOR THE INFORM ATION IT CONTAI NS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PR IOR WRI TTEN CO NSENT OF COMPAL EL ECTRONI CS, INC .

BOOTSEL

R_C

1 2

R15

0_0402_5%

Pop: No rt hwood

Depop: Pr es cott

Compal Electronics, Inc.

Title

Prescott Processor in uFCPGA478 (1/2)

Size Document Number Re v

C

LA-1911

Date: Sheet

星期

T, 16, 2003

2

七月

1

457

0.2

of

Page 5

5

4

3

2

1

Asynch GTL+ PULL HIGH

+CPU_CORE

H_FERR#

1 2

R518 62_0402_5%

H_PROCHOT#

1 2

R27 130_0402_5%

H_P WRGOOD

D D

1 2

R74 300_0402_5%

H_RESET#

1 2

R75 62_0402_5%

JTAG PULL DOWN

RP4

1K_8P4 R _1206_5%

Close to the CPU

+CPU_CORE

ITP_TMS

ITP_TRST#

ITP_TCK

ITP_TDI

1 8

2 7

3 6

4 5

C C

B B

Place near ICH

Place near CPU

+CPU_CORE

R37 62_0402_5%

R33 62_0402_5%

R30 62_0402_5%

R36 62_0402_5%

R32 62_0402_5%

Note: Please change to 10uH, DC current

of 100mA parts and close to cap

L5 L Q G 2 1 F 4R7N00_0805

1 2

**

L6 L Q G 2 1 F 4R7N00_0805

1 2

**

PLL Layout note :

1.Place cap within 600 mils of

the VCCA and VSSA pins.

2.H_VCCIOPLL,HVCCA,HVSSA trace wide

12 mils(min)

R29 62_0402_5%

C80

+

Trace >= 25mils

1 2

33U_D2_8M_R35

Pop: Prescott

Depop: Northwood

H_A20M#23

H_IGNNE#23

H_SMI#23

H_PWR GOOD23

H_STPCLK#23

CPU_CLKSEL015

CPU_CLKSEL115

H_THERMTRIP#24

H_RS#[0..2]7

H_TRDY#7

H_FERR#23

H_INTR23

H_NMI23

H_INIT#23

H_RESET#7

H_DBSY#7

H_DRDY#7

1 2

1 2

1 2

1 2

1 2

1 2

VCCSENSE52

VSSSENSE52

+CPUVID

H_VCCA

H_VSSA

1 2

R26

CLK_ITP15

CLK_ITP#15

R65

61.9_ 0603_1%

H_RS#0

H_RS#1

H_RS#2

H_FERR#

H_P WRGOOD

H_RESET#

H_THERMDA

H_THERMDC

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

ITP_TDI

ITP_TMS

ITP_TRST#

VCCVIDLB

@0_0402_5%

CLK_ITP

CLK_ITP#

COMP0

COMP1

12

12

R14

61.9_ 0603_1%

AMP_3 - 1 565030-1_Pres cot t

AD20

AD22

AC26

AD26

AB23

AB25

AE23

AD6

AD5

AC6

AC4

F1

G5

F4

AB2

J6

C6

B6

B2

B5

Y4

D1

E5

W5

H5

H2

B3

C4

A2

AB5

Y6

AA5

AB4

D4

C1

D5

F7

E6

A5

A4

AF3

L24

P1

JCPU1B

RS#0

RS#1

RS#2

RSP#

TRDY#

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

LINT0

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

TCK

TDI

TDO

TMS

TRST#

VCCIOPLL

VCCA

VCCSENSE

VSSSENSE

VCCVIDLB

VSSA

ITP_CLK0

ITP_CLK1

COMP0

COMP1

AE11

AE13

VSS_57

VSS_129F8VSS_130

G21

AE15

VSS_58

G24

AE17

AE19

VSS_59

VSS_60

VSS_61

VSS_131

VSS_132G3VSS_133G6VSS_134J2VSS_135

AE22

AE24

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

C11

C13

C15

C17

C19

C22

C25

D10

D12

D14

D16

D18

D20

D21

D24

E11

E13

E15

E17

E19

E23

E26

F10

F12

F14

F16

F18

F22

F25

F5

VSS_62

VSS_63

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85B4VSS_86B8VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92C2VSS_93

VSS_94

VSS_95C5VSS_96C7VSS_97C9VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106D3VSS_107D6VSS_108D8VSS_109E1VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117E4VSS_118E7VSS_119E9VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125F2VSS_126

VSS_127

VSS_128

OPTIMIZED/COMPAT#

Prescott

VID0

VID1

VID2

VID3

VSS_136

VSS_137J5VSS_138

VSS_139

VSS_140K3VSS_141K6VSS_142L1VSS_143

VSS_144

VSS_145L4VSS_146M2VSS_147

VSS_148

VSS_149M5VSS_150

VSS_151

VSS_152N3VSS_153N6VSS_154P2VSS_155

VSS_156

VSS_157P5VSS_158R1VSS_159

VSS_160

VSS_161R4VSS_162

VSS_163

VSS_164T3VSS_165T6VSS_166U2VSS_167

VSS_168

VSS_169U5VSS_170V1VSS_171

VSS_172

VSS_173V4VSS_174

VSS_175

VSS_176W3VSS_177W6VSS_178Y2VSS_179

VSS_180

VSS_181

J22

J25

L23

L26

K21

K24

N21

N24

M22

M25

T21

P22

T24

P25

R23

R26

V23

V26

U22

U25

H_VID052

H_VID152

H_VID252

H_VID352

H_VID452

H_VID552

Y5

Y22

Y25

W21

W24

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

VID4

VID5

AE5

AE4

AE3

AE2

AE1

AD3

VIDPWRGD

AD2

VCCVID

AF4

Trace >= 25mils

1

2

H_VID_PWRGD

AF26

SKTOCC#

DP#0

DP#1

DP#2

DP#3

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

PROCHOT#

MCERR#

SLP#

+CPUVID

C39

0.1U_ 0 402_10V6K

R84

1 2

0_0402_5%

J26

K25

K26

L25

AA21

AA6

F20

F6

AE26

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

AD25

E22

K22

R22

W22

F21

J23

P23

W23

L5

R5

E21

G25

P26

V21

AE25

C3

V6

AB26

A22

NC1

A7

NC2

AF25

NC3

AF24

NC4

AE21

NC5

@2.43 K_0603_1%

R_E

R31

1 2

R83 0_0402_5%

1 2

H_TEST HI 0

H_TEST HI 1

H_TEST HI 2_7

H_TEST HI 8

H_TEST HI 9

H_TEST HI 10

H_TEST HI 11

H_TEST HI 12

H_DSTBN#0 7

H_DSTBN#1 7

H_DSTBN#2 7

H_DSTBN#3 7

H_DSTBP#0 7

H_DSTBP#1 7

H_DSTBP#2 7

H_DSTBP#3 7

H_ADSTB#0 7

H_ADSTB#1 7

H_DINV#0 7

H_DINV#1 7

H_DINV#2 7

H_DINV#3 7

H_PROCHOT#

1 2

R82

62_0402_5%

RE

Pop: Pr es cott

Depop: No rt hwood

+CPUVID

+CPU_GTLREF

R_G

R78 62_0402_5%

1 2

R20 62_0402_5%

1 2

R64 62_0402_5%

1 2

R34 62_0402_5%

1 2

R28 62_0402_5%

1 2

R19 62_0402_5%

1 2

R38 62_0402_5%

1 2

R79 62_0402_5%

1 2

H_PROCHOT# 7,51

H_CPUSLP# 23

+CPU_CORE

Pop: No rt hwood

Depop: Pr es cott

+CPU_CORE

VID PULL HIGH VID PWRGD Circuit Thermal SensorGTL Reference Voltage

+3VS

H_VID5

1 2

R18 1K_0402_5%

H_VID4

1 2

R17 1K_0402_5%

RP3

H_VID3

H_VID2

H_VID1

A A

H_VID0

45

36

27

18

1K_8P4 R _1206_5%

5

+CPU_GMCH_GTLREF

+CPU_CORE

R_A

R_B

12

R59

200_0603_1%

12

R60

169_0603_1%

4

2

C68

0.1U_ 0 402_10V6K

1

Layout note :

1. +CPU_GTLREF Trace wide

12mils(min),Space 15mils

2. Place R_A and R_B near CPU.

3. Place decoupling cap 220PF near CPU.

+CPU_GTLREF

12

R63

0_0603_5%

1

C78

220P_0402_50V8K

2

H_VID_PWRGD

SN74LVC125APWLE_TSSOP14

3

+3V

1

C780

0.1U_ 0 402_16V4Z

2

U4A

3

+3V POWER

THIS SHEET OF EN G I N EERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONIC S, INC. AND CONTAINS CONFID ENTIAL

AND TRADE SECRET IN F ORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZ ED BY COMP AL ELECTR ONICS, INC. NE ITHER T HIS SHEET NOR THE INFORM ATION IT CONTAI NS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PR IOR WRI TTEN CO NSENT OF COMPAL EL ECTRONI CS, INC .

14

1

OE#

I2O

7

12

R70

10K_0402_5%

1 2

R66 0_0402_5%

P

G

VID_PWRGD 52

VCORE_ENLL 49,52

2

2200P_0402_50V7K

EC_SMB_CK237

EC_SMB_DA237

+3VS

1

H_THERMDA

1

C47

2

H_THERMDC

Title

Size Document Number Re v

C

Date: Sheet

2

3

8

7

Compal E lect ronics, Inc.

Prescott Processor in uFCPGA478 (2/2)

LA-1911

星期

T, 16, 2003

七月

2

U3

VDD1

D+

ALERT#

D-

THERM#

SCLK

GND

SDATA

ADM1032AR M_R M8

1

C48

0.1U_0402_16V4Z

1

6

4

5

12

557

R41

@10K_0402_5%

of

0.2

Page 6

5

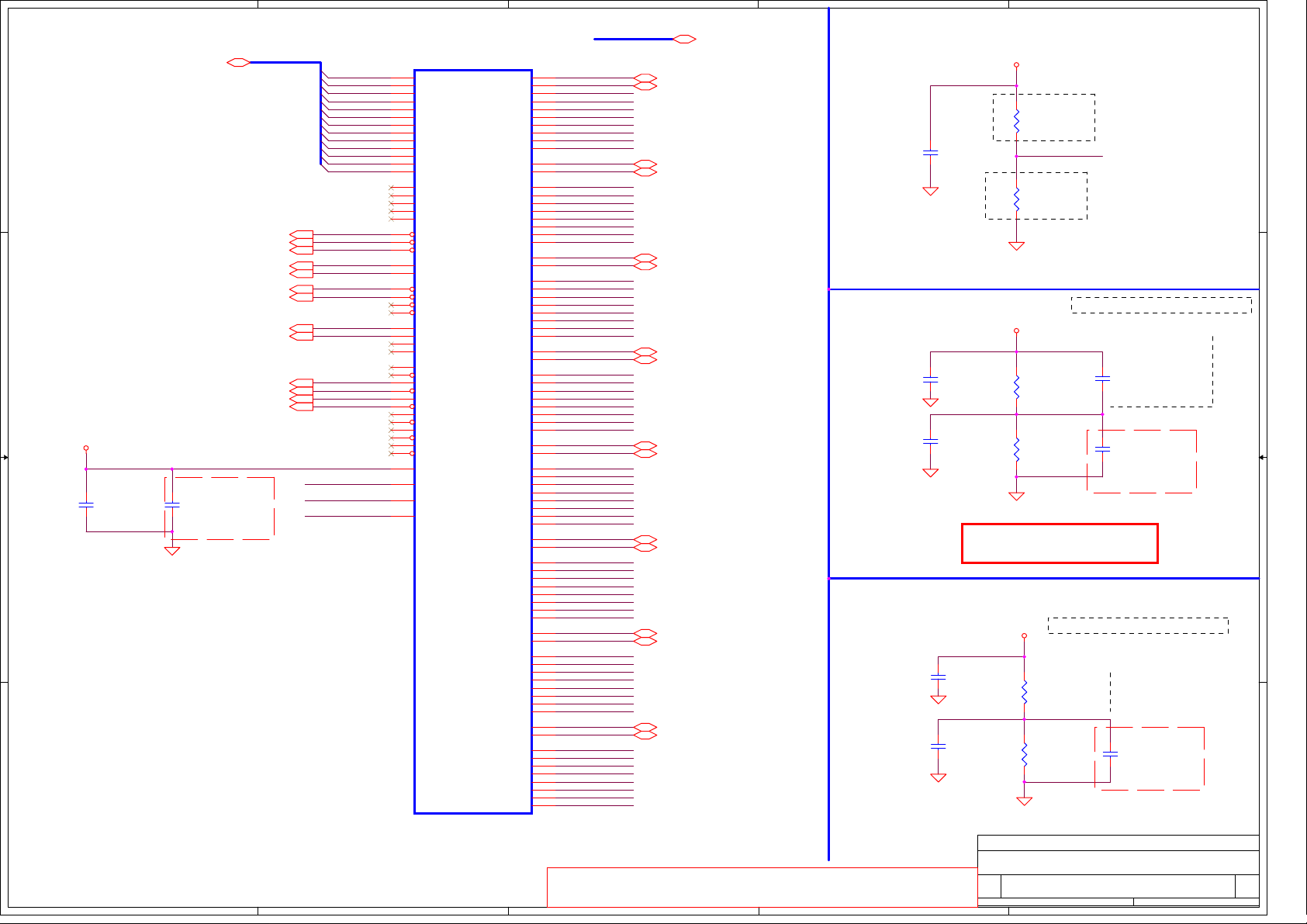

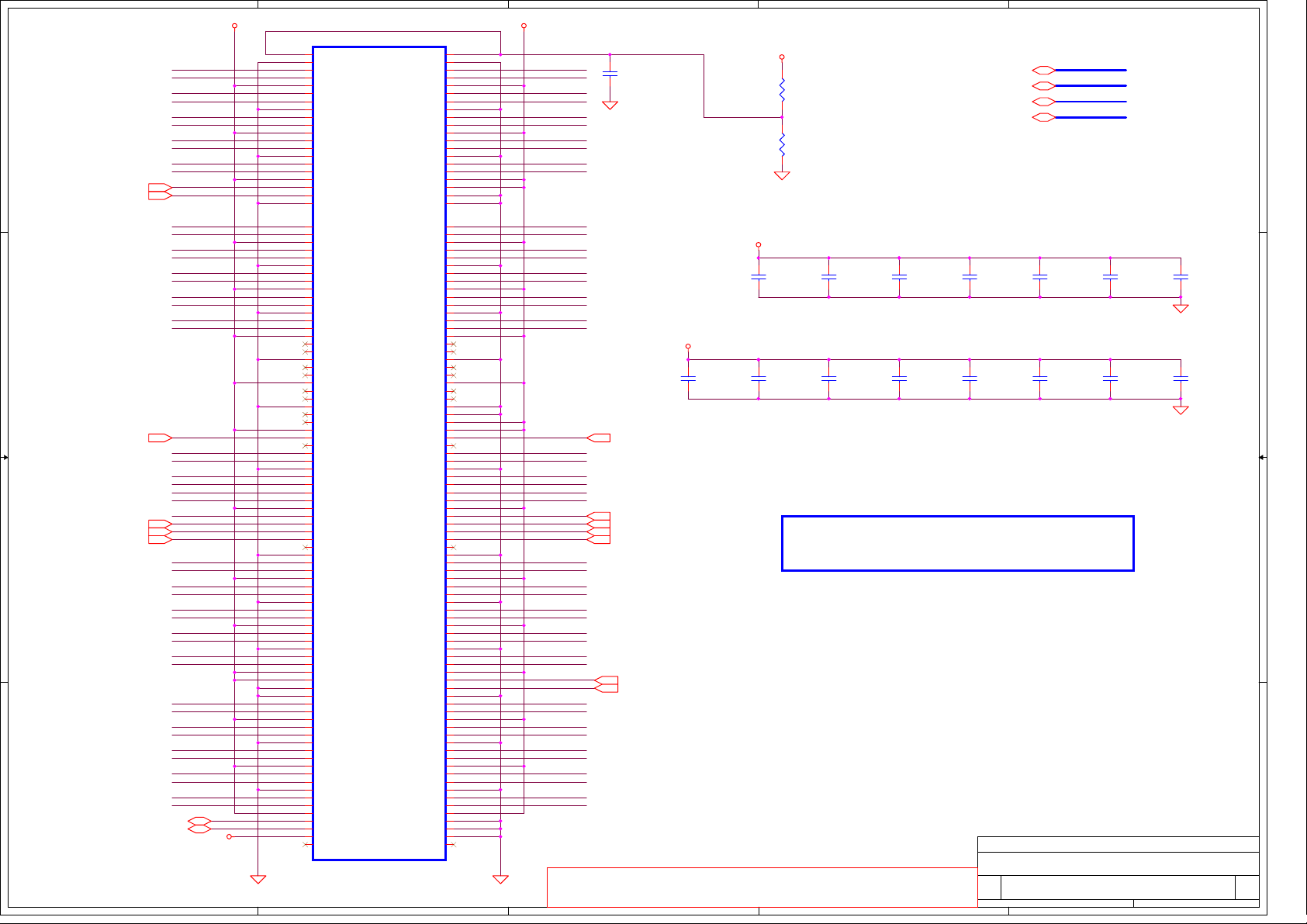

4

3

2

1

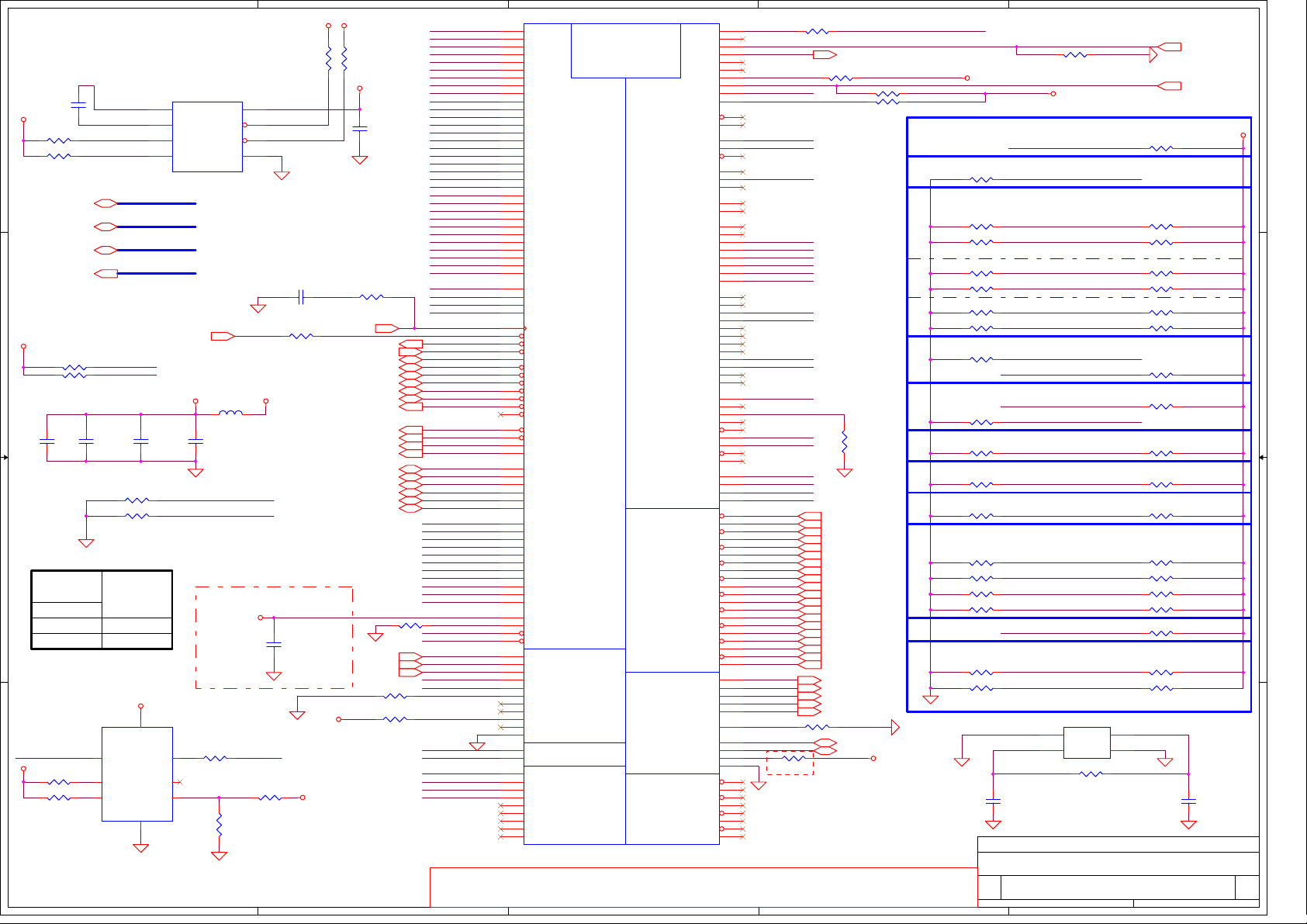

+CPU_CORE

1

C468

22U_1206_6.3V6M

2

D D

+CPU_CORE

1

C514

22U_1206_6.3V6M

2

+CPU_CORE

1

C59

22U_1206_6.3V6M

2

C C

+CPU_CORE

1

C491

22U_1 206_6.3V6M

2

1

C536

22U_1 206_6.3V6M

2

1

C70

22U_1 206_6.3V6M

2

1

C508

22U_1 206_6.3V6M

2

1

C558

22U_1 206_6.3V6M

2

Place 11 North of Socket(Stuff 8)

1

C523

22U_1 206_6.3V6M

2

1

C545

22U_1206_6.3V6M

2

1

2

Place 12 Inside Socket(Stuff all)

1

C571

22U_1 206_6.3V6M

2

1

C518

22U_1206_6.3V6M

2

1

2

Place 9 South of Socket(Unstuff all)

C560

22U_1206_6.3V6M

C535

22U_1206_6.3V6M

1

C16

22U_1 206_6.3V6M

2

1

C557

22U_1 206_6.3V6M

2

1

C408

22U_1 206_6.3V6M

2

1

C570

22U_1 206_6.3V6M

2

1

C421

22U_1 206_6.3V6M

2

22uF depop reference

Springdale Customer Schematic R1.2 page82

1

C60

22U_1 206_6.3V6M

2

1

C440

22U_1206_6.3V6M

2

1

C52

22U_1206_6.3V6M

2

1

C455

22U_1206_6.3V6M

2

**

1

C15

22U_1206_6.3V6M

2

1

C14

22U_1 206_6.3V6M

2

1

C13

22U_1 206_6.3V6M

2

1

C12

22U_1 206_6.3V6M

2

1

C19

22U_1206_6.3V6M

2

1

C18

22U_1206_6.3V6M

2

1

C17

22U_1 206_6.3V6M

2

B B

+CPU_CORE

1

+

C119

470U_D4_2.5VM

2

+CPU_CORE

1

+

C51

470U_D4_2.5VM

2

+CPU_CORE

A A

1

+

C63

470U_D4_2.5VM

2

1

+

C95

470U_D4_2.5VM

2

1

+

C8

470U_D4_2.5VM

2

1

+

C33

470U_D4_2.5VM

2

5

470uF _ERS10m ohm* 15, ESR=0.5m ohm

1

+

C85

470U_D4_2.5VM

2

1

+

C75

470U_D4_2.5VM

2

**

1

+

C29

470U_D4_2.5VM

2

1

+

C28

470U_D4_2.5VM

2

1

+

C44

470U_D4_2.5VM

2

4

1

+

C67

470U_D4_2.5VM

2

1

+

C53

470U_D4_2.5VM

2

1

+

C61

470U_D4_2.5VM

2

Decoupling Reference Document:

Springdale Chipset Platform Design guide Rev1.11

(12474)page239

Decoupling Reference Requirement:

560uF Polymer, ESR:5m ohm(each) * 10

22uF X5R * 32

THIS SHEET OF EN G I N EERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONIC S, INC. AND CONTAINS CONFID ENTIAL

AND TRADE SECRET IN F ORMATION. THIS SHEET MAY NOT BE TRANSFER ED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZ ED BY COMP AL ELECTR ONICS, INC. NE ITHER T HIS SHEET NOR THE INFORM ATION IT CONTAI NS

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WI THOUT PR IOR WRI TTEN CO NSENT OF COMPAL EL ECTRONI CS, INC .

Compal Electronics, Inc.

Title

CPU Decoupling

Size Document Number Re v

C

LA-1911

Date: Sheet

星期

T, 16, 2003

2

七月

1

657

0.2

of

Page 7

5

4

3

2

1

+VTT_GMCH

12

D D

12

12

C C

+CPU_GMCH_GTLREF

GTL Ref e r e n c e V o l tage

B B

A A

Layout note :

1. +G MC H_G T LR EF Trace wide

12mil s( min),Sp ace 15mils.

2. Place decoup ling cap 220PF near GMCH.

Trace width 10mils,Space

7mils

R531

301_0603_1%

HD_SWING

HDRCOMP

12

R511

200_0603_1%

1

C301

0.01U_0402_16V7K

2

R535

102_0603_1%

R525

24.9_0603_1%

+VTT_GMCH

1 2

R522 0_0603_5%

+GMCH_GTLREF

1

C286

220P_0402_50V8K

2

H_RS#[0..2]5

H_A#[3..31]4

H_REQ#[0..4]4

+GMCH_GTLREF

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_RS#0

H_RS#1

H_RS#2

HDRCOMP

HD_SWING

H_REQ#4

H_ADSTB#05

H_ADSTB#15

CLK_HCLK15

CLK_HCLK#15

H_DSTBP#05

H_DSTBN#05

H_DINV#05

H_DSTBP#15

H_DSTBN#15

H_DINV#15

H_DSTBP#25

H_DSTBN#25

H_DINV#25

H_DSTBP#35

H_DSTBN#35

H_DINV#35

H_ADS#4

H_TRDY#5

H_DRDY#5

H_DEFER#4

H_HITM#4

H_HIT#4

H_LOCK#4

H_BR0#4

H_BNR#4

H_BPRI#4

H_DBSY#5

H_RESET#5 MCH_CLKSEL0 15

SYS_PWROK24,27,40

U43A

D26

HA3#

D30

HA4#

L23

HA5#

E29

HA6#

B32

HA7#

K23

HA8#

C30

HA9#

C31

HA10#

J25

HA11#

B31

HA12#

E30

HA13#

B33

HA14#

J24

HA15#

F25

HA16#

D34

HA17#

C32

HA18#

F28

HA19#

C34

HA20#

J27

HA21#

G27

HA22#

F29

HA23#

E28

HA24#

H27

HA25#

K24

HA26#

E32

HA27#

F31

HA28#

G30

HA29#

J26

HA30#

G26

HA31#

B29

HREQ0#

J23

HREQ1#

L22

HREQ2#

C29

HREQ3#

J21

HREQ4#

B30

HADSTB0#

D28

HADSTB1#

B7

HCLKP

C7

HCLKN

B19

HDSTBP0#

C19

HDSTBN0#

C17

DINV0#

L19

HDSTBP1#

K19

HDSTBN1#

L17

DINV1#

G9

HDSTBP2#

F9

HDSTBN2#

L14

DINV2#

D12

HDSTBP3#

E12

HDSTBN3#

C15

DINV3#

F27

ADS#

D24

HTRDY#

G24

DRDY#

L21

DEFER#

E23

HITM#

K21

HIT#

E25

HLOCK#

B24

BREQ0#

B28

BNR#

B26

BPRI#

E27

DBSY#

G22

RS0#

C27

RS1#

B27

RS2#

E8

CPURST#

AE14

PWROK#

E24

HDRCOMP

C25

HDSWING

F23

HDVREF

SPRINGDALE_UFCBGA932

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

FSB

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

PROCHOT#

BSEL0

BSEL1

B23

E22

B21

D20

B22

D22

B20

C21

E18

E20

B16

D16

B18

B17

E16

D18

G20

F17

E19

F19

J17

L18

G16

G18

F21

F15

E15

E21

J19

G14

E17

K17

J15

L16

J13

F13

F11

E13

K15

G12

G10

L15

E11

K13

J11

H10

G8

E9

B13

E14

B14

B12

B15

D14

C13

B11

D10

C11

E10

B10

C9

B9

D8

B8

L20

L13

L12

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_PROCHOT#

H_D#[0..63] 4

H_PROCHOT# 5,51

MCH_CLKSEL1 15

U43F

AR32

VSS

AR29

VSS

AR27

VSS

AR25

VSS

AR23

VSS

AR20

VSS

AR16

VSS

AR13

VSS

AR11

VSS

AR9

VSS

AN32

VSS

AN30

VSS

AN28

VSS

AN26

VSS

AN24

VSS

AN22

VSS

AN20

VSS

AN18

VSS

AN16

VSS

AN14

VSS

AN12

VSS

AN10

VSS

AM35

VSS

AM29

VSS

AM27

VSS

AM25

VSS

AM23

VSS

AM21

VSS

AM19

VSS

AM17

VSS

AM15

VSS

AM13

VSS

AM11

VSS

AM9

VSS

AL32

VSS

AL1

VSS

AK28

VSS

AK26

VSS

AK24

VSS

AK22

VSS

AK20

VSS

AK18

VSS

AK16

VSS

AK14

VSS

AK12

VSS

AK10

VSS

AK8

VSS

AK3

VSS

AJ35

VSS

AJ32

VSS

AJ9

VSS

AJ4

VSS

AJ1

VSS

AH33

VSS

AH30

VSS

AH24

VSS

AH22

VSS

AH20

VSS

AH18

VSS

AH16

VSS

AH14

VSS

AH12

VSS

AH10

VSS

AH6

VSS

AH3

VSS

AG35

VSS

AG32

VSS

AG28

VSS

AG26

VSS

AG24

VSS

AG22

VSS

AG20

VSS

AG18

VSS

AG16

VSS

AG14

VSS

AG8

VSS

AG4

VSS

AF33

VSS

AF30

VSS

AF25

VSS

AF24

VSS

AF22

VSS

AF20

VSS

AF18

VSS

AF16

VSS

AF14

VSS

AF11

VSS

AF9

VSS

AF6

VSS

AF3

VSS

AE35

VSS

AE32

VSS

AE26

VSS

AE25

VSS

AE13

VSS

AE12

VSS

SPRINGDALE_UFCBGA932

AE11

VSS

AE10

VSS

AE4

VSS

AE1

VSS

AD33

VSS

AD30

VSS

AD28

VSS

AD10

VSS

AD9

VSS

AD8

VSS

AD6

VSS

AD3

VSS

AC35

VSS

AC32

VSS

AC4

VSS

AC1

VSS

AB33

VSS

AB30

VSS

AB28

VSS

AB27

VSS

AB26

VSS

AB10

VSS

AB9

VSS

AB8

VSS

AB6

VSS

AB3

VSS

AA32

VSS

AA4

VSS

AA1

VSS

Y35

VSS

Y33

VSS

Y30

VSS

Y28

VSS

Y27

VSS

Y26

VSS

Y10

VSS

Y9

VSS

Y8

VSS

Y6

VSS

Y3

VSS

W32

VSS

W18

VSS

W17

VSS

W4

VSS

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

V33

V30

V28

V27

V26

V19

V17

V10

V9

V8

V6

V3

U32

U19

U18

U4

T35

T33

T30

T28

T27

T26

T10

T9

T8

T6

T3

T1

R32

R4

R1

P33

P30

P28

P27

P26

P9

P8

P6

P3

N35

N32

N4

N1

M33

M30

M28

M27

M26

M6

M3

L35

U43G

L31

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L26

L25

L24

K33

K29

K27

K25

K22

K20

K18

K16

K14

K12

K11

J35

J32

J28

J22

J20

J18

J16

J14

J12

J10

H33

H30

H26

H24

H22

H20

H18

H16

H14

H12

H9

H8

H5

H2

G35

G31

G28

F26

F24

F22

F20

F18

SPRINGDALE_UFCBGA932

F16

F14

F12

F10

F8

F5

F3

F1

E3

E1

D35

D33

D31

D29

D27

D25

D23

D21

D19

D17

D15

D13

D11

D9

D1

C28

C26

C24

C22

C20

C18

C16

C14

C12

C10

C8

C4

A32

A29

A27

A25

A23

A20

A16

A13

A11

A9

A7

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

3

2

Size Document Number Rev

Dat e : Sheet

Compal Electronics, Inc.

Springdale-Host/GND (1/4)

B

LA-1911

期三 七月

0.2

of

757¬P , 16, 2003

1

Page 8

5

DDRA_SMA[0..12]12,14

D D

C C

+SM_VREF_A

+SM_VREF_A trace width of 12mils and space

12mils(min)

2

C730

2.2U_0805_16V4Z

1

2

C731

0.1U_0402_16V4Z

1

DDRA_SMA[0..12]

DDRA_SWE#12,14

DDRA_SCAS#12,14

DDRA_SRAS#12,14

DDRA_SBS012,14

DDRA_SBS112,14

DDRA_SCS#012,14

DDRA_SCS#112,14

DDRA_CKE012,14

DDRA_CKE112,14

DDRA_CLK112

DDRA_CLK1#12

DDRA_CLK212

DDRA_CLK2#12

DDRA_SCS#0

DDRA_SCS#1 DDRA_SDQ18

DDRA_CKE0

DDRA_CKE1

SMXRCOMP

SMXRCOMPVOH

SMXRCOMPVOL

Close to GMCH(E34)

B B

A A

5

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

4

U43B

AJ34

SMAA_A0

AL33

SMAA_A1

AK29

SMAA_A2

AN31

SMAA_A3

AL30

SMAA_A4

AL26

SMAA_A5

AL28

SMAA_A6

AN25

SMAA_A7

AP26

SMAA_A8

AP24

SMAA_A9

AJ33

SMAA_A10

AN23

SMAA_A11

AN21

SMAA_A12

AL34

SMAB_A1

AM34

SMAB_A2

AP32

SMAB_A3

AP31

SMAB_A4

AM26

SMAB_A5

AB34

SWE_A#

Y34

SCAS_A#

AC33

SRAS_A#

AE33

SBA_A0

AH34

SBA_A1

AA34

SCS_A0#

Y31

SCS_A1#

Y32

SCS_A2#

W34

SCS_A3#

AL20

SCKE_A0

AN19

SCKE_A1

AM20

SCKE_A2

AP20

SCKE_A3

AK32

SCMDCLK_A0

AK31

SCMDCLK_A0#

AP17

SCMDCLK_A1

AN17

SCMDCLK_A1#

N33

SCMDCLK_A2

N34

SCMDCLK_A2#

AK33

SCMDCLK_A3

AK34

SCMDCLK_A3#

AM16

SCMDCLK_A4

AL16

SCMDCLK_A4#

P31

SCMDCLK_A5

P32

SCMDCLK_A5#

E34

SMVREF_A

AK9

SMXRCOMP

AN9

SMXRCOMPVOH

AL9

SMXRCOMPVOL

SPRINGDALE_UFCBGA932

4

AN11

SDQS_A0

AP12

SDM_A0

AP10

SDQ_A0

AP11

SDQ_A1

AM12

SDQ_A2

AN13

SDQ_A3

AM10

SDQ_A4

AL10

SDQ_A5

AL12

SDQ_A6

AP13

SDQ_A7

AP15

SDQS_A1

AP16

SDM_A1

AP14

SDQ_A8

AM14

SDQ_A9

AL18

SDQ_A10

AP19

SDQ_A11

AL14

SDQ_A12

AN15

SDQ_A13

AP18

SDQ_A14

AM18

SDQ_A15

AP23

SDQS_A2

AM24

SDM_A2

AP22

SDQ_A16

AM22

SDQ_A17

AL24

SDQ_A18

AN27

SDQ_A19

AP21

SDQ_A20

AL22

SDQ_A21

DDR Channel A

SDQ_A22

SDQ_A23

SDQS_A3

SDM_A3

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_A31

SDQS_A4

SDM_A4

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_A35

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_A39

SDQS_A5

SDM_A5

SDQ_A40

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_A47

SDQS_A6

SDM_A6

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_A54

SDQ_A55

SDQS_A7

SDM_A7

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_A63

AP25

AP27

AM30

AP30

AP28

AP29

AP33

AM33

AM28

AN29

AM31

AN34

AF34

AF31

AH32

AG34

AF32

AD32

AH31

AG33

AE34

AD34

V34

W33

AC34

AB31

V32

V31

AD31

AB32

U34

U33

M32

M34

T34

T32

K34

K32

T31

P34

L34

L33

H31

H32

J33

H34

E33

F33

K31

J34

G34

F34

3

DDRA_SDQ[0..63]

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

DDRA_SDQ[0..63] 12,14

DDRA_SDQS0 12,14

DDRA_SDM0 12,14

DDRA_SDQS1 12,14

DDRA_SDM1 12,14

DDRA_SDQS2 12,14

DDRA_SDM2 12,14

DDRA_SDQS3 12,14

DDRA_SDM3 12,14

DDRA_SDQS4 12,14

DDRA_SDM4 12,14

DDRA_SDQS5 12,14

DDRA_SDM5 12,14

DDRA_SDQS6 12,14

DDRA_SDM6 12,14

DDRA_SDQS7 12,14

DDRA_SDM7 12,14

2

DDR Resistive Compensation

2

C92

2.2U_0805_16V4Z

1

DDR RCOMP VOH Circuitry

2

C590

2.2U_0805_16V4Z

1

1

C595

1U_0603_10V6K

2

DDR RCOMP VOL Circuitry

2

C110

2.2U_0805_16V4Z

1

1

C146

1U_0603_10V6K

2

2

1

+2.5V

Trace width of 12mils and space

10mils(min)

12

R94

42.2_0603_1%

SMXRCOMP

12

+2.5V

12

12

R98

42.2_0603_1%

R434

10K_0603_1%

SMXRCOMPVOH

R436

30.9K_0603_1%

*

Place resistors within

1.0 inch of GMCH (AK9)

*

R391 Change to 31.12K is real

Trace width of 12mils and space

10mils(min)

1

C777

0.01U_0402_16V7K

2

1

C152

0.01U_0402_16V7K

2

Close to Pin AN9

Close to GMCH <1"

Follow Intel design guide

R1.11(12474) page124,125

*

+2.5V

R153 Change to 31.12K is real

Trace width of 12mils and space

10mils(min)

12

R106

30.9K_0603_1%

*

SMXRCOMPVOL

12

R110

10K_0603_1%

1

C167

0.01U_0402_16V7K

2

Close to Pin AL9

Close to GMCH <1"

Compal Electronics, Inc.

Title

Springdale-DDR Interface-A(2/5)

Size Document Number Rev

B

LA-1911

Dat e : Sheet

期三 七月

1

of

857¬P , 16, 2003

0.2

Page 9

5

DDRB_SMA[0..12]13,14

D D

C C

SM_VREF_B and SM_VREF_A

are connected inside GMCH.

+2.5V

2

12

R442

150_0603_1%

12

B B

R444

150_0603_1%

C598

2.2U_0805_16V4Z

1

2

C612

2.2U_0805_16V4Z

1

DDRB_SMA[0..12]

DDRB_SWE#13,14

DDRB_SCAS#13,14

DDRB_SRAS#13,14

DDRB_SBS013,14

DDRB_SBS113,14

DDRB_SCS#013,14

DDRB_SCS#113,14

DDRB_CKE013,14

DDRB_CKE113,14

DDRB_CLK113

DDRB_CLK1#13

DDRB_CLK213

DDRB_CLK2#13

+SM_VREF_B

+SM_VREF_B trace width of

12mils and space

12mils(min)

2

C138

0.1U_0402_16V4Z

1

DDRB_SCS#0

DDRB_SCS#1

DDRB_CKE0

DDRB_CKE1

SMYRCOMP

SMYRCOMPVOH

SMYRCOMPVOL

Close to GMCH(AP9)

A A

DDRB_SMA0

DDRB_SMA1

DDRB_SMA2

DDRB_SMA3

DDRB_SMA4

DDRB_SMA5

DDRB_SMA6

DDRB_SMA7

DDRB_SMA8

DDRB_SMA9

DDRB_SMA10

DDRB_SMA11

DDRB_SMA12

4

U43C

AG31

SMAA_B0

AJ31

SMAA_B1

AD27

SMAA_B2

AE24

SMAA_B3

AK27

SMAA_B4

AG25

SMAA_B5

AL25

SMAA_B6

AF21

SMAA_B7

AL23

SMAA_B8

AJ22

SMAA_B9

AF29

SMAA_B10

AL21

SMAA_B11

AJ20

SMAA_B12

AE27

SMAB_B1

AD26

SMAB_B2

AL29

SMAB_B3

AL27

SMAB_B4

AE23

SMAB_B5

W27

SWE_B#

W31

SCAS_B#

W26

SRAS_B#

Y25

SBA_B0

AA25

SBA_B1

U26

SCS_B0#

T29

SCS_B1#

V25

SCS_B2#

W25

SCS_B3#

AK19

SCKE_B0

AF19

SCKE_B1

AG19

SCKE_B2

AE18

SCKE_B3

AG29

SCMDCLK_B0

AG30

SCMDCLK_B0#

AF17

SCMDCLK_B1

AG17

SCMDCLK_B1#

N27

SCMDCLK_B2

N26

SCMDCLK_B2#

AJ30

SCMDCLK_B3

AH29

SCMDCLK_B3#

AK15

SCMDCLK_B4

AL15

SCMDCLK_B4#

N31

SCMDCLK_B5

N30

SCMDCLK_B5#

AP9

SMVREF_B

AA33

SMYRCOMP

R34

SMYRCOMPVOH

R33

SMYRCOMPVOL

SPRINGDALE_UFCBGA932

AF15

SDQS_B0

AG11

SDM_B0

AJ10

SDQ_B0

AE15

SDQ_B1

AL11

SDQ_B2

AE16

SDQ_B3

AL8

SDQ_B4

AF12

SDQ_B5

AK11

SDQ_B6

AG12

SDQ_B7

AG13

SDQS_B1

AG15

SDM_B1

AE17

SDQ_B8

AL13

SDQ_B9

AK17

SDQ_B10

AL17

SDQ_B11

AK13

SDQ_B12

AJ14

SDQ_B13

AJ16

SDQ_B14

AJ18

SDQ_B15

AG21

SDQS_B2

AE21

SDM_B2

AE19

SDQ_B16

AE20

SDQ_B17

AG23

SDQ_B18

AK23

SDQ_B19

AL19

SDQ_B20

DDR Channel B

SDQ_B21

SDQ_B22

SDQ_B23

SDQS_B3

SDM_B3

SDQ_B24

SDQ_B25

SDQ_B26

SDQ_B27

SDQ_B28

SDQ_B29

SDQ_B30

SDQ_B31

SDQS_B4

SDM_B4

SDQ_B32

SDQ_B33

SDQ_B34

SDQ_B35

SDQ_B36

SDQ_B37

SDQ_B38

SDQ_B39

SDQS_B5

SDM_B5

SDQ_B40

SDQ_B41

SDQ_B42

SDQ_B43

SDQ_B44

SDQ_B45

SDQ_B46

SDQ_B47

SDQS_B6

SDM_B6

SDQ_B48

SDQ_B49

SDQ_B50

SDQ_B51

SDQ_B52

SDQ_B53

SDQ_B54

SDQ_B55

SDQS_B7

SDM_B7

SDQ_B56

SDQ_B57

SDQ_B58

SDQ_B59

SDQ_B60

SDQ_B61

SDQ_B62

SDQ_B63

AK21

AJ24

AE22

AH27

AJ28

AK25

AH26

AG27

AF27

AJ26

AJ27

AD25

AF28

AD29

AC31

AE30

AC27

AC30

Y29

AE31

AB29

AA26

AA27

U30

U31

AA30

W30

U27

T25

AA31

V29

U25

R27

L27

M29

P29

R30

K28

L30

R31

R26

P25

L32

J30

J31

K30

H29

F32

G33

N25

M25

J29

G32

DDRB_SDQ[0..63]

DDRB_SDQ0

DDRB_SDQ1

DDRB_SDQ2

DDRB_SDQ3

DDRB_SDQ4

DDRB_SDQ5

DDRB_SDQ6

DDRB_SDQ7

DDRB_SDQ8

DDRB_SDQ9

DDRB_SDQ10

DDRB_SDQ11

DDRB_SDQ12

DDRB_SDQ13

DDRB_SDQ14

DDRB_SDQ15

DDRB_SDQ16

DDRB_SDQ17

DDRB_SDQ18

DDRB_SDQ19

DDRB_SDQ20

DDRB_SDQ21

DDRB_SDQ22

DDRB_SDQ23

DDRB_SDQ24

DDRB_SDQ25

DDRB_SDQ26

DDRB_SDQ27

DDRB_SDQ28

DDRB_SDQ29

DDRB_SDQ30

DDRB_SDQ31

DDRB_SDQ32

DDRB_SDQ33

DDRB_SDQ34

DDRB_SDQ35

DDRB_SDQ36

DDRB_SDQ37

DDRB_SDQ38

DDRB_SDQ39

DDRB_SDQ40

DDRB_SDQ41

DDRB_SDQ42

DDRB_SDQ43

DDRB_SDQ44

DDRB_SDQ45

DDRB_SDQ46

DDRB_SDQ47

DDRB_SDQ48

DDRB_SDQ49

DDRB_SDQ50

DDRB_SDQ51

DDRB_SDQ52

DDRB_SDQ53

DDRB_SDQ54

DDRB_SDQ55

DDRB_SDQ56

DDRB_SDQ57

DDRB_SDQ58

DDRB_SDQ59

DDRB_SDQ60

DDRB_SDQ61

DDRB_SDQ62

DDRB_SDQ63

3

DDRB_SDQS0 13,14

DDRB_SDM0 13,14

DDRB_SDQS1 13,14

DDRB_SDM1 13,14

DDRB_SDQS2 13,14

DDRB_SDM2 13,14

DDRB_SDQS3 13,14

DDRB_SDM3 13,14

DDRB_SDQS4 13,14

DDRB_SDM4 13,14

DDRB_SDQS5 13,14

DDRB_SDM5 13,14

DDRB_SDQS6 13,14

DDRB_SDM6 13,14

DDRB_SDQS7 13,14

DDRB_SDM7 13,14

DDRB_SDQ[0..63] 13,14

2

DDR Resistive Compensation

+2.5V

DDR RCOMP VOH Circuitry

+2.5V

2

C709

2.2U_0805_16V4Z

1

1

C691

1U_0603_10V6K

2

DDR RCOMP VOL Circuitry

+2.5V

2

C316

2.2U_0805_16V4Z

1

1

C300

1U_0603_10V6K

2

1

2

12

R494

42.2_0603_1%

SMYRCOMP

12

R496

42.2_0603_1%

R398 Change to 31.12K is real

*

Trace width of 12mils and space

10mils(min)

12

R510

10K_0603_1%

SMYRCOMPVOH

12

R506

30.9K_0603_1%

R163 Change to 31.12K is real

*

Trace width of 12mils and space

10mils(min)

12

R224

30.9K_0603_1%

SMYRCOMPVOL

12

R223

10K_0603_1%

C685

2.2U_0805_16V4Z

1

Trace width of 12mils

and space 10mils(min)

Place resistors within

1.0 inch of GMCH (AA33)

1

C778

0.01U_0402_16V7K

2

1

C296

0.01U_0402_16V7K

2

Close to Pin R14

Close to GMCH <1"

1

C292

0.01U_0402_16V7K

2

Close to Pin R33

Close to GMCH <1"

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Springdale-DDR Interface-B(3/5)

Size Document Number Rev

B

LA-1911

Dat e : Sheet

期三 七月

1

of

957¬P , 16, 2003

0.2

Page 10

5

+1.5VS

12

R112

43.2_0402_1%

+1.5VS

12

R163

226_0603_1%

12

R439

147_0603_1%

12

R437

113_0603_1%

1

C151

0.1U_0402_16V4Z

2

1

C149

0.1U_0402_16V4Z

2

GRCOMP

HI_SW ING_MCH

1

2

HI_VREF_MCH

1

2

+1.5VS

12

CI_SW ING_GMCH

12

12

D D

C C

B B

+1.5VS

C164

0.1U_0402_16V4Z

C605

0.1U_0402_16V4Z

R100

226_0603_1%

R99

147_0603_1%

CI_VREF_GMCH

R108

113_0603_1%

12

R103

52.3_0603_1%

HI_RCOMP_MCH

GMCH-HUB Reference Circuit

Close to GMCH(AE3)

1

C170

0.01U_0402_16V7K

2

Close to GMCH ball <250mils

Close to GMCH(AE2)

1

C603

0.01U_0402_16V7K

2

Close to GMCH ball <250mils

GMCH-CSA Reference Circuit

Close to GMCH(AF2)

1

C137

0.01U_0402_16V7K

2

Close to GMCH ball <250mils

0.35V

Close to GMCH(AF4)

1

C158

0.01U_0402_16V7K

2

CLK_MCH_66M

Note:

HI_SWING_MCH, HI_VREF_MCH

trace width of 10mils and

space 7mils

Note:

CI_SWING_MCH, CI_VREF_MCH

trace width of 10mils and

space 20mils

Close to GMCH ball <250mils

+1.5VS

12

R150

60.4_0603_1%

AGP_SWING

12

R143

39.2_0603_1%

+AGP_VREF = 0.3535

1 2

A A

R144

44.2_0603_1%

12

R151

100_0603_1%

5

GMCH-AGP Reference Circuit

Close GMCH ball (AC3) less than 250mils

1

C175

0.1U_0402_16V4Z

2

+AGP_VREF

1

C160

0.01U_0402_16V7K

2

Close GMCH ball (AD2)

less than 250mils

1

C171

0.01U_0402_16V7K

2

Follow Springdale Chipset Platform Design guide Rev1.11(12474)

Note:

Springdale Customer Schematic R1.2 page18

AGP_SWING only had 0.1u cap ; But Springdale

Chipset Platform Design guide Rev1.11(12474)

page138 had a 0.01uf cap. need confirm with

Intel.

12

R453

@10_0402_5%

1

C624

@10P_0402_50V8K

2

4

R590

+3VS

4

1 2

R596

@1K_0402_5%

@0_0402_5%

12

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

AGP_C/BE#[0..3]16

AGP_FRAME#16

CLK_MCH_66M15

AGP_DEVSEL#16

AGP_IRDY#16

AGP_TRDY#16

AGP_STOP#16

AGP_PAR16

AGP_REQ#16

AGP_GNT#16

+AGP_VREF

AGP_RBF#16

AGP_WBF#16

AGP_DBIHI16

AGP_DBILO16

AGP_ST[0..2]16

HUB_HL[0..10]23

HUB_HLSTRF23

HUB_HLSTRS23

R435 52.3_0603_1%

+1.5VS

PCIRST#16,22,23,26,27,29,30,33,34,37

3

1 2

R166 0_0402_5%

R128 0_0402_5%

AGP_C/BE#0

AGP_C/BE#1

AGP_C/BE#2

AGP_C/BE#3

CLK_MCH_66M AGP_AD3

AGP_PAR

GRCOMP

AGP_SWING

+AGP_VREF

AGP_ST0

AGP_ST1

AGP_ST2

HUB_HL0

HUB_HL1

HUB_HL2

HUB_HL3

HUB_HL4

HUB_HL5

HUB_HL6

HUB_HL7

HUB_HL8

HUB_HL9

HUB_HL10

HI_RCOMP_MCH

HI_SW ING_MCH

HI_VREF_MCH

CI_SWING_GMCH

CI_VREF_GMCH

12

12

2

U43D

Y7

GCBE0

W5

GCBE1

AA3

GCBE2

U2

GCBE3

U6

GFRAME

H4

GCLKIN

AB4

GDEVSEL

V11

GIRDY

AB5

GTRDY

W11

GSTOP

AB2

GPAR/ADD_DETECT

N6

GREQ

M7

GGNT

AC2

GRCOMP/DVOBCGCOMP

AC3

GVSWING

AD2

GVREF

R10

GRBF

R9

GWBF

M4

DBI_HI

M5

DBI_LO

N3

GST0

N5

GST1

N2

GST2

AF5

HI0

AG3

HI1

AK2

HI2

AG5

HI3

AK5

HI4

AL3

HI5

AL2

HI6

AL4

HI7

AJ2

HI8

AH2

HI9

AJ3

HI10

AH5

HISTRF

AH4

HISTRS

AD4

HI_RCOMP

AE3

HI_SWING

AE2

HI_VREF

AK7

CI0

AH7

CI1

AD11

CI2

AF7

CI3

AD7

CI4

AC10

AG10

AN35

AP34

CSA

CI5

AF8

CI6

AG7

CI7

AE9

CI8

AH9

CI9

AG6

CI10

AJ6

CISTRF

AJ5

CISTRS

AG2

CI_RCOMP

AF2

CI_SWING

AF4

CI_VREF

G4

DREFCLK

AP8

EXTTS#

AJ8

ICH_SYNC#

AK4

RSTIN#

RESERVED_1

AG9

RESERVED_2

RESERVED_3

RESERVED_4

AR1

RESERVED_5

SPRINGDALE_UFCBGA932

2

1

AGP_AD[0..31] 16

AC6

GADSTBF0

GADSTBS0#

AGP

GADSTBS1#

HUB

DDCA_DATA

VGA

AC5

AGP_AD0

AE6

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GADSTBF1

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29

GAD30

GAD31

GSBSTBF

GSBSTBS#

GSBA0#

GSBA1#

GSBA2#

GSBA3#

GSBA4#

GSBA5#

GSBA6#

GSBA7#

DDCA_CLK

RED

RED#

GREEN

GREEN#

BLUE

BLUE#

HSYNC

VSYNC

REFSET

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

NC_20

Title

Size Document Number Rev

B

Dat e : Sheet

AGP_AD1

AC11

AGP_AD2

AD5

AE5

AGP_AD4

AA10

AGP_AD5

AC9

AGP_AD6

AB11

AGP_AD7

AB7

AGP_AD8

AA9

AGP_AD9

AA6

AGP_AD10

AA5

AGP_AD11

W10

AGP_AD12

AA11

AGP_AD13

W6

AGP_AD14

W9

AGP_AD15

V7

V4

V5

AGP_AD16

AA2

AGP_AD17

Y4

AGP_AD18

Y2

AGP_AD19

W2

AGP_AD20

Y5

AGP_AD21

V2

AGP_AD22

W3

AGP_AD23

U3

AGP_AD24

T2

AGP_AD25

T4

AGP_AD26

T5

AGP_AD27

R2

AGP_AD28

P2

AGP_AD29

P5

AGP_AD30

P4

AGP_AD31

M2

U11

T11

AGP_SBA0

R6

AGP_SBA1

P7

AGP_SBA2

R3

AGP_SBA3

R5

AGP_SBA4

U9

AGP_SBA5

U10

AGP_SBA6

U5

AGP_SBA7

T7

R149 0_0402_5%

H3

R165 0_0402_5%

F2

R170 0_0402_5%

F4

E4

R169 0_0402_5%

H6

G5

R172 0_0402_5%

H7

G6

G3

E2

R460 0_0402_5%

D2

A3

A33

A35

Analog RGB/CRT guidelines

AF13

for Springdale-P

AF23

AJ12

AN1

AP2

AR3

AR33

AR35

B2

B25

B34

C1

C23

C35

E26

M31

R25

Springdale-AGP/HUB/VGA/CSA (4/5)

LA-1911

期三 七月

AGP_AD_STBF0 16

AGP_AD_STBS0 16

AGP_AD_STBF1 16

AGP_AD_STBS1 16

12

12

12

12

12

12

1

AGP_SB_STBF 16

AGP_SB_STBS 16

AGP_SBA[0..7] 16

of

10 57¬P , 16, 2003

0.2

Page 11

5

Note:

Placed less than 100 mils from ball

Route to GMCH ball without via

D D

1

C681

0.47U_0603_16V7K

2

2

C713

0.1U_0402_10V6K

1

C C

C618

0.1U_0402_10V6K

12

C620 0.22U_0603_10V7K

C736

0.47U_0603_16V7K

12

C719 0.22U_0603_10V7K

C128

Trace 14mils

R467

B B

Note:

Placed less than 100 mils from ball

Route to GMCH ball without via

A A

0.1U_0402_10V6K

12

12

C329 0.1U_0402_10V6K

R462 0_0402_5%

0_0402_5%

12

12

1 2

C248 0.1U_0402_10V6K

VTT_DCAP1

VTT_DCAP2

1

C699

0.47U_0603_16V7K

2

+VTT_GMCH

+2.5V

VCC_DDR_DCAP5

12

VCC_DDR_DCAP4

VCC_DDR_DCAP1

12

+3VS

VCC_AGP_DCAP2

+1.5VS

VTT_DCAP3

VCCA_FSB

VCCA_DPLL

VCCA_DAC

VCC_DDR_DCAP2 VCCA_FSB1 VCCA_FSB

VCCA1P5_DDR_SM

(1A)

A15

A21

A4

A5

A6

B5

B6

C5

C6

D5

D6

D7

E6

E7

F7

AA35

AL6

AL7

AM1

AM2

AM3

AM5

AM6

AM7

AM8

AN2

AN4

AN5

AN6

AN7

AN8

AP3

AP4

AP5

AP6

AP7

AR15

AR21

*

AR31

AR4

AR5

AR7

E35

R35

G1

G2

AG1

Y11

A31

B4

B3

C2

AL35

AB25

AC25

AC26

Decoupling Reference Document:

Springdale Chipset Platform Design guide Rev1.11

(12474)page246,248

Decoupling Reference Document:

Springdale Customer Schematic R1.2 page84

4

U43E

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DDR

VCC_DAC

VCC_DAC

VCCA_AGP

VCCA_AGP

VCCA_FSB

VCCA_FSB

VCCA_DPLL

VCCA_DAC

VCCA_DDR

VCCA_DDR

VCCA_DDR

VCCA_DDR

SPRINGDALE_UFCBGA932

POWER

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VCC_AGP

VSSA_DAC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

J6

J7

J8

J9

K6

K7

K8

K9

L6

L7

L9

L10

L11

M8

M9

M10

M11

N9

N10

N11

P10

P11

R11

T16

T17

T18

T19

T20

U16

U17

U20

V16

V18

V20

W16

W19

W20

Y16

Y17

Y18

Y19

Y20

J1

J2

J3

J4

J5

K2

K3

K4

K5

L1

L2

L3

L4

L5

Y1

D3

+1.5VS

VCC_AGP_DCAP1

3

+2.5V

1

C105

0.1U_0402_10V6K

2

1

C283

0.1U_0402_10V6K

2

1

C217

0.1U_0402_10V6K

2

C243

10U_1206_10V4Z

+2.5V

+1.5VS

+1.5VS

1

2

1

2

1

2

1

+

2

C90

22U_1206_10V4Z

C150

0.1U_0402_10V6K

C231

0.1U_0402_10V6K

C198

470U_D4_2.5VM

2

C91

4.7U_0805_6.3V6K

1

1

C98

0.1U_0402_10V6K

2

1

C229

0.1U_0402_10V6K

2

2

C224

4.7U_0805_6.3V6K

1

Place at the output of the 1.5V VR

+VTT_GMCH +2.5V

1

C242

0.1U_0402_10V6K

2

Place near GMCH

1 2

C166

0.1U_0402_10V6K

+1.5VS

1

C233

0.1U_0402_10V6K

2

Place near ball

Y11,routing trace

from cap to ball

Note: Please change to 0.82uH, DC current

of 30mA parts and close to cap

+1.5VS

12

R141

0_0603_5%

Note: Please change to 1uH(0.54uH-D-IN), DC current

of 1000mA parts and close to cap

Trace 50mils

Trace 35mils (under GMCH ball field)

+1.5VS

VCCA_DDR VCCA1P5_DDR_SM

12

R183

0_0603_5%

1

C208

0.1U_0402_10V6K

2

+1.5VS

1

C246

0.1U_0402_10V6K

2

1

C213

0.1U_0402_10V6K

2

+VTT_GMCH

1

+

C266

470U_D4_2.5VM

2

L15

1 2

LQG21F4R7N00_0805

1 2

0_0805_5%

1

C103

0.1U_0402_10V6K

2

1

C207

0.1U_0402_10V6K

2

1

C148

0.1U_0402_10V6K

2

Place near GMCH

**

**

L18

2

1

C201

0.1U_0402_10V6K

2

2

C240

0.1U_0402_16V4Z

1

Trace 14milsTrace 14mils

12

C214

+

150U_D2_6.3VM

Trace 35mils

(1A)(1A)

1

C222

22U_1206_6.3V6M

2

1

C114

0.1U_0402_10V6K

2

1

C220

0.1U_0402_10V6K

2

2

C253

4.7U_0805_6.3V6K

1

1

C117

0.1U_0402_10V6K

2

1

C197

0.1U_0402_10V6K

2

2

1

2

C235

0.1U_0402_16V4Z

1

Close to GMCH

2

C241

0.1U_0402_16V4Z

1

Close to GMCH

1

C109

0.1U_0402_10V6K

2

1

C216

0.1U_0402_10V6K

2

C258

4.7U_0805_6.3V6K

1

1

C249

1U_0603_10V6K

2

1

C123

0.1U_0402_10V6K

2

1

C234

0.1U_0402_10V6K

2

1

2

C244

0.47U_0603_16V7K

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Dat e : Sheet

Compal El ectronics, Inc.

Springdale-Decoupling (5/5)

B

LA-1911

期三 七月

0.2

of

11 57¬P , 16, 2003

1

Page 12

5

+2.5V

JP22

1

VREF

3

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQS0

DDRA_SDQ6 DDRA_SDQ7

DDRA_SDQ2

D D

DDRA_CLK18

DDRA_CLK1#8

C C

DDRA_CKE18,14

DDRA_SBS08,14

DDRA_SWE#8,14

DDRA_SCS#08,14

B B

A A

ICH_SMB_DATA13,15,23

ICH_SMB_CLK13,15,23

5

DDRA_SDQ12

DDRA_SDQ8

DDRA_SDQS1

DDRA_SDQ10

DDRA_SDQ15

DDRA_SDQ20

DDRA_SDQ16

DDRA_SDQS2

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQS3

DDRA_SDQ30

DDRA_SDQ27

DDRA_CKE1

DDRA_SMA12

DDRA_SMA9

DDRA_SMA7

DDRA_SMA5

DDRA_SMA3

DDRA_SMA1

DDRA_SMA10

DDRA_SBS0

DDRA_SWE#

DDRA_SCS#0

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQS4

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ44

DDRA_SDQ41 DDRA_SDQ45

DDRA_SDQS5

DDRA_SDQ43

DDRA_SDQ46

DDRA_SDQ48

DDRA_SDQ53

DDRA_SDQS6

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQS7

DDRA_SDQ62

DDRA_SDQ59

+3VS

VSS

5

DQ0

7

DQ1

9

VDD

11

DQS0

13

DQ2

15

VSS

17

DQ3

19

DQ8

21

VDD

23

DQ9

25

DQS1

27

VSS

29

DQ10

31

DQ11

33

VDD

35

CK0

37

CK0#

39

VSS

41

DQ16

43

DQ17

45

VDD

47

DQS2

49

DQ18

51

VSS

53

DQ19

55

DQ24

57

VDD

59

DQ25

61

DQS3

63

VSS

65

DQ26

67

DQ27

69

VDD

71

CB0

73

CB1

75

VSS

77

DQS8

79

CB2

81

VDD

83

CB3

85

DU

87

VSS

89

CK2

91

CK2#

93

VDD

95

CKE1

97

DU/A13

99

A12

101

A9

103

VSS

105

A7

107

A5

109

A3

111

A1

113

VDD

115

A10/AP

117

BA0

119

WE#

121

S0#

123

DU

125

VSS

127

DQ32

129

DQ33

131

VDD

133

DQS4

135