Page 1

5

hexainf@hotmail.com

D D

4

3

2

1

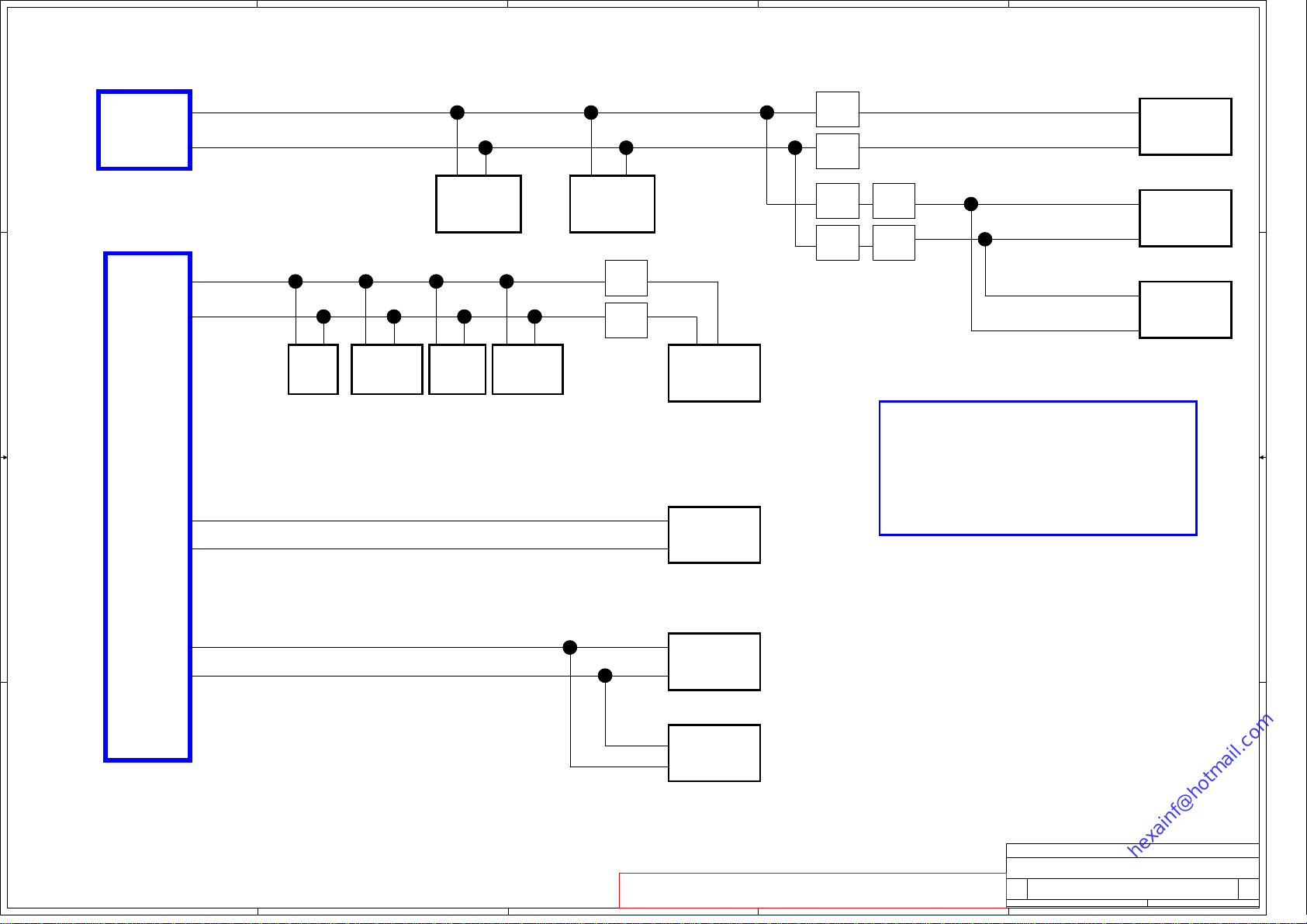

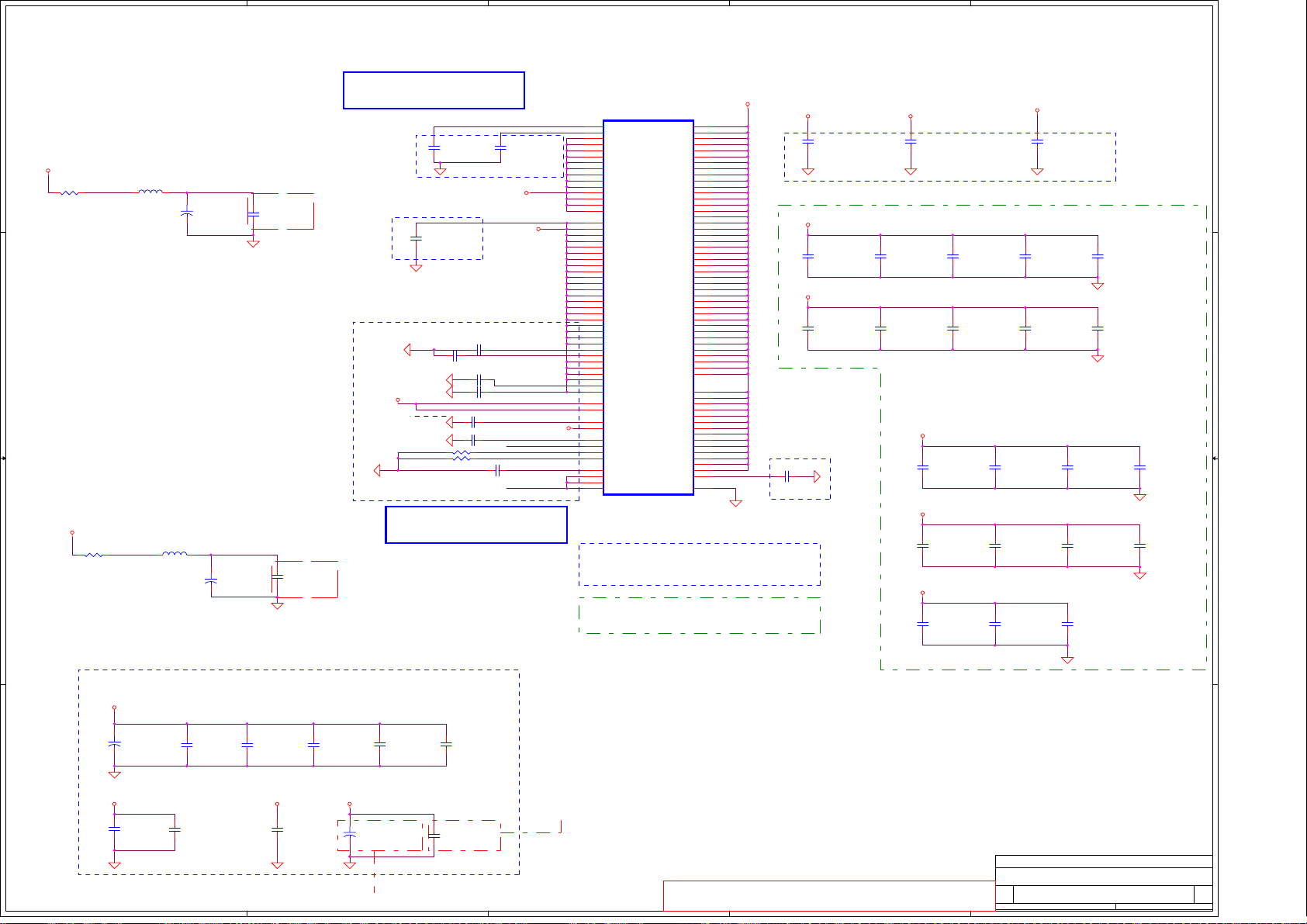

Prescott & Springdale Schematic with Capture CIS

and Function field

C C

uFCPGA Prescott

2003-07-23

Cature library ball out check document

Prescott : Prescott processor Electrial,Mechanical and

Thermal Specification Rev0.5 [Check by HW:Henry,Steve]

B B

Springdale(GMCH): Springdale GMCH External Design

Specification (EDS) REV1.0 [Check by HW: Henry,Rita]

ICH5: N/A

REV: X02-D

@ : Depop Component

1@ : Depop on Nimitz(Inspiron)

2@ : Depop on Beijing(Precision)

A A

Compal Electronics, Inc.

Cover Sheet

LA-1711

1

160Wednesday , July 23, 2003

X02-D

of

5

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS , INC. NEITH ER THIS S HEET NOR T HE INFORMA TION IT CONT AINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSEN T OF COMP AL ELEC TRONICS , INC.

3

2

Size Document Number Re v

Dat e: Sheet

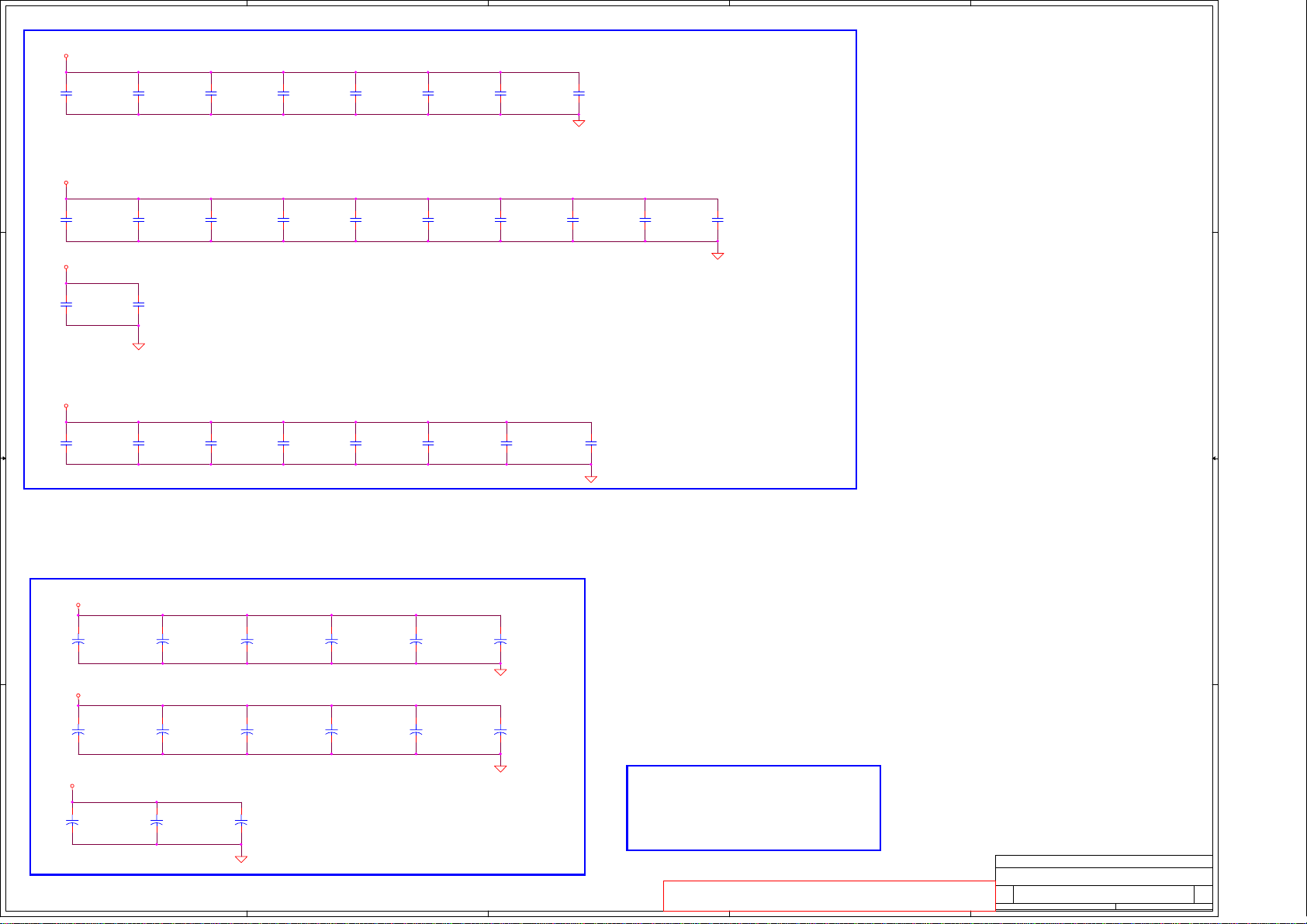

Page 2

5

hexainf@hotmail.com

4

3

2

1

Compal confidential

D D

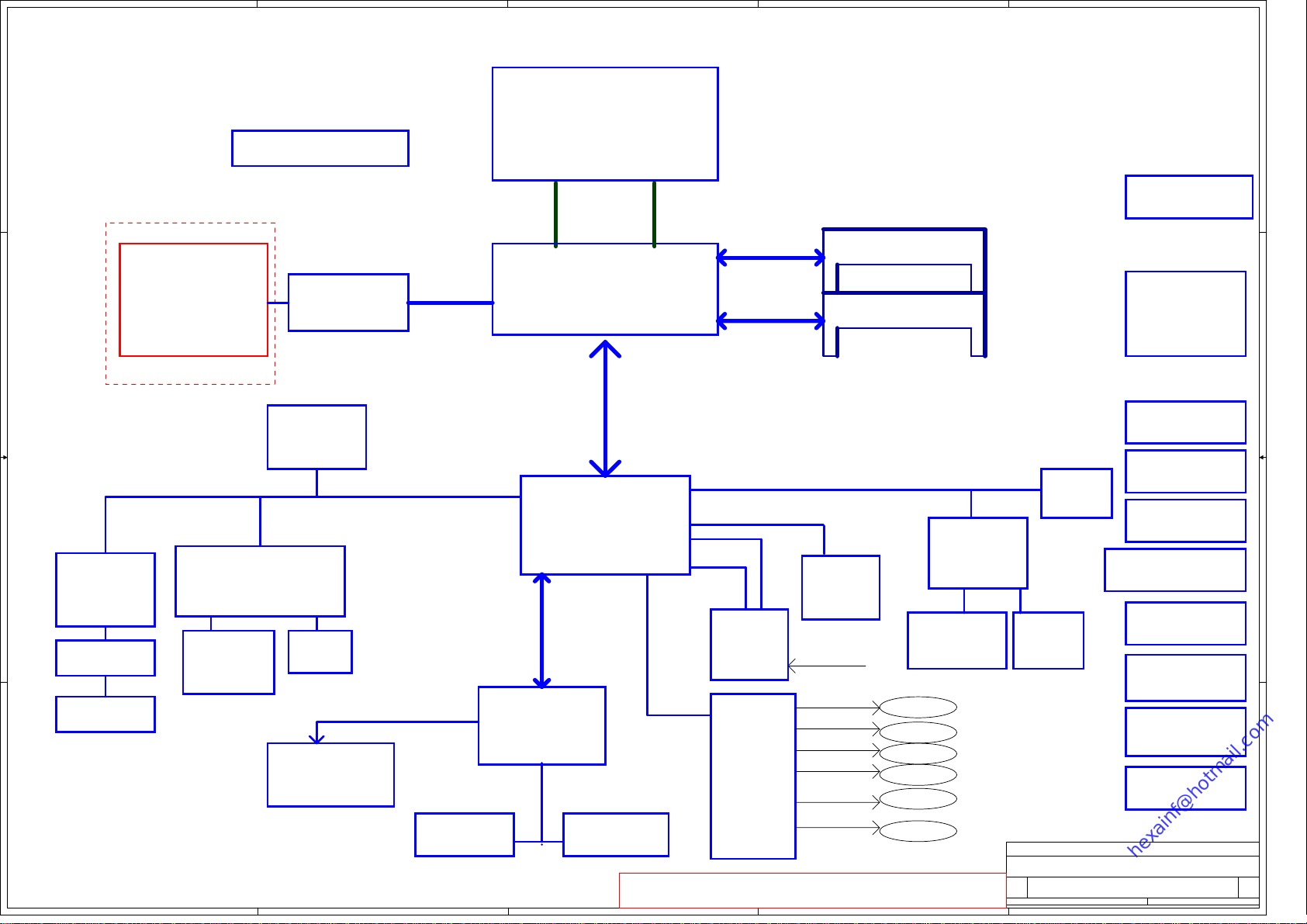

ADT7460 Thermal sensor

page 19

HA#( 3..31)

VGA

Board

[CRT CONN. & TV-OUT]

C C

AGP CONN.

page 18

AGP4X/8X(1.5V)

Prescott

478 uFCPGA CPU

page 7,8,9

System Bus

533/800MHz

Springdale

GMCH

932 FC-BGA

page

10,11,12,13

HD#(0..63)

Block Diagram

Memory

BUS(DDR)

2.5V

266/333/400MHz

2.5V

266/333/400MHz

Channel A SO-DIMM

BANK 0, 1, 2,3

Channel B SO-DIMM

BANK 0, 1, 2,3

page 15

page 16

Fan Control

page 14

Clock Generator

CK409

page 6

HUB Link

MINI PCI

page 32

PCI BUS

IDSEL:AD20

(PIRQA/B#,GNT#2,REQ#2)

B B

LAN

BCM5705M

BCM4401

Transformer

RJ45

page 28

page 29

page 29

CardBus Controller

PCI7510/PCI4510

1394, Smart

card

page31

3.3V 33MHz

page 30

Slot 0

page31

X BUS

LPC BUS

3.3V 33MHz

SST39VF080

A A

5

page 35

Touch Pad

page 35

4

1.5V

66Mhz

266MB/S

Macallen

LPC to X-BUS

& Super I/O

ICH5

460 BGA

Page

33,34

Int.KBD

3.3V 24.57 6MHz

3.3V ATA100

Page

20,21,22

SATA

ATA100

ATA100

HDD

page 21

CDROM

USB

FDD

page 23

USB2.0

page 26

page 27

page 35

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVIS ION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE IN FORMATION IT CONT AINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL E LECTRON ICS, INC .

3

USBPORT 4

USBPORT 1

USBPORT 2

USBPORT 3

USBPORT 4

USBPORT 6

BT

BACK

DOG

MOD

BACKUSBPORT 5

BACK

2

AC97

Codec

STAC9750

AMP& Phone

Jack Interface

page 25

AC-LINK

MDC

page 27

page 24

Subwoofer

page 50

Title

Size Doc ument Number Re v

Date: Sheet

Compal Electronics, Inc.

LA-1711

DC IN

BATT

IN

3.3V/5V

1.5V/+VTT_GMCH

1.25V/2.5V

VCORE

VCORE_CTRL

CHARGER

Block Diagram

1

260Wednesday, July 23, 2003

page 41

page 42

page 43

page 44

page 45

page 47

page 46

page 48

of

X02-D

Page 3

5

hexainf@hotmail.com

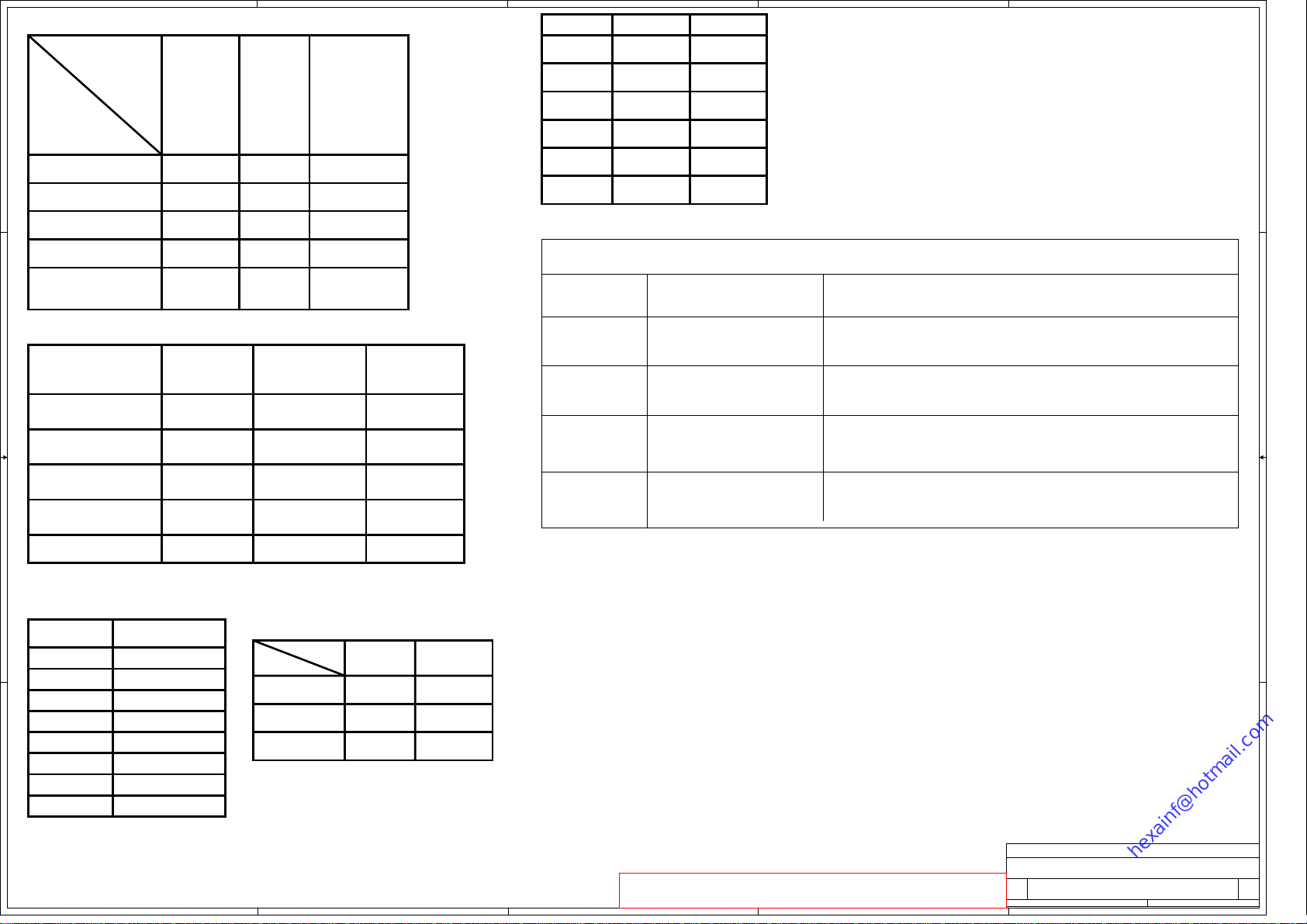

PM TABLE

power

plane

State

D D

S0

S1

+3VALW

+5VALW

+3VSUS

+5VSUS

+2.5V_MEM

+3.3VRTC

+RTC_PWR

V_1P25V_DDR_VTT

ON

ON

ON

ON

+3VRUN

+5VRUN

+1.5VRUN

+VCC_CORE

+12V

+VCCVID

ON

ON

4

Bring up

SST-Build

PT-Build

ST-Build

QT-Build

Pilot-Build

3

MCH Rev. ICH5 Rev.

RG828SDGES FW82801EB

RG828SDGP

A2(QE45)

A1(QE16ES)A1(QE18)

FW82801EB

A3(QE51ES)

2

1

S3

S5 S4/AC

S5 S4/AC don't exist

ON

ON

ON

OFF

OFF

OFF

OFF

OFFOFF

Configuration List

BOM Structure

TABLE

PCI

C C

PCI DEVICE

CARD BUS

LAN

MINI PCI

IDSEL

AD17

AD16

AD19

REQ#/GNT#

1

4

3

VGA

B B

USB

A A

TABLE

USB PORT#

0

1

2

3

4

5

6

7

DESTINATION

Reserved

BT

BACK

DOG

MOD

BACK

BACK

Reserved

Note : "@" means all model depop

"1@" means Nimitz depoped only

"2@" means Beijing depoped only

Model

Function

Smart Card

LAN

Dog House

PIRQ

D,C

C

D,B(NP)

A,B(NP)

Nimitz Beijing

No

10/100

(4401)

YES YES

YES

1000

(5705M)

Function

5

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVIS ION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE IN FORMATION IT CONT AINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL E LECTRON ICS, INC .

3

2

Size Doc ument Number Re v

Date: Sheet

Compal Electronics, Inc.

Index and Config.

LA-1711

1

360Wednesday, July 23, 2003

X02-D

of

Page 4

5

hexainf@hotmail.com

4

3

2

1

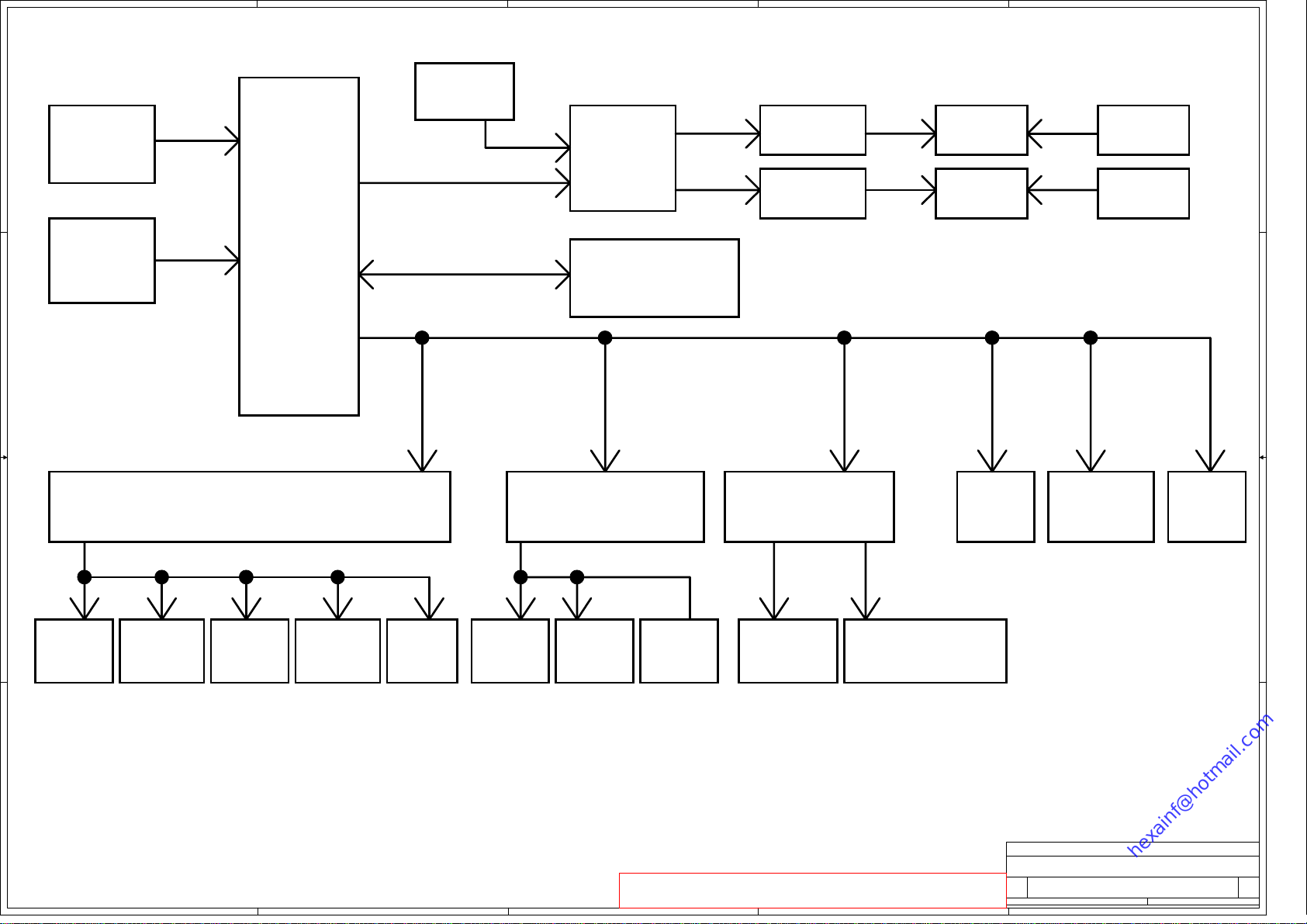

RBAT

D D

ADAPTER

+RTCSRC

+RTC_PWR

+5VALW

+5VSUS

PWR_SRC

+3VALW+3.3VRTC

BATTERY

+3VSUS

SUSPWROK

DOCK _PWR_SRC

C C

+5VSUS

B B

+3VSRC

+2.5VMEMP

+VCCP

+VCC_CORE

+12V

+5VHDD

A A

+5VMOD

5

+5VRUN

VDDA

4

+3VRUN +3VSUS+1.5VRUN

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVIS ION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE IN FORMATION IT CONT AINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL E LECTRON ICS, INC .

3

+2.5V_MEM

V_1P25V_DDR_VTTV3P3LAN

Title

Size Doc ument Number Re v

2

Date: Sheet

Compal Electronics, Inc.

Power Rail

LA-1711

1

460Wednesday, July 23, 2003

X02-D

of

Page 5

5

hexainf@hotmail.com

4

3

2

1

ICH_SMBCLK

D D

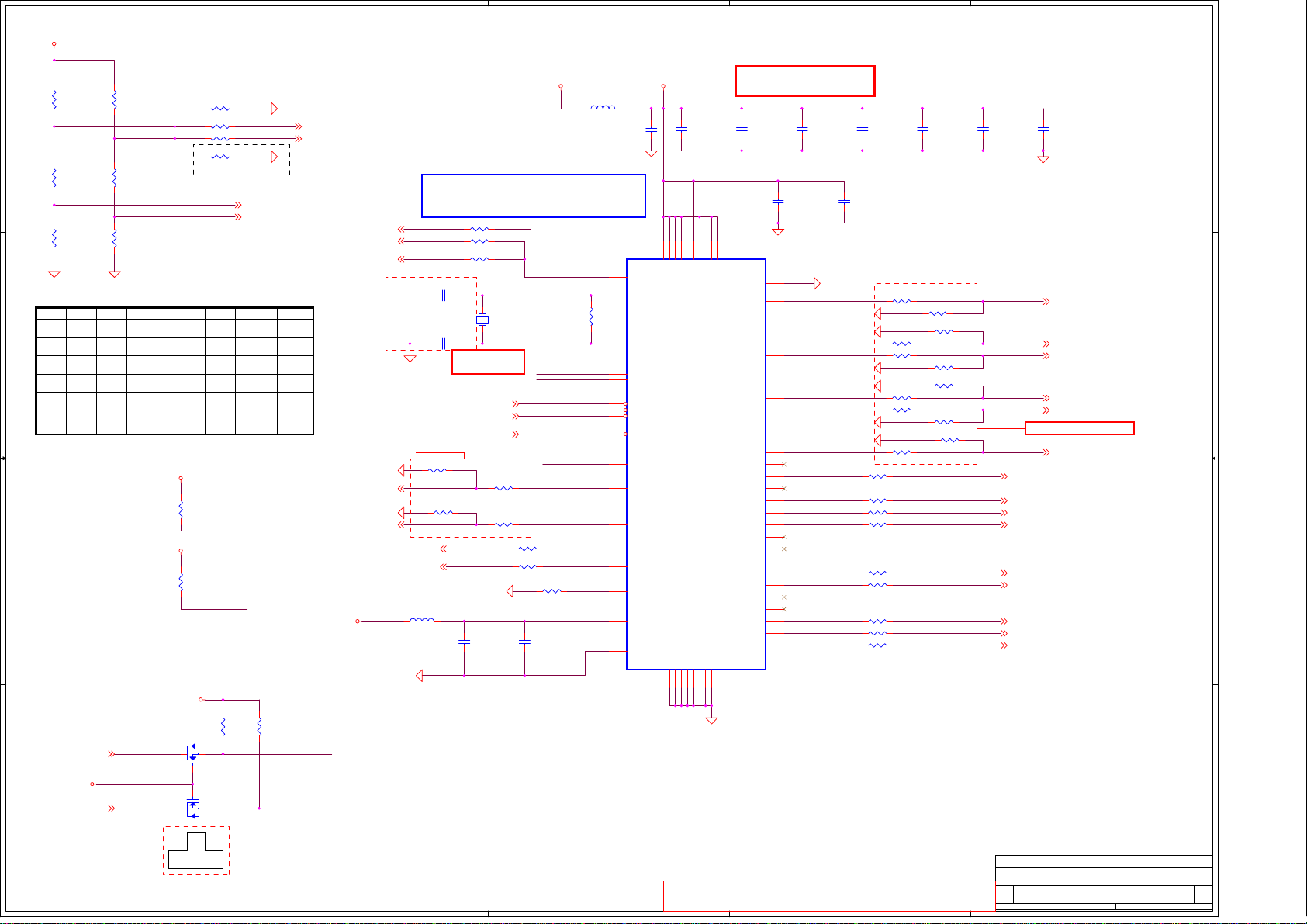

ICH5

ICH_SMBDATA

+3VSUS

7002

+3VRUN

CK_SCLK

CLK GEN.

CK_SDATA

7002

V_3P3_LAN

DIMM0

DIMM1

7002

7002

LAN_SMBCLK

NIC

LAN_SMBDATA

7002

CLK_SMB

+3VALW

7002

DAT_SMB

7002

C C

24C05

ADT7460

AD7414 PCA9561

DH PORT

SIO

Macallen

SBAT_SMBCLK

SBAT_SMBDAT

+5VALW

VGA

7002

MPCI

EC SMBus Address

CPU Temp.(ADT7460ARQ) : 5Ch/5Dh (P.19)

DDR Temp.(AD7414ART-0) : 90h/91h (P.15)

CPU Power Temp.(AD7414ART-0) : 92h/93h (P.?)

EC EEPROM(FM24C05U) : A0h/A1h/A2h/A3h (P.37)

VID Select(PCA9561PW) : 9Ch/9Dh (P.38)

B B

PBAT_SMBCLK

1'nd

PBAT_SMBDAT

+5VALW

BATTERY

CHARGER

A A

Compal Electronics, Inc.

SMBUS TOPOLOGY

LA-1711

1

560Wednesday, July 23, 2003

X02-D

of

5

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAIN S CONF IDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETE NT DIVIS ION OF R &D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE IN FORMATION IT CONT AINS

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL E LECTRON ICS, INC .

3

2

Size Doc ument Number Re v

Date: Sheet

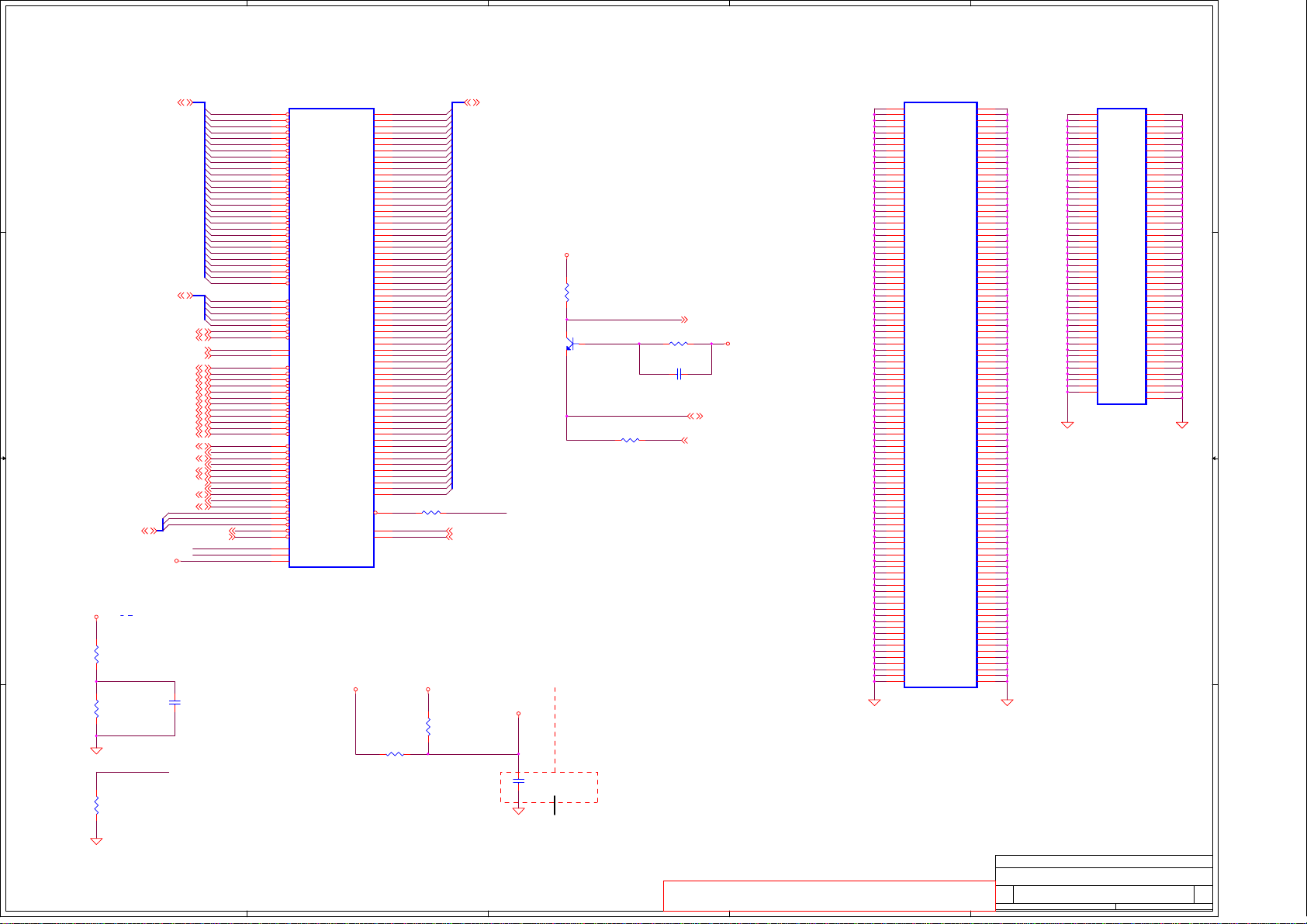

Page 6

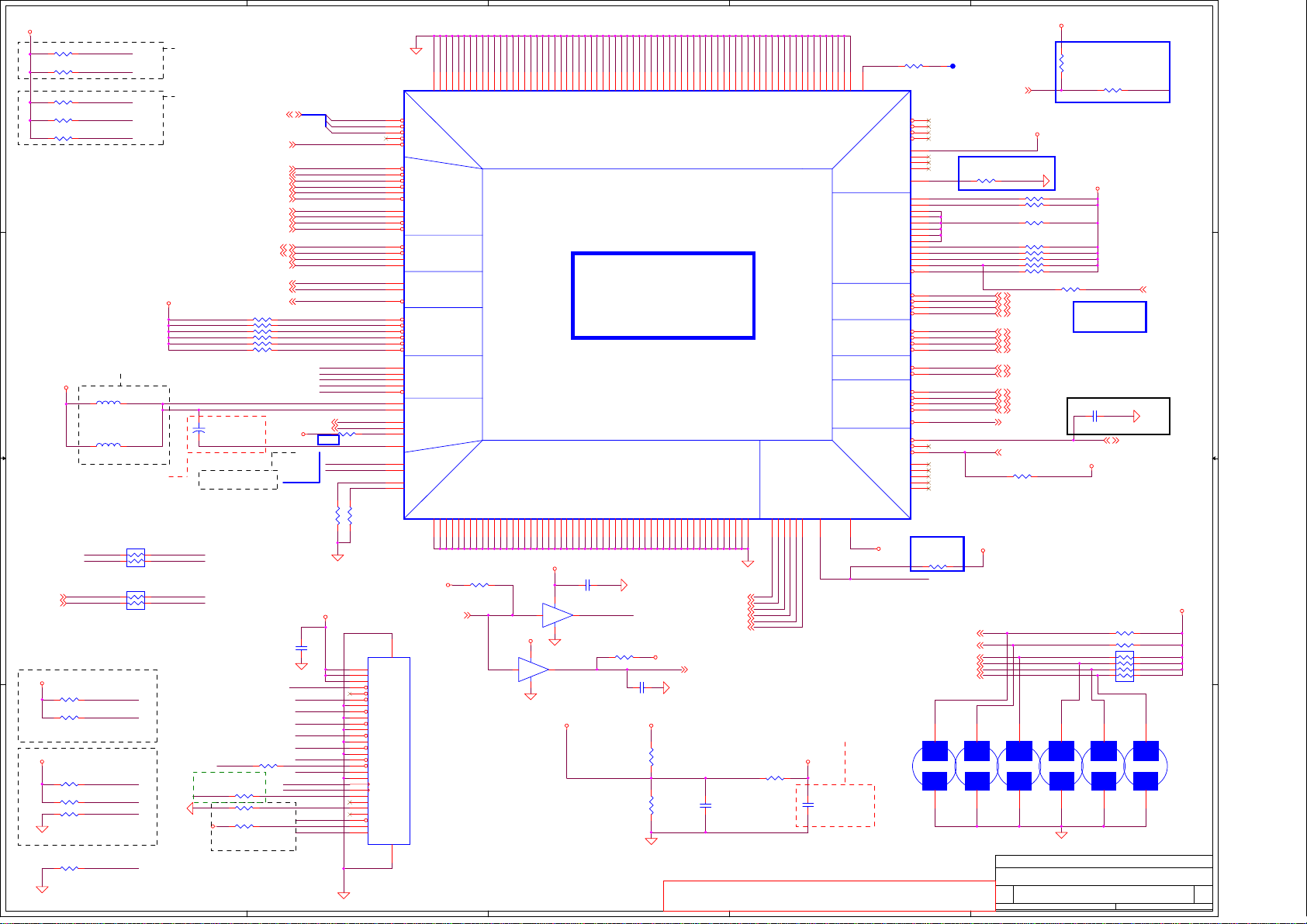

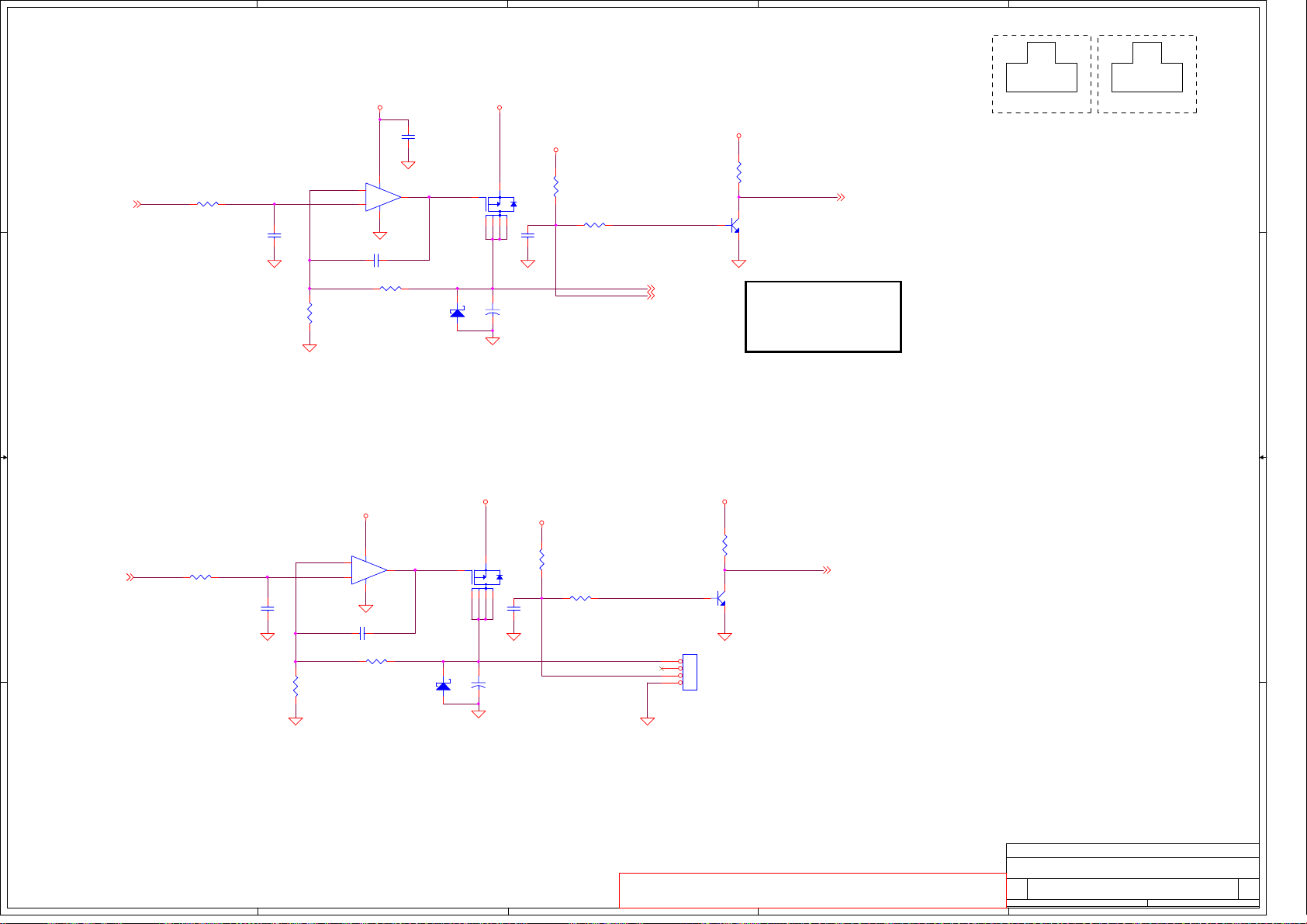

+3VRUN

5

4

3

2

1

Place near each pin

W>40 mil

1

C587

0.1U_0402_10V6K~D

2

36

42

48

VDD_48

VSS_CPU

VDD_SRC

VDD_CPU

VDD_CPU

CPUCLKT2

CPU_CLKC2

CPUCLKT1

CPUCLKC1

CPUCLKT0

CPUCLKC0

48/66MHZ_OUT/3V66_4

66MHZ_OUT3/3V66_3

66MHZ_OUT2/3V66_2

66MHZ_OUT1/3V66_1

66MHZ_OUT0/3V66_0

PCICLK_F2

PCICLK_F1

PCICLK_F0

PCICLK6

PCICLK5

PCICLK4

PCICLK3

PCICLK2

PCICLK1

PCICLK0

VSS_48

VSS_SRC

VSS_IREF

CY28409ZCT_TSSOP56~D

39

53

1

C553

2

45

47

46

44

43

41

40

29

27

26

23

22

9

8

7

20

19

18

15

14

13

12

1

C585

0.1U_0402_10V6K~D

2

0.1U_0402_10V6K~D

CK_CPU2

CK_CPU2#

CK_CPU1

CK_CPU1#

CK_CPU0H_STP_PCI#

CK_CPU0#

CLK66M_OU T3

CLK66M_OU T1

CLK66M_OU T0

PCICLK_F2

PCICLK6

PCICLK5

PCICLK2

PCICLK1

PCICLK0

1

C554

0.1U_0402_10V6K~D

2

1

C193

4.7U_0805_6.3V6K~D

2

1 2

1 2

1 2

1 2

1 2

1 2

R543

1 2

33_0402_5%~D

R547

1 2

33_0402_5%~D

R546

1 2

33_0402_5%~D

R540

1 2

33_0402_5%~D

R545

1 2

33_0402_5%~D

R542

1 2

33_0402_5%~D

R541

1 2

33_0402_5%~D

R544

1 2

33_0402_5%~D

1 2

R587 33_0402_5%~D

2

Trace wide=20 mils

1

C552

0.1U_0402_10V6K~D

2

R488

33_0402_5%~D

R472

1 2

49.9_ 0402_1%~D

R473

1 2

49.9_ 0402_1%~D

R489

33_0402_5%~D

R490

33_0402_5%~D

R474

1 2

49.9_ 0402_1%~D

R475

1 2

49.9_ 0402_1%~D

R491

33_0402_5%~D

R492

33_0402_5%~D

R476

1 2

49.9_ 0402_1%~D

R477

1 2

49.9_ 0402_1%~D

R493

33_0402_5%~D

1

C551

0.1U_0402_10V6K~D

2

CK_BCLK

CK_BCLK#

CK_ITP

CK_ITP#

CK_HCLK

1

C588

0.1U_0402_10V6K~D

2

CK_BCLK <7>

CK_BCLK# <7>

CK_I TP <8>

CK_ ITP# <8>

CK_HCLK <10>

Place near CK409

CK_HCLK#

Title

Size Document Number Re v

Date: Sheet

CK_ HCLK # <10>

CK_66M_AGP <18>

CK_66M_MCH <12>

CK_66M_ICH <20>

CK_33M_ICHPCI <20>

CK_33M_MINIPCI <32>

CK_33M_CBPCI <30>

CK_33M_LANPCI <28>

CK_33M_SIOPCI <34>

CK_33M_CPLD <36>

Compal Electronics, Inc.

LA-1711

Clock Generator

1

660Wednesday, July 23, 2003

X02-D

of

1

2

4

5

51

56

21

49

50

35

28

30

37

38

31

32

52

55

54

3

CK_VDD_MAIN+3VRUN

2

C204

U39

REF_1

REF_0

XTAL_IN

XTAL_OUT

SEL0

SEL1

PWRDWN#

PCI_STP#

CPU_STP#

VTT_PWRGD#

SCLK

SDATA

SRCLKN_100MHZ

SRCLKP_100MHZ

USB_48MHZ

DOT_48MHZ

IREF

VDD_PLL

VSS_PLL

1

C586

0.1U_0402_10V6K~D

1

2

24

16

34

3

VDD_PCI10VDD_PCI

VDD_REF

VDD_3V66

CK409

VSS_REF

VSS_PCI11VSS_PCI

VSS_3V66

6

17

25

33

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFI DENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETEN T DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZ ED BY CO MPAL ELE CTRON ICS, I NC. N EITHER THIS S HEET N OR THE I NFORM ATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOU T PRIO R WRIT TEN CO NSENT OF COMP AL ELEC TRONI CS, IN C.

+3VRUN

12

R518

1K_0603_1%~D

CLKSEL0

CLKSEL1

12

R519

2K_0603_1%~D

12

R208

2.49K _0603_1%~D

66 14.3 100/200 48

R215 0_0402_5%~D@

12

R206 0_0402_5%~D

12

R508 0_0402_5%~D

12

R509 0_0402_5%~D@

12

14.3

14.3

+3VRUN

12

R192

1K_0603_1%~ D

H_STP_PCI#

+3VRUN

12

R218

1K_0603_1%~ D@

ICH_SLP_S1#

+3VRUN

100K_0402_5%~D

D

1 3

2

2

1 3

D

D

1

G

14.3

12

R524

S

Q68

2N700 2_SOT23~D

G

G

Q69

2N7002_SOT23~ D

S

3

S2

66 14.3 100/2004848

ICH_ SMBDATA

MCH_CLKSEL0 <10>

MCH_CLKSEL1 <10>

REF

100/200

12

R536

100K_0402_5%~D

CPU_CLKSEL0 <8>

CPU_CLKSEL1 <8>

Bring Up: Populate R509 (Because CPU

is Nor thwood-MT, Frequency 533MHz)

Close to X'tal pin

48

Place near CK409

+3VRUN

CK_SDATA

CK_SCLKICH_SMBCLK

CK_14M_ICH<21>

CK_14M_SIO<34>

CK_14M_CODEC<24>

10P_04 02_50V8J~D@

10P_04 02_50V8J~D@

1 2

CK_100M_ICH#<21>

CK_100M_ICH<21>

Check SPEC (250mA,300 ohm)

49.9_ 0402_1%~D

1 2

CK_48M_ICH<20>

CK_48M_SCR<30>

L45

BLM11A601S_0603~D

1 2

L17

BLM21 PG600SN1D_0805~D

1 2

10U_1206_6.3V7K~D

CK_XTAL_IN and CK_XTAL_OUT equal length traces,

Please place R_J between Pins 4,5 of CK409 Pins

before X'tal

R538

33_0402_5%~D

33_0402_5%~D

33_0402_5%~D@

C597

C598

R479

R478

49.9_0402_1%~D

12

R539

12

R611

12

12

12

X6

14.31 818MHz_20P_1BX14318CC1A~D

12

Place crystal within

500 mils of CK409

ICH_SLP_S1#<21>

CLK_STP_CPU#<36>

CK_VTT_PG#<37>

1 2

33_0402_5%~D

1 2

33_0402_5%~D

33_0402_5%~D

33_0402_5%~D

CLK_VDD_PLL

1

C166

10U_1206_6.3V7K~D

2

R485

R484

CLKREF1

CLKREF0

CK_XTAL_IN

2M_0603_5%~D @

CK_XTAL_OUT

ICH_SLP_S1#

CLK_STP_CPU#

CK_VTT_PG#

R501

12

R500

12

R199

1 2

475_0603_1%~D

1

C550

0.1U_0402_16V4Z~D

2

R548

CLKSEL0

CLKSEL1

CK_SCLK

CK_SDATA

CK_SATA#

CK_SATA

CLK48M_OU T0

CLK48M_OU T1

12

R_J

12

R529

D D

1K_0603_1%~D

12

R530

2K_0603_1%~D

12

R214

2.49K _0603_1%~D

SL0 SL1 CPU 3V66[0..3] REF0 REF1 SRC USB/Dot

0 0 100 66 14.3 14.3 100/200

C C

0 MID REF REF REF REF REF

0 1 200

1 0 133 66 14.3

1 1 166

1 MID Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z Hi-Z

B B

ICH_SMBDATA<15,16,21,32>

A A

ICH_SMBCLK<15,16,21,32>

2N7002

5

4

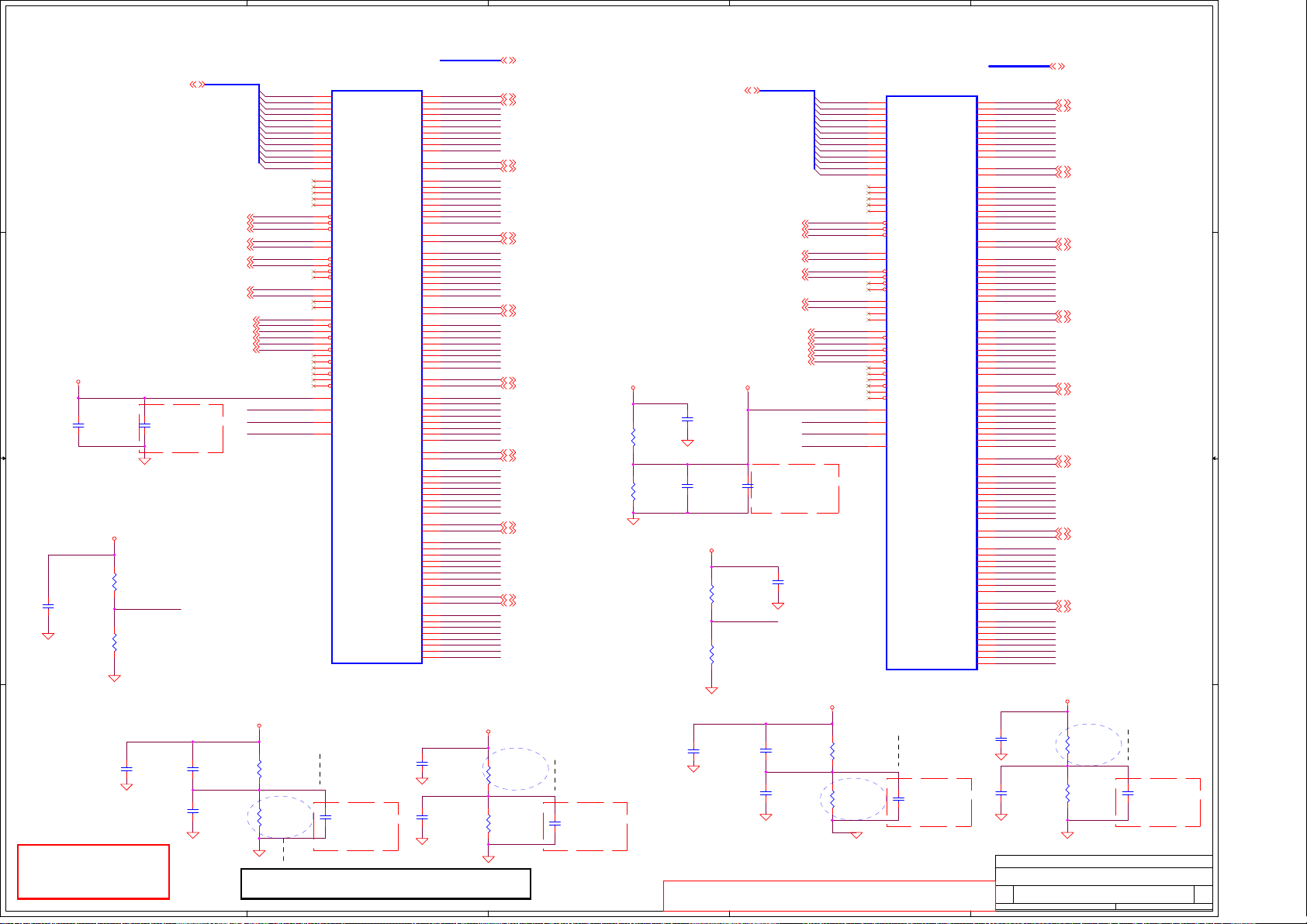

Page 7

5

4

+VCC_CORE

3

2

1

D D

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

C C

H_REQ#[0..4]<10>

H_ADS#<10>

R339

62_0402_5%@

+VCC_CORE

+VCC_CORE

B B

R371

1 2

1 2

H_BR0#< 10>

H_BPRI#<10>

H_BNR#<10>

H_LOCK#<10>

CK_BCLK<6>

CK_BCLK#<6>

H_HIT#<10>

H_HITM#<10>

H_DEFER#<10>

200_0402_5%

CK_BCLK#

CK_BCLK

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_IERR#

AMP_3 -1565030-1_Prescott~D

AF22

AF23

A10

A12

A14

A16

A18

A20

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

D9

VCC_65C8VCC_66

VCC_84

VCC_85

F9

F11

VCC_67

VCC_68

VCC_79E8VCC_80

E20

VCC_69

VCC_78

E18

VCC_70

VCC_77

E16

E10

VCC_71D7VCC_72

VCC_75

VCC_76

E12

E14

VCC_73

VCC_74

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

H_D#0

B21

D#0

H_D#1

B22

D#1

H_D#2

A23

D#2

H_D#3

A25

D#3

H_D#4

C21

D#4

H_D#5

D22

D#5

H_D#6

B24

D#6

H_D#7

C23

D#7

H_D#8

C24

D#8

H_D#9

B25

D#9

H_D#10

G22

H_D#11

H21

H_D#12

C26

H_D#13

D23

H_D#14

J21

H_D#15

D25

H_D#16

H22

H_D#17

E24

H_D#18

G23

H_D#19

F23

H_D#20

F24

H_D#21

E25

H_D#22

F26

H_D#23

D26

H_D#24

L21

H_D#25

G26

H_D#26

H24

H_D#27

M21

H_D#28

L22

H_D#29

J24

H_D#30

K23

H_D#31

H25

H_D#32

M23

H_D#33

N22

H_D#34

P21

H_D#35

M24

H_D#36

N23

H_D#37

M26

H_D#38

N26

H_D#39

N25

H_D#40

R21

H_D#41

P24

H_D#42

R25

H_D#43

R24

H_D#44

T26

H_D#45

T25

H_D#46

T22

H_D#47

T23

H_D#48

U26

H_D#49

U24

H_D#50

U23

H_D#51

V25

H_D#52

U21

H_D#53

V22

H_D#54

V24

H_D#55

W26

H_D#56

Y26

H_D#57

W25

H_D#58

Y23

H_D#59

Y24

H_D#60

Y21

H_D#61

AA25

H_D#62

AA22

H_D#63

AA24

H_D#[ 0..63] <10>H_A#[3..31]<10>

JCPUA

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6A8VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56B7VCC_57B9VCC_58

VCC_59

VCC_61

VCC_62

VCC_63

K2

A#3

K4

A#4

L6

A#5

K1

A#6

L3

A#7

M6

A#8

L2

A#9

M3

A#10

M4

A#11

N1

A#12

M1

A#13

N2

A#14

N4

A#15

N5

A#16

T1

A#17

R2

A#18

P3

A#19

P4

A#20

R3

A#21

T2

A#22

U1

A#23

P6

A#24

U3

A#25

T4

A#26

V2

A#27

R6

A#28

W1

A#29

T5

A#30

U4

A#31

V3

A#32

W2

A#33

Y1

A#34

AB1

A#35

J1

REQ#0

K5

REQ#1

J4

REQ#2

J3

REQ#3

H3

REQ#4

G1

ADS#

AC1

AP#0

V5

AP#1

AA3

BINIT#

AC3

IERR#

H6

BR0#

D2

BPRI#

G2

BNR#

G4

LOCK#

BCLK0

BCLK1

F3

HIT#

E3

HITM#

E2

DEFER#

VSS_0H1VSS_1H4VSS_2

VSS_3

VSS_4

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12A3VSS_13A9VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

A11

A13

A15

A17

A19

A21

A24

H23

H26

A26

AA1

AA4

AA11

AA13

AA15

AA17

AA19

AA23

AA26

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

AA7

AA9

AB10

AB12

AB14

AB16

Prescott

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

AB3

AB6

AB8

AB18

AB20

AB21

AB24

AC11

AC13

AC15

AC17

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

AC2

AC5

AC7

AC9

AC19

AC22

AC25

AD10

AD12

AD14

AD16

AD18

AD21

AD23

VCC_64

BOOTSELECT

VSS_54

VSS_55

VCC_81

VCC_82

VCC_83

F13

F15

F17

F19

AD1

AD4

AD8

+VCC_CORE

Reference Intel document

Desktop P4 Spec.: 10988 P4 0.13u 512KB L2 EMTS Rev.2.0

Desktop Prescott Spec.: 11910 Prescott EMTS Rev.0.5

Pin number Northwood

Pin name

A6 TESTHI11 G HIPull-up 200ohm

TESTHI11

B6 FERR# FERR#/PBE# Pull-up 62ohm

AA20 ITPCLKOUT0 Pull-up56ohm

AB22 ITPCLKOUT1 Pull-up 56ohm

AD2 NC VIDPWRGD Pull-up 2.43K ohm

AD3 NC float VID5 Pull-up1Kohm to

A A

AF3 NC float VCCVIDLB Connect to +VCCVID

AD20 VCCA VCCIOPLLConnect to CPU

VCCIOPLL VCCA

AF23 Connect to CPU

TESTHI12 TESTHI12AD25 DPSLP

Comment Comment

to +VCC_CORE

Pull-up 62ohm

to +VCC_CORE

to +VCC_CORE

to +VCC_CORE

float

Filter

Filter

Pull-up 200ohm

to +VCC_CORE

5

Prescott

Pin name

Pull-up 62ohm

to +VCC_CORE

to +VCC_CORE

TESTHI6 Pull-up 62ohm

TESTHI7 Pull-up 62ohm

to +VCC_CORE

to +VCC_CORE

to +VCCVID

+3VRUN & connect

to PWRIC

Connect to CPU

Filter

Connect to CPU

Filter

COMPAT#

float

Pull-up 62ohm

to +VCC_CORE

Northwood MT

Pin name

FERR#

ITPCLKOUT0

ITPCLKOUT1

NC

NC

NC

VCCA

VCCIOPLL

VSSAE26 VSS Connect to GND OPTIMIZED/

Comment

Connect to PLD

CPUPREF through

0ohm

Pull-up 62ohm

to +VCC_CORE

Pull-up56ohm

to +VCC_CORE

Pull-up 56ohm

to +VCC_CORE

float

float

float

Connect to CPU

Filter

Connect to CPU

Filter

Connect to GND

Connect to PLD

through 0ohm

4

Northwood

Prescott

Northwood

MT

PopPop Pop

Pop

Pop

Pop

Depop

Depop

Pop Pop

Pop

Pop

Pop

PopDepop

Pop

Pop

DepopPop

Pop

Pop

Pop

Pop

Depop

Depop

Depop

Pop

Note: AD2,AD3 pop(bring up)

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFI DENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETEN T DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZ ED BY CO MPAL ELE CTRON ICS, I NC. N EITHER THIS S HEET N OR THE I NFORM ATION IT CON TAINS

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOU T PRIO R WRIT TEN CO NSENT OF COMP AL ELEC TRONI CS, IN C.

VCORE_BOOTSELECT <49>

2

Compal Electronics, Inc.

Title

Prescott Processor in uFCPGA478

Size Document Number Re v

C

LA-1711

Date: Sheet

1

of

760Wednesday, July 23, 2003

X02-D

Page 8

5

+VCC_CORE

+VCC_CORE

CK_ITP_CPU

14

CK_ITP_CPU#

23

CK_ITP_JITP#

14

CK_ITP_JITP

23

Place near ICH

Place near CPU

1

+

2

ITP_TDO

+VCC_CORE

H_RS#[0..2]<10>

H_TRDY#<10>

H_A20M#<21>

H_FERR#<21>

H_IGNNE#<21>

H_PWR GOOD<21>

H_STPCLK#<36>

H_RESET#<10>

H_DBSY#<10>

H_DRDY#<10>

CPU_CLKSEL0<6>

CPU_CLKSEL1<6>

H_THERMDA<19>

H_THERMDC<19>

H_THERMTRIP#<21,37>

R338 62_0402_5%

1 2

R341 62_0402_5%

1 2

R337 62_0402_5%

1 2

R346 62_0402_5%

1 2

R343 62_0402_5%

1 2

R342 62_0402_5%

1 2

C368

33U_D2_8M_R35~D

Pop: Prescott

Depop: Northwood

0.1U_ 0402_10V6K~D

R361

150_0402_5%~D

H_RESET#

1 2

R364

47_0402_5%~D

1 2

1 2

R370 2 7.4_0603_1%~D

1 2

R376

39.2_ 0603_1%~D

Close to the ITP

H_SMI#<21>

H_INTR<21>

H_NMI<21>

H_INIT#<21>

H_VCCA

+VCCVID

H_VSSA

C386

VCCSENSE<46>

VSSSENSE<46>

R333

R_D

R97

61.9_ 0603_1%

+VCC_CORE

1

2

ITP_DBRESET#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

CK_ITP_JITP

CK_ITP_JITP#

ITP_TCK

ITP_TRST#

ITP_TMS

ITP_TDI

R131 62_0402_5%

R129 62_0402_5%

D D

R84 62_0402_5%@

C C

B B

+VCC_CORE

H_FERR#

1 2

H_THERMTRIP#

1 2

R111 130_0402_5%

H_PROCHOT#

1 2

R87 300_0402_5%~D

H_P WRGOOD

1 2

H_RESET#

1 2

10uH, DC current of 100mA parts

and close to cap

+VCC_CORE

L40 10U_LQH31M N100K01_100mA_10%_1206~D

1 2

1 2

L41 10U_LQH31M N100K01_100mA_10%_1206~D

PLL Layout note :

1.Place cap within 600 mils of

the VCCA and VSSA pins.

2.H_VCCIOPLL,HVCCA,HVSSA trace wide

12 mils(min)

CK_ITP

CK_ITP#

0_4P2R_0404_5%~D

CK_ITP#

CK_ITP#<6>

CK_ITP

CK_ITP<6>

54.9_ 0603_1%~D

1 2

54.9_ 0603_1%~D

1 2

R363

R358

0_4P2R_0404_5%~D @

ITP_TDO

H_RESET#

RN9

RN8

Close to the ITP

+VCC_CORE

R377

47_0402_5%~D@

R108 150_0402_5%~D

A A

1 2

R379 47_0402_5%~D @

ITP_TMS

12

ITP_TDI

ITP_TCK

12

Close to the CPU

R381

680_0402_5%~D

1 2

Between the CPU and ITP

ITP_TRST#

5

4

H_RS#0

H_RS#1

H_RS#2

H_FERR#

H_P WRGOOD

H_RESET#

H_THERMDA

H_THERMDC

H_THERMTRIP#

ITP_BPM#0

ITP_BPM#1

ITP_BPM#2

ITP_BPM#3

ITP_BPM#4

ITP_BPM#5

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

1 2

0_0402_5%~D

CK_ITP_CPU

CK_ITP_CPU#

12

12

R349

61.9_ 0603_1%

AMP_3 -1565030-1_Prescott~D

JITP

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

4

VTT1

VTT0

VTAP

DBR#

DBA#

BPM0#

GND5

BPM1#

GND4

BPM2#

GND3

BPM3#

GND2

BPM4#

GND1

BPM5#

RESET#

FBO

GND0

BCLKP

BCLKN

TDO

NC2

TCK

NC1

TRST#

TMS

TDI

AB23

AB25

AD20

AE23

AD22

AC26

AD26

G5

AB2

C6

D1

W5

H5

H2

AD6

AD5

C4

AC6

AB5

AC4

AA5

AB4

D4

C1

D5

AF3

L24

29

30

F1

F4

J6

B6

B2

B5

Y4

E5

B3

A2

Y6

F7

E6

A5

A4

P1

GND6

GND7

MOLEX_52435-2891_28P~D@

JCPUB

RS#0

RS#1

RS#2

RSP#

TRDY#

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

LINT0

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

TCK

TDI

TDO

TMS

TRST#

VCCIOPLL

VCCA

VCCSENSE

VSSSENSE

VCCVIDLB

VSSA

ITP_CLK0

ITP_CLK1

COMP0

COMP1

+3VSUS

AE11

AE13

AE15

AE17

AE19

AE22

AE24

VSS_57

VSS_58

VSS_59

VSS_60

VSS_61

VSS_62

VSS_129F8VSS_130

VSS_131

VSS_132G3VSS_133G6VSS_134J2VSS_135

J22

G21

G24

R152

1 2

10K_0402_5%~ D

VID_PWRGD<46>

Level shift

+CPU_GMCH_GTLREF trace

wide 12mils(min),Space

15mils

3

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

C11

C13

C15

C17

C19

C22

C25

D10

D12

D14

D16

D18

D20

D21

D24

E11

E13

E15

E17

E19

E23

E26

F10

VSS_63

VSS_65

VSS_66

VSS_67

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85B4VSS_86B8VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92C2VSS_93

VSS_94

VSS_95C5VSS_96C7VSS_97C9VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106D3VSS_107D6VSS_108D8VSS_109E1VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117E4VSS_118E7VSS_119E9VSS_120

Prescott

VID0

VID1

VID2

VID3

VSS_136

VSS_137J5VSS_138

VSS_139

VSS_140K3VSS_141K6VSS_142L1VSS_143

VSS_144

VSS_145L4VSS_146M2VSS_147

VSS_148

VSS_149M5VSS_150

VSS_151

VSS_152N3VSS_153N6VSS_154P2VSS_155

VSS_156

VSS_157P5VSS_158R1VSS_159

VSS_160

VSS_161R4VSS_162

VSS_163

VSS_164T3VSS_165T6VSS_166U2VSS_167

VSS_168

VSS_169U5VSS_170V1VSS_171

VSS_172

VSS_173V4VSS_174

VSS_175

VSS_176W3VSS_177W6VSS_178Y2VSS_179

VSS_180

VSS_181

J25

L23

L26

K21

K24

3

N21

N24

M22

M25

+3VSUS

1 2

5

U6A

P

1

O6I

G

SN74LVC2G07DBVR_SOT23-6~D

2

+3VSUS

5

U6B

P

O4I

G

SN74LVC2G07DBVR_SOT23-6~D

2

+CPU_GMCH_GTLREF

C131

0.1U_0402_16V4Z~D

H_VID_PWRGD

T21

P22

P25

R23

R26

R155 10K_ 0402_5%~D

1 2

1 2

+VCC_CORE

R_A

R_B

3

T24

C121

0.1U_0402_16V4Z~D

V23

V26

U22

U25

+3VSUS

VCORE_ENLL <46>

12

R357

200_0603_1%~D

12

R356

169_0603_1%

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFI DENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETEN T DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZ ED BY CO MPAL ELE CTRON ICS, I NC. N EITHER THIS S HEET N OR THE I NFORM ATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOU T PRIO R WRIT TEN CO NSENT OF COMP AL ELEC TRONI CS, IN C.

Y5

Y22

Y25

W21

W24

H_VID0<36>

H_VID1<36>

H_VID2<36>

H_VID3<36>

H_VID4<36>

H_VID5<36>

GTL Reference Voltage

Layout note :

2

C369

0.1U_0402_16V4Z~D

1

VID4

AE5

AE4

AE3

AE2

AE1

AD3

1. +CPU_GTLREF Trace wide

12mils(min),Space 1 5mils

2. Place R_A and R_B near CPU.

3. Place decoupling cap 220PF near CPU.

+CPU_GTLREF

12

R340

0_0603_5%~D

F12

F14

F16

F18

VSS_121

VSS_122

VSS_123

VIDPWRGD

VID5

AD2

1

C372

220P_0402_50V7K

2

2

F22

F25

F5

VSS_124

VSS_125F2VSS_126

VSS_127

OPTIMIZED/COMPAT#

AF4

2

AF26

VSS_128

SKTOCC#

VCCVID

1 2

0_0402_5%~D

DP#0

DP#1

DP#2

DP#3

GTLREF0

GTLREF1

GTLREF2

GTLREF3

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI6

TESTHI7

TESTHI8

TESTHI9

TESTHI10

TESTHI11

TESTHI12

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

PROCHOT#

MCERR#

SLP#

NC1

NC2

NC3

NC4

NC5

+VCCVID

H_VID_PWRGD

R71

J26

K25

K26

L25

AA21

AA6

F20

F6

AE26

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

AD25

E22

K22

R22

W22

F21

J23

P23

W23

L5

R5

E21

G25

P26

V21

AE25

C3

V6

AB26

A22

A7

AF25

AF24

AE21

R_E

R336

681_0603_1%

1 2

@

T1

PAD@

R70 0_0402_5%~D

1 2

H_TESTHI0

H_TESTHI1

H_TEST HI2_7

H_TESTHI8

H_TESTHI9

H_TESTHI10

H_TESTHI11

H_DPSLP#

H_TESTHI12

ITP_DBRESET#

H_PROCHOT#

RE

Pop: Prescott

Depop: Northwood

+VCCVID

VID5<36,46>

VID4<36,46>

VID3<36,46>

VID2<36,46>

VID1<36,46>

VID0<36,46>

B_VID5

OPEN

2

2

1

1

@

1

+VCC_CORE

12

DPSLP#<36>

+CPU_GTLREF

Pop: Northwood

R_G

R77 62_0402_5%

R344 62_ 0402_5%

R82 62_0402_5%

R354 62_ 0402_5%

R350 62_ 0402_5%

R347 62_ 0402_5%

R382 62_ 0402_5%

R79 62_0402_5%

H_DSTBN#0 <10>

H_DSTBN#1 <10>

H_DSTBN#2 <10>

H_DSTBN#3 <10>

H_DSTBP#0 <10>

H_DSTBP#1 <10>

H_DSTBP#2 <10>

H_DSTBP#3 <10>

H_ADSTB#0 <10>

H_ADSTB#1 <10>

H_ DIN V#0 <10>

H_ DIN V#1 <10>

H_ DIN V#2 <10>

H_ DIN V#3 <10>

ITP_D BRESET# <37>

H_CPUSLP# <36>

R83 62_0402_5%@

1 2

B_VID4

OPEN

2

2

1

1

@

Title

Size Document Number Re v

C

Date: Sheet

Depop: Prescott

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

R_H

R380 0_0402_5%~D@

1 2

VID5

VID4

VID3

VID2

VID1

VID0

B_VID3

B_VID2

OPEN

2

1

OPEN

2

2

2

1

1

1

@

Compal Electronics, Inc.

Prescott Processor in uFCPGA478

LA-1711

CPLD Enable

Pop R76, R78

R76

200_0402_5%@

R78 0_0402_5%~D@

1 2

+VCC_CORE

RH

Pop: Prescott

Depop: Northwood MT

CPLD Enable

Pop R380

Closely Pin AE25

C660

12

1000P_0402_50V7K~D@

+VCC_CORE

R37 1K_04 02_5%~D

1 2

R35 1K_04 02_5%~D

1 2

RN7 1K_8P4R_1206_5%~D

B_VID1

OPEN

2

2

1

1

@

1

H_DPSLP#

CP UPR EF# <36>

H_PROCHOT# <10>

45

36

27

18

B_VID0

OPEN

2

2

1

1

@

860Wednesday, July 23, 2003

+3VRUN

X02-D

of

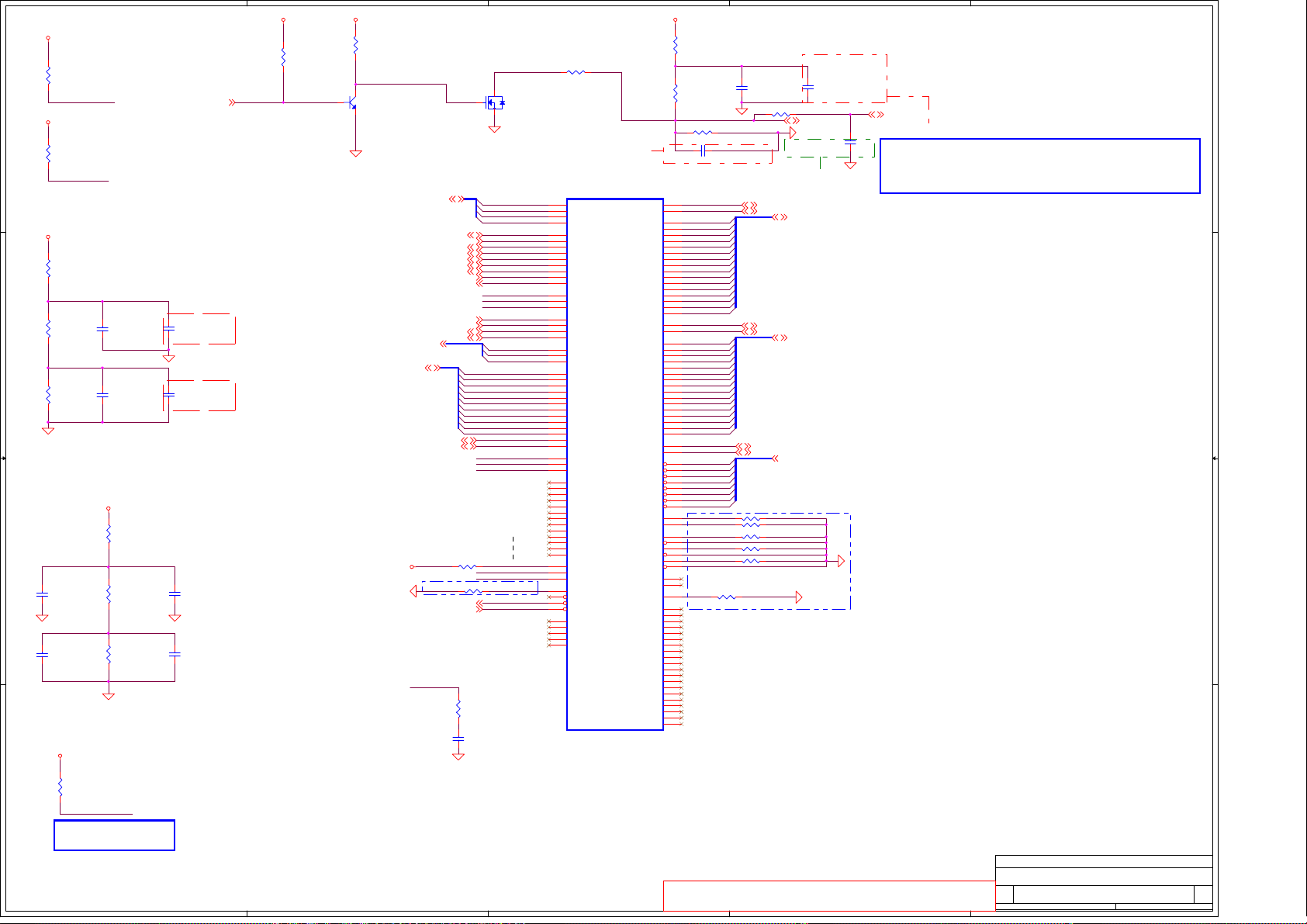

Page 9

5

4

3

2

1

+VCC_CORE

1

C31

22U_1 206_6.3VAM~D

2

D D

+VCC_CORE

1

C46

22U_1 206_6.3VAM~D

2

+VCC_CORE

1

C381

22U_1 206_6.3VAM~D

2

C C

+VCC_CORE

1

C76

22U_1 206_6.3VAM~D

@

2

1

C27

22U_1 206_6.3VAM~D

@

2

1

C56

22U_1 206_6.3VAM~D

2

1

C411

22U_1 206_6.3VAM~D

2

1

C71

22U_1 206_6.3VAM~D

@

2

1

C28

22U_1 206_6.3VAM~D

2

1

C55

22U_1 206_6.3VAM~D

2

1

C72

22U_1 206_6.3VAM~D

@

2

Place 11 North of Socket(Stuff 6)

1

C29

22U_1 206_6.3VAM~D

2

1

C32

22U_1 206_6.3VAM~D @

2

1

2

Place 12 Inside Socket(Stuff all)

1

C45

22U_1 206_6.3VAM~D

2

1

C394

22U_1 206_6.3VAM~D

2

1

2

Place 9 South of Socket(Unstuff all)

1

C75

22U_1 206_6.3VAM~D

@

2

1

C69

22U_1 206_6.3VAM~D

@

2

1

@

2

C30

22U_1 206_6.3VAM~D

C403

22U_1 206_6.3VAM~D

C70

22U_1 206_6.3VAM~D

1

C77

22U_1 206_6.3VAM~D

@

2

1

C404

22U_1 206_6.3VAM~D

2

1

C73

22U_1 206_6.3VAM~D

@

2

1

C331

22U_1 206_6.3VAM~D

@

2

22uF depop reference

Springdale Chipset Platform Design Guide Rev1.11(12474)

1

C412

22U_1 206_6.3VAM~D

2

1

C74

22U_1 206_6.3VAM~D

@

2

1

C395

22U_1 206_6.3VAM~D

2

1

C382

22U_1 206_6.3VAM~D

2

Note:For PT-phase

22uF depop reference

Springdale Chipset Platform Design Guide Rev1.2(12837)

Inside the socket cavity 12 pcs (all stuffed)

North side 12pcs (4 sites stuffed)

Delete south side

B B

+VCC_CORE

5

1

+

C302

470U_D4_2.5V_R10M~D

2

1

+

C294

470U_D4_2.5V_R10M~D

2

1

+

C423

470U_D4_2.5V_R10M~D

@

2

1

+

C303

470U_D4_2.5V_R10M~D

2

+VCC_CORE

1

+

C299

470U_D4_2.5V_R10M~D

@

2

+VCC_CORE

A A

1

+

C68

470U_D4_2.5V_R10M~D

2

470uF _ERS10m ohm* 15, ESR=0.5m ohm

1

+

C304

470U_D4_2.5V_R10M~D

2

1

+

C298

470U_D4_2.5V_R10M~D

2

1

+

C422

470U_D4_2.5V_R10M~D

2

1

+

C301

470U_D4_2.5V_R10M~D

@

2

1

+

C296

470U_D4_2.5V_R10M~D

@

2

4

1

+

C300

470U_D4_2.5V_R10M~D

2

1

+

C295

470U_D4_2.5V_R10M~D

2

1

+

C305

470U_D4_2.5V_R10M~D

2

1

+

C297

470U_D4_2.5V_R10M~D

@

2

Decoupling Reference Document:

Springdale Chipset Platform Design guide Rev1.11

(12474)page239

Decoupling Reference Requirement:

560uF Polymer, ESR:5m ohm(each) * 10

22uF X5R * 32

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFI DENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETEN T DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZ ED BY CO MPAL ELE CTRON ICS, I NC. N EITHER THIS S HEET N OR THE I NFORM ATION IT CON TAINS

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOU T PRIO R WRIT TEN CO NSENT OF COMP AL ELEC TRONI CS, IN C.

Compal Electronics, Inc.

Title

CPU Decoupling

Size Document Number Re v

C

LA-1711

2

Date: Sheet

1

960Wednesday, July 23, 2003

X02-D

of

Page 10

5

4

3

2

1

H_A#[3..31]<7>

D D

H_REQ#[0..4]<7>

H_ADSTB#0<8>

C C

H_RS#[0..2]<8> MCH_CLKSEL0 <6>

B B

+VTT_GMCH

12

R331

301_0402_1%~D

12

R332

102_0402_1%~D

HDRCOMP

12

A A

R335

20_0603_1%~D

H_ADSTB#1<8>

CK_HCLK<6>

CK_HCLK#<6>

H_DSTBP#0<8>

H_DSTBN#0<8>

H_DINV#0<8>

H_DSTBP#1<8>

H_DSTBN#1<8>

H_DINV#1<8>

H_DSTBP#2<8>

H_DSTBN#2<8>

H_DINV#2<8>

H_DSTBP#3<8>

H_DSTBN#3<8>

H_DINV#3<8>

H_ADS#<7>

H_TRDY#<8>

H_DRDY#<8>

H_DEFER#<7>

H_HITM#<7>

H_HIT#<7>

H_LOCK#<7>

H_BR0#<7>

H_BNR#<7>

H_BPRI#<7>

H_DBSY#<8>

+GMCH_GTLREF

Follow Intel design guide R1.11(12474) page80

Trace width 12mils,Space

10mils

HD_SWING

1

C365

0.01U _0402_16V7K~D

2

Trace width 10mils,Space

7mils

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_RESET#<8>

PWRGD_3V<21,37>

HDRCOMP

HD_SWING

U3A

D26

HA3#

D30

HA4#

L23

HA5#

E29

HA6#

B32

HA7#

K23

HA8#

C30

HA9#

C31

HA10#

J25

HA11#

B31

HA12#

E30

HA13#

B33

HA14#

J24

HA15#

F25

HA16#

D34

HA17#

C32

HA18#

F28

HA19#

C34

HA20#

J27

HA21#

G27

HA22#

F29

HA23#

E28

HA24#

H27

HA25#

K24

HA26#

E32

HA27#

F31

HA28#

G30

HA29#

J26

HA30#

G26

HA31#

B29

HREQ0#

J23

HREQ1#

L22

HREQ2#

C29

HREQ3#

J21

HREQ4#

B30

HADSTB0#

D28

HADSTB1#

B7

HCLKP

C7

HCLKN

B19

HDSTBP0#

C19

HDSTBN0#

C17

DINV0#

L19

HDSTBP1#

K19

HDSTBN1#

L17

DINV1#

G9

HDSTBP2#

F9

HDSTBN2#

L14

DINV2#

D12

HDSTBP3#

E12

HDSTBN3#

C15

DINV3#

F27

ADS#

D24

HTRDY#

G24

DRDY#

L21

DEFER#

E23

HITM#

K21

HIT#

E25

HLOCK#

B24

BREQ0#

B28

BNR#

B26

BPRI#

E27

DBSY#

G22

RS0#

C27

RS1#

B27

RS2#

E8

CPURST#

AE14

PWROK#

E24

HDRCOMP

C25

HDSWING

F23

HDVREF

RG828SDGES_FCBGA932_SPRINGDALE~D

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

FSB

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

PROCHOT#

BSEL0

BSEL1

+CPU_GMCH_GTLREF

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

B23

E22

B21

D20

B22

D22

B20

C21

E18

E20

B16

D16

B18

B17

E16

D18

G20

F17

E19

F19

J17

L18

G16

G18

F21

F15

E15

E21

J19

G14

E17

K17

J15

L16

J13

F13

F11

E13

K15

G12

G10

L15

E11

K13

J11

H10

G8

E9

B13

E14

B14

B12

B15

D14

C13

B11

D10

C11

E10

B10

C9

B9

D8

B8

L20

L13

L12

R329

0_0603_5%~D

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

1 2

0_0402_5%~D

+VTT_GMCH

12

R608

12

R323

200_0603_1%~D

H_D#[0..63] <7>

+3VRUN

12

Q24

MMBT3904_SOT23~D

3 1

Settig CPU Output

H_PROCHOT#

MCH_CLKSEL1 <6>

GTL Reference Voltage

Layout note :

1. +GMCH_GTLREF Trace wide

12mils(min),Space 1 5mils.

2. Place decoupling cap 220PF near GMCH.

+GMCH_GTLREF

1

C366

220P_0402_50V7K

2

Create

R90

1.24K _0402_1%~D

2

H_PROCHOT#

R605

1 2

0_0402_5%~D@

H_PROCHOT_SIO# <34>

R91 10K_0402_5%~ D

1 2

C670

12

100P_0402_50V8J~D

H_PROCHOT# <8>

VCORE_PHOT# <34,46>

+VCC_CORE

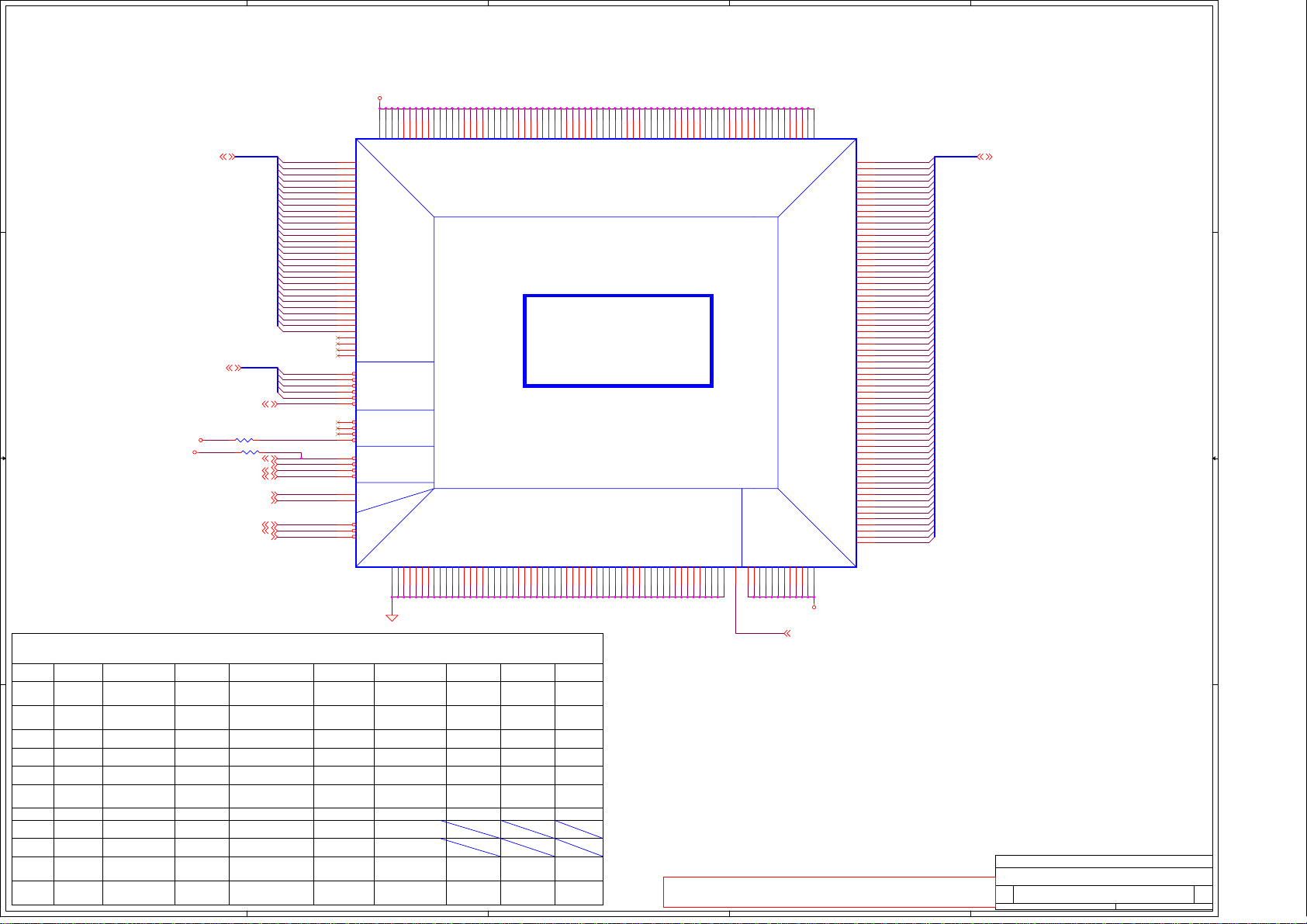

U3F

AR32

VSS

AR29

VSS

AR27

VSS

AR25

VSS

AR23

VSS

AR20

VSS

AR16

VSS

AR13

VSS

AR11

VSS

AR9

VSS

AN32

VSS

AN30

VSS

AN28

VSS

AN26

VSS

AN24

VSS

AN22

VSS

AN20

VSS

AN18

VSS

AN16

VSS

AN14

VSS

AN12

VSS

AN10

VSS

AM35

VSS

AM29

VSS

AM27

VSS

AM25

VSS

AM23

VSS

AM21

VSS

AM19

VSS

AM17

VSS

AM15

VSS

AM13

VSS

AM11

VSS

AM9

VSS

AL32

VSS

AL1

VSS

AK28

VSS

AK26

VSS

AK24

VSS

AK22

VSS

AK20

VSS

AK18

VSS

AK16

VSS

AK14

VSS

AK12

VSS

AK10

VSS

AK8

VSS

AK3

VSS

AJ35

VSS

AJ32

VSS

AJ9

VSS

AJ4

VSS

AJ1

VSS

AH33

VSS

AH30

VSS

AH24

VSS

AH22

VSS

AH20

VSS

AH18

VSS

AH16

VSS

AH14

VSS

AH12

VSS

AH10

VSS

AH6

VSS

AH3

VSS

AG35

VSS

AG32

VSS

AG28

VSS

AG26

VSS

AG24

VSS

AG22

VSS

AG20

VSS

AG18

VSS

AG16

VSS

AG14

VSS

AG8

VSS

AG4

VSS

AF33

VSS

AF30

VSS

AF25

VSS

AF24

VSS

AF22

VSS

AF20

VSS

AF18

VSS

AF16

VSS

AF14

VSS

AF11

VSS

AF9

VSS

AF6

VSS

AF3

VSS

AE35

VSS

AE32

VSS

AE26

VSS

AE25

VSS

AE13

VSS

AE12

VSS

RG828SDGES_FCBGA932_SPRINGDALE~D

AE11

VSS

AE10

VSS

AE4

VSS

AE1

VSS

AD33

VSS

AD30

VSS

AD28

VSS

AD10

VSS

AD9

VSS

AD8

VSS

AD6

VSS

AD3

VSS

AC35

VSS

AC32

VSS

AC4

VSS

AC1

VSS

AB33

VSS

AB30

VSS

AB28

VSS

AB27

VSS

AB26

VSS

AB10

VSS

AB9

VSS

AB8

VSS

AB6

VSS

AB3

VSS

AA32

VSS

AA4

VSS

AA1

VSS

Y35

VSS

Y33

VSS

Y30

VSS

Y28

VSS

Y27

VSS

Y26

VSS

Y10

VSS

Y9

VSS

Y8

VSS

Y6

VSS

Y3

VSS

W32

VSS

W18

VSS

W17

VSS

W4

VSS

V33

GND

VSS

V30

VSS

V28

VSS

V27

VSS

V26

VSS

V19

VSS

V17

VSS

V10

VSS

V9

VSS

V8

VSS

V6

VSS

V3

VSS

U32

VSS

U19

VSS

U18

VSS

U4

VSS

T35

VSS

T33

VSS

T30

VSS

T28

VSS

T27

VSS

T26

VSS

T10

VSS

T9

VSS

T8

VSS

T6

VSS

T3

VSS

T1

VSS

R32

VSS

R4

VSS

R1

VSS

P33

VSS

P30

VSS

P28

VSS

P27

VSS

P26

VSS

P9

VSS

P8

VSS

P6

VSS

P3

VSS

N35

VSS

N32

VSS

N4

VSS

N1

VSS

M33

VSS

M30

VSS

M28

VSS

M27

VSS

M26

VSS

M6

VSS

M3

VSS

L35

VSS

U3G

L31

VSS

L26

VSS

L25

VSS

L24

VSS

K33

VSS

K29

VSS

K27

VSS

K25

VSS

K22

VSS

K20

VSS

K18

VSS

K16

VSS

K14

VSS

K12

VSS

K11

VSS

J35

VSS

J32

VSS

J28

VSS

J22

VSS

J20

VSS

J18

VSS

J16

VSS

J14

VSS

J12

VSS

J10

VSS

H33

VSS

H30

VSS

H26

VSS

H24

VSS

H22

VSS

H20

VSS

H18

VSS

H16

VSS

H14

VSS

H12

VSS

H9

VSS

H8

VSS

H5

VSS

H2

VSS

G35

VSS

G31

VSS

G28

VSS

F26

VSS

F24

VSS

F22

VSS

F20

VSS

F18

VSS

RG828SDGES_FCBGA932_SPRINGDALE~D

F16

VSS

F14

VSS

F12

VSS

F10

VSS

F8

VSS

F5

VSS

F3

VSS

F1

VSS

E3

VSS

E1

VSS

D35

VSS

D33

VSS

D31

VSS

D29

VSS

D27

VSS

D25

VSS

D23

VSS

D21

VSS

D19

VSS

D17

VSS

D15

VSS

D13

VSS

D11

VSS

D9

VSS

D1

VSS

C28

GND

VSS

C26

VSS

C24

VSS

C22

VSS

C20

VSS

C18

VSS

C16

VSS

C14

VSS

C12

VSS

C10

VSS

C8

VSS

C4

VSS

A32

VSS

A29

VSS

A27

VSS

A25

VSS

A23

VSS

A20

VSS

A16

VSS

A13

VSS

A11

VSS

A9

VSS

A7

VSS

Compal Electronics, Inc.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFI DENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETEN T DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZ ED BY CO MPAL ELE CTRON ICS, I NC. N EITHER THIS S HEET N OR THE I NFORM ATION IT CON TAINS

5

4

3

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOU T PRIO R WRIT TEN CO NSENT OF COMP AL ELEC TRONI CS, IN C.

2

Springdale-Host/GND

Size Document Number Re v

C

LA-1711

Date: Sheet

1

of

10 60Thurs day, July 24, 2003

X02-D

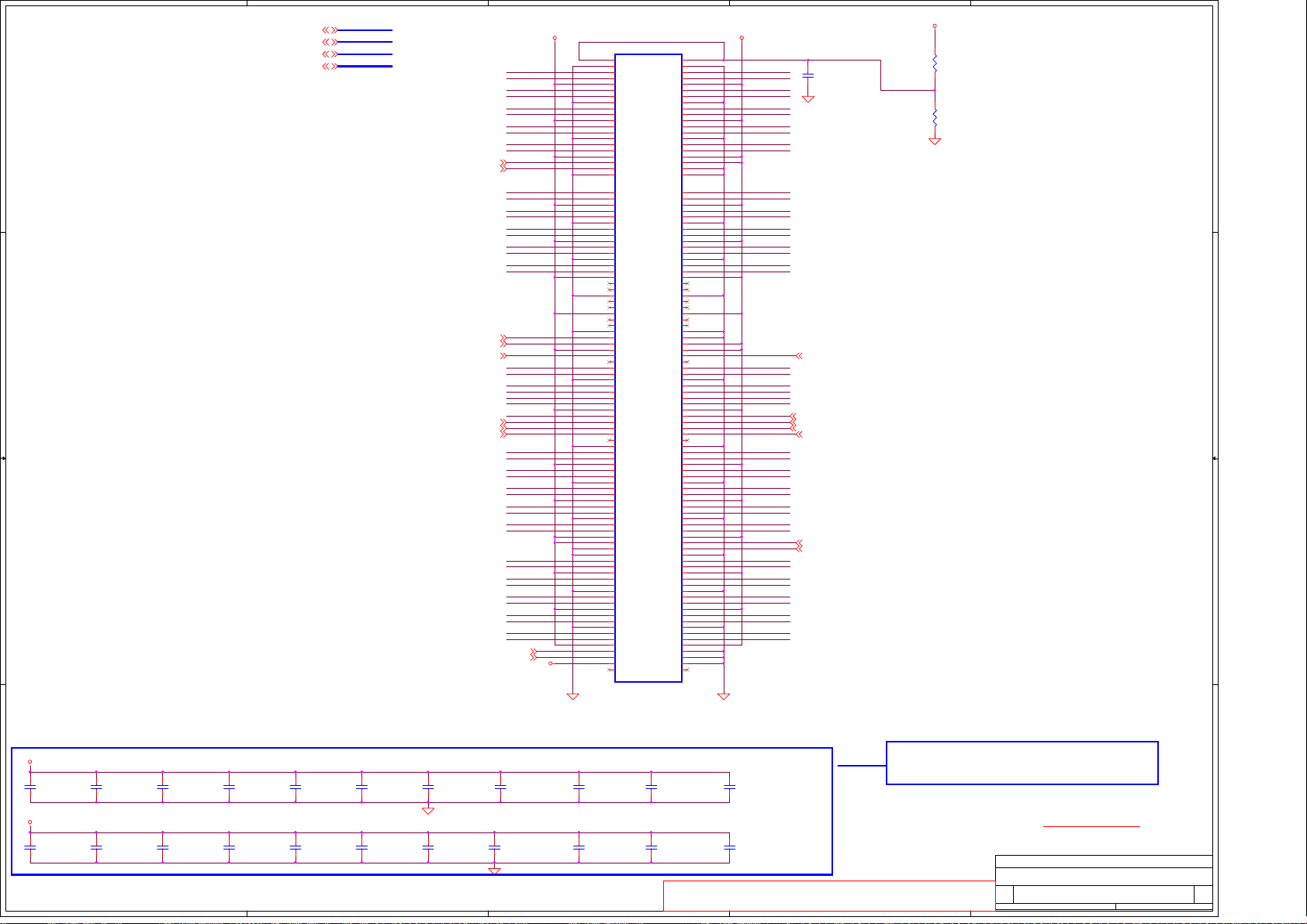

Page 11

5

4

3

2

1

DDRA_SDQ[0..63]

DDRA_SMA[0..12]<15,17>

D D

C C

SM_VREF_A

SM_VREF_A trace width of 12mils and space

12mils(min)

2

C48

2.2U_0805_16VFZ~D

1

2

C47

0.1U_0402_16V4Z~D

1

Close to GMCH

+2.5V_MEM

Trace width of 12mils and space

10mils(min)

B B

2

C64

2.2U_0805_16VFZ~D

1

A A

Follow Intel design guide

R1.11(12474) page124,125

12

R372

42.2_ 0603_1%~D

SMXRCOMP

12

R367

42.2_ 0603_1%~D

2

C65

2.2U_0805_16VFZ~D

1

5

DDRA_SMA[0..12]

DDRA_SWE#<15,17>

DDRA_SCAS#<15,17>

DDRA_SRAS#<15,17>

DDRA_SBS0<15,17>

DDRA_SBS1<15,17>

DDRA_SCS#0<15,17>

DDRA_SCS#1<15,17>

DDRA_CKE0<15, 17>

DDRA_CKE1<15, 17>

DDRA_CLK0<15>

DDRA_CLK0#<15>

DDRA_CLK1<15>

DDRA_CLK1#<15>

DDRA_CLK2<15>

DDRA_CLK2#<15>

1

C637

0.01U _0402_16V7K~D

2

1

C406

1U_0603_6.3V6M~D

2

DDRA_SMA0

DDRA_SMA1

DDRA_SMA2

DDRA_SMA3

DDRA_SMA4

DDRA_SMA5

DDRA_SMA6

DDRA_SMA7

DDRA_SMA8

DDRA_SMA9

DDRA_SMA10

DDRA_SMA11

DDRA_SMA12

DDRA_SCS#0

DDRA_SCS#1

DDRA_CKE0

DDRA_CKE1

SMXRCOMP

SMXRCOMPVOH

SMXRCOMPVOL

+2.5V_MEM

Trace width of 12mils and space

10mils(min)

12

R374

10K_0603_1%~ D

SMXRCOMPVOH

12

R369

30.9K _0603_1%~D

*

U3B

AJ34

SMAA_A0

AL33

SMAA_A1

AK29

SMAA_A2

AN31

SMAA_A3

AL30

SMAA_A4

AL26

SMAA_A5

AL28

SMAA_A6

AN25

SMAA_A7

AP26

SMAA_A8

AP24

SMAA_A9

AJ33

SMAA_A10

AN23

SMAA_A11

AN21

SMAA_A12

AL34

SMAB_A1

AM34

SMAB_A2

AP32

SMAB_A3

AP31

SMAB_A4

AM26

SMAB_A5

AB34

SWE_A#

Y34

SCAS_A#

AC33

SRAS_A#

AE33

SBA_A0

AH34

SBA_A1

AA34

SCS_A0#

Y31

SCS_A1#

Y32

SCS_A2#

W34

SCS_A3#

AL20

SCKE_A0

AN19

SCKE_A1

AM20

SCKE_A2

AP20

SCKE_A3

AK32

SCMDCLK_A0

AK31

SCMDCLK_A0#

AP17

SCMDCLK_A1

AN17

SCMDCLK_A1#

N33

SCMDCLK_A2

N34

SCMDCLK_A2#

AK33

SCMDCLK_A3

AK34

SCMDCLK_A3#

AM16

SCMDCLK_A4

AL16

SCMDCLK_A4#

P31

SCMDCLK_A5

P32

SCMDCLK_A5#

E34

SMVREF_A

AK9

SMXRCOMP

AN9

SMXRCOMPVOH

AL9

SMXRCOMPVOL

RG828SDGES_FCBGA932_SPRINGDALE~D

1

C400

0.01U _0402_16V7K~D

2

SDQS_A0

SDQS_A1

SDQ_A10

SDQ_A11

SDQ_A12

SDQ_A13

SDQ_A14

SDQ_A15

SDQS_A2

SDQ_A16

SDQ_A17

SDQ_A18

SDQ_A19

SDQ_A20

SDQ_A21

DDR Channel A

SDQ_A22

SDQ_A23

SDQS_A3

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_A31

SDQS_A4

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_A35

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_A39

SDQS_A5

SDQ_A40

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_A47

SDQS_A6

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_A54

SDQ_A55

SDQS_A7

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_A63

SDM_A0

SDQ_A0

SDQ_A1

SDQ_A2

SDQ_A3

SDQ_A4

SDQ_A5

SDQ_A6

SDQ_A7

SDM_A1

SDQ_A8

SDQ_A9

SDM_A2

SDM_A3

SDM_A4

SDM_A5

SDM_A6

SDM_A7

AN11

AP12

AP10

AP11

AM12

AN13

AM10

AL10

AL12

AP13

AP15

AP16

AP14

AM14

AL18

AP19

AL14

AN15

AP18

AM18

AP23

AM24

AP22

AM22

AL24

AN27

AP21

AL22

AP25

AP27

AM30

AP30

AP28

AP29

AP33

AM33

AM28

AN29

AM31

AN34

AF34

AF31

AH32

AG34

AF32

AD32

AH31

AG33

AE34

AD34

V34

W33

AC34

AB31

V32

V31

AD31

AB32

U34

U33

M32

M34

T34

T32

K34

K32

T31

P34

L34

L33

H31

H32

J33

H34

E33

F33

K31

J34

G34

F34

2

C63

2.2U_0805_16VFZ~D

1

1

C407

1U_0603_6.3V6M~D

2

DDRA_SDQ0

DDRA_SDQ1

DDRA_SDQ2

DDRA_SDQ3

DDRA_SDQ4

DDRA_SDQ5

DDRA_SDQ6

DDRA_SDQ7

DDRA_SDQ8

DDRA_SDQ9

DDRA_SDQ10

DDRA_SDQ11

DDRA_SDQ12

DDRA_SDQ13

DDRA_SDQ14

DDRA_SDQ15

DDRA_SDQ16

DDRA_SDQ17

DDRA_SDQ18

DDRA_SDQ19

DDRA_SDQ20

DDRA_SDQ21

DDRA_SDQ22

DDRA_SDQ23

DDRA_SDQ24

DDRA_SDQ25

DDRA_SDQ26

DDRA_SDQ27

DDRA_SDQ28

DDRA_SDQ29

DDRA_SDQ30

DDRA_SDQ31

DDRA_SDQ32

DDRA_SDQ33

DDRA_SDQ34

DDRA_SDQ35

DDRA_SDQ36

DDRA_SDQ37

DDRA_SDQ38

DDRA_SDQ39

DDRA_SDQ40

DDRA_SDQ41

DDRA_SDQ42

DDRA_SDQ43

DDRA_SDQ44

DDRA_SDQ45

DDRA_SDQ46

DDRA_SDQ47

DDRA_SDQ48

DDRA_SDQ49

DDRA_SDQ50

DDRA_SDQ51

DDRA_SDQ52

DDRA_SDQ53

DDRA_SDQ54

DDRA_SDQ55

DDRA_SDQ56

DDRA_SDQ57

DDRA_SDQ58

DDRA_SDQ59

DDRA_SDQ60

DDRA_SDQ61

DDRA_SDQ62

DDRA_SDQ63

Close to GMCH <1" Close to GMCH <1"

Note: Intel recommend is 31.12K,the value isn't popularize.

Follow Dell's DT team use 30.9K

4

DDRA_SDQ[0..63] <15,17>

DD RA_SDQS 0 <15,17>

DDRA_SDM0 <15,17>

DD RA_SDQS 1 <15,17>

DDRA_SDM1 <15,17>

DD RA_SDQS 2 <15,17>

DDRA_SDM2 <15,17>

DD RA_SDQS 3 <15,17>

DDRA_SDM3 <15,17>

DD RA_SDQS 4 <15,17>

DDRA_SDM4 <15,17>

DD RA_SDQS 5 <15,17>

DDRA_SDM5 <15,17>

DD RA_SDQS 6 <15,17>

DDRA_SDM6 <15,17>

DD RA_SDQS 7 <15,17>

DDRA_SDM7 <15,17>

+2.5V_MEM

Trace width of 12mils and space

10mils(min)

12

R373

30.9K _0603_1%~D

*

SMXRCOMPVOL

12

R368

10K_0603_1%~ D

1

C401

0.01U _0402_16V7K~D

2

3

+2.5V_MEM

12

12

R104

150_0603_1%~D

R100

150_0603_1%~D

DDRB_SMA[0..12]<16,17>

2

C62

2.2U_0805_16VFZ~D

1

2

C52

2.2U_0805_16VFZ~D

1

DDRB_SMA[0..12]

DDRB_SWE#< 16,17>

DDRB_SCAS#<16,17>

DDRB_SRAS#<16,17>

DDRB_SBS0<16,17>

DDRB_SBS1<16,17>

DDRB_SCS#0<16,17>

DDRB_SCS#1<16,17>

DDRB_CKE0<16, 17>

DDRB_CKE1<16, 17>

DDRB_CLK0<16>

DDRB_CLK0#<16>

DDRB_CLK1<16>

DDRB_CLK1#<16>

DDRB_CLK2<16>

DDRB_CLK2#<16>

SM_VREF_B

SM_VREF_B trace width of

12mils and space

12mils(min)

2

C50

0.1U_0402_16V4Z~D

1

DDRB_SMA0

DDRB_SMA1

DDRB_SMA2

DDRB_SMA3

DDRB_SMA4

DDRB_SMA5

DDRB_SMA6

DDRB_SMA7

DDRB_SMA8

DDRB_SMA9

DDRB_SMA10

DDRB_SMA11

DDRB_SMA12

DDRB_SCS#0

DDRB_SCS#1

DDRB_CKE0

DDRB_CKE1

SMYRCOMP

SMYRCOMPVOH

SMYRCOMPVOL

AG31

AJ31

AD27

AE24

AK27

AG25

AL25

AF21

AL23

AJ22

AF29

AL21

AJ20

AE27

AD26

AL29

AL27

AE23

AA25

AK19

AF19

AG19

AE18

AG29

AG30

AF17

AG17

AJ30

AH29

AK15

AL15

AA33

W27

W31

W26

Y25

U26

T29

V25

W25

N27

N26

N31

N30

AP9

R34

R33

U3C

SMAA_B0

SMAA_B1

SMAA_B2

SMAA_B3

SMAA_B4

SMAA_B5

SMAA_B6

SMAA_B7

SMAA_B8

SMAA_B9

SMAA_B10

SMAA_B11

SMAA_B12

SMAB_B1

SMAB_B2

SMAB_B3

SMAB_B4

SMAB_B5

SWE_B#

SCAS_B#

SRAS_B#

SBA_B0

SBA_B1

SCS_B0#

SCS_B1#

SCS_B2#

SCS_B3#

SCKE_B0

SCKE_B1

SCKE_B2

SCKE_B3

SCMDCLK_B0

SCMDCLK_B0#

SCMDCLK_B1

SCMDCLK_B1#

SCMDCLK_B2

SCMDCLK_B2#

SCMDCLK_B3

SCMDCLK_B3#

SCMDCLK_B4

SCMDCLK_B4#

SCMDCLK_B5

SCMDCLK_B5#

SMVREF_B

SMYRCOMP

SMYRCOMPVOH

SMYRCOMPVOL

Close to GMCH

+2.5V_MEM

2

C66

2.2U_0805_16VFZ~D

1

Trace width of 12mils

and space 10mils(min)

+2.5V_MEM

1

C636

0.01U _0402_16V7K~D

2

1

C57

1U_06 03_6.3V6M~D

2

RG828SDGES_FCBGA932_SPRINGDALE~D

Trace width of 12mils and space

10mils(min)

12

R102

10K_0603_1%~ D

SMYRCOMPVOH

12

R101

30.9K _0603_1%~D

*

1

C54

0.01U _0402_16V7K~D

2

2

C53

2.2U_0805_16VFZ~D

1

12

R110

42.2_ 0603_1%~D

SMYRCOMP

12

R109

42.2_ 0603_1%~D

Close to GMCH <1" Close to GMCH <1"

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, I NC. AND CONTAINS CONFI DENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FR OM THE CUSTODY OF THE COMPETEN T DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZ ED BY CO MPAL ELE CTRON ICS, I NC. N EITHER THIS S HEET N OR THE I NFORM ATION IT CON TAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY W ITHOU T PRIO R WRIT TEN CO NSENT OF COMP AL ELEC TRONI CS, IN C.

2

DDRB_SDQ[0..63]

AF15

SDQS_B0

AG11

SDM_B0

SDQ_B0

SDQ_B1

SDQ_B2

SDQ_B3

SDQ_B4

SDQ_B5

SDQ_B6

SDQ_B7

SDQS_B1

SDM_B1

SDQ_B8

SDQ_B9

SDQ_B10

SDQ_B11

SDQ_B12

SDQ_B13

SDQ_B14

SDQ_B15

SDQS_B2

SDM_B2

SDQ_B16

SDQ_B17

SDQ_B18

SDQ_B19

SDQ_B20

DDR Channel B

SDQ_B21

SDQ_B22

SDQ_B23

SDQS_B3

SDM_B3

SDQ_B24

SDQ_B25

SDQ_B26

SDQ_B27

SDQ_B28

SDQ_B29

SDQ_B30

SDQ_B31

SDQS_B4

SDM_B4

SDQ_B32

SDQ_B33

SDQ_B34

SDQ_B35

SDQ_B36

SDQ_B37

SDQ_B38

SDQ_B39

SDQS_B5

SDM_B5

SDQ_B40

SDQ_B41

SDQ_B42

SDQ_B43

SDQ_B44

SDQ_B45

SDQ_B46

SDQ_B47

SDQS_B6

SDM_B6

SDQ_B48

SDQ_B49

SDQ_B50

SDQ_B51

SDQ_B52

SDQ_B53

SDQ_B54

SDQ_B55

SDQS_B7

SDM_B7

SDQ_B56

SDQ_B57

SDQ_B58

SDQ_B59

SDQ_B60

SDQ_B61

SDQ_B62

SDQ_B63

DDRB_SDQ0

AJ10

DDRB_SDQ1

AE15

DDRB_SDQ2

AL11

DDRB_SDQ3

AE16

DDRB_SDQ4

AL8

DDRB_SDQ5

AF12

DDRB_SDQ6

AK11

DDRB_SDQ7

AG12

AG13

AG15

DDRB_SDQ8

AE17

DDRB_SDQ9

AL13

DDRB_SDQ10

AK17

DDRB_SDQ11

AL17

DDRB_SDQ12

AK13

DDRB_SDQ13

AJ14

DDRB_SDQ14

AJ16

DDRB_SDQ15

AJ18

AG21

AE21

DDRB_SDQ16

AE19

DDRB_SDQ17

AE20

DDRB_SDQ18

AG23

DDRB_SDQ19

AK23

DDRB_SDQ20

AL19

DDRB_SDQ21

AK21

DDRB_SDQ22

AJ24

DDRB_SDQ23

AE22

AH27

AJ28

DDRB_SDQ24

AK25

DDRB_SDQ25

AH26

DDRB_SDQ26

AG27

DDRB_SDQ27

AF27

DDRB_SDQ28

AJ26

DDRB_SDQ29

AJ27

DDRB_SDQ30

AD25

DDRB_SDQ31

AF28

AD29

AC31

DDRB_SDQ32

AE30

DDRB_SDQ33

AC27

DDRB_SDQ34

AC30

DDRB_SDQ35

Y29

DDRB_SDQ36

AE31

DDRB_SDQ37

AB29

DDRB_SDQ38

AA26

DDRB_SDQ39

AA27

U30

U31

DDRB_SDQ40

AA30

DDRB_SDQ41

W30

DDRB_SDQ42

U27

DDRB_SDQ43

T25

DDRB_SDQ44

AA31

DDRB_SDQ45

V29

DDRB_SDQ46

U25

DDRB_SDQ47

R27

L27

M29

DDRB_SDQ48

P29

DDRB_SDQ49

R30

DDRB_SDQ50

K28

DDRB_SDQ51

L30

DDRB_SDQ52

R31

DDRB_SDQ53

R26

DDRB_SDQ54

P25

DDRB_SDQ55

L32

J30

J31

DDRB_SDQ56

K30

DDRB_SDQ57

H29

DDRB_SDQ58

F32

DDRB_SDQ59

G33

DDRB_SDQ60

N25

DDRB_SDQ61

M25

DDRB_SDQ62

J29

DDRB_SDQ63

G32

2

C59

2.2U_0805_16VFZ~D

1

1

C61

1U_06 03_6.3V6M~D

2

Compal Electronics, Inc.

Title

Springdale-DDR Interface

Size Document Number Re v

C

Date: Sheet

LA-1711

DDRB_SDQ[0..63] <16,17>

DDR B_SDQS0 <16,17>

DDRB_SDM0 <16,17>

DDR B_SDQS1 <16,17>

DDRB_SDM1 <16,17>

DDR B_SDQS2 <16,17>

DDRB_SDM2 <16,17>

DDR B_SDQS3 <16,17>

DDRB_SDM3 <16,17>

DDR B_SDQS4 <16,17>

DDRB_SDM4 <16,17>

DDR B_SDQS5 <16,17>

DDRB_SDM5 <16,17>

DDR B_SDQS6 <16,17>

DDRB_SDM6 <16,17>

DDR B_SDQS7 <16,17>

DDRB_SDM7 <16,17>

+2.5V_MEM

Trace width of 12mils and space

10mils(min)

12

R106

30.9K _0603_1%~D

*

SMYRCOMPVOL

12

R105

10K_0603_1%~ D

1

C58

0.01U _0402_16V7K~D

2

1

11 60Wednesday, July 23, 2003

X02-D

of

Page 12

5

+1.5VRUN

12

R64

43.2_ 0603_1%~D

GRCOMP

+1.5VRUN

D D

12

R328

52.3_ 0603_1%~D

HI_RCOMP_MCH

+1.5VRUN

12

R330

226_0603_1%~D

HI_SWIN G_MCH

12

R68

C C

B B

147_0603_1%~D

12

R69

113_0603_1%

2

C43

0.1U_0402_16V4Z~D

1

2

C360

0.1U_0402_16V4Z~D

1

+1.5VRUN

HI_VREF_MCH

Note:

HI_SWING_MCH, trace width of

12mils and space 10mils

2

C355

0.1U_0402_16V4Z~D

1

2

C41

0.1U_0402_16V4Z~D

1

Note:

HI_VREF_MCH trace width of

10mils and space 7mils

+1.5VRUN

12

R74

226_0603_1%~D

CI_SWING_GMCH

12

R75

147_0603_1%~D

CI_VREF_GMCH

12

R334

113_0603_1%

AGP8X_DET_GC<18>

1

C364

0.01U _0402_16V7K~D

2

Close to GMCH ball <250mils

1

C42

0.01U _0402_16V7K~D

2

Close to GMCH ball <250mils

Note:

CI_SWING_MCH, CI_VREF_MCH

trace width of 12mils and

space 20mils

0.8V

1

C44

0.01U _0402_16V7K~D

2

0.35V

1

C363

0.01U _0402_16V7K~D

2

+1.5VRUN

12

R45

8.2K_ 0402_5%~D

+12V

2

4

12

R48

8.2K_ 0402_5%~D

Q10

MMBT3904_SOT23~D

3 1

HUB_HL[0..10]<20>

+1.5VRUN

G_C/BE#[0..3]<18>

G_PIPE#_DBI_HI<18>

G_ST[0..2]<18>

HUB_HLSTRF<20>

HUB_HLSTRS<20>

CK_66M_MCH

G_FRAME#<18>

CK_66M_MCH<6>

G_DEVSEL#<18>

G_IRDY#<18>

G_TRDY#<18>

G_STOP#<18>

G_PAR<18>

G_REQ#<18>

G_GNT#<18>

G_RBF#< 18>

G_WBF#<18>

G_DBI_LO<18>

Trace 10mils, space 7mils

52.3_ 0603_1%~D

R81

1 2

R40

ICH_SYNC#<21>

PCI_PCIRST#<20, 36>

12

1

@

2

3

R55

1 2

39.2_ 0603_1%~D

2

G

GC_DET_REF

13

D

Q13

2N700 2_SOT23~D

S

Close to VGA Conn.

G_C/BE#0

G_C/BE#1

G_C/BE#2

G_C/BE#3

CK_66M_MCH G_AD3

G_PAR

GRCOMP

AGP_SWING

VREFGC

G_ST0

G_ST1

G_ST2

HUB_HL0

HUB_HL1

HUB_HL2

HUB_HL3

HUB_HL4

HUB_HL5

HUB_HL6

HUB_HL7

HUB_HL8

HUB_HL9

HUB_HL10

HI_RCOMP_MCH

HI_SWIN G_MCH

HI_VREF_MCH

CI_SWING_GMCH

CI_VREF_GMCH

0_0402_5%~D

12

R320

22_0402_5%~D @

C324

10P_04 02_50V8J~D

U3D

Y7

GCBE0

W5

GCBE1

AA3

GCBE2

U2

GCBE3

U6

GFRAME

H4

GCLKIN

AB4

GDEVSEL

V11

GIRDY

AB5

GTRDY

W11

GSTOP

AB2

GPAR/ADD_DETECT

N6

GREQ

M7

GGNT

AC2

GRCOMP/DVOBCGCOMP

AC3

GVSWING

AD2

GVREF

R10

GRBF

R9

GWBF

M4

DBI_HI

M5

DBI_LO

N3

GST0

N5

GST1

N2

GST2

AF5

HI0

AG3

HI1

AK2

HI2

AG5

HI3

AK5

HI4

AL3

HI5

AL2

HI6

AL4

HI7

AJ2

HI8

AH2

HI9

AJ3

HI10

AH5

HISTRF

AH4

HISTRS

AD4

HI_RCOMP

AE3

HI_SWING

AE2

HI_VREF

AK7

CI0

AH7

CI1

AD11

CI2

AF7

CI3

AD7

CI4

AC10

CI5

AF8

CI6

AG7

CI7

AE9

CI8

AH9

CI9

AG6

CI10

AJ6

CISTRF

AJ5

CISTRS

AG2

CI_RCOMP

AF2

CI_SWING

AF4

CI_VREF

G4

DREFCLK

AP8

EXTTS#

AJ8

ICH_SYNC#

AK4

RSTIN#

AG10

RESERVED_1

AG9

RESERVED_2

AN35

RESERVED_3

AP34

RESERVED_4

AR1

RESERVED_5

RG828SDGES_FCBGA932_SPRINGDALE~D

GADSTBF0

GADSTBS0#

AGP

GADSTBF1

GADSTBS1#

HUB

GSBSTBS#

CSA

DDCA_DATA

DDCA_CLK

VGA

GSBSTBF

GSBA0#

GSBA1#

GSBA2#

GSBA3#

GSBA4#

GSBA5#

GSBA6#

GSBA7#

GREEN#

REFSET

GAD0

GAD1

GAD2

GAD3

GAD4

GAD5

GAD6

GAD7

GAD8

GAD9

GAD10

GAD11

GAD12

GAD13

GAD14

GAD15

GAD16

GAD17

GAD18

GAD19

GAD20

GAD21

GAD22

GAD23

GAD24

GAD25

GAD26

GAD27

GAD28

GAD29