Page 1

A

B

COMPAL CONFIDENTIAL

C

D

E

1 1

MODEL NAME :

COMPAL P/N :

PCB NO :

Revision :

LA-1452

0.2

BDW00

DA8DW00L100

DATE :

2 2

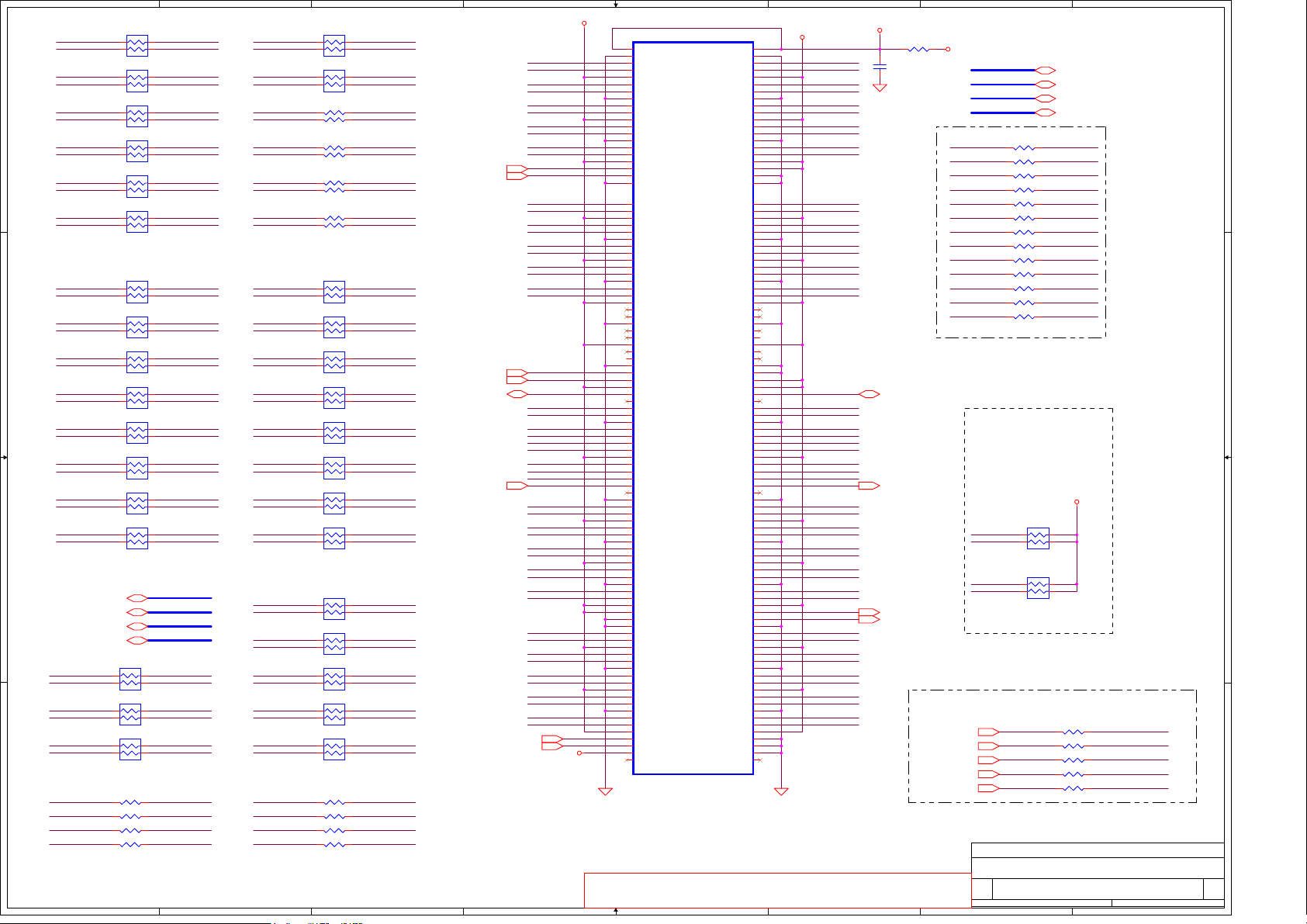

Abacus/TangII Schematics Document

uFCBGA/uFCPGA Northwood

2002-08-22

3 3

REV: 0.2 (PT)

4 4

Dell-Compal Confidential

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

A

B

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

D

Size Document Number Re v

Abacus/TangII LA-1452

Date: Sheet

Compal Electronics, Inc.

Cover Sheet

E

0.2

of

143Monday, August 26, 2002

Page 2

A

Compal confidential

Model Name : ABACUS/TangII

File Name :

LA-1452

B

C

D

E

Block Diagram

DT & Mobile Northwood

1 1

2 2

Minipci CONN

WIRELESS

+3VALW

+3V

+3VS +3VALW

3 3

Fan Control

page 7

DT/BD-PE/ICH4/EXT VGA

DT/BD-GL/ICH4/INT VGA

(PIRQE#,G_GNT#,G_REQ#) FOR EXT.

AGP GRAPHIC/CHRONTEL

LVDS Connector

IDSEL:AD18

(PIRQC#D#,GNT#1,REQ#1)

LAN

BCM-4401L

page 26

+3VS

RJ45

EXT. CRT

+3VS 33MHz

IDSEL:AD17

(PIRQB#,GNT#0,REQ#0)

page 22

page 22

CPU Bypass

& CPUVID

page 7, 8

CRT Connector

AGP Conn

TV OUT

page 17

page 16

page 17

CardBus

& 1394

PCI4510/PCI1510

+3V

page 23,24,25

Card Bus

SLOT CONN

page 24

INT. CRT

AGP4X(1.5V)

PCI BUS

IDSEL:AD20

(PIRQA#,GNT#2,REQ#2)

1394

page 23

uFCBGA/uFCPGA CPU

+1.2VP

+CPU_CORE

System Bus

400/533 MHz

INTEL

BROOKDALE-GL/PE

+1.5VS

+2.5V

+1.25VS

+CPU_CORE

760 BGA

HUB LINK

+1.5VS

66MHz

+3VS

+3VALW

+1.5VS

+1.5VALW

+CPU_CORE

VCC5REF

VCC5REFSUS

INTEL

ICH4

421 BGA

LPC BUS

+3VS

33MHz

page 5,6

HD#(0..63)HA#(3..31)

page 9,10,11

page 18,19,20

Memory

BUS(DDR)

48MHz

24.576MHz

ATA100

IDE HDD

+5VALW

page 21

NS EC87591L

845PE / PCI4510

845GL / PCI1510

Touch Pad

LED Status

LID Switch

+5VS

+5VALW

4 4

Power Circuit

DC/DC

page

34,35,36,37,38,39,40

A

DC/DC Interface

Suspend

page 33

Power On/Off

Reset & RTC

page 32

B

+3VALW

EC I/O Buffer

+5VALW +3VALW

Embedded

Controller

+3VS

+3VALW

page 29

page 30

Int.KBD

+3VALW

BIOS

page 31

page 30

EC DEBUG

page 31

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPA L ELECTRONIC S, INC. NEITHE R THIS SHEET NO R THE INFORMA TION IT CONT AINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C

page 30

Thermal Sensor

ADM1032

+3VS +3VS

+2.5V 200/266MHz

AC-LINK

IDE

CD-ROM

+5VS

page 21

PIDE IRQ14SIDE IRQ15

page 6

AC97 Codec

+5VDDA

AMP & INT.

Speaker

+5VALW

page 28

DDR-DIMM X2

BANK 0, 1, 2, 3

+2.5V

+1.25VS

STAC9750

page 27

HeadPhone

& MIC Jack

+5VDDA

Dell-Compal Confidential

Title

Size Document Number Rev

Abacus/TangII LA-1452

D

Date: Sheet

Clock Generator

ICS950810

page 12,13,14

2 USB Ports

+3VALW

+5VALW

page 15

page 32

MDC

+3VALW

+3V

page 29

Cable

RJ11

page 28

Compal Electronics, Inc.

Block Diagram

E

0.2

of

243Monday, August 26, 2002

Page 3

5

4

3

2

1

Revision List

Schematics Rev

SST-Build

D D

PT-Build

ST-Build

QT-Build

0.1

0.2 0.2

PCB Rev CHIPS Rev

0.1

845PE Rev B0

845GL Rev B1

ICH4 Rev B0

Power Managment table

Signal

State

S0

S1

S3

S5 S4/AC

S5 S4/AC don't exist

+3VALW

+5VALW

+12VALW

ON

+3V

+5V

+2.5V

ON ON

ON ON ON

ON ON

ON OFF

OFF OFF OFF

+3VS

+5VS

+1.5VS

+1.2VP

+CPU_CORE

+1.25VS

OFF

OFF

Ceramic Capacitor Spec Guide:

C C

Temperature Characteristics:

Symbol

CODE

0

Z5U

8

NP0 SH

H

UK

UJ

1

Z5V

9

C0G SJ

I

J

Z5P

A

BJ

SL

3

2

Y5U X7R

C

B

CH

Y5V

CJ

4

5

Y5P

D

E

CK

X5R

6

7

F

G

Tolerance:

Symbol

B B

CODE

+-10%

K

A

+-0.05PF

M

+-20%

B

+-0.1PF

N

+-30%

C

+-0.25PF

P

+100,-0%

D

+-0.5PF +-1PF

Q

+30,-10%

F

V

+20,-10%

G

+-2%

X

+40,-20%

H

+-3%

Z

+80,-20%

J

+-5%

SMBUS Control Table

SOURCE

SMB_EC_CK1

SMB_EC_DA1

SMB_EC_CK2

SMB_EC_DA2

A A

SMB_CLK

SMB_DATA

NS 87591

NS 87591

ICH4

5

INVERTER BATT

SERIAL SENSOR

EEPROM

(1010)

THERMAL

(CPU)

(U57) (U25/U23)

4

THERMAL

SENSOR

SODIMM CLK CHIP

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. N EITHER THIS SHEET N OR THE INFORMATION I T CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

MINI PCI

3

NOTE1:

@XX : Depop component

1@XX : Pop for INT, Depop for EXT

2@XX : Pop for EXT, Depop for INT

Title

Size Document Number Re v

2

Date: Sheet

Compal Electronics, Inc.

Note & Revision

Abacus/TangII LA-1452

Dell-Compal Confidential

of

343Monday, August 26, 2002

1

0.2

Page 4

5

4

3

2

1

PQ26

+1.5VALW

D D

SUSP#

+5VALW

SHDN#

MAX1632

page 36

SIDEPWR

SUSP#

+3VALW

C C

page 34

AC

Battery

B+

VR_ON#

page 34

+12VALW

page 35

page 31

page 21

page 25

SYSON

SUSP#

+5VS

+5VSHDD

+5VDDA

+3V

page 31

+3VS

page 31

SUSP#

VR_ON#

+1.5VS

page 35

CM2843

page 38

+1.2V

+5VS

Mobile

B B

ISL6215

DT

page 38

+CPU_CORE

+3VS

+1.5VS

+2.5V

VGA Conn.

180 pin

+3V

ISL6219

+5VALW

(Either one by CPU)

SUSP#

+12VALW

B+

page 16

+1.25VS

A A

5

SYSON

4

ISL6225

page 36

+2.5V

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPA L ELECTRONIC S, INC. NEITHE R THIS SHEET NO R THE INFORMA TION IT CONT AINS

3

2

Dell-Compal Confidential

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

POWER DIAGRAM

Abacus/TangII LA-1452

of

443Monday, August 26, 2002

1

0.2

Page 5

A

B

C

D

E

F

G

H

I

J

1 1

+CPU_CORE

2 2

HA#[3..31]<9>

3 3

4 4

H_REQ#[0..4]<9>

5 5

H_ADS#<9>

+CPU_CORE

H_BREQ0#<9>

H_BPRI#<9>

H_BNR#<9>

H_LOCK#<9>

CLK_CPU_BCLK<15>

CLK_CPU_BCLK#<15>

HA#[3..31]

H_REQ#[0..4]

R284 @4.7K_0402_5%

1 2

R301 200_0402_5%

For Mobile

12

CLK_CPU_BCLK

CLK_CPU_BCLK#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

AF22

AF23

6 6

H_HIT#<9>

H_HITM#<9>

H_DEFER#<9>

A10

A12

A14

A16

A18

A20

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

D13

D15

D17

D19

D9

VCC_85

F11

VCC_67

VCC_68

HOST DATA

VCC_79E8VCC_80

VCC_69

VCC_78

E20

VCC_70

VCC_77

E18

VCC_71D7VCC_72

VCC_76

E14

E16

E10

VCC_73

D#10

D#11

D#12

D#13

D#14

D#15

D#16

D#17

D#18

D#19

D#20

D#21

D#22

D#23

D#24

D#25

D#26

D#27

D#28

D#29

D#30

D#31

D#32

D#33

D#34

D#35

D#36

D#37

D#38

D#39

D#40

D#41

D#42

D#43

D#44

D#45

D#46

D#47

D#48

D#49

D#50

D#51

D#52

D#53

D#54

D#55

D#56

D#57

D#58

D#59

D#60

D#61

D#62

D#63

VCC_74

VCC_75

E12

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

B21

B22

A23

A25

C21

D22

B24

C23

C24

B25

G22

H21

C26

D23

J21

D25

H22

E24

G23

F23

F24

E25

F26

D26

L21

G26

H24

M21

L22

J24

K23

H25

M23

N22

P21

M24

N23

M26

N26

N25

R21

P24

R25

R24

T26

T25

T22

T23

U26

U24

U23

V25

U21

V22

V24

W26

Y26

W25

Y23

Y24

Y21

AA25

AA22

AA24

NorthWood

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HD#[0..63]

HD#[0..63] <9>

U19A

VCC_0

VCC_1

VCC_2

VCC_3

VCC_4

VCC_5

VCC_6A8VCC_7

VCC_8

VCC_9

VCC_10

VCC_11

VCC_12

VCC_13

VCC_14

VCC_15

VCC_16

VCC_17

VCC_18

VCC_19

VCC_20

VCC_21

VCC_22

VCC_23

VCC_24

VCC_25

VCC_26

VCC_27

VCC_28

VCC_29

VCC_30

VCC_31

VCC_32

VCC_33

VCC_34

VCC_35

VCC_36

VCC_37

VCC_38

VCC_39

VCC_40

VCC_41

VCC_42

VCC_43

VCC_44

VCC_45

VCC_46

VCC_47

VCC_48

VCC_49

VCC_50

VCC_51

VCC_52

VCC_53

VCC_54

VCC_55

VCC_56B7VCC_57B9VCC_58

VCC_59

VCC_61

VCC_62

VCC_63

VCC_64

VSS_56

AD8

VCC_65C8VCC_66

CPU CORE

VCC_81

VCC_82

VCC_83

VCC_84

F9

F13

F15

F17

F19

K2

A#3

K4

A#4

L6

A#5

K1

A#6

L3

A#7

M6

A#8

L2

A#9

M3

A#10

M4

A#11

N1

A#12

M1

A#13

N2

A#14

N4

A#15

N5

A#16

T1

A#17

R2

A#18

P3

A#19

P4

A#20

R3

A#21

T2

A#22

U1

A#23

P6

A#24

U3

A#25

T4

A#26

V2

A#27

R6

A#28

W1

A#29

T5

A#30

U4

A#31

V3

A#32

W2

A#33

Y1

A#34

AB1

A#35

J1

REQ#0

K5

REQ#1

J4

REQ#2

J3

REQ#3

H3

REQ#4

G1

ADS#

AC1

AP#0

V5

AP#1

AA3

BINIT#

AC3

IERR#

H6

BR0#

D2

BPRI#

G2

BNR#

G4

LOCK#

BCLK0

BCLK1

F3

HIT#

E3

HITM#

E2

DEFER#

VSS_0H1VSS_1H4VSS_2

H23

HOST ADDRESS CONTROL SIGNAL

VSS_3

VSS_4

A11

H26

VSS_5

VSS_6

VSS_7

VSS_8

VSS_9

VSS_10

VSS_11

VSS_12A3VSS_13A9VSS_14

VSS_15

VSS_16

VSS_17

VSS_18

VSS_19

VSS_20

VSS_21

A13

A15

A17

A19

A21

A24

A26

AA1

AA11

AA4

AA13

AA15

AA17

AA19

AA23

AA26

CPU CORE

DT/Mobile

NorthWood

GND

VSS_22

VSS_23

VSS_24

VSS_25

VSS_26

VSS_27

VSS_28

VSS_29

VSS_30

VSS_31

VSS_32

VSS_33

AA7

AA9

AB10

AB12

AB3

AB14

AB16

AB18

AB20

AB21

AB24

VSS_34

VSS_35

VSS_36

VSS_37

VSS_38

VSS_39

VSS_40

VSS_41

VSS_42

VSS_43

VSS_44

VSS_45

VSS_46

VSS_47

VSS_48

VSS_49

VSS_50

VSS_51

VSS_52

VSS_53

VSS_54

VSS_55

AB6

AB8

AC2

AC5

AC7

AC9

AC11

AC13

AC15

AC17

AC19

AD1

AC22

AC25

AD10

AD4

AD12

AD14

AD16

AD18

AD21

AD23

7 7

+CPU_CORE

Dell-Compal Confidential

8 8

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMP AL ELECTRONIC S, INC. NEITH ER THIS SHEET NO R THE INFORM ATION IT CONT AINS

A

B

C

D

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

E

F

G

H

Compal Electronics, Inc.

Title

Northwood / P4 uFCPGA (1/2)

Size Document Number Rev

Abacus/TangII LA-1452

Custom

Date: Sheet

I

of

543Monday, August 26, 2002

J

0.2

Page 6

A

1 1

2 2

+CPU_CORE

R271

R288 300_0402_5%

3 3

4 4

R279

Place resistor <100mils from

CPU pin

R206

@0_0603_5%

For

Mobile

5 5

+CPU_CORE

R278 51_0402_5%

R291

R262

R272 51_0402_5%

R268 51_0402_5%

6 6

R296 51_0402_5%

1 2

R313 1.5K_0402_5%

1 2

R305 1.5K_0402_5%

1 2

R314 680_0402_5%

+1.2VP

12

H_DPSLP#<18>

200_0402_5%

12

12

51.1_0603_1%

12

+CPU_CORE

12

R207

0_0603_5%

L24

1 2

L25

1 2

Murata LQG21F4R7N00

CLK_CPU_ITP<15>

CLK_CPU_ITP#<15>

CLK_ITP#<8>

CLK_ITP<8>

12

12

51_0402_5%

51_0402_5%

12

12

12

12

If used ITP port must depop

7 7

SMB_EC_CK2<8,30>

SMB_EC_DA2<8,30>

H_THERMDA

Width 10mil , Spacing 10mil

2200P_0603_50V7K

H_THERMDC

8 8

A

B

H_RS#0<9>

H_RS#1<9>

H_RS#2<9>

H_TRDY#<9>

H_A20M#<18>

H_FERR#<18>

H_IGNNE#<18>

H_SMI#<18>

H_PWRGD<18>

H_STPCLK#<18>

12

1 4

2 3

H_INTR<18>

H_NMI<18 >

H_INIT#<18 >

H_RESET#<8,9>

H_DBSY#<9>

H_DRDY#<9>

H_BSEL0<10>

1 2

R315 62_0402_5%

ITP_BPM0<8>

ITP_BPM1<8>

ITP_PRDY#<8>

ITP_PREQ#<8 >

ITP_TCK<8>

ITP_TDI<8>

ITP_TDO<8 >

ITP_TMS<8>

ITP_TRST#<8 >

RP61

12

TP2

C320

1U_0603_10V4Z

CLK_CPU_ITTP

CLK_CPU_ITTP#

R333

8.2K_0402_5%

U57

2

D+

3

D-

8

SCLK

7

SDATA

ADM1032ARM_RM8

12

@0_0402_4P2R_5%

H_DPSLPR#

H_PWRGD

H_RESET#

SMB_EC_CK2

SMB_EC_DA2

R269

4.7UH_80mA

4.7UH_80mA

12

22U_1206_10V4Z

C321

22U_1206_10V4Z

RP62

1 4

2 3

0_0402_4P2R_5%

ITP_PREQ#

ITP_PRDY#

ITP_BPM0

ITP_BPM1

ITP_BPM2

ITP_BPM3

ITP_TDI

ITP_TMS

ITP_TRST#

C470

12

For

Mobile

@0_0402_5%

+CPU_CORE

C305

H_VSSA

8.2K_0402_5%

R334

12

CPU Temperature Sensor

B

C

H_THERMDA

H_THERMDC

H_THERMTRIP#

1

H_VCCIOPLL

R302

51.1_0603_1%

+5VS+5VS

C

R267

H_A20M#

H_FERR#

H_IGNNE#

H_SMI#

H_PWRGD

H_STPCLK#

H_DPSLPR#

H_INTR

H_NMI

H_INIT#

H_RESET#

ITP_BPM0

ITP_BPM1

ITP_BPM2

ITP_BPM3

ITP_PRDY#

ITP_PREQ#

ITP_TCK

ITP_TDI

ITP_TDO

ITP_TMS

ITP_TRST#

H_VCCA

1 2

12

C174

.1U_0402_16V4Z

VDD1

ALERT

THERM

GND

@33_0402_5%

AB23

AD25

AB25

AD20

AE23

AF25

AC26

AD26

1 2

R300

51.1_0603_1%

1

6

4

5

12

F1

G5

F4

AB2

J6

C6

B6

B2

B5

Y4

D1

E5

W5

H5

H2

AD6

AD5

B3

C4

A2

AC6

AB5

AC4

Y6

AA5

AB4

D4

C1

D5

F7

E6

A5

AF3

L24

P1

D

AE11

U19B

RS#0

RS#1

RS#2

RSP#

TRDY#

A20M#

FERR#

IGNNE#

SMI#

PWRGOOD

STPCLK#

DPSLP#

LINT0

LINT1

INIT#

RESET#

DBSY#

DRDY#

BSEL0

BSEL1

THERMDA

THERMDC

THERMTRIP#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

TCK

TDI

TDO

TMS

TRST#

VCCA

VCCSENSE

VCCIOPLL

NC7

NC8

ITP_CLK0

ITP_CLK1

COMP0

COMP1

12

R337

@10K_0402_5%

D

VSS_57

AE13

VSS_58

VSS_129F8VSS_130

AE15

VSS_59

G21

AE17

AE19

VSS_60

VSS_61

VSS_131

VSS_132G3VSS_133G6VSS_134J2VSS_135

G24

AE22

AE24

VSS_62

VSS_63

H_SKTOCC#

AE26

AE7

AE9

AF1

VSS_64

VSS_65

VSS_66

VSS_67

VSS_136

VSS_137J5VSS_138

J22

J25

K21

+CPU_CORE

R_A

R_B

E

AF10

AF12

AF14

AF16

AF18

AF20

AF26

AF6

AF8

B10

B12

B14

B16

B18

B20

B23

B26

VSS_68

VSS_69

VSS_70

VSS_71

VSS_72

VSS_73

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

SKTOCC#

VSS_85B4VSS_86B8VSS_87

DT/Mobile

NorthWood

GND

VSS_139

VSS_140K3VSS_141K6VSS_142L1VSS_143

VSS_144

VSS_145L4VSS_146M2VSS_147

VSS_148

VSS_149M5VSS_150

VSS_151

VSS_152N3VSS_153N6VSS_154P2VSS_155

VSS_156

VSS_157P5VSS_158R1VSS_159

L23

L26

K24

12

12

M22

M25

GTL Reference Voltage

Layout note :

1. Place R_A and R_B near CPU (Within 1.5").

2. Place decoupling cap 220PF near CPU.(Within

500mils)

R265

49.9_0603_1%

Trace width>=7mil

R261

100_0603_1%

1U_0603_10V4Z

E

P22

P25

N21

N24

C319

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMP AL ELECTRONIC S, INC. NEITH ER THIS SHEET NO R THE INFORM ATION IT CONT AINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

C318

220P_0603_50V8J

F

C11

C13

C15

C17

C19

C22

C25

D10

D12

D14

D16

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92C2VSS_93

VSS_94

VSS_95C5VSS_96C7VSS_97C9VSS_98

VSS_99

VSS_100

GND

VSS_160

VSS_161R4VSS_162

VSS_163

VSS_164T3VSS_165T6VSS_166U2VSS_167

VSS_168

VSS_169U5VSS_170V1VSS_171

T21

T24

R23

R26

U22

U25

+H_GTLREF1

V23

V26

VSS_101

VSS_172

D18

VSS_102

VSS_173V4VSS_174

D20

VSS_103

W21

D21

D24

VSS_104

VSS_105

VSS_175

VSS_176W3VSS_177W6VSS_178Y2VSS_179

W24

G

E11

VSS_106D3VSS_107D6VSS_108D8VSS_109E1VSS_110

VSS_180

VSS_181

Y5

Y22

Y25

SHDN_1632#<34,36>

H_THERMTRIP#<19>

H

DP#0

DP#1

DP#2

DP#3

NC1

NC2

TESTHI0

TESTHI1

TESTHI2

TESTHI3

TESTHI4

TESTHI5

TESTHI8

TESTHI9

GHI#

DBI#0

DBI#1

DBI#2

DBI#3

DBR#

MCERR#

SLP#

VSSA

NC3

NC4

NorthWood

R316

47K_0402_5%

1 2

Q59

3 1

3904

H_GHI#

J26

K25

K26

L25

AA21

AA6

F20

F6

A22

A7

AD24

AA2

AC21

AC20

AC24

AC23

AA20

AB22

U6

W4

Y3

A6

E22

K22

R22

W22

F21

J23

P23

W23

L5

R5

E21

G25

P26

V21

AE25

C3

V6

AB26

AD22

A4

AD2

AD3

+1.2VP

+CPU_COREVL

2

H_THERMTRIP#

E13

E15

E17

E19

E23

E26

F10

F12

F14

F16

F18

F22

F25

F5

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117E4VSS_118E7VSS_119E9VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125F2VSS_126

VSS_127

VSS_128

GTLREF0

GTLREF1

GTLREF2

GTLREF3

ITPCLKOUT0

ITPCLKOUT1

TESTHI10

DSTBN#0

DSTBN#1

DSTBN#2

DSTBN#3

DSTBP#0

DSTBP#1

DSTBP#2

DSTBP#3

ADSTB#0

ADSTB#1

PROCHOT#

VSSSENSE

VID0

VID1

VID2

VID3

VID4

AE5

AE4

AE3

AE2

AE1

PCIRST#<10,16,18, 22,23,25,26,30,33>

Q62

2N7002

NC5

NC6

AF24

AE21

CPU_V ID4 <8,40>

CPU_V ID3 <8,40>

CPU_V ID2 <8,40>

CPU_V ID1 <8,40>

CPU_V ID0 <8,40>

G

2

13

D

S

VCCVID

AF4

1 2

R317@0_0402_5%

+H_GTLREF1

TESTTHI0_1

TESTTHI2_7

ITPCLKOUT0

ITPCLKOUT1

TESTTHI8_10

H_GHI#

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

H_DBR#

H_PROCHOT#

H_SLP#

H_VSSA

1

C317

.1U_0402_16V4Z

12

R320

470_0402_5%

I

1 2

R318 56_0402_5%

PM_CPUPERF#

For Mobile

R285 56_0402_5%

1 2

R275 56_0402_5%

1 2

R293 56_0402_5%

1 2

R276 56_0402_5%

1 2

R294 56_0402_5%

1 2

H_DSTBN#[0..3]

H_DSTBP#[0..3]

H_DBI#[0..3]

R266 @0_0402_5%

1 2

R311 62_0402_5%

TP1

PROCHOT#<19,31>

R303

1K_0402_5%

H_DSTBN#[0..3] <9>

H_DSTBP#[0..3] <9>

H_ADSTB#0 <9>

H_ADSTB#1 <9>

H_DBI#[0..3] <9>

12

H_ITP_DBR# <8>

H_SLP# <18>

+3VS

1 2

3 1

J

+CPU_CORE

PM_CPUPERF# <19>

+CPU_CORE

SYSRST# <19>

+CPU_CORE

+CPU_CORE

R307

470_0402_5%

1 2

Q26

2

3904

H_PROCHOT#

Dell-Compal Confidential

Compal Electronics, Inc.

Title

Mobile Northwood / P4 uFCPGA & Thermal sensor (2/2)

Size Document Number Rev

Abacus/TangII LA-1452

Custom

F

G

H

Date: Sheet

I

643Monday, August 26, 2002

0.2

of

J

Page 7

A

Layout note :

Place close to CPU, Use 2~3 vias per PAD.

Place .22uF caps underneath balls on solder side.

Place 10uF caps on the peripheral near balls.

1 1

Use 2~3 vias per PAD.

Please place these cap in the socket cavity area

+CPU_CORE

12

2 2

3 3

C407

10U_1206_6.3V7K

+CPU_CORE

12

C412

10U_1206_6.3V7K

Please place these cap on the socket north side

+CPU_CORE

12

C388

10U_1206_6.3V7K

B

12

C391

10U_1206_6.3V7K

12

C376

10U_1206_6.3V7K

12

C408

10U_1206_6.3V7K

12

C63

10U_1206_6.3V7K

12

C290

10U_1206_6.3V7K

12

C400

10U_1206_6.3V7K

C

12

C65

10U_1206_6.3V7K

12

C282

10U_1206_6.3V7K

12

C258

10U_1206_6.3V7K

12

C294

10U_1206_6.3V7K

12

C406

10U_1206_6.3V7K

12

C293

10U_1206_6.3V7K

D

E

Layout note :

Place close to CPU power and

ground pin as possible

(<1inch)

For Desktop's CPU:

ESR total=0.75m ohm

C total=6350uF

For Mobile's CPU:

ESR total=1.875m ohm

C total=2590uF

F

+CPU_CORE

+CPU_CORE

+CPU_CORE

+CPU_CORE

.22U_0603_10V7K

+12VALW

G

12

C390

+

470U_D4_2.5V_10m

12

C352

+

470U_D4_2.5V_10m

12

C151

+

330U_D2_2.5V_15m

.22U_0603_10V7K

12

C104

+

+

+

12

C111

.22U_0603_10V7K

12

C371

470U_D4_2.5V_10m

12

C259

470U_D4_2.5V_10m

12

C152

330U_D2_2.5V_15m

.22U_0603_10V7K

12

C113

H

For DT

12

C261

+

470U_D4_2.5V_10m

12

C148

+

470U_D4_2.5V_10m

12

C265

+

330U_D2_2.5V_15m

12

C147

+

470U_D4_2.5V_10m

12

C149

+

470U_D4_2.5V_10m

12

C262

+

330U_D2_2.5V_15m

PLACE ON CPU SIDE

12

C119

.22U_0603_10V7K

.22U_0603_10V7K

12

C120

.22U_0603_10V7K

12

C117

I

12

C110

.22U_0603_10V7K

12

C112

12

C263

+

470U_D4_2.5V_10m

12

C150

+

470U_D4_2.5V_10m

12

C266

+

330U_D2_2.5V_15m

12

C116

.22U_0603_10V7K

J

.22U_0603_10V7K

12

C118

+CPU_CORE

4 4

5 5

12

10U_1206_6.3V7K

+CPU_CORE

12

10U_1206_6.3V7K

C411

C403

12

C410

10U_1206_6.3V7K

12

C405

10U_1206_6.3V7K

12

C257

10U_1206_6.3V7K

12

C291

10U_1206_6.3V7K

12

C402

10U_1206_6.3V7K

12

C99

10U_1206_6.3V7K

12

C401

10U_1206_6.3V7K

SUSP<17,33>

.1U_0402_16V4Z

EN_FAN1<30>

R385

13K_0603_1%

Please place these cap on the socket south side

+CPU_CORE

12

C122

10U_1206_6.3V7K

6 6

7 7

+CPU_CORE

12

10U_1206_6.3V7K

+CPU_CORE

12

10U_1206_6.3V7K

C351

C409

12

C121

10U_1206_6.3V7K

12

C292

10U_1206_6.3V7K

12

C64

10U_1206_6.3V7K

12

C356

10U_1206_6.3V7K

12

C368

10U_1206_6.3V7K

12

C68

10U_1206_6.3V7K

12

C62

10U_1206_6.3V7K

12

C100

10U_1206_6.3V7K

12

C66

10U_1206_6.3V7K

12

C404

10U_1206_6.3V7K

12

C296

10U_1206_6.3V7K

+12VS

EN_FAN2<30>

R10

13K_0603_1%

Q29

2

1 3

12

C574

U10 LMV321_SOT23-5

12

U1 LMV321_SOT23-5

12

SI2303DS

+12VS

+5VS

5

1

+

3

-

2

R381

7.32K_0603_1%

+5VS

5

1

+

3

-

2

R6

7.32K_0603_1%

Fan1 Control circuit

R376

3.48K_0603_1%

4

12

12

21

D22

1N4148

31

2

Q12

2SA1036K

Q10

FMMT619

C578

.1U_0402_16V4Z

1 2

D21

1N4148

2

Fan2 Control circuit

Q8

R11

3.48K_0603_1%

4

12

12

21

D20

1N4148

31

2

Q1

2SA1036K

2SC2411EK

C234

.1U_0402_16V4Z

1 2

D6

@1N4148

2

3 1

2 1

3 1

2 1

+5VS

D14

1SS355

2 1

+5VFAN_1

C566

@1000P_0402_50V7K

+5VS

D11

1SS355

2 1

+5VFAN_2

C235

@1000P_0402_50V7K

JP12

1

2

3

MOLEX_53398-0390_3P

1 2

R340 10K_0402_5%

FAN1_TACH <30>

JP19

1

2

3

MOLEX_53398-0390_3P

1 2

R200 10K_0402_5%

FAN2_TACH <30>

+3VS

+3VS

Dell-Compal Confidential

8 8

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMP AL ELECTRONIC S, INC. NEITH ER THIS SHEET NO R THE INFORM ATION IT CONT AINS

A

B

C

D

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

E

F

G

H

Compal Electronics, Inc.

Title

CPU Decoupling CAP. & Fan control

Size Document Number Rev

Abacus/TangII LA-1452

Custom

Date: Sheet

I

of

743Monday, August 26, 2002

J

0.2

Page 8

10

9

8

7

6

5

4

3

2

1

Mobile CPU Desktop CPU

H H

CPU_VID0<6,40>

CPU_VID1<6,40>

CPU_VID2<6,40>

CPU_VID3<6,40>

G G

CPU_VID4<6,40>

CPU_VID0

CPU_VID1

CPU_VID2

CPU_VID3

CPU_VID4

R260 1K_0402_5%

R259 1K_0402_5%

R258 1K_0402_5%

R257 1K_0402_5%

R256 1K_0402_5%

+3VS

12

12

12

12

12

MO/DT_CPU

VID

VCC

1.750V

1.700V

1.650V

1.600V

1.550V

1.500V

1.450V

1.400V

1.350V

1.300V

1.250V

+CPU_CORE

F F

E E

ITP_BPM0<6>

ITP_BPM1<6>

ITP_PRDY#<6>

ITP_PREQ#<6 >

H_RESET#<6,9>

ITP_TCK<6>

CLK_ITP<6>

CLK_ITP#<6>

C201

@2.2P_0402_16V8J

12

C200

@10U_1206_6.3V7K

12

12

C199

@.1U_0402_16V4Z

C198

12

@2.2P_0402_16V8J

12

C560

@.1U_0402_16V4Z

JP15

1

2

1

3

4

3

5

6

5

7

8

7

9

10

9

11

12

11

13

14

13

151516

171718

191920

212122

232324

2525K

@2MM SMT KEY26

R184 @1.5K_0603_1%

1 2

R183 @75_0603_1%

1 2

R372 @39_0603_1%

1 2

R310 @150_0603_1%

1 2

2

4

6

8

10

12

14

16

18

20

22

24

26

R373 @33_0402_5%

12

12

R304

@27.4_0603_1%

+CPU_CORE

AGP_BUSY # <16,19>

H_ITP_DBR# <6>

ITP_TDI <6>

ITP_TMS <6>

ITP_TRST# <6>

ITP_TCK <6>

ITP_TDO <6>

1.200V

1.150V

1.100V

1.050V

1.000V

0.975V

0.950V

0.925V

0.900V

0.875V

0.850V

0.825V

0.800V

0.775V

0.750V

0.725V

0.700V

D D

ITP Debug Connector

0.675V

0.650V

0.625V

0.600V

10

00000

0000

1

000

00 0

00

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0000

1

1

1

1

1

1

0000

1

00

1

0

1

1

0

1

1

1

1

0

1

1

1

1

1

1

1

1

000

0

000

1

00

1

1

00

1

0

1

1

0

1

1

1

0

00

1

00

1

1

0

1

1

1

1

0

1

1

1

1

1

00 01

00011

1

0000

1

1

000

1

1

0

1

00

1

0

1

0

0

0

11

0

1

11

0

0

0

1

0

0

1

0

1

1

0

1

1

0

1

1

0

1

1

1

1

1

1

1

1

XXXXX

1

1

X

000

XXX

1

000

XXXXX

1

0

1

XXXXX

00

1

XXXXX

1

00

XXXXX

1

0

XXXXX

11111

VRM output off 1 1 1 1

0412134023

0

0

0

0

11

0

0

0

0

0

0

1

0

0

0

1

0

0

0

1

0

0

0

0

1

XXXXX

X

XXXXXXX

X

XX

X

XXXX

XXXXX

XXXXX

XXXXX

XXXXX

XXXXX

XXXXX

XXXXX

1

C C

+5VS

12

C482

U25

SMB_EC_DA2<6,30>

B B

SMB_EC_CK2<6,30>

1

SDA

2

SCL

3

OS#

4

GND

LM75CIMMX-5

Address:1001_000X Address:1001_000X

VCC

8

7

A0

6

A1

5

A2

.1U_0402_16V4Z

R351 1K_0402_5%

1 2

SMB_EC_DA2<6,30>

SMB_EC_CK2<6,30>

U23

1

SDA

2

SCL

3

OS#

4

GND

LM75CIMMX-5

VCC

8

7

A0

6

A1

5

A2

C394

.1U_0402_16V4Z

1 2

1 2

R308 10K_0402_5%

12

R306

1K_0402_5%

+5VS

Dell-Compal Confidential

A A

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMP AL ELECTRONIC S, INC. NEITH ER THIS SHEET NO R THE INFORM ATION IT CONT AINS

10

9

8

7

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

6

5

4

3

COMPAL Electronics, Inc.

Title

CPU VID & ITP PORT

Size Document Number Rev

Abacus/TangI I LA-1452

Custom

Date: Sheet

2

of

843Monday, August 26, 2002

1

0.2

Page 9

5

HD#[0..63]

HA#[3..31]

U12A

HD#0

D D

C C

B B

H_DSTBP#0<6>

H_DSTBP#1<6>

H_DSTBP#2<6>

H_DSTBP#3<6>

H_DSTBN#0<6>

H_DSTBN#1<6>

H_DSTBN#2<6>

H_DSTBN#3<6>

H_RESET#<6,8>

CLK_MCH_BCLK<15>

CLK_MCH_BCLK#<15>

MCH_GTLREF<11>

C335

.1U_0402_10V6K

.1U_0402_10V6K

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

12

12

C304

12

.1U_0402_10V6K

BROOKDALE-GL/PE

T30

HD#0

R33

HD#1

R34

HD#2

N34

HD#3

R31

HD#4

L33

HD#5

L36

HD#6

P35

HD#7

J36

HD#8

K34

HD#9

K36

HD#10

M30

HD#11

M35

HD#12

L34

HD#13

K35

HD#14

H36

HD#15

G34

HD#16

G36

HD#17

J33

HD#18

D35

HD#19

F36

HD#20

F34

HD#21

E36

HD#22

H34

HD#23

F35

HD#24

D36

HD#25

H35

HD#26

E33

HD#27

E34

HD#28

B35

HD#29

G31

HD#30

C36

HD#31

D33

HD#32

D30

HD#33

D29

HD#34

E31

HD#35

D32

HD#36

C34

HD#37

B34

HD#38

D31

HD#39

G29

HD#40

C32

HD#41

B31

HD#42

B32

HD#43

B30

HD#44

B29

HD#45

E27

HD#46

C28

HD#47

B27

HD#48

D26

HD#49

D28

HD#50

B26

HD#51

G27

HD#52

H26

HD#53

B25

HD#54

C24

HD#55

B23

HD#56

B24

HD#57

E23

HD#58

C22

HD#59

G25

HD#60

B22

HD#61

D24

HD#62

G23

HD#63

L31

HDSTBP0#

J34

HDSTBP1#

E29

HDSTBP2#

E25

HDSTBP3#

N31

HDSTBN0#

G33

HDSTBN1#

C30

HDSTBN2#

D25

HDSTBN3#

D22

CPURST#

K30

HCLK

J31

HCLK#

D27

HD_VREF2

H24

HD_VREF1

H30

HD_VREF0

AD30

HA_VREF

P30

HCC_VREF

BROOKDALE-GL /PE_760P

C274

82845GL-INT VGA

82845PE-EXT VGA

HOST,HUB

HD#[0..63] <5>

HA#[3..31] <5>

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HADSTB0#

HADSTB1#

HIT#

HITM#

ADS#

BNR#

BPRI#

BREQ0#

DBSY#

DEFER#

DRDY#

HTRDY#

HLOCK#

DINV3

DINV2

DINV1

DINV0

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HI10

HI_STBS

HI_STBF

RS2#

RS1#

RS0#

HX_RCOMP

HY_RCOMP

HX_SWING

HY_SWING

HI_VREF

HI_RCOMP

HI_SWING

W31

AA33

AB30

V34

Y36

AC33

Y35

AA36

AC34

AB34

Y34

AB36

AC36

AC31

AF35

AD36

AD35

AE34

AD34

AE36

AF36

AE33

AF34

AG34

AG36

AE31

AH35

AG33

AG31

AB35

AF30

P36

M36

T36

T34

M34

U33

U31

N36

U36

V30

T35

C26

B33

C35

N33

V36

AA31

W33

AA34

W35

AF2

AE2

HI9

AF3

HI8

AE5

HI7

AE4

HI6

AF4

HI5

AD8

HI4

AC5

HI3

AC7

HI2

AB8

HI1

AA7

HI0

AD4

AC4

P34

U34

R36

B28

V35

H28

Y30

AD3

AC2

AD2

4

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HI10

HI9

HI8

HI7

HI6

HI5

HI4

HI3

HI2

HI1

HI0

HX_RCOMP

HY_RCOMP

R295

1 2

68.1_0603_1%

12

C302

.1U_0402_10V6K

H_ADSTB#0 <6>

H_ADSTB#1 <6>

H_HIT# <5>

H_HITM# <5>

H_ADS# <5>

H_BNR# <5>

H_BPRI# <5>

H_BREQ0# <5>

H_DBSY# <6>

H_DEFER# <5>

H_DRDY# <6>

H_TRDY# <6>

H_LOCK# <5>

H_DBI#3 <6>

H_DBI#2 <6>

H_DBI#1 <6>

H_DBI#0 <6>

H_REQ#0 <5>

H_REQ#1 <5>

H_REQ#2 <5>

H_REQ#3 <5>

H_REQ#4 <5>

HI[0..10] <18>

HUB_PSTRB <18>

HUB_PSTRB# <18>

H_RS#2 <6>

H_RS#1 <6>

H_RS#0 <6>

1 2

24.9_0603_1%

10 mil

10 mil

H_XY_ SWING <11>

HUB_V REF <11,18>

HUB_VSW ING <11,18>

12

R18

R263

1 2

24.9_0603_1%

C327

.1U_0402_10V6K

+1.5VS

3

DDR_SDQ[0..63]<12>

DDR_SDQS[0..7]<12>

DDR_SDM[0..7]<12>

DDR_SMA[0..12]<12,13>

DDR_CLK2#<12>

DDR_CLK2<12> DDR_CLK3# <13>

DDR_CLK1#<12>

DDR_CLK1<12>

DDR_CLK0#<12>

DDR_CLK0<12>

DDR_SDQ0

AN4

DDR_SDQ1

AP2

DDR_SDQ2

AT3

DDR_SDQ3

AP5

DDR_SDQ4

AN2

DDR_SDQ5

AP3

DDR_SDQ6

AR4

DDR_SDQ7

AT4

DDR_SDQ8

AT5

DDR_SDQ9

AR6

DDR_SDQ10

AT9

DDR_SDQ11

AR10

DDR_SDQ12

AT6

DDR_SDQ13

AP6

DDR_SDQ14

AT8

DDR_SDQ15

AP8

DDR_SDQ16

AP10

DDR_SDQ17

AT11

DDR_SDQ18

AT13

DDR_SDQ19

AT14

DDR_SDQ20

AT10

DDR_SDQ21

AR12

DDR_SDQ22

AR14

DDR_SDQ23

AP14

DDR_SDQ24

AT15

DDR_SDQ25

AP16

DDR_SDQ26

AT18

DDR_SDQ27

AT19

DDR_SDQ28

AR16

DDR_SDQ29

AT16

DDR_SDQ30

AP18

DDR_SDQ31

AR20

DDR_SDQ32

AR22

DDR_SDQ33

AP22

DDR_SDQ34

AP24

DDR_SDQ35

AT26

DDR_SDQ36

AT22

DDR_SDQ37

AT23

DDR_SDQ38

AT25

DDR_SDQ39

AR26

DDR_SDQ40

AP26

DDR_SDQ41

AT28

DDR_SDQ42

AR30

DDR_SDQ43

AP30

DDR_SDQ44

AT27

DDR_SDQ45

AR28

DDR_SDQ46

AT30

DDR_SDQ47

AT31

DDR_SDQ48

AR32

DDR_SDQ49

AT32

DDR_SDQ50

AR36

DDR_SDQ51

AP35

DDR_SDQ52

AP32

DDR_SDQ53

AT33

DDR_SDQ54

AP34

DDR_SDQ55

AT35

DDR_SDQ56

AN36

DDR_SDQ57

AM36

DDR_SDQ58

AK36

DDR_SDQ59

AJ36

DDR_SDQ60

AP36

DDR_SDQ61

AM35

DDR_SDQ62

AK35

DDR_SDQ63

AK34

DDR_SDQ[0..63]

DDR_SDQS[0..7]

DDR_SDM[0..7]

DDR_SMA[0..12]

U12B

SDQ_0

SDQ_1

SDQ_2

SDQ_3

SDQ_4

SDQ_5

SDQ_6

SDQ_7

SDQ_8

SDQ_9

SDQ_10

SDQ_11

SDQ_12

SDQ_13

SDQ_14

SDQ_15

SDQ_16

SDQ_17

SDQ_18

SDQ_19

SDQ_20

SDQ_21

SDQ_22

SDQ_23

SDQ_24

SDQ_25

SDQ_26

SDQ_27

SDQ_28

SDQ_29

SDQ_30

SDQ_31

SDQ_32

SDQ_33

SDQ_34

SDQ_35

SDQ_36

SDQ_37

SDQ_38

SDQ_39

SDQ_40

SDQ_41

SDQ_42

SDQ_43

SDQ_44

SDQ_45

SDQ_46

SDQ_47

SDQ_48

SDQ_49

SDQ_50

SDQ_51

SDQ_52

SDQ_53

SDQ_54

SDQ_55

SDQ_56

SDQ_57

SDQ_58

SDQ_59

SDQ_60

SDQ_61

SDQ_62

SDQ_63

BROOKDALE-GL /PE_760P

AL21

SCMD_CLK0

AN11

AM34

AP21

AP9

AK22

AP11

SCMD_CLK1

SCMD_CLK0#

AP33

AL33

AN21

AN9

AN34

SCMD_CLK2

SCMD_CLK3

SCMD_CLK4

SCMD_CLK1#

SCMD_CLK5

SCMD_CLK2#

SCMD_CLK3#

SCMD_CLK4#

SCMD_CLK5#

BROOKDALE-GL/PE

DDR

SMAA12/BS0

SMAA11/DQS8

SMAA10/DQ31

SMAA9/SMA3

SMAA8/SMA4

SMAA7/SMA6

SMAA6/SDQ29

SMAA5/SMA8

SMAA4/SMA11

SMAA3/SMA7

SMAA2/SMA9

SMAA1/SDQ19

SMAA0/SMA12

SCKE3/SCK#5

SCKE2/RSVD

SCKE1/SDQ58

SCKE0/RSVD

SCS#0/SCKE2

SCS#1/RSVD

SCS#2/SCK#2

SCS#3/SCAS#

SRAS#/SCKE0

SCAS#/RSVD

SWE#/SDQ5

SRCVEN_OUT#

SRCVEN_IN#

SMY_RCOMP

SM_VREF

SMAB5

SMAB4

SMAB2

SMAB1

SBA1

SBA0

SDQS0

SDQS1

SDQS2

SDQS3

SDQS4

SDQS5

SDQS6

SDQS7

SDM0

SDM1

SDM2

SDM3

SDM4

SDM5

SDM6

SDM7

2

DDR_CLK3 <13>

DDR_CLK4 <13>

DDR_CLK4# <13>

DDR_CLK5 <13>

DDR_CLK5# <13>

DDR_SMA12

AN15

DDR_SMA11

AL15

DDR_SMA10

AK26

DDR_SMA9

AK16

DDR_SMA8

AN17

DDR_SMA7

AP17

DDR_SMA6

AP19

DDR_SMA5

AL17

DDR_SMA4

AL19

DDR_SMA3

AK20

DDR_SMA2

AP23

DDR_SMA1

AN25

DDR_SMA0

AL25

DDR_SMAB5

AK18

DDR_SMAB4

AN19

DDR_SMAB2

AN23

DDR_SMAB1

AP25

DDR_SBS1

AP27

DDR_SBS0

AN27

DDR_SDQS0

AR2

DDR_SDQS1

AT7

DDR_SDQS2

AT12

DDR_SDQS3

AT17

DDR_SDQS4

AR24

DDR_SDQS5

AT29

DDR_SDQS6

AT34

DDR_SDQS7

AL36

DDR_SDM0

AP4

DDR_SDM1

AR8

DDR_SDM2

AP12

DDR_SDM3

AR18

DDR_SDM4

AT24

DDR_SDM5

AP28

DDR_SDM6

AR34

DDR_SDM7

AL34

DDR_CKE3

AL13

DDR_CKE2

AK14

DDR_CKE1

AN13

DDR_CKE0

AP13

DDR_SCS#0

AL29

DDR_SCS#1

AP31

DDR_SCS#2

AK30

DDR_SCS#3

AN31

DDR_SRAS#

AK28

DDR_SCAS#

AN29

DDR_SWE#

AP29

RDCLKO

AK24

RDCLKI

AL23

AJ34

AM2

12

1 2

C364

.1U_0402_10V6K

DDR_SMAB5 <13>

DDR_SMAB4 <13>

DDR_SMAB2 <13>

DDR_SMAB1 <13>

DDR_SBS1 <12,13>

DDR_SBS0 <12,13>

DDR_CKE3 <13>

DDR_CKE2 <13>

DDR_CKE1 <12>

DDR_CKE0 <12>

DDR_SCS#0 <12>

DDR_SCS#1 <12>

DDR_SCS#2 <13>

DDR_SCS#3 <13>

DDR_SR AS# <12,13>

DDR_SC AS# <12,13>

DDR_SW E# <12,13>

12

R297 @0_0603_5%

R299

0_0603_5%

RDCLKI & RDCLKO 100mils

LENGTH 5mils WIDTH

12

R292

60.4_0603_1%

R298

60.4_0603_1%

SDREF

12

1

+2.5V

12

C357

.1U_0402_10V6K

Close to H28 Close to Y30

A A

Layout note :

1. HX_RCOM P, HY_RCOMP Trace width 10 mil.

2. Terminator Max 500 mil.

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPA L ELECTRONIC S, INC. NEITHE R THIS SHEET NO R THE INFORMA TION IT CONT AINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Date: Sheet

Dell-Compal Confidential

Compal Electronics, Inc.

BROOKDALE-GL/PE (1/3)

Abacus/TangII LA-1452

1

0.2

of

943Monday, August 26, 2002

Page 10

A

U12C

AGP_PIPE#<16>

A A

AGP_WBF#<16>

AGP_RBF#<16>

AGP_ST0<16>

AGP_ST1<16>

AGP_ST2<16>

AGP_ADSTB0<16>

AGP_ADSTB0#<16>

AGP_ADSTB1<16>

AGP_ADSTB1#<16>

AGP_SBSTB<16>

AGP_SBSTB#<16>

AGP_FRAME#<16>

AGP_IRDY#<16>

AGP_TRDY#<16>

AGP_STOP#<16>

AGP_DEVSEL#<16>

AGP_REQ#<16>

AGP_PAR<16>

AGP_GNT#<16>

AGP_C/BE#3<16>

AGP_C/BE#2<16>

AGP_C/BE#1<16>

AGP_C/BE#0<16>

B B

C C

D D

INT_HSYNC<16>

INT_VSYNC<16>

INTDDCDA<16>

+AGPREF

INTDDCCK<16>

R17

137_0603_1%

RSTIN#

INTCRT_B#

INTCRT_G#

INTCRT_R#

AGP_PIPE#

AGP_SBA0

AGP_SBA1

AGP_SBA2

AGP_SBA3

AGP_SBA4

AGP_SBA5

AGP_SBA6

AGP_SBA7

AGP_ST0

AGP_ST1

AGP_ST2

AGP_C/BE#3

AGP_C/BE#2

AGP_C/BE#1

AGP_C/BE#0

47.5_0603_1%

R215

1 2

1 2

R21447.5_0603_1%

R241

36.5_0603_1%

R43 0_0402_5%

12

C69

1 2

@15P_0402_50V8J

A

H8

GPIPE#

C3

GSBA0/ADDIN0

C2

GSBA1/ADDIN1

D3

GSBA2/ADDIN2

D2

GSBA3/ADDIN3

E4

GSBA4/ADDIN4

E2

GSBA5/ADDIN5

F3

GSBA6/ADDIN6

F2

GSBA7/ADDIN7

G5

GWBF#

G7

GRBF#

C4

GST0

B4

GST1

B3

GST2

V8

GAD_STB0/DVOBCLK

U7

GAD_STB0#/DVOBCLK#

M8

GAD_STB1/DVOCCLK

L7

GAD_STB1#/DVOCCLK#

F4

GSBSTB

E5

GSBSTB#

M4

G_FRAME#/MDVI DATA

N7

G_IRDY#/MI2C CLK

N5

G_TRDY#/MDVI CLK

P2

G_STOP#/MDDC DATA

N2

G_DEVSEL#/MI2C DATA

D5

G_REQ#

P4

G_PAR/ADD_DETECT

B5

G_GNT#

H2

GCBE3#/DVOCD5

M2

GCBE2#

N4

GCBE1#/DVOBBLANK#

R4

GCBE0#/DVOBD7

L2

AGP RCOMP/DVOBCRCOMP

W2

AGP_VREF

B7

HSYNC

C6

VSYNC

D7

DDCA_CLK

C7

DDCA_DATA

B16

REFSET

BROOKDALE-GL /PE_760P

12

C324

.1U_0402_10V6K

PCIRST# <6,16,18,2 2,23,25,26,30,33>

AGP/DVO

BROOKDALE-GL/PE

ANALOG DISPLAY

B

AGP_AD[0..31]<16>

AGP_SBA[0..7]<16>

GAD0/DVOBHSYNC

GAD1/DVOBVSYNC

GAD2/DVOBD1

GAD3/DVOBD0

GAD4/DVOBD3

GAD5/DVOBD2

GAD6/DVOBD5

GAD7/DVOBD4

GAD8/DVOBD6

GAD9/DVOBD9

GAD10/DVOBD8

GAD11/DVOBD11

GAD12/DVOBD10

GAD13/DVOBCCLKINT#

GAD14/DVOBFLDSTL

GAD15/MDDC CLK

GAD16/DVOCVSYNC

GAD17/DVOCHSYNC

GAD18/DVOCBLANK#

GAD19/DVOCD0

GAD20/DVOCD1

GAD21/DVOCD2

GAD22/DVOCD3

GAD23/DVOCD4

GAD24/DVOCD7

GAD25/DVOCD6

GAD26/DVOCD9

GAD27/DVOCD8

GAD28/DVOCD11

GAD29/DVOCD10

GAD30/DVOBCINTR#

GAD31/DVOCFLDSTL

GCLKIN

RSTIN#

DREFCLK

PWROK

PSBSEL

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

*

+1.5VS

+1.5VS

+1.5VS

.1U_0402_10V6K

NEAR AA1

B

AGP_AD[0..31]

AGP_SBA[0..7]

AGP_AD0

V4

AGP_AD1

V2

AGP_AD2

W4

AGP_AD3

W5

AGP_AD4

U5

AGP_AD5

U4

AGP_AD6

U2

AGP_AD7

V3

AGP_AD8

T2

AGP_AD9

T3

AGP_AD10

T4

AGP_AD11

R2

AGP_AD12

R5

AGP_AD13

R7

AGP_AD14

T8

AGP_AD15

P3

AGP_AD16

P8

AGP_AD17

K4

AGP_AD18

K2

AGP_AD19

J2

AGP_AD20

M3

AGP_AD21

L5

AGP_AD22

L4

AGP_AD23

H4

AGP_AD24

G2

AGP_AD25

K3

AGP_AD26

J4

AGP_AD27

J5

AGP_AD28

J7

AGP_AD29

H3

AGP_AD30

K8

AGP_AD31

G4

AE7

RSTIN#

AJ31

D14

R270 2@8.2K_0402_5%

E7

1 2

Y3

INTCRT_B

G15

INTCRT_B#

H16

INTCRT_G

E15

INTCRT_G#

F16

INTCRT_R

C15

INTCRT_R#

D16

12

R273

8.2K_0402_5%

PSBSEL FSB FREQUENCY

12

400 MHZ

533 MHZ

VCCA_DPLL

12

12

C28

22U_1206_10V4Z

12

+

VCCA_FSB

12

0

1

L3

FBM-L11-201209-221LMAT

1 2

C29

22U_1206_10V4Z

L4

FBM-L11-201209-221LMAT

1 2

C27

.1U_0402_10V6K

12

C343

Place close to pin AE7

CLK_MCH_DISPLAY

@10_0402_5%

@10P_0402_50V8K

Place close to pin AE7

CLK_MCH_66M

@22_0402_5%

@10P_0402_50V8K

CLK_MCH_66M <15>

CLK_MCH_DISPLAY <15>

PM_PWROK <19,30,32>

H_BSEL0 <6>

H_SEL0 <15>

INTCRT_B <16>

INTCRT_G <16>

INTCRT_R <16>

C22

150U_D_6.3VM

12

C33

.1U_0402_10V6K

C341

.1U_0402_10V6K

NEAR AE1

C

+1.5VS

12

R234

12

C249

12

R286

12

C333

+CPU_CORE

R277

+1.5VS

12

C251

.1U_0402_10V6K

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPA L ELECTRONIC S, INC. NEITHE R THIS SHEET NO R THE INFORMA TION IT CONT AINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

12

1.5K_0402_5%

C

U12D

Y19

VCC1

AA19

VCC2

W20

VCC3

U21

VCC4

W21

VCC5

AA21

VCC6

A9

VCC7

B9

VCC8

C9

VCC9

D9

VCC10

E9

VCC11

B10

VCC12

C10

VCC13

D10

VCC14

F10

VCC15

H10

VCC16

A11

VCC17

B11

VCC18

C11

VCC19

D11

VCC20

E11

VCC21

G11

VCC22

J11

VCC23

B12

VCC24

C12

VCC25

D12

VCC26

F12

VCC27

H12

VCC28

G13

VCC29

J13

VCC30

H14

VCC31

J15

VCC32

AA17

VCC33

W17

VCC34

U17

VCC35

W18

VCC36

V19

VCC37

U19

VCC38

K10

VCC39

K12

VCC40

K14

VCC41

K16

VCC42

W19

VCC43

B18

VTTFSB0

C18

VTTFSB1

D18

VTTFSB2

H18

VTTFSB3

B19

VTTFSB4

C19

VTTFSB5

D19

VTTFSB6

E19

VTTFSB7

G19

VTTFSB8

J19

VTTFSB9

B20

VTTFSB10

C20

VTTFSB11

D20

VTTFSB12

F20

VTTFSB13

H20

VTTFSB14

F18

VTTFSB15

K18

VTTFSB16

K20

VTTFSB17

K22

VTTFSB18

K26

VTTFSB19

M28

VTTFSB20

T28

VTTFSB21

Y28

VTTFSB22

AD28

VTTFSB23

AB2

TESTIN#

Y2

MEM_SEL

A37

RSVD0

AB3

RSVD1

AA2

RSVD2

AA3

RSVD3

AA4

RSVD4

AA5

RSVD5

Y4

RSVD6

Y8

RSVD7

W7

RSVD8

AU37

NC

AU36

NC

AT37

NC

AU2

NC

AU1

NC

AT1

NC

AJ35

NC

AH34

NC

BROOKDALE-GL /PE_760P

VCCAGP0A3VCCAGP1A7VCCAGP2C1VCCAGP3D4VCCAGP4D6VCCAGP5G1VCCAGP6K6VCCAGP7L1VCCAGP8L9VCCAGP9

BROOKDALE-GL/PE

P6

VCCAGP10R1VCCAGP11R9VCCAGP12W9VCCAGP13

POWER

D

V6

P10

VCCAGP14

D

V10

AB10

VCCAGP15

VCCAGP16

VCCA_SM0

VCCA_SM1

VTTDECAP0

VTTDECAP1

VTTDECAP2

VTTDECAP3

VTTDECAP4

VCCA_DPLL

VCCA_DAC0

VCCA_DAC1

SMX_RCOMP

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCQSM0

VCCQSM1

VCCQSM2

VCCA_FSB

VCCA_HI

VCCHI0

VCCHI1

VCCHI2

VCCHI3

VCCGPIO

E

+2.5V

AH8

AK8

AG9

AJ9

AL9

AM22

AJ23

AL37

AU9

AK10

AJ11

AL11

AU25

AM26

AU13

AM14

AJ27

AJ1

AL1

AJ15

AP15

AU29

AH2

AJ2

AK2

AL2

AM30

AH3

AJ3

AK3

AL3

AH4

AJ4

AK4

AL4

AU17

AJ5

AL5

AU5

AM18

AJ19

AK32

AU33

AH6

AK6

AP20

AG7

AJ7

AL7

AP7

AH10

AH12

AH14

AH18

AH22

AH26

AG1

AG2

AT20

AT21

AU21

A31

AC37

R37

L37

G37

A17

AD10

AD6

AC9

AC1

AE3

A13

B6

B14

A15

AF10

A2

NC

A36

NC

B37

NC

B1

NC

100U_D_6.3VM

.1U_0402_10V6K

12

VCCA_SM

C640

.1U_0402_10V6K

VCCA_FSB

+1.5VS

VCCA_DPLL

VCCA_DAC

12

R283

60.4_0603_1%

12

C340

+

12

L27

FBM-L11-201209-221LMAT

12

C334

4.7U_0805_10V4Z

C385

12

R281

1_0402_5%

.1U_0402_10V6K

12

C353

.1U_0402_10V6K

12

R287

60.4_0603_1%

12

C399

+

100U_D_6.3VM

12

.1U_0402_10V6K

12

C277

12

C344

.1U_0402_10V6K

12

+

+1.5VS

12

12

+

.1U_0402_10V6K

12

C297

.1U_0402_10V6K

+2.5V

C159

100U_D_6.3VM

L28

FBM-L11-201209-221LMAT

C336

100U_D_6.3VM

12

C316

12

C270

.1U_0402_10V6K

C268

VCCA_DAC

12

.1U_0402_10V6K

12

C332

+3VS

12

C267

12

C32

.1U_0402_10V6K

.01U_0402_25V4Z

Dell-Compal Confidential

Title

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

BROOKDALE-GL/PE (2/3)

Abacus/TangII LA-1452

0.2

of

10 43Monday, August 26, 2002

E

Page 11

5

U12E

AM10

VSS0

AR23

D D

C C

B B

A A

VSS1

AU23

VSS2

F24

VSS3

AM24

VSS4

A25

VSS5

C16

VSS6

N37

VSS7

U18

VSS8

V18

VSS9

Y18

VSS10

AA18

VSS11

AL31

VSS12

AR31

VSS13

AU31

VSS14

F32

VSS15

H32

VSS16

K32

VSS17

M32

VSS18

P32

VSS19

T32

VSS20

V32

VSS21

Y32

VSS22

AB32

VSS23

AD32

VSS24

AF32

VSS25

AH32

VSS26

AM4

VSS27

A5

VSS28

C5

VSS29

AG5

VSS30

AN5

VSS31

AR5

VSS32

AR19

VSS33

AM32

VSS34

A33

VSS35

C33

VSS36

AJ33

VSS37

AN33

VSS38

AR33

VSS39

F6

VSS40

H6

VSS41

M6

VSS42

T6

VSS43

Y6

VSS44

AB6

VSS45

AF6

VSS46

AM6

VSS47

U20

VSS48

V20

VSS49

Y20

VSS50

AA20

VSS51

AM20

VSS52

A21

VSS53

B21

VSS54

C21

VSS55

D21

VSS56

E21

VSS57

G21

VSS58

J21

VSS59

D34

VSS60

W34

VSS61

A35

VSS62

E35

VSS63

G35

VSS64

J35

VSS65

L35

VSS66

AN7

VSS67

AR7

VSS68

AU7

VSS69

B8

VSS70

C8

VSS71

D8

VSS72

F8

VSS73

V21

VSS74

Y21

VSS75

AJ21

VSS76

AR21

VSS77

F22

VSS78

H22

VSS79

M10

VSS80

T10

VSS81

Y10

VSS82

AH16

VSS83

AH20

VSS84

AH24

VSS85

BROOKDALE-GL /PE_760P

AR9

AR17

AJ17

Y17

AG4

AB4

AU3

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

BROOKDALE-GL/PE

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

N35

R35

U35

AL35

AA35

AE35

AC35

AN35

AR35

AG35

VSS117

VSS95

AR3

VSS118

VSS

VSS96

AU35

AN3

AM3

AG3

AC3

C31

AH30

V17

J17

G17

E17

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS97

VSS98

VSS99

VSS100

VSS101G9VSS102J9VSS103N9VSS104U9VSS105

VSS106

VSS107

VSS108

VSS109

B36

AF8

W36

AM8

J23

A23

C23

D23

AA9

AE9

4

R264 226_0603_1%

+1.5VS

C17

VSS129

B17

VSS130

AM16

VSS131

W3

VSS132

U3

VSS133

R3

VSS134

D17

VSS135

N3

VSS136

L3

VSS137

J3

VSS138

G3

VSS139

E3

VSS140

AT2

VSS141

F30

VSS142

AR29

VSS143

AJ29

VSS144

AG29

VSS145

AE29

VSS146

AC29

VSS147

AA29

VSS148

W29

VSS149

R29

VSS150

U29

VSS151

N29

VSS152

L29

VSS153

J29

VSS154

C29

VSS155

A29

VSS156

AU15

VSS157

AR15

VSS158

D15

VSS159

B2

VSS160

AR1

VSS161

AN1

VSS162

AE1

VSS163

AA1

VSS164

U1

VSS165

N1

VSS166

J1

VSS167

E1

VSS168

AM28

VSS169

F28

VSS170

AU27

VSS171

AR27

VSS172

AL27

VSS173

F14

VSS174

AR13

VSS175

AJ13

VSS176

J27

VSS177

C27

VSS178

A27

VSS179

E13

VSS180

D13

VSS181

C13

VSS182

B13

VSS183

AM12

VSS184

AK12

VSS185

F26

VSS186

AR25

VSS187

AJ25

VSS188

J25

VSS189

AU11

VSS190

AR11

VSS191

AR37

VSS192

AN37

VSS193

C25

VSS194

AJ37

VSS195

AG37

VSS196

AE37

VSS197

AA37

VSS198

U37

VSS199

AH28

VSS200

AF28

VSS201

AB28

VSS202

V28

VSS203

P28

VSS204

K28

VSS205

K24

VSS206

J37

VSS207

E37

VSS208

C37

VSS209

AT36

VSS210

AH36

VSS211

B15

VSSA_DAC0

C14

VSSA_DAC1

VSS110

1 2

.01U_0402_25V4Z

+CPU_CORE

12

10U_1206_6.3V7K

12

.1U_0402_10V6K

+2.5V

12

C345

.1U_0402_10V6K

12

C360

.1U_0402_10V6K

+1.5VS

12

C326

.1U_0402_10V6K

12

C301

.1U_0402_10V6K

C245

C288

.1U_0402_10V6K

3

.01U_0402_25V4Z

12

C337

C126

NEAR MCH NEAR ICH

FSB DECOUPLING

10U_1206_6.3V7K

12

C246

.1U_0402_10V6K

.1U_0402_10V6K

12

C281

.1U_0402_10V6K

.1U_0402_10V6K

C346

.1U_0402_10V6K

C367

.1U_0402_10V6K

C329

.1U_0402_10V6K

C300

.1U_0402_10V6K

12

12

12

12

12

.1U_0402_10V6K

12

.1U_0402_10V6K

12

12

R312 100_0603_1%

1 2

12

12

C253

12

C279

.1U_0402_10V6K

.1U_0402_10V6K

12

C393

.1U_0402_10V6K

12

C255

.1U_0402_10V6K

12

C284

SYSTEM MEMORY DECOUPLING

.1U_0402_10V6K

12

C348

C378

C349

.1U_0402_10V6K

12

C380

.1U_0402_10V6K

.1U_0402_10V6K

GMCH DECOUPLING

.1U_0402_10V6K

12

C322

C285

C331

.1U_0402_10V6K

12

C269

.1U_0402_10V6K

.1U_0402_10V6K

PLACE NOTE:

CAP PLACE

AT MIDPOINT

OF THE BUS.

.1U_0402_10V6K

12

C254

12

C289

.1U_0402_10V6K

.1U_0402_10V6K

12

C350

.1U_0402_10V6K

12

C379

.1U_0402_10V6K

12

C308

.1U_0402_10V6K

12

C276

12

R309

100_0603_1%

12

C252

12

C370

12

C383

12

C330

12

C275

12

C392

.1U_0402_10V6K

12

12

C359

.1U_0402_10V6K

12

C384

.1U_0402_10V6K

12

C328

.1U_0402_10V6K

12

C260

.1U_0402_10V6K

2

.01U_0402_25V4Z

NEAR MCH

Within 250milWithin 250mil

C250

.1U_0402_10V6K

.1U_0402_10V6K

12

.1U_0402_10V6K

12

.1U_0402_10V6K

12

.1U_0402_10V6K

12

12

C339

C347

.1U_0402_10V6K

C381

.1U_0402_10V6K

C271

.1U_0402_10V6K

C307

.1U_0402_10V6K

12

C125

.01U_0402_25V4Z

NEAR ICH

+CPU_CORE

+CPU_CORE

.1U_0402_10V6K

12

C363

.1U_0402_10V6K

12

C382

.1U_0402_10V6K

12

C278

.1U_0402_10V6K

12

C295

HUB_VSW ING <9,18>

10 mil Trace,

7mil Space

HUB_V REF <9,18>

R245 49.9_0603_1%

1 2

100_0603_1%

NEAR MCH

R246

12

301_0603_1%

R247

150_0603_1%

12

12

12

12

C362

.1U_0402_10V6K

C366

.1U_0402_10V6K

C298

C287

12

12

.1U_0402_10V6K

.1U_0402_10V6K

R244

1 2

.1U_0402_10V6K

C373

.1U_0402_10V6K

C338

.1U_0402_10V6K

12

C256

.1U_0402_10V6K

12

C311

1

10 mil Trace,

7mil Space

12

12

C299

.1U_0402_10V6K

10 mil Trace,

7mil Space

12

C309

.01U_0402_25V4Z

12

C374

.1U_0402_10V6K

12

C354

.1U_0402_10V6K

12

C342

12

C286

MCH_GTLREF <9>

H_XY_SWING <9>

12

C361

12

C365

12

.1U_0402_10V6K

12

.1U_0402_10V6K

C358

.1U_0402_10V6K

12

C280

C283

Dell-Compal Confidential

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENT IAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHO RIZED BY COMPA L ELECTRONIC S, INC. NEITHE R THIS SHEET NO R THE INFORMA TION IT CONT AINS

5

4

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

3

2

Size Document Number Rev

Date: Sheet

Compal Electronics, Inc.

BROOKDALE-GL/PE (3/3)

Abacus/TangII LA-1452

0.2

of

11 43Monday, August 26, 2002

1

Page 12

A

DDR_SDQ4

DDR_SDQ0

DDR_SDQ1

DDR_SDQ5

DDR_SDQ6

1 1

2 2

3 3

4 4

DDR_SDQ2

DDR_SDQ3

DDR_SDQ7

DDR_SDQ9 DDR_DQ9

DDR_SDQ8

DDR_SDQ13 DDR_DQ13

DDR_SDQ12

DDR_SDQ15 DDR_DQ15

DDR_SDQ14 DDR_DQ14

DDR_SDQ11

DDR_SDQ10

DDR_SDQ16

DDR_SDQ20

DDR_SDQ17 DDR_DQ17

DDR_SDQ22 DDR_DQ22

DDR_SDQ18

DDR_SDQ28 DDR_DQ28

DDR_SDQ24

DDR_SDQ25 DDR_DQ25

DDR_SDQ29

DDR_SDQ[0..63]<9>

DDR_SDQS[0..7]<9>

DDR_SMA[0..12]<9,13>

DDR_SDM[0..7]<9>

DDR_SDQ57

DDR_SDQ61

DDR_SDQ56 DDR_DQ56

DDR_SDQ60

DDR_SDQ58

DDR_SDQ63 DDR_DQ63

DDR_SDQS0

DDR_SDQS1

DDR_SDQS2

DDR_SDQS3

RP32 10_0402_4P2R_5%

1 4

2 3

RP42 10_0402_4P2R_5%

1 4

2 3

RP33 10_0402_4P2R_5%

1 4

2 3

RP43 10_0402_4P2R_5%

1 4

2 3

RP20 10_0402_4P2R_5%

1 4

2 3

RP31 10_0402_4P2R_5%

1 4

2 3

RP21 10_0402_4P2R_5%

1 4

2 3

RP40 10_0402_4P2R_5%

1 4

2 3

RP41 10_0402_4P2R_5%

1 4

2 3

RP35 10_0402_4P2R_5%

1 4

2 3

RP44 10_0402_4P2R_5%

1 4

2 3

RP34 10_0402_4P2R_5%

1 4

2 3

RP45 10_0402_4P2R_5%

1 4

2 3

RP38 10_0402_4P2R_5%

1 4

2 3

RP51 10_0402_4P2R_5%

1 4

2 3

RP50 10_0402_4P2R_5%

1 4

2 3

RP36 10_0402_4P2R_5%

1 4

2 3

R119 10_0402_5%

R109 10_0402_5%

R120 10_0402_5%

R127 10_0402_5%

A

DDR_DQ4

DDR_DQ0

DDR_DQ1

DDR_DQ5

DDR_DQ6

DDR_DQ2

DDR_DQ3

DDR_DQ7

DDR_DQ8

DDR_DQ12

DDR_DQ11

DDR_DQ10

DDR_DQ16

DDR_DQ20

DDR_DQ21DDR_SDQ21

DDR_DQ18

DDR_DQ23DDR_SDQ23

DDR_DQ19DDR_SDQ19

DDR_DQ24

DDR_DQ29

DDR_SDQ[0..63]

DDR_SDQS[0..7]

DDR_SMA[0..12]

DDR_SDM[0..7]

DDR_DQ57

DDR_DQ61

DDR_DQ60

DDR_DQ58 DDR_SDQ59 DDR_DQ59

DDR_DQS0

12

DDR_DQS1

12

DDR_DQS2

12

DDR_DQS3

12

B

DDR_SDQ30 DDR_DQ30

DDR_SDQ26 DDR_DQ26

DDR_SDQ31

DDR_SDQ27

DDR_SDM0

DDR_SDM1