Page 1

AMIGA HARDWARE

REFERENCE MANUAL

© 1992 Commodore Business Machines

Amiga 1200 PAL

Page 2

AMIGA HARDWARE REFERENCE MANUAL

TABLE OF CONTENTS

Chapter 1 INTRODUCTION

Components of the Amiga ..................................2

THE MC68000 AND THE AMIGA CUSTOM CHIPS.................2

VCR AND DIRECT CAMERA INTERFACE........................5

PERIPHERALS............................................5

SYSTEM EXPANDABILITY AND ADAPTABILITY..................6

About the Examples........................................7

Some Caveats to Hardware Level Programmers ...............9

Chapter 2 COPROCESSOR HARDWARE ............................13

Introduction.............................................13

ABOUT THIS CHAPTER....................................14

What is a Copper Instruction? ...........................14

The MOVE Instruction ....................................15

The WAIT Instruction.....................................17

HORIZONTAL BEAM POSITION..............................18

VERTICAL BEAM POSITION ...............................18

THE COMPARISON ENABLE BITS............................19

Using the Copper Registers...............................20

LOCATION REGISTERS ...................................20

JUMP STROBE ADDRESS...................................21

CONTROL REGISTER......................................21

Putting Together a Copper Instruction List ..............22

COMPLETE SAMPLE COPPER LIST...........................24

LOOPS AND BRANCHES ...................................25

Starting and Stopping the Copper ........................25

STARTING THE COPPER AFTER RESET.......................25

STOPPING THE COPPER...................................26

Advanced Topics..........................................27

THE SKIP INSTRUCTION..................................27

COPPER LOOPS AND BRANCHES AND COMPARISON ENABLE.......28

USING THE COPPER IN INTERLACED MODE ..................30

USING THE COPPER WITH THE BLITTER.....................31

THE COPPER AND THE 68000..............................31

Summary of Copper Instructions ..........................32

Chapter 3 PLAYIELD HARDWARE................................33

Introduction.............................................33

ABOUT THIS CHAPTER....................................34

PLAYFIELD FEATURES ...................................34

Forming a Basic Playfield ...............................38

HEIGHT AND WIDTH OF THE PLAYFIELD.....................39

BIT-PLANES AND COLOR .................................39

SELECTING HORIZONTAL AND VERTICAL RESOLUTION .........43

ALLOCATING MEMORY FOR BIT-PLANES .....................46

CODING THE BIT-PLANES FOR CORRECT COLORING ...........49

DEFINING THE SIZE OF THE DISPLAY WINDOW ..............50

TELLING THE SYSTEM HOW TO FETCH AND DISPLAY DATA .....53

DISPLAYING AND REDISPLAYING THE PLAYFIELD ............56

ENABLING THE COLOR DISPLAY ...........................56

BASIC PLAYFIELD SUMMARY ..............................57

EXAMPLES OF FORMING BASIC PLAYFIELDS .................59

Forming a Dual-playfield Display ........................62

Page 3

Bit-Plane Assignment in Dual-playfield Mode .............62

COLOR REGISTERS IN DUAL-PLAYFIELD MODE ...............65

DUAL-PLAYFIELD PRIORITY AND CONTROL ..................66

ACTIVATING DUAL-PLAYFIELD MODE .......................67

DUAL PLAYFIELD SUMMARY ...............................67

Bit-planes and Display Windows of All Sizes .............68

WHEN THE BIG PICTURE IS LRGR THAN THE DISPLAY WINDOW .68

MAXIMUM DISPLAY WINDOW SIZE...........................74

Moving (Scrolling) Playfields ...........................75

VERTICAL SCROLLING....................................75

HORIZONTAL SCROLLING .................................77

SCROLLED PLAYFIELD SUMMARY ...........................80

Advanced Topics..........................................81

INTERACTIONS AMONG PLAYFIELDS AND OTHER OBJECTS ......81

HOLD-AND-MODIFY MODE .................................81

FORMING A DISPLAY WITH SEVERAL DIFFERENT PLAYFELD ....84

USING AN EXTERNAL VIDEO SOURCE .......................84

SUMMARY OF PLAYFIELD REGISTERS .......................84

Summary of Color Selection ..............................87

COLOR REGISTER CONTENTS ..............................87

SOME SAMPLE COLOR REGISTER CONTENTS ..................88

COLOR SELECTION IN LOW-RESOLUTION MODE ...............88

COLOR SELECTION IN HOLD-AND-MODIFY MODE ..............90

COLOR SELECTION IN HIGH-RESOLUTION MODE ..............90

Chapter 4 SPRITE HARDWARE .................................93

Introduction.............................................93

ABOUT THIS CHAPTER....................................94

Forming a Sprite ........................................94

SCREEN POSITION ......................................94

SIZE OF SPRITES ......................................97

SHAPE OF SPRITES .....................................97

SPRITE COLOR..........................................98

DESIGNING A SPRITE...................................101

BUILDING THE DATA STRUCTURE..........................101

Displaying a Sprite.....................................106

SELECTING A DMA CHANNEL AND SETTING THE POINTERS.....107

RESETTING THE ADDRESS POINTERS ......................107

SPRITE DISPLAY EXAMPLE...............................108

Moving a Sprite.........................................110

Creating Additional Sprites.............................111

SPRITE PRIORITY......................................112

Reusing Sprite DMA Channels ............................113

Overlapped Sprites......................................115

Attached Sprites .......................................117

Manual Mode ............................................120

Sprite Hardware Details ................................121

Summary of Sprite Registers.............................124

POINTERS.............................................124

CONTROL REGISTERS....................................124

DATA REGISTERS ......................................126

Summary of Sprite Color Registers.......................126

INTERACTIONS AMONG SPRITES AND OTHER OBJECTS ........128

Chapter 5 AUDIO HARDWARE..................................129

Introduction............................................129

INTRODUCING SOUND GENERATION.........................130

THE AMIGA SOUND HARDWARE.............................133

Forming and Playing a Sound ............................134

Page 4

DECIDING WHICH CHANNEL TO USE........................134

CREATING THE WAVEFORM DATA...........................134

TELLING THE SYSTEM ABOUT THE DATA ...................136

SELECTING THE VOLUME ................................136

SELECTING THE DATA OUTPUT RATE.......................137

PLAYING THE WAVEFORM ................................140

STOPPING THE AUDIO DMA...............................141

SUMMARY..............................................142

EXAMPLE..............................................142

Producing Complex Sounds................................143

JOINING TONES .......................................143

PLAYING MULTIPLE TONES AT THE SAME TIME..............145

MODULATING SOUND ....................................145

Producing High-quality Sound............................148

MAKING WAVEFORM TRANSITIONS .........................148

SAMPLING RATE .......................................148

EFFICIENCY...........................................149

NOISE REDUCTION......................................150

ALIASING DISTORTION .................................150

LOW-PASS FILTER .....................................152

Using Direct (Non-DMA) Audio Output ....................153

The Equal-tempered Musical Scale........................154

Decibel Values for Volume Ranges .......................159

The Audio State Machine.................................160

Chapter 6 BLITTER HARDWARE................................163

Introduction............................................163

Memory Layout ..........................................164

DMA Channels............................................164

Function Generator......................................168

DESIGNING THE LF CONTROL BYTE WITH MINTERMS..........169

DESIGNING THE LF CONTROL BYTE WITH VENN DIAGRAMS.....172

Shifts and Masks........................................173

Descending Mode ........................................176

Copying Arbitrary Regions...............................177

Area Fill Mode..........................................178

Blitter Done Flag.......................................180

MULTITASKING AND THE BLITTER ........................181

Interrupt Flag .........................................181

Zero Flag...............................................182

Pipeline Register.......................................182

Line Mode...............................................184

REGISTER SUMMARY FOR LINE MODE.......................186

Blitter Speed ..........................................188

Blitter Operations and System DMA ......................189

Blitter Block Diagram...................................193

Blitter Key Points......................................195

EXAMPLE: ClearMem....................................195

EXAMPLE: SimpleLine..................................197

EXAMPLE: RotateBits..................................199

Chapter 7 SYSTEM CONTROL HARDWARE ........................201

Introduction............................................201

Video Priorities .......................................202

FIXED SPRITE PRIORITES ..............................202

HOW SPRITES ARE GROUPED..............................203

UNDERSTANDING VIDEO PRIORITIES ......................203

SETTING THE PRIORITY CONTROL REGISTER................204

Collision Detection ....................................207

Page 5

HOW COLLISIONS ARE DETERMINED........................207

HOW TO INTERPRET THE COLLISION DATA .................208

HOW COLLISION DETECTION IS CONTROLLED ...............209

Beam Position Detection.................................210

USING THE BEAM POSITION COUNTER......................210

Interrupts .............................................211

NONMASKABLE INTERRUPT ...............................212

MASKABLE INTERRUPTS..................................212

USER INTERFACE TO THE INTERRUPT SYSTEM ..............212

INTERRUPT CONTROL REGISTERS .........................212

SETTING AND CLEARING BITS............................213

DMA Control ............................................217

Processor Access to Chip Memory.........................217

Reset and Early Startup Operation.......................219

Chapter 8 INTERFACE HARDWARE..............................221

Introduction............................................221

Controller Port Interface...............................222

REGISTERS USED WITH THE CONTROLLER PORT..............223

Floppy Disk Controller .....,.............................235

REGISTERS USED BY THE DISK SUBSYSTEM ................236

DISK INTERRUPTS .....................................244

The Keyboard............................................245

HOW THE KEYBOARD DATA IS RECEIVED....................245

TYPE OF DATA RECEIVED................................245

LIMITATIONS OF THE KEYBOARD .........................247

Parallel Input/Output Interface.........................250

Serial Interface .......................................250

INTRODUCTION TO SERIAL CIRCUITRY ....................250

SETTING THE BAUD RATE................................250

SETTING THE RECEIVE MODE ............................251

CONTENTS OF THE RECEIVE DATA REGISTER................251

HOW OUTPUT DATA IS TRANSMITTED.......................253

SPECIFYING THE REGISTER CONTENTS ....................254

Display Output Connections .............................255

Appendix A Register Summary-Alphabetical Order............257

Appendix B Register Summary-Address Order.................281

Appendix C Custom Chip Pin Allocation List................289

Appendix D System Memory Map..............................293

Appendix E Interfaces ....................................295

Appendix F Complex Interface Adapters.....................317

8520 Complex Interface Adaptor (CIA) Chips..............317

Chip Register Map.......................................319

Register Functional Description.........................320

I/O PORTS (PRA, PRB, DDRA, DDRB).....................320

HANDSHAKING..........................................320

INTERVAL TIMERS (TIMER A, TIMER B)...................320

INPUT MODES..........................................322

BIT NAMES on READ-Register...........................322

BIT NAMES on WRITE-Register .........................322

Time of Day Clock.......................................323

BIT NAMES for WRITE TIME/ALARM or READ TIME..........323

Serial Shift Register (SDR).............................324

Page 6

INPUT MODE ..........................................324

OUTPUT MODE .........................................324

BIDIRECTIONAL FEATURE ...............................325

Interrupt Control Register (ICR) .......................325

READ INTERRUPT CONTROL REGISTER .....................326

WRITE INTERRUPT CONTROL MASK ........................326

Control Registers ......................................327

CONTROL REGISTER A ..................................327

BIT MAP OF REGISTER CRA .............................328

BIT MAP OF REGISTER CRB .............................329

Port Signal Assignments.................................329

Hardware Connection Details.............................332

INTERFACE SIGNALS ...................................332

Appendix G AUTOCONFIG ....................................335

Debugging AUTOCONFIG Boards.............................336

Address Specification Table.............................337

Appendix H Keyboard.......................................343

Keyboard Communications.................................344

Keycodes................................................345

"CAPS LOCK" Key.........................................345

"Out-of-Sync" Condition.................................346

Power-Up Sequence ......................................346

Reset Warning...........................................348

Hard Reset..............................................348

Special Codes...........................................349

Matrix Table............................................350

Appendix I External Disk Connector Interface Spec. .......353

General.................................................353

Summary Table...........................................354

Signals When Driving a Disk.............................355

Device I.D..............................................357

Appendix J Hardware Example Include File..................359

Glossary .................................................365

Index ....................................................373

Page 7

LIST OF FIGURES

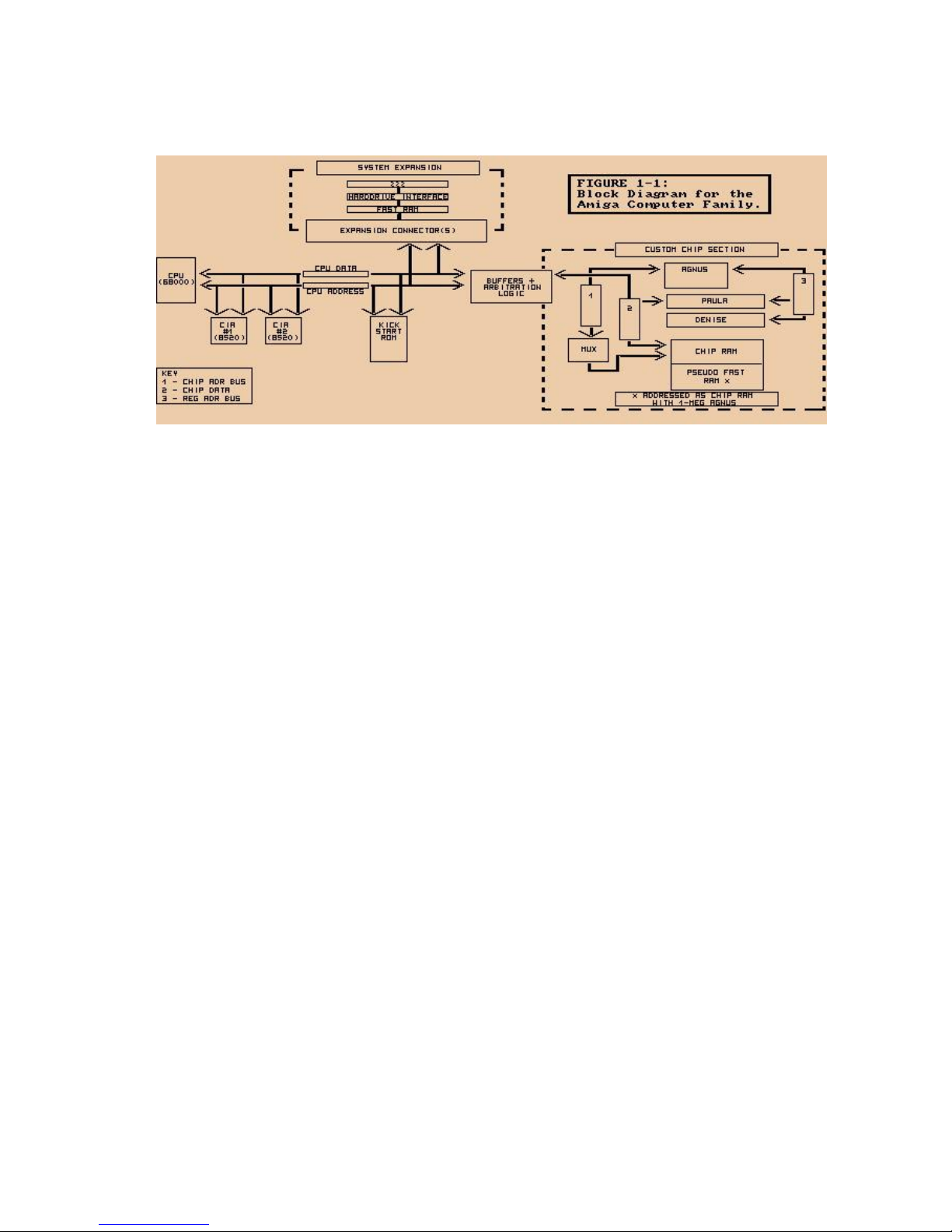

Figure 1-1 Block Diagram for the Amiga Computer Family............11

Figure 2-1 Interlaced Bit-Plane in RAM............................30

Figure 3-1 How the Video Display Picture Is Produced..............34

Figure 3-2 What Is a Pixel?.......................................35

Figure 3-3 How Bit-planes Select a Color..........................37

Figure 3-4 Significance of Bit-Plane Data in Selecting Colors.....38

Figure 3-5 Interlacing............................................44

Figure 3-6 Effect of Interlaced Mode on Edges of Objects..........44

Figure 3-7 Memory Organization for a Basic Bit-Plane..............48

Figure 3-8 Combining Bit-planes...................................50

Figure 3-9 Positioning the On-screen Display......................51

Figure 3-10 Data Fetched for the First Line When Modulo=0 ........54

Figure 3-11 Data Fetched for the Second Line When Modulo=0........55

Figure 3-12 A Dual-playfield Display..............................63

Figure 3-13 How Bit-Planes Are Assigned to Dual Playfields........64

Figure 3-14 Memory Picture Larger than the Display................69

Figure 3-15 Data Fetch for the First Line When Modulo=40..........69

Figure 3-16 Data Fetch for the Second Line When Modulo=40.........70

Figure 3-17 Data Layout for First Line-Right Half of Big Picture..70

Figure 3-18 Data Layout for Second Line-Right Half of Big Picture.70

Figure 3-19 Display Window Horizontal Starting Position ..........72

Figure 3-20 Display Window Vertical Starting Position ............72

Figure 3-21 Display Window Horizontal Stopping Position .........73

Figure 3-22 Display Window Vertical Stopping Position ............74

Figure 3-23 Vertical Scrolling....................................76

Figure 3-24 Horizontal Scrolling .................................78

Figure 3-25 Memory Picture Larger than the Display Window ........79

Figure 3-26 Data for Line 1 - Horizontal Scrolling ...............79

Figure 3-27 Data for Line 2 - Horizontal Scrolling ...............79

Figure 4-1 Defining Sprite On-screen Position.....................95

Figure 4-2 Position of Sprites ...................................96

Figure 4-3 Shape of Spaceship.....................................97

Figure 4-4 Sprite with Spaceship Shape Defined ...................98

Figure 4-5 Sprite Color Definition ...............................99

Figure 4-6 Color Register Assignments ...........................100

Figure 4-7 Data Structure Layout ................................103

Figure 4-8 Sprite Priority ......................................112

Figure 4-9 Typical Example of Sprite Reuse ......................113

Figure 4-10 Typical Data Structure for Sprite Re-use ............114

Figure 4-11 Overlapping Sprites (Not Attached) ..................116

Figure 4-12 Placing Sprites Next to Each Other ..................117

Figure 4-13 Sprite Control Circuitry ............................122

Figure 5-1 Sine Waveform ........................................131

Figure 5-2 Digitized Amplitude Values ...........................133

Figure 5-3 Example Sine Wave ....................................139

Figure 5-4 Waveform with Multiple Cycles ........................149

Figure 5-5 Frequency Domain Plot of Low-Pass Filter .............151

Figure 5-6 Noise-free Output (No Aliasing Distortion) ...........151

Figure 5-7 Some Aliasing Distortion .............................152

Figure 5-8 Audio State Diagram ..................................162

Figure 6-1 How Images are Stored in Memory ......................165

Figure 6-2 BLTxP and BLTxMOD calculations .......................167

Figure 6-3 Blitter Minterm Venn Diagram .........................172

Figure 6-4 Extracting a Range of Columns ........................175

Figure 6-5 Use of the FCI Bit - Bit Is a 0 ......................179

Figure 6-6 Use of the FCI Bit - Bit Is a 1 ......................179

Figure 6-7 Single-Point Vertex Example ..........................180

Figure 6-8 Octants for Line Drawing .............................184

Page 8

Figure 6-9 DMA Time Slot Allocation .............................190

Figure 6-10 Norma 68000 Cycle ...................................191

Figure 6-11 Time Slots Used by a Six Bit Plane Display ..........192

Figure 6-12 Time Slots Used by a High Resolution Display ........192

Figure 6-13 Blitter Block Diagram ...............................194

Figure 7-1 Inter-Sprite Fixed Priorities ........................202

Figure 7-2 Analogy for Video Priority ...........................203

Figure 7-3 Sprite playfield Priority ............................206

Figure 7-4 Interrupt Priorities .................................216

Figure 8-1 Controller Plug and Computer Connector ...............222

Figure 8-2 Mouse Quadrature .....................................224

Figure 8-3 Joystick to Counter Connections ......................227

Figure 8-4 Typical Paddle Wiring Diagram ........................229

Figure 8-5 Effects of Resistance on Charging Rate ...............230

Figure 8-6 Potentiometer Charging Circuit .......................231

Figure 8-7 Chinon Timing Diagram ................................236

Figure 8-8 Chinon Timing Diagram (cont.) ........................237

Figure 8-9 The A1000 Keyboard, Showing Keycodes in Hex ..........249

Figure 8-10 The A500/2000 Keyboard, Keycodes in Hex .............249

Figure 8-11 Starting Appearance of SERDAT and Shift Reg .........254

Figure 8-12 Ending Appearance of Shift Register..................254

Figure G-1 How to read the Address Specification Table ..........338

Page 9

LIST OF TABLES

Table 2-1 Interrupting the 68000..................................31

Table 2-2 Copper Instruction Summary .............................32

Table 3-1 Colors in a Single Playfield............................39

Table 3-2 Portion of the Color Table .............................40

Table 3-3 Contents of the Color Registers ........................41

Table 3-4 Sample Color Register Contents .........................41

Table 3-5 Setting the Number of Bit-Planes........................42

Table 3-6 Lines in a Normal Playfield.............................43

Table 3-7 Playfield Memory Requirements, NTSC.....................46

Table 3-8 Playfield Memory Requirements, PAL .....................47

Table 3-9 DIWSTRT AND DIWSTOP Summary.............................53

Table 3-10 Playfield 1 Color Registers-Low-resolution Mode........65

Table 3-11 Playfield 2 Color Registers-Low-resolution Mode........65

Table 3-12 Playfields 1 & 2 Color Registers High-res Mode.........66

Table 3-13 Maximum Allowable Vertical Screen Video................74

Table 3-14 Maximum Allowable Horizontal Screen Video .............75

Table 3-15 Color Register Contents................................87

Table 3-16 Some Register Values and Resulting Colors..............88

Table 3-17 Low-resolution Color Selection ........................89

Table 3-18 Color Selection in Hold-and-modify Mode................90

Table 3-19 High-resolution Color Selection........................91

Table 4-1 Sprite Data Structure..................................102

Table 4-2 Sprite Color Registers ................................105

Table 4-3 Color Registers for Sprite Pairs.......................112

Table 4-4 Data Words for First Line of Spaceship Sprite..........118

Table 4-5 Color Registers in Attached Sprites ...................119

Table 4-6 Color Registers for Single Sprites.....................127

Table 4-7 Color Registers for Attached Sprites...................128

Table 5-1 Sample Audio Data Set for Channel 0 ...................135

Table 5-2 Volume Values .........................................137

Table 5-3 DMA and Audio Channel Enable Bits......................141

Table 5-4 Data Interpretation in Attach Mode.....................146

Table 5-5 Channel Attachment for Modulation......................147

Table 5-6 Sampling Rate and Frequency Relationship...............153

Table 5-7 Equal-tempered Octave for a 16 Byte Sample.............154

Table 5-8 Five Octave Even-tempered Scale........................156

Table 5-9 Decibel Values and Volume Ranges.......................159

Table 6-1 Table of Common Minterm Values.........................171

Table 6-2 Typical Blitter Cycle Sequence.........................183

Table 6-3 BLTCON1 Code Bits for Octant Line Drawing..............185

Table 7-1 Bits in BPLCON2........................................204

Table 7-2 Prirty of Plyflds Based on Values of Bits PF1P2-PF1P0..205

Table 7-3 CLXDAT Bits............................................208

Table 7-4 CLXCON Bits ...........................................209

Table 7-5 Contents of the Beam Position Counter..................211

Table 7-6 Contents of DMA Register...............................218

Table 8-1 Typical Controller Connections ........................223

Table 8-2 Determining the Direction of the Mouse.................226

Table 8-3 Interpreting Data from JOY0DAT and JOY1DAT.............228

Table 8-4 POTGO ($DFF034) and POTINP ($DFF016) Registers.........234

Table 8-5 Disk Subsystem ........................................238

Table 8-6 DSKLEN Register ($DFF024)..............................240

Table 8-7 DSKBYTR Register.......................................242

Table 8-8 ADKCON and ADKCONR Register............................243

Table 8-9 SERDATR / ADKCON Registers.............................252

Table G-1 Address Specification Table............................338

Page 10

CHAPTER 1

INTRODUCTION

The Amiga family of computers consists of several models, each of which has been

designed on the same premise to provide the user with a low cost computer that features

high cost performance. The Amiga does this through the use of custom silicon hardware

that yields advanced graphics and sound features.

There are three distinct models that make up the Amiga computer family: the A500,

A1000, and A2000. Though the models differ in price and features, they have a common

hardware nucleus that makes them software compatible with one another. This chapter

describes the Amiga's hardware components and gives a brief overview of its graphics and

sound features.

- Introduction 1 -

Page 11

COMPONENTS OF THE AMIGA

These are the hardware components of the Amiga:

o Motorola MC68000 16/32 bit main processor. The Amiga also supports the 68010,

68020, and 68030 processors as an option.

o 512K bytes of internal RAM, expandable to 1 MB on the A500 and A2000.

o 256K bytes of ROM containing a real time, multitasking operating system with sound,

graphics, and animation support routines.

o Built-in 3.5 inch double sided disk drive.

o Expansion disk port for connecting up to three additional disk drives, which may be

either 3.5 inch or 5.25 inch, double sided.

o Fully programmable RS-232-C serial port.

o Fully programmable parallel port.

o Two button opto-mechanical mouse.

o Two reconfigurable controller ports (for mice, joysticks, light pens, paddles, or custom

controllers).

o A professional keyboard with numeric keypad, 10 function keys, and cursor keys. A

variety of international keyboards are also supported.

o Ports for simultaneous composite video, and analog or digital RGB output.

o Ports for left and right stereo audio from four special purpose audio channels.

o Expansion options that allow you to add RAM, additional disk drives (floppy or hard),

peripherals, or co-processors.

THE MC6X000 AND THE AMIGA CUSTOM CHIPS

The Motorola 68000 is a 16/32 bit microprocessor. The system clock speed for NTSC

Amiga’s is 7.15909 megahertz (PAL 7.09379 MHz). These speeds may vary when using an

external system clock, such as from a genlock. The 68000 has an address space of 16

megabytes. In the Amiga, the 68000 can address over 8 megabytes of continuous random

access memory (RAM).

- 2 Introduction -

Page 12

In addition to the 68000, the Amiga contains special purpose hardware known as the

"custom chips" that greatly enhance system performance. The term "custom chips" refers

to the 3 integrated circuits which were designed specifically for the Amiga computer.

These three custom chips (called Agnus, Paula, and Denise) each contain the logic to

handle a specific set of tasks, such as video, sound, direct memory access (DMA),

or graphics.

Among other functions, the custom chips provide the following:

Bitplane generated, high resolution graphics capable of supporting both PAL and

NTSC video standards.

o On NTSC systems the Amiga typically produces a 320 by 200 non-interlaced

or 320 by 400 interlaced display in 32 colors and a 640 by 200 noninterlaced or 640 by 400 interlaced display in 16 colors.

o On PAL systems, the Amiga typically produces a 320 by 256 non-interlaced

or 320 by 512 interlaced display in 32 colors, and a 640 by 256 noninterlaced or 640 by 512 interlaced display in 16 colors.

Additional video modes allow for the display of up to 4,096 colors on screen

simultaneously (hold-and-modify) or provide for larger, higher resolution displays

(overscan).

A custom display co-processor that allows changes to most of the special purpose

registers in synchronization with the position of the video beam. This allows such

special effects as mid-screen changes to the color palette, splitting the screen into

multiple horizontal slices each having different video resolutions and color depths,

beam synchronized interrupt generation for the 68000 and more. The co-processor

can trigger many times per screen, in the middle of lines, and at the beginning or

during the blanking interval. The co-processor itself can directly affect most of the

registers in the other custom chips, freeing the 68000 for general computing tasks.

32 system color registers, each of which contains a twelve bit number as four bits

of RED, four bits of GREEN, and four bits of BLUE intensity information. This allows

a system color palette of 4,096 different choices of color for each register.

Eight reusable 16 bit wide sprites with up to 15 color choices per sprite pixel (when

sprites arc paired). A sprite is an easily movable graphics object whose display is

entirely independent of the background (called a playfield); sprites can be

displayed over or under this background. A sprite is 16 low resolution pixels wide

and an arbitrary number of lines tall. After producing the last line of a sprite on the

screen, a sprite DMA channel may be used to produce yet another sprite image

elsewhere on screen (with at least one horizontal line between each reuse of a

sprite processor). Thus, many small sprites can be produced by simply reusing the

sprite processors appropriately.

Dynamically controllable inter-object priority, with collision detection. This means

that the system can dynamically control the video priority between the sprite

objects and the bitplane backgrounds (playfields). You can control which object or

objects appear over or under the background at any time.

Page 13

Additionally, you can use system hardware to detect collisions between objects and have

your program react to such collisions.

o Custom bit blitter used for high speed data movement, adaptable to bitplane animation.

The blitter has been designed to efficiently retrieve data from up to three sources,

combine the data in one of 256 different possible ways, and optionally store the combined

data in a destination area. This is one of the situations where the 68000 gives up memory

cycles to a DMA channel that can do the job more efficiently (see below). The bit blitter, in

a special mode, draws patterned lines into rectangularly organized memory regions at a

speed of about 1 million dots per second; and it can efficiently handle area fill.

o Audio consisting of four digital channels with independently programmable volume and

sampling rate. The audio channels retrieve their control and data via direct memory

access. Once started, each channel can automatically play a specified waveform without

further processor interaction. Two channels are directed into each of the two stereo audio

outputs. The audio channels may be linked together to provide amplitude or frequency

modulation or both forms of modulation simultaneously.

o DMA controlled floppy disk read and write on a full track basis. This means that the

built-in disk can read over 5600 bytes of data in a single disk revolution (11 sectors of

512 bytes each).

The internal memory shared by the custom chips and the 68000 CPU is also called "chip

memory". The original custom chips in the Amiga were designed to be able to physically

access up to 512K bytes of shared memory. The new version of the Agnus custom chip

was created which allows the graphics and audio hardware to access up to a full megabyte

of memory.

The Amiga 500 and 2000 models were designed to be able to accept the new Agnus

custom chip, called "Fat Agnus", due to its square shape. Hence, the A500 and A2000

have allocated a chip memory space of 1 MB. This entire 1 MB space is subject to the

arbitration logic that controls the CPU and custom chip accesses. On the A1000, only the

first 512K bytes of memory space is shared, chip memory.

These custom chips and the 68000 share memory on a fully interleaved basis. Since the

68000 only needs to access the memory bus during each alternate clock cycle in order to

run full speed, the rest of the time the memory bus is free for other activities. The custom

chips use the memory bus during these free cycles, effectively allowing the 68000 to run

at full rated speed most of the time. We say "most of the time" because there are some

occasions when the special purpose hardware steals memory cycles from the 68000, but

with good reason. Specifically, the coprocessor and the data moving DMA channel called

the blitter can each steal time from the 68000 for jobs they can do better than the 68000.

Thus, the system DMA channels are designed with maximum performance in mind. The

job to be done is performed by the most efficient hardware element available. Even when

such cycle stealing occurs, it only blocks the 68000's access to the internal, shared

memory. When using ROM or external memory, the 68000 always runs at full speed.

- 4 Introduction -

Page 14

Another primary feature of the Amiga hardware is the ability to dynamically control which

part of the chip memory is used for the background display. audio, and sprites. The Amiga

is not limited to a small, specific area of RAM for a frame buffer. Instead, the system

allows display bitplanes, sprite processor control lists, coprocessor instruction lists, or

audio channel control lists to be located anywhere within chip memory.

This same region of memory can be accessed by the bit blitter. This means, for example,

that the user can store partial images at scattered areas of chip memory and use these

images for animation effects by rapidly replacing on screen material while saving and

restoring background images. In fact, the Amiga includes firmware support for display

definition and control as well as support for animated objects embedded within playfields.

VCR AND DIRECT CAMERA INTERFACE

In addition to the connectors for monochrome composite, and analog or digital RGB

monitors, the Amiga can be expanded to include a VCR or camera interface. This system

is capable of synchronizing with an external video source and replacing the system

background color with the external image. This allows development of fully integrated

video images with computer generated graphics. Laser disk input is accepted in the same

manner.

PERIPHERALS

Floppy disk storage is provided by a built in, 3.5 inch floppy disk drive. Disks are 80 track,

double sided, and formatted as 11 sectors per track, 512 bytes per sector (over 900,000

bytes per disk). The disk controller can read and write 320/360K IBM PC (MS-DOS)

formatted 3.5 or 5.25 inch disks, and 640/720K IBM PC (MS-DOS) formatted 3.5 inch

disks. External 3.5 inch or 5.25 inch disk drives can be added to the system through the

expansion connector. Circuitry for some of the peripherals resides on Paula. Other chips

handle various signals not specifically assigned to any of the custom chips, including

modem controls, disk status sensing, disk motor and stepping controls, ROM enable,

parallel input/output interface, and keyboard interface.

The Amiga includes a standard RS-232-C serial port for external serial input/output

devices.

A keyboard with numeric keypad, cursor controls and 10 function keys is included in the

base system. For maximum flexibility, both key-down and key-up signals are sent. The

Amiga also supports a variety of international keyboards. Many other types of controllers

can be attached through the two controller ports on the base unit. You can use a mouse,

joystick, keypad, track-ball, light pen, or steering wheel controller in either of the

controller ports.

- Introduction 5 -

Page 15

SYSTEM EXPANDABILITY AND ADAPTABILITY

New peripheral devices may be easily added to all Amiga models. These devices are

automatically recognized and used by system software through a well defined, well

documented linking procedure called AUTOCONFIG.

On the A500 and A1000 models, peripheral devices can be added to the Amiga's 86 pin

expansion connector, including additional external RAM. Extra disk units may be added

from a connector at the rear of the unit.

The A2000 model provides the user with the same features as the A500 or A1000, but

with the added convenience of simple and extensive expandability. The 86 pin, external

connector of the A1000 and A500 is not externally accessible on the A2000. Instead, the

A2000 contains 7 internal slots that allow many types of expansion boards to be quickly

and easily added inside the machine. These expansion boards may contain coprocessors,

RAM expansion, hard disk controllers, video or I/O ports. There is also room to mount

both floppy and hard disks internally. The A2000 also supports the special Bridgeboard

coprocessor card. This provides a complete IBM PC on a card and allows the Amiga to run

MS-DOS compatible software, while simultaneously running native Amiga software.

- 6 Introduction -

Page 16

ABOUT THE EXAMPLES

The examples in this book all demonstrate direct manipulation of the Amiga hardware.

However, as a general rule, it is not permissible to directly access the hardware in the

Amiga unless your software either has full control of the system, or has arbitrated via the

OS for exclusive access to the particular parts of the hardware you wish to control.

Almost all of the hardware discussed in this manual, most notably the Blitter, Copper,

playfield, sprite, CIA, trackdisk, and system control hardware, are in either exclusive or

arbitrated use by portions of the Amiga OS in any running Amiga system. Additional

hardware, such as the audio, parallel, and serial hardware, may be in use by applications

which have allocated their use through the system software.

Before attempting to directly manipulate any part of the hardware in the Amiga's

multitasking environment, your application must first be granted exclusive access to that

hardware by the operating system library, device, or resource which arbitrates its

ownership. The operating system functions for requesting and receiving control of parts of

the Amiga hardware are varied and are not within the scope of this manual. Generally

such functions, when available, will be found in the library, device, or resource which

manages that portion of the Amiga hardware in the multitasking environment. The

following list will help you to find the appropriate operating system functions or

mechanisms which may exist for arbitrated access to the hardware discussed in this

manual.

Copper, Playfield, Sprite, Blitter - graphics.library

Audio - audio.device

Trackdisk - trackdisk.device, disk.resource

Serial - serial.device, misc.resource

Parallel - parallel.device, cia.resource, misc.resource

Gameport - input.device, gameport.device, potgo.resource

Keyboard - input.device, keyboard.device

System Control - graphics.library, exec.library (interrupts)

Most of the examples in this book use the hw_examples.i file (see Appendix J) to define

the chip register names. hw_examples.i uses the system include file hardware/custom.i to

define the chip structures and relative addresses. The values defined in hardware/custom.i

and how examples.i are offsets from the base chip register address space. In general, this

base value is defined as _custom and is resolved during linking from amiga.lib. (_ciaa and

_ciab are also resolved in this way.)

Normally, the base address is loaded into an address register and the offsets given by

hardware/custom.i and hw_examples.i are then used to address the correct register.

- Introduction 7 -

Page 17

NOTE

The offset values of the registers are the addresses that the Copper must use to talk to

the registers. For example, in assembler:

INCLUDE "exec/types.i"

INCLUDE "hardware/custom.i"

XREF custom ; External reference

Start: lea _custom,a0 ; Use a0 as base register

move.w #$7FFF,intena(a0) ; Disable all interrupts

In C, you would use the structure definitions in hardware/custom.h For

example:

#include "exec/types.h"

#include "hardware/custom.h"

extern struct Custom custom;

/* You may need to define the above external as

** extern struct Custom far custom;

** Check you compiler manual.

*/

main()

{

custom.intena = 0x7FFF; /* Disable all interrupts */

}

The Amiga hardware include files are generally supplied with your compiler or assembler.

Listings of the hardware include files may also be found in the Addison-Wesley Amiga ROM

Kernel Manual "Includes and Autodocs". Generally, the include file label names are very

similar to the equivalent hardware register list names with the following typical

differences.

o Address registers which have low word and high word components are generally listed

as two word sized registers in the hardware register list, with each register name

containing either a suffix or embedded "L" or "H" for low and high. The include file label

for the same register will generally treat the whole register as a longword (32 bit)

register,

and therefore will not contain the "L" or "H" distinction.

o Related sequential registers which are given individual names with number suffixes in

the hardware register list, are generally referenced from a single base register definition

in the include files. For example, the color registers in the hardware list (COLOR00,

COLOR01, etc.) would be referenced from the "color" label defined in "hardware/custom.i"

(color+0, color+2, etc.).

o Examples of how to define the correct register offset can be found in the hw_examples.i

file listed in Appendix J.

- 8 Introduction -

Page 18

SOME CAVEATS TO HARDWARE LEVEL PROGRAMMERS

The Amiga is available in a variety of models and configurations, and is further diversified

by a wealth of add-on expansion peripherals and processor replacements. In addition,

even standard Amiga hardware such as the keyboard and floppy disks, are supplied by a

number of different manufacturers and may vary subtly in both their timing and in their

ability to perform outside of their specified capabilities.

The Amiga operating system is designed to operate the Amiga hardware within spec,

adapt to different hardware and RAM configurations, and generally provide upward

compatibility with any future hardware upgrades or "add ons" envisioned by the

designers. For maximum upward compatibility, it is strongly suggested that programmers

deal with the hardware through the commands and functions provided by the Amiga

operating system.

If you find it necessary to program the hardware directly, then it is your responsibility to

write code which will work properly on various models and configurations. Be sure to

properly request and gain control of the hardware you are manipulating, and be especially

careful in the following areas:

Do not jump into ROM. Beware of any example code that calls routines in the $F80000 to

$FFFFFF range. These are ROM addresses and the ROM routines WILL move with every OS

revision. The only supported interface to system ROM code is through the provided library,

device, and resource calls.

Do not modify or depend on the format of any private system structures. This includes the

poking of copper lists, memory lists, and library bases.

Do not depend on any address containing any particular system structure or type of

memory. The system modules dynamically allocate their memory space when they are

initialized. The addresses of system structures and buffers differ with every OS, every

model, and every configuration, as does the amount of free memory and system stack

usage. Remember that all data for direct custom chip access must be in CHIP RAM. This

includes bit images (bitplanes, sprites, etc), sound samples, trackdisk buffers, and copper

lists.

Do not write spurious data to, or interpret undefined data from currently unused bits or

addresses in the custom chip space. All undefined bits must be set to zero for writes, and

ignored on reads.

Do not write data past the current end of custom chip space. Custom chips may be

extended or enhanced to provide additional registers, or to use currently undefined bits in

existing registers.

All custom chip registers are read only OR write only. Do not read write only registers, and

do not write to read only registers.

- Introduction 9 -

Page 19

Do not read, write, or use any currently undefined address ranges. The current and future

usage of such areas is reserved by Commodore and is definitely subject to change.

If you are using the system libraries, devices, and resources, you must follow the defined

interface. Assembler programmers (and compiler writers) must enter functions through

the library base jump Tables, with arguments passed as longs and library base address in

A6. Results returned in D0 must be tested, and the contents of D0-D1/A0-A1 must be

assumed gone after a system call.

NOTE

The assembler TAS instruction should not be used in any Amiga program. The TAS

instruction assumes an indivisible read-modify-write but this can be defeated by system

DMA. Instead use BSET and BCLR. These instructions perform a test and set operation

which cannot be interrupted.

TAS is only needed for a multiple CPU system. On a single CPU system, the BSET and

BCLR instructions are identical to TAS, as the 68000 does not interrupt instructions in the

middle. BSET and BCLR first test, then set bits.

Do not use assembler instructions which are privileged on any 68000 family processor,

most notably MOVE SR,<ea> which is privileged on the 68010/20/30. Use the Exec

function GetCC() instead of MOVE SR, or use the appropriate non-privileged instruction as

shown below:

CPU User Mode Super Mode

68000 MOVE SR,<ea> MOVE SR,<ea>

68010/20/30 MOVE CCR,<ea> MOVE SR,<ea>

All addresses must be 32 bits. Do not use the upper 8 bits for other data, and do not use

signed variables or signed math for addresses. Do not execute code on your stack or use

self-modifying code since such code can be defeated by the caching capabilities of some

68xxx processors. And never use processor or clock speed dependent software loops for

timing delays. See Appendix F for information on using an 8520 timer for delays.

NOTE

When strobing any register which responds to either a read or a write, (for example

copjmp2) be sure to use a MOVE.W #$00, not CLR.W. The CLR instruction causes a read

and a clear (two accesses) on a 68000, but only a single access on 68020 and above. This

will give different results on different processors.

If you are programming at the hardware level, you must follow hardware interfacing

specifications. All hardware is NOT the same. Do not assume that low level hacks for

speed or copy protection will work on all drives, or all keyboards, or all systems, or future

systems. Test your software on many different systems, with different processors, OS,

hardware, and RAM configurations.

- 10 Introduction -

Page 20

Figure 1-1: Block Diagram for the Amiga Computer Family.

- Introduction 11 -

Page 21

- 12 Introduction -

Page 22

Chapter 2

COPROCESSOR HARDWARE

INTRODUCTION

The Copper is a general purpose coprocessor that resides in one of the Amiga's custom

chips. It retrieves is instructions via direct memory access (DMA). The Copper can control

nearly the entire graphics system, freeing the 68000 to execute program logic; it can also

directly affect the contents of most of the chip control registers. It is a very powerful tool

for directing mid-screen modifications in graphics displays and for directing the register

changes that must occur during the vertical blanking periods. Among other things, it can

control register updates, reposition sprites, change the color palette, update the audio

channels, and control the blitter.

- Coprocessor Hardware 13 -

Page 23

One of the features of the Copper is its ability to WAIT for a specific video beam position,

then MOVE data into a system register. During the WAIT period, the Copper examines the

contents of the video beam position counter directly. This means that while the Copper is

waiting for the beam to reach a specific position, it does not use the memory bus at all.

Therefore, the bus is freed for use by the other DMA channels or by the 68000.

When the WAIT condition has been satisfied, the Copper steals memory cycles from either

the blitter or the 68000 to move the specified data into the selected special-purpose

register.

The Copper is a two-cycle processor that requests the bus only during odd-numbered

memory cycles. This prevents collision with audio, disk, refresh, sprites, and most lowresolution display DMA access, all of which use only the even-numbered memory cycles.

The Copper, therefore, needs priority over only the 68000 and the blitter (the DMA

channel that handles animation, line drawing, and polygon filling).

As with all the other DMA channels in the Amiga system, the Copper can retrieve its

instructions only from the chip RAM area of system memory.

ABOUT THIS CHAPTER

In this chapter, you will learn how to use the special Copper instruction set to organize

mid-screen register value modifications and pointer register set-up during the vertical

blanking interval. The chapter shows how to organize Copper instructions into Copper

lists, how to use Copper lists in interlaced mode, and how to use the Copper with the

blitter. The Copper is discussed in this chapter in a general fashion. The chapters that deal

with playfields, sprites, audio, and the blitter contain more specific suggestions for using

the Copper.

WHAT IS A COPPER INSTRUCTION?

As a coprocessor, the Copper adds its own instruction set to the instructions already

provided by the 68000. The Copper has only three instructions, but you can do a lot with

them:

o WAIT for a specific screen position specified as x and y co-ordinates.

o MOVE n immediate data value into one of the special-purpose registers.

o SKIP the next instruction if the video beam has already reached a specified screen

position.

- 14 Coprocessor Hardware -

Page 24

All Copper instructions consist of two 16-bit words in sequential memory locations. Each

time the Copper fetches an instruction, it fetches both words. The MOVE and SKIP

instructions require two memory cycles and two instruction words. Because only the odd

memory cycles are requested by the Copper, four memory cycle times are required per

instruction. The WAIT instruction requires three memory cycles and six memory cycle

times; it takes one extra memory cycle to wake up.

Although the Copper can directly affect only machine registers, it can affect the memory

by setting up a blitter operation. More information about how to use the Copper in

controlling the blitter can be found in the sections called "Control Register" and "Using the

Copper with the Blitter."

The WAIT and MOVE instructions are described below. The SKIP instruction is described in

the "Advanced Topics" section.

THE MOVE INSTRUCTION

The MOVE instruction transfers data from RAM to a register destination. The transferred

data is contained in the second word of the MOVE instruction; the first word contains the

address of the destination register. This procedure is shown in detail in the section called

"Summary of Copper Instructions."

FIRST INSTRUCTION WORD (IR1)

Bit 0 Always set to 0.

Bits 8 - 1 Register destination address (DA8-1).

Bits 15 - 9 Not used, but should be set to 0.

SECOND INSTRUCTION WORD (IR2)

Bits 15 - 0 16 bits of data to be transferred (moved) to the register

destination.

- Coprocessor Hardware 15 -

Page 25

The Copper can store data into the following registers:

o Any register whose address is $20 or above.

o Any register whose address is between $10 and $20 if the Copper danger bit is a 1. The

Copper danger bit is in the Copper's control register, COPCON, which is described in the

"Control Register" section.

o The Copper cannot write into any register whose address is lower than $10.

Appendix B contains all of the machine register addresses.

The following example MOVE instructions point bit-plane pointer 1 at $21000 and bitplane pointer 2 at S25000.2

DC.W $00E0,$0002 ;Move $0002 to register $0E0 (BPL1PTH)

DC.W $00E2,$1000 ;Move $1000 to register $0E2 (BPL1PTL)

DC.W $00E4,$0002 ;Move $0002 to register $0E4 (BPL2PTH)

DC.W $00E6,$5000 ;Move $5000 to register $0E6 (BPL2PTL)

Normally, the appropriate assembler ".i" files are included so that names, rather than

addresses, may be used for referencing hardware registers. It is strongly recommended

that you reference all hardware addresses via their defined names in the system include

files. This will allow you to more easily adapt your software to take advantage of future

hardware or enhancements. For example:

INCLUDE "hardware/custom.i"

DC.W bplpt+$00,$0002 ;Move $0002 into register $0E0 (BPLlPTH)

DC.W bplpt+$02,$1000 ;Move $1000 into register $0E2 (BPLlPTL)

DC.W bplpt+$04,$0002 ;Move $0002 into regi3ter $0E4 (PL2PTH)

DC.W bplpt+$06,$5000 ;Move $5000 into register $0E6 (BPL2PTL)

For use in the hardware manual examples, we have made a special include file (see

Appendix J) that defines all of the hardware register names based off of the

"hardware/custom.i" file. This was done to make the examples easier to read from a

hardware point of view. Most of the examples in this manual are here to help explain the

hardware and are, in most cases, not useful without modification and a good deal of

additional code.

1 Hexadecimal numbers are distinguished from decimal numbers by the $ prefix.

2 All sample code segments are in assembly language.

- 16 Coprocessor Hardware -

Page 26

THE WAIT INSTRUCTION

The WAIT instruction causes the Copper to wait until the video beam counters are equal to

(or greater than) the coordinates specified in the instruction. While waiting, the Copper is

off the bus and not using memory cycles.

The first instruction word contains the vertical and horizontal coordinates of the beam

position. The second word contains enable bits that are used to form a "mask" that tells

the system which bits of the beam position to use in making the comparison.

FIRST INSTRUCTION WORD (IR1)

Bit 0 Always set to 1.

Bits 15 - 8 Vertical beam position (called VP).

Bits 7 - 1 Horizontal beam position (called HP).

SECOND INSTRUCTION WORD (IR2)

Bit 0 Always set to 0.

Bit 15 The blitter-finished-disable bit.

Normally, this bit is a 1.

(See the "Advanced Topics" section below.)

Bits 14 - 8 Vertical position compare enable bits (called VE).

Bits 7 - 1 Horizontal position compare enable bits (called HE).

The following example WAIT instruction waits for scan line 150 ($96) with the horizontal

position masked off.

DC.W $9601,$FF00 ; Wait for line 150,

; ignore horizontal counters.

The following example WAIT instruction waits for scan line 255 and horizontal position

254. This event will never occur, so the Copper stops until the next vertical blanking

interval begins.

DC.W $FFFF,$FFFE ; Wait for line 255,

; H = 254 (ends Copper list).

To understand why position VP=$FF HP=$FE will never occur, you must look at the

comparison operation of the Copper and the size restrictions of the position information.

Line number 255 is a valid line to wait for, in fact it is the maximum value that will fit into

this field. Since 255 is the maximum number, the next line will wrap to zero (line 256 will

appear as a zero in the

- Coprocessor Hardware 17 -

Page 27

comparison.) The line number will never be greater than $FF The horizontal position has a

maximum value of $E2. This means that the largest number that will ever appear in the

comparison is $FFE2. When waiting for $FFE2, the line $FF will be reached, but the

horizontal position $FE will never happen. Thus, the position will never reach $FFFE.

You may be tempted to wait for horizontal position $FE (since it will never happen), and

put a smaller number into the vertical position field. This will not lead to the desired

result. The comparison operation is waiting for the beam position to become greater than

or equal to the entered position. If the vertical position is not $FF, then as soon as

the line number becomes higher than he entered number, the comparison will evaluate to

true and the wait will end.

The following notes on horizontal and vertical beam position apply to both the WAIT

instruction and o the SKIP instruction. The SKIP instruction is described below in the

"Advanced Topics" section.

HORIZONTAL BEAM POSITION

The horizontal beam position has a value of $0 to $E2. The least significant bit is not used

in the comparison, so there are 113 positions available for Copper operations. This

corresponds to 4 pixels in low resolution and 8 pixels in high resolution. Horizontal

blanking falls in the range of $0F to $35. The standard screen (320 pixels wide) has an

unused horizontal portion of $04 to $47 (during which only the background color is

displayed).

All lines are not the same length in NTSC. Every other line is a long line (228 color clocks,

0-$E3), with the others being 227 color clocks long. In PAL, they are all 227 long. The

display sees all these lines as 227 1/2 color clocks long, while the copper sees alternating

long & short lines.

VERTICAL BEAM POSITION

The vertical beam position can be resolved to one line, with a maximum value of 255.

There are actually 262 NTSC (312 PAL) possible vertical positions. Some minor

complications can occur if you want something to happen within these last six or seven

scan lines. Because there are only eight bits of resolution for vertical beam position

(allowing 256 different positions), one of the simplest ways to handle this is shown below.

- 18 Coprocessor Hardware -

Page 28

INSTRUCTION EXPLANATION

[ ... other instructions ... ]

WAIT for position (0,255) At this point, the vertical

counter appears to wrap to 0

because the comparison works

on the least significant bits

of the vertical count.

WAIT for any horizontal position with Thus the total of 256+6 = 262

vertical position 0 through 256, covering lines of video beam travel

the last 6 lines of the scan before vertical during which Copper

blanking occurs. instructions can be executed.

NOTE

The vertical is like the horizontal - as there are alternating long and short lines, there are

also long and short fields (interlace only). In NTSC, the fields are 262, then 263 lines and

in PAL, 312,313.

This alteration of lines & fields produces the standard NTSC 4 field repeating pattern:

short field ending on short line

long field ending on long line

short field ending on long line

long field ending on short line

& back to the beginning...

1 horizontal count takes 1 cycle of the system clock. (Processor is twice this)

NTSC- 3,579,545 Hz

PAL- 3,546,895 Hz

genlocked- basic clock frequency plus or minus about 2%.

THE COMPARISON ENABLE BITS

Bits 14-1 are normally set to all 1s. The use of the comparison enable bits is described

later in the "Advanced Topics " section.

- Coprocessor Hardware 19 -

Page 29

USING THE COPPER REGISTERS

There are several machine registers and strobe addresses dedicated to the Copper:

o Location registers

o Jump address strobes

o Control register

LOCATION REGISTERS

The Copper has two sets of location registers:

COP1LCH High 3 bits of first Copper list address.

COP1LCL Low 16 bits of first Copper list address.

COP2LCH High 3 bits of second Copper list address.

COP2LCL Low 16 bits of second Copper list address.

In accessing the hardware directly, you often have to write to a pair of registers that

contains the address of some data. The register with the lower address always has a

name ending in "H" and contains the most significant data, or high 3 bits of the address.

The register with the higher address has a name ending in "L" and contains the least

significant data, or low 15 bits of the address. Therefore, you write the 18-bit address by

moving one long word to the register whose name ends in "H." This is because when you

write long words with the 68000, the most significant word goes in the lower addressed

word.

In the case of the Copper location registers, you write the address to COP1LCH. In the

following text, for simplicity, these addresses are referred to as COP1LC or COP2LC.

The Copper location registers contain the two indirect jump addresses used by the

Copper. The Copper fetches its instructions by using its program counter and increments

the program counter after each fetch. When a jump address strobe is written, the

corresponding location register is loaded into the Copper program counter. This causes the

Copper to jump to a new location, from which its next instruction will be fetched.

Instruction fetch continues sequentially until the Copper is interrupted by another jump

address strobe.

- 20 Coprocessor Hardware -

Page 30

NOTE

At the start of each vertical blanking interval, COP1LC is automatically used to start the

program counter. That is, no matter what the Copper is doing, when the end of vertical

blanking occurs, the Copper is automatically forced to restart its operations at the address

contained in COP1LC.

JUMP STROBE ADDRESS

When you write to a Copper strobe address, the Copper reloads its program counter from

the corresponding location register. The Copper can write its own location registers and

strobe addresses to perform programmed jumps. For instance, you might MOVE an

indirect address into the COP2LC location register. Then, any MOVE instruction that

addresses COPJMP2 strobes this indirect address into the program counter.

There are two jump strobe addresses:

COPJMP1 Restart Copper from address contained in COP1LC.

COPJMP2 Restart Copper from address contained in COP2LC.

CONTROL REGISTER

The Copper can access some special-purpose registers all of the time, some registers only

when a special control bit is set to a 1, some registers not at all. The registers that the

Copper can always affect are numbered $20 through $FF inclusive. Those it cannot affect

at all are numbered $00 to $0F inclusive. (See Appendix B for a list of registers

in address order.) The Copper control register is within this group ($00 to $0F). Thus it

takes deliberate action on the part of the 68000 to allow the Copper to write into a

specific range of the special-purpose registers.

The Copper control register, called COPCON, contains only one bit, bit #1. This bit, called

CDANG (for Copper Danger Bit) protects all registers numbered between $10 and $1F

inclusive. This range includes the blitter control registers. When CDANG is 0, these

registers cannot be written by the Copper. When CDANG is 1, these registers can be

written by the Copper. Preventing the Copper from accessing the blitter control registers

prevents a "runaway" Copper (caused by a poorly formed instruction list) from

accidentally affecting system memory.

NOTE

The CDANG bit is cleared after a reset.

- Coprocessor Hardware 21 -

Page 31

PUTTING TOGETHER A COPPER INSTRUCTION LIST

The Copper instruction list contains all the register resetting done during the vertical

blanking interval and the register modifications necessary for making mid-screen

alterations. As you are planning what will happen during each display field, you may find it

easier to think of each aspect of the display as a separate subsystem, such as playfields,

sprites, audio, interrupts, and so on. Then you can build a separate list of things that must

be done for each sub-system individually at each video beam position.

When you have created all these intermediate lists of things to be done, you must merge

them together into a single instruction list to be executed by the Copper once for each

display frame. The alternative is to create this all-inclusive list directly, without the

intermediate steps.

For example, the bit-plane pointers used in playfield displays and the sprite pointers must

be rewritten during the vertical blanking interval so the data will be properly retrieved

when the screen display starts again. This can be done with a Copper instruction list that

does the following:

WAIT until first line of the display

MOVE data to bit-plane pointer 1

MOVE data to bit-plane pointer 2

MOVE data to sprite pointer 1

and so on

As another example, the sprite DMA channels that create movable objects can be re-used

multiple times during the same display field. You can change the size and shape of the

reuses of a sprite; however, every multiple reuse normally uses the same set of colors

during a full display frame.

You can change sprite colors mid-screen with a Copper instruction list that waits until the

last line of the first use of the sprite processor and changes the colors before the first line

of the next use of the same sprite processor:

WAIT for first line of display

MOVE firstcolor1 to COLOR 17

MOVE firstcolor2 to COLOR 18

MOVE firstcolor3 to COLOR 19

WAIT for last line +1 of sprite's first use

MOVE secondcolor1 to COLOR 17

MOVE secondcolor2 to COLOR 18

MOVE secondcolor3 to COLOR 19

and so on

- 22 Coprocessor Hardware -

Page 32

As you create Copper instruction lists, note that the final list must be in the same order as

that in which the video beam creates the display. The video beam traverses the screen

from position (0,0) in the upper left hand corner of the screen to the end of the display

(226,262) NTSC (or (226,312) PAL) in the lower right hand corner. The first 0 in (0,0)

represents the x position. The second 0 represents the y position. For example, an

instruction that does something at position (0,100) should come after an instruction that

affects the display at position (0,60).

NOTE

Given the form of the WAIT instruction, you can sometimes get away with not sorting the

list in strict video beam order. The WAIT instruction causes the Copper to wait until the

value in the beam counter is equal to or greater than the value in the instruction.

This means, for example, if you have instructions following each other like this:

WAIT for position (64,64)

MOVE data

WAIT for position (60,60)

MOVE data

The Copper will perform both moves, even though the instructions are out of sequence.

The "greater than" specification prevents the Copper from locking up if the beam has

already passed the specified position. A side effect is that the second MOVE below will be

performed:

WAIT for position (60,60)

MOVE data

WAIT for position (60,60)

MOVE data

At the time of the second WAIT in this sequence, the beam counters will be greater than

the position shown in the instructions. Therefore, the second MOVE will also be performed.

Note also that the above sequence of instructions could just as easily be

WAIT for position (60,60)

MOVE data

MOVE data

because multiple MOVEs can follow a single WAIT.

- Coprocessor Hardware 23 -

Page 33

COMPLETE SAMPLE COPPER LIST

The following example shows a complete Copper list. This list is for two bitplanes-one at

$21000 and one at $25000. At the top of the screen, the color registers are loaded with

the following values:

REGISTER COLOR

COLOR00 white

COLOR01 red

COLOR02 green

COLOR03 blue

At line 150 on the screen, the color registers are reloaded:

REGISTER COLOR

COLOR00 black

COLOR01 yellow

COLOR02 cyan

COLOR03 magenta

The complete Copper list follows.

;

; Notes:

; 1. Copper lists must be in CHIP ram.

; 2. Bitplane addresses used in the example are arbitrary.

; 3. Destination register addresses in copper move instructions

; are offsets from the base address of the custom chips.

; 4. As always, hardware manual examples assume that your

; application has taken full control of the hardware,

; and is not conflicting with operating system use of

; the same hardware.

; 5. Many of the examples just pick memory addresses to

; be used. Normally you would need to allocate the

; required type of memory from the system with AllocMem()

; 6. As stated earlier, the code examples are mainly to help

; clarify the way the hardware works.

; 7. The following INCLUDEs are required by all example code

; in this chapter.

;

INCLUDE "exec/types.i"

INCLUDE "hardware/custom.i"

INCLUDE "hardware/dmabits.i"

INCLUDE "hardware/hw_examples.i"

- 24 Coprocessor Hardware -

Page 34

COPPERLIST:

;

; Set up pointers to two bit planes

;

DC.W BPL1PTH,$0002 ;Move S0002 into register $0E0 (BPL1PTH)

DC.W BPL1PTL,$1000 ;Move $1000 into register $0E2 (BPL1PTL)

DC.W BPL2PTH,$0002 ;Move $0002 into register $0E4 (BPL2PTH)

DC.W BPL2PTL,$5000 ;Move $5000 into register $0E6 (BPL2PTL)

;

; Load color registers

;

DC.W COLOR00,$0FFF ;Move white into register $180 (COLOR00

DC.W COLOR01,$0F00 ;Move red into register $182 (COLOR01)

DC.W COLOR02,$00F0 ;Move green into register $189 (COLOR02)

DC.W COLOR03,$000F ;Move blue into register $186 (COLOR03)

;

; Specify 2 lo-res bitplanes

;

DC.W BPLCON0,$2200 ;2 lores planes, color on

;

; Wait for line 150

;

DC.W $9601,$FF00 ;Wait for line 150, ignore horiz. position

;

; Change color registers mid-display

;

DC.W COLOR00,$0000 ;Move black into register $0180 (COLOR00)

DC.W COLOR01,$0FF0 ;Move yellow into register $0182 (COLOR01)

DC.W COLOR02,$00FF ;Move cyan into register $0184 (COLOR02)

DC.W COLOR03,$0F0F :Move magenta into register $0186 (COLOR03)

;

; End Copper list by waiting for the impossible

;

DC.W $FFFF,$FFFE ;Wait for line 255, H = 254 (never happens)

For more information about color registers, see Chapter 3, "Playfield

Hardware."

LOOPS AND BRANCHES

Loops and branches in Copper lists are covered in the "Advanced Topics" section below.

STARTING AND STOPPING THE COPPER

STARTING THE COPPER AFTER RESET

At power-on or reset time, you must initialize one of the Copper location registers

(COP1LC or COP2LC) and write to its strobe address before Copper DMA is tuned on. This

ensures a known start address and known state. Usually, COP1LC is used because this

particular register is reused during each vertical blanking time. The following sequence of

instructions shows how to

- Coprocessor Hardware 25 -

Page 35

initialize a location register. It is assumed that the user has already

created the correct Copper instruction list at location "mycoplist."

;

; Install the copper list

;

LEA CUSTOM,a1 ; a1 = address of custom chips

LEA MYCOPLIST(pc),a0 ; Address of our copper list

MOVE.L a0,COP1LC(a1) ; Write whole longword address

MOVE.W COPJMP1(a1),d0 ; Causes copper to load PC from COP1LC

;

; Then enable copper and raster dma

;

MOVE.W #(DMAF SETCLR!DMAF_COPPER!DMAF_RASTER!DMAF_MASTER),DMACON(a1)

;

Now, if the contents of COP1LC are not changed, every time vertical blanking occurs the

Copper will restart at the same location for each subsequent video screen. This forms a

repeatable loop which, if the list is correctly formulated, will cause the displayed screen to

be stable.

STOPPING THE COPPER

No stop instruction is provided for the Copper. To ensure that it will stop and do nothing

until the screen display ends and the program counter starts again at the top of the

instruction list, the last instruction should be to WAIT for an event that cannot occur. A

typical instruction is to WAIT for VP = $FF and HP = $FE. An HP of greater than $E2 is not

possible. When the screen display ends and vertical blanking starts, the Copper will

automatically be pointed to the top of its instruction list, and this final WAIT instruction

never finishes.

You can also stop the Copper by disabling its ability to use DMA for retrieving instructions

or placing data. The register called DMACON controls all of the DMA channels. Bit7,

COPEN, enables Copper DMA when set to 1.

For information about controlling the DMA, see Chapter 7, "System Control Hardware."

- 26 Coprocessor Hardware -

Page 36

ADVANCED TOPICS

THE SKIP INSTRUCTION

The SKIP instruction causes the Copper to skip the next instruction if the video beam

counters are equal to or greater than the value given in the instruction.

The contents of the SKIP instructions words are shown below. They are identical to the

WAIT instruction, except that bit 0 of the second instruction word is a 1 to identify this as

a SKIP instruction.

FIRST INSTRUCTION WORD (IR1)

Bit 0 Always set to 1.

Bits 15 - 8 Vertical position (called VP).

Bits 7 - 1 Horizontal position (called HP).

Skip if the beam counter is equal to or

greater than these combined bits

(bits 15 through 1).

SECOND INSTRUCTION WORD (IR2)

Bit 0 Always set to 1.

Bit 15 The blitter-finished-disable bit.

(See "Using the Copper with the

Blitter" below.)

Bits 14 - 8 Vertical position compare enable bits (called VE).

Bits 7 - 1 Horizontal position compare enable bits (called HE).

The notes about horizontal and vertical beam position found in the discussion of the WAIT

instruction apply also to the SKIP instruction.

- Coprocessor Hardware 27 -

Page 37

The following example SKIP instruction skips the instruction following it if VP (vertical

beam position) is greater than or equal to 100 ($64).