Colex VME-80186 User Manual

talEX

VME

80186

TECHNICAL

MANUAL

.

All information included in this manual,

is

subject to

Copyright

© COLEX Inc.' 1983.

AU

rights reserved.

VME-80186

COLEX

VME-S81S6

COLEX's

most

popular

Intel

address

proper

VMEbus

B

or

later.

The

VME-80186

,system

of

installations

8088/8086

The

result

builder.

The

features

Processor

Clock

On-board

Add-on

Off-board

Video

Serial

DMA

Printer

VMEbus

Mass

Real

storage

time

MultiCpu

advanced

80186

space

timing

standard

MSDOS

upward

is

speed

memory

memory

memory

output

I/O

output

expansion

clock

option

system

16

bit

to

controls,

allows,

together

a

of

system

concepts

microprocessor

16

megabytes,

and

to

other

for

with

among

compatibility

wide

the

range

VME-80186

80186

13

CPU

MHz

l28kb

2 JEDEC

128kb

Parity

16

megabytes

5

address

Optional

2

RS232

High

speed

Centronics

Full

Bus

SASI

with

For

VMEbus

master,

interface

alarm,

parallel

design

COLEX

the

all

of

EPROM

for

video

ports

has

of

adding

has

VMEbus

first

the

VMEbuL

16

bit

while

software

include:

sockets

all

256k

address

modifiers

controller

with

DMA

channel

compatible,

interface,

slave

to

timer,

processing

made

the

80's

and

the

address

made

products

time,

The

computers.

compressing

and

bytes

space

25

pin

and

controller

floppy

and

it

possible

together

VMEbus.

the

VME-80186

meeting

the

8088/8086

hardware

of

connectors

25

pin

slot

and

battery

By

modifiers,

use

of

The

80186,

40

chips

memory

connector

one

functions

hard

disks

backup

to

bring

onto

one

expanding

and

compatible

specification

the

popular

has

the

incorporates

into

options

for

two

board:

the

providing

Revision

operating

widest

one

package.

the

of

the

the

memory

the

to

the

range

full

system

HIGH

PERFORMANCE

Applications

contra

and

with

llers

I/O

processor

VMEbus

products

devices,

controllers,

and

and

direct

APPLICATIONS

for

the

preprocessor

for

products

can

be

industrial

and

many

VME-80186

5,

multi-processor

from

expanded

interfaces,

more.

include

small

dozens

to

,use

machine

busi

systems.

of

AID

CMOS

I

tool

ness

vendors,

converters,

RAM

control,

computers,

The

VME-80186

plus

additional

modules,

other

communications

process

is

control,

compatible

COLEX

mass

graphics

display

VMEbus

memory

128/256k

MEMORY

This

memory

expanded

is

provided

main

board

625ns.

80186

The

m~mory

Three

the

VMEbus,

read

by

On-board

Off-board

Vector

VMEbus

not

On-board

This

used

mapping

by

by

memory

Refresh

card.

map

segments

the

used

COLEX

consists

an

additional

by

the

XRAM

and

for

all

on

the

perform

the

80186

RAM

last

chip.

memory

memory

interrupt

short

I/O

EPROM.memory

is

programmable

in

standard

of

128k

128k

add-on

the

plug-on

VME-80l86

VME-80186

actual

is

to

allow

input

software.

bytes

by,tes

and

located

by

performs

memory.

memory

card

memory

is

functions,

VMEbus

0-

256Kb

256768800832-

768Kb

800Kb

832Kb

960Kb

96@-l@24Kb

by

the

80186

on

using

Cycle

is

done

separated

generated

CPU

the

main

the

XRAM

parity

time

checking

of

by a controller

into

one

is

vector

256Kb

5l2Kb

32Kb

32Kb

128Kb

64Kb

chip.

The

board,

card.

the

5

working

for

interrupts

above

Parity

on

memory

on

I/O

accesses

mapping

it

can

logic

both

averages

the

VME-

segments.

to

be

the

to

be

is

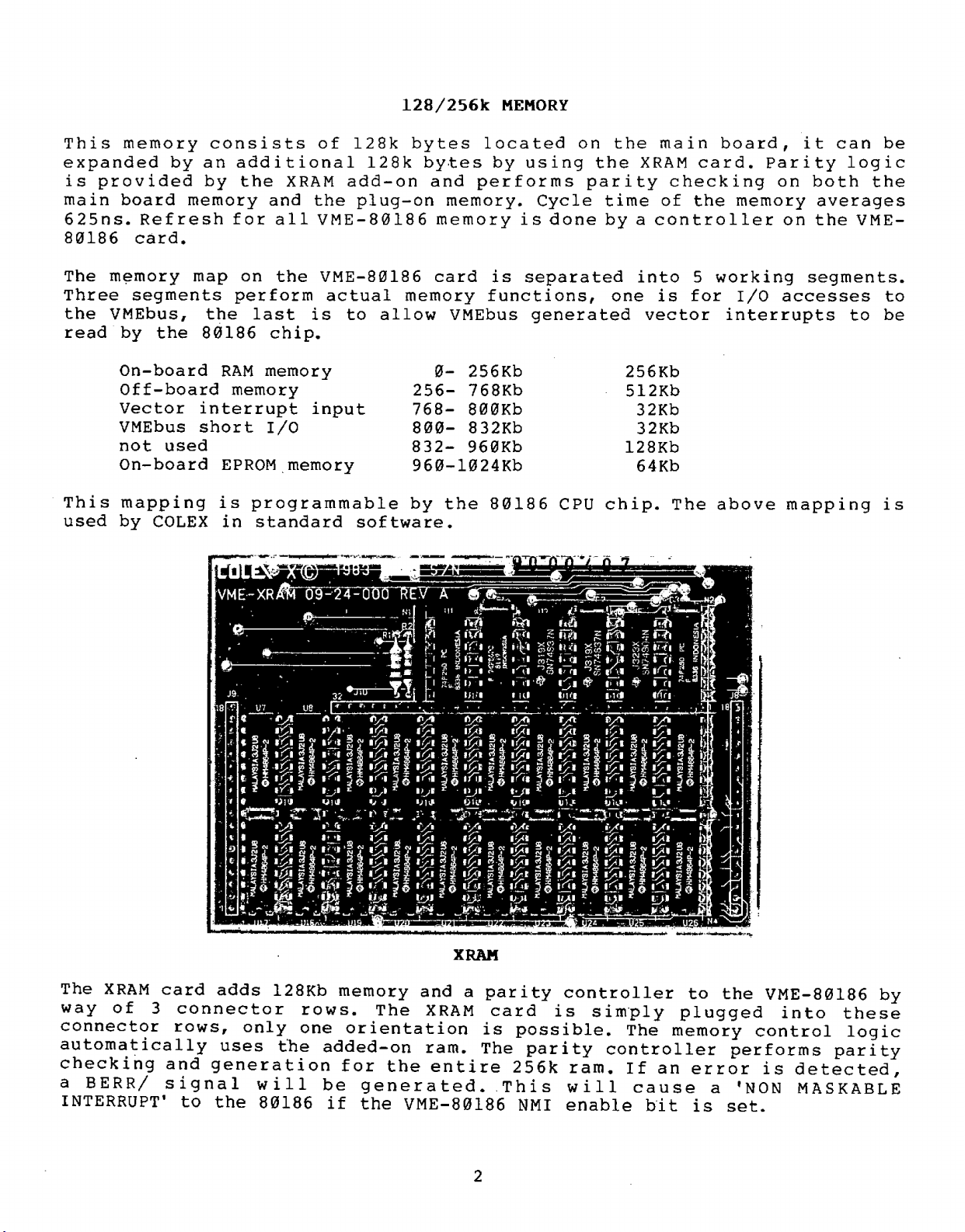

The

XRAM

way

of

3

connector

automatically

checking

a

BERR/

INTERRUPT'

card

adds

connector

rows,

and

generation

signal

to

the

only

uses

l28Kb

the

will

813186

memory

rows.

one

added-on

for

be

if

and

The

XRAM

orientation

ram.

the

generated

the

VME-8@186

X

RAM

a

entire

parity

card

is

The

•.

This

2

controller

is

possible.

parity

256k

ram.

will

NMI

enable

simply

The

controller

If

cause

bit

to

plugged

memory

an

error

is

the

VME-8@186

into

control

performs

is

detected,

by

these

logic

parity

a 'NON MASKABLE

set.

SERIAL PORTS

Serial

DCE

connection

rate

baud

BYSYNC,

programmed

ports

serial

details

is

provided

The

clocks,

Jl

P3

a

clock

connected

I/O

for

generator

rates

are

I/O

DTE

and

J3

pin

17

HDLC,

can

and

is

possible

direct

to a modem,

may

and

for

interfaced

controller

be

at

port

input.

(See

internal

Jl

J2

J3

should

is

connected

to

both

connection

connected

be

used.

SDLe

PM,

NRZI,

found.

the

selects

selects

enables

not

with

in

end

channel

or

be

the

via

or

to

to

Multiple

at

speeds

and

via

J2

25

chip

the

of

this

external

external

the

the

inserted

to

the

installed,

/RTxeA

the

to

used

A)

internal

internally

2

a

another

a

3.6864

BIPHASE

pin

ZILOG

document.

can

SCC

input

ports

terminal,

computer.

protocols

up

to

plugs

is

the

see

be

programmed

sync

sync

at

by

from

baud

the

/TRxCA

the

and

on

the

P3

is

MHz

programming

crystal

are

I

megabaud.

encoding

on

the

ZILOG SCC

the

following

P3

rate

generated

same

to

time.

input

on-board

P3

pin

front

pin

generator

card.

Each

supported,

and

for

sync

allowing

14

P4

wired

port

oscillator.

The

decoding.

panel

8530,

manual,

internal

15

to

baud

for

is

connected

as

DTE

has

including

channels

of

full

a

jumpers:

from

P3

pin

this

rate

the

clock

for

direct

its

own

All

can

Both

the

programming

brief

or

channel

to

generator

card.

external

15

be

output.

common

ASYNC,

also

serial

summary

used

as

baud

The

B

a

be

as

is

While

SCC

chip

of

common

1)

Baud

The

source

RTXCB

crystal:

This

and

B

Register

the

used

rate

to

channel

channel

enables

channels.

14

Zilog

programming

of

SYNCB.

should

technical

on

the

selection

the

baud

Register

A:

B:

the

56h

D4h

2,

Both

89186

options

rate

16

bit

transmit

be

programmed

sec

manual

for

all

can

clock

11

should

divide

and

PROGRAttMING

is

the

best

serial

save

is

a

be

counters

receive

with

I/O,

the

3.6864

programmed

rates

a

9lh.

user

to

source

the

time.

MHz

provide

will

of

following

crystal

as

be

information

on

channel

fo1:1ows

a

baud

the

same.

quick

to

rate

on

summary

B

from

use

this

to

the

the

A

3

2)

Baud

To

calculate

formula:

=

rate

(BR =

115200

BR

speed

the

required

-2

correct

sec

divide

baud

Programming

count

rate)

continued

for

each

channel,

use

the

following

Example:

This

,3)

Registers

For

RTS

4)

To

is

Data

n6rmal

active)

register

General

reset

channel

115200

9600

programmed

parameters

3,4

and

operation

the

following

3

4

5

parameters

the

chip,

A:

-2

into

5

determine

(~

content

Clh

44h

EAh

tbe

following

=

10

register

data

codes

register

9

9

15

the

bits,

are

for

9600

12/13,

parameters

no

used~

data

data

80h

00b

00h

baud

register

parity,

should

be

13

used

1

stop

written

is

in

the

the

bit,

first:

MSB.

character

ASYNC,

~

data.

DTR

and

5)

The

both

The

channel

Summary

byte

channel

A:

B:

first

B:

strings

s

09/80/09/00/03/Cl/04/44/05/EA/0B/56/0C/0A/0D/00/0E/01/0F/00

09/40/09/00/03/Cl/04/44/05/EA/0B/D4/0C/0A/00/00/0E/0l/0F/00

byte

would

is

to

the

be

be:

register,

9

9·

15

outputted

(a

11

data

the

40h

00b

00h

to

hex)

second

4

the

SCC

is

for

the

9600

data.

baud

operation

on

6)

Interrupts

The

7)

Reading

The

listed

SCC

sec

chip

can

bit.

cannot

status

be

polled

SCC

generate

for

Programming

interrupts

data

ready

continued

to

or

transmitter

the

80186.

empty

by

testing

the

For

connection

The

This

connector

the

before

on

the

interface

connector

BUSY

strobe

the

receive

transmit

for

and

data

printer

to

is

matches

ease

PE

can

should

ready

ready

a

made

(paper

be

sent.

be

used).

printer,

via

the

of

cable

empty)

pulsed

=

bit

0

=

bit

CENTRONICS INTERFACE

PS,

lower

After

2

a

Centronics-compatible

a

25

pin

connector

25

pins

construction.

signals

data

low

for

is

at

of

should

outputted

least

When

the

be

10

interface

on

the

standard

outputting

tested,

to

the

us

(exact

front"of

36

pin

to

both

printer

duration

is

provided.

the

Centronics

the

printer,

must

data

depends

card.

be

port,

low

5

Loading...

Loading...