Page 1

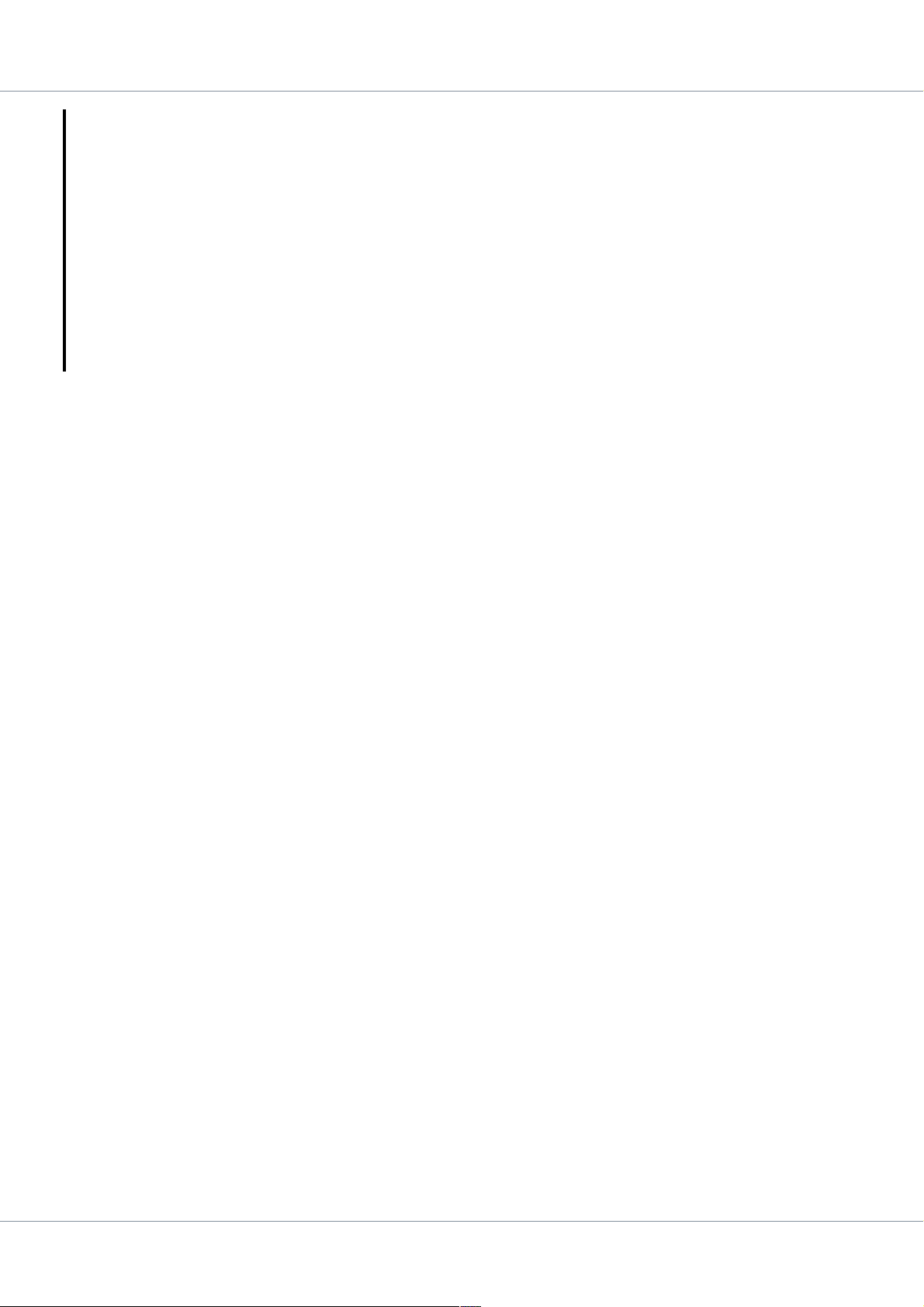

GR740

FPU

MMU

Caches

X

LEON4 LEON4

FPUFPU

MMU

Caches

Ethernet

MIL-STD

1553B

CAN

Controller

SpW router

PCI

Target

PCI

DMA

Bootstrap

GP register

TDP

controller

SPI

controller

Timer unit 0

watchdog

GPIO port

0 - 1

UART

Temperature

sensor

Clock gating

unit

Pad / PLL

controller

AHB

Status

Timer units

1 - 4

PCI

Master

L2

Cache

SDRAM

CTRL w.

EDAC

Memory

Scrubber

PROM

& IO

CTRL w.

EDAC

AHB/APB

Bridges

AHB/AHB

Bridge

AHB Bridge

IOMMU

AHB

Status

AHB/AHB

Bridge

DSU4

AHB/APB

Bridge

SpW RMAP

DCL

AHBTRACE

JTAG

DCL

IRQ(A)MP

LEON4

STAT.UNIT

Debug bus

32-bit APB

SSS

SM

MSS

32-bit APB

MS

M

S

X

MM MM

SSSSSS

M

S

MM

S

S

S

X

M

M

S

MM

M

SSS

S

MXMXMXMX

Processor bus

128-bit AHB

Memory bus

128-bit AHB

SM

X

SSSSSS

S

S

Slave IO bus

32-bit AHB

S

S

S

S

S

S

Statistics

SS

96-bit

PC100

SDRAM

PROM

IO

8/16-bit

32-bit AHB

Master IO bus

32-bit AHB

MMU

Caches

Quad Core LEON4 SPARC V8 Processor

2017 Preliminary Data Sheet and User’s Manual

The most important thing we build is trust

Features

• Fault-tolerant quad-processor

SPARC V8 integer unit

with 7-stage pipeline, 8 register windows, 4x4 KiB

instruction and 4x4 KiB data caches.

• Double-precision IEEE-754 floating point units

• 2 MiB Level-2 cache

• 64-bit PC100 SDRAM memory interface with ReedSolomon EDAC*

• 8/16-bit PROM/IO interface with EDAC*

• SpaceWire router with eight SpaceWire links

• 2x 10/100/1000 Mbit Ethernet interfaces*

• PCI Initiator/Target interface*

• MIL-STD-1553B interface*

• 2x CAN 2.0 controller interface*

• 2x UART, SPI, Timers and watchdog, 16+22 GPIO*

• CPU and I/O memory management units

• SpaceWire Time Distribution Protocol controller and

support for time synchronisation

• JTAG, Ethernet* and SpaceWire* debug links

* Interfaces have shared pins

Description

The GR740 device is a radiation-hard system-onchip featuring a quad-core fault-tolerant LEON4

SPARC V8 processor, eight port SpaceWire router,

PCI initiator/target interface, MIL-STD-1553B

interface, CAN 2.0 interfaces and 10/100/1000

Mbit Ethernet interfaces.

Specification

• System frequency: 250 MHz

• Main memory interface: PC100 SDRAM

• SpaceWire router with SpaceWire links: 300

Mbit/s

• 33 MHz PCI 2.3 initiator/target

interface

• Ethernet 10/100/1000 Mbit MACs

• CCGA625 / LGA625 package

Applications

The GR740 device is targeted at high-performance general purpose

processing. The architecture is suitable for both symmetric and

asymmetric multiprocessing. Shared resources can be monitored to

support mixed-criticality applications.

GR740-UM-DS, Nov 2017, Version 1.7 www.cobham.com/gaisler

Page 2

GR740

Table of contents

1 Introduction.............................................................................................................................. 8

1.1 Scope .......................................................................................................................................................8

1.2 Preliminary data sheet limitations ...........................................................................................................8

1.3 Updates and feedback.............................................................................................................................. 8

1.4 Software support...................................................................................................................................... 8

1.5 Development board .................................................................................................................................8

1.6 Performance, power consumption and radiation tolerance .....................................................................8

1.7 Reference documents ..............................................................................................................................9

1.8 Document revision history ....................................................................................................................10

1.9 Acronyms .............................................................................................................................................. 13

1.10 Definitions .............................................................................................................................................14

1.11 Register descriptions .............................................................................................................................15

2 Architecture............................................................................................................................ 16

2.1 Overview ...............................................................................................................................................16

2.2 Cores......................................................................................................................................................18

2.3 Memory map .........................................................................................................................................19

2.4 Interrupts ...............................................................................................................................................22

2.5 Plug & play and bus index information.................................................................................................22

3 Signals.................................................................................................................................... 27

3.1 Bootstrap signals ...................................................................................................................................27

3.2 Configuration for flight .........................................................................................................................28

3.3 Pin multiplexing .................................................................................................................................... 28

3.4 Complete signal list ...............................................................................................................................32

3.5 Pin driver configuration......................................................................................................................... 35

4 Clocking and reset.................................................................................................................. 36

4.1 Clock inputs...........................................................................................................................................36

4.2 Clock loop for SDRAM ........................................................................................................................36

4.3 Reset scheme .........................................................................................................................................37

4.4 Clock multiplexing for main system clock, SDRAM and SpaceWire .................................................. 38

4.5 PLL control and configuration ..............................................................................................................39

4.6 PLL watchdog .......................................................................................................................................40

4.7 PCI clock ...............................................................................................................................................40

4.8 MIL-STD-1553B clock .........................................................................................................................40

4.9 Clock gating unit ................................................................................................................................... 40

4.10 Debug AHB bus clocking......................................................................................................................41

4.11 Notes on Ethernet interface clock and mode switch .............................................................................41

5 Technical notes....................................................................................................................... 42

5.1 GRLIB AMBA plug&play scanning .....................................................................................................42

5.2 Processor register file initialisation and data scrubbing ........................................................................ 42

5.3 PROM-less systems and SpaceWire RMAP.........................................................................................42

5.4 System integrity and debug communication links ................................................................................ 43

5.5 Separation and ASMP configurations ................................................................................................... 43

5.6 Clock gating ..........................................................................................................................................44

5.7 Software portability............................................................................................................................... 45

5.8 Level-2 cache ........................................................................................................................................45

5.9 Time synchronisation ............................................................................................................................ 46

5.10 Bridges, posted-writes and ERROR response propagation................................................................... 47

GR740-UM-DS, Nov 2017, Version 1.7 2 www.cobham.com/gaisler

Page 3

GR740

6 LEON4 - Fault-tolerant High-performance SPARC V8 32-bit Processor ............................. 48

6.1 Overview ...............................................................................................................................................48

6.2 LEON4 integer unit ...............................................................................................................................50

6.3 Cache system......................................................................................................................................... 56

6.4 Memory management unit.....................................................................................................................59

6.5 Floating-point unit................................................................................................................................. 60

6.6 Co-processor interface........................................................................................................................... 61

6.7 AMBA interface ....................................................................................................................................61

6.8 Multi-processor system support ............................................................................................................63

6.9 ASI assignments ....................................................................................................................................64

6.10 Configuration registers ..........................................................................................................................69

6.11 Software considerations ........................................................................................................................78

7 Floating-point Control Unit ................................................................................................... 80

7.1 Floating-Point register file.....................................................................................................................80

7.2 Floating-Point State Register (FSR)...................................................................................................... 80

7.3 Floating-Point Exceptions and Floating-Point Deferred-Queue ........................................................... 80

8 High-performance IEEE-754 Floating-point Unit ................................................................. 82

8.1 Overview ...............................................................................................................................................82

8.2 Functional description ...........................................................................................................................82

9 Level 2 Cache controller........................................................................................................ 86

9.1 Overview ...............................................................................................................................................86

9.2 Operation ............................................................................................................................................... 86

9.3 Operation ............................................................................................................................................... 89

9.4 Registers ................................................................................................................................................92

10 SDRAM Memory Controller with Reed-Solomon EDAC .................................................. 100

10.1 Overview .............................................................................................................................................100

10.2 Operation .............................................................................................................................................100

10.3 Limitations...........................................................................................................................................100

10.4 SDRAM back-end operation ...............................................................................................................101

10.5 Fault-tolerant operation .......................................................................................................................104

10.6 Registers ..............................................................................................................................................107

11 Memory Scrubber and AHB Status Register ....................................................................... 112

11.1 Overview ............................................................................................................................................. 112

11.2 Operation ............................................................................................................................................. 112

11.3 Registers .............................................................................................................................................. 115

12 IOMMU - Bridge connecting Master I/O AHB bus ............................................................ 121

12.1 Overview .............................................................................................................................................121

12.2 Bridge operation ..................................................................................................................................121

12.3 General access protection and address translation ..............................................................................124

12.4 Access Protection Vector .....................................................................................................................125

12.5 IO Memory Management Unit (IOMMU) functionality.....................................................................127

12.6 Fault-tolerance..................................................................................................................................... 130

12.7 Statistics...............................................................................................................................................131

12.8 ASMP support ..................................................................................................................................... 131

12.9 Registers ..............................................................................................................................................132

13 SpaceWire router.................................................................................................................. 142

13.1 Overview .............................................................................................................................................142

GR740-UM-DS, Nov 2017, Version 1.7 3 www.cobham.com/gaisler

Page 4

GR740

13.2 Operation .............................................................................................................................................142

13.3 SpaceWire ports...................................................................................................................................152

13.4 AMBA ports ........................................................................................................................................154

13.5 Configuration port ............................................................................................................................... 177

14 Gigabit Ethernet Media Access Controller (MAC) ............................................................. 204

14.1 Overview .............................................................................................................................................204

14.2 Operation .............................................................................................................................................204

14.3 Tx DMA interface ...............................................................................................................................205

14.4 Rx DMA interface ...............................................................................................................................207

14.5 MDIO Interface ...................................................................................................................................210

14.6 Ethernet Debug Communication Link (EDCL) ..................................................................................210

14.7 Media Independent Interfaces ............................................................................................................. 212

14.8 Registers ..............................................................................................................................................213

15 32-bit PCI/AHB bridge ........................................................................................................ 218

15.1 Overview .............................................................................................................................................218

15.2 Configuration.......................................................................................................................................218

15.3 Operation .............................................................................................................................................224

15.4 PCI Initiator interface..........................................................................................................................227

15.5 PCI Target interface............................................................................................................................. 228

15.6 DMA Controller .................................................................................................................................. 229

15.7 PCI trace buffer ................................................................................................................................... 232

15.8 Interrupts .............................................................................................................................................232

15.9 Reset ....................................................................................................................................................233

15.10 Registers .............................................................................................................................................. 233

16 MIL-STD-1553B / AS15531 Interface ................................................................................ 241

16.1 Overview .............................................................................................................................................241

16.2 Electrical interface............................................................................................................................... 241

16.3 Operation .............................................................................................................................................242

16.4 Bus Controller Operation .................................................................................................................... 243

16.5 Remote Terminal Operation ................................................................................................................248

16.6 Bus Monitor Operation........................................................................................................................ 252

16.7 Clocking and reset ...............................................................................................................................252

16.8 Registers ..............................................................................................................................................253

17 CAN 2.0 Controllers with DMA.......................................................................................... 263

17.1 Overview .............................................................................................................................................263

17.2 Interface...............................................................................................................................................264

17.3 Protocol ...............................................................................................................................................264

17.4 Status and monitoring.......................................................................................................................... 264

17.5 Transmission........................................................................................................................................ 264

17.6 Reception.............................................................................................................................................267

17.7 Global reset and enable ....................................................................................................................... 270

17.8 Interrupt ...............................................................................................................................................270

17.9 Registers ..............................................................................................................................................271

17.10 Memory mapping ................................................................................................................................281

18 Bridge connecting Slave I/O AHB bus to Processor AHB bus............................................ 282

18.1 Overview .............................................................................................................................................282

18.2 Operation .............................................................................................................................................282

18.3 Registers ..............................................................................................................................................285

GR740-UM-DS, Nov 2017, Version 1.7 4 www.cobham.com/gaisler

Page 5

GR740

19 Fault-tolerant 8/16-bit PROM/IO Memory Interface .......................................................... 286

19.1 Overview .............................................................................................................................................286

19.2 PROM access ......................................................................................................................................286

19.3 Memory mapped IO ............................................................................................................................288

19.4 8-bit and 16-bit PROM access............................................................................................................. 289

19.5 8- and 16-bit I/O access.......................................................................................................................290

19.6 Burst cycles .........................................................................................................................................290

19.7 Memory EDAC ...................................................................................................................................291

19.8 Bus Ready signalling...........................................................................................................................291

19.9 Registers ..............................................................................................................................................293

20 General Purpose Timer Units............................................................................................... 297

20.1 Overview .............................................................................................................................................297

20.2 Operation .............................................................................................................................................297

20.3 Registers ..............................................................................................................................................298

21 Multiprocessor Interrupt Controller with extended ASMP support..................................... 301

21.1 Overview .............................................................................................................................................301

21.2 Operation .............................................................................................................................................301

21.3 Registers ..............................................................................................................................................306

22 General Purpose I/O Ports ................................................................................................... 316

22.1 Overview .............................................................................................................................................316

22.2 Operation .............................................................................................................................................316

22.3 Registers ..............................................................................................................................................317

23 UART Serial Interfaces........................................................................................................ 323

23.1 Overview .............................................................................................................................................323

23.2 Operation .............................................................................................................................................323

23.3 Baud-rate generation ........................................................................................................................... 324

23.4 Loop back mode ..................................................................................................................................325

23.5 FIFO debug mode................................................................................................................................ 325

23.6 Interrupt generation ............................................................................................................................. 325

23.7 Registers ..............................................................................................................................................326

24 SPI Controller supporting master and slave operation ........................................................ 328

24.1 Overview .............................................................................................................................................328

24.2 Operation .............................................................................................................................................328

24.3 Registers ..............................................................................................................................................331

25 Clock gating unit .................................................................................................................. 338

25.1 Overview .............................................................................................................................................338

25.2 Operation .............................................................................................................................................338

25.3 Registers ..............................................................................................................................................339

26 LEON4 Statistics Unit (Performance Counters) .................................................................. 342

26.1 Overview .............................................................................................................................................342

26.2 Multiple APB interfaces ...................................................................................................................... 344

26.3 Registers ..............................................................................................................................................345

27 AHB Status Registers .......................................................................................................... 349

27.1 Overview .............................................................................................................................................349

27.2 Operation .............................................................................................................................................349

27.3 Registers ..............................................................................................................................................350

GR740-UM-DS, Nov 2017, Version 1.7 5 www.cobham.com/gaisler

Page 6

GR740

28 Register for bootstrap signals............................................................................................... 351

28.1 Overview .............................................................................................................................................351

28.2 Operation .............................................................................................................................................351

28.3 Registers ..............................................................................................................................................351

29 Temperature sensor controller.............................................................................................. 353

29.1 Overview .............................................................................................................................................353

29.2 Operation .............................................................................................................................................353

29.3 Registers ..............................................................................................................................................354

30 Register Bank For I/O and PLL configuration registers ...................................................... 356

30.1 Overview .............................................................................................................................................356

30.2 Operation .............................................................................................................................................356

30.3 Registers ..............................................................................................................................................358

31 SpaceWire - Time Distribution Protocol Controller ............................................................ 363

31.1 Overview .............................................................................................................................................363

31.2 Protocol ...............................................................................................................................................363

31.3 Functionality........................................................................................................................................363

31.4 Registers ..............................................................................................................................................370

32 Bridge connecting Debug AHB bus to Processor AHB bus ................................................ 385

32.1 Overview .............................................................................................................................................385

32.2 Operation .............................................................................................................................................385

32.3 Registers ..............................................................................................................................................388

33 LEON4 Hardware Debug Support Unit............................................................................... 389

33.1 Overview .............................................................................................................................................389

33.2 Operation .............................................................................................................................................389

33.3 AHB Trace Buffer ...............................................................................................................................390

33.4 Instruction trace buffer ........................................................................................................................392

33.5 DSU memory map............................................................................................................................... 393

33.6 DSU registers ......................................................................................................................................395

34 JTAG Debug Link with AHB Master Interface ................................................................... 405

34.1 Overview .............................................................................................................................................405

34.2 Operation .............................................................................................................................................405

34.3 Registers ..............................................................................................................................................406

35 SpaceWire Debug Link ........................................................................................................ 407

35.1 Overview .............................................................................................................................................407

35.2 Operation .............................................................................................................................................407

35.3 Link interface ...................................................................................................................................... 408

35.4 Time-Code distribution ....................................................................................................................... 410

35.5 Receiver DMA channels......................................................................................................................410

35.6 Transmitter DMA channels ................................................................................................................. 415

35.7 RMAP..................................................................................................................................................418

35.8 AMBA interface .................................................................................................................................. 422

35.9 Registers ..............................................................................................................................................423

36 AHB Trace buffer tracing Master I/O AHB bus .................................................................. 429

36.1 Overview .............................................................................................................................................429

36.2 Operation .............................................................................................................................................429

36.3 Registers ..............................................................................................................................................431

GR740-UM-DS, Nov 2017, Version 1.7 6 www.cobham.com/gaisler

Page 7

GR740

37 AMBA AHB controller with plug&play support................................................................. 435

37.1 Overview .............................................................................................................................................435

37.2 Operation .............................................................................................................................................435

38 AMBA AHB/APB bridge with plug&play support ............................................................. 437

38.1 Overview .............................................................................................................................................437

38.2 Operation .............................................................................................................................................437

39 Electrical description ........................................................................................................... 438

39.1 Absolute maximum ratings .................................................................................................................438

39.2 Recommended DC operating conditions............................................................................................. 438

39.3 Input and output signal DC characteristics..........................................................................................439

39.4 Power supplies.....................................................................................................................................439

39.5 AC characteristics................................................................................................................................441

40 Mechanical description ........................................................................................................458

40.1 Component and package .....................................................................................................................458

40.2 Package placement diagram ................................................................................................................459

40.3 Pin assignment.....................................................................................................................................460

40.4 Package drawing..................................................................................................................................475

41 Temperature and thermal resistance..................................................................................... 479

42 Ordering information ........................................................................................................... 480

43 Silicon Revisions and Errata ................................................................................................ 481

43.1 Overview .............................................................................................................................................481

43.2 Change and errata descriptions........................................................................................................... 482

GR740-UM-DS, Nov 2017, Version 1.7 7 www.cobham.com/gaisler

Page 8

GR740

1 Introduction

1.1 Scope

This document is the preliminary data sheet for the GR740 device. The GR740 was developed in an

activity funded by the European Space Agency.

1.2 Preliminary data sheet limitations

Note that this document is a preliminary data sheet:

• Advanced data sheet - Product in development

• Preliminary data sheet - Shipping prototype

• Data sheet - Shipping space-grade product

1.3 Updates and feedback

Updates are available at http://www.gaisler.com/gr740

Feedback can be sent to Cobham Gaisler AB support: support@gaisler.com

For commercial questions please contact sales@gaisler.com

1.4 Software support

The GR740 design is supported by standard toolchains provided by Cobham Gaisler. Toolchains can

be downloaded from http://www.gaisler.com.

1.5 Development board

A development board with the GR740 device is available. Please see http://www.gaisler.com/gr-cpcigr740.

1.6 Performance, power consumption and radiation tolerance

A technical note on GR740 validation and benchmarking is available at http://www.gaisler.com/

gr740.

GR740-UM-DS, Nov 2017, Version 1.7 8 www.cobham.com/gaisler

Page 9

GR740

1.7 Reference documents

[AMBA] AMBA Specification, Rev 2.0, ARM Limited

[CCSDS] Time Code Formats, CCSDS 301.0-B-4, Blue Book, Issue 4, Novem-

[FTMBCH] FTMCTRL: BCH EDAC with multiple 8-bit wide PROM and SRAM

[RMAP] Space engineering: SpaceWire - Remote memory access protocol,

[GR-AN-0004] Handling of External Memory EDAC Errors in LEON/GRLIB Sys-

[SPARC] The SPARC Architecture Manual, Version 8, SPARC International

[SPW] Space engineering: SpaceWire - Links, nodes, routers and networks,

[SPWBT] Booting a LEON system over SpaceWire RMAP, GRLIB-AN-0002,

[SPWCUC] High Accuracy Time Synchronization over SpaceWire Networks,

ber 2010, http://www.CCSDS.org

banks, GRLIB-AN-0003, http://www.gaisler.com/notes

ECSS-E-ST-50-52C, February 2010

tems, GRLIB-AN-0004, http://www.gaisler.com/notes

Inc.

ECSS-E-ST-50-12C, July 2008

http://www.gaisler.com/notes

SPWCUC-REP-0003, Version 1.1, September 2012

[SPWD] SpaceWire-D - Deterministic Control and Data Delivery over Space-

Wire Networks, Draft B, April 2010, ESA Contract Number 22077407-NL/LvH

[SPWID] Space engineering: SpaceWire Protocol Identification, ECSS-E-ST-

50-51C, 5 February 2010

[SPWINT] Yuriy Sheynin, Distributed Interrupts in SpaceWire Interconnections,

International SpaceWire Conference, Nara, November 2008 (outdated)

[SPWPNP] Space Engineering: SpaceWire Plug-and-Play protocol, ECSS-E-ST-

50-54C, Draft, March 2013

[V8E] SPARC-V8 Supplement, SPARC-V8 Embedded (V8E) Architecture

Specification, SPARC-V8E, Version 1.0, SPARC International Inc.

GR740-UM-DS, Nov 2017, Version 1.7 9 www.cobham.com/gaisler

Page 10

GR740

1.8 Document revision history

Change record information is provided in table 1.

Table 1. Change record

Version Date Note

1.0 2015 April First public release of GR740 document.

1.1 2015 November Fix typo of CE/NE bit in AHBSTAT section.

1.2 2016 January Correct name of TOV field in DSU Instruction trace buffer control register 1

1.3 2016 February Correct information on LEON4 AMBA access size in section 6.7.4.

1.4 2016 June Change status from advanced to preliminary data sheet

Clarify that Level-2 cache is unified.

Correct L4STAT section 26.1 to state that the unit has sixteen counters.

Correct GRSPWROUTER documentation: Error in the description of the ICODEGEN register. The UA bit is independent of the setting of the AH bit. It is not required for AH to be set

in order for UA to have effect.

Corrected AHBTRACE TIMETAG register APB address offset in table caption.

Corrected MEMSCRUB APB address offsets in table captions for two last range registers.

Corrected SPICTRL MASK register access attributes.

Added missing reset values for L2C Scrub delay register and Access control register.

Document TCTRL register WS and WN fields in timer unit section.

Correct reset value for LEON4 %asr17.DBP, CCTRL.DS and %tbr.

Update pinlist in section 40.3

Updated front page and back page.

Converted to new headers and footers.

Corrected description for EDCL 1 bootstrap signals (GPIO[5:4])

Corrected register table headings and add value for trace buffer FDEPTH field in GRPCI2

section 20.

Add note about pulsed interrupts in interrupt controller section

Update footer

Correct typos in %ASR22-23 description in section 6.10.3

Correct typo on Memory scrubber Error Threshold registers, BECTE field.

Add package drawing in section 40.4.

Correct to PCIMODE_ENABLE=HIGH in table 27, row 1, column 3.

Correct Level-2 cache tag and checkbit register layout in section 9.4

Correct SDCFG2 register reference in section 10.4.6.

Correct reference to description of tick-out connection SpaceWire router register descriptions under section 13.4.8.

Added description in section 4.11 of how to handle Ethernet TXCLK and mode switch to

Gigabit operation.

Clarify in section 29.1 that temperature sensor is disabled on current prototype and engineering model devices.

Update description of GRGPIO IFLAG register in section 22.3.10.

Add note about development board in new section 1.5.

Clarify trace point usage in sections 6.9.1 and 33.4.

Clarify in section 13.5.3 that SpaceWire router RTR.RTCOMB register is only accessible via

RMAP.

Rephrase unified cache description in Level-2 cache section 9.1.

Update Level-2 cache error injection description in sections 9.3.6 and 9.4.5.

Minor updates to supplies in section 39.

GR740-UM-DS, Nov 2017, Version 1.7 10 www.cobham.com/gaisler

Page 11

GR740

Table 1.

Version Date Note

1.5 2016 November Update system frequency and package types on front page.

1.6 2017 March Update feature list on front page to mark interfaces subject to pin sharing.

Change record

Add bootstrap signal requirement for flight (section 3.2) and pin driver configuration (3.5)

Add note that it is the top part of the data bus that is used for PROM in 8-bit mode in section

3.3.1.

Restructure pin multiplexing tables 24,25,27 to have consistent naming with table 28.

Correct missing PROMIO_READ signal in table 28

Correct maximum number of SDRAM banks supported (4) in section 10.1, correct register

name in 10.5.4

Rename section 15 to Spacewire Debug Link for clarity.

Revised GRSPWROUTER section 13 for readability.

Add note that GPTIMER TCTRL LD is automatically cleared after load in section 20.3.

Major update to electrical characteristics section 39, update list of parameters, add power-up/

down sequencing, cold sparing, add MDIO diagram, update clock table, reference internal

clocks in diagrams, update thermal information and AC limits.

Add errata in section 43.

Update SpaceWire link speed on front page

Changed title of GRSPW2 (SpaceWire Debug Link) section

Clarify signal names in pin-multiplexing tables 24 and 25.

Add pin driver configuration section 3.5, add reference in section 13.1.

Remove references to PC133 SDRAM operation.

Added placement diagram in section 40.2.

Removed LEON4 section on partial WRPSR (unsupported due to errata)

Update section 1.1 (Scope).

Move description of Debug AHB bus and corresponding controller documentation to be last

bus described in document. This modifies section numbers for section 12 to 36.

Change order of IOMMU and SpaceWire router sections.

Update errata section 43 overview, added LVDS ESD sensitivity erratum.

Correct UART1_RXD signal name in table 24.

Added section 1.6 with reference to technical note on validation and benchmarking.

Updates under section 12 to clarify that bus selection can be made even if IOMMU is disabled.

Describe planned package dimension change in section 40.4.

Note that TESTEN should be connected to ground in section 3.4

Correct PCI_HOSTN signal name typo in table 27.

Correct PCIMODE_ENABLE heading in table 27.

Effect of bootstrap signal GPIO[15] was inverted. LOW enables full PROM/IO interface,

corrected in table 23 and section 3.3.1.

GR740-UM-DS, Nov 2017, Version 1.7 11 www.cobham.com/gaisler

Page 12

GR740

Table 1. Change record

Version Date Note

1.7 2017 November Updated ordering information in section 42.

Updated placement diagram under section 40.

Add new package drawings in section 40.4.

Add information on booting over RMAP, changes in sections 1.7 and 5.3.

Add information about bridges, posted writes and AMBA ERROR response propagation to

sections 2.3, 5.10, 6.2.13, 6.3.5, 6.7.4, 10.5.1, 13.4.4.9, 13.4.5.7.2, 14.3.3, 14.4.4, 15.4.4,

16.4.5, 17.6.6, 19.7.1, 19.7.2, 19.8, 19.9, 35.5.9, 35.6.7, 35.7.2, 35.8.2, 35.9, 37.2.2.

Add information on PROM EDAC handling with multiple external devices in section 1.7

and 19.7.1.

Change errata section 43 to also include design changes between silicon revisions. Update

and add additional errata descriptions. Add silicon revision 1 column in table 602.

Document new L2 cache register fields in section 9.4.

Add partial WRPSR description to LEON4 section 6.2.16.

Extend LEON4 MMU TLB disable description in section 6.10.8.

Describe new IRQMP boot/monitor interface in sections 21.2.10 and 21.3.

Update GRGPIO interrupt flag register description in section 22.3.10.

Added description of AHB status register multiple error logging and filtering in section 27.

Correct number of up-counter bits in section 5.9.2.

Clarify timetag counter behaviour in sections 6.10.4 and 36.1.

Document PCI controller DFA bit in section 15.10.1.

Clarify PCI target supported byte-enables in section 15.5.3.

Update PCI DMA controller description in section 15.6.3.

Update register for bootstrap signals description in section 28.3 for silicon revision 1.

Add reference to GRLIB-AN-0004 in sections 1.7 and 6.11.4.

Indicate AHB and instruction trace buffer sizes in section 2.1.

Add note about using the MMU to mark memory as cacheable in section 6.3.6.

Describe SDRAM bus parking functionality in section 10.6.2.

Update description of SDRAM controller BANKSZ field in section 10.6.1.

Clarifications about internal and external SDRAM banks under section 10.

Update SpaceWire router configuration port memory range in sections 2.3 and 13.5.3.

Document SpaceWire router AMBA port interrupt in section 2.4 and table 193.

Describe SpaceWire TDP functionality added for silicon revision 1 in sections 3.1, 5.9.2, and

31.

Added information on SpaceWire receive rate in section 13.3.1.2. Clarify that t

t

in table 587 are valid assuming use of SpW PLL in nominal mode.

SPW5

Extend section 5.5 ASMP configurations to 5.5 Separation and ASMP configurations.

Add description of LEON4 %ASR16 register in section 6.10.2.

Updated LEON4 %ASR17 description in section 6.10.3.

Corrected range and recommended values of RTR.AMBADMACTRL.INTNUM register in

table 160.

Corrected range of RTR.ICODEGEN.IN register in table 193.

Update temperature sensor controller documentation in section 29.

Corrected field ranges in SPI controller mode register description in table 421.

Updated package references to CCGA/LGA on front page and in sections 40 and 42.

Update processor status monitoring description in 21.2.4.

Clarify that PROC_ERRORN is connected to processor 0 only, in section 6.2.13

Clarify bootstrap signal effects in section 3.1. Clarify that GPIO[7:6] are still used to disable

EDCL 1. Update clock gate unit conditions in section 25.

Add GRLIB-TN-0013 issue in section 43.2.27.

Clarify that WDOGN and ERRORN are open-drain in tables 28 and 597.

Updated Absolute Maximum Ratings and recommended operating conditions, adding overshoot specifications, in section 39.

SPW4

and

GR740-UM-DS, Nov 2017, Version 1.7 12 www.cobham.com/gaisler

Page 13

GR740

1.9 Acronyms

Table 2. Acronyms

Acronym Comment

AHB Advanced High-performance bus, part of [AMBA]

AMBA Advanced Microcontroller Bus Architecture

AMP See ASMP

APB Advanced Peripheral Bus, part of [AMBA]

ASMP Asymmetric Multi-Processing (in the context of this document: different OS instances run-

ning on own processor cores)

BCH Bose-Hocquenghem-Chaudhuri, class of error-correcting codes

CAN Controller Area Network, bus standard

CPU Central Processing Unit, used to refer to one LEON4 processor core.

DCL Debug Communication Link. Provides a bridge between an external interface and on-chip

AHB bus.

DDR Double Data Rate

DMA Direct Memory Access

DSU Debug Support Unit

EDAC Error Detection and Correction

EDCL Ethernet Debug Communication Link

FIFO First-In-First-Out, refers to buffer type

FPU Floating Point Unit

Gb

GB

GiB

Gigabit, 10

Gigabyte, 10

Gibibyte, gigabinary byte, 2

9

bits

9

bytes

30

bytes, unit defined in IEEE 1541-200

I/O Input/Output

IP, IPv4 Internet Protocol (version 4)

ISR Interrupt Service Routine

JTAG Joint Test Action Group (developer of IEEE Standard 1149.1-1990)

kB

KiB

Kilobyte, 10

Kibibyte, 2

3

bytes

10

bytes, unit defined in IEEE 1541-2002

L2 Level-2, used in L2 cache abbreviation

MAC Media Access Controller

Mb, Mbit

MB, Mbyte

MiB

Megabit, 10

Megabyte, 10

Mebibyte, 2

6

bits

6

bytes

20

bytes, unit defined in IEEE 1541-2002

OS Operating System

PCI Peripheral Component Interconnect

PROM Programmable Read Only Memory. In this document used to signify boot-PROM.

RAM Random Access Memory

RMAP Remote Memory Access Protocol

SEE Single Event Effects

SEL/SEU/SET Single Event Latchup/Upset/Transient

GR740-UM-DS, Nov 2017, Version 1.7 13 www.cobham.com/gaisler

Page 14

GR740

Table 2. Acronyms

1.10 Definitions

This section and the following subsections define the typographic and naming conventions used

throughout this document.

1.10.1 Bit numbering

The following conventions are used for bit numbering:

• The most significant bit (MSb) of a data type has the leftmost position

• The least significant bit of a data type has the rightmost position

Acronym Comment

SMP Symmetric Multi-Processing

SPARC Scalable Processor ARChitecture

TCP Transmission Control Protocol

UART Universal Asynchronous Receiver/Transmitter

UDP User Datagram Protocol

• Unless otherwise indicated, the MSb of a data type has the highest bit number and the LSb the

lowest bit number

1.10.2 Radix

The following conventions is used for writing numbers:

• Binary numbers are indicated by the prefix "0b", e.g. 0b1010.

• Hexadecimal numbers are indicated by the prefix "0x", e.g. 0xF00F

• Unless a radix is explicitly declared, the number should be considered a decimal.

1.10.3 Data types

Byte (BYTE) 8 bits of data

Halfword (HWORD) 16 bits of data

Word (WORD) 32 bits of data

Double word (DWORD) 64 bits of data

Quad word (4WORD) 128-bits of data

GR740-UM-DS, Nov 2017, Version 1.7 14 www.cobham.com/gaisler

Page 15

GR740

1.11 Register descriptions

An example register, showing the register layout used throughout this document, can be seen

in table 3. The values used for the reset value fields are described in table 4, and the values

used for the field type fields are described in table 5. Fields that are named RESERVED,

RES, or R are read-only fields. These fields can be written with zero or with the value read

from the same register field.

Table 3. <Address> - <Register acronym> - <Register name>

31 24 23 16 15 8 7 0

EF3 EF2 EF1 EF0

<Reset value for EF3> <Reset value for EF2> <Reset value for EF1> <Reset value for EF0>

<Field type for EF3> <Field type for EF2> <Field type for EF1> <Field type for EF0>

31: 24 Example field 3 (EF3) - <Field description>

23: 16 Example field 2 (EF2) - <Field description>

15: 8 Example field 1 (EF1) - <Field description>

7: 0 Example field 0 (EF0) - <Field description>

Table 4. Reset value definitions

Value Description

0 Reset value 0.

1 Reset value 1. Used for single-bit fields.

0xNN Hexadecimal representation of reset value. Used for multi-bit fields.

0bNN Binary representation of reset value. Used for multi-bit fields.

NR Field not reset

* Special reset condition, described in textual description of the field. Used for example when reset

value is taken from a pin.

- Don’t care / Not applicable

Table 5. Field type definitions

Value Description

r Read-only. Writes have no effect.

w Write-only. Used for a writable field in a register where the field’s read-value has no meaning.

rw Readable and writable.

rw* Readable and writable. Special condition for write, described in textual description of field.

wc Write-clear. Readable, and cleared when written with a 1

cas Readable, and writable through compare-and-swap. Only applies to SpaceWire Plug-and-Play regis-

ters.

GR740-UM-DS, Nov 2017, Version 1.7 15 www.cobham.com/gaisler

Page 16

GR740

2 Architecture

2.1 Overview

The system is built around five AMBA AHB buses; one 128-bit Processor AHB bus, one 128-bit

Memory AHB bus, two 32-bit I/O AHB buses and one 32-bit Debug AHB bus. The Processor AHB

bus houses four LEON4FT processor cores connected to a shared L2 cache. The Memory AHB bus is

located between the L2 cache and the main external memory interface (SDRAM) and attaches a memory scrubber.

The two separate I/O AHB buses connect peripherals. Slave interfaces of the PCI master/target and

PROM/IO memory controller are placed on one bus (Slave I/O AHB bus). All master/DMA interfaces

are placed on the other bus (Master I/O AHB bus). The Master I/O AHB bus connects to the Processor

AHB bus via an AHB/AHB bridge that provides access restriction and address translation (IOMMU)

functionality. The IOMMU also has an AHB master interface connected to the Memory AHB bus.

The AHB master interface to use when propagating traffic from a peripheral on the Master I/O AHB

bus is dynamically configurable.

Peripheral unit register interfaces such as timers, interrupt controllers, UARTs, general purpose I/O

port, SPI controller, MIL-STD-1553B interface, Ethernet MACs, CAN controllers, and SpaceWire

router AMBA interfaces are connected via two AHB/APB bridges that are attached to the Processor

AHB bus.

The fifth bus, a dedicated 32-bit Debug AHB bus, connects a debug support unit (DSU), one AHB

trace buffer monitoring the Master I/O AHB bus and several debug communication links. The Debug

AHB bus allows for non-intrusive debugging through the DSU and direct access to the complete system, as the Debug AHB bus is not placed behind an AHB bridge with access restriction functionality.

The chapters in this document have been grouped after the bus topology. The first chapters describe

components connected to the Processor AHB bus, followed by the Memory AHB bus, Master I/O

AHB bus and finally Slave I/O AHB bus, APB buses and Debug AHB bus.

GR740-UM-DS, Nov 2017, Version 1.7 16 www.cobham.com/gaisler

Page 17

GR740

The GR740 has the following on-chip functions:

• 4x LEON4 SPARC V8 processor cores with MMU and GRFPU floating-point unit

• Level-2 cache, 4-ways, BCH protection, supports locking of 1-4 ways

• Debug Support Unit (DSU) with instruction (512 lines) and AHB trace (256 lines) buffers

• Ethernet, JTAG and SpaceWire debug communication links

• 96-bit PC100 SDRAM memory controller with Reed-Solomon EDAC

• Hardware memory scrubber

• 8/16-bit PROM/IO controller with BCH EDAC

• I/O Memory Management Unit (IOMMU) with support for eight groups of DMA units

• 8-port SpaceWire router/switch with four on-chip AMBA ports with RMAP

• SpaceWire TDP controller

• 2x 10/100/1000 Mbit Ethernet MAC

• 32-bit 33 MHz PCI master/target interface with DMA engine

• MIL-STD-1553B interface controller

• 2x CAN 2.0B controllers

•2x UART

• SPI master/slave controller

• Interrupt controller with extended support for asymmetric multiprocessing

• 1x Timer unit with five timers, time latch/set functionality and watchdog functionality

• 4x Timer unit with four timers and time latch/set functionality

• Separate AHB and PCI trace buffers

• Temperature sensor

• Clock gating unit

• LEON4 statistics unit (performance counters)

• Pad and PLL control unit

• AHB status registers

GR740-UM-DS, Nov 2017, Version 1.7 17 www.cobham.com/gaisler

Page 18

GR740

2.2 Cores

The design is based on the following IP cores from the GRLIB IP Library:

Table 6. Used IP cores

Documented in

Core Function

AHB2AHB Uni-directional AHB/AHB bridge 32, 18 0x01 0x020

AHBJTAG JTAG/AHB Debug interface 34 0x01 0x01C

AHBSTAT AHB Status Register 27 0x01 0x052

AHBTRACE AHB trace buffer 36 0x01 0x017

APBCTRL AHB/APB bridge 38 0x01 0x006

IRQ(A)MP Multiprocessor interrupt controller 21 0x01 0x00D

APBUART 8-bit UART with FIFO 23 0x01 0x00C

DSU4 LEON4 Debug Support Unit 33 0x01 0x049

MMCTRL Memory controller 10 0x01 0x05D

GPTIMER Modular timer unit with watchdog 20 0x01 0x011

GR1553B MIL-STD-1553B / AS15531 interface 16 0x01 0x04D

GRCAN CAN 2.0 controller with DMA 17 0x01 0x03D

GRCLKGATE Clock gating unit 25 0x01 0x02C

GRETH_GBIT 10/100/1000 Ethernet MAC with DCL 14 0x01 0x01D

GRGPIO General Purpose I/O Port 22 0x01 0x01A

GRGPRBANK General Purpose Register Bank 30 0x01 0x08F

GRGPREG General Purpose Register 28 0x01 0x087

GRIOMMU AHB/AHB bridge with protection (IOMMU) 12 0x01 0x04F

GRPCI2 Fast 32-bit PCI bridge 15 0x01 0x07C

GRSPW2 SpaceWire codec with RMAP 35 0x01 0x029

GRSPWROUTER SpaceWire router switch 13 0x01 0x08B

GRSPWTDP SpaceWire - Time Distribution Protocol 31 0x01 0x097

FTMCTRL 8/16/32-bit memory controller with EDAC 19 0x01 0x054

L2CACHE Level 2 cache 9 0x01 0x04B

L4STAT LEON4 statistical unit 26 0x01 0x047

LEON4 LEON4 SPARC V8 32-bit processor 6 0x01 0x048

MEMSCRUB Memory scrubber 11 0x01 0x057

SPICTRL SPI controller 24 0x01 0x02D

GR740THSENS GR740 Temperature sensor controller 29 0x01 0x099

section Vendor Device

The information in the last two columns is available via plug’n’play information in the system and is

used by software to detect units and to initialize software drivers.

GR740-UM-DS, Nov 2017, Version 1.7 18 www.cobham.com/gaisler

Page 19

GR740

2.3 Memory map

The memory map of the internal AHB and APB buses as seen from the processor cores can be seen

below. Software does not need to be aware that a bridge is positioned between the processor and a

peripheral since the address mapping between buses is one-to-one.

Table 7. AMBA memory map, as seen from processors

Component Address range Area Bus

L2CACHE 0x00000000 - 0x7FFFFFFF L2 cache memory area. Covers

GRPCI2 0x80000000 - 0xBFFFFFFF PCI memory area Slave I/O

FTMCTRL 0xC0000000 - 0xCFFFFFFF

L2CACHE 0xF0000000 - 0xF03FFFFF L2 cache configuration registers Processor

GRPCI2 0xFF800000 - 0xFF83FFFF PCI I/O area Slave I/O

GRIOMMU 0xFF840000 - 0xFF847FFF IOMMU configuration registers Slave I/O

GRSPWROUTER 0xFF880000 - 0xFF881FFF SpaceWire router configuration port

APBBRIDGE0 0xFF900000 - 0xFF9FFFFF APB bridge 0 Processor

A

P

B

B

R

I

D

G

E

0

APBBRIDGE1 0xFFA00000 - 0xFFAFFFFF APB bridge 1 Processor

Processor

SDRAM memory area.

PROM area

0xD0000000 - 0xDFFFFFFF

0xE0000000 - 0xEFFFFFFF Unused. This memory range is occu-

0xF0400000 - 0xFF7FFFFF Unused Processor

0xFF848000 - 0xFF87FFFF Unused Slave I/O

0xFF882000 - 0xFF8FEFFF Unused Slave I/O

0xFF8FF000 - 0xFF8FFFFF Slave I/O bus plug&play area Slave I/O

APBUART0 0xFF900000 - 0xFF9000FF UART 0 registers Processor

APBUART1 0xFF901000 - 0xFF9010FF UART 1 registers Processor

GRGPIO0 0xFF902000 - 0xFF9020FF General purpose I/O port registers Processor

FTMCTRL 0xFF903000 - 0xFF9030FF PROM/IO controller registers Processor

IRQ(A)MP 0xFF904000 - 0xFF907FFF Interrupt controller registers Processor

GPTIMER0 0xFF908000 - 0xFF9080FF Timer unit 0 registers Processor

GPTIMER1 0xFF909000 - 0xFF9090FF Timer unit 1 registers Processor

GPTIMER2 0xFF90A000 - 0xFF90A0FF Timer unit 2 registers Processor

GPTIMER3 0xFF90B000 - 0xFF90B0FF Timer unit 3 registers Processor

GPTIMER4 0xFF90C000 - 0xFF90C0FF Timer unit 4 registers Processor

GRSPWROUTER 0xFF90D000 - 0xFF90DFFF SpaceWire router AMBA interface 0 Processor

GRSPWROUTER 0xFF90E000 - 0xFF90EFFF SpaceWire router AMBA interface 1 Processor

GRSPWROUTER 0xFF90F000 - 0xFF90FFFF SpaceWire router AMBA interface 2 Processor

GRSPWROUTER 0xFF910000 - 0xFF910FFF SpaceWire router AMBA interface 3 Processor

GRETH_GBIT0 0xFF940000 - 0xFF9400FF Gigabit Ethernet MAC 0 registers Processor

GRETH_GBIT1 0xFF980000 - 0xFF9800FF Gigabit Ethernet MAC 1 registers Processor

APBBRIDGE0 0xFF990000 - 0xFF9FFEFF Unused Processor

APBBRIDGE0 0xFF9FF000 - 0xFF9FFFFF APB bus 0 plug&play area Processor

Memory mapped I/O area

pied on the Debug AHB bus and is

not visible from the processors. A

separate table below shows the mapping.

Note: Silicon revision 0 maps the

area 0xFF880000 - 0xFF880FFF.

See section 43.2.23.

Slave I/O

Processor

Slave I/O

GR740-UM-DS, Nov 2017, Version 1.7 19 www.cobham.com/gaisler

Page 20

GR740

Table 7. AMBA memory map, as seen from processors

Component Address range Area Bus

A

GRPCI2 0xFFA00000 - 0xFFA000FF PCI controller registers Processor

P

GRCAN0 0xFFA01000 - 0xFFA013FF CAN 2.0 controller 0 Processor

B

GRCAN1 0xFFA02000 - 0xFFA023FF CAN 2.0 controller 1 Processor

B

SPICTRL 0xFFA03000 - 0xFFA030FF SPI controller Processor

R

GRCLKGATE 0xFFA04000 - 0xFFA040FF Clock gating unit Processor

I

GR1553B 0xFFA05000 - 0xFFA050FF MIL-STD-1553B controller Processor

D

AHBSTAT0 0xFFA06000 - 0xFFA060FF AHB status register monitoring Pro-

G

AHBSTAT1 0xFFA07000 - 0xFFA070FF AHB status register monitoring

E

1

GRGPIO1 0xFFA08000 - 0xFFA080FF General purpose I/O register for mul-

GRGPREG 0xFFA09000 - 0xFFA090FF Register for bootstrap signals Processor

GR740THSENS 0xFFA0A000 - 0xFFA0A0FF Temperature sensor Processor

GRGPRBANK 0xFFA0B000 - 0xFFA0B0FF General purpose register bank Processor

GRSPWTDP 0xFFA0C000 - 0xFFA0C1FF CCSDS TDP controller Processor

L4STAT 0xFFA0D000 - 0xFFA0D1FF LEON4 Statistics Unit Processor

APBBRIDGE1 0xFFA0D200 - 0xFFAFFEFF Unused Processor

APBBRIDGE1 0xFFAFF000 - 0xFFAFFFFF APB bus 1 plug&play area Processor

0xFFB00000 - 0xFFDFFFFF Unused Processor

MMCTRL 0xFFE00000 - 0xFFE000FF SDRAM controller registers Memory

0xFFE00100 - 0xFFE00FFF Unused Memory

MEMSCRUB 0xFFE01000 - 0xFFE010FF Memory scrubber registers Memory

0xFFE01100 - 0xFFEFEFFF Unused Memory

0xFFEFF000 - 0xFFEFFFFF Memory bus plug&play area Memory

0xFFF00000 - 0xFFFFEFFF Unused Processor

0xFFFFF000 - 0xFFFFFFFF Processor bus plug&play area Processor

cessor AHB bus

Slave I/O AHB bus

tiplexed pins.

Processor

Processor

Processor

When connecting to the system via one of the debug communication links (JTAG, Ethernet, USB, or

SpaceWire) connected to the Debug AHB bus, several debug support peripherals will be visible.

Table 8 below lists the address map of these peripherals. Note that peripherals in the address range

0xE0000000 - 0xEFFFFFFF are not accessible from the processors or from any peripherals on the

Master I/O AHB bus. Accesses to this range from any peripheral not located on the Debug AHB bus

will result in an AMBA ERROR response (see also the AMBA ERROR propagation description in

section 5.10.). Apart from the area 0xE0000000 - 0xEFFFFFFF, the AMBA memory space seen via

the debug communication links is identical to the address space seen from other master in the system.

Accesses to unused AMBA AHB address space will result in an AMBA ERROR response, this

applies to the memory areas that are marked as "Unused" in the table above. Accesses to unused areas

located on one of the AHB/APB bridges will not have any effect, note that these unoccupied address

ranges are not

marked as "Unused" in the table above. No AMBA ERROR response will be given for

memory allocated to one of the APB bridges. See also the AMBA ERROR propagation description in

section 5.10.

GR740-UM-DS, Nov 2017, Version 1.7 20 www.cobham.com/gaisler

Page 21

GR740

Table 8. AMBA address range 0xE0000000 - 0xEFFFFFFF on Debug AHB bus

Peripheral Address range Comment

DSU4 0xE0000000 - 0xE07FFFFF

0xE1000000 - 0xE17FFFFF

0xE2000000 - 0xE27FFFFF

0xE3000000 - 0xE37FFFFF

APBBRIDGED 0xE4000400 - 0xE40FFFFF APB bridge on Debug AHB bus

A

GRSPW2 0xE4000000 - 0xE40000FF SpaceWire RMAP target with AMBA interface

P

L4STAT 0xE4000200 - 0xE40003FF LEON4 Statistics unit, secondary port

B

APBBRIDGED 0xE4000200 - 0xE403FFFF Unused

D

GRPCI2 0xE4040000 - 0xE407FFFF GRPCI2 secondary PCI trace buffer interface

APBBRIDGED 0xE4080000 - 0xE40FFEFF Unused

APBBRIDGED 0xE40FFF00 - 0xE40FFFFF Debug APB bus plug&play area

0xE4100000 - 0xEEFFFFFF Unused

AHBTRACE 0xEFF00000 - 0xEFF1FFFF AHB trace buffer, tracing master I/O AHB bus

0xEFF20000 - 0xEFFFEFFF Unused

0xEFFFF000 - 0xEFFFFFFF Debug AHB bus plug&play area

Debug Support Unit area for processor 0

Debug Support Unit area for processor 1

Debug Support Unit area for processor 2

Debug Support Unit area for processor 3

GR740-UM-DS, Nov 2017, Version 1.7 21 www.cobham.com/gaisler

Page 22

GR740

2.4 Interrupts

The table below indicates the interrupt assignments. Note that the table below describes interrupt bus

lines, these can be remapped in the interrupt controller.

Table 9. Interrupt assignments

Interrupt Peripheral Comment

1 GPTIMER0 GPTIMER unit 0, timer 1

2 GPTIMER0 GPTIMER unit 0, timer 2

3 GPTIMER0 GPTIMER unit 0, timer 3

4 GPTIMER0 GPTIMER unit 0, timer 4

5 GPTIMER0 GPTIMER unit 0, timer 5

6 GPTIMER1 Shared interrupt for all timers on GPTIMER unit 1

7 GPTIMER2 Shared interrupt for all timers on GPTIMER unit 2

8 GPTIMER3 Shared interrupt for all timers on GPTIMER unit 3

9 GPTIMER4 Shared interrupt for all timers on GPTIMER unit 4

10 IRQ(A)MP Extended interrupt line.

11 GRPCI/PCIDMA PCI master/target and PCI DMA

12 Unassigned Suitable for use by software for inter-processor and

13 Unassigned

14 Unassigned

15 Unassigned Note: Not maskable by processor

16 GRGPIO0 /1 / CAN The GPIO port has configuration registers that deter-

17 GRGPIO0 /1 / CAN

18 GRGPIO0 /1 / CAN

19 GRGPIO0/1/ SPICTRL

20 SPWROUTER AMBA I/F 0 SpaceWire router AMBA interface 0

21 SPWROUTER AMBA I/F 1 SpaceWire router AMBA interface 1

22 SPWROUTER AMBA I/F 2 SpaceWire router AMBA interface 2

23 SPWROUTER AMBA I/F 3 SpaceWire router AMBA interface 3

24 GRETH_GBIT0 Gigabit Ethernet MAC 0

25 GRETH_GBIT1 Gigabit Ethernet MAC 1

26 GR1553B MIL-STD-1553B interface controller

27 AHBSTAT/ST65THSENS Shared by all AHB Status registers in design and by

28 MEMSCRUB/L2CACHE Memory scrubber and L2 cache

29 APBUART0 UART 0

30 APBUART1 UART 1

31 GRIOMMU / GRSPWTDP /

SPWROUTER

inter-process synchronization.

mine the mapping between general purpose I/O lines

and the four interrupt lines allocated to the GPIO port.

Interrupt lines 16 -18 are shared between the GPIO port

and CAN controllers.

Interrupt line 19 is shared between the GPIO port and

the SPI controller.

temperature sensor.

IOMMU register interface interrupt.

CCSDS TDP controller interrupt

SpaceWire router AMBA configuration port interrupt

(only applies to silicon revision 1)

2.5 Plug & play and bus index information

The format of GRLIB AMBA Plug&play information is given in sections 37 and 38. The address

ranges of the plug&play configuration areas are given in the preceding section and is also replicated

GR740-UM-DS, Nov 2017, Version 1.7 22 www.cobham.com/gaisler

Page 23

GR740

for each unit in the tables below. The plug&play areas are used by software to detect the system-onchip architecture. The values in the tables below are fixed. The tables also include the bus indexes for

all masters and slaves on the system’s AHB and APB buses.

The plug & play memory map and bus indexes for AMBA AHB masters on the Processor AHB bus

are shown in table 10.

Table 10. Plug & play information for masters on Processor AHB bus

Master Index Function Address range

LEON4 0 LEON4 SPARC V8 Processor 0xFFFFF000 - 0xFFFFF01F

LEON4 1 LEON4 SPARC V8 Processor 0xFFFFF020 - 0xFFFFF03F

LEON4 2 LEON4 SPARC V8 Processor 0xFFFFF040 - 0xFFFFF05F

LEON4 3 LEON4 SPARC V8 Processor 0xFFFFF060 - 0xFFFFF07F

GRIOMMU 4 AHB/AHB bridge with protection functionality 0xFFFFF080 - 0xFFFFF09F

AHB2AHB 5 Uni-directional AHB/AHB bridge connecting Debug

AHB bus to Processor AHB bus

0xFFFFF0B0 - 0xFFFFF0BF

The plug & play memory map and bus indexes for AMBA AHB slaves on the Processor AHB bus are

shown in table 11.

Table 11. Plug & play information for slaves on Processor AHB bus

Slave Index Function Address range

L2CACHE 0 Level 2 cache 0xFFFFF800 - 0xFFFFF81F

AHB2AHB 1 Uni-directional AHB/AHB bridge connecting Proces-