Page 1

GR716

LEON3FT Microcontroller

2019 Advanced Data Sheet and User’s Manual

The most important thing we build is trust

Features

• Fault-tolerant SPARC V8 processor with 31 register

windows, 192KiB EDAC protected tightly coupled

memory and support for reduced instruction set.

• Double precision IEEE-754 floating point unit

• Advanced on-chip debug support unit

• Memory protection units

• 8-bit external PROM/SRAM interface with BCH EDAC

protection

• Boot from external SRAM/PROM, SPI or I

2

C memory

protected by EDAC and dual memory redundancy

• SpaceWire interface with time distribution support

• SPI for Space master and slave interface

• MIL-STD-1553B interface

• CAN 2.0B controller interface

• PacketWire with CRC acceleration support

• On-chip 12-bit DAC and two 11-bit ADC

• Programmable PWM interface

• UARTs, SPI, I

2

C, GPIO, Timers with Watchdog, Inter-

rupt controller, Status registers, UART debug, etc.

• Configurable I/O switch matrix

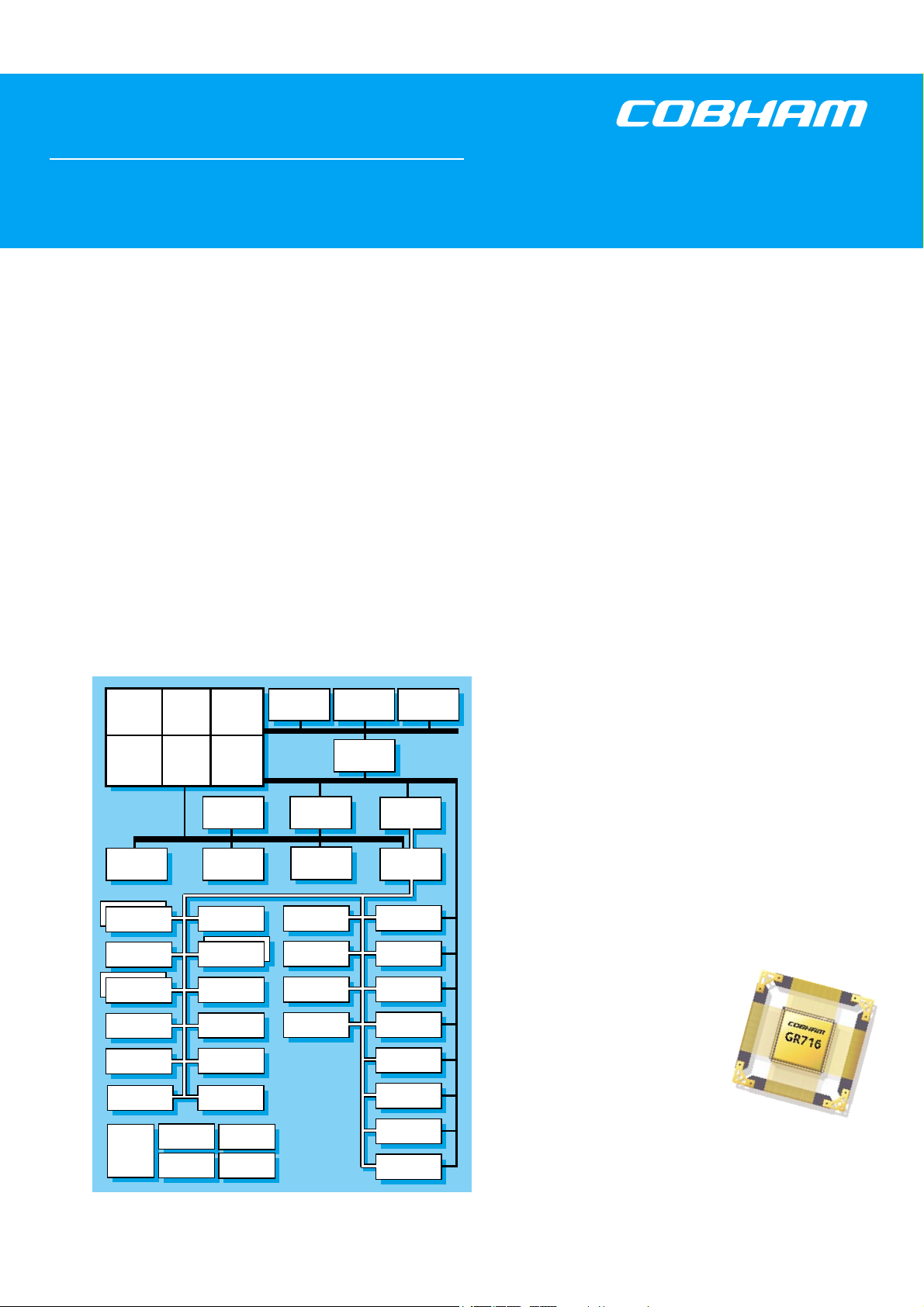

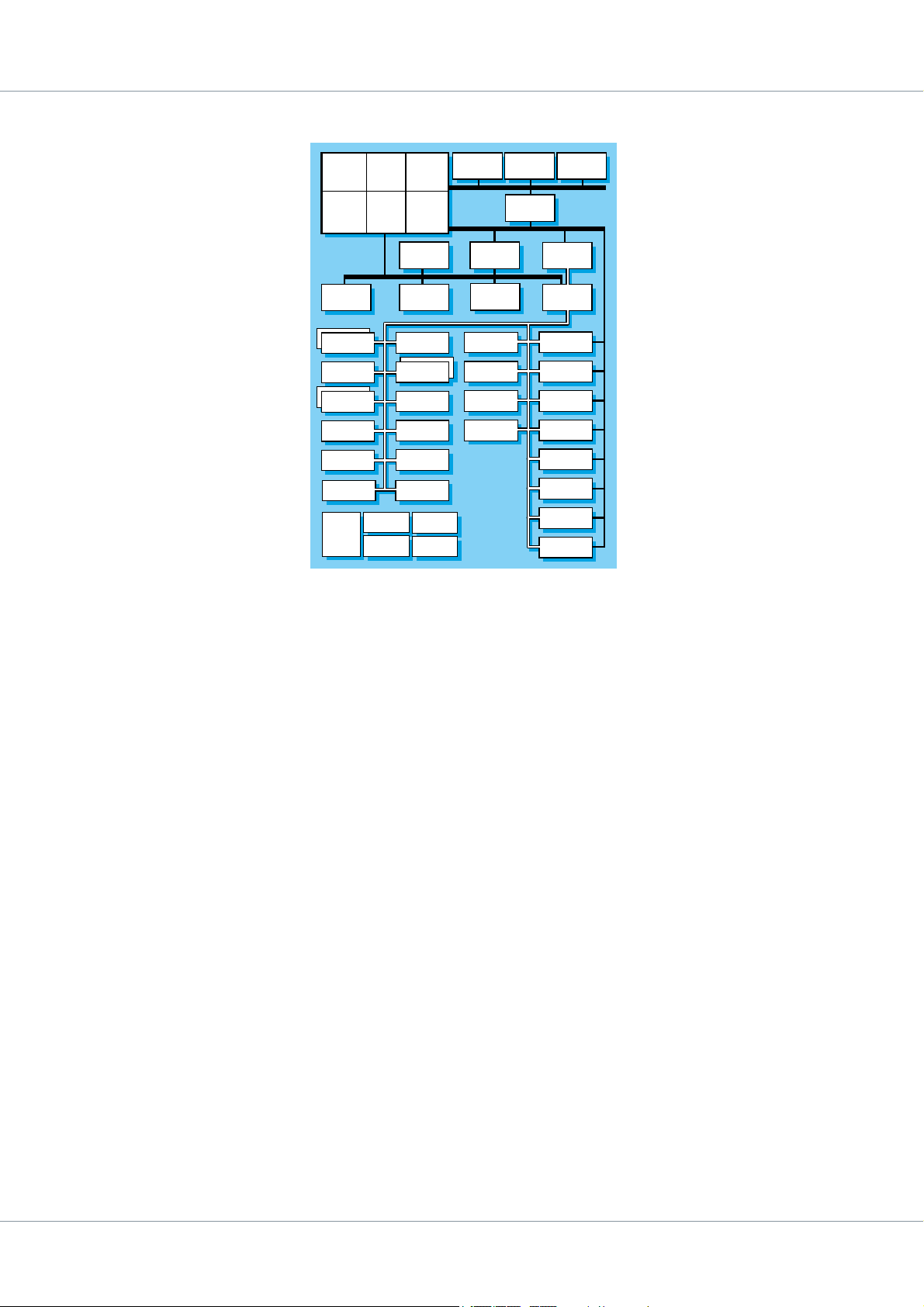

Floating

Point

Unit

Local

Dual-port

Instruction

RAM

Main bus

FTMCTRL

UART

I2CMST /

I2CSLV

SPICTRL

GRGPIO

GRPULSE

GRPWM

On-chip

LDO

Integer

Unit

AMBA

Interface

On-chip

Oscillator

PLL

Debug

Support

Unit

Local

Dual-port

Data

RAM

Memory

Scrubber

SPIMCTRL

IRQ Control

Timers

AHBSTAT

GRADCDAC

On-chip DAC

On-chip ADC

Brownout

Detector

Power-on

reset

LEON3

Statistics

Unit

Debug bus

DMA bus

AHB2AHB

Bridge

AHBROM

MEMPROT

CLKGATE

GPREG

LSTAT

UART

Dbg Link

AHB2AHB

Bridge

AHB

Trace

DMA

Controller

APBCTRL

Bridges

1553B

SpaceWire

I2C to AHB

SPI to AHB

GRPWRX

(MAP)

GRPWTX

GRCAN

AHB

UART

Description

The GR716 device is a fault-tolerant LEON3

SPARC V8 processor with various communication

interfaces and on-chip ADC, DAC, Power-onReset, Oscillator, Brown-out detection, LVDS

transceivers, regulators to support single 3.3V

supply, ideally suited for space and other high-rel

applications.

Specification

• System frequency up-to 50 MHz

• SpaceWire links up-to 100 Mbps

• CQFP132 hermetically sealed ceramic package

• Total Ionizing Dose (TID) up to 100 krad (Si)

• Single-Event Latch-up Immunity (SEL) to LET

> 118 MeV-cm

• Single-Event Upset (SEU) below 10

2

mg

-6

errors per

TH

device and day in space environment (TBC)

• Support for single 3.3V supply

Applications

The GR716 microcontroller is an advanced microcontroller, targeting high reliability space and aeronautics applications.

Support for many different standard interfaces makes

the GR716 microcontroller ideal for supervision, monitoring and control in a satellite, such as:

• propulsion system control

• sensor bus control

• robotics applications control

• simple motor control

• mechanism control

• power control

• particle detector instrumentation

• radiation environment monitoring

• thermal control

• antenna pointing control

• AOCS / GNC (Gyro, IMU, MTM)

• remote terminal unit control

• simple instrument control

• wireless networking

Availability

The GR716 microcontroller is currently available as engineering samples. Contact Cobham Gaisler for information on flight model schedule.

GR716-DS-UM, May 2019, Version 1.29 www.cobham.com/gaisler

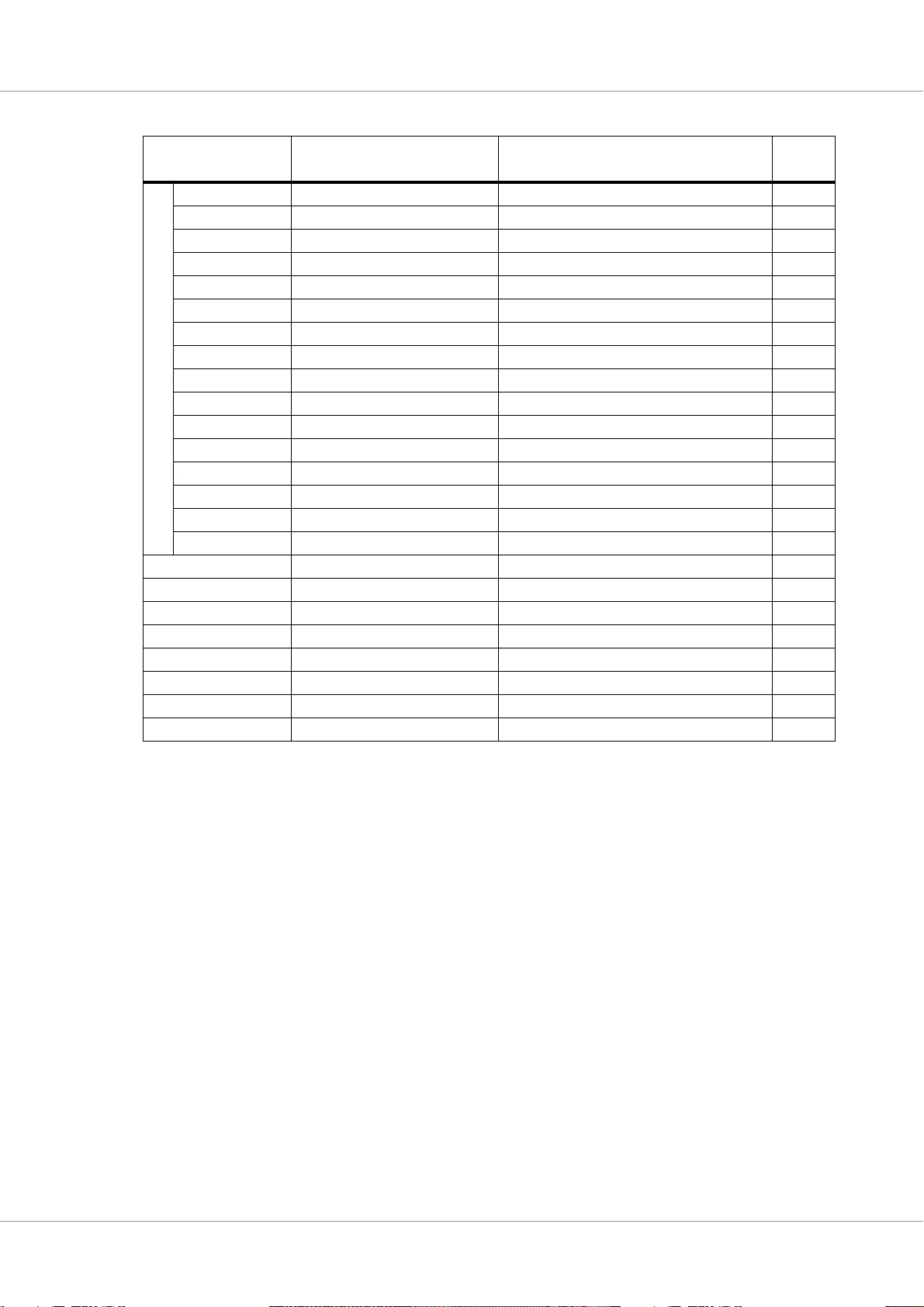

Page 2

GR716

1 Introduction.............................................................................................................................. 9

1.1 Scope .......................................................................................................................................................9

1.2 Data sheet limitations ..............................................................................................................................9

1.3 Updates and feedback.............................................................................................................................. 9

1.4 Software support...................................................................................................................................... 9

1.5 Reference documents ..............................................................................................................................9

1.6 Document revision history .................................................................................................................... 10

1.7 Acronyms ..............................................................................................................................................13

1.8 Definitions .............................................................................................................................................14

1.9 Register descriptions .............................................................................................................................15

2 Architecture............................................................................................................................ 16

2.1 Key features...........................................................................................................................................17

2.2 Digital Architecture Overview .............................................................................................................. 20

2.3 Analog Architecture Overview.............................................................................................................. 28

2.4 Signal Overview....................................................................................................................................32

2.5 I/O switch matrix overview................................................................................................................... 32

2.6 I/O switch default configurations for bootstraps...................................................................................35

2.7 I/O switch matrix options, considerations and limitations .................................................................... 38

2.8 I/O switch matrix pin validation script.................................................................................................. 39

2.9 I/O switch matrix scenario examples ....................................................................................................42

2.10 Cores......................................................................................................................................................48

2.11 Memory map .........................................................................................................................................49

2.12 Interrupts ...............................................................................................................................................54

3 Signals.................................................................................................................................... 56

3.1 Bootstrap signals ...................................................................................................................................56

3.2 Configuration for flight ......................................................................................................................... 63

3.3 Complete signal list ............................................................................................................................... 64

4 Clocking................................................................................................................................. 66

4.1 PLL Configuration and Status...............................................................................................................67

4.2 Clock Source and divisor ......................................................................................................................67

4.3 System clock.......................................................................................................................................... 68

4.4 SpaceWire clock.................................................................................................................................... 68

4.5 MIL-STD-1553B clock .........................................................................................................................68

4.6 PacketWire RX Clock ........................................................................................................................... 68

4.7 ADC Clock ............................................................................................................................................68

4.8 DAC Clock ............................................................................................................................................69

4.9 PWM Clock...........................................................................................................................................69

4.10 Clock gating unit ...................................................................................................................................69

4.11 Debug AHB bus clocking......................................................................................................................69

4.12 Test mode clocking................................................................................................................................ 69

5 Reset....................................................................................................................................... 70

5.1 IO Reset.................................................................................................................................................70

6 Technical notes....................................................................................................................... 71

6.1 GRLIB AMBA plug&play scanning.....................................................................................................71

6.2 Software portability...............................................................................................................................71

7 System Startup Status and General Configuration................................................................. 72

7.1 Configuration Registers......................................................................................................................... 72

7.2 Boot Strap information register.............................................................................................................77

GR716-DS-UM, May 2019, Version 1.29 2 www.cobham.com/gaisler

Page 3

GR716

7.3 Special Configuration Registers ............................................................................................................78

8 Reset Generation and Brownout Detection............................................................................ 86

8.1 Overview ...............................................................................................................................................86

8.2 Operation ...............................................................................................................................................86

8.3 Registers ................................................................................................................................................ 87

9 Crystal (XO) Oscillator.......................................................................................................... 91

9.1 Overview ...............................................................................................................................................91

9.2 Operation ...............................................................................................................................................91

10 PLL......................................................................................................................................... 93

10.1 Overview ...............................................................................................................................................93

10.2 Operation ...............................................................................................................................................93

10.3 Registers ................................................................................................................................................ 94

11 Voltage and Current References........................................................................................... 100

11.1 Overview .............................................................................................................................................100

11.2 Operation .............................................................................................................................................100

12 ADC, Pre-Amplifier and Analog MUX ............................................................................... 101

12.1 Overview .............................................................................................................................................101

12.2 Operation .............................................................................................................................................102

12.3 Registers .............................................................................................................................................. 107

13 LDO ..................................................................................................................................... 112

13.1 Overview ............................................................................................................................................. 112

13.2 Operation ............................................................................................................................................. 112

14 Temperature Sensor.............................................................................................................. 113

14.1 Overview ............................................................................................................................................. 113

14.2 Operation ............................................................................................................................................. 113

15 DAC ..................................................................................................................................... 114

15.1 Overview ............................................................................................................................................. 114

15.2 Operation ............................................................................................................................................. 115

15.3 Registers .............................................................................................................................................. 116

16 LEON3/FT - High-performance SPARC V8 32-bit Processor ............................................ 119

16.1 Overview ............................................................................................................................................. 119

16.2 LEON3 integer unit .............................................................................................................................120

16.3 Local instruction and data RAM .........................................................................................................128

16.4 Floating-point unit...............................................................................................................................128

16.5 AMBA interface .................................................................................................................................. 129

16.6 Configuration registers ........................................................................................................................130

16.7 Software considerations ......................................................................................................................136

17 IEEE-754 Floating-Point Unit ............................................................................................. 137

17.1 Overview .............................................................................................................................................137

17.2 Functional Description ........................................................................................................................137

18 UART Serial Interface ......................................................................................................... 140

18.1 Overview .............................................................................................................................................141

18.2 Operation .............................................................................................................................................141

18.3 Baud-rate generation ........................................................................................................................... 142

18.4 Loop back mode .................................................................................................................................. 143

18.5 FIFO debug mode................................................................................................................................143

GR716-DS-UM, May 2019, Version 1.29 3 www.cobham.com/gaisler

Page 4

GR716

18.6 Interrupt generation .............................................................................................................................143

18.7 Registers .............................................................................................................................................. 144

19 Hardware Debug Support Unit ............................................................................................ 147

19.1 Overview .............................................................................................................................................147

19.2 Operation .............................................................................................................................................147

19.3 AHB trace buffer .................................................................................................................................148

19.4 Instruction trace buffer ........................................................................................................................150

19.5 Using the DSU trace buffer .................................................................................................................151

19.6 DSU memory map...............................................................................................................................151

19.7 DSU registers ...................................................................................................................................... 152

20 On-chip Dual-port Memory with EDAC Protection............................................................ 158

20.1 Overview .............................................................................................................................................158

20.2 Local Memory memory map and register ...........................................................................................161

21 Fault Tolerant PROM/SRAM Memory Interface ................................................................ 165

21.1 Overview .............................................................................................................................................165

21.2 PROM access ......................................................................................................................................166

21.3 SRAM access ......................................................................................................................................168

21.4 Memory EDAC ................................................................................................................................... 168

21.5 Bus Ready signalling...........................................................................................................................169

21.6 Access errors .......................................................................................................................................171

21.7 Registers .............................................................................................................................................. 172

22 Fault Tolerant NVRAM Memory Interface ......................................................................... 176

23 MIL-STD-1553B / AS15531 Interface ................................................................................ 177

23.1 Overview .............................................................................................................................................177

23.2 Electrical interface............................................................................................................................... 178

23.3 Operation .............................................................................................................................................178

23.4 Bus Controller Operation .................................................................................................................... 180

23.5 Remote Terminal Operation ................................................................................................................185

23.6 Bus Monitor Operation........................................................................................................................189

23.7 Registers .............................................................................................................................................. 190

24 ADC / DAC Interface .......................................................................................................... 202

24.1 Overview .............................................................................................................................................202

24.2 Operation .............................................................................................................................................204

24.3 Registers .............................................................................................................................................. 206

25 CAN 2.0 Controller.............................................................................................................. 211

25.1 Overview ............................................................................................................................................. 211

25.2 Interface............................................................................................................................................... 213

25.3 Protocol ...............................................................................................................................................213

25.4 Status and monitoring.......................................................................................................................... 214

25.5 Transmission........................................................................................................................................ 214

25.6 Reception.............................................................................................................................................217

25.7 Global reset and enable ....................................................................................................................... 220

25.8 Registers .............................................................................................................................................. 221

25.9 Memory mapping ................................................................................................................................ 230

26 Clock gating unit (Primary) ................................................................................................. 232

26.1 Overview .............................................................................................................................................232

26.2 Operation .............................................................................................................................................232

GR716-DS-UM, May 2019, Version 1.29 4 www.cobham.com/gaisler

Page 5

GR716

26.3 Registers .............................................................................................................................................. 233

27 Clock gating unit (Secondary) ............................................................................................. 236

27.1 Overview .............................................................................................................................................236

27.2 Operation .............................................................................................................................................236

27.3 Registers .............................................................................................................................................. 237

28 DMA Controller with internal AHB/APB bridge ................................................................240

28.1 Overview .............................................................................................................................................240

28.2 Configuration.......................................................................................................................................241

28.3 Operation .............................................................................................................................................250

28.4 AHB transfers......................................................................................................................................252

28.5 Interrupts .............................................................................................................................................252

28.6 Errors ...................................................................................................................................................252

28.7 Internal Buffer Readout Interface........................................................................................................ 253

28.8 Registers .............................................................................................................................................. 253

28.9 DMA Transfer Example ...................................................................................................................... 259

29 General Purpose I/O Port ..................................................................................................... 263

29.1 Overview .............................................................................................................................................264

29.2 Operation .............................................................................................................................................264

29.3 Pulse command....................................................................................................................................264

29.4 Pulse sequencer ...................................................................................................................................264

29.5 Pulse sampler......................................................................................................................................266

29.6 Registers .............................................................................................................................................. 266

30 Pulse Width Modulation Generator ..................................................................................... 277

30.1 Overview .............................................................................................................................................278

30.2 Operation .............................................................................................................................................278

30.3 Registers .............................................................................................................................................. 280

31 PacketWire Receiver............................................................................................................ 285

31.1 Overview .............................................................................................................................................285

31.2 PacketWire interface............................................................................................................................ 285

31.3 Operation .............................................................................................................................................286

31.4 Operation .............................................................................................................................................286

31.5 Registers .............................................................................................................................................. 288

32 PacketWire Transmitter........................................................................................................ 291

32.1 Overview .............................................................................................................................................291

32.2 PacketWire interface............................................................................................................................ 291

32.3 Operation .............................................................................................................................................292

32.4 Registers .............................................................................................................................................. 293

33 SpaceWire Interface and RMAP target................................................................................ 296

33.1 Overview .............................................................................................................................................296

33.2 Operation .............................................................................................................................................297

33.3 Link interface ...................................................................................................................................... 298

33.4 Time-code distribution ........................................................................................................................ 301

33.5 Interrupt distribution............................................................................................................................302

33.6 Receiver DMA channels......................................................................................................................304

33.7 Transmitter DMA channels ................................................................................................................. 310

33.8 RMAP..................................................................................................................................................313

33.9 AMBA interface .................................................................................................................................. 317

GR716-DS-UM, May 2019, Version 1.29 5 www.cobham.com/gaisler

Page 6

GR716

33.10 SpaceWire Plug-and-Play....................................................................................................................318

33.11 Registers .............................................................................................................................................. 324

34 SpaceWire - Time Distribution Protocol.............................................................................. 342

34.1 Overview .............................................................................................................................................342

34.2 Protocol ...............................................................................................................................................342

34.3 Functionality........................................................................................................................................342

34.4 Data formats ........................................................................................................................................348

34.5 Reference documents ..........................................................................................................................348

34.6 Registers .............................................................................................................................................. 349

35 General Purpose Timer Unit with Watchdog ....................................................................... 365

35.1 Overview .............................................................................................................................................365

35.2 Operation .............................................................................................................................................365

35.3 Registers .............................................................................................................................................. 367

36 General Purpose Timer Unit (Secondary)............................................................................ 371

36.1 Overview .............................................................................................................................................371

36.2 Operation .............................................................................................................................................371

36.3 Registers .............................................................................................................................................. 372

37 I2C to AHB bridge............................................................................................................... 376

37.1 Overview .............................................................................................................................................376

37.2 Operation .............................................................................................................................................377

37.3 Registers .............................................................................................................................................. 381

38 I2C master ............................................................................................................................ 384

38.1 Overview .............................................................................................................................................384

38.2 Operation .............................................................................................................................................385

38.3 Registers .............................................................................................................................................. 388

39 I2C slave .............................................................................................................................. 391

39.1 Overview .............................................................................................................................................391

39.2 Operation .............................................................................................................................................392

39.3 Registers .............................................................................................................................................. 394

40 Interrupt Controller .............................................................................................................. 398

40.1 Overview .............................................................................................................................................398

40.2 Operation .............................................................................................................................................399

40.3 Registers .............................................................................................................................................. 403

41 LEON3 Statistics Unit ......................................................................................................... 415

41.1 Overview .............................................................................................................................................415

41.2 Using the LEON3 statistics unit.......................................................................................................... 417

41.3 Registers .............................................................................................................................................. 417

42 Memory Scrubber and Status Register ................................................................................ 420

42.1 Overview .............................................................................................................................................421

42.2 Operation .............................................................................................................................................421

42.3 Registers .............................................................................................................................................. 423

43 SPI to AHB bridge ............................................................................................................... 428

43.1 Overview .............................................................................................................................................428

43.2 Transmission protocol .........................................................................................................................429

43.3 System clock requirements and sampling ...........................................................................................430

43.4 SPI instructions....................................................................................................................................430

GR716-DS-UM, May 2019, Version 1.29 6 www.cobham.com/gaisler

Page 7

GR716

43.5 Registers .............................................................................................................................................. 432

44 SPI Controller ...................................................................................................................... 434

44.1 Overview .............................................................................................................................................434

44.2 Operation .............................................................................................................................................435

44.3 Registers .............................................................................................................................................. 438

45 SPI for Space Slave Controller ............................................................................................ 445

45.1 Overview .............................................................................................................................................445

45.2 Implementation of SPI protocols......................................................................................................... 446

45.3 Transmission........................................................................................................................................ 446

45.4 Operation .............................................................................................................................................447

45.5 SPI 2 Protocol Handler........................................................................................................................447

45.6 Message Header - Command Token.................................................................................................... 448

45.7 Redundancy ......................................................................................................................................... 454

45.8 Registers .............................................................................................................................................. 455

46 SPI Memory Controller........................................................................................................ 460

46.1 Overview .............................................................................................................................................461

46.2 Operation .............................................................................................................................................461

46.3 Registers .............................................................................................................................................. 464

47 AMBA Protection Unit ........................................................................................................ 467

47.1 Overview .............................................................................................................................................467

47.2 Operation .............................................................................................................................................468

47.3 Registers .............................................................................................................................................. 468

47.4 Example of configure and use the Memory protection .......................................................................484

48 Serial Debug and remote access Interface ........................................................................... 486

48.1 Overview .............................................................................................................................................487

48.2 Operation .............................................................................................................................................487

48.3 Registers .............................................................................................................................................. 488

49 AHB Status Registers .......................................................................................................... 490

49.1 Overview .............................................................................................................................................490

49.2 Operation .............................................................................................................................................490

49.3 Registers .............................................................................................................................................. 491

50 Trace buffer.......................................................................................................................... 493

50.1 Overview .............................................................................................................................................493

50.2 Operation .............................................................................................................................................494

50.3 Using the AHB trace buffer................................................................................................................. 495

50.4 Registers .............................................................................................................................................. 496

51 Boot ROM............................................................................................................................ 499

51.1 Overview .............................................................................................................................................499

51.2 ROM Architecture............................................................................................................................... 500

51.3 Loader description............................................................................................................................... 505

51.4 Standby description ............................................................................................................................. 505

51.5 State at handover to application software............................................................................................506

51.6 Boot source requirements.................................................................................................................... 507

51.7 Protection schemes.............................................................................................................................. 507

52 Electrical description ........................................................................................................... 510

52.1 Absolute maximum ratings .................................................................................................................510

52.2 Recommended operating conditions ................................................................................................... 512

GR716-DS-UM, May 2019, Version 1.29 7 www.cobham.com/gaisler

Page 8

GR716

52.3 Power supplies characteristics............................................................................................................. 513

52.4 Input voltages, leakage currents and capacitances .............................................................................. 514

52.5 Output voltages, leakage currents and capacitances ........................................................................... 515

52.6 Simplified IO buffer schematics..........................................................................................................517

52.7 DAC Electrical Characteristics ........................................................................................................... 519

52.8 ADC Electrical Characteristics ........................................................................................................... 520

52.9 Reference Voltages and Currents Electrical Characteristics ............................................................... 524

52.10 Reset and Brownout-Detector Electrical Characteristics ....................................................................524

52.11 AC characteristics................................................................................................................................526

53 Mechanical description ........................................................................................................540

53.1 Component and package .....................................................................................................................540

53.2 Pin assignment.....................................................................................................................................540

53.3 Mechanical package drawings............................................................................................................. 544

54 Ordering information ........................................................................................................... 546

55 Errata .................................................................................................................................... 547

55.1 Overview .............................................................................................................................................547

55.2 Errata description ................................................................................................................................ 547

56 Features ................................................................................................................................ 549

56.1 Overview .............................................................................................................................................549

56.2 Feature description .............................................................................................................................. 549

GR716-DS-UM, May 2019, Version 1.29 8 www.cobham.com/gaisler

Page 9

GR716

1 Introduction

1.1 Scope

This document is the advanced data sheet and user’s manual for the GR716 LEON3FT microcontroller. The GR716 microcontroller has been developed in an activity initiated by the European Space

Agency under ESTEC contract 40001117749/14/NL/AK.

1.2 Data sheet limitations

Note that this document is an advanced data sheet:

• Advanced data sheet - Product in development

• Preliminary data sheet - Shipping prototype

• Data sheet - Shipping space-grade product

1.3 Updates and feedback

Feedback can be sent to:

Cobham Gaisler AB support: support@gaisler.com

1.4 Software support

The GR716 LEON3FT microcontroller design is supported by standard toolchains provided by

Cobham Gaisler. Toolchains can be downloaded from http://www.cobham.com/gaisler.

1.5 Reference documents

[AMBA] AMBA Specification, Rev 2.0, ARM Limited

[GRLIB] GRLIB IP Library User's Manual, Cobham Gaisler, www.cobham.com/gaisler

[GRIP] GRLIB IP Core User's Manual, Cobham Gaisler, www.cobham.com/gaisler

[SPARC] The SPARC Architecture Manual, Version 8, SPARC International Inc.

[LEON-REX] LEON-REX Instruction Set Extension, Cobham Gaisler

[GRMON3] GRMON3 User's Manual, Cobham Gaisler

GR716-DS-UM, May 2019, Version 1.29 9 www.cobham.com/gaisler

Page 10

GR716

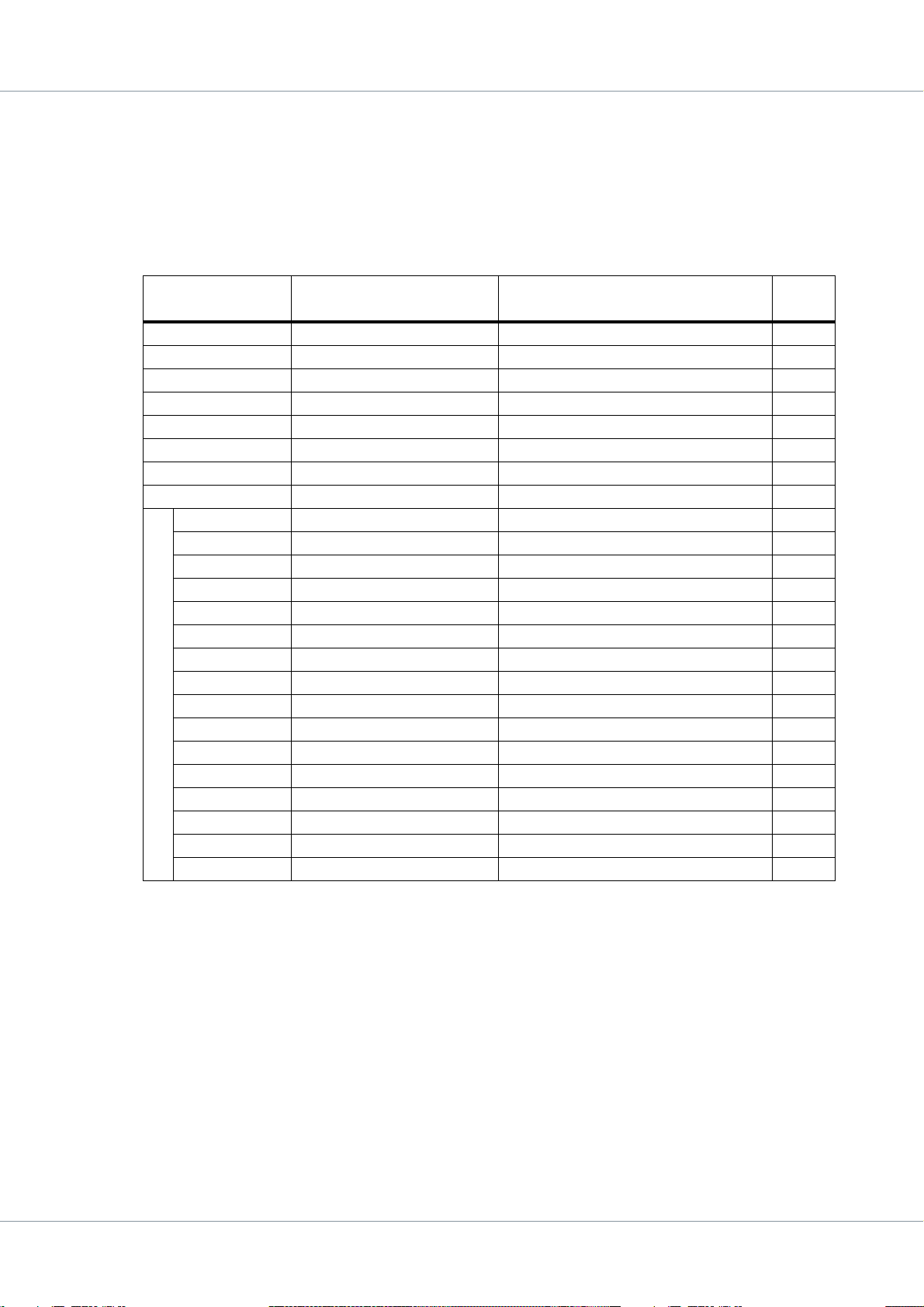

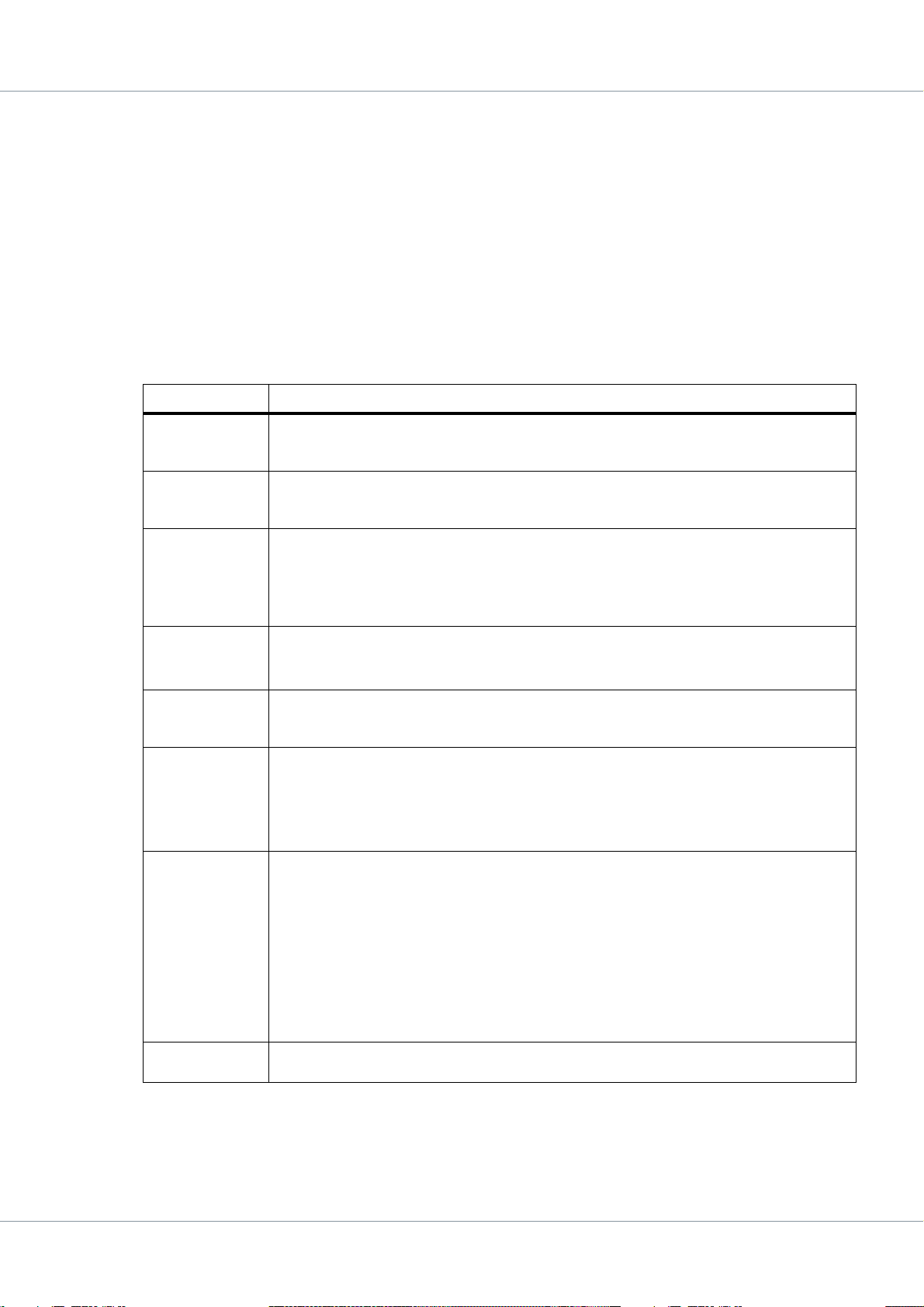

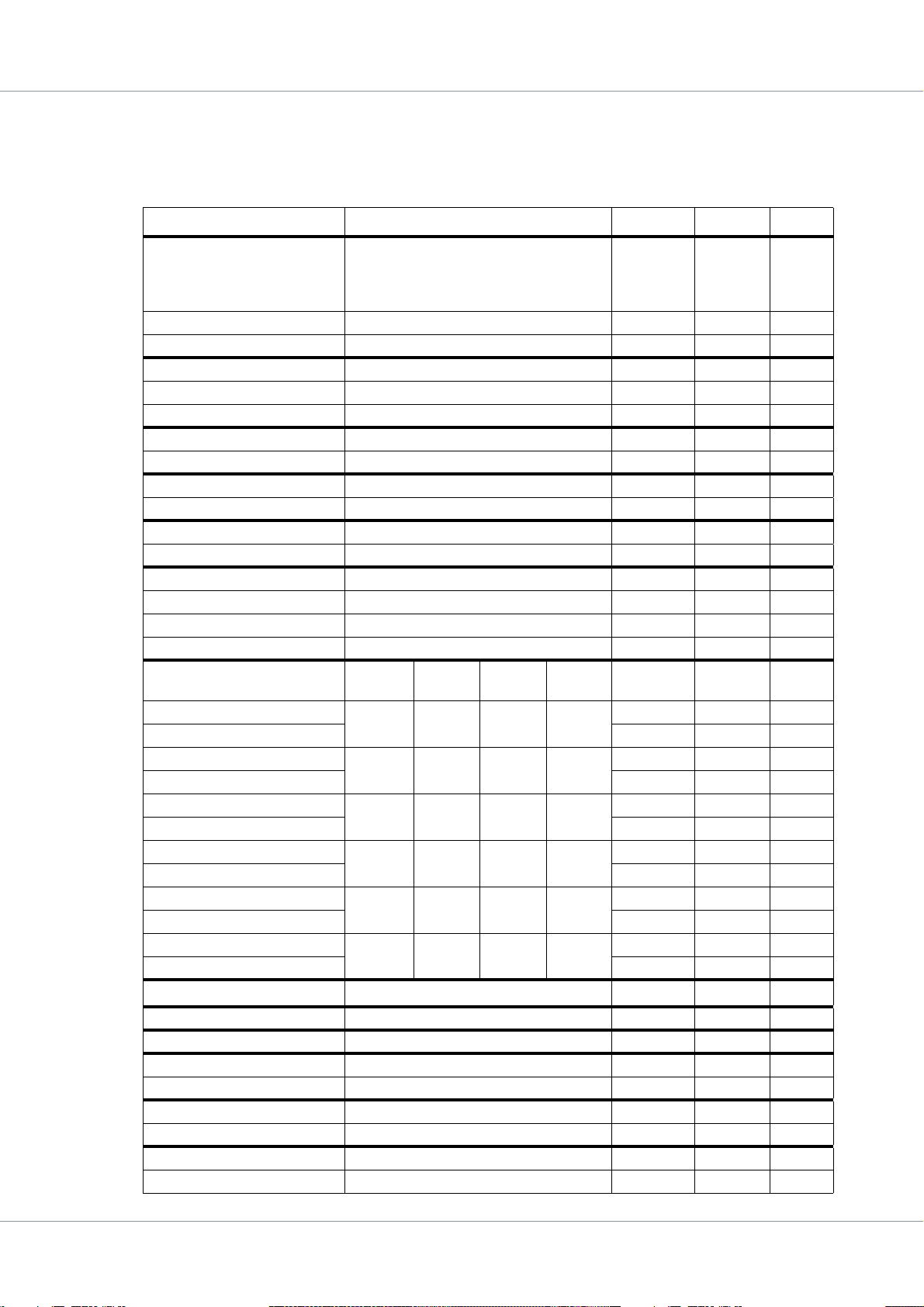

1.6 Document revision history

Change record information is provided in table 1.

Table 1. Change record

Version Date Note

1.29 May 2019 First public release

GR716-DS-UM, May 2019, Version 1.29 10 www.cobham.com/gaisler

Page 11

GR716

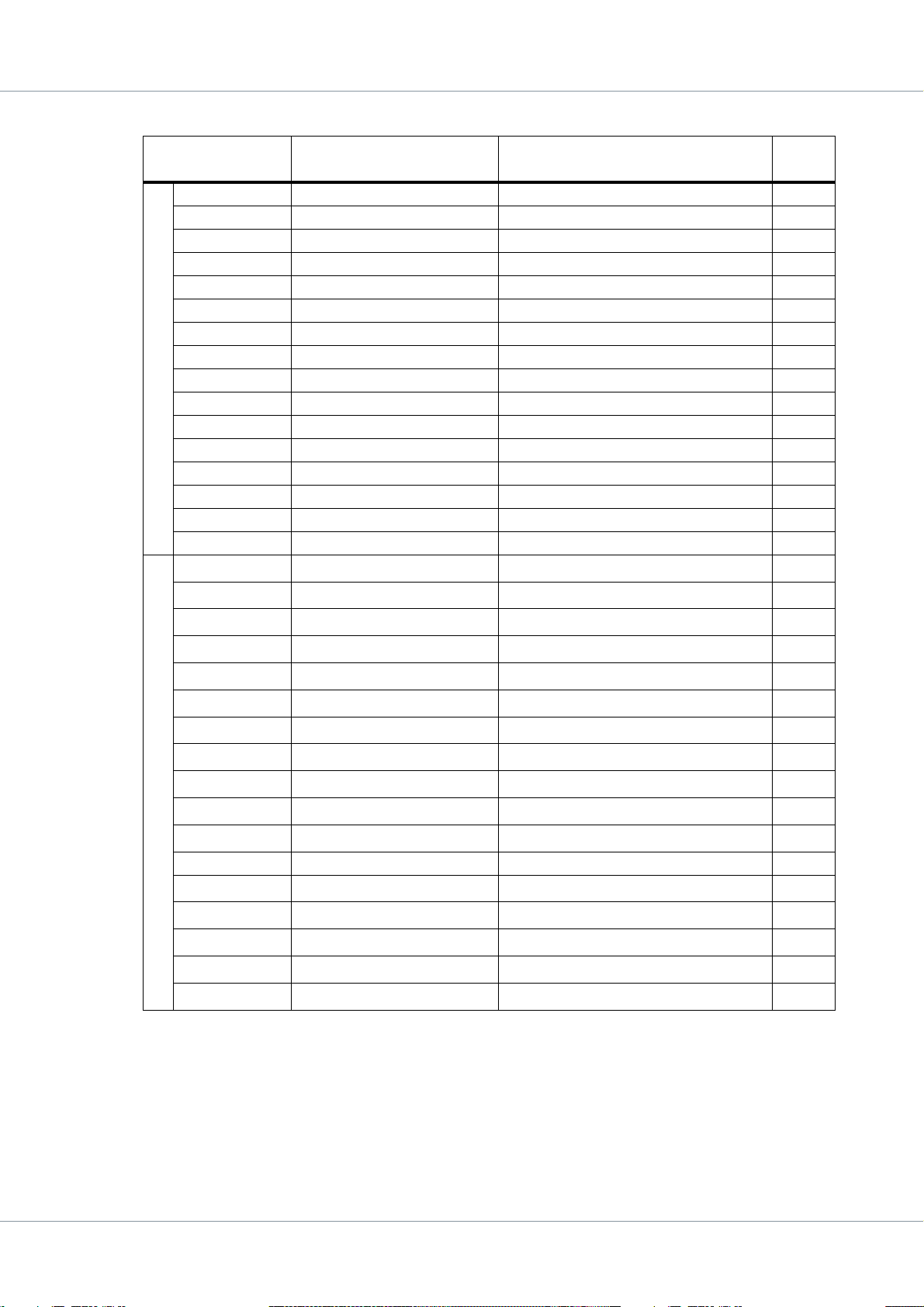

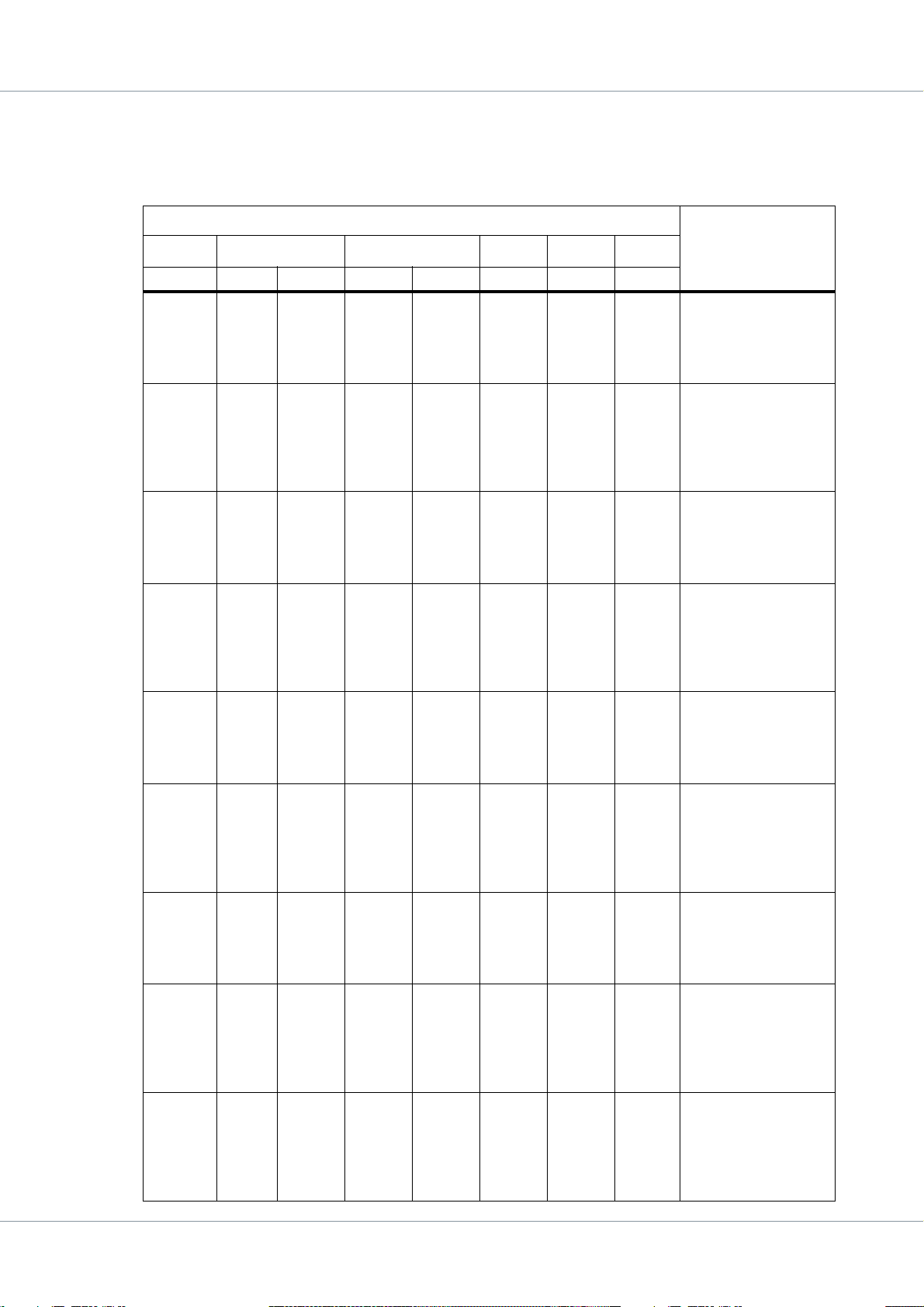

1.7 Acronyms

Table 2. Acronyms

Acronym Comment

AHB Advanced High-performance bus, part of [AMBA]

AMBA Advanced Microcontroller Bus Architecture

APB Advanced Peripheral Bus, part of [AMBA]

BCH Bose–Chaudhuri–Hocquenghem, class of error-correcting codes

CAN Controller Area Network, bus standard

CPU Central Processing Unit, used to refer to one LEON4 processor core.

DMA Direct Memory Access

DSU Debug Support Unit

EDAC Error Detection and Correction

FIFO First-In-First-Out, refers to buffer type

FPU Floating Point Unit

Gb

GB

GiB

Gigabit, 10

Gigabyte, 10

Gibibyte, gigabinary byte, 2

9

bits

9

bytes

30

bytes, unit defined in IEEE 1541-200

I/O Input/Output

ISR Interrupt Service Routine

JTAG Joint Test Action Group (developer of IEEE Standard 1149.1-1990)

kB

KiB

Mb, Mbit

MB, Mbyte

MiB

Kilobyte, 10

Kibibyte, 2

Megabit, 10

Megabyte, 10

Mebibyte, 2

3

bytes

10

bytes, unit defined in IEEE 1541-2002

6

bits

6

bytes

20

bytes, unit defined in IEEE 1541-2002

PROM Programmable Read Only Memory

RAM Random Access Memory

SEE Single Event Effects

SEL/SEU/

Single Event Latchup/Upset/Transient

SET

SPARC Scalable Processor ARChitecture

SW Software

UART Universal Asynchronous Receiver/Transmitter

GR716-DS-UM, May 2019, Version 1.29 11 www.cobham.com/gaisler

Page 12

GR716

1.8 Definitions

This section and the following subsections define the typographic and naming conventions used

throughout this document.

1.8.1 Bit numbering

The following conventions are used for bit numbering:

• The most significant bit (MSb) of a data type has the leftmost position

• The least significant bit of a data type has the rightmost position

• Unless otherwise indicated, the MSb of a data type has the highest bit number and the LSb the

1.8.2 Radix

The following conventions is used for writing numbers:

• Binary numbers are indicated by the prefix "0b", e.g. 0b1010.

• Hexadecimal numbers are indicated by the prefix "0x", e.g. 0xF00F

• Unless a radix is explicitly declared, the number should be considered a decimal.

lowest bit number

1.8.3 Data types

Byte (BYTE) 8 bits of data

Halfword (HWORD) 16 bits of data

Word (WORD) 32 bits of data

GR716-DS-UM, May 2019, Version 1.29 12 www.cobham.com/gaisler

Page 13

GR716

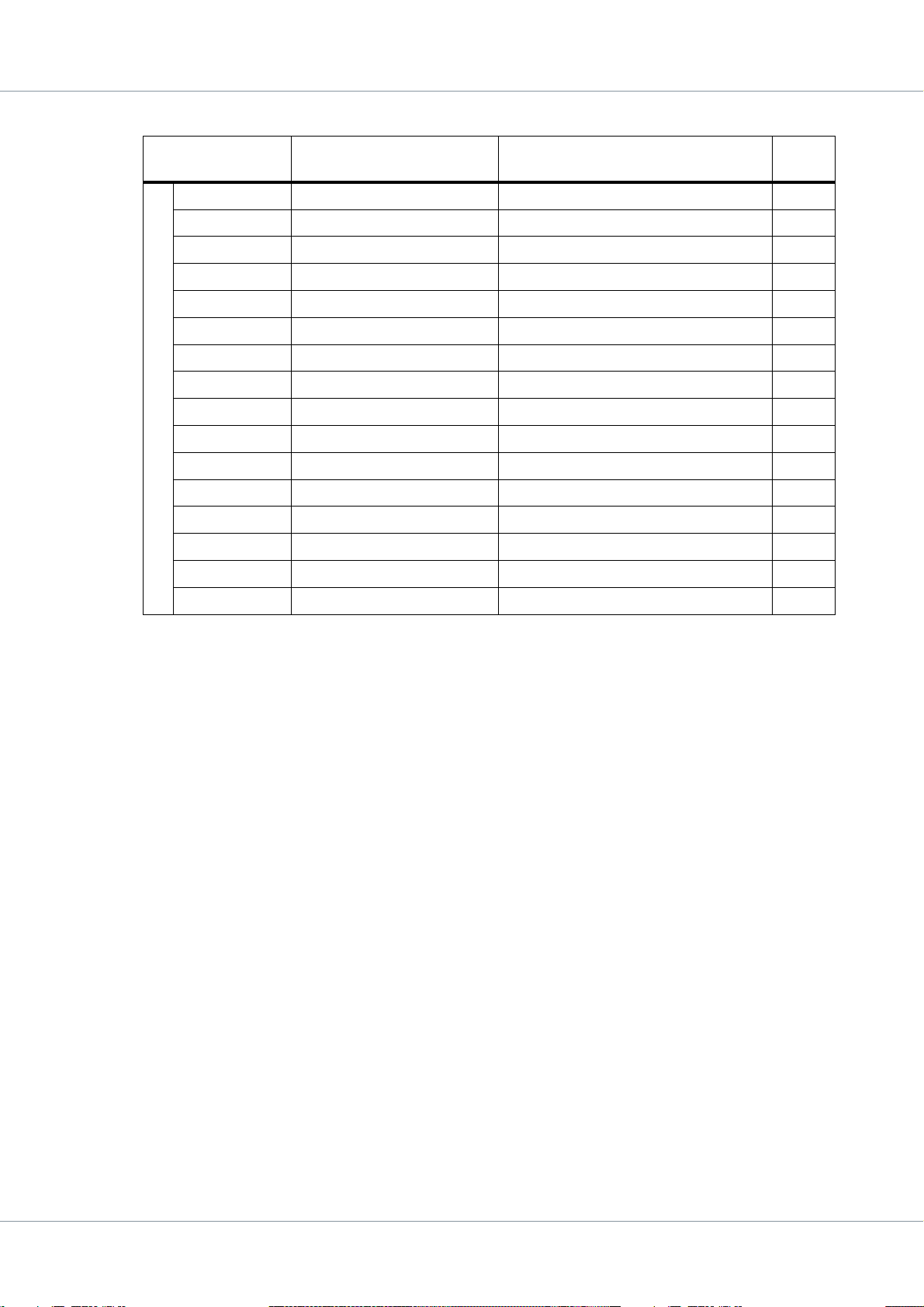

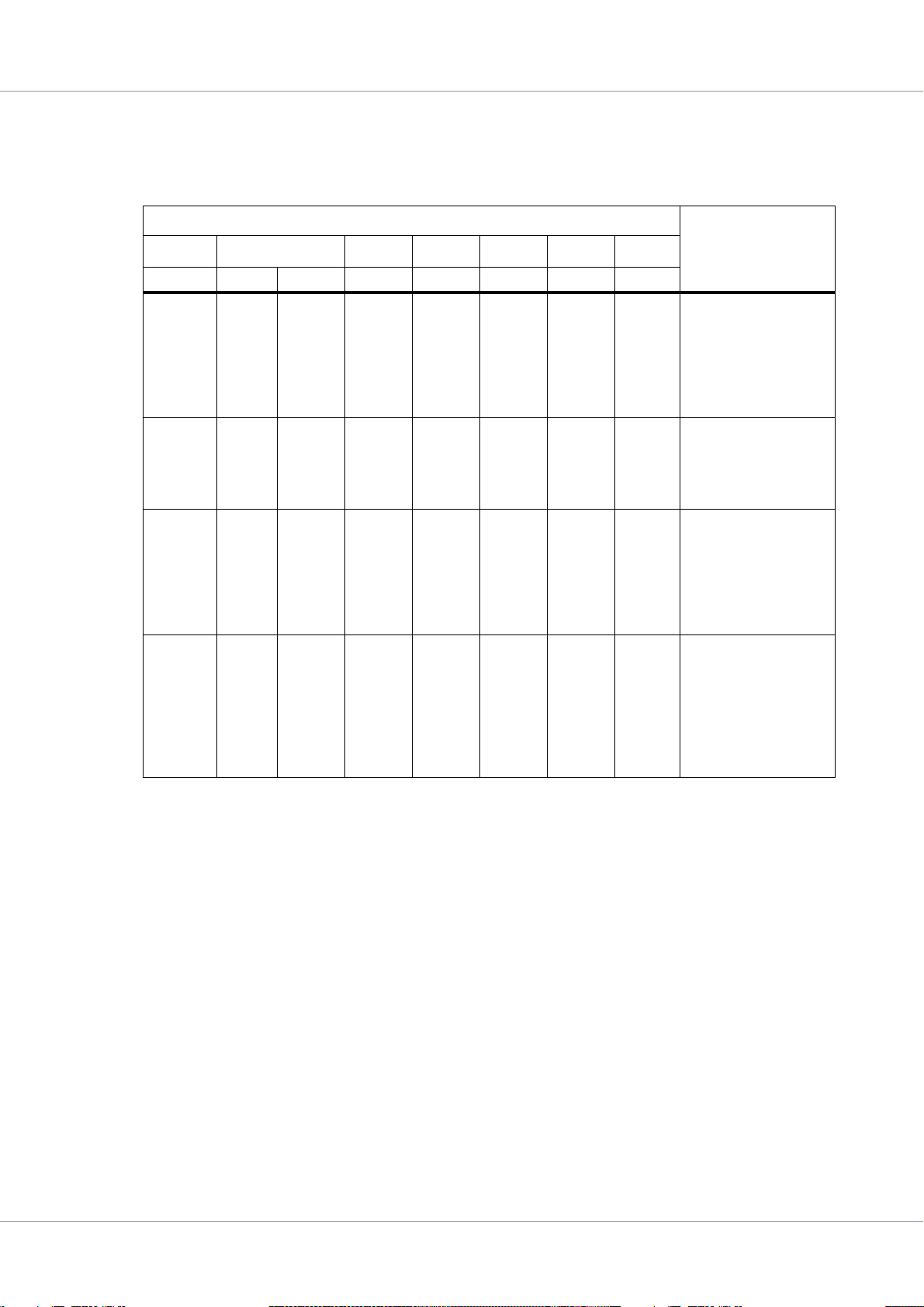

1.9 Register descriptions

An example register, showing the register layout used throughout this document, can be seen

in table 3. The values used for the reset value fields are described in table 4, and the values

used for the field type fields are described in table 5. Fields that are named RESERVED,

RES, or R are read-only fields. These fields can be written with zero or with the value read

from the same register field.

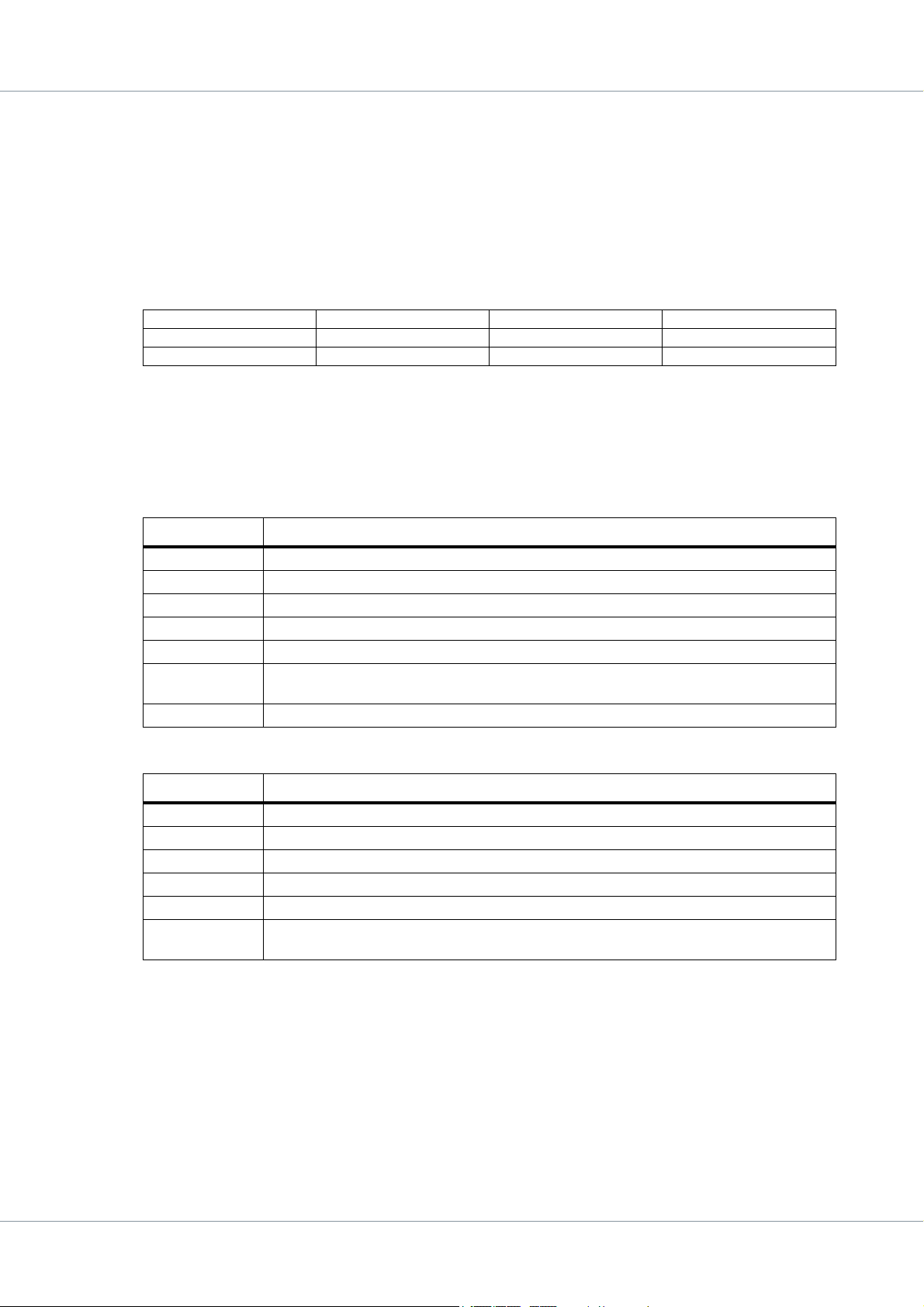

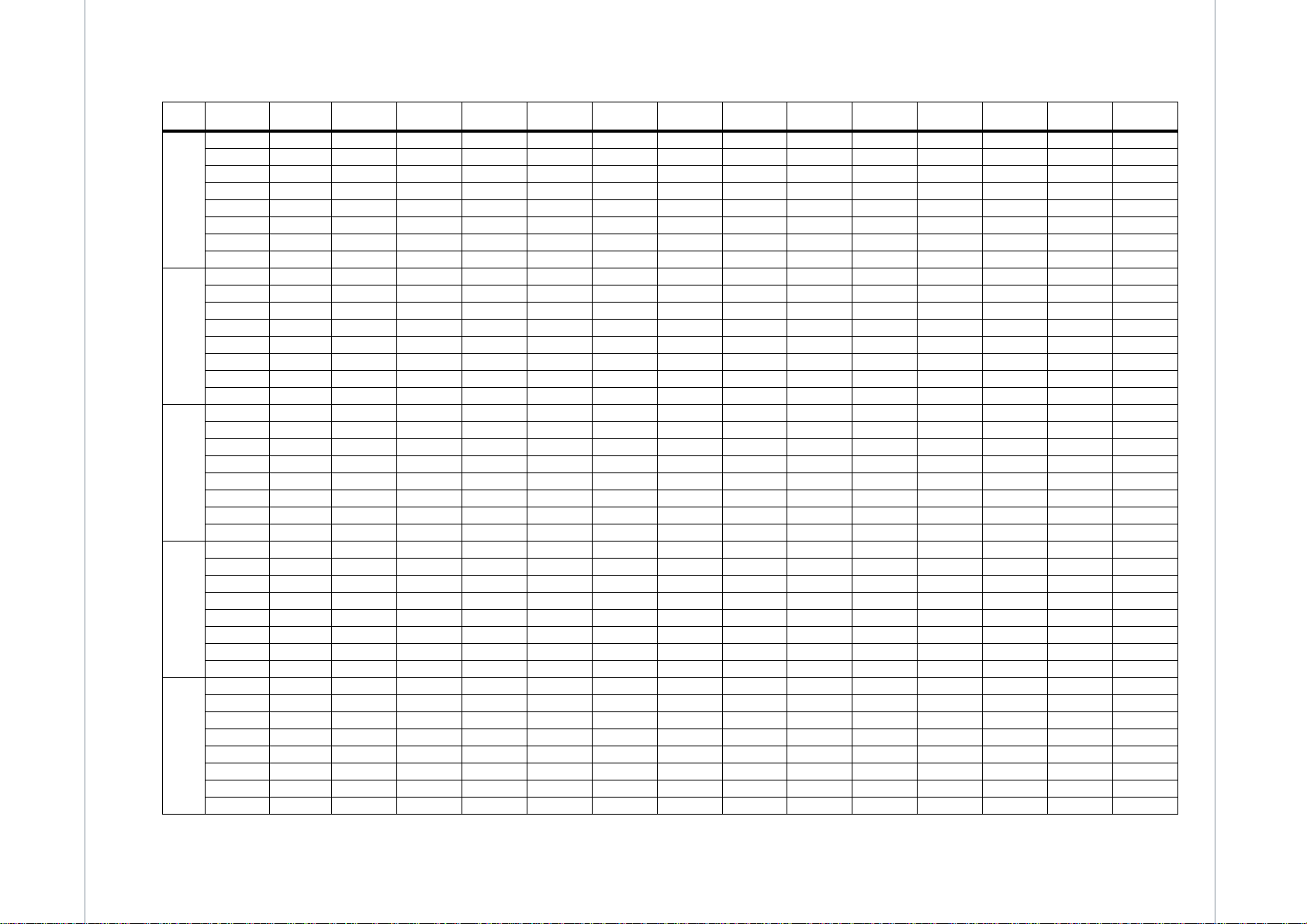

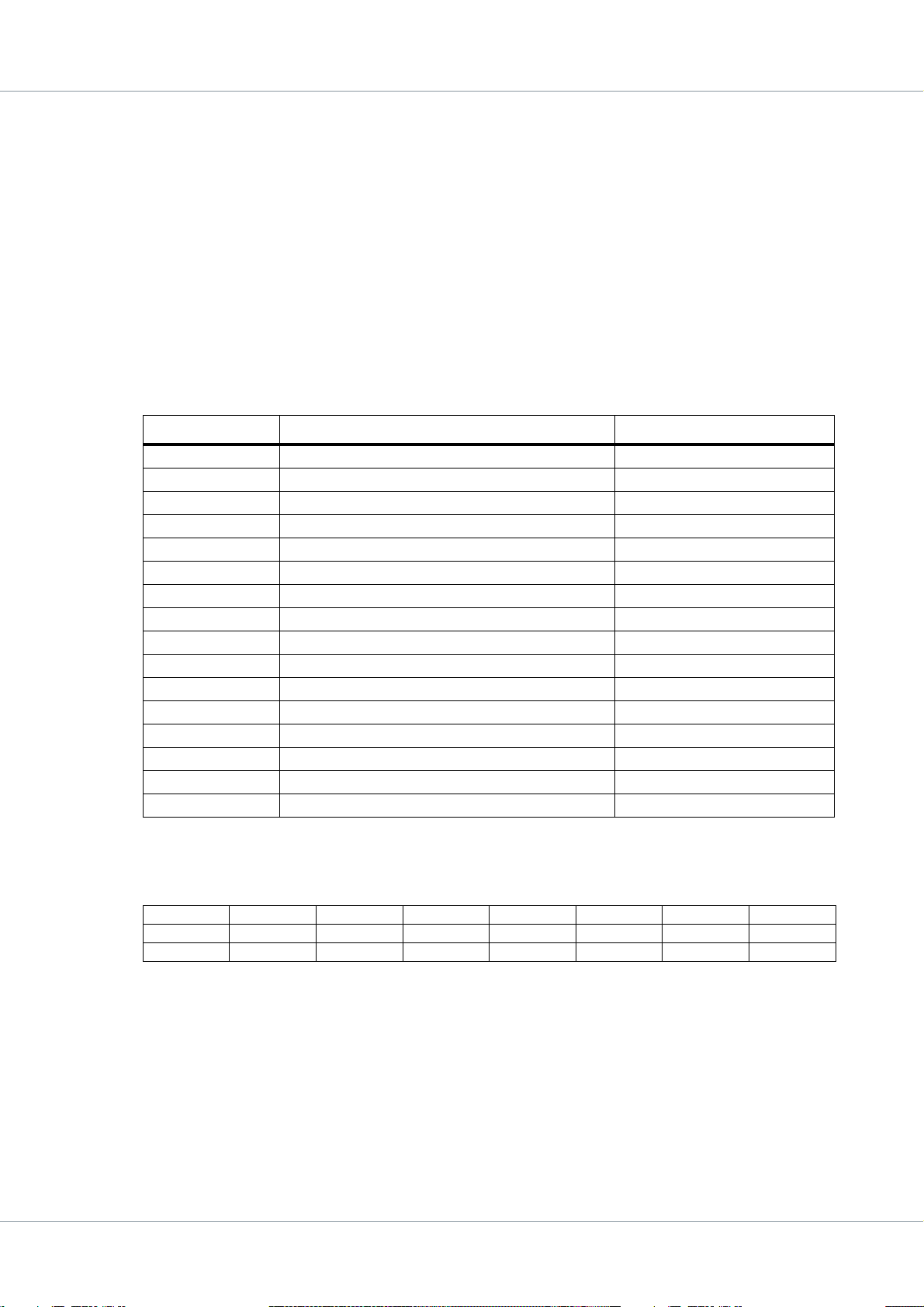

Table 3. <Address> - <Register acronym> - <Register name>

31 24 23 16 15 8 7 0

EF3 EF2 EF1 EF0

<Reset value for EF3> <Reset value for EF2> <Reset value for EF1> <Reset value for EF0>

<Field type for EF3> <Field type for EF2> <Field type for EF1> <Field type for EF0>

31: 24 Example field 3 (EF3) - <Field description>

23: 16 Example field 2 (EF2) - <Field description>

15: 8 Example field 1 (EF1) - <Field description>

7: 0 Example field 0 (EF0) - <Field description>

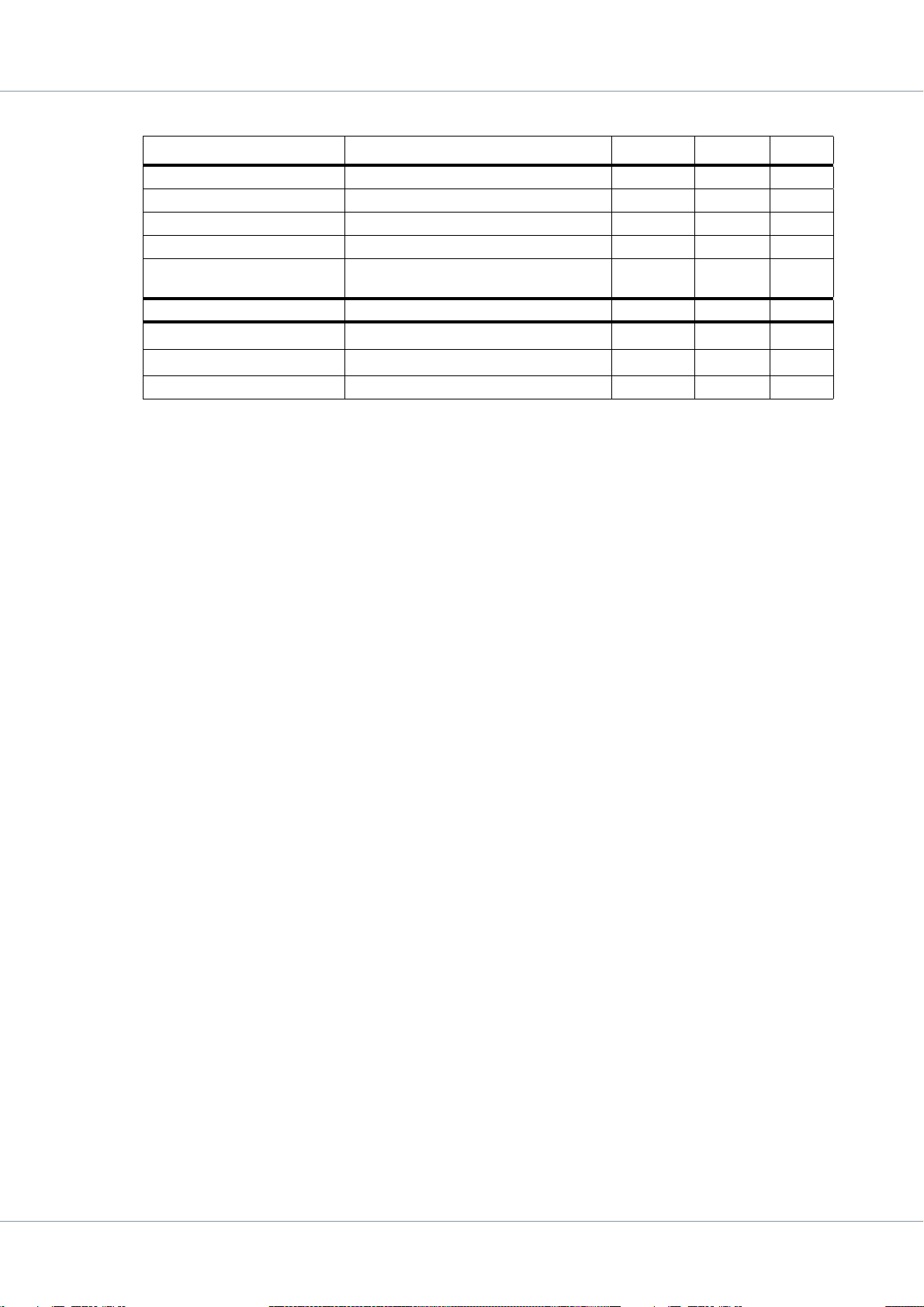

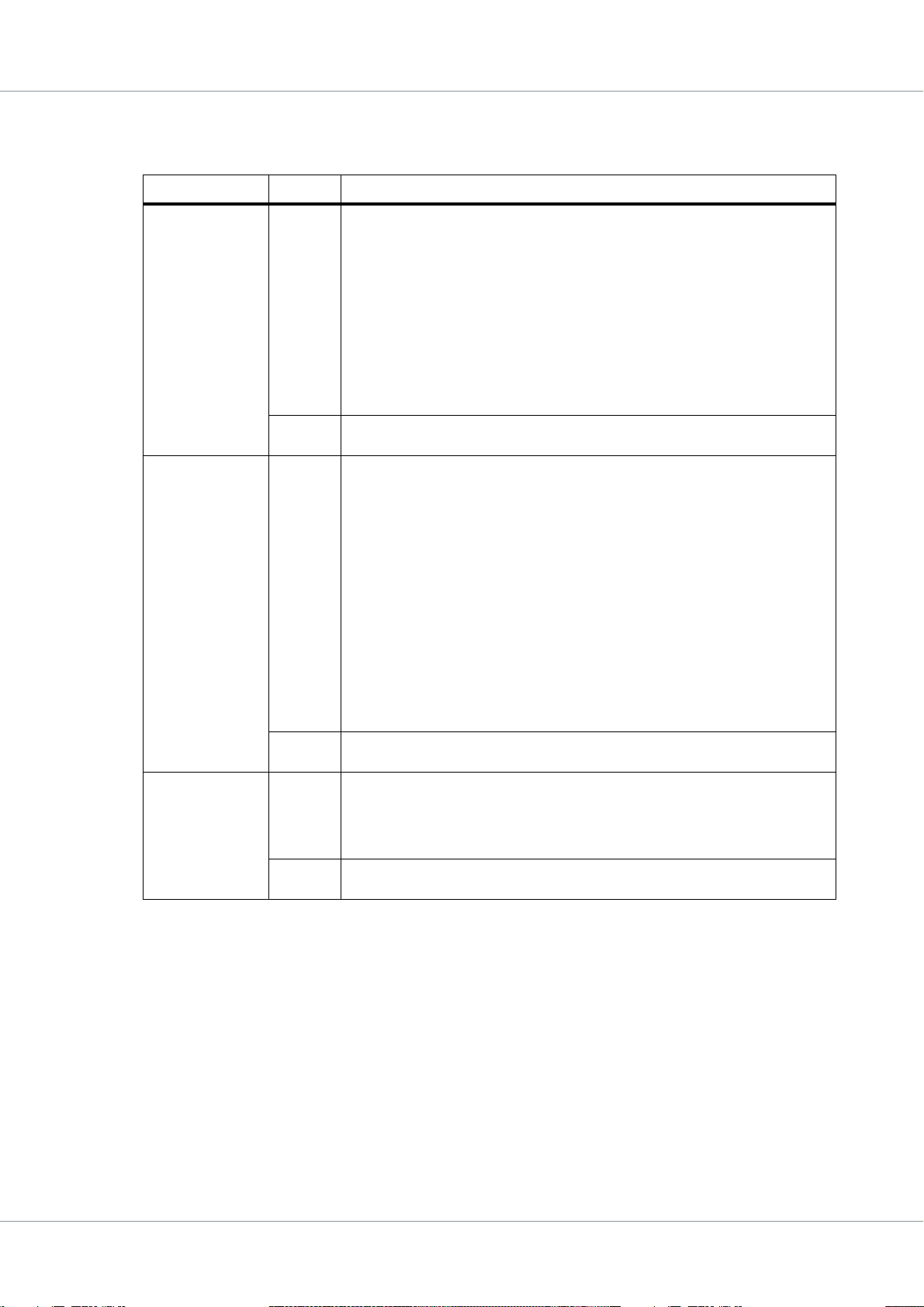

Table 4. Reset value definitions

Value Description

0 Reset value 0.

1 Reset value 1. Used for single-bit fields.

0xNN Hexadecimal representation of reset value. Used for multi-bit fields.

0bNN Binary representation of reset value. Used for multi-bit fields.

NR Field not reset

* Special reset condition, described in textual description of the field. Used for example when reset

value is taken from a pin.

- Don’t care / Not applicable

Table 5. Field type definitions

Value Description

r Read-only. Writes have no effect.

w Write-only. Used for a writable field in a register where the field’s read-value has no meaning.

rw Readable and writable.

rw* Readable and writable. Special condition for write, described in textual description of field.

wc Write-clear. Readable, and cleared when written with a 1

cas Readable, and writable through compare-and-swap. Only applies to SpaceWire Plug-and-Play regis-

ters.

GR716-DS-UM, May 2019, Version 1.29 13 www.cobham.com/gaisler

Page 14

GR716

2 Architecture

Floating

Point

Unit

Local

Dual-port

Instruction

RAM

Main bus

FTMCTRL

UART

I2CMST /

I2CSLV

SPICTRL

GRGPIO

GRPULSE

GRPWM

On-chip

LDO

Integer

Unit

AMBA

Interface

On-chip

Oscillator

PLL

Debug

Support

Unit

Local

Dual-port

Data

RAM

Memory

Scrubber

SPIMCTRL

IRQ Control

Timers

AHBSTAT

GRADCDAC

On-chip DAC

On-chip ADC

Brownout

Detector

Power-on

reset

LEON3

Statistics

Unit

Debug bus

DMA bus

AHB2AHB

Bridge

AHBROM

MEMPROT

CLKGATE

GPREG

LSTAT

UART

Dbg Link

AHB2AHB

Bridge

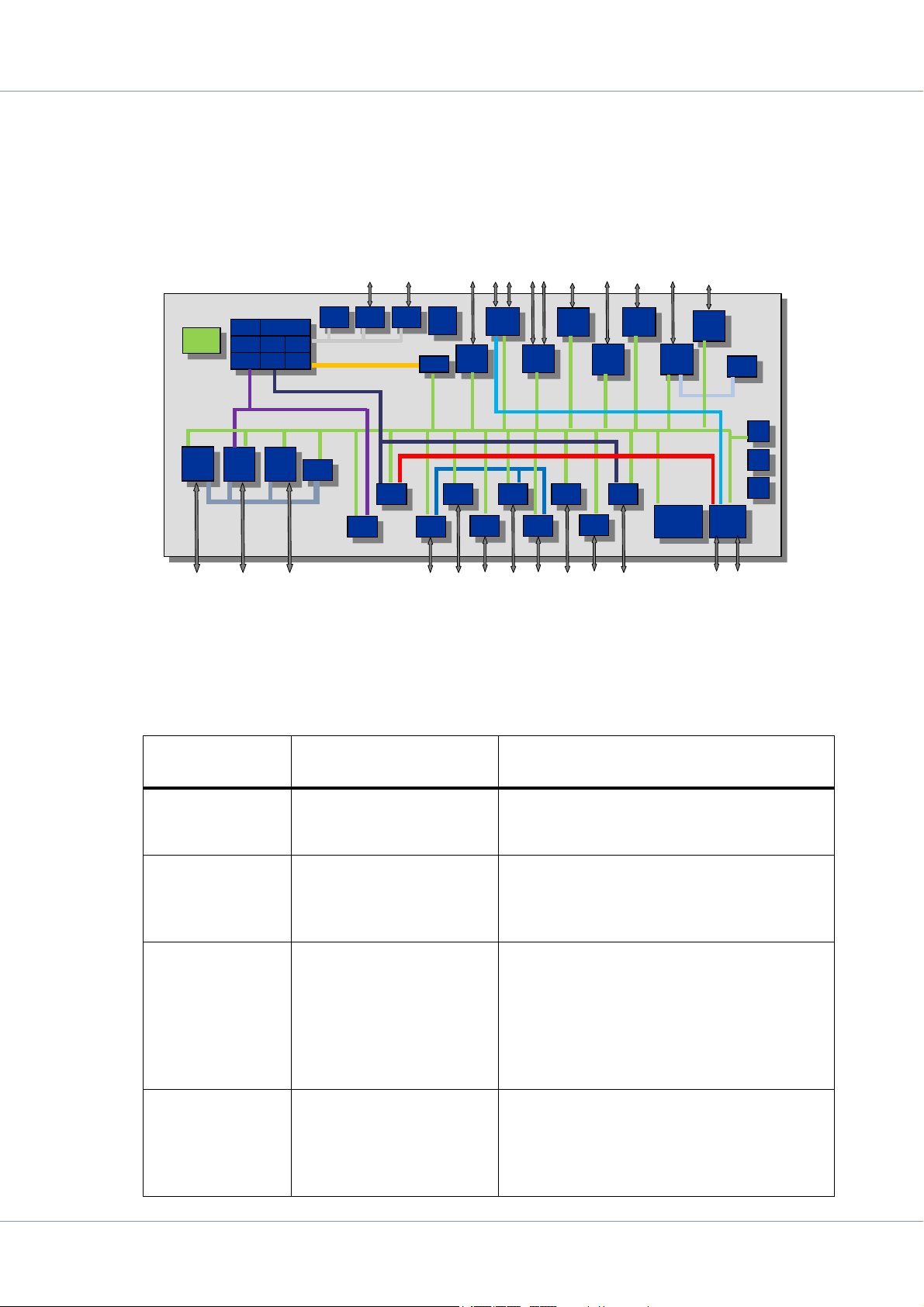

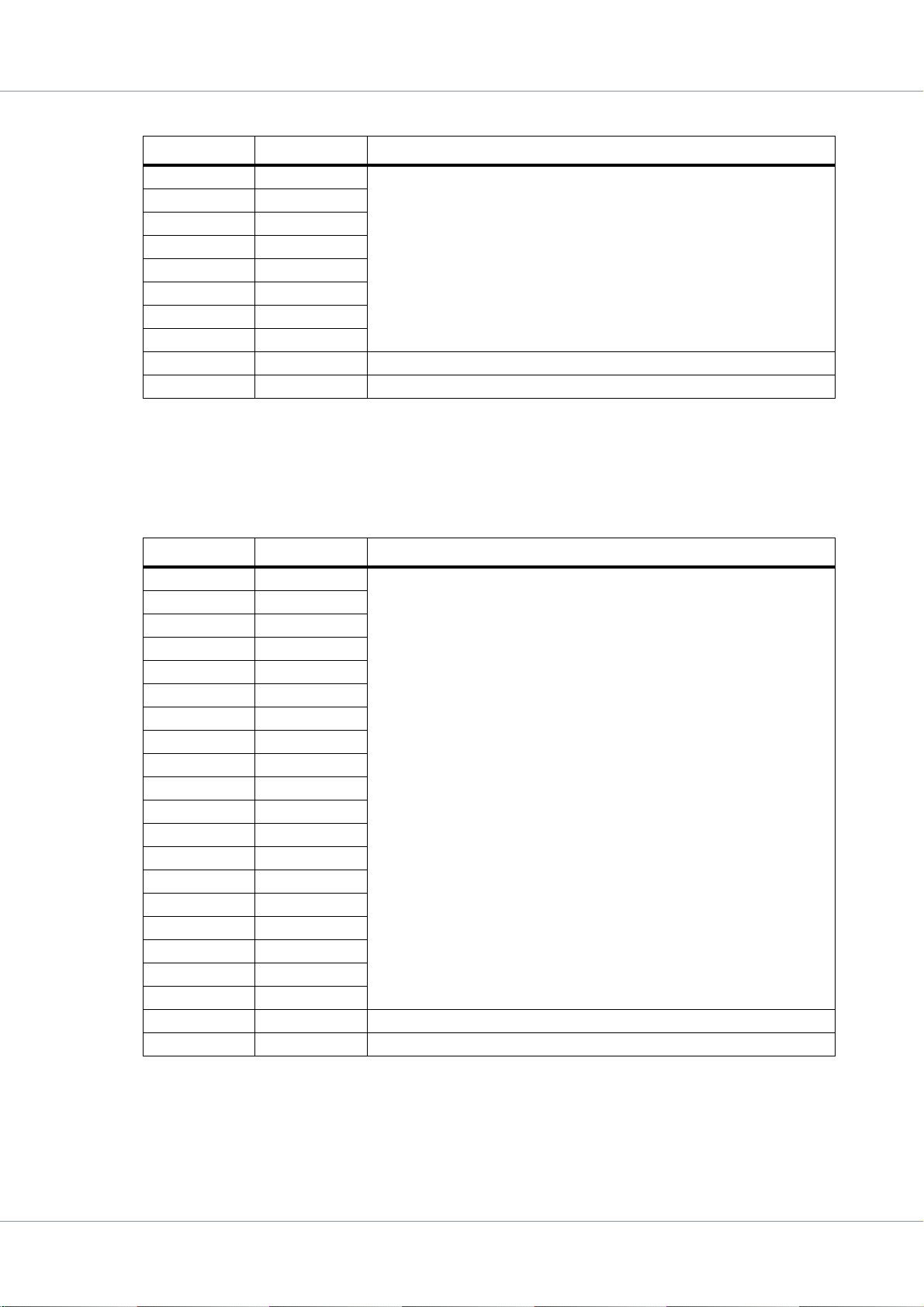

Figure 1. GR716 block diagram

AHB

Trace

DMA

Controller

APBCTRL

Bridges

1553B

SpaceWire

I2C to AHB

SPI to AHB

GRPWRX

(MAP)

GRPWTX

GRCAN

AHB

UART

The microcontroller is a single core LEON3FT SPARC V8 processor, with advanced interface protocols, that has been optimized for real-time systems and deterministic software execution. Features

such as SPARC V8E Alternate Window Pointer, interrupt zero jitter latency, SPARC V8E multiply

step instructions and the possibility to run software (including interrupt handlers) from local RAM are

supported to increase the determinism and responsiveness in the system. The LEON-REX instruction

set extension is also supported by the microcontroller and is further described in [LEON-REX].

The architecture is centered around multiple instances of the AMBA Advanced High-speed Bus

(AHB), to which the LEON3FT processor and other high-bandwidth units are connected. Low bandwidth peripherals/functions are connected to the AMBA Advanced Peripheral Bus (APB) which is

accessed through an AHB to APB bridge. The use of multiple processor buses also enables non-intrusive debugging and the possibility to have direct access to on-board memory without interrupting or

involving the LEON3FT processor.

64 external CMOS pins and six LVDS transceivers are configurable from software via configuration

registers. Pre-defined pin configurations are defined in the boot software and can be enabled by using

pull-up/pull-down resistors on external pins during reset. Pre-defined configuration of external pins

are useful in cases when the microcontroller should boot from external memories or remote controlled

via SpaceWire, UART, SPI or I2C after reset. The program controlling the microcontroller needs to

set appropriate direction and functionality on all pins after reset depending on the environment that

the microcontroller is used in. On-chip LVDS transceivers for SpaceWire and SPI for Space and dedicated pins for external SPI boot ROM boot are available and can optionally be used.

The microcontroller has a high level of integrated analog functions. Analog function integrated onchip includes Analog to digital converters, Brown out detection, Crystal Oscillator, Digital to Analog

Converters, Power-on and reset functionality and Linear Voltage Regulators for single 3.3V supply.

GR716-DS-UM, May 2019, Version 1.29 16 www.cobham.com/gaisler

Page 15

GR716

2.1 Key features

•Core

•Memories

- Fault-tolerant SPARC V8 processor with 31 register windows and support for LEONREX.

- Double precision IEEE-754 floating point unit.

- Memory protection units with 8 zones and individual access control of APB peripherals

for memory protection.

- Advanced on-chip debug support unit with trace buffers and statistic unit for software profiling.

- Single cycle instructions execution and data fetch from tightly coupled memory.

- Deterministic instruction execution and interrupt latency.

- Fast context switching (Partial write %PSR, AWP, Register file partitioning, interrupt

mapping, MVT).

- Single Vector Trap support.

- Interrupt zero jitter delay.

- 192KiB EDAC protected tightly coupled memory with single cycle access from processor

and ATOMIC bit operations.

- Embedded ROM with boot loader for initializing and remote access.

- Dedicated SPI memory interface with boot ROM capability.

- I2C memory interface with boot ROM capability.

- 8-bit SRAM/ROM (FTMCTRL) with support up to 16 MB ROM and 256 MB SRAM.

- Support for package option with embedded SRAM/PROM (FTMCTRL).

- Scrubber with programmable scrub rate for all embedded memories and external PROM/

SRAM and SPI memories.

•System

- On-chip voltage regulators for single supply support. Capability to sense core voltage for

trimming of the embedded voltage regulator for low power applications.

- Power-on-reset, brownout detection and dual watchdogs for safe operation. External reset

signal generation for reseting companion chips.

- Crystal oscillator support.

- PLL for System and SpaceWire clock generation. In-application programming of system

clock and peripheral clocks. System and SpaceWire clocks switches glitch free.

- Low power mode and individual clock gating of functions and peripherals.

- Temperature and core voltage sensor.

- External precision voltage reference for precision measurement.

- Four programmable DMA controllers with up to 16 individual channels. DMA transfers

can be triggered on events such as interrupts or bits/register changing value.

- Timer units with seven 32-bit timers including watchdog.

- Multiple bus structures for non-intrusive debug, DMA transfers and memory scrubbers.

- Atomic access support for all APB registers (AND, OR, XOR, Set&Clear).

GR716-DS-UM, May 2019, Version 1.29 17 www.cobham.com/gaisler

Page 16

GR716

- Support for NVRAM (SRAM and/or PROM) embedded in package. Support for software

boot and execution from embedded RAM for future package options.

- Peripheral access control.

- Embedded trace and statistics unit for profiling of the system.

• Peripherals

- SpaceWire with support for RMAP and Time Distribution Protocol.

- Redundant MIL-STD-1553B BRM (BC/RT/BM) interface.

- Two CAN 2.0B bus controllers.

- Six UART ports, with 16-byte FIFO.

- Two SPI master/slave serial ports.

- SPI4SPACE - hardware support for SPI protocol 0,1 and 2 in HW for SPI for SPI4SPACE.

- Two I2C master/slave serial ports.

- PacketWire interface.

- PWM with up to 16 channels. PWM clock support up to 200 MHz.

- Up to 64 general purpose input and outputs (GPIO) with external interrupt capability,

pulse generation and sampling.

- Four single ended Digital to Analog Converters (DAC), 12-bit at 3MS/s.

- Four differential or eight single ended Analog to Digital Converters (ADC) 11-bit at

200KS/s with programmable pre-amplifier and support for oversampling. Dual sample and

hold circuit integrated for simultaneously sampling.

- External ADC and DAC support up to 16-bit at 1MS/s.

•I/O

- Configurable I/O selection matrix with support for mixed signals, internal pull-up/pulldown resistors.

- LVDS transceivers for SpaceWire or SPI4SPACE.

- Dedicated SPI boot ROM support for configuration.

• Supply

- Single 3.3V±0.3V supply or separate Core Voltage 1.8V±0.18V, I/O voltage 3.3V±0.3V.

• Radiation tolerance

- Technology: 180 nm process, UMC Taiwan

- Library: DARE+ Library version 5.5, IMEC

- TID: up to 100 Krad(Si)

- SEL: > 118 MeV-cm2/mg

- SEU: Proven tolerance with hardened flip-flops and error corrections on all on-chip and

external memories

•Package

- 132-lead CQFP, 0.635 mm pitch, 24mm x 24mm, hermetically sealed with flat pins and

insulating lead-frame for customer trim and form.

•Software

- Supported by standard tools-chains and debug tools provided by Cobham Gaisler. Toolchains, simulators and debug software is available at www.cobham.com/gaisler.

GR716-DS-UM, May 2019, Version 1.29 18 www.cobham.com/gaisler

Page 17

GR716

• Boot ROM and boot options

- Remote boot directly via SpaceWire, UART, SPI or I2C.

- Direct software execution from onchip RAM, external SRAM, PROM or SPI memory.

- Direct software execution from in package embedded memory.

- Application Software Container (ASW) for boot software integrity check.

- Boot via ASW from external SRAM, PROM, SPI memory or I2C memory.

- Boot from redundant memory.

- Fast boot option.

• System configuration

- Reset and boot status.

- Individual reset and clock control for digital and analog peripherals.

- Remote reset and boot control.

- Clock source and divide control for the system, SpaceWire, SPI4S, ADC, DAC, 1553 and

PWM clock domain.

- Support for external system reset.

- Support for external clock source for the system, SpaceWire, SPI4S, 1553 and PWM.

- Automatic oscillator shutdown if oscillator not used.

- Individual programmable brown-out levels.

- Protection for erroneous I/O configuration during power-up and power-down.

- Programmable LDO output level for low power mode.

GR716-DS-UM, May 2019, Version 1.29 19 www.cobham.com/gaisler

Page 18

GR716

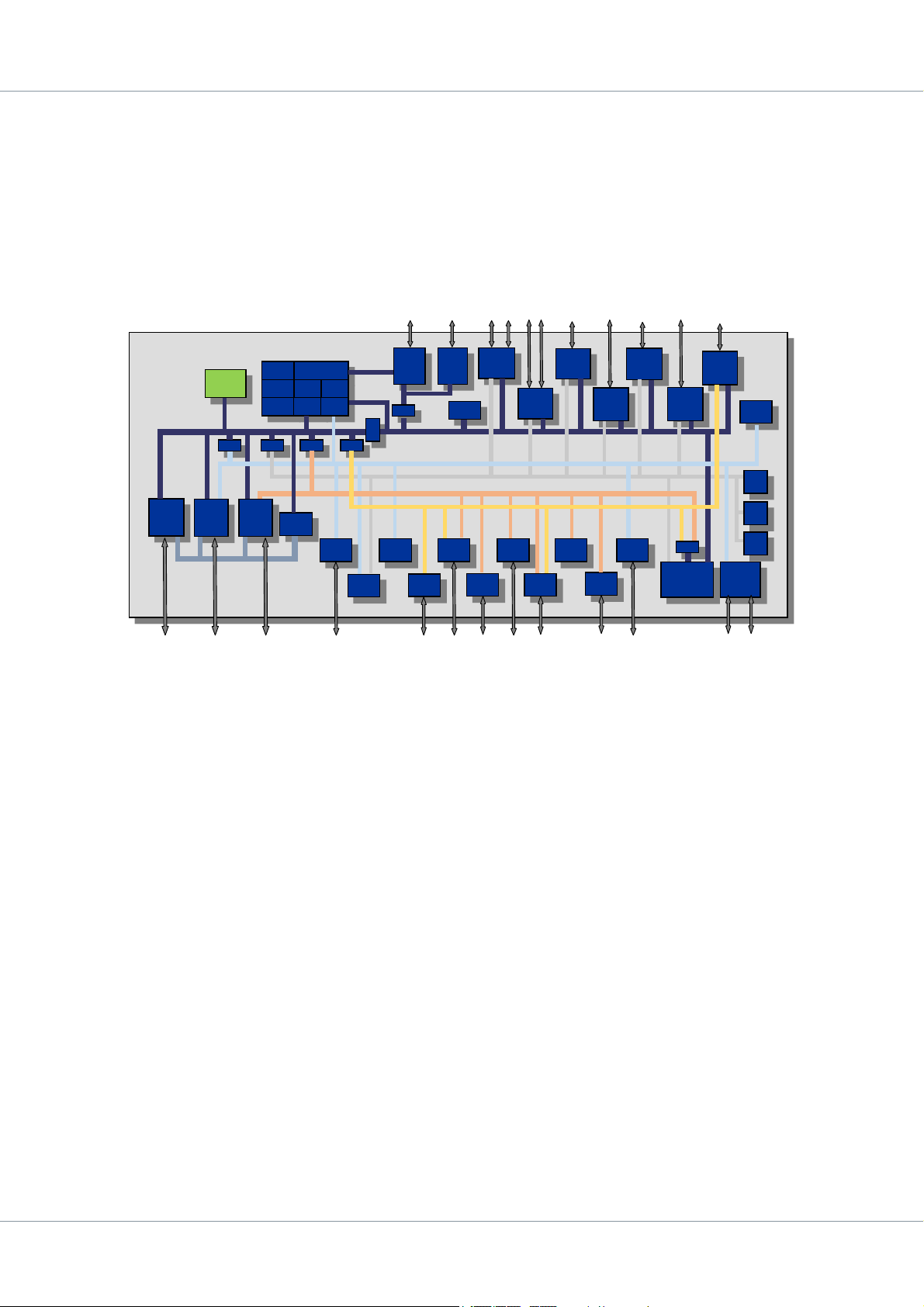

AHBSTAT

Onchip

ADC &

DAC

Bridge

Bridge

Bridge Bridge Bridge

Debug

Unit

(DSU)

I2C

DMA AMBA AH B

AMBA APB 0

Memory

Controller

Serial

Debug

Link

RS232

I2C

SPI

1553 A/B

Mil-1553B

BC/RT/MT

SpaceWire

Links

RMAP

CAN

2.0

LVDS /

LVTTL

CAN N/R

DMA

Controller

I/O Port

LEON3FT

SPARC V8

Mul

Trace

64kB

D-ram

FPU

PacketWire

LVDS /

LVTTL

SPI

GPIO

External

ADC &

DAC

PWM

PWM

UART

RS232

Config &

Status

DMA

Controller

Scrub &

ahbstat

AMBA

128kB

I-ram

REX

Main AMB A AHB

Memory

Prot

Embeeded

Boot ROM

Bridge

IrqCtrl &

Timers

Onchip

ADCDAC

Bridge

SPI2AHB

SPI

I2C2AHB

I2C

SPI4S

SPI

Memory

Controller

Scrubber Bus

PacketWire

Debug Control

Reset /

Clock

Reset /

Watchdog

Clock

DBG AMBA

BO

POR

BO

LDO

NVRAM

Controller

AMBA APB 1

Ext

ADC

SpacWire

TDP

AHBUART

RS232

AMBA APB 2

SPI

Memory

Ext

PROM/SRAM

Memory

NVRAM

AMBA APB 3

Status

and

Control

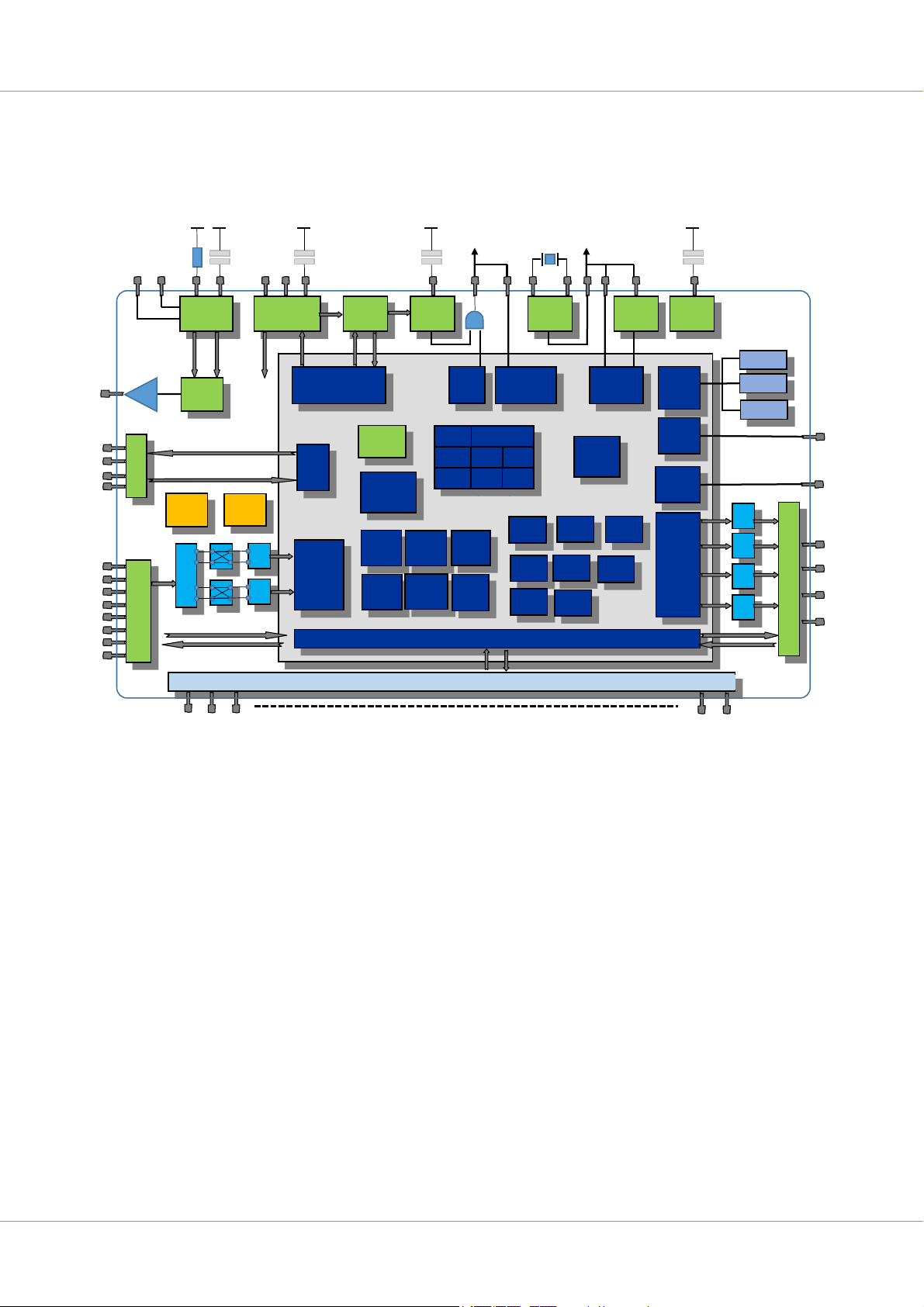

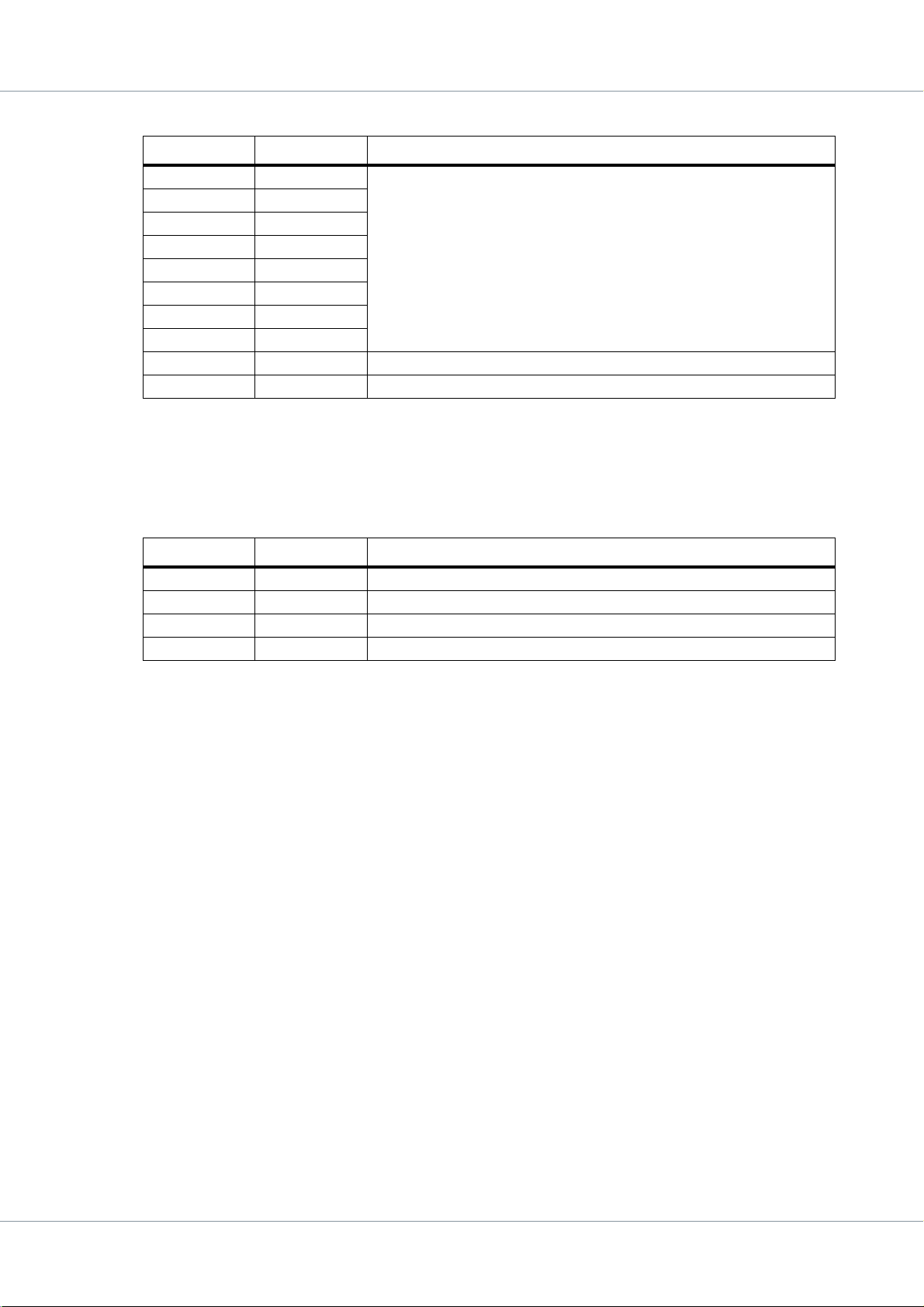

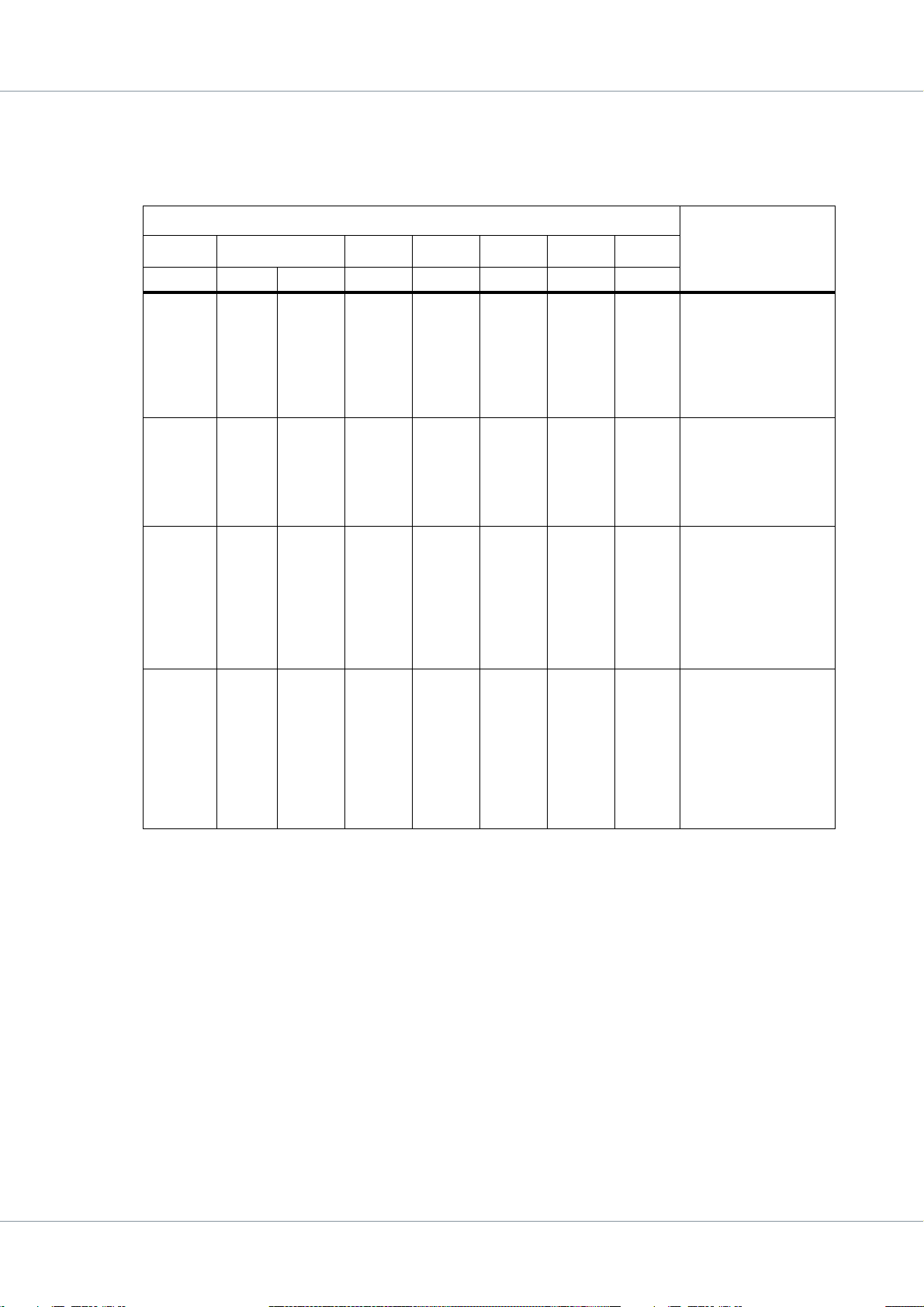

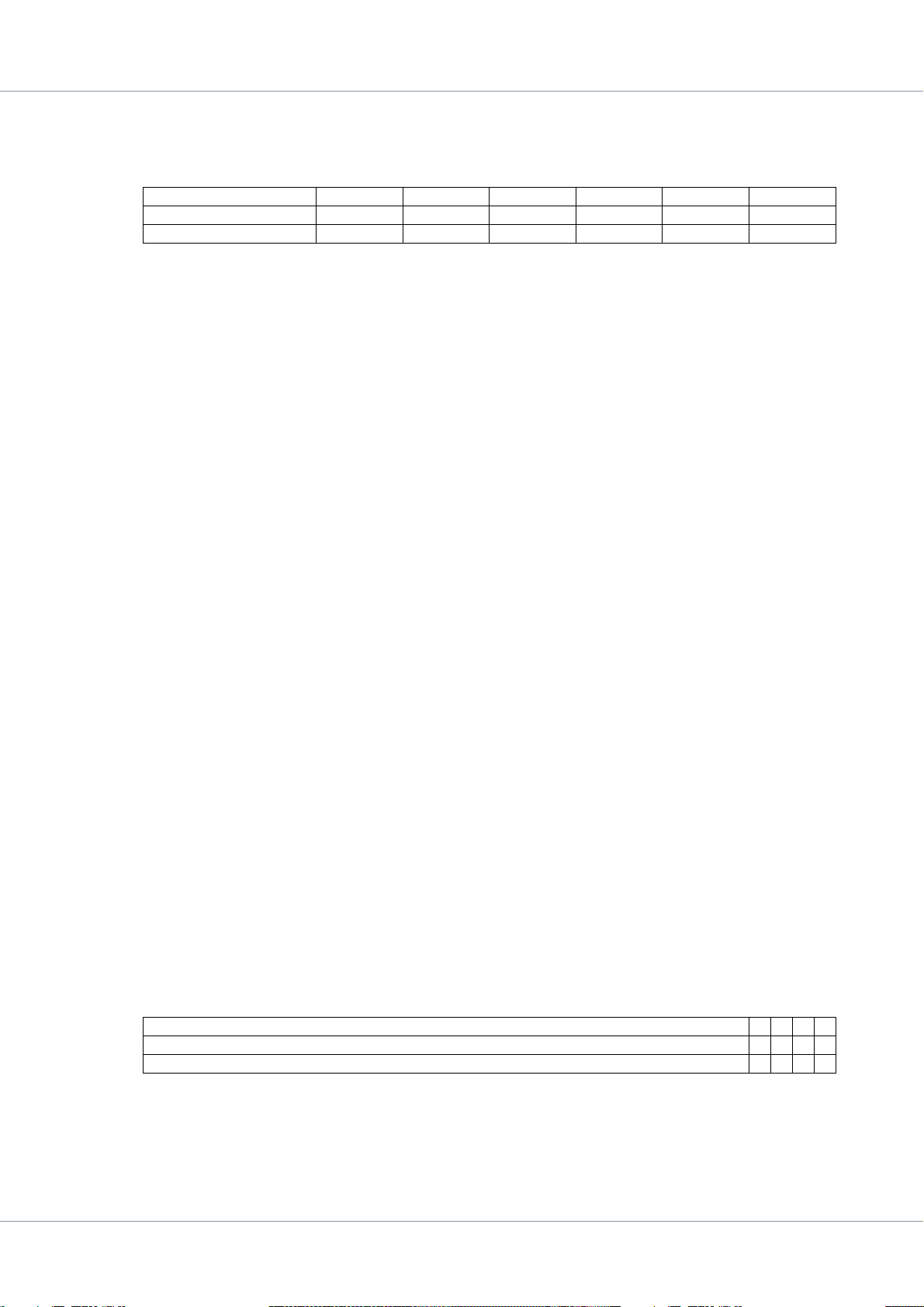

2.2 Digital Architecture Overview

The system is built around three 32-bit AMBA AHB buses; one 32-bit Main AHB bus, one 32-bit

DMA AHB buses and one 32-bit Debug AHB bus. The main bus connects the LEON3FT core with

all other peripheral cores in the design as well as the external memory controllers. Several peripherals

are connected through AMBA AHB/APB bridges where one of the bridges is integrated with the

DMA controller.

The debug AMBA AHB bus connects a UART serial debug communications link to the debug support unit and also to the rest of the system through an AMBA AHB bridge.

Figure 2. Simplified architecture and functional block diagram of the microcontroller

2.2.1 Processor core and memory subsystem

The microcontroller implements a LEON3FT 32-bit processor core conforming to the IEEE-1754

(SPARC V8) architecture. The microcontroller is designed for embedded applications, combining

high performance with low complexity and low power consumption. The LEON3FT core has the following main features: 7-stage pipeline with Harvard architecture, hardware multiplier and divider and

on-chip debug support. The LEON3FT processor is enhanced with fault tolerance against SEU errors.

The fault tolerance is focused on the protection of the on-chip RAM, processor register file and protection of external memory interfaces.

The LEON3FT integer pipeline is implemented with 31 register windows, SEU protection of register

file with zero impact on software timing, and hardware multiply and divide units. The multiplier is a

16x16 hardware multiplier that is iterated four times. Floating-point operations are supported by integration of a hardware floating-point unit (GRFPU-lite).

Memory protection units are located on the AMBA system bus and on AMBA DMA bus. Each protection unit monitors access on the AHB bus. When an access is made to a protected area then the protection unit will assert a signal to the memory controller that will annul the operation and respond to

the AMBA access with an AMBA ERROR response. Four areas can be protected on the system bus

and four areas can be protected on the DMA bus.

Exclusive write permission can be enforced for individual APB peripherals to protect interfaces from

erroneous writes during normal operations.

GR716-DS-UM, May 2019, Version 1.29 20 www.cobham.com/gaisler

Page 19

GR716

To protect tightly coupled instruction and data memory directly connected to the processor core from

software the LEON3FT hardware watchpoints (located within the processor integer unit) can function

as memory protection registers for both the instruction and data RAM.

Several features are supported in the architecture in order to enhance it for embedded microcontroller

applications:

• Support for SPARC V8E write partial %psr

• Support for SPARC V8E Alternative Window Pointer

• Support of the SPARC V8E Multiply step instructions

The microcontroller program execution is deterministic due to the microcontroller being cache-less,

and AMBA accesses made by the processor being unaffected by other AMBA masters in the microcontroller. The processor uses separate EDAC protected instruction and data memories with fixed

latencies. The instruction memory latency is 1 system clock and the delay for the data memory is 1

system clock. The local instruction and data memory in the system have the same latency and behaviour in the corrected as in the uncorrected case. This also applies to the CPU, so dynamic SEU handling schemes such as the LEON3FT pipeline restart on error options is not be used.

The microcontroller has 64 KiB of shared data RAM and 128 KiB of tightly coupled instruction memory connected to the processor. The tightly coupled instruction and data RAM can be accessed via the

AMBA buses. This AMBA access can be used to upload new software into the instruction memory or

read/write data to/from any AMBA master in the system. The access to the data memory will not

affect or delay any access made by the processor on the AMBA bus.

The processor or any AMBA master can access the external PROM/SRAM or SPI memory controller

for program execution or reading/writing data. The external SRAM memory can be protected by the

scrubber located on the main system bus. The scrubber connected to the main system bus will block

access for the processor to the external memories during scrub execution. The scrub rate can be configured and should be set to an acceptable rate for the mission. The scrubber access will not block the

AMBA bus since masters and slaves on the main system bus support split transactions.

GR716-DS-UM, May 2019, Version 1.29 21 www.cobham.com/gaisler

Page 20

GR716

2.2.2 DMA controller

The microcontroller has four parallel DMA controllers. The GRDMAC core provides a flexible direct

memory access controller. The DMA controller can perform burst transfers of data between AHB and

APB peripherals at aligned or unaligned memory addresses. The GRDMAC core has multiple AHB

master interfaces for access to AHB peripheral bus and direct access to all APB slaves. The GRDMAC is able to perform programmable sequences of data transfers between any slaves in AMBA

address space. The IP core is able to transfer data between peripherals and memory and between

memory areas. If the accessed memory is internal or external does not matter, as long as the memory

is mapped into AMBA address space reachable from the AHB bus where the DMA controller is

mapped.

The DMA controller configuration registers are accessible through an APB interface. Each DMA controller can be flexibly configured by means of two descriptor chains residing in main memory: a

Memory to Buffer (M2B) chain and a Buffer to Memory (B2M) chain. Each chain is composed of a

linked list of descriptors, where each descriptor specifies an AHB address and the size of the data to

read/write, supporting a scatter/gather behavior.

Once enabled, the DMA controller will proceed in reading the descriptor chains, then reading memory mapped addresses specified by the M2B chain and filling its internal buffer. It will then write the

content of the buffer back to memory-mapped addresses by elaborating the B2M descriptor chain.

The DMA controller supports a simplified mode of operation, with only one channel. In this mode of

operation only one descriptor is present for each of the M2B and B2M chains. These two descriptors

are written directly in the core's register via APB.

The DMA controller will offload the CPU and provide DMA capabilities to IP cores in the microcontroller design that do not have an internal DMA engine. The DMA controller can be programmed to

initiate DMA transfers on events, such as interrupts, to the GRDMAC core to achieve timely readouts

of values. An example of use can be found the detailed description of the DMA controller in section

28.

2.2.3 Interrupt handling

The microcontroller supports interrupt time stamping and interrupt handling mechanism to ensure that

a fixed number of clock cycles occurs between the assertion of an interrupt and the processor's jump

to the trap table. Depending on the software application, several types of time stamping can be of

interest:

• Timestamp when interrupt line is raised from peripheral IP core. This time is of particular importance when time needs to be synchronized with an external event.

• Timestamp when processor acknowledges the interrupt. This stamp is primarily of interest in system characterization where users may want to measure the time it takes for the processor to divert

execution flow to the interrupt service routine after the processor has discovered the pending

interrupt.

• Timestamp when software enters ISR. This timestamp is typically taken by software by reading a

timer register when the ISR is entered.

Interrupt time stamping is controlled via the Interrupt Timestamp Control register(s) described in section 40. Each Interrupt Timestamp Control register contains a field (TSTAMP) that contains the number of timestamp register sets that the core implements. A timestamp register sets consist of one

Interrupt Timestamp Counter register, one Interrupt Timestamp Control register, one Interrupt Assertion Timestamp register and one Interrupt Acknowledge Timestamp register.

Software enables time stamping for a specific interrupt via an Interrupt Timestamp Control Register.

When the selected interrupt line is asserted, software will save the current value of the interrupt timestamp counter into the Interrupt Assertion Timestamp register. When the processor acknowledges the

interrupt, the Interrupt Timestamp Control register will be set and the current value of the timestamp

GR716-DS-UM, May 2019, Version 1.29 22 www.cobham.com/gaisler

Page 21

GR716

counter will be saved in the Interrupt Acknowledge Timestamp Register. The difference between the

Interrupt Assertion timestamp and the Interrupt Acknowledge timestamp is the number of system

clock cycles that was required for the processor to react to the interrupt and divert execution to the

trap handler.

2.2.4 Reset and software boot

The reset default behavior for all included cores, except the LEON3FT processor, is to enter an idle

state upon reset. The internal reset signal will be asserted as a result of power-on. In the idle state the

cores do not initiate any transactions nor keep any output signals in an idle state. This is of particular

concern for bidirectional signals to prevent contention.

The LEON3FT processor will normally start executing from a predefined start address 0x0000000 at

reset. The start of execution can be prevented by assertion of an external break signal. If the break signal is asserted then the processor will enter power-down mode after reset. This will allow software