Coactive Aesthetics CA386-N1 Reference Manual

CA386-N1

AESTHETICS, INC

Networked

Embedded PC

REFERENCE

MANUAL

VERSION 1.0

CA386-N1

Reference Manual

Disclaimers

Coactive Aesthetics reserves the right to make changes without further notice to an y product herein to impro v e reliability,

function, or design. Coactive Aesthetics does not assume any liability arising out of the application or use of any product

or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Coactive

Aesthetics products are not authorized for use as components in life support devices or systems intended for surgical

implant into the body or intended to support or sustain wet life. Buyer agrees to notify Coactive Aesthetics of any such

intended end use whereupon Coactive Aesthetics shall determine availability and suitability of its product or products for

use intended.

Use, duplication, or disclosure by the United States Government is subject to restrictions as set forth in subparagraph (c)

(1) (ii) of the Rights in T echnical Data and Computer Software clause at CFR 52.227-7013. Coactiv e Aesthetics, Inc. 4000

Bridgeway Suite 303, Sausalito, CA 94965.

Trademarks

Motorola is a registered trademark of Motorola, Inc.

Intel is a registered trademark of Intel Corp.

UNIX is a registered trademark of American Telephone and Telegraph Co.

IBM is a registered trademark of International Business Machines, Inc.

MS-DOS is a registered trademark of Microsoft Corp.

Echelon, LON, LonWorks, LonBuilder, LonManager, LonTalk, LonUsers, NEURON, 3120, and 3150 are trademarks of

Echelon Corporation.

All other trademarks are the property of their respective owners.

Copyrights

Copyright (c) 1994-1995 by Coactive Aesthetics.

All rights reserved.

Manual Revision 4

Covers:

CA386-N1 Hardware, Revision C

Programming the CA386-N1, Version 1.0

Coactive Aesthetics

4000 Bridgeway, Suite 303

Sausalito, CA 94965

(415) 289-1722

(415) 289-1320 (FAX)

info@coactive.com (Email)

http://www.coactive.com (WWW)

Tab le of Contents

Chapter 1 Hardware

1.1 Introduction 1

1.2 Specifications 2

1.3 Related Documentation 2

1.4 Power 2

1.5 Connectors and Jumpers 3

1.5.1 Overview 3

1.5.2 Flash Loader Start-up (JP1) 5

1.5.3 i386EX Reset Generation Jumper (JP2) 5

1.5.4 SMI Source Selection Jumper (JP3) 5

1.5.5 NMI Signal Generation Jumper (JP4) 5

1.5.6 DMA Channel Selection for PC/104 Bus (JP5, JP6) 5

1.5.7 Memory Size Configuration Jumpers (JP7, JP8) 6

1.5.8 User Definable Input Jumper/Switch (JP9) 6

1.5.9 RS-485 Option Jumper (JP10) 7

1.5.10 Asynchronous Serial Communications: COM1, COM2 (J1, J2, J5) 7

1.5.11 PC/104 Bus (J3, J4) 9

1.5.12 I/O Ports (J6) 9

1.5.13 Power Connectors (J7, J10) 11

1.5.14 Serial Peripheral Interface (SPI) (J8) 11

1.5.15 SIMM Memory Socket (U9) 12

1.6 Parts Listing 12

1.7 Mechanical Information 15

Chapter 2 DOS Programming

2.1 Introduction 1

2.2 Quick Start 1

2.3 Desktop Development 3

2.4 Memory Map 7

Table of Contents

2.1.1 Related Documents 1

2.2.1 Overview 1

2.2.2 Tools 2

2.2.3 QuickStart Steps 2

2.3.1 CA386-N1 Companion Diskette 4

2.3.2 The RAM Disk 4

2.3.3 Development using the Remote Serial Disk 4

2.3.4 Development under DOS 5

Table of Contents

2.5 Peripheral I/O 8

2.6 Flash Loader 9

2.6.1 General 9

2.6.2 Addresses 9

2.6.3 Memory Map 10

2.6.4 Downloading a .HEX File to Flash 10

2.6.5 Help Command 11

2.6.6 “:<.....>” (Hex Record) 11

2.6.7 “m <A1> <A2>” (Address Remapping) 11

2.6.8 “w <A1> <A2>” (Address Window) 11

2.6.9 “e <A> [L]” (Erase Sectors) 12

2.6.10 “d <A> [L]” (Display Memory) 12

2.6.11 “j [A]” (Set Jump Address) 12

2.6.12 “b <n>” (Set Baud Rate) 12

2.6.13 “a <n>” (Auto Erase) 12

2.6.14 “v <n>” (Verify Mode) 12

2.6.15 “s” (Show Status) 13

2.6.16 “r” (Reboot) 13

2.7 Flash Disk Organization and Programming 13

2.7.1 ROM Disks 14

2.8 Peripherals 14

2.8.1 Serial Ports 15

2.9 Troubleshooting 15

2.9.1 Communicating with the CA386-N1 15

Appendix A CA386-N1 Schematic

Appendix B PC/104 Specification

CA386-N1 REFERENCE MANUAL

Chapter 1 Hardware

1

1

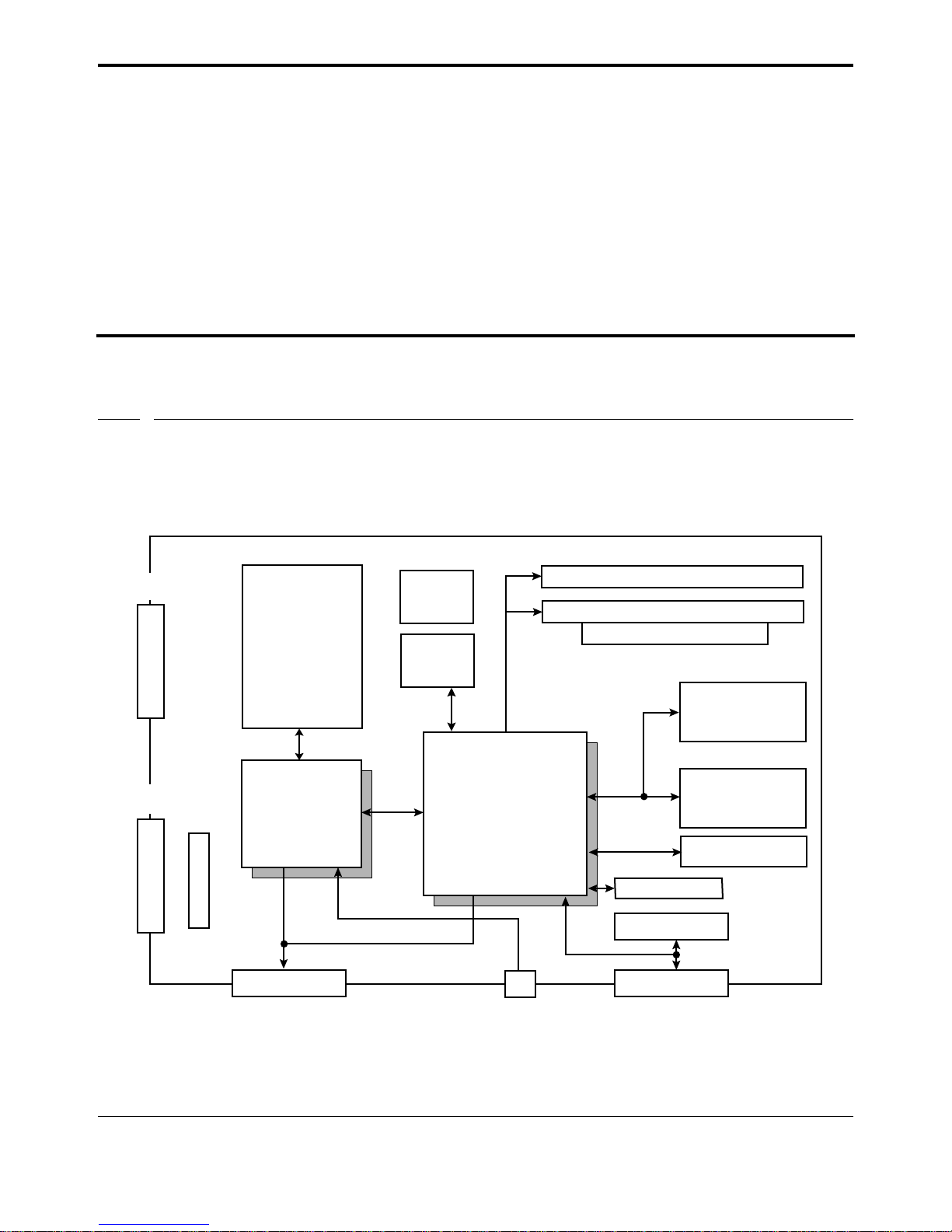

1.1 Introduction

This chapter describes the CA386-N1 hardware. It lists specifications for I/O, power, and mechanical dimensions, covers communications issues, and describes all the jumpers and connectors and their pin-outs. A schematic and a parts list are also included at the end of the chapter. Figure 1.1 is a simplified block diagram of the

CA386-N1.

NETWORK

CONNECTOR

POWER

CONNECTOR

3.0V

CLOCK

78kB or 1.2MB

TWISTED

PAIR

TRANSCEIVER

NEURON

3120

PROCESSOR

INTERNAL PWR

STATUS LEDs NETWORK

BATTERY

OPTIONAL

REAL-TIME

CLOCK

i386EX

MICROCONTROLLER

I/O CONNECTOR

8/16-BIT PC/104

CONNECTOR

256K to 4MB RAM

512K FLASH EPROM

Application

Input Jumper

SPI INTERFACE

RS-232 (COM2)

RS-232 (COM1)

SERVICE

PUSHBUTTON

FIGURE 1.1 CA386-N1 Block Diagram

Hardware 1-1

Specifications

1.2 Specifications

The CA386-N1 is an Intel i386EX based single-board computer with integrated LonTalk interface. Hardware

specifications are as follows:

• 25MHz Intel i386EX Processor

• 256K, 1M, or 4M SIMM DRAM

• 512K Flash EPROM

• NEURON 3120 with MIP Firmware installed

• LonTalk Transceiver: TPT/XF-78, TPT/XF-1250, or FTT-10

• 2 RS-232 asynchronous serial ports (COM1, COM2)

• RS485 option on COM1

• 8 TTL-level digital I/O

• 3 programmable counter/timers

• Battery-backed real-time clock (optional)

• 8/16-bit PC/104 Bus

• Power Requirements: single +5 volt operation (+12V, -12V required if certain PC/104 peripherals are

used)

• Power Consumption: nominal 500mA@5VDC

• Power Connector: 5-wire 5.08mm removable-plug screw terminal

• Network Connector: 2-wire 5.08mm removable-plug screw terminal or dual RJ45 jacks

• Dimensions: 4” (10.2mm) x6.25”(15.9mm) x approximately 1/2”

• Operating Temperature: 0-70 C

1.3 Related Documentation

The following documents are useful for a full understanding of the CA386-N1 system:

• Intel386EX Embedded Microprocessor Hardware Reference - available from Intel Corporation Liter-

ature Sales, P.O. Box 7641, Mt. Prospect, IL 60056-7641

• LONWorks Technology Device Data - available from Motorola Literature Distribution Center, P.O.

Box 20912, Phoenix, AZ 85036

1.4 Power

Power is supplied to the CA386-N1 through either connector J7 or J10. There are lines on both J7 and J10 for the

following voltages:

• +5VDC

• +12VDC

• -12VDC

• Gnd

• Vin - Variable Voltage Input for use with a power supply or converter

1-2 CA386-N1 REFERENCE MANUAL

The board is designed to be powered in one of two ways:

• “Raw” power and ground connected through J7-Vin, and a regulator attached to J10 which takes the

raw power in and produces +5V (and +12V, -12V if required).

• +5V (and +12V, -12V if required) supplied through J7; J10 unused.

The first method is useful for providing an internal power supply or converter in an enclosure.

1.5 Connectors and Jumpers

1.5.1 Overview

Figure 1.2 shows the locations of all the connectors and jumpers on the CA386-N1. The following sections

describe each jumper and connector in detail. Note that each connector or jumper shown below is oriented such

that the power and network connectors (J7, J9) are at the “top” of the board. Also note that the reference designators (labels) are shown in their actual location and orientation relative to the connector or jumper.

Connectors and Jumpers

Hardware 1-3

Connectors and Jumpers

C

JP10

FIGURE 1.2 CA386-N1 Parts Locations

1-4 CA386-N1 REFERENCE MANUAL

Loading...

Loading...