Page 1

Global LCD Panel Exchange Center

www.panelook.com

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

www.panelook.com

Page 2

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

- CONTENTS -

REVISION HISTORY

1. GENERAL DESCRIPTION

1.1 OVERVIEW

1.2 FEATURES

1.3 APPLICATION

1.4 GENERAL SPECIFICATIONS

1.5 MECHANICAL SPECIFICATIONS

2. ABSOLUTE MAXIMUM RATINGS

2.1 ABSOLUTE RATINGS OF ENVIRONMENT

2.2 ELECTRICAL ABSOLUTE RATINGS

2.2.1 TFT LCD MODULE

2.2.2 BACKLIGHT UNIT

3. ELECTRICAL CHARACTERISTICS

3.1 TFT LCD MODULE

3.2 BACKLIGHT UNIT

4. BLOCK DIAGRAM

4.1 TFT LCD MODULE

4.2 BACKLIGHT UNIT

5. INPUT TERMINAL PIN ASSIGNMENT

5.1 TFT LCD MODULE

5.2 BACKLIGHT UNIT

5.3 TIMING DIAGRAM OF LVDS INPUT SIGNAL

5.4 COLOR DATA INPUT ASSIGNMENT

5.5 EDID DATA STRUCTURE

6. INVERTER SPECIFICATION

6.1 INPUT CONNECTOR PIN ASSIGNMENT

6.2 INPUT CONNECTOR PIN ASSIGNMENT

6.3 OUTPUT CONNECTOR PIN ASSIGNMENT

6.4 GENERAL ELECTRICAL SPECIFICATION

7. INTERFACE TIMING ------------------------------------------------------- 23

7.1 INPUT SIGNAL TIMING SPECIFICATIONS

7.2 POWER ON/OFF SEQUENCE

8. OPTICAL CHARACTERISTICS

8.1 TEST CONDITIONS

8.2 OPTICAL SPECIFICATIONS

9. PRECAUTIONS

9.1 HANDLING PRECAUTIONS

9.2 STORAGE PRECAUTIONS

9.3 OPERATION PRECAUTIONS

10. PACKING ------------------------------------------------------- 32

10.1 CARTON

10.2 PALLET

------------------------------------------------------- 1

------------------------------------------------------- 5

------------------------------------------------------- 6

------------------------------------------------------- 8

------------------------------------------------------- 12

------------------------------------------------------- 13

------------------------------------------------------- 19

------------------------------------------------------- 25

------------------------------------------------------- 27

2 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 3

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

11. DEFINITION OF LABELS ------------------------------------------------------- 32

11.1 CMO MODULE LABEL

11.2 CMO CARTON LABE

3 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 4

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Version Date

3.0

Jan 17,’06 All

Page

(New)

REVISION HISTORY

Section Description

All Approval specification was first issued.

4 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 5

Global LCD Panel Exchange Center

1 GENERAL DESCRIPTION

1.1 OVERVIEW

N141C1 - L01 is a 14.1” TFT Liquid Crystal Display module with single CCFL Backlight unit and 30 pins

LVDS interface. This module supports 1440 x (3 RGB) x 900 WXGA+ mode and can display 262,144 colors.

The optimum viewing angle is at 6 o’clock direction. The inverter module for Backlight is built in.

1.2 FEATURES

- Thin and Light Weight

- WXGA+ (1440 x 900 pixels) resolution

- DE only mode

- 3.3V LVDS (Low Voltage Differential Signaling) interface with 2 pixel/clock

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

1.3 APPLICATION

- TFT LCD Notebook

1.4 GENERAL SPECIFICATI0NS

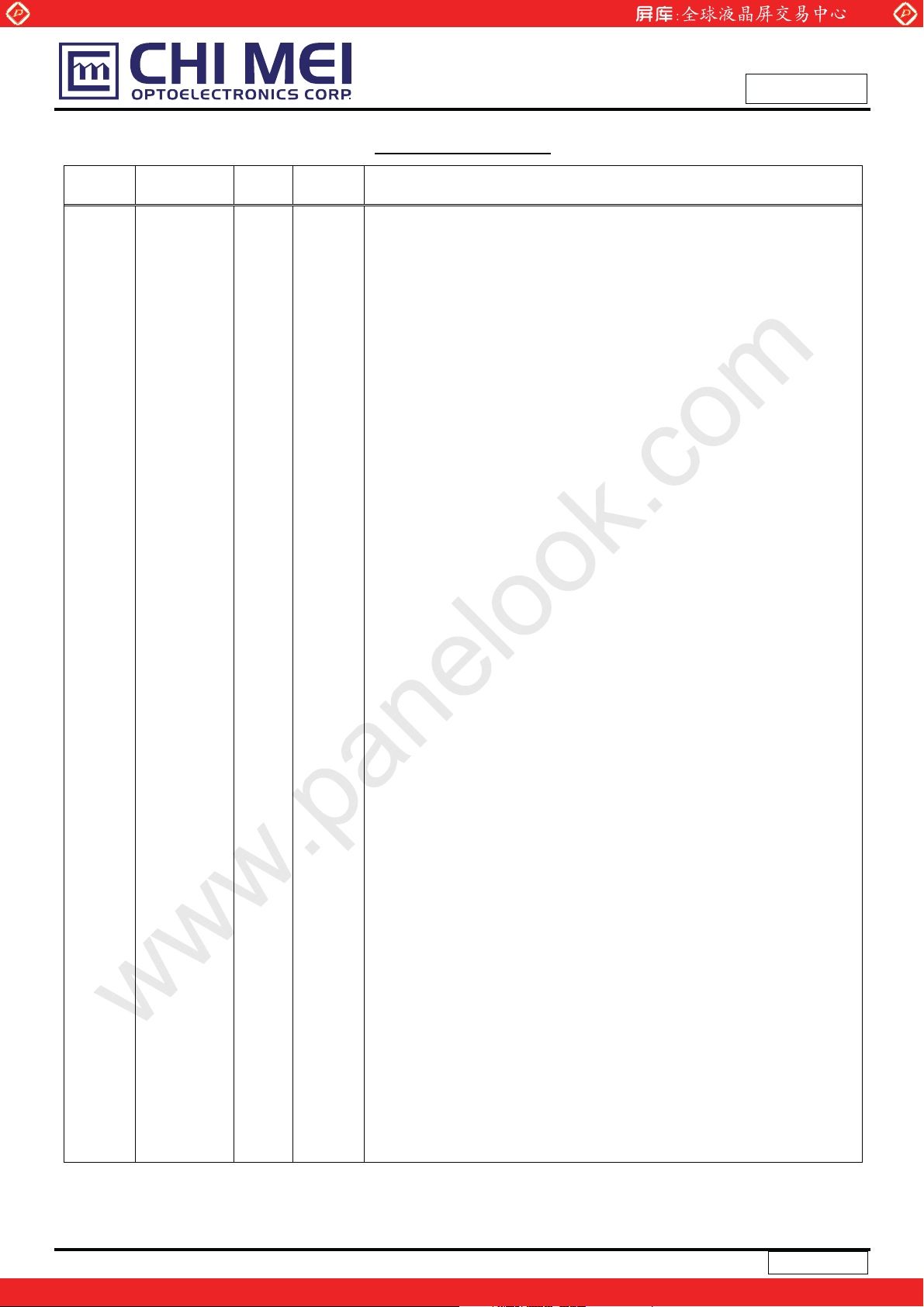

Item Specification Unit Note

Active Area 303.48(H) X 189.675(V) (14.1 inch Diagonal) mm

Bezel Opening Area 306.76 (H) x 193.0 (V) mm

Driver Element a-si TFT active matrix - Pixel Number 1440 x R.G.B. x 900 pixel Pixel Pitch 0.21075 (H) x 0.21075 (V) mm Pixel Arrangement RGB vertical stripe - Display Colors 262,144 color Transmissive Mode Normally white - Surface Treatment Antiglare/ Antisatic and Hard Coat (3H min.) - -

1.5 MECHANICAL SPECIFICATIONS

Item Min. Typ. Max. Unit Note

Horizontal(H) 319 319.5 320 mm

Module Size

Vertical(V) 205 205.5 206 mm

Depth(D) -- 5.2 5.5 mm

Weight -- 395 410 g (2)

Weight -- 410 425 g (3)

(1)

(1)

Note (1) Please refer to the attached drawings for more information of front and back outline dimensions

(2) Weight without inverter

(3) Weight with inverter.

5 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 6

Global LCD Panel Exchange Center

A

2 ABSOLUTE MAXIMUM RATINGS

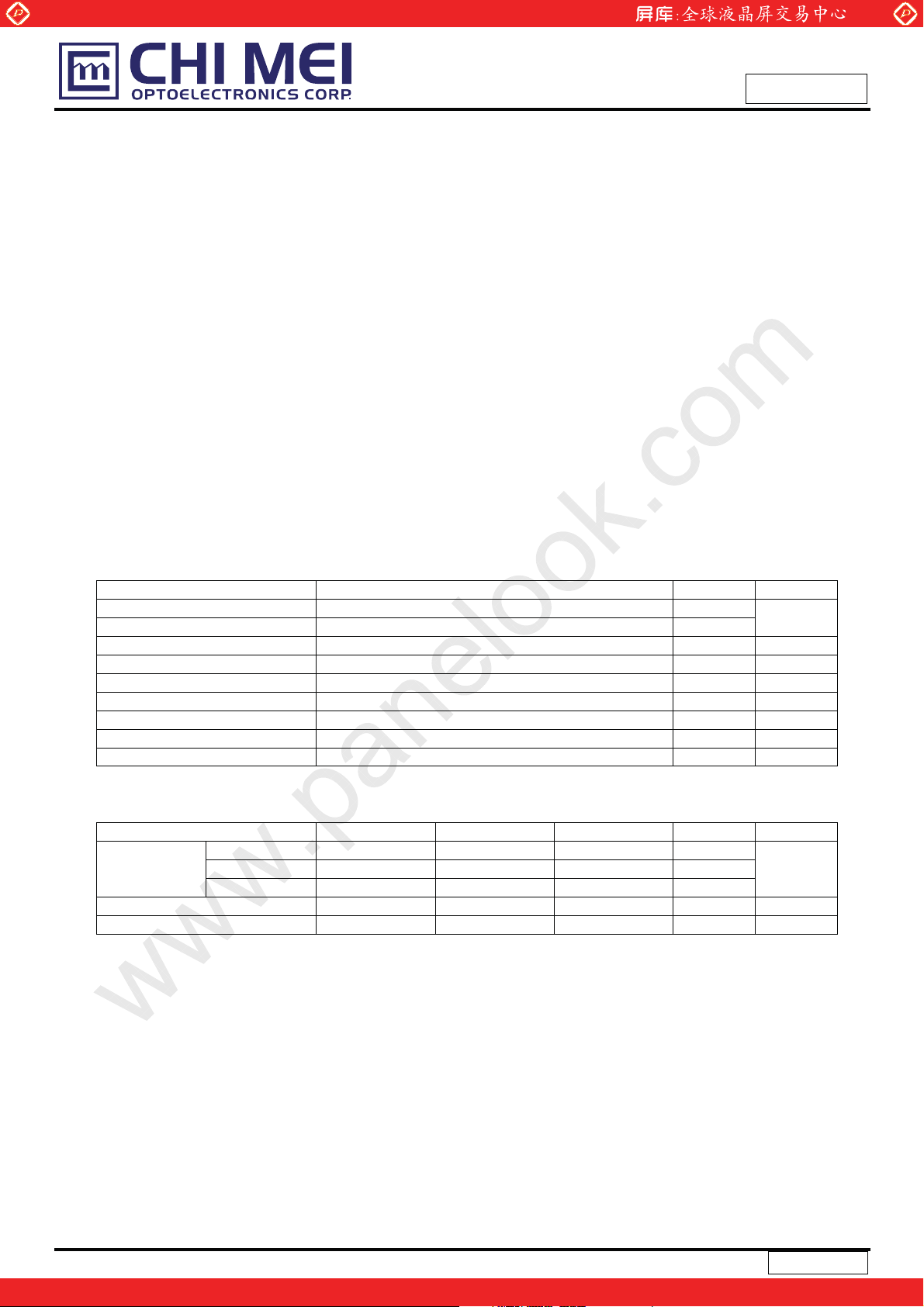

2.1 ABSOLUTE RATINGS OF ENVIRONMENT

Item Symbol

Storage Temperature TST -20 +60 ºC (1)

Operating Ambient Temperature TOP 0 +50 ºC (1), (2)

Shock (Non-Operating) S

Vibration (Non-Operating) V

Note (1) Temperature and relative humidity range is shown in the figure below.

(a) 90 %RH Max. (Ta Љ 40 ºC).

(b) Wet-bulb temperature should be 39 ºC Max. (Ta > 40 ºC).

(c) No condensation .

Note (2) The temperature of panel display surface area should be 0 ºC Min. and 60 ºC Max.

www.panelook.com

Min. Max.

- 220 G (3), (5)

NOP

- 1.5 G (4), (5)

NOP

Value

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Unit Note

Relative Humidity (%RH)

100

90

80

60

Operating Range

40

20

10

Storage Range

Temperature (ºC)

Note (3) 1 time for ± X, ± Y, ± Z. for Condition (220G / 2ms) is half Sine Wave

8060 -20 40020-40

Note (4) 10 ~ 300 Hz, 10 min / Cycle, 3 cycles for each X, Y, Z.:

Note (5) At testing Vibration and Shock, the fixture in holding the module has to be hard and rigid enough

so that the module would not be twisted or bent by the fixture.

The fixing condition is shown as below:

t Room Temperature

Side Mount Fixing Screw

Gap=2mm

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Bracket

LCD Module

Side Mount Fixing Screw

Stage

6 / 35

Version 3.0

www.panelook.com

Page 7

Global LCD Panel Exchange Center

2.2 ELECTRICAL ABSOLUTE RATINGS

2.2.1 TFT LCD MODULE

Item Symbol

Power Supply Voltage VCC -0.3 +4.0 V

Logic Input Voltage VIN -0.3 VCC+0.3 V

2.2.2 BACKLIGHT UNIT

Item Symbol

Lamp Voltage VL - 2.5K V

Lamp Current IL 2.0 6.5 mA

Lamp Frequency FL 45 80 KHz

Note (1) Permanent damage to the device may occur if maximum values are exceeded. Function operation

should be restricted to the conditions described under Normal Operating Conditions.

www.panelook.com

Value

Min. Max.

Value

Min. Max.

Unit Note

Unit Note

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

(1)

(1), (2)

RMS

RMS

(1), (2)

Note (2) Specified values are for lamp (Refer to 3.2 for further information).

7 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 8

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

3 ELECTRICAL CHARACTERISTICS

3.1 TFT LCD MODULE Ta = 25 ± 2 ºC

Parameter Symbol

Min. Typ. Max.

Power Supply Voltage Vcc 3.0 3.3 3.6 V Ripple Voltage VRP - - 100 mV Rush Current I

Power Supply Current

Logical Input Voltage

White - 380 430 mA (3)a

Black

“H” Level VIL - - +100 mV “L” Level V

- - 1.5 A (2)

RUSH

lcc

-100 - - mV -

IH

- 465 510 mA (3)b

Terminating Resistor RT - 100 - Ohm Power per EBL WG P

- 3.19 - W (4)

EBL

Note (1) The module should be always operated within above ranges.

Value

Unit Note

Approval

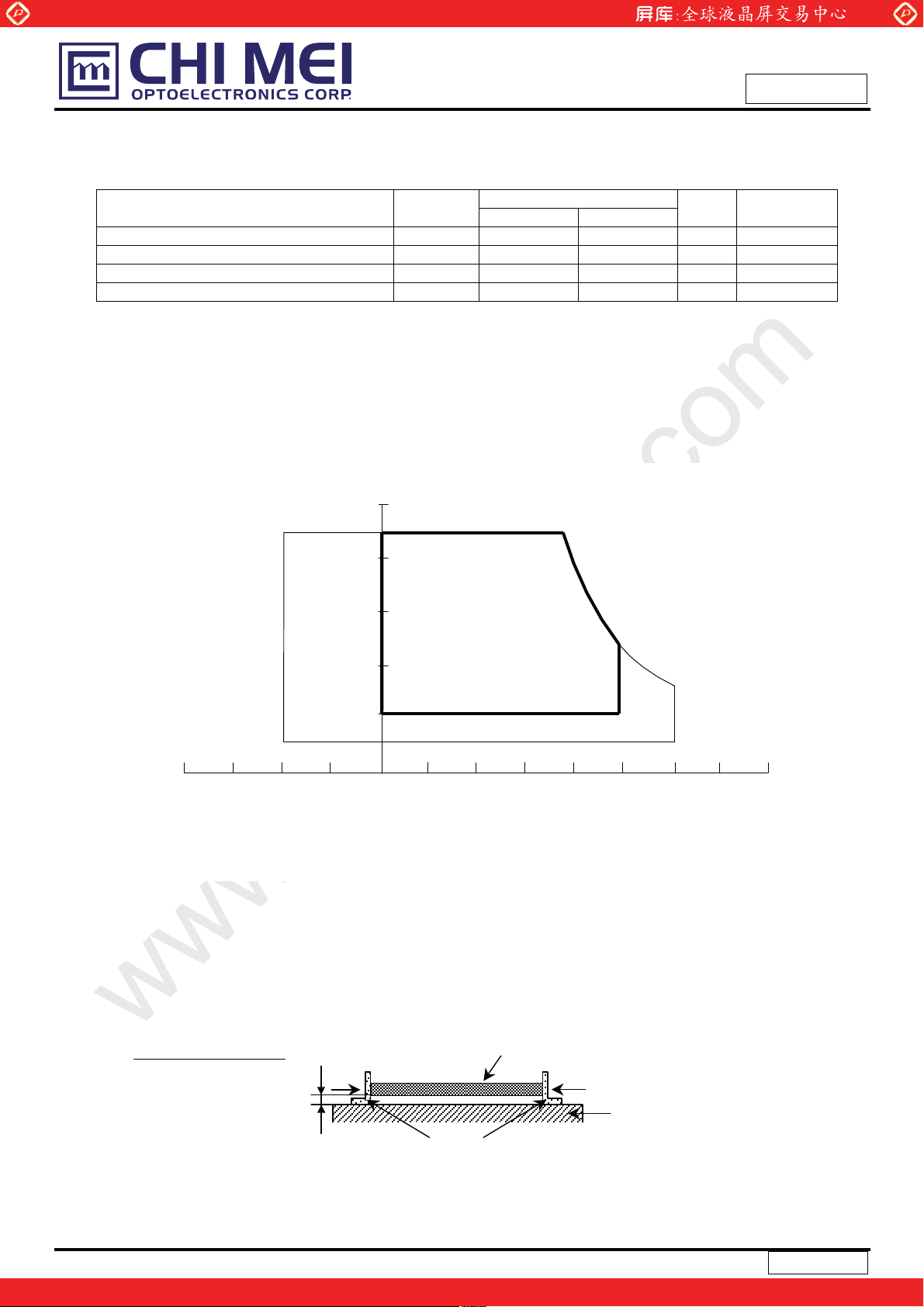

Note (2) Measurement Conditions:

+3.3V

R1

47K

(High to Low)

(Control Signal)

SW

+12V

C1

1uF

VR1

R2

1K

47K

Vcc rising time is 470us

Q1 2SK1475

C2

0.01uF

Q2

2SK1470

+3.3V

FUSE

C3

1uF

Vcc

(LCD Module Input)

0.9Vcc

0.1Vcc

GND

470us

Note (3) The specified power supply current is under the conditions at Vcc = 3.3 V, Ta = 25 ± 2 ºC, f

Hz, whereas a power dissipation check pattern below is displayed.

8 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

= 60

v

Version 3.0

www.panelook.com

Page 9

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Note (4) The specified power are the sum of LCD panel electronics input power and the inverter input

a. White Pattern

Active Area

power. Test conditions are as follows.

(a) Vcc = 3.3 V, Ta = 25 ± 2 ºC, f

(b) The pattern used is a black and white 32 x 36 checkerboard, slide #100 from the VESA file

“Flat Panel Display Monitor Setup Patterns”, FPDMSU.ppt.

(c) Luminance: 60 nits.

.(d) The inverter used is provided from Sumida (www.sumida.com.tw)

= 60 Hz,

v

b. Black Pattern

Active Area

. Please contact Sumida for detail

information. CMO provides the inverter in this product.

9 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 10

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

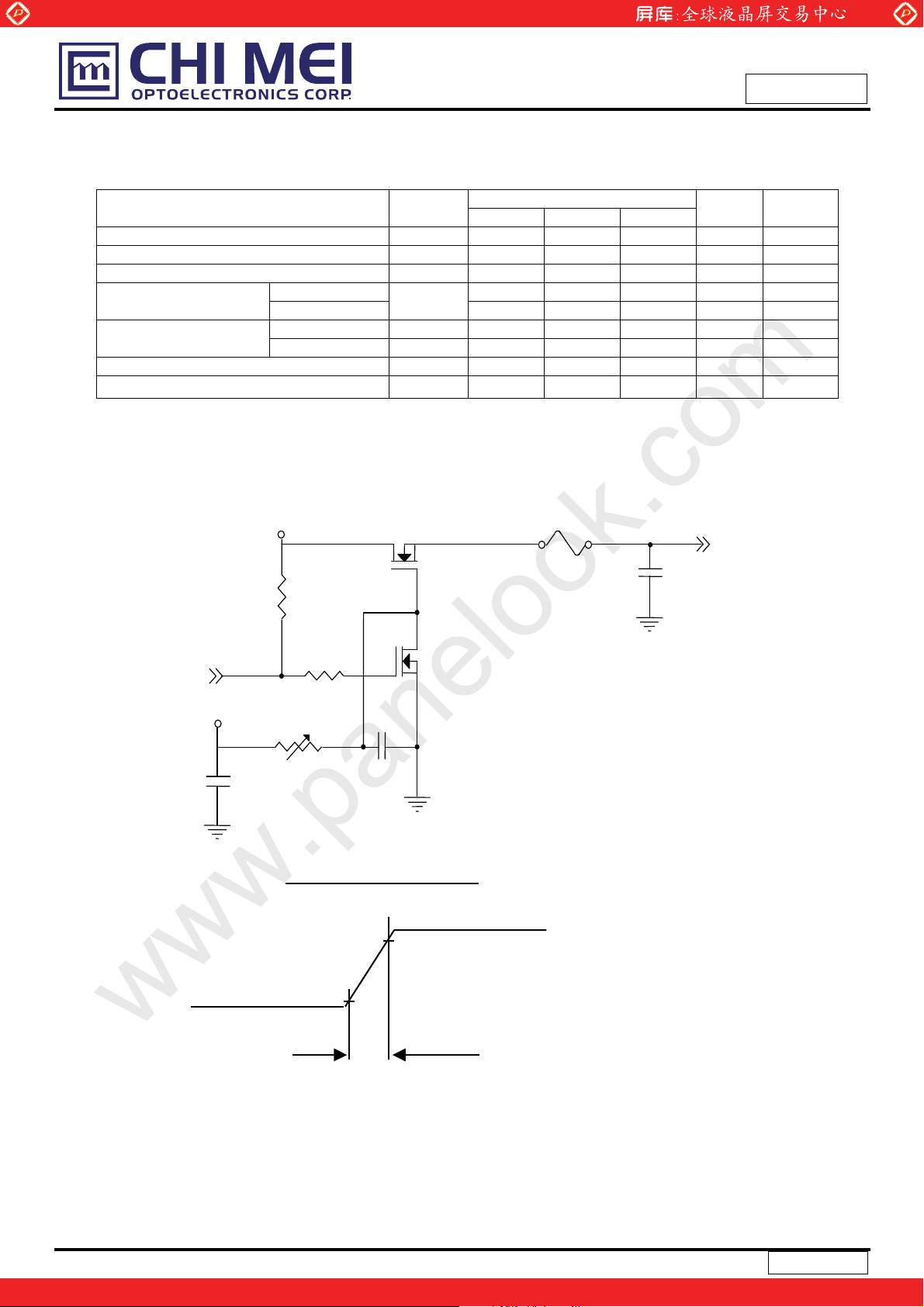

3.2 BACKLIGHT UNIT Ta = 25 ± 2 ºC

Parameter Symbol

Min. Typ. Max.

Lamp Input Voltage VL 612 680 748 V

Lamp Current IL 2.0 6.0 6.5 mA

Lamp Turn On Voltage VS

- - 1370 (25

- - 1520 (0

Operating Frequency FL 45 - 80 KHz (3)

Lamp Life Time LBL 15,000 - - Hrs (5)

Power Consumption PL - 4.08 - W (4), IL = 6.0 mA

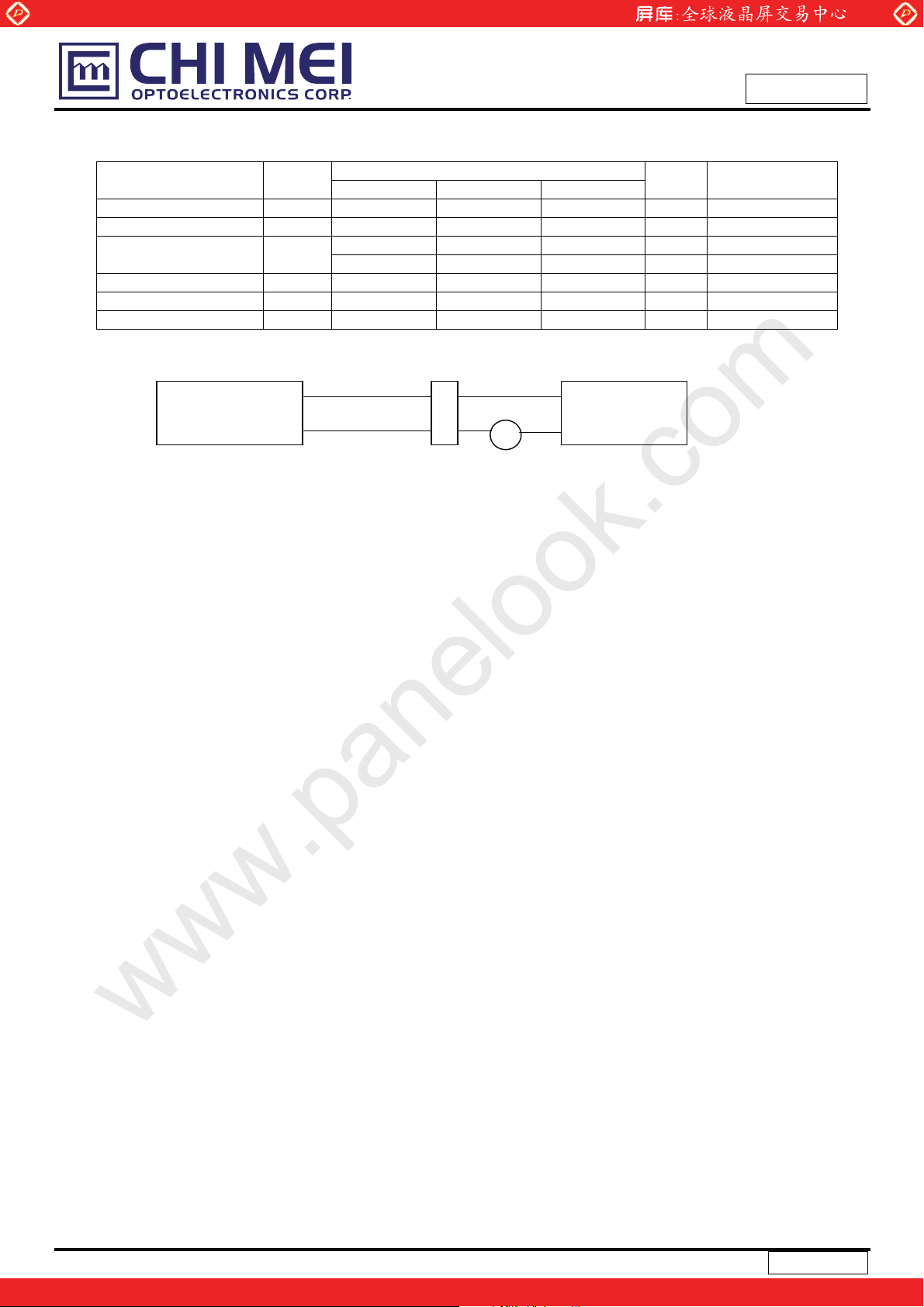

Note (1) Lamp current is measured by utilizing a high frequency current meter as shown below:

Value

o

C) V

o

C) V

Unit Note

I

RMS

(1)

RMS

(2)

RMS

(2)

RMS

Approval

= 6.0 mA

L

LCD

Module

HV (Pink)

LV (White)

1

2

Current Meter

Inverter

A

Note (2) The voltage that must be larger than Vs should be applied to the lamp for more than 1 second

after startup. Otherwise the lamp may not be turned on.

Note (3) The lamp frequency may produce interference with horizontal synchronous frequency from the

display, and this may cause line flow on the display. In order to avoid interference, the lamp

frequency should be detached from the horizontal synchronous frequency and its harmonics as far

as possible.

Note (4) P

= IL VL

L

Note (5) The lifetime of lamp can be defined as the time in which it continues to operate under the condition

Ta = 25 2

o

C and IL = 6 mArms until one of the following events occurs:

(a) When the brightness becomes or lowers than 50% of its original value.

(b) When the effective ignition length becomes or lowers than 80% of its original value. (Effective

ignition length is defined as an area that has less than 70% brightness compared to the

brightness in the center point.)

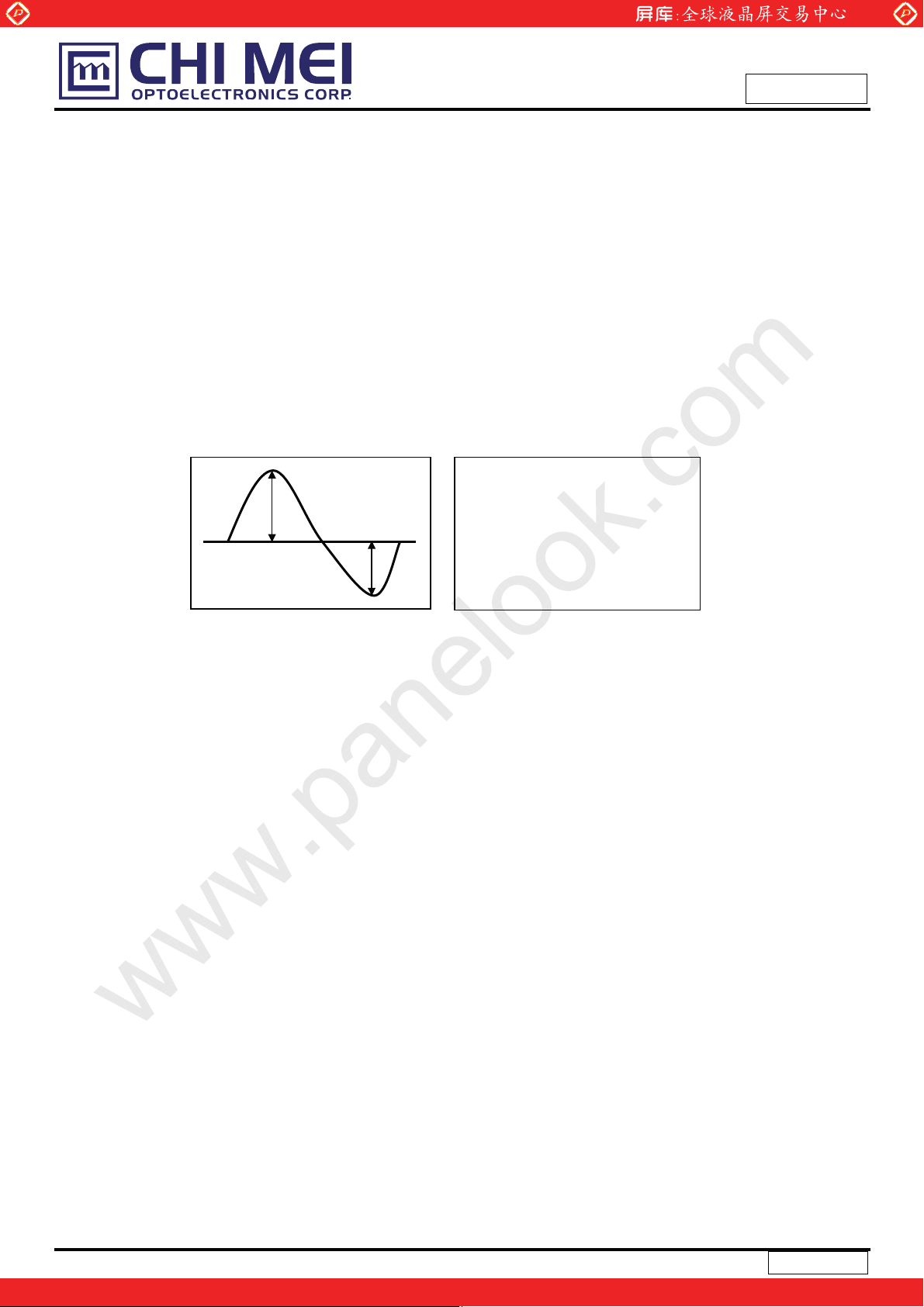

Note (6) The waveform of the voltage output of inverter must be area-symmetric and the design of the

inverter must have specifications for the modularized lamp. The performance of the Backlight,

such as lifetime or brightness, is greatly influenced by the characteristics of the DC-AC inverter for

the lamp. All the parameters of an inverter should be carefully designed to avoid producing too

much current leakage from high voltage output of the inverter. When designing or ordering the

inverter please make sure that a poor lighting caused by the mismatch of the Backlight and the

inverter (miss-lighting, flicker, etc.) never occurs. If the above situation is confirmed, the module

should be operated in the same manners when it is installed in your instrument.

The output of the inverter must have symmetrical (negative and positive) voltage waveform and

symmetrical current waveform.(Unsymmetrical ratio is less than 10%) Please do not use the inverter

10 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 11

Global LCD Panel Exchange Center

which has unsymmetrical voltage and unsymmetrical current and spike wave. Lamp frequency may

produce interface with horizontal synchronous frequency and as a result this may cause beat on the

display. Therefore lamp frequency shall be as away possible from the horizontal synchronous

frequency and from its harmonics in order to prevent interference.

Requirements for a system inverter design, which is intended to have a better display performance, a

better power efficiency and a more reliable lamp. It shall help increase the lamp lifetime and reduce its

leakage current.

a. The asymmetry rate of the inverter waveform should be 10% below.

b. The distortion rate of the waveform should be within Ѕ2 ± 10%.

c. The ideal sine wave form shall be symmetric in positive and negative polarities.

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

* Asymmetry rate:

I p

-p

I

| I

* Distortion rate

I

– I –p | / I

p

(or I –p) / I

p

rms

rms

* 100%

11 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 12

Global LCD Panel Exchange Center

)

4 BLOCK DIAGRAM

4.1 TFT LCD MODULE

Rxin0(+/-)

Rxin1(+/-)

Rxin2(+/-)

(JAE-FI-XB30SRL-HF11)

INPUT CONNECTOR

CLK(+/-)

Vcc

GND

Data

CLK

V

EDID

EDID

EDID

VL

LAMP CONNECTOR

(JST-BHSR-02VS-1)

www.panelook.com

LVDS INPUT /

TIMING CONTROLLER

DC/DC CONVERTER &

REFERENCE VOLTAGE

GENERATOR

EDID

EEPROM

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

SCAN DRIVER IC

TFT LCD PANEL

(1440xR.G.B.x900)

DATA DRIVER IC

BACKLIGHT UNIT

Approval

4.2 BACKLIGHT UNIT

1 HV (Pink)

2 LV (White

12 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 13

Global LCD Panel Exchange Center

5 INPUT TERMINAL PIN ASSIGNMENT

5.1 TFT LCD MODULE

Pin Symbol Description Polarity Remark

1 Vss Ground

2 Vcc Power Supply +3.3 V (typical)

3 Vcc Power Supply +3.3 V (typical)

4 V

5 BIST Panel BIST enable

6 CLK

7 DATA

8 RXO0- LVDS Differential Data Input (Odd) Negative

9 RXO0+ LVDS Differential Data Input (Odd) Positive

10 Vss Ground

11 RXO1- LVDS Differential Data Input (Odd) Negative

12 RXO1+ LVDS Differential Data Input (Odd) Positive

13 Vss Ground

14 RXO2- LVDS Differential Data Input (Odd) Negative

15 RXO2+ LVDS Differential Data Input (Odd) Positive

16 Vss Ground

17 RXOC- LVDS Clock Data Input (Odd) Negative

18 RXOC+ LVDS Clock Data Input (Odd) Positive

19 Vss Ground

20 RxE0- LVDS Differential Data Input (Even) Negative

21 RxE0+ LVDS Differential Data Input (Even) Positive

22 Vss Ground

23 RxE1- LVDS Differential Data Input (Even) Negative

24 RxE1+ LVDS Differential Data Input (Even) Positive

25 Vss Ground

26 RxE2- LVDS Differential Data Input (Even) Negative

27 RxE2+ LVDS Differential Data Input (Even) Positive

28 Vss Ground

29 RXEC- LVDS Clock Data Input (Even) Negative

30 RXEC+ LVDS Clock Data Input (Even) Positive

Note (1) Connector Part No.: JAE-FI-XB30SRL-HF11 or equivalent

DDC 3.3V Power

EDID

DDC Clock

EDID

DDC Data -

EDID

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Note (2) User’s connector Part No: JAE-FI-X30C2L or equivalent

Note (3) The first pixel is odd as shown in the following figure.

13 / 35

Version 3.0

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

www.panelook.com

Page 14

Global LCD Panel Exchange Center

5.2 BACKLIGHT UNIT

Pin Symbol Description Color

1 HV High Voltage Pink

2 LV Ground White

Note (1) Connector Part No.: JST- BHSR-02VS-1 or equivalent

Note (2) User’s connector Part No.: SM02B-BHSS-1-TB or equivalent

5.3 TIMING DIAGRAM OF LVDS INPUT SIGNAL

RXOC+

T/7

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

RXO2+/-

RXO1+/-

RXO0+/-

RXEC+

RXE2+/-

RXE1+/-

RXE0+/-

IN20 IN19 IN18 IN17 IN16 IN15 IN14

DE OB5 OB4 OB3 OB2 Vsync Hsync

IN13 IN12 IN11 IN10 IN9 IN8 IN7

OB1 OG4 OG3 OG2 OG1 OB0 OG5

IN6 IN5 IN4 IN3 IN2 IN1 IN0

OG0 OR3 OR2 OR1 OR0 OR5 OR4

Signal for 1 DCLK Cycle (T)

T/7

IN20 IN19 IN18 IN17 IN16 IN15 IN14

DE EB5 EB4 EB3 EB2 Vsync Hsync

IN13 IN12 IN11 IN10 IN9 IN8 IN7

EB1 EG4 EG3 EG2 EG1 EB0 EG5

IN6 IN5 IN4 IN3 IN2 IN1 IN0

EG0 ER3 ER2 ER1 ER0 ER5 ER4

Signal for 1 DCLK Cycle (T)

14 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 15

Global LCD Panel Exchange Center

5.4 COLOR DATA INPUT ASSIGNMENT

The brightness of each primary color (red, green and blue) is based on the 6-bit gray scale data input for

the color. The higher the binary input, the brighter the color. The table below provides the assignment of

color versus data input.

Color

R5 R4 R3 R2 R1 R0 G5 G4 G3 G2 G1 G0 B5 B4 B3 B2 B1 B0

Black

Red

Green

Basic

Colors

Gray

Scale

Of

Red

Gray

Scale

Of

Green

Gray

Scale

Of

Blue

Note (1) 0: Low Level Voltage, 1: High Level Voltage

Blue

Cyan

Magenta

Yellow

White

Red(0)/Dark

Red(1)

Red(2)

:

:

Red(61)

Red(62)

Red(63)

Green(0)/Dark

Green(1)

Green(2)

:

:

Green(61)

Green(62)

Green(63)

Blue(0)/Dark

Blue(1)

Blue(2)

:

:

Blue(61)

Blue(62)

Blue(63)

0

0

1

1

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

:

:

1

1

1

1

1

1

0

0

0

0

0

0

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

0

0

0

0

0

0

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Data Signal

Red Green Blue

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

1

1

0

1

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

0

0

0

0

1

1

1

1

0

1

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

1

1

1

1

0

1

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

15 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 16

Global LCD Panel Exchange Center

5.5 EDID DATA STRUCTURE

The EDID (Extended Display Identification Data) data formats are to support displays as defined in the

VESA Plug & Display and FPDI standards.

Byte #

(decimal)

0 0 Header

1 1 Header

2 2 Header

3 3 Header

4 4 Header

5 5 Header

6 6 Header

7 7 Header

8 8 EISA ID manufacturer name (“CMO”)

9 9 EISA ID manufacturer name (Compressed ASCII)

10 0A ID product code (N141C1-L01) 15

11 0B ID product code (hex LSB first; N141C1-L01) 14

12 0C ID S/N (fixed “0”)

13 0D ID S/N (fixed “0”)

14 0E ID S/N (fixed “0”)

15 0F ID S/N (fixed “0”)

16 10 Week of manufacture (fixed “00H”)

17 11 Year of manufacture (fixed “00H”)

18 12 EDID structure version # (“1”)

19 13 EDID revision # (“3”)

20 14 Video I/P definition (“digital”)

21 15 Active area horizontal 30.348cm

22 16 Active area vertical 18.9675cm

23 17 Display Gamma (Gamma = ”2.2”)

24 18 Feature support (“Active off, RGB Color”)

25 19 Rx1 Rx0 Ry1 Ry0 Gx1 Gx0 Gy1 Gy0

26 1A Bx1 Bx0 By1 By0 Wx1 Wx0 Wy1 Wy0

27 1B Rx=0.597

28 1C Ry=0.340

29 1D Gx=0.320

30 1E Gy=0.535

31 1F Bx=0.152

32 20 By=0.125

33 21 Wx=0.313

34 22 Wy=0.329

35 23 Established timings 1

36 24 Established timings 2 (1280*800@60Hz)

37 25 Manufacturer’s reserved timings

38 26 Standard timing ID # 1

39 27 Standard timing ID # 1

40 28 Standard timing ID # 2

41 29 Standard timing ID # 2

Byte

#(hex)

Field Name and Comments Value

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Value

(hex)

00 00000000

FF 11111111

FF 11111111

FF 11111111

FF 11111111

FF 11111111

FF 11111111

00 00000000

0D 00001101

AF 10101111

00 00000000

00 00000000

00 00000000

00 00000000

00 00000000

00 00000000

01 00000001

03 00000011

80 10000000

1E 00011110

13 00010011

78 01111000

0A 00001010

C0 11000000

05 00000101

98 10011000

57 01010111

52 01010010

89 10001001

27 00100111

20 00100000

50 01010000

54 01010100

00 00000000

00 00000000

00 00000000

01 00000001

01 00000001

01 00000001

01 00000001

(binary)

00010101

00010100

16 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 17

Global LCD Panel Exchange Center

42 2A Standard timing ID # 3 01 00000001

43 2B Standard timing ID # 3

44 2C Standard timing ID # 4

45 2D Standard timing ID # 4

46 2E Standard timing ID # 5

47 2F Standard timing ID # 5

48 30 Standard timing ID # 6

49 31 Standard timing ID # 6

50 32 Standard timing ID # 7

51 33 Standard timing ID # 7

52 34 Standard timing ID # 8

53 35 Standard timing ID # 8

Detailed timing description # 1 Pixel clock (“88.75MHz”,

54 36

55 37 # 1 Pixel clock (hex LSB first)

56 38 # 1 H active (“1440”)

57 39 # 1 H blank (“160”)

58 3A # 1 H active : H blank (“1440 : 160”)

59 3B # 1 V active (”900”)

60 3C # 1 V blank (”26”)

61 3D # 1 V active : V blank (”900 :26”)

62 3E # 1 H sync offset (”48”)

63 3F # 1 H sync pulse width ("32”)

64 40 # 1 V sync offset : V sync pulse width (”3 : 6”)

65 41

66 42 # 1 H image size (”303 mm”)

67 43 # 1 V image size (”190 mm”)

68 44 # 1 H image size : V image size (”303 : 190”)

69 45 # 1 H boarder (”0”)

70 46 # 1 V boarder (”0”)

71 47

72 48

73 49 # 2 Pixel clock (hex LSB first)

74 4A # 2 H active (“1440”)

75 4B # 2 H blank (“160”)

76 4C # 2 H active : H blank (“1440 : 160”)

77 4D # 2 V active (”900”)

78 4E # 2 V blank (”22”)

79 4F # 2 V active : V blank (”900 : 22”)

80 50 # 2 H sync offset (”48”)

81 51 # 2 H sync pulse width (”32”)

82 52 # 2 V sync offset : V sync pulse width (”3 : 6”)

83 53

84 54 # 2 H image size (”303 mm”)

85 55 # 2 V image size (”190 mm”)

According to VESA CVT Rev1.1)

# 1 H sync offset : H sync pulse width : V sync offset : V sync

width (”48: 32 : 3 : 6”)

# 1 Non-interlaced, Normal, no stereo, Separate sync, H/V pol

Negatives

Detailed timing description # 2 Pixel clock (“73.75 MHz”,

According to VESA CVT Rev1.1)

# 2 H sync offset : H sync pulse width : V sync offset : V sync

width (”48 : 32 : 3 : 6”)

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

01 00000001

01 00000001

01 00000001

01 00000001

01 00000001

01 00000001

01 00000001

01 00000001

01 00000001

01 00000001

01 00000001

AB 10101011

22 00100010

A0 10100000

A0 10100000

50 01010000

84 10000100

1A 00011010

30 00110000

30 00110000

20 00100000

36 00110110

00 00000000

2F 00101111

BE 10111110

10 00010000

00 00000000

00 00000000

18 00011000

CF 11001111

1C 00011100

A0 10100000

A0 10100000

50 01010000

84 10000100

16 00010110

30 00110000

30 00110000

20 00100000

36 00110110

00 00000000

2F 00101111

BE 10111110

17 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 18

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

86 56 # 2 H image size : V image size (”303 : 190”)

87 57 # 2 H boarder (”0”)

88 58 # 2 V boarder (”0”) 00 00000000

89 59 Module "A" Revision = Example: 00, 01, 02, 03, etc.

90 5A Detailed timing description # 3

91 5B # 3 Flag

92 5C # 3 Reserved

# 3 FE (hex) defines ASCII string (Model Name “N141C1”,

93 5D

94 5E # 3 Flag

95 5F # Dell P/N "MC196" 1st character (“M”)

96 60 # Dell P/N " MC196" 1st character (“C”)

97 61 # Dell P/N " MC196" 1st character (“1”)

98 62 # Dell P/N " MC196" 1st character (“9”)

99 63 # Dell P/N " MC196" 1st character (“6”)

100 64 LCD Supplier EEDID Revision #: "3"

101 65 Manufacturer P/N ( "N")

102 66 Manufacturer P/N ( "1" )

103 67 Manufacturer P/N ( "4" )

104 68 Manufacturer P/N ( "1" )

105 69 Manufacturer P/N ( "C" )

106 6A Manufacturer P/N ( "1" )

107 6B

108 6C Flag

109 6D Flag

110 6E Flag

111 6F Data Type Tag:

112 70 Flag

113 71 SMBUS value @ 10nits = 36d 24

114 72 SMBUS value @ 17nits = 51d 33

115 73 SMBUS value @ 24nits = 58d 3A

116 74 SMBUS value @ 30nits = 70d 46

117 75 SMBUS value @ 60nits = 98d 62

118 76 SMBUS value @ 110nits = 141d 8D

119 77 SMBUS value @ 150nits = 171d AB

120 78 SMBUS value @ max nits = 232d E8

121 79 Numbers of LVDS Recevier chip = 2

122 7A BIST Enable: Yes = '01' No = '00' ("Yes")

123 7B

124 7C

125 7D

126 7E Extension flag

127 7F Checksum

ASCII)

Manufacturer P/N (If <13 char, then terminate with ASCII code

0Ah, set remaining char = 20h)

(If <13 char, then terminate with ASCII code 0Ah, set remaining

char = 20h)

(If <13 char, then terminate with ASCII code 0Ah, set remaining

char = 20h)

(If <13 char, then terminate with ASCII code 0Ah, set remaining

char = 20h)

10 00010000

00 00000000

00 00000000

00 00000000

00 00000000

00 00000000

FE 11111110

00 00000000

4D 01001101

43 01000011

31 00110001

39 00111001

36 00110110

33 00110011

4E 01001110

31 00110001

34 00110100

31 00110001

43 01000011

31 00110001

0A 00001010

00 00000000

00 00000000

00 00000000

FE 11111110

00 00000000

00100100

00110011

00111010

01000110

01100010

10001101

10101011

11101000

02 00000010

01 00000001

0A 00001010

20 00100000

20 00100000

00 00000000

6B 01101011

18 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 19

Global LCD Panel Exchange Center

6 INVERTER SPECIFICATION

6.1 Connector type

Input connector type: LVC-D20SFYG (HONDA)

Output connector: JST SM02B-BHSS-1-TB (JST)

6.2 Input connector pin assignment

6.2.1 Input Connector pin assignment:

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Input connector

HONDA LVC-D20SFYG

Pin Function

1 INV_SRC

2 INV_SRC

3 INV_SRC

4 INV_SRC

5 GND Ground

6 NC No Connection

7 5VALW

8 GND Ground

9 SMB_DAT

10 SMB_CLK

11 GND Ground

12 INV_PWM System side PWM input signal for brightness control

13 GND Ground

14 NC No Connection

15 ~ 20 NC No Connection

This power rail should be used as a power rail to drive the backlight

DC-AC converter

This power rail should be used as a power rail to drive the backlight

DC-AC converter

This power rail should be used as a power rail to drive the backlight

DC-AC converter

This power rail should be used as a power rail to drive the backlight

DC-AC converter

This should be used as power source that stores the brightness/contrast

values & the circuit that interfaces with SMB_CLK & SMB_DAT

SMBus interface for sending brightness & contrast information to the

inverter/panel

SMBus interface for sending brightness & contrast information to the

inverter/panel

Comments

6.2.2 Absolute maximum ratings

Items Absolute max. ratings Unit

INV_SRC (Voltage) -1.0~23.5 V

FPBACK/SMB_CLK/SMB_DAT

(Voltage)

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

-1.0~5.5 V

19 / 35

Version 3.0

www.panelook.com

Page 20

Global LCD Panel Exchange Center

6.3 Output connector pin assignment

Pin Name Description

1 CFL-High High-voltage output to the CCFL

2 CFL-Low Low-voltage output to the CCFL

6.4 General electrical specification

6.4.1 Absolute maximum ratings

Items Absolute max. ratings Unit

INV_SRC (Voltage) -1.0~23.5 V

FPBACK/SMB_CLK/SMB_DAT

(Voltage)

6.4.2 Electrical characteristics:

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

-1.0~5.5 V

No. Item Symbol

1 Input Voltage INV_SRC 7.5 14.4 21 V

Input Signal Level for

2

Input Signal Level for

3

4 Input Power Pin(Max) 220nits@Vin=12V - - 5.5 W

Brightness Adjust (Lamp

5

6 Output Voltage Vout IL = 6.3mA(typ) 612 680 748 Vrms

7

5VSUS

5VALW

Current Control)

Output Current

5VSUS - - - V

5VALW 4.75 5 5.2 V

SMB_DAT

Iout (Min)

Iout (Max)

Condition

Control by SMBus(256 steps

dimming control)

Vin=7.5V~21V SMB_DAT=00H

Ta =2 5к, after running 30 min.

Vin=7.5V~21V SMB_DAT=FFH

Ta =2 5к, after running 30 min.

Min. Typ. Max. Uint

00H - FFH -

1.5 1.8 2.1 mArms

6 6.3 6.6 mArms

8 Operation Frequency Freq Vin=7.5V~21V 45 - 65 KHz

9 Burst mode frequency fB Vin=7.5V~21V 200 - 220 Hz

10 Open Lamp Voltage Vopen No Load 1400 -- 1800 Vrms

11 Striking Time Ts No Loadw 0.6 1 1.4 Sec

12

13 Start and Delay Time

Efficiency K

Vin=7.5V, SMB_DAT=FFH

(RES LOAD=100K ohm)

Vin=14.4V,

SMB_DAT=00H - 130 200 uS

20 / 35

80 - - %

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 21

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Start –up time

14

(Turn on delay time)

zInput Voltage

The operating input voltage of inverter shall be defined.

The inverter shall ignite the CCFL lamp at minimum input voltage at any environment conditions.

zOn/Off control

Enable: At “ON” condition (FPBACK=Hi), enable the inverter.

Disable: At “OFF” condition (FPBACK=Lo), disable the inverter.

zQuiescent current

At the inverter “OFF” condition, input quiescent should be less than 0.1mA.

zOpen lamp voltage

The inverter start-up output voltage will be above “Vopen” for “Ts” minimum at any condition under specify

until lamp to be ignited. The inverter should be shutdown if lamp ignition was failed in “Ts” maximum. The

inverter shall be capable of withstanding the output connections open without component over-stress / fire /

smoke /arc.

zBurst mode frequency

The burst mode frequency should be in specification in any environment condition and electrical condition.

Vin=14.4V,

SMB_DAT=FFH - - 0.1 Sec

zBrightness control

SM-BUS values for panel luminance are to be included in the on LCD board EEDID ROM chip table. The

supplier will measure panel luminance in a system and define the SMBUS values for each of the 8 required

luminance levels. The panel luminance, for which SMBUS values will be provided in the EEDID from byte #

113(hex #71), to byte # 120, (hex # 78), is show in the table below. The inverter supplier should provide

these appropriate values to CMO.

Step Count Step 1 Step 2 Step3 Step 4 Step 5 Step 6 Step 7 Step 8

Address Byte

SM-Bus Data Value 24 33 3A 46 62 8D AB E8

Luminance (nits) 10 17 24 30 60 110 150 Max

113

Byte

114

Byte

115

Byte

116

Byte

117

Byte

118

Byte

119

Byte

120

z Output ripple ratio

Ripple ratio = 2 * (Ipeak - Ivalley) / (Ipeak + Ivalley) * 100%

The Ripple ratio should be less than 5% and ripple frequency should be less than 200 Hz.

z Power up Overshoot & Undershoot

Overshoot & Undershoot at power up should not exceed the following limits.

Vin

0ШVin(min.)

0ШVin(typ.)

Output current

Io(rms)

Io(max.)

Io(min.)

Io(max.)

Io(min.)

Overshoot/Undershoot

Io (dI)

150% / 50% 5 ms max.

150% / 50% 5 ms max.

Settling time

(dT)

21 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 22

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

0ШVin(max.)

dI=Imax.-Io or dI=(Io-Imin.)/Io

z Output connections short protection

The inverter shall be capable of withstanding the output connections short without damage or over-stress.

And the inverter maximum input power shall be limited within 1W.

Io(max.)

Io(min.)

150% / 50% 5 ms max.

6.4.3 Mechanical Drawing

6.4.4 Other Information

z Safety

x The inverter shall meet the requirement of “Limited current circuits” in paragraphs 2.4.1 in IEC60950.

There is no fire/smoke while simulating the component of the inverter open/short test.

x The Inverter AND panel must be UL certified with CB certificate and LCC (Limited Current Circuit) test

and test reports from UL. Inverter panel combo must pass Dell Safety requirements.

z EMI

The inverter must meet the radiated limitation requirement of CISPR22 class B, FCC-B and VCCI level II

with 6dB margin minimum while the inverter operating in the complete system.

z Environment Regulation

x Follow the RoHS requirement.

x Fill in CMO’s official document <<Environmentally Conscious Products Questionnaire for Suppliers of

Materials, Parts, and Products>> and turn in to CMO before CMO’s specification approval process.

z Dell’s other requirements

1. The inverter must not emit any audible noise.

2. Please refer to CMO’s official document. “General Inverter Specification for LCD Module” for other

general information such as reliability test, safety and etc..

3. Please also refer to DELL’s official document about inverter:

z LCD Backlight Design Spec X00-04

z DELL’s LCD Inverter Qualification Plan, Rev. A00

z Prohibited Components

“Holy Stone(كعഘ)”’s products are prohibited.

z

Confidential Notice

Remind that all the information described in this document is confidential. Please don’t reveal to other people

else before getting CMO’s agreement.ibed in this document is confidential. Please don’t reveal to other people

else before getting CMO’s agreement.

22 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 23

Global LCD Panel Exchange Center

7 INTERFACE TIMING

7.1 INPUT SIGNAL TIMING SPECIFICATIONS

The specifications of input signal timing are as the following table and timing diagram.

Signal Item Symbol Min. Typ. Max. Unit Note

DCLK Frequency 1/Tc 25 44.5 60 MHz -

Vertical Total Time TV 910 926 1500 TH -

DE

Vertical Addressing Time TVD 900 900 900 TH -

Horizontal Total Time TH 760 800 880 Tc -

Horizontal Addressing Time THD 720 720 720 Tc -

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

DE

DCLK

TC

DE

DATA

7.2 POWER ON/OFF SEQUENCE

INPUT SIGNAL TIMING DIAGRAM

Power On

90%

Power Off

90%

HD

T

Restart

t7

Power Supply

for LCD, Vcc

- Interface Signal

(LVDS Signal of

Transmitter), V

I

- Power for Lamp

0V

0V

10%

t1

Valid Data

t6 t5

50%50%

ONOFF OFF

10%

t4

t3 t2

10%

23 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 24

Global LCD Panel Exchange Center

Timing Specifications:

0.5< t1 Љ 10 msec

0 < t2 Љ 50 msec

0 < t3 Љ 50 msec

t4 Њ 500 msec

t5 Њ 200 msec

t6 Њ 200 msec

Note (1) Please avoid floating state of interface signal at invalid period.

Note (2) When the interface signal is invalid, be sure to pull down the power supply of LCD Vcc to 0 V.

Note (3) The Backlight inverter power must be turned on after the power supply for the logic and the

interface signal is valid. The Backlight inverter power must be turned off before the power supply

for the logic and the interface signal is invalid.

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Note (4) Sometimes some slight noise shows when LCD is turned off (even backlight is already off). To

avoid this phenomenon, we suggest that the Vcc falling time had better to follow

t7 Њ 5 msec

24 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 25

Global LCD Panel Exchange Center

8 OPTICAL CHARACTERISTICS

8.1 TEST CONDITIONS

Item Symbol Value Unit

Ambient Temperature Ta

Ambient Humidity Ha

Supply Voltage VCC 3.3 V

Input Signal According to typical value in "3. ELECTRICAL CHARACTERISTICS"

Inverter Current IL 6 mA

Inverter Driving Frequency FL 61 KHz

Inverter Sumida H05-4915

The relative measurement methods of optical characteristics are shown in 8.2. The following items

should be measured under the test conditions described in 8.1 and stable environment shown in Note (6).

8.2 OPTICAL SPECIFICATIONS

Item Symbol Condition Min. Typ. Max. Unit Note

Contrast Ratio CR 400 600 - - (2), (5)

Response Time

Average Luminance of White L5p 185 230 - cd/m2(4), (5)

Luminance Non-Uniformity

Color Gamut C.G 42 45 - % (5), (7)

Red

Color

Chromaticity

Viewing Angle

Green

Blue

White

Horizontal

Vertica l

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

o

25r2

50r10

TR - 5 10 ms

- 11 16 ms

T

F

GW5p

GW

13p

=0q, TY =0q

T

x

Rx

Ry

Gx

Gy

Bx

By

Wx 0.313 -

Wy

Tx+

T

-

x

TY+

T

-

Y

Viewing Normal

Angle

CRt10

- - 20 %

- - 35 %

0.590

0.340

0.319

TYP

-0.02

0.541

0.152

0.125

0.329

40 45 40 45 15 20 40 45 -

TYP

+0.02

C

%RH

(3)

(5), (6)

-

-

-

-

-

(1), (5)

-

Deg.

25 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 26

Global LCD Panel Exchange Center

.67 ms

Note (1) Definition of Viewing Angle (Tx, Ty):

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

TX- = 90º

x-

6 o’clock

T

y- = 90º

y-

Note (2) Definition of Contrast Ratio (CR):

The contrast ratio can be calculated by the following expression.

Contrast Ratio (CR) = L

L

: Luminance of gray level 63

63

L

: Luminance of gray level 0

0

63

/ L0

Normal

Tx = Ty = 0º

Ty- Ty

Tx

Tx

y+

12 o’clock direction

T

y+ = 90º

x+

TX+ = 90º

CR = CR (5)

CR (X) is corresponding to the Contrast Ratio of the point X at Figure in Note (6).

Note (3) Definition of Response Time (T

100%

90%

Optical

Response

10%

0%

R

T

R

66.67 ms

, TF):

66

Time

T

F

26 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 27

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Note (4) Definition of Average Luminance of White (L

Measure the luminance of gray level 63 at 5 points

L5p = [L (5)+ L (10)+ L (11)+ L (12)+ L (13)] / 5

L (x) is corresponding to the luminance of the point X at Figure in Note (6)

Note (5) Measurement Setup:

The LCD module should be stabilized at given temperature for 20 minutes to avoid abrupt

temperature change during measuring. In order to stabilize the luminance, the measurement

should be executed after lighting Backlight for 20 minutes in a windless room.

LCD Module

LCD Panel

Center of the Screen

Field of View = 2º

):

5p

Photometer

(CA210, CS-1000T)

500 mm

Light Shield Room

(Ambient Luminance < 2 lux)

27 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 28

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Note (6) Definition of White Variation (GW5p, GW

Measure the luminance of gray level 63 at 5, 13 points

GW

={1-{ Minimum [L (5)+ L (10)+ L (11)+ L (12)+ L (13)] / Maximum [L (5)+ L (10)+ L (11)+ L (12)+

5p

L (13)]}} *100%

GW

={1-{ Minimum [L (1) ~ L (13)] / Maximum [L (1) ~ L (13)]}} *100%

13p

13p

):

X

: Test Point

X=1 to 5

Note (7) Definition of color gamut (C.G):

C.G= 'R G B /'R

R

, G0, B0 : color coordinates of red, green, and blue defined by NTSC, respectively.

0

R, G, B

'R

0 G0 B0

0 G0 B0

: color coordinates of module on 63 gray levels of red, green, and blue, respectively.

: area of triangle defined by R0, G0, B0

,*100%

'R G B: area of triangle defined by R, G, B

˖˜˘ ʳ˄ˌ ˆ˄

˃ˁˌ

˃ˁˋ

˃ˁˊ

˃ˁˉ

˃ˁˈ

˃ˁˇ

˃ˁˆ

˃ˁ˅

˃ˁ˄

˃

˃ ˃ˁ˅ ˃ˁˇ ˃ˁˉ ˃ˁˋ

G

0

G

B

B

0

R

0

R

28 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 29

Global LCD Panel Exchange Center

9 PRECAUTIONS

9.1 ASSEMBLY AND HANDLING PRECAUTIONS

(1) The module should be assembled into the system firmly by using every mounting hole. Be

careful not to twist or bend the module.

(2) While assembling or installing modules, it can only be in the clean area. The dust and oil may cause

electrical short or damage the polarizer.

(3) Use fingerstalls or soft gloves in order to keep display clean during the incoming inspection and

assembly process.

(4) Do not press or scratch the surface harder than a HB pencil lead on the panel because the polarizer is

very soft and easily scratched.

(5) If the surface of the polarizer is dirty, please clean it by some absorbent cotton or soft cloth. Do not use

Ketone type materials (ex. Acetone), Ethyl alcohol, Toluene, Ethyl acid or Methyl chloride. It might

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

permanently damage the polarizer due to chemical reaction.

(6) Wipe off water droplets or oil immediately. Staining and discoloration may occur if they left on panel for

a long time.

(7) If the liquid crystal material leaks from the panel, it should be kept away from the eyes or mouth. In

case of contacting with hands, legs or clothes, it must be washed away thoroughly with soap.

(8) Protect the module from static electricity, it may cause damage to the C-MOS Gate Array IC.

(9) Do not disassemble the module.

(10) Do not pull or fold the lamp wire.

(11) Pins of I/F connector should not be touched directly with bare hands.

9.2 SAFETY PRECAUTIONS

(1) High temperature or humidity may reduce the performance of module. Please store LCD module within

the specified storage conditions.

(2) It is dangerous that moisture come into or contacted the LCD module, because the moisture may

damage LCD module when it is operating.

(3) It may reduce the display quality if the ambient temperature is lower than 10 ºC. For example, the

response time will become slowly, and the starting voltage of lamp will be higher than the room

temperature.

9.3 OPERATION PRECAUTIONS

(1) Do not pull the I/F connector in or out while the module is operating.

(2) Always follow the correct power on/off sequence when LCD module is connecting and operating. This

can prevent the CMOS LSI chips from damage during latch-up.

(3) The startup voltage of Backlight is approximately 1000 Volts. It may cause electrical shock while

assembling with inverter. Do not disassemble the module or insert anything into the Backlight unit.

29 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 30

Global LCD Panel Exchange Center

10 PACKAGING

10.1 CARTON

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Figure. 10-1 Packing method

30 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 31

Global LCD Panel Exchange Center

10.2 PALLET

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

Figure. 10-2 Packing method

31 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 32

Global LCD Panel Exchange Center

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

11 DEFINITION OF LABELS

11.1 CMO MODULE LABEL

The barcode nameplate is pasted on each module as illustration, and its definitions are as following explanation.

-

(a) Model Name: N141C1 - L01

(b) Revision: Rev. XX, for example: A1, …, C1, C2 …etc.

(c) Serial ID: X X

(d) Production Location: MADE IN XXXX. XXXX stands for production location.

Serial ID includes the information as below:

(a) Manufactured Date: Year: 1~9, for 2001~2009

(b) Revision Code: cover all the change

X X X X X Y M D X N N N N

Month: 1~9, A~C, for Jan. ~ Dec.

Day: 1~9, A~Y, for 1

Serial No.

CMO Internal Use

Year, Month, Date

CMO Internal Use

Revision

CMO Internal Use

st

to 31st, exclude I , O and U

(c) Serial No.: Manufacturing sequence of product

11.2 CMO CARTON LABEL

(a) Production location: Made In XXXX. XXXX stands for production location.

32 / 35

Version 3.0

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

www.panelook.com

Page 33

Global LCD Panel Exchange Center

11.3 CARTON LABEL

PKG ID (3S)124161241729112345609886C20

www.panelook.com

Issued Date: Jan 17, 2006

Model No.: N141C1 - L01

Approval

REV.A06

DP/N 03J849

BOX Qty 20 Made in Taiwan

11.4 PALLET LABEL

FROM :CMO Corporation

Tainan,

Taiwan 744 R.O.C

P.O.NUMBER

12345678

COUNTRY OF ORIGIN

TW

TO:DELL COMPUTER

2128 West Braker

Austin TX

DELL P/N

12345

PACKING LIST#

1234567890123

Vendor ID Loc Id

12416 12416

Mfg Id

70896

PACKING LIST QTY

654321

DESTINATION MAS LOC

DESTINATION LOCATION

B4

12345678901234567890

PKG CNT

999 OF 999 12345

PART DESCRIPTION XXXXXXXXXXXXXXXXXXXXXXXXX

12345678901234567890123456789012345678901

BOX CNT REVISION

A00-00 Apr 29,2003

60

AIRBILL NUMBER

SHIP DATE

33 / 35

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

Version 3.0

www.panelook.com

Page 34

Global LCD Panel Exchange Center

www.panelook.com

One step solution for LCD / PDP / OLED panel application: Datasheet, inventory and accessory!

www.panelook.com

Loading...

Loading...