Page 1

Schematic Diagrams

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

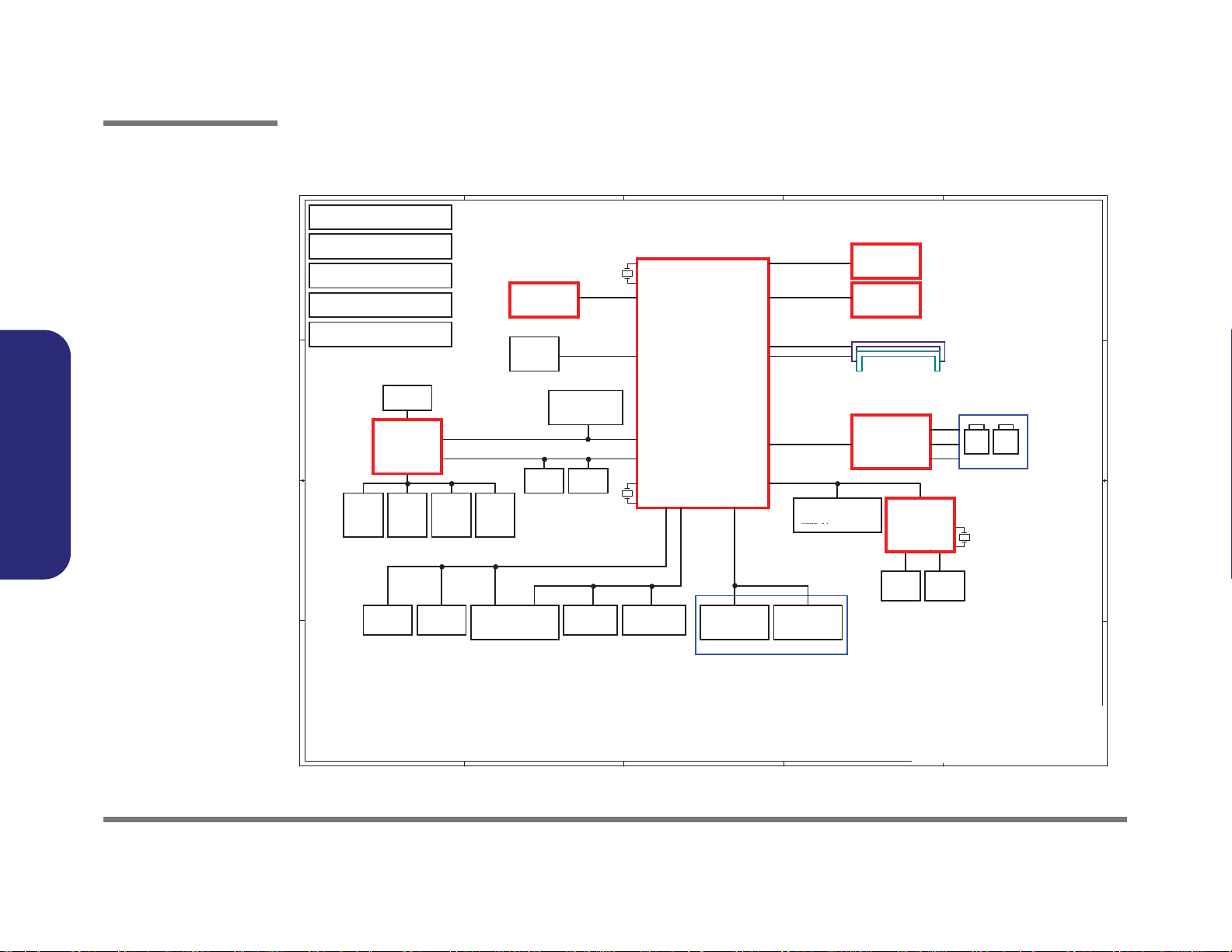

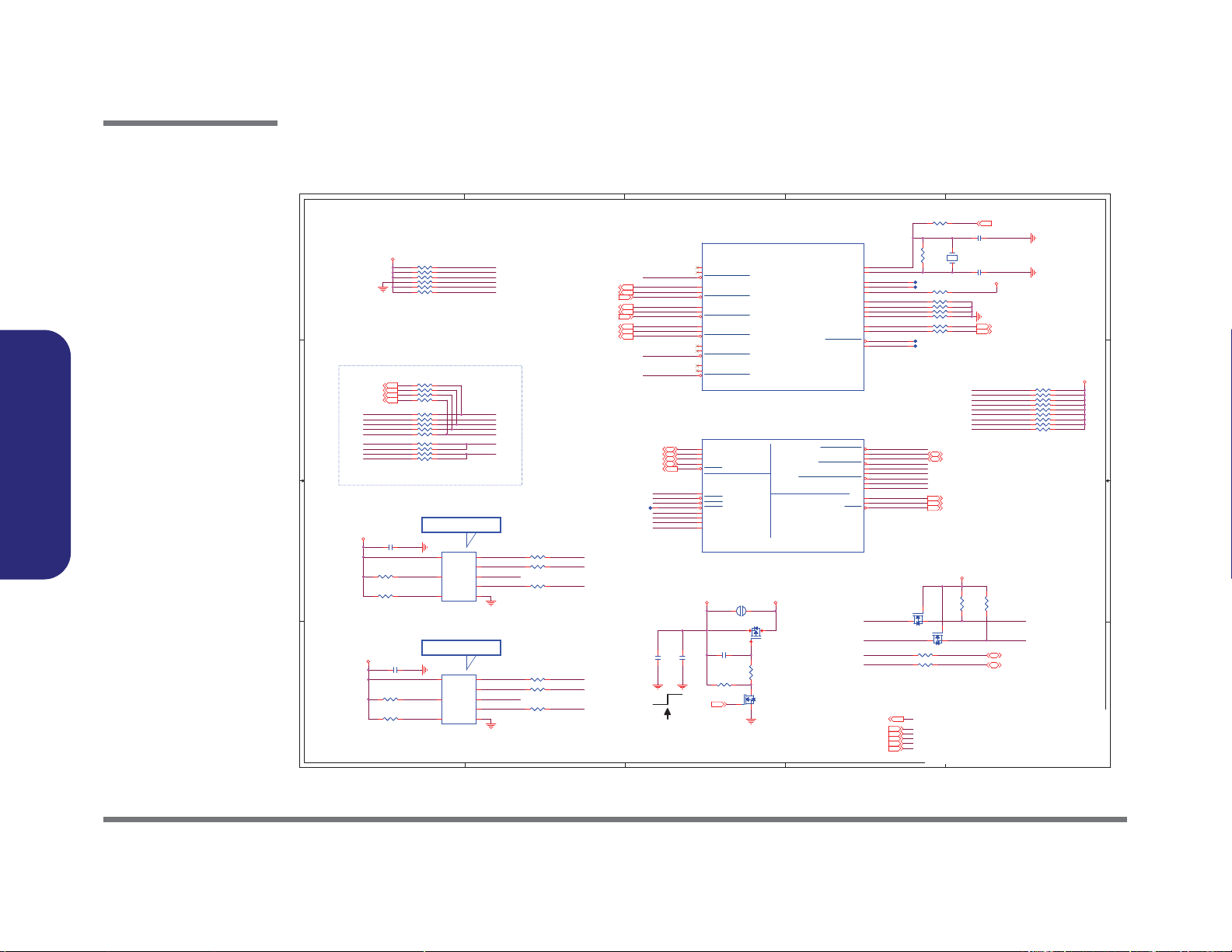

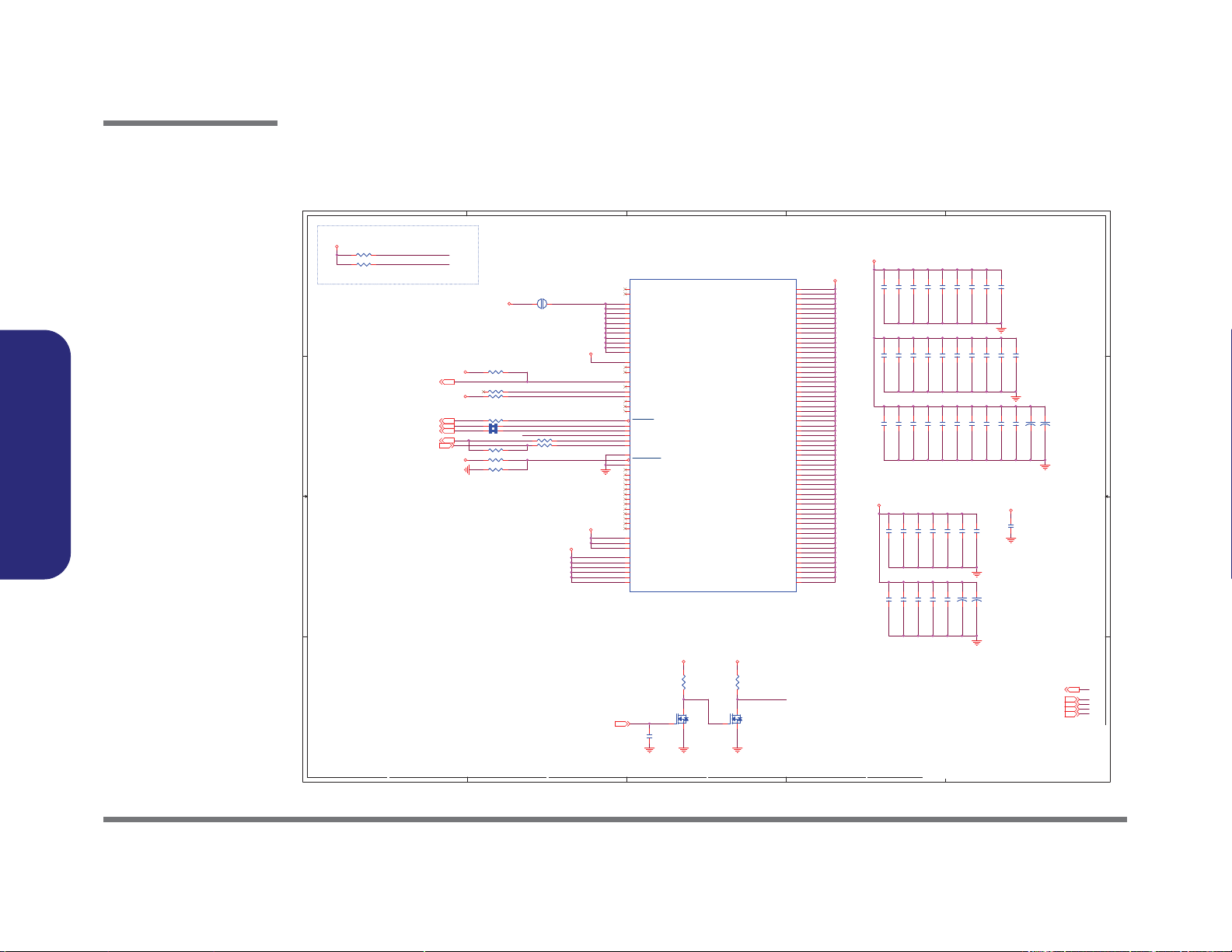

System Block Diagram

VDD3,VDD5

5V,3V,5VS,3VS

1.05VS SERIES

VCORE

DDR 1.35V,1.5VS

Sheet 1 of 39

System Block

Diagram

TIME

KEEPER

B.Schematic Diagrams

INT. K/B

SHEET 24

ITE 8587

128pins LQFP

14*14*1.6mm

THERMAL

SENSOR

SHEET 2

SATA HDD

SHEET 26

SHEET 28

SHEET 27

SHEET 30

SHEET 31

SHEET 29

EC

SHEET 24

EC SMBUS

SMART

FAN

SHEET 20

SATA ODD

SHEET 26

PS8625

EDP TO LVDS

G-SENSER

Optional

SHEET 23

0.5"~11"

LPC

SPI

SMART

BATTERY

AC-IN

SHEET 32

SATA III 6.0Gb/s

Mini PCIE SOCKET

M-SATA

3G

(USB2_2)

SHEET 21

System Block Diagram (Shark Bay ULT)

<7" (3 VIA)

SHEET 17

SYSTEM SMBUS

TPM 1.2 & 2.0

Optional

SHEET 23

24 MHz

BIOS

SHEET 5

<7" (3 VIA)

USB2.0

ME

SHEET 5

480 Mbps

CCD + Mic

SHEET 25

32.768KHz

24 MHz

Haswell

PROCESSOR

rPGA946B

37.5x37.5mm

Power: 1.05V.1.5V,

3.3V,VCORE(VR12.5)

SHEET 02,03,04,05,06,

07,08,09,10,11,12

<7"

TOUCH PANEL

SHEET 39

USB3.0

USB2.0 PORT0

(USB3.0 PORT1) (USB3.0 PORT2)

SHEET 23

<10" (4 VIA)

1067/1333/1600 MHz

DDR3 /1.35

SYSTEM SMBUS

0.1"~13

AZALIA LINK

PCIE

<7" (MS), 9"(SL)

5 Gbps

USB2.0 PORT1

USB3.0

SHEET 23

HDMI

PS8613

DP TO VGA

DDR3 DDR3

SO-DIMM_A_0

ALC269Q-VB7

24 MHz

100 MHz

Mini PCIE SOCKET

WLAN

SHEET 24

<8" (3 VIA)

(USB2_4)

SHEET 20

SHEET 16

DDR3L

Power: 1.35V

SHEET 13

Azalia Codec

SHEET 26

REALTEK

RTL8411B

LAN

CARD READER

SHEET 19

RJ-45

SHEET 20 SHEET 19

SO-DIMM_B_0

SHEET 14

AUDIO BOARD

MIC

IN

25 MHz

7IN1

SOCKET

HP

OUT

SHEET 33,34

B - 2 System Block Diagram

www.schematic-x.blogspot.com

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Title

Title

[01] BLOCK DIAGRAM

[01] BLOCK DIAGRAM

[01] BLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

6-71-W5S20-D03

6-71-W5S20-D03

Date: Sheet

Date: Sheet

Date: Sheet

6-71-W5S20-D03

of

139Monday, October 14, 2013

of

139Monday, October 14, 2013

of

139Monday, October 14, 2013

1.0

1.0

1.0

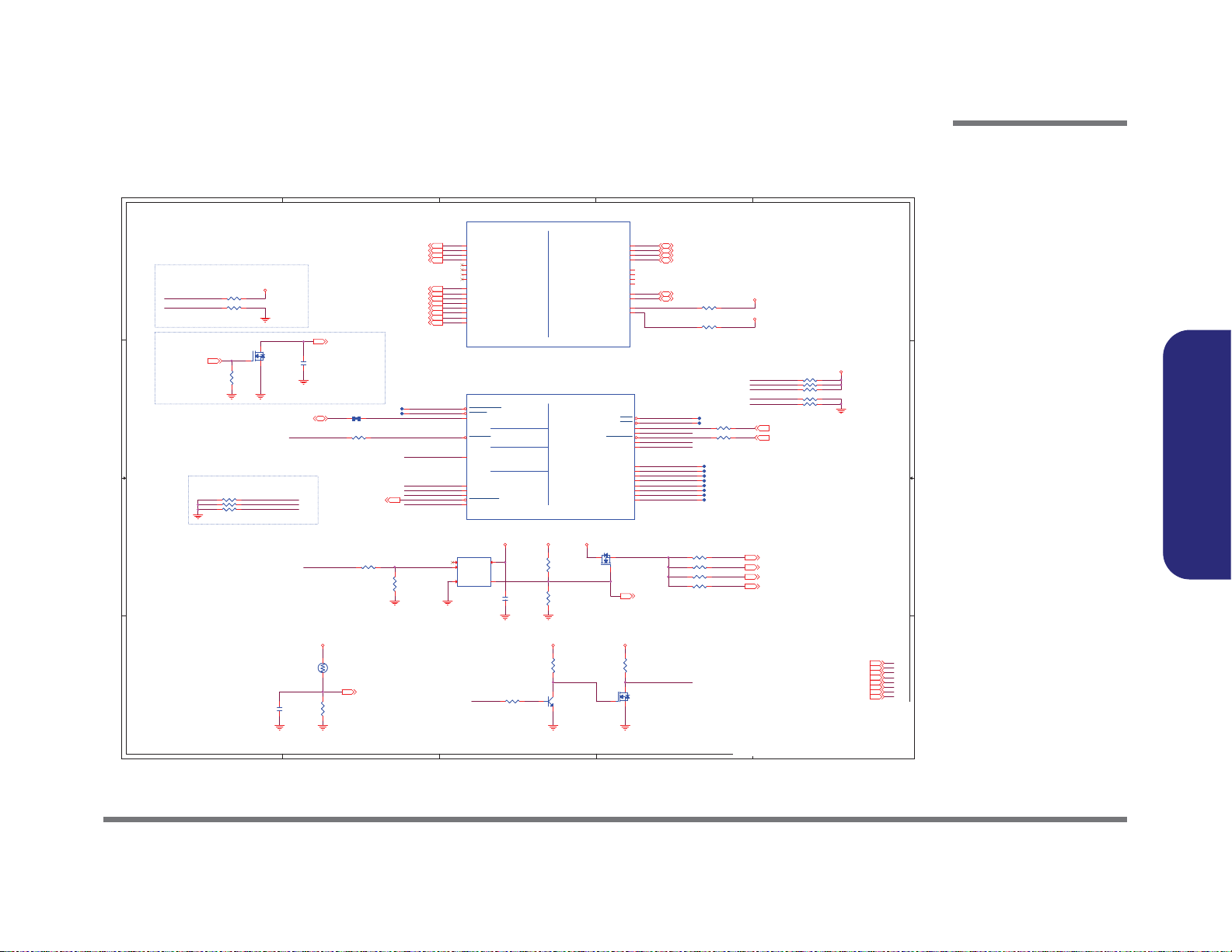

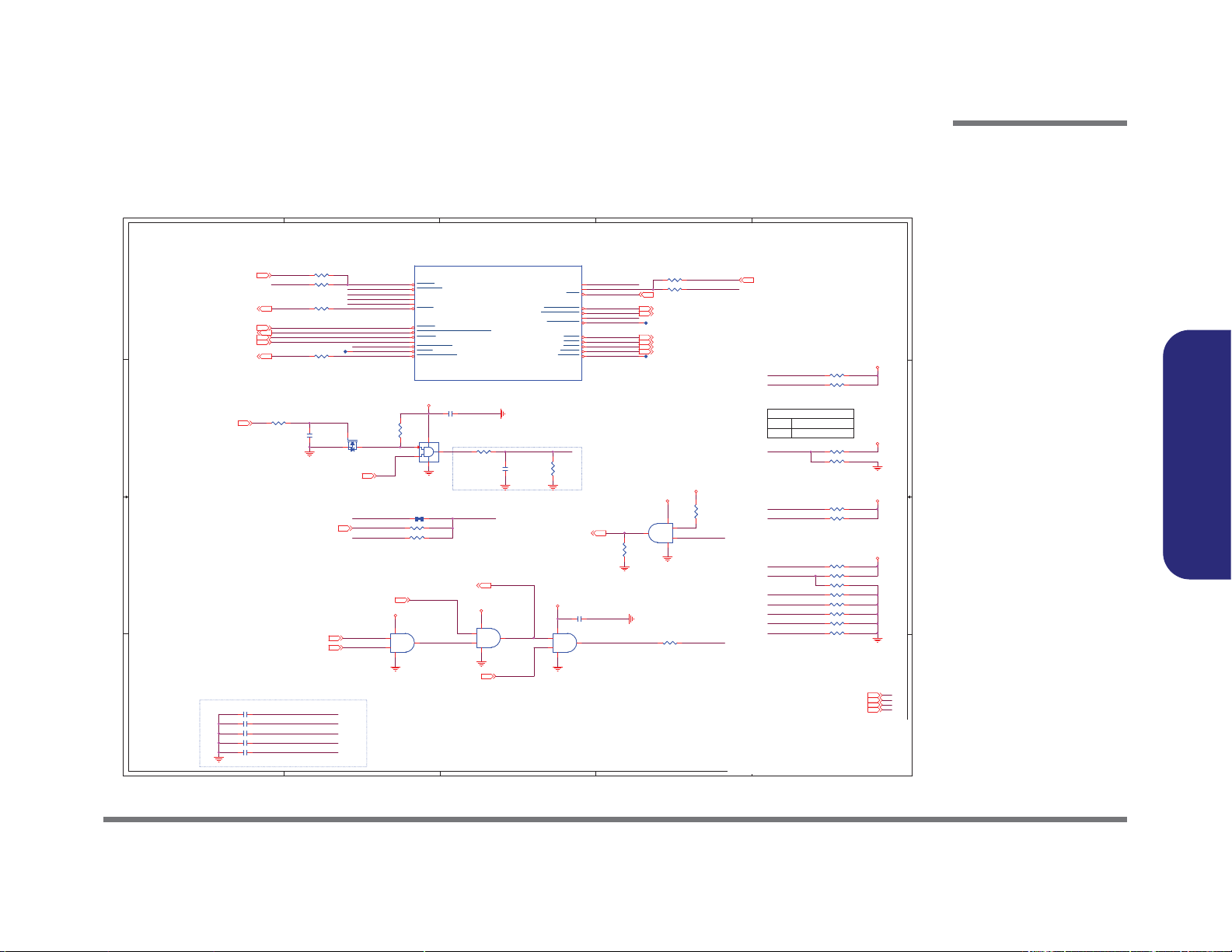

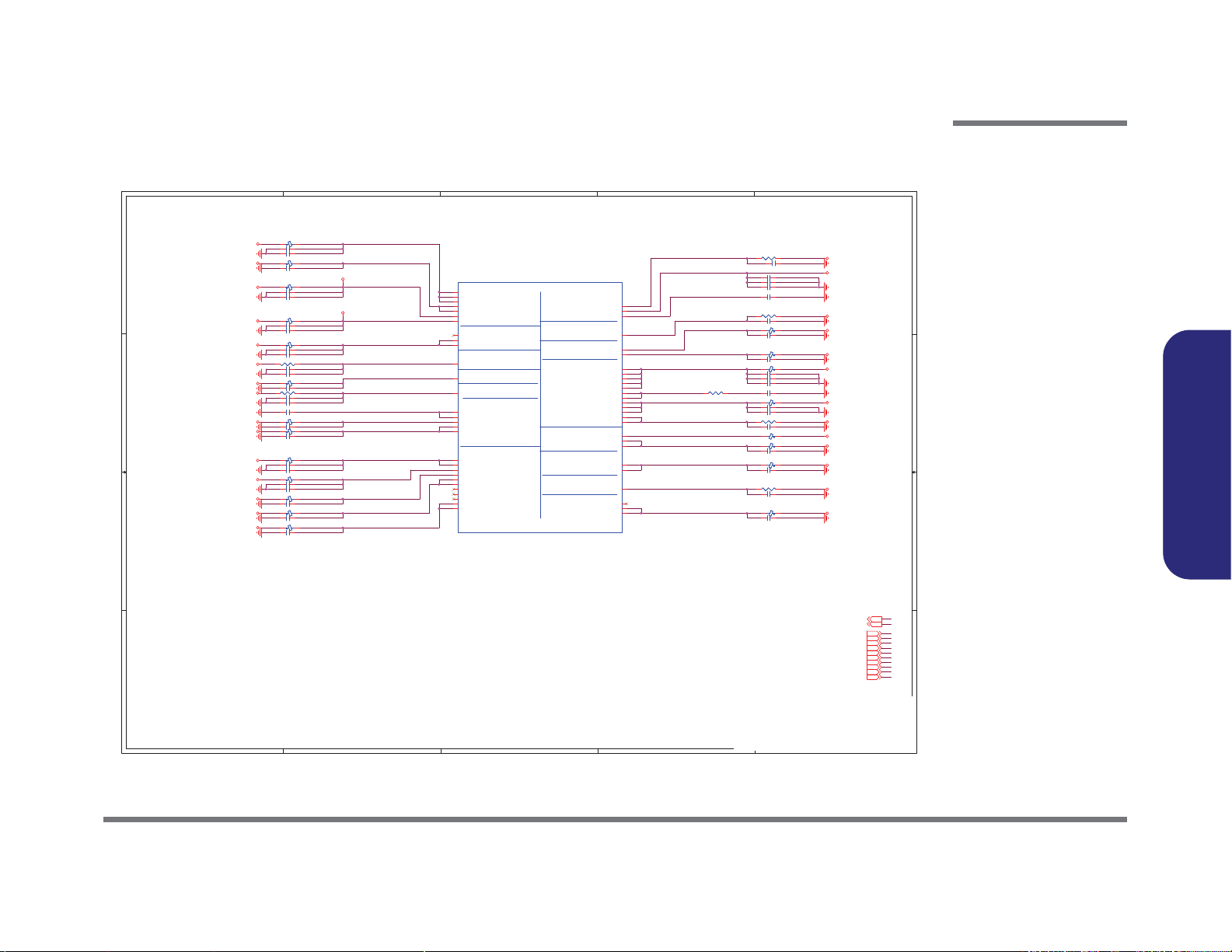

Page 2

Processor 1/7

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

HSW_ULT_DDR3L

5

4

HSW_ULT_DDR3L

HSW_ULT_DDR3L

MISC

MISC

THERMAL

THERMAL

PWR

PWR

DDR3L

DDR3L

C332

C332

0.1u_16V_Y5V_04

0.1u_16V_Y5V_04

HSW_ULT_DDR3L

1 OF 19

1 OF 19

EDPDDI

EDPDDI

JTAG

JTAG

2 OF 19

2 OF 19

V_VCCDDQVDD5V_VCCDDQ

R464

R464

220K_1%_04

220K_1%_04

DDR_VTT_PG_CTRL

R465

R465

*2M_04

*2M_04

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

PROC_TCK

PROC_TMS

PROC_TRST

PROC_TDI

PROC_TDO

Q11

Q11

BSS138

BSS138

D S

G

SINGLE=50ohm, DIFF=85ohm, L <=10"

C45

EDP_TXN_0 17

B46

EDP_TXP_0 17

A47

EDP_TXN_1 17

B47

EDP_TXP_1 17

C47

C46

A49

B49

A45

EDP_AUXN 17

B45

EDP_AUXP 17

D20

EDP_RCOMP

A43

L <=100MILS, W=20MILS, SPACE=25MILS

EDP_UTIL

J62

XDP_PRDY#

PRDY

K62

XDP_PREQ#

PREQ

E60

XDP_TCLK

E61

XDP_TMS

E59

XDP_TRST#

F63

XDP_TDI_R

F62

XDP_TDO_R

J60

XDP_BPM0

BPM#0

H60

XDP_BPM1

BPM#1

H61

XDP_BPM2

BPM#2

H62

XDP_BPM3

BPM#3

K59

XDP_BPM4

BPM#4

H63

XDP_BPM5

BPM#5

K60

XDP_BPM6

BPM#6

J61

XDP_BPM7

BPM#7

M_A_B_DIMM_ODT

DDR_VTT_PG_CTRL 29

R150 66.5_1%_04R150 66.5_1%_04

R151 66.5_1%_04R151 66.5_1%_04

R133 66.5_1%_04R133 66.5_1%_04

R131 66.5_1%_04R131 66.5_1%_04

R79 24.9_1%_04R79 24.9_1%_04R332 10K_04R332 10K_04

R331 *10K_04R331 *10K_04

R422 *0_04R422 *0_04

R430 0_04R430 0_04

VCCIOA_OUT

3.3VS

PU/PD for JTAG signals

XDP_TMS

XDP_TDI_R

XDP_TDO_R

XDP_TCLK

XDP_TRST#

PCH_JTAG_TCK 4

XDP_TRST_CPU_N 4

M_A_DIM0_ODT0 13

M_A_DIM0_ODT1 13

M_B_DIM0_ODT0 14

M_B_DIM0_ODT1 14

U20A

U20A

PROC DETECT#

H_CATERR#

H_PEC I_ISO

H_CPUPWRGD_R

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

CPUDRAMRST#

DDR_PG_CTRL

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

U23

U23

1

NC

2

A

3

GND

74AUP1G07GW

74AUP1G07GW

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

U20B

U20B

PROC_DETECT

CATERR

PECI

PROCHOT

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST

SM_PG_CNTL1

VCC

Y

VGA_LANE0N16

VGA_LANE0P16

VGA_LANE1N16

Processor Pullups/Pull downs

H_PROCHOT#

H_CPUPWRGD_R

TRACE WIDTH 10MIL, LENGTH <500MILS

H_PROCHOT_EC24

R348 62_04R348 62_04

G

R345

R345

100K_04

100K_04

1.05VS

H_PROCHOT#

DS

Q6

MTN7002ZHS3Q6MTN7002ZHS3

CAD Note: Capacitor need to be placed

close to buffer output pin

H_PROCHOT# 31

C315

C315

47p_50V_NPO_04

47p_50V_NPO_04

R387 *10mil_04R387 *10mil_04

H_PECI24

H_PROCHOT# H_PROCHOT#_D

R353 56_1%_04R353 56_1%_04

VGA_LANE1P16

HDMI2_C0CN20

HDMI2_C0CP20

HDMI2_C1CN20

HDMI2_C1CP20

HDMI2_C2CN20

HDMI2_C2CP20

HDMI2_CLKCN20

HDMI2_CLKCP20

DDR3 Compensation Signals

R102 200_1%_04R102 200_1%_04

R122 75_1%_04R122 75_1%_04

R121 100_1%_04R121 100_1%_04

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

CLOSE TO CHIP 500mil

CPUDRAMRST#13

R448 0_04R448 0_04

DDR_PG_CTRL_RDDR_PG_CTRL

R446

R446

*0_04

*0_04

1.05VS_VCCST

R344 *51_04R344 *51_04

R346 *51_04R346 *51_04

R347 *51_04R347 *51_04

R423 51_04R423 51_04

R426 *51_04R426 *51_04

Schematic Diagrams

B.Schematic Diagrams

Sheet 2 of 39

Processor 1/7

3.3V

10K_1%

12

PTH1

PTH1

TH05-3H103FR

TH05-3H103FR

1:2 (4mils:8mils)

C83

C83

0.1u_10V_X7R_04

0.1u_10V_X7R_04

R99

R99

10K_1%_04

10K_1%_04

THERM_VOLT 24

DDR_PG_CTRL

R457

R457

*100K_04

*100K_04

3.3VA 3.3VA

R458

R458

*100K_04

*100K_04

Q13

Q13

B

*2N3904

*2N3904

E C

R463

R463

*100K_04

*100K_04

DDR_VTT_PG_CTRL

DS

Q14

Q14

G

*MTN7002ZHS3

*MTN7002ZHS3

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Title

Title

[02] HASWELL ULT (DISPLAY,MISC)

[02] HASWELL ULT (DISPLAY,MISC)

[02] HASWELL ULT (DISPLAY,MISC)

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

Date: Sheet

Date: Sheet of

Date: Sheet of

1.05VS4,5,7,9,10,30,31

V_VCCDDQ9,13,14,16,29

VCCIOA_OUT9

VDD34,5,6,7,10,19,21,24,25,27,28,29,30,32

3.3V9,15,19,21,23,25,27,29,30

3.3VA4,5,6,7,8,10,27

3.3VS4,5,6,7,8,10,13,14,15,16,17,19,20,21,22,23,24,25,26,27,29,30,31

VDD523,27,28,30

6-71-W5S20-D03

6-71-W5S20-D03

6-71-W5S20-D03

1.0

1.0

1.0

of

239Thursday, October 17, 2013

239Thursday, October 17, 2013

239Thursday, October 17, 2013

Processor 1/7 B - 3

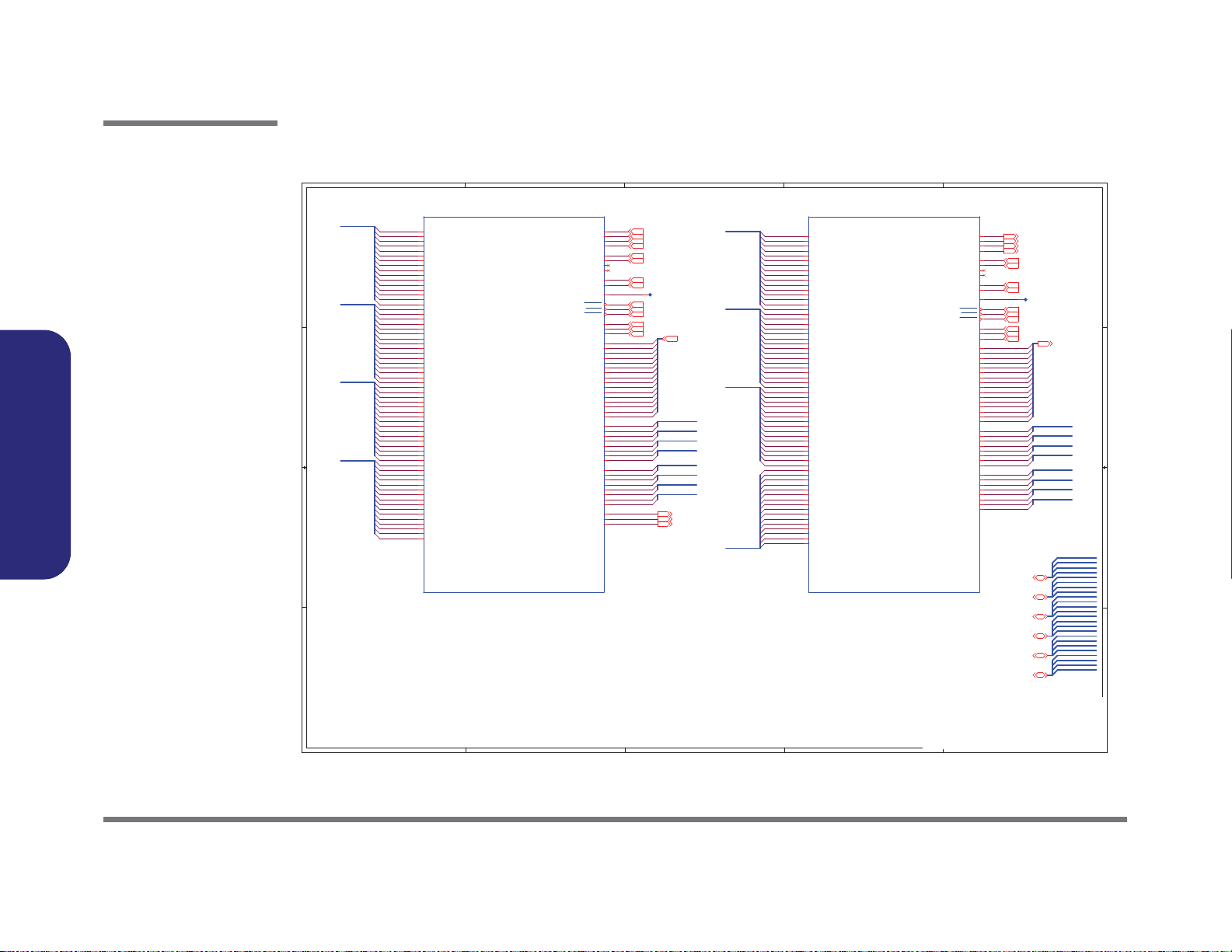

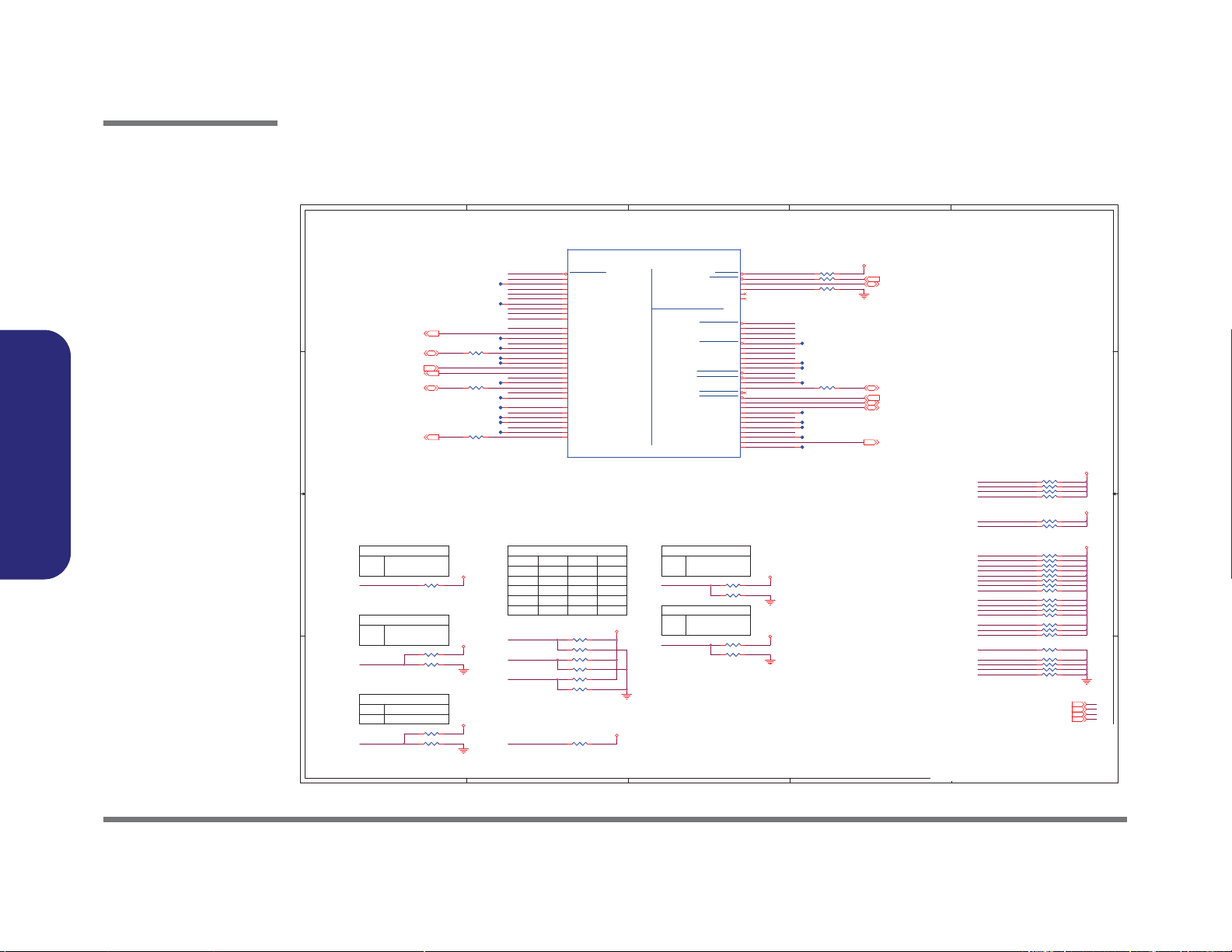

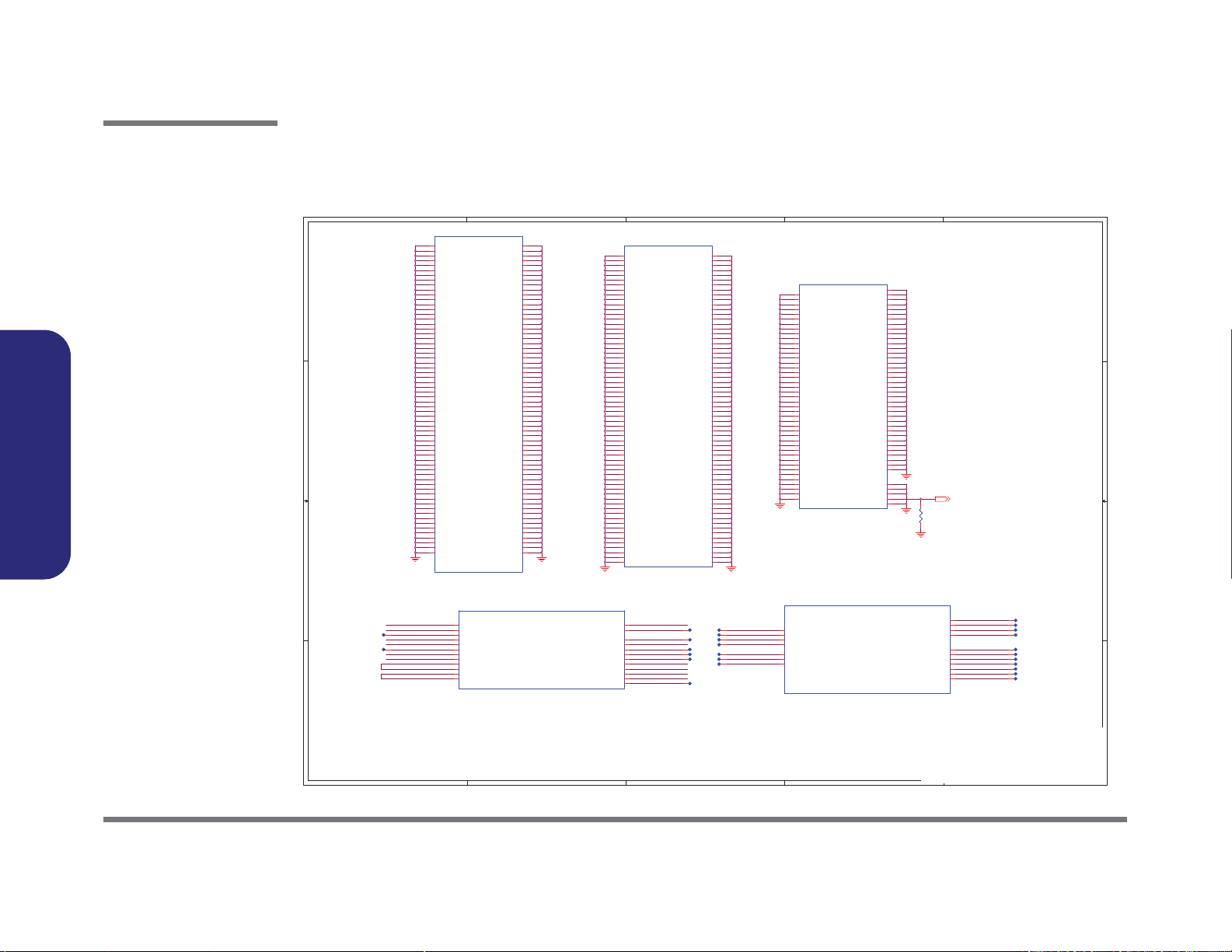

Page 3

Schematic Diagrams

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Processor 2/7

CHANNEL A CHANNEL B

HSW_ULT_DDR3L

U20C

M_A_DQ[15:0]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_B_DQ[15:0]

M_A_DQ15

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

Sheet 3 of 39

Processor 2/7

M_A_DQ[31:16]

M_B_DQ[31:16]

M_B_DQ14

M_B_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

U20C

AH63

SA_DQ0

AH62

SA_DQ1

AK63

SA_DQ2

AK62

SA_DQ3

AH61

SA_DQ4

AH60

SA_DQ5

AK61

SA_DQ6

AK60

SA_DQ7

AM63

SA_DQ8

AM62

SA_DQ9

AP63

SA_DQ10

AP62

SA_DQ11

AM61

SA_DQ12

AM60

SA_DQ13

AP61

SA_DQ14

AP60

SA_DQ15

AP58

SA_DQ16

AR58

SA_DQ17

AM57

SA_DQ18

AK57

SA_DQ19

AL58

SA_DQ20

AK58

SA_DQ21

AR57

SA_DQ22

AN57

SA_DQ23

AP55

SA_DQ24

AR55

SA_DQ25

AM54

SA_DQ26

AK54

SA_DQ27

AL55

SA_DQ28

AK55

SA_DQ29

AR54

SA_DQ30

AN54

SA_DQ31

AY58

SA_DQ32

AW58

SA_DQ33

AY56

SA_DQ34

AW56

SA_DQ35

AV58

SA_DQ36

AU58

SA_DQ37

AV56

SA_DQ38

AU56

SA_DQ39

AY54

SA_DQ40

AW54

SA_DQ41

AY52

SA_DQ42

AW52

SA_DQ43

AV54

SA_DQ44

AU54

SA_DQ45

AV52

SA_DQ46

AU52

SA_DQ47

AK40

SA_DQ48

AK42

SA_DQ49

AM43

SA_DQ50

AM45

SA_DQ51

AK45

SA_DQ52

AK43

SA_DQ53

AM40

SA_DQ54

AM42

SA_DQ55

AM46

SA_DQ56

AK46

SA_DQ57

AM49

SA_DQ58

AK49

SA_DQ59

AM48

SA_DQ60

AK48

SA_DQ61

AM51

SA_DQ62

AK51

SA_DQ63

B.Schematic Diagrams

HSW_ULT_DDR3L

DDR CHANNEL A

DDR CHANNEL A

3 OF 19

3 OF 19

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS

SA_WE

SA_CAS

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

AU37

M_A_CLK_DDR#0 13

AV37

M_A_CLK_DDR0 13

AW36

M_A_CLK_DDR#1 13

AY36

M_A_CLK_DDR1 13

AU43

M_A_CKE0 13

AW43

M_A_CKE1 13

AY42

AY43

AP33

M_A_CS#0 13

AR32

M_A_CS#1 13

AP32

SA_ODT0

AY34

M_A_RAS# 13

AW34

M_A_WE# 13

AU34

M_A_CAS# 13

AU35

M_A_BS0 13

AV35

M_A_BS1 13

AY41

M_A_BS2 13

AU36

M_A_A0

AY37

M_A_A1

AR38

M_A_A2

AP36

M_A_A3

AU39

M_A_A4

AR36

M_A_A5

AV40

M_A_A6

AW39

M_A_A7

AY39

M_A_A8

AU40

M_A_A9

AP35

M_A_A10

AW41

M_A_A11

AU41

M_A_A12

AR35

M_A_A13

AV42

M_A_A14

AU42

M_A_A15

AJ61

M_A_DQS#0

AN62

M_A_DQS#1

AM58

M_B_DQS#0

AM55

M_B_DQS#1

AV57

M_A_DQS#2

AV53

M_A_DQS#3

AL43

M_B_DQS#2

AL48

M_B_DQS#3

AJ62

M_A_DQS0

AN61

M_A_DQS1

AN58

M_B_DQS0

AN55

M_B_DQS1

AW57

M_A_DQS2

AW53

M_A_DQS3

AL42

M_B_DQS2

AL49

M_B_DQS3

AP49

AR51

AP51

M_A_A[15:0] 13

M_A_DQS#[1:0]

M_B_DQS#[1:0]

M_A_DQS#[3:2]

M_B_DQS#[3:2]

M_A_DQS[1:0]

M_B_DQS[1:0]

M_A_DQS[3:2]

M_B_DQS[3:2]

V_VREF_CA_DIMM 13,14

V_DDR_WR_VREF01 13

V_DDR_WR_VREF02 14

M_A_DQ[47:32]

M_B_DQ[47:32]

M_A_DQ[63:48]

M_B_DQ[63:48]

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

HSW_ULT_DDR3L

U20D

U20D

AY31

SB_DQ0

AW31

SB_DQ1

AY29

SB_DQ2

AW29

SB_DQ3

AV31

SB_DQ4

AU31

SB_DQ5

AV29

SB_DQ6

AU29

SB_DQ7

AY27

SB_DQ8

AW27

SB_DQ9

AY25

SB_DQ10

AW25

SB_DQ11

AV27

SB_DQ12

AU27

SB_DQ13

AV25

SB_DQ14

AU25

SB_DQ15

AM29

SB_DQ16

AK29

SB_DQ17

AL28

SB_DQ18

AK28

SB_DQ19

AR29

SB_DQ20

AN29

SB_DQ21

AR28

SB_DQ22

AP28

SB_DQ23

AN26

SB_DQ24

AR26

SB_DQ25

AR25

SB_DQ26

AP25

SB_DQ27

AK26

SB_DQ28

AM26

SB_DQ29

AK25

SB_DQ30

AL25

SB_DQ31

AY23

SB_DQ32

AW23

SB_DQ33

AY21

SB_DQ34

AW21

SB_DQ35

AV23

SB_DQ36

AU23

SB_DQ37

AV21

SB_DQ38

AU21

SB_DQ39

AY19

SB_DQ40

AW19

SB_DQ41

AY17

SB_DQ42

AW17

SB_DQ43

AV19

SB_DQ44

AU19

SB_DQ45

AV17

SB_DQ46

AU17

SB_DQ47

AR21

SB_DQ48

AR22

SB_DQ49

AL21

SB_DQ50

AM22

SB_DQ51

AN22

SB_DQ52

AP21

SB_DQ53

AK21

SB_DQ54

AK22

SB_DQ55

AN20

SB_DQ56

AR20

SB_DQ57

AK18

SB_DQ58

AL18

SB_DQ59

AK20

SB_DQ60

AM20

SB_DQ61

AR18

SB_DQ62

AP18

SB_DQ63

HSW_ULT_DDR3L

DDR CHANNEL B

DDR CHANNEL B

4 OF 19

4 OF 19

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS

SB_WE

SB_CAS

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

M_B_CLK_DDR#0 14

AN38

M_B_CLK_DDR0 14

AK38

M_B_CLK_DDR#1 14

AL38

M_B_CLK_DDR1 14

AY49

M_B_CKE0 14

AU50

M_B_CKE1 14

AW49

AV50

AM32

M_B_CS#0 14

AK32

M_B_CS#1 14

AL32

SB_ODT0

AM35

M_B_RAS# 14

AK35

M_B_WE# 14

AM33

M_B_CAS# 14

AL35

M_B_BS0 14

AM36

M_B_BS1 14

AU49

M_B_BS2 14

AP40

M_B_A0

AR40

M_B_A1

AP42

M_B_A2

AR42

M_B_A3

AR45

M_B_A4

AP45

M_B_A5

AW46

M_B_A6

AY46

M_B_A7

AY47

M_B_A8

AU46

M_B_A9

AK36

M_B_A10

AV47

M_B_A11

AU47

M_B_A12

AK33

M_B_A13

AR46

M_B_A14

AP46

M_B_A15

AW30

M_A_DQS#4

AV26

M_A_DQS#5

AN28

M_B_DQS#4

AN25

M_B_DQS#5

AW22

M_A_DQS#6

AV18

M_A_DQS#7

AN21

M_B_DQS#6

AN18

M_B_DQS#7

AV30

M_A_DQS4

AW26

M_A_DQS5

AM28

M_B_DQS4

AM25

M_B_DQS5

AV22

M_A_DQS6

AW18

M_A_DQS7

AM21

M_B_DQS6

AM18

M_B_DQS7

M_A_DQS#[7:0]13

M_A_DQS[7:0]13

M_A_DQ[63:0]13

M_B_DQS#[7:0]14

M_B_DQS[7:0]14

M_B_DQ[63:0]14

M_B_A[15:0] 14

M_A_DQS#[5:4]

M_B_DQS#[5:4]

M_A_DQS#[7:6]

M_B_DQS#[7:6]

M_A_DQS[5:4]

M_B_DQS[5:4]

M_A_DQS[7:6]

M_B_DQS[7:6]

M_A_DQS#[1:0]

M_A_DQS#[3:2]

M_A_DQS#[5:4]

M_A_DQS#[7:6]

M_A_DQS[1:0]

M_A_DQS[3:2]

M_A_DQS[5:4]

M_A_DQS[7:6]

M_A_DQ[15:0]

M_A_DQ[31:16]

M_A_DQ[47:32]

M_A_DQ[63:48]

M_B_DQS#[1:0]

M_B_DQS#[3:2]

M_B_DQS#[5:4]

M_B_DQS#[7:6]

M_B_DQS[1:0]

M_B_DQS[3:2]

M_B_DQS[5:4]

M_B_DQS[7:6]

M_B_DQ[15:0]

M_B_DQ[31:16]

M_B_DQ[47:32]

M_B_DQ[63:48]

B - 4 Processor 2/7

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Title

Title

[03] HASWELL ULT DDR

[03] HASWELL ULT DDR

[03] HASWELL ULT DDR

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

6-71-W5S20-D03

6-71-W5S20-D03

Date: Sheet

Date: Sheet

Date: Sheet

6-71-W5S20-D03

of

339Monday, October 14, 2013

of

339Monday, October 14, 2013

of

339Monday, October 14, 2013

1.0

1.0

1.0

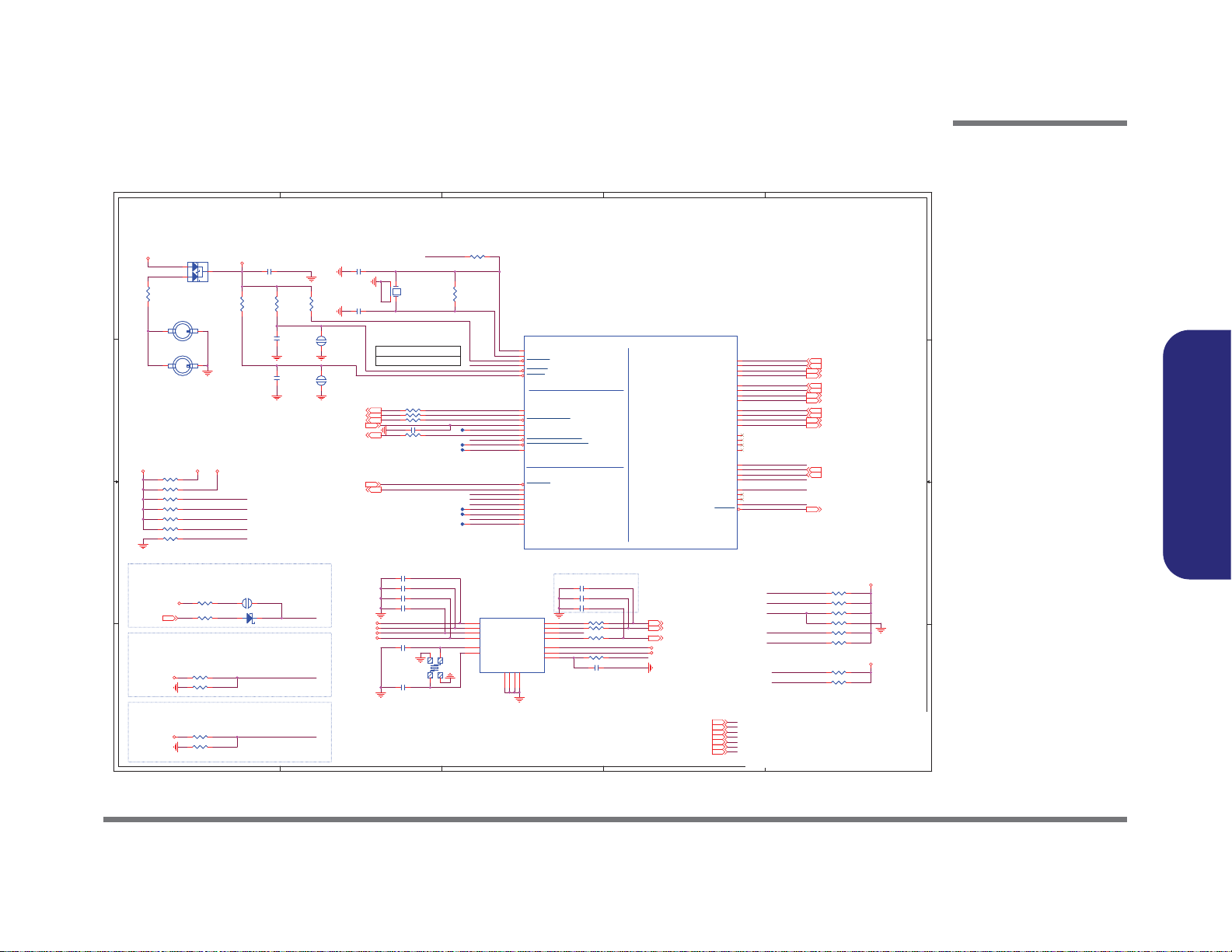

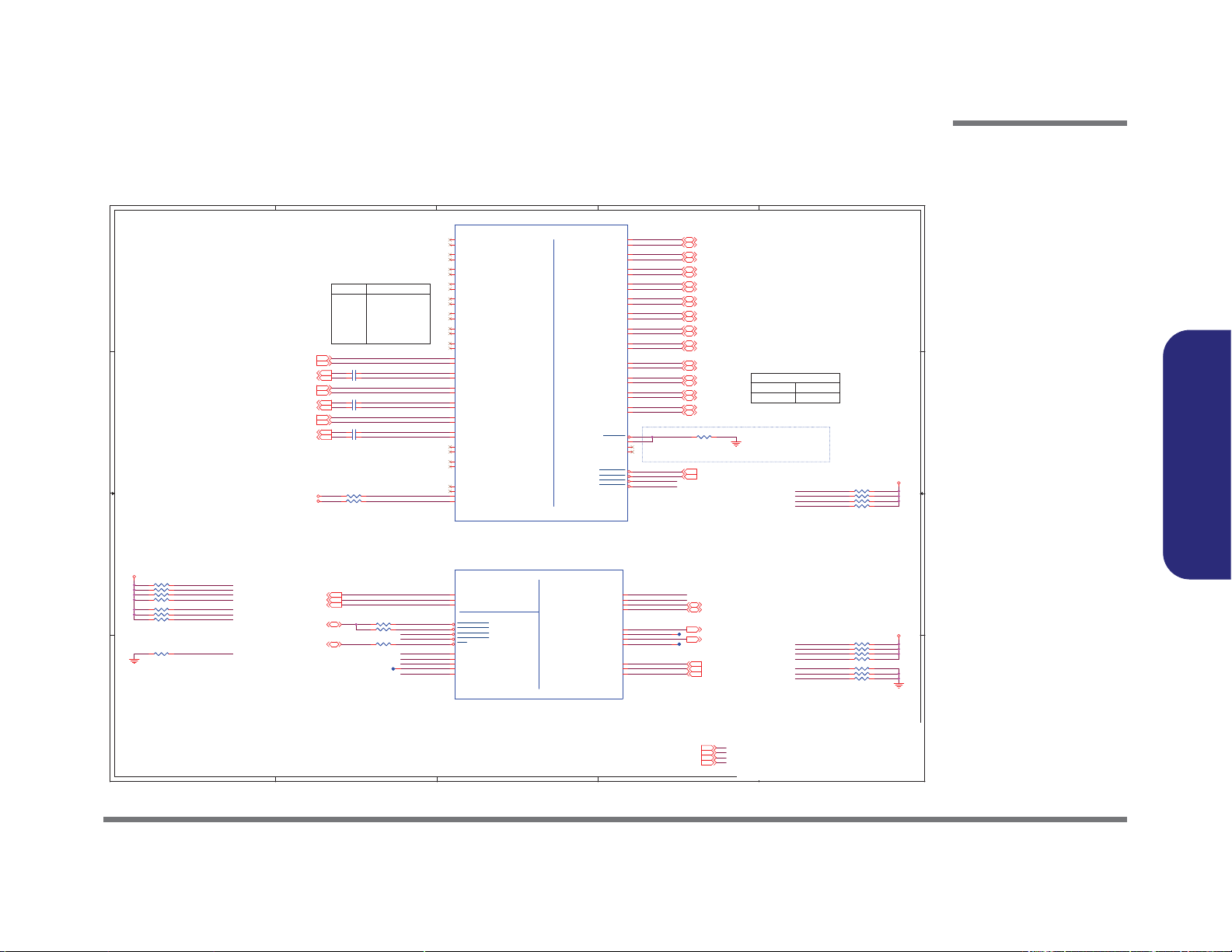

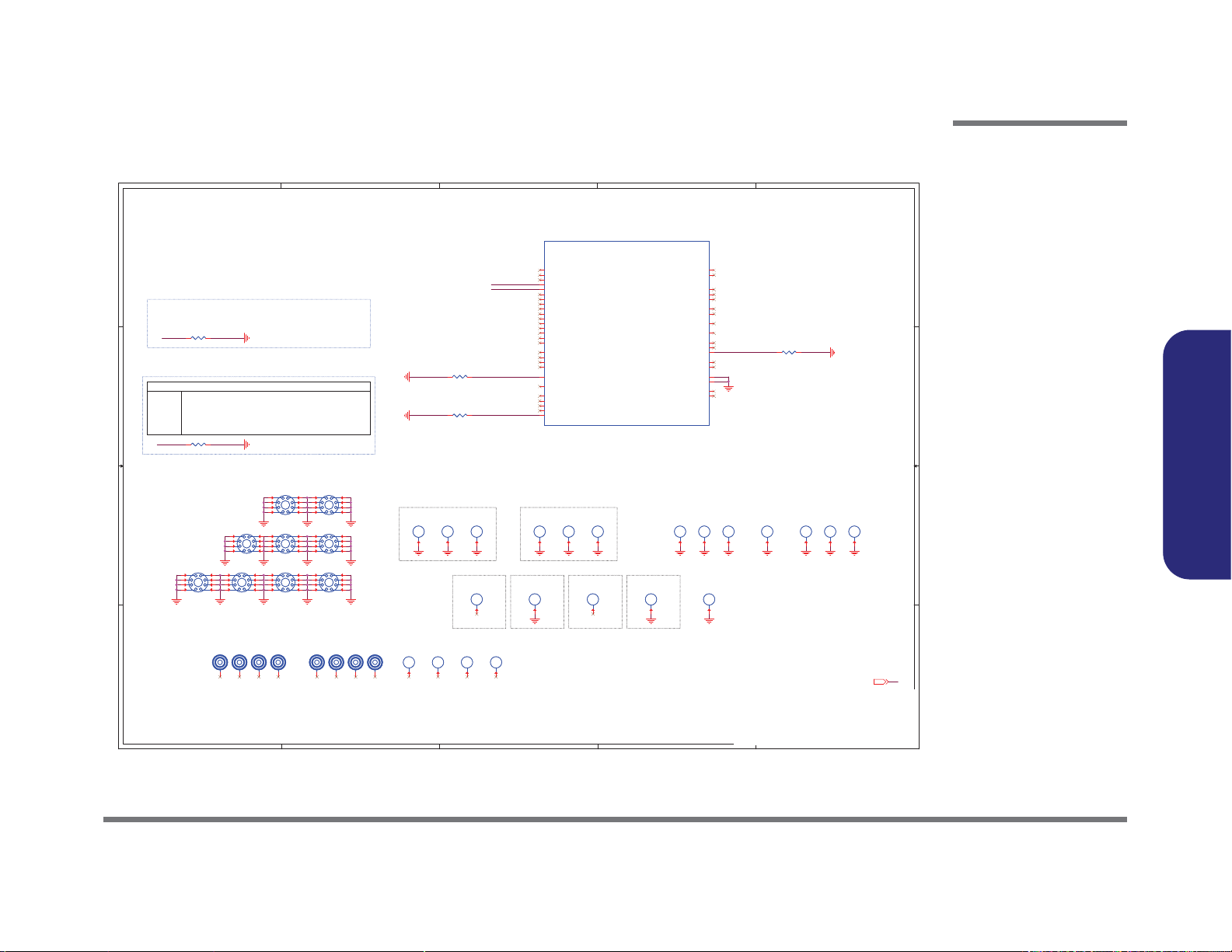

Page 4

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

SATA ODD

20mils

20mils

RTC CLEAR

RTC CLEAR

6-22-32R76-0B2

6-22-32R76-0BG

MSATA HDD

SATA HDD

STRAP PIN

STRAP PIN

Zo= 50ȍ±15%

Flash Descriptor Security Overide

Low = Disabled-(Default)

High = Enabled

INTVRMEN - INTEGRATED SUS 1.05V VRM ENABLE

HIGH - ENABLE INTERNAL VR'S

LOW - ENABLE EXTERNAL VR'S

JOPEN1

JOPEN2

CLEAR COMS

CLEAR ME RTC REGISTER

J_RTC1, J_RTC2 CO-LAY

XTAL 25MHz 20ppm CL<=12pF

6-22-25R00-1B6

RESERVED FOR EMI

PCH_JTAG_TMS

PCH_JTAG_TDI

PCH_JTAG_TDO

XDP_TCK_JTACK

RTC_VBAT_R

SM_INTRUDER#

PCH_INTVRMEN

SRTC_RTC#

HDA_SYNC

HDADOCKEN_N

RTC_X2

HDA_RST#

HDA_SDOUT

RTC_X1

RTC_VBAT

PCH_GPIO34

PCH_GPIO37

SATAIREF

SATAICOMP

SATA_LED#

PCH_GPIO34

PCH_GPIO37

MSATA_DET#

SATAICOMP

SATAIREF

SATA_LED#

SATA_ODD_PRSNT#

HDA_BITCLK

RTC_RST#

PCH_JTAG_TDI

PCH_JTAG_TDO

PCH_JTAG_TMS

XDP_TCK_JTACK

PCH_JTAG_TCK

PCH_JTAG_TCK

HDADOCKEN_N

PCH_INTVRMEN

HDA_SDOUT

VRTC

GCLK_32K

GCLK_32K

RTC_VBAT

SATA_ODD_PRSNT#

MSATA_DET#

3.3VA1.05VA

3.3VS

1.05V_SATA3PLL

VDD3

RTCVCC

VCC_JTAG

3.3VS

RTCVCC

3.3VA

VDD3

3.3VS

1.05VS

VDD3

VDD3

RTCVCC

XDP_TRST_CPU_N2

HDA_SDIN022

PCH_JTAG_TCK2

AZ_RST#_R22

AZ_BITCLK_R22

AZ_SDOUT_R22

AZ_SYNC_R22

RTCVCC6,10

1.05VS2,5,7,9,10,30,31

1.05V_SATA3PLL10

VDD35,6,7,10,19,21,24,25,27,28,29,30,32

3.3VS2,5,6,7,8,10,13,14,15,16,17,19,20,21,22,23,24,25,26,27,29,30,31

SATARXN0 26

SATARXP0 26

SATATXN0 26

SATATXP0 26

SATARXN1 26

SATARXP1 26

SATATXN1 26

SATATXP1 26

SATARXN2 21

SATARXP2 21

SATATXN2 21

SATATXP2 21

ME_WE24

1.05VA10,30

GCLK_27M 16

GCLK_24M 5

GCLK_25M 19

3.3VA2,5,6,7,8,10,27

SATA_ODD_PRSNT# 26

MSATA_DET# 21

SATA_LED# 26

Title

Size Document Number Rev

Date: Sheet of

1.0

[04] HASWELL ULT RTC/HDA/SATA

A3

439Wednesday, November 27, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

6-7P-W5S27-005

6-71-W5S20-D03

Title

Size Document Number Rev

Date: Sheet of

1.0

[04] HASWELL ULT RTC/HDA/SATA

A3

439Wednesday, November 27, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

6-7P-W5S27-005

6-71-W5S20-D03

Title

Size Document Number Rev

Date: Sheet of

1.0

[04] HASWELL ULT RTC/HDA/SATA

A3

439Wednesday, November 27, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

6-7P-W5S27-005

6-71-W5S20-D03

C434 *10p_50V_NPO_04C434 *10p_50V_NPO_04

JOPEN1

*CV-40mil

JOPEN1

*CV-40mil

12

R119

20K_1%_04

R119

20K_1%_04

C228 *0.1u_16V_Y5V_04C228 *0.1u_16V_Y5V_04

R383 43K_04R383 43K_04

R399 51_04R399 51_04

R307 0_04R307 0_04

C344 1u_6.3V_X5R_04C344 1u_6.3V_X5R_04

R411 *1K_04R411 *1K_04

X3

*MC-306_32.768KHz

X3

*MC-306_32.768KHz

14

3 2

R444 *10K_04R444 *10K_04

R248 *0_04R248 *0_04

R495

*1K_04

R495

*1K_04 C338

*18p_50V_NPO_04

C338

*18p_50V_NPO_04

R428 *0_04R428 *0_04

R408 51_04R408 51_04

R42 10K_04R42 10K_04

C90

1u_6.3V_X5R_04

C90

1u_6.3V_X5R_04

C336

*18p_50V_NPO_04

C336

*18p_50V_NPO_04

R416 *51_04R416 *51_04

D16 RB751S-40C2D16 RB751S-40C2

A C

R452 22_04R452 22_04

J_RTC2

*BAT-063-P01

J_RTC2

*BAT-063-P01

-2+

1

C238 *22u_6.3V_X5R_08C238 *22u_6.3V_X5R_08

JOPEN2

*CV-40mil

JOPEN2

*CV-40mil

12

R459

*10M_04

R459

*10M_04

R157 *0_04R157 *0_04

C237 *15p_50V_NPO_04C237 *15p_50V_NPO_04

R128 1K_04R128 1K_04

C247 *10p_50V_NPO_04C247 *10p_50V_NPO_04

R404 10K_04R404 10K_04

R429 0_04R429 0_04

R276 *33_04R276 *33_04

R451 22_04R451 22_04

R453 *330K_04R453 *330K_04

JOPEN4 *CV-40milJOPEN4 *CV-40mil

1 2

C232 *12p_50V_NPO_04C232 *12p_50V_NPO_04

R33 43K_04R33 43K_04

R250 *330_04R250 *330_04

C278 *10p_50V_NPO_04C278 *10p_50V_NPO_04

R454 330K_04R454 330K_04

R460 *1K_04R460 *1K_04

R117

20K_1%_04

R117

20K_1%_04

C227 *0.1u_16V_Y5V_04C227 *0.1u_16V_Y5V_04

C294 *10p_50V_NPO_04C294 *10p_50V_NPO_04

R168 *33_04R168 *33_04 R378 *0_04R378 *0_04

R439

1M_04

R439

1M_04

R445 22_04R445 22_04

J_RTC1

W5000102-001

J_RTC1

W5000102-001

-2+

1

R450 22_04R450 22_04

HSW_ULT_DDR3L

JTAG

RTC

AUDIO SATA

5 OF 19

U20E

HSW_ULT_DDR3L

JTAG

RTC

AUDIO SATA

5 OF 19

U20E

RSVD

L11

RSVD

K10

PCH_TMS

AD62

PCH_TDO

AE61

PCH_TDI

AD61

PCH_TCK

AE62

PCH_TRST

AU62

HDA_DOCK_RST/I2S1_SFRM

AV10

HDA_DOCK_EN/I2S1_TXD

AW10

HDA_SDI1/I2S1_RXD

AU12

HDA_SDO/I2S0_TXD

AU11

HDA_SDI0/I2S0_RXD

AY10

HDA_RST/I2S_MCLK

AU8

HDA_SYNC/I2S0_SFRM

AV11

HDA_BCLK/I2S0_SCLK

AW8

RSVD

AC4

RSVD

AL11

RSVD

AV2

I2S1_SCLK

AY8

SATALED

U3

JTAGX

AE63

RTCX2

AY5

SATA_RCOMP

C12

SATA_IREF

A12

SATA3GP/GPIO37

AC1

SATA2GP/GPIO36

V6

SATA1GP/GPIO35

U1

SATA0GP/GPIO34

V1

SATA_TP3/PETP6_L0

D17

SATA_TN3/PETN6_L0

C17

SATA_RP3/PERP6_L0

E5

SATA_RN3/PERN6_L0

F5

SATA_TP2/PETP6_L1

C15

SATA_TN2/PETN6_L1

B14

SATA_RN2/PERN6_L1

J6

SATA_RP2/PERP6_L1

H6

SATA_TP1/PETP6_L2

B17

SATA_TN1/PETN6_L2

A17

SATA_RN1/PERN6_L2

J8

SATA_RP1/PERP6_L2

H8

SATA_TP0/PETP6_L3

A15

SATA_TN0/PETN6_L3

B15

SATA_RP0/PERP6_L3

H5

SATA_RN0/PERN6_L3

J5

RTCX1

AW5

RTCRST

AU7

SRTCRST

AV6

INTVRMEN

AV7

INTRUDER

AU6

R388 10K_04R388 10K_04

C229 *2.2u_6.3V_X5R_04C229 *2.2u_6.3V_X5R_04

C245 *0.1u_16V_Y5V_04C245 *0.1u_16V_Y5V_04

R401 51_04R401 51_04

R443 *1K_04R443 *1K_04

C

A

A

D17

*BAT54CS3

C

A

A

D17

*BAT54CS3

1

2

3

U54

*SLG3NB3454VTR

PCB Footprint = TQFN16-2X3MM

U54

*SLG3NB3454VTR

PCB Footprint = TQFN16-2X3MM

XTAL_IN

1

VDD

2

VDDIO_24M

3

GND

4

24M

5

25M

6

GND

7

VDDIO_25M

8

32.768K

9

VRTC

10

VDDIO_27M1127M

12

GND

13

VOUT

14

V3.3A

15

XTAL_OUT

16

PAD

17

C86

1u_6.3V_X5R_04

C86

1u_6.3V_X5R_04

R310 3K_1%_04R310 3K_1%_04

X5

*FSX3L_25MHz

X5

*FSX3L_25MHz

12

3 4

Processor 3/7

Schematic Diagrams

B.Schematic Diagrams

Sheet 4 of 39

Processor 3/7

Processor 3/7 B - 5

Page 5

Schematic Diagrams

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Processor 4/7

HSW_ULT_DDR3L

C335

C335

PJ11

PJ11

*OPEN-1mm

*OPEN-1mm

SHORT

G

Q15

Q15

HSW_ULT_DDR3L

HSW_ULT_DDR3L

LPC

LPC

12

Q12

Q12

*MTP3403N3

*MTP3403N3

G

R461

R461

*1M_04

*1M_04

DS

HSW_ULT_DDR3L

CLOCK

CLOCK

SIGNALS

SIGNALS

6 OF 19

6 OF 19

SMBUS

SMBUS

C-LINKSPI

C-LINKSPI

3.3V_SPIVDD3

DS

U20F

C337

C337

*0.1u_16V_Y5V_04

*0.1u_16V_Y5V_04

ON

U20F

C43

CLKOUT_PCIE_N0

C42

CLKOUT_PCIE_P0

U2

PCIECLKRQ0/GPIO18

B41

CLKOUT_PCIE_N1

A41

CLKOUT_PCIE_P1

Y5

PCIECLKRQ1/GPIO19

C41

CLKOUT_PCIE_N2

B42

CLKOUT_PCIE_P2

AD1

PCIECLKRQ2/GPIO20

B38

CLKOUT_PCIE_N3

C37

CLKOUT_PCIE_P3

N1

PCIECLKRQ3/GPIO21

A39

CLKOUT_PCIE_N4

B39

CLKOUT_PCIE_P4

U5

PCIECLKRQ4/GPIO22

B37

CLKOUT_PCIE_N5

A37

CLKOUT_PCIE_P5

T2

PCIECLKRQ5/GPIO23

U20G

U20G

AU14

LAD0

AW12

LAD1

AY12

LAD2

AW11

LAD3

AV12

LFRAME

AA3

SPI_CLK

Y7

SPI_CS0

Y4

SPI_CS1

AC2

SPI_CS2

AA2

SPI_MOSI

AA4

SPI_MISO

Y6

SPI_IO2

AF1

SPI_IO3

C333

C333

*0.1u_16V_Y5V_04

*0.1u_16V_Y5V_04

GPG224

*MTN7002ZHS3

*MTN7002ZHS3

*1u_6.3V_X5R_04

*1u_6.3V_X5R_04

R462 *100K_04R462 *100K_04

3.3VS

R26 10K_04R26 10K_04

R66 10K_04R66 10K_04

R413 10K_04R413 10K_04

R49 *10K_04R49 *10K_04

R48 10K_04R48 10K_04

R381 10K_04R381 10K_04

Sheet 5 of 39

Processor 4/7

Share ROM

HSPI_SCLK24

HSPI_MSO24

HSPI_CE#24

HSPI_MSI24

SPI_SCLK

SPI_CS0#

SPI_CS1#

SPI_SI

SPI_SO

SPI_WP#_0

SPI_WP#_1

SPI_HOLD#_1

R398 0_04R398 0_04

R390 0_04R390 0_04

R405 0_04R405 0_04

R409 0_04R409 0_04

R395 0_04R395 0_04 R414 2.2K_04R414 2.2K_04

R84 0_04R84 0_04

R397 0_04R397 0_04

R400 0_04R400 0_04

R403 0_04R403 0_04

R37 33_04R37 33_04

R40 33_04R40 33_04

R415 33_04R415 33_04

R412 33_04R412 33_04

ᓮᓮᓮᓮإإإإહહહહᦤᦤᦤᦤ

3.3V_SPI

C84

C84

0.1u_16V_Y5V_04

0.1u_16V_Y5V_04

B.Schematic Diagrams

3.3V_SPI

R111

R111

3.3K_1%_04

3.3K_1%_04

R98

R98

3.3K_1%_04

3.3K_1%_04

C82

C82

0.1u_16V_Y5V_04

0.1u_16V_Y5V_04

R109

R109

3.3K_1%_04

3.3K_1%_04

R95

R95

3.3K_1%_04

3.3K_1%_04

SPI_WP#_1

SPI_HOLD#_1

SPI_WP#_0

SPI_HOLD#_0

PCIECLKRQ0#

CARD_CLKRQ1#

WLAN_CLKREQ#

PCIECLKRQ4#

PCIECLKRQ5#

SPI_SCLK_R

SPI_CS_0#

SPI_CS_1#

SPI_SI_R

SPI_SO_R

PCH_SPI_DQ2

PCH_SPI_DQ3SPI_HOLD#_0

Co_Lay

BIOS ROM

SPI_* = 1.5"~6.5"

U22

U22

5

8

SI

VDD

2

SO

1

3

CE#

WP#

6

SCK

4

7

VSS

HOLD#

GD25B32B

GD25B32B

PCB Footprint = M-SOP8B

PCB Footprint = M-SOP8B

32Mbit

ME ROM

SPI_* = 1.5"~6.5"

U21

U21

5

8

SI

VDD

2

SO

1

3

CE#

WP#

6

SCK

4

7

VSS

HOLD#

GD25B16B

GD25B16B

PCB Footprint = M-SOP8B

PCB Footprint = M-SOP8B

16Mbit

SPI_SI_B SPI_SI

R105 33_04R105 33_04

SPI_SO_B

SPI_CS1#

SPI_SCLK_B SPI_SCLK

SPI_SI_M SPI_SI

SPI_SO_M

SPI_CS0#

SPI_SCLK_M SPI_SCLK

R434 33_04R434 33_04

R106 33_04R106 33_04

R108 33_04R108 33_04

R433 33_04R433 33_04

R107 33_04R107 33_04

SPI_SO

SPI_SO

CLK_PCIE_CARD#19

CLK_PCIE_CARD19

CARD_CLKRQ1#19

CLK_PCIE_MINI#21

CLK_PCIE_MINI21

WLAN_CLKREQ#21

CLK_PCIE_GLAN#19

CLK_PCIE_GLAN19

LAN_CLKREQ#19

LAN_CLKREQ# PU 10K_04 IN RTL8411B SIDE

100MHz

PCIECLKRQ0#

CARD_CLKRQ1#

WLAN_CLKREQ#

LAN_CLKREQ#

PCIECLKRQ4#

PCIECLKRQ5#

LPC_AD023,24

LPC_AD123,24

LPC_AD223,24

LPC_AD323,24

LPC_FRAME#23,24

SPI_SCLK_R

SPI_CS_0#

SPI_CS_1#

SPI_SI_R

SPI_SO_R

PCH_SPI_DQ2

PCH_SPI_DQ3

3.3V_SPI

XTAL24_IN

XTAL24_OUT

DIFFCLK_BIASREF

TESTLOW_C35

TESTLOW_C34

TESTLOW_AK8

TESTLOW_AL8

CLKOUT_LPC_0

CLKOUT_LPC_1

CLKOUT_ITPXDP

CLKOUT_ITPXDP_P

SMBALERT/GPIO11

SMBCLK

SMBDATA

SML0ALERT/GPIO60

SML0CLK

SML0DATA

SML1ALERT/PCHHOT/GPIO73

SML1CLK/GPIO75

SML1DATA/GPIO74

CL_CLK

CL_DATA

CL_RST

7 OF 19

7 OF 19

R89 *0_04R89 *0_04

R71

R71

*1M_04

LPC_0

LPC_1

CK_XDP_P

CK_XDP_N

PCH_GPIO11

SMB_CLK

SMB_DATA

DRAMRST_CNTRL

SML0CLK

SML0DATA

PCH_GPIO73

SML1CLK

SML1DATA

CL_CLK1

CL_DATA1

CL_RST#1

Q10A

Q10A

MTDK5S6R

MTDK5S6R

MTDK5S6R

MTDK5S6R

*1M_04

R290 3.01K_1%_04R290 3.01K_1%_04

R330 10K_04R330 10K_04

R76 10K_04R76 10K_04

R82 10K_04R82 10K_04

R83 10K_04R83 10K_04

R127 22_04R127 22_04

R125 22_04R125 22_04

SMB_CLK 23

SMB_DATA 23

CL_CLK1 21

CL_DATA1 21

CL_RST#1 21

2

G

G

6 1

S

D

S

D

5

Q10B

Q10B

G

G

3 4

D

D

R421 *0_04R421 *0_04

R407 *0_04R407 *0_04

Title

Title

Title

[05] HASWELL ULT LPC/SPI/SMB/CL

[05] HASWELL ULT LPC/SPI/SMB/CL

[05] HASWELL ULT LPC/SPI/SMB/CL

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

A25

XTAL24_IN

B25

XTAL24_OUT

K21

RSVD1LAN_CLKREQ#

RSVD

M21

RSVD2

RSVD

C26

XCLK_BIASRE

C35

TESTLOW1

C34

TESTLOW2

AK8

TESTLOW3

AL8

TESTLOW4

AN15

AP15

B35

A35

AN2

AP2

AH1

AL2

AN1

AK1

AU4

AU3

AH3

AF2

AD2

AF4

SMB_CLK

SMB_DATA

SMB_CLK

SMB_DATA

3.3V_SPI10

1.05VS2,4,7,9,10,30,31

RTCVCC4,6,10

VDD34,6,7,10,19,21,24,25,27,28,29,30,32

3.3VA2,4,6,7,8,10,27

3.3VS2,4,6,7,8,10,13,14,15,16,17,19,20,21,22,23,24,25,26,27,29,30,31

GCLK_24M 4

C23 *18p_50V_NPO_04C23 *18p_50V_NPO_04

12

X1

*RG24MHZX1*RG24MHZ

RG24000152 PN: 6-22-24R00-1B8

C22 *18p_50V_NPO_04C22 *18p_50V_NPO_04

1.05VS

PCLK_KBC 24

PCLK_TPM 23

PCH_GPIO11

SMB_DATA

SMB_CLK

DRAMRST_CNTRL

SML0CLK

SML0DATA

PCH_GPIO73

SML1CLK

SML1DATA

3.3VS

R420

R420

2.2K_04

2.2K_04

S

S

SMB_CLK_DDR

SMB_DAT_DDR

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

6-7P-W5S27-005

6-7P-W5S27-005

6-7P-W5S27-005

R424 10K_04R424 10K_04

R402 2.2K_04R402 2.2K_04

R112 2.2K_04R112 2.2K_04

R418 *1K_04R418 *1K_04

R110 2.2K_04R110 2.2K_04

R114 10K_04R114 10K_04

R101 2.2K_04R101 2.2K_04

R93 2.2K_04R93 2.2K_04

R406

R406

2.2K_04

2.2K_04

SMB_CLK_DDR

SMB_DAT_DDR

SMB_CLK_DDR 13,14

SMB_DAT_DDR 13,14

6-71-W5S20-D03

6-71-W5S20-D03

6-71-W5S20-D03

3.3VA

1.0

1.0

1.0

539Monday, October 14, 2013

539Monday, October 14, 2013

539Monday, October 14, 2013

B - 6 Processor 4/7

Page 6

Processor 5/7

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

HSW_ULT_DDR3L

U20H

VDD3

4

5

AK2

AC3

AG2

AY7

AB5

AG7

AW6

AV4

AL7

AJ8

AN4

AF3

AM5

R562

R562

*100K_04

*100K_04

R435 0_04R435 0_04

R436 *0_04R436 *0_04

1.5VS_PWRGD

147

U24B

U24B

74LVC08PW

74LVC08PW

1

2

R50

R50

*10mil_04

*10mil_04

U20H

SUSACK

SYS_RESET

SYS_PWROK

PCH_PWROK

APWROK

PLTRST

RSMRST

SUSWARN/SUSPWRDNACK/GPIO 30

PWRBTN

ACPRESENT/GPIO31

BATLOW/GPIO72

SLP_S0

SLP_WLAN/GPIO29

VDD3

5

3

6

SUS_PWR_ACK24

PLT_RST#23

RSMRST#24

SUSWARN#24

PWR_BTN#24

AC_PRESENT24

PCH_SLP_WLAN#_R24

SLP_A27,30

C339 *0.1u_16V_Y5V_04C339 *0.1u_16V_Y5V_04

C340 *0.1u_16V_Y5V_04C340 *0.1u_16V_Y5V_04

C330 *0.1u_16V_Y5V_04C330 *0.1u_16V_Y5V_04

C327 *0.1u_16V_Y5V_04C327 *0.1u_16V_Y5V_04

C328 *0.1u_16V_Y5V_04C328 *0.1u_16V_Y5V_04

close to AND gate side

SUSWARN#

PLT_RST#

R563 *470K_04R563 *470K_04

*3300p_50V_X7R_04

*3300p_50V_X7R_04

R419 *0_04R419 *0_04

R417 0_04R417 0_04

R62 0_04R62 0_04

RSMRST# PD 10K_04 IN TI8587 SIDE

R86 0_04R86 0_04

C475

C475

1.05VS_PWRGD9,27,30

VDDQ_PWRGD29

1.05VS_PWRGD

VDDQ_PWRGD

1.5VS_PWRGD

PCH_PWROK_EC

ALL_SYS_PWRGD

PM_PWROK24

*MTN7002ZHS3

*MTN7002ZHS3

1.05VM_PWRGD30

1.05VS_PWRGD

VDDQ_PWRGD

G

Q23

Q23

SUS_ACK

SYS_RESET#

SYS_PWROK

PCH_PWROK

APWROK

PLT_RST_N

RSMRST#

SUSWARN#

PWR_BTN#

AC_PRESENT

PM_BATLOW#

SLP_SO

PCH_SLP_WLAN#

DS

APWROK

ALL_SYS_PWRGD

1.5VS_PWRGD29

SYSTEM POWER MANAGEMENT

SYSTEM POWER MANAGEMENT

C331 *0.1u_16V_Y5V_04C331 *0.1u_16V_Y5V_04

4

R564 *0_04R564 *0_04

U36

U36

*MC74VHC1G08DFT2G

*MC74VHC1G08DFT2G

PCH_PWROK

ALL_SYS_PWRGD15,24

VDD3

9

10

PCH_PWROK_EC24

HSW_ULT_DDR3L

8 OF 19

8 OF 19

ALL_SYS_PWRGD

147

U24C

U24C

74LVC08PW

74LVC08PW

C476

C476

*1u_6.3V_X5R_04

*1u_6.3V_X5R_04

8

PCH_PWROK_EC

DSWVRMEN

DPWROK

WAKE

CLKRUN/GPIO32

SUS_STAT/GPIO61

SUSCLK/GPIO62

SLP_S5/GPIO63

SLP_S4

SLP_S3

SLP_A

SLP_SUS

SLP_LAN

M STEP

APWROK

R565

R565

*1M_04

*1M_04

BUF_PLT_RST#19,21,24

VDD3

147

12

13

AW7

DSWODVREN

AV5

PCH_DPWROK

AJ5

PCIE_WAKE#

PCIE_WAKE# PU 10K_04 IN RTL8411B SIDE

V5

PM_CLKRUN#

AG4

AE6

PCH_GPIO62

AP5

SLP_S5#

AJ6

AT4

AL5

SLP_A#

AP4

SLP_SUS#

AJ7

PM_SLP_LAN#

PLT_RST# to Buffer

R467

R467

100K_04

100K_04

C329 *0.1u_16V_Y5V_04C329 *0.1u_16V_Y5V_04

11

U24D

U24D

74LVC08PW

74LVC08PW

R442 *0_04R442 *0_04

R441 0_04R441 0_04

PCIE_WAKE# 19,21

PM_CLKRUN# 23

S4_STATE# 23

SUSC# 24,29

SUSB# 23,24,27

SLP_A# 27

SLP_SUS# 24,27

VDD3

147

3

R437 1K_04R437 1K_04

1

2

U24A

U24A

74LVC08PW

74LVC08PW

PCH_DPWROK_EC

RSMRST#

3.3VS

R466

R466

100K_04

100K_04

PLT_RST#

SYS_PWROKALL_SYS_PCH_PWROK_ECVDDQ_PWRGD_R

PCH_DPWROK_EC 24

SUSWARN#

PM_BATLOW#

STRAP PIN

DSWODVREN - ON DIE DSW VR ENABLE

HIGH

LOW

DSWODVREN

SYS_RESET#

PM_CLKRUN#

PWR_BTN#

AC_PRESENT

PCH_GPIO62

SYS_PWROK

PCH_DPWROK

APWROK

PCH_PWROK

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Title

Title

[06] HASWELL ULT POWER MAMT

[06] HASWELL ULT POWER MAMT

[06] HASWELL ULT POWER MAMT

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

Date: Sheet

Date: Sheet

Date: Sheet

R431 10K_04R431 10K_04

R81 10K_04R81 10K_04

ENABLED (DEFAULT)

DISABLED

R449 330K_04R449 330K_04

R447 *330K_04R447 *330K_04

R410 10K_04R410 10K_04

R29 8.2K_04R29 8.2K_04

R85 10K_04R85 10K_04

R73 10K_04R73 10K_04

R70 *100K_04R70 *100K_04

R69 *1K_04R69 *1K_04

R438 *100K_04R438 *100K_04

R440 *100K_04R440 *100K_04

R53 *100K_04R53 *100K_04

R43 *100K_04R43 *100K_04

RTCVCC4,10

VDD34,5,7,10,19,21,24,25,27,28,29,30,32

3.3VA2,4,5,7,8,10,27

3.3VS2,4,5,7,8,10,13,14,15,16,17,19,20,21,22,23,24,25,26,27,29,30,31

6-71-W5S20-D03

6-71-W5S20-D03

6-71-W5S20-D03

Schematic Diagrams

B.Schematic Diagrams

3.3VA

Sheet 6 of 39

RTCVCC

3.3VS

VDD3

1.0

1.0

1.0

639Monday, October 14, 2013

639Monday, October 14, 2013

639Monday, October 14, 2013

of

of

of

Processor 5/7

Processor 5/7 B - 7

Page 7

Schematic Diagrams

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Processor 6/7

HSW_ULT_DDR3L

BOARD_ID2

1

1

1

1

3.3VA

3.3VA

HSW_ULT_DDR3L

GPIO

GPIO

10 OF 19

10 OF 19

CPU/

CPU/

MISC

MISC

SERIAL IO

SERIAL IO

Microphone Type Detect

PCH_GPIO8

D-MIC_DET#

G-Sensor Detect

PCH_GPIO10

G-SENSOR_DET

THRMTRIP

RCIN/GPIO82

SERIRQ

PCH_OPI_RCOMP

RSVD

RSVD

GSPI0_CS/GPIO83

GSPI0_CLK/GPIO84

GSPI0_MISO/GPIO85

GSPI0_MOSI/GPIO86

GSPI1_CS/GPIO87

GSPI1_CLK/GPIO88

GSPI1_MISO/GPIO89

GSPI_MOSI/GPIO90

UART0_RXD/GPIO91

UART0_TXD/GPIO92

UART0_RTS/GPIO93

UART0_CTS/GPIO94

UART1_RXD/GPIO0

UART1_TXD/GPIO1

UART1_RST/GPIO2

UART1_CTS/GPIO3

I2C0_SDA/GPIO4

I2C0_SCL/GPIO5

I2C1_SDA/GPIO6

I2C1_SCL/GPIO7

SDIO_CLK/GPIO64

SDIO_CMD/GPIO65

SDIO_D0/GPIO66

SDIO_D1/GPIO67

SDIO_D2/GPIO68

SDIO_D3/GPIO69

LOW = D-MIC

HIGH = A-MIC

R103 *10K_04R103 *10K_04

R277 *10K_04R277 *10K_04

HIGH = G-Sensor Stuff

R425 *10K_04R425 *10K_04

R577 *10K_04R577 *10K_04

D60

V4

T4

AW15

AF20

AB21

R6

L6

N6

L8

R7

L5

N7

K2

J1

K3

J2

G1

K4

G2

J3

J4

F2

F3

G4

F1

E3

F4

D3

E4

C3

E2

THRMTRIP_R_N

SB_KBCRST#_R

SERIRQ

PCH_OPI_RCOMP

PCH_GPIO83

PCH_GPIO84

PCH_GPIO85

GSPI0_BBS0

PCH_GPIO87

PCH_GPIO88

PCH_GPIO89

PCH_GPIO90

PCH_GPIO91

PCH_GPIO92

PCH_GPIO93

PCH_GPIO94

PCH_GPIO0

SCI#_R

SATA_ODD_DA#

T_SDA

T_SCL

PCH_GPIO6

PCH_GPIO7

PCH_GPIO64

PCH_GPIO65

SDIO_D0

PCH_GPIO67

SATA_ODD_PWRGT

PCH_GPIO69

3.3VA

3.3VA

U20J

U20J

P1

PCH_GPIO76

D-MIC_DET#

PCH_GPIO12

PCH_GPIO15

PCH_GPIO16

PCH_GPIO17

PCH_GPIO24

PCH_GPIO27

BOARD_ID1

BOARD_ID0

SB_BLON15

SMI#24

T_INT25

MPHY_PWREN30

R52 0_04R52 0_04

R100 0_04R100 0_04

Sheet 7 of 39

Processor 6/7

B.Schematic Diagrams

STRAP PIN

No Reboot

LOW = Disable (default)

STP_A16OVR

HIGH = Enable

PCH_HDA_SPKR

STRAP PIN

A16 SWAP OVERRIDE STRAP

LOW = A16 SWAP OVERRIDE

STP_A16OVR

HIGH = NO OVERRIDE

SDIO_D0

STRAP PIN

GSPI0_BBS0

HIGH

LOW SPI BUS

GSPI0_BBS0

PCH_SPKR22

LPC BUS

R386 *1K_04R386 *1K_04

R320 *1K_04R320 *1K_04

R46 *1K_04R46 *1K_04

R51 *1K_04R51 *1K_04

R385 0_04R385 0_04

3.3VS

3.3VS

3.3VS

PCH_GPIO56

PCH_GPIO58

PCH_GPIO59

PCH_GPIO44

SMI#_R

PCH_GPIO48

PCH_GPIO49

T_INT

MPHY_PWREN

BOARD_ID2

PCH_GPIO14

SWI#_R

PCH_GPIO45

PCH_GPIO46

PCH_GPIO9

G-SENSOR_DET

DEVSLP0

PCH_GPIO70

DEVSLP1

DEVSLP2

PCH_HDA_SPKR

W54

W55

W94

W95

W97 0

BOARD_ID0

BOARD_ID1

BOARD_ID2

PCH_GPIO15

BMBUSY/GPIO76

AU2

GPIO8

AM7

LAN_PHY_PWR_CTRL/GPIO12

AD6

GPIO15

Y1

GPIO16

T3

GPIO17

AD5

GPIO24

AN5

GPIO27

AD7

GPIO28

AN3

GPIO26

AG6

GPIO56

AP1

GPIO57

AL4

GPIO58

AT5

GPIO59

AK4

GPIO44

AB6

GPIO47

U4

GPIO48

Y3

GPIO49

P3

GPIO50

Y2

HSIOPC/GPIO71

AT3

GPIO13

AH4

GPIO14

AM4

GPIO25

AG5

GPIO45

AG3

GPIO46

AM3

GPIO9

AM2

GPIO10

P2

DEVSLP0/GPIO33

C4

SDIO_POWER_EN/GPIO70

L2

DEVSLP1/GPIO38

N5

DEVSLP2/GPIO39

V2

SPKR/GPIO81

BOARD_ID LIST

BOARD_ID0 BOARD_ID1

00

10

01

11

00

R78 *10K_04R78 *10K_04

R77 *10K_04R77 *10K_04

R67 *10K_04R67 *10K_04

R68 *10K_04R68 *10K_04

R113 *10K_04R113 *10K_04

R234 *10K_04R234 *10K_04

R59 1K_04R59 1K_04

R333 1K_04R333 1K_04

R34 0_04R34 0_04

R455 49.9_1%_04R455 49.9_1%_04

R359 0_04R359 0_04

1.05VS

SB_KBCRST# 24

SERIRQ 23,24

SCI# 24SWI#24

SATA_ODD_DA# 26

T_SDA 25

T_SCL 25

SATA_ODD_PWRGT 26

PCH_GPIO45

PCH_GPIO56

PCH_GPIO59

SMI#

PCH_GPIO27

SWI#_R

PCH_GPIO7

PCH_GPIO16

PCH_GPIO17

PCH_GPIO76

PCH_GPIO88

PCH_GPIO89

PCH_GPIO93

PCH_GPIO94

SATA_ODD_DA#

T_SCL

T_SDA

T_INT

SERIRQ

SCI#_R

SB_KBCRST#_R

DEVSLP1

PCH_GPIO83

PCH_GPIO84

PCH_GPIO85

PCH_GPIO90

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Title

Title

[07] HASWELL ULT GPIOS

[07] HASWELL ULT GPIOS

[07] HASWELL ULT GPIOS

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

Date: Sheet

Date: Sheet

Date: Sheet

R63 10K_04R63 10K_04

R65 10K_04R65 10K_04

R123 10K_04R123 10K_04

R58 10K_04R58 10K_04

R156 10K_04R156 10K_04

R104 10K_04R104 10K_04

R354 *10K_04R354 *10K_04

R396 100K_04R396 100K_04

R39 10K_04R39 10K_04

R380 4.7K_04R380 4.7K_04

R60 10K_04R60 10K_04

R55 10K_04R55 10K_04

R364 10K_04R364 10K_04

R361 10K_04R361 10K_04

R356 10K_04R356 10K_04

R315 10K_04R315 10K_04

R355 10K_04R355 10K_04

R373 10K_04R373 10K_04

R32 10K_04R32 10K_04

R362 10K_04R362 10K_04

R35 10K_04R35 10K_04

R369 100K_04R369 100K_04

R28 3.3K_1%_04R28 3.3K_1%_04

R54 100K_04R54 100K_04R321 *1K_04R321 *1K_04

R23 10K_04R23 10K_04

R365 10K_04R365 10K_04

6-71-W5S20-D03

6-71-W5S20-D03

6-71-W5S20-D03

3.3VA

VDD3

3.3VS

1.05VS2,4,5,9,10,30,31

VDD34,5,6,10,19,21,24,25,27,28,29,30,32

3.3VA2,4,5,6,8,10,27

3.3VS2,4,5,6,8,10,13,14,15,16,17,19,20,21,22,23,24,25,26,27,29,30,31

of

739Wednesday, November 06, 2013

of

739Wednesday, November 06, 2013

of

739Wednesday, November 06, 2013

1.0

1.0

1.0

B - 8 Processor 6/7

Page 8

Processor 7/7

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

HSW_ULT_DDR3L

U20K

U20K

F10

PERN5_L0

E10

PERP5_L0

C23

PETN5_L0

C22

PETP5_L0

F8

PERN5_L1

E8

PERP5_L1

B23

PCI-E x1 Usage

Lane 1 X

Lane 2 X

Lane 3 WLAN

Lane 4 GLAN / CARD READER

Lane 5 RESERVED FOR 17"

Lane 6 X

Lane 7 X

Lane 8 X

PCIE_RXN3_WLAN21

PCIE_RXP3_WLAN21

PCIE_TXN3_WLAN21

PCIE_TXP3_WLAN21

PCIE_RXN4_GLAN19

PCIE_RXP4_GLAN19

PCIE_TXN4_GLAN19

PCIE_TXP4_GLAN19

PCIE_RXN1_CARD19

PCIE_RXP1_CARD19

PCIE_TXN1_CARD19

PCIE_TXP1_CARD19

1.05V_USB3PLL

1.05V_USB3PLL

C287 0.1u_10V_X7R_04C287 0.1u_10V_X7R_04

C288 0.1u_10V_X7R_04C288 0.1u_10V_X7R_04

C300 0.1u_10V_X7R_04C300 0.1u_10V_X7R_04

C299 0.1u_10V_X7R_04C299 0.1u_10V_X7R_04

C301 *0.1u_10V_X7R_04C301 *0.1u_10V_X7R_04

C302 *0.1u_10V_X7R_04C302 *0.1u_10V_X7R_04

R75 3K_1%_04R75 3K_1%_04

R279 0_04R279 0_04

PCIE_TXN3_C

PCIE_TXP3_C

PCIE_TXN4_C

PCIE_TXP4_C

PCIE_TXN1_C

PCIE_TXP1_C

PCIE_RCOMP

PCIE_IREF

A23

H10

G10

B21

C21

E6

F6

B22

A21

G11

F11

C29

B30

F13

G13

B29

A29

G17

F17

C30

C31

F15

G15

B31

A31

E15

E13

A27

B27

PETN5_L1

PETP5_L1

PERN5_L2

PERP5_L2

PETN5_L2

PETP5_L2

PERN5_L3

PERP5_L3

PETN5_L3

PETP5_L3

PERN3

PERP3

PETN3

PETP3

PERN4

PERP4

PETN4

PETP4

PERN1/USB3RN3

PERP1/USB3RP3

PETN1/USB3TN3

PETP1/USB3TP3

PERN2/USB3RN4

PERP2/USB3RP4

PETN2/USB3TN4

PETP2/USB3TP4

RSVD

RSVD

PCIE_RCOMP

PCIE_IREF

HSW_ULT_DDR3L

PCIE USB

PCIE USB

11 OF 19

11 OF 19

AN8

USB2N0

AM8

USB2P0

AR7

USB2N1

AT7

USB2P1

AR8

USB2N2

AP8

USB2P2

AR10

USB2N3

AT10

USB2P3

AM15

USB2N4

AL15

USB2P4

AM13

USB2N5

AN13

USB2P5

AP11

USB2N6

AN11

USB2P6

AR13

USB2N7

AP13

USB2P7

G20

USB3RN1

H20

USB3RP1

USB3TN1

USB3TP1

USB3RN2

USB3RP2

USB3TN2

USB3TP2

USBRBIAS

USBRBIAS

RSVD

RSVD

OC0/GPIO40

OC1/GPIO41

OC2/GPIO42

OC3/GPIO43

C33

B34

E18

F18

B33

A33

AJ10

USBCOMP

AJ11

AN10

AM10

USBCOMP (R7F11): TIE TRACES TOGETHER CLOSE TO PINS,

WITH LENGTH NO LONGER THAN 450 MILS TO RESISTOR

AL3

USB_OC#01

AT1

USB_OC#23

AH2

USB_OC#45

AV3

USB_OC#67

USB_PN0 23

USB_PP0 23

USB_PN1 23

USB_PP1 23

USB_PN2 18

USB_PP2 18

USB_PN3 25

USB_PP3 25

USB_PN4 21

USB_PP4 21

USB_PN5 25

USB_PP5 25

USB_PN6 25

USB_PP6 25

USB_PN7 18

USB_PP7 18

USB3_RX1_N 23

USB3_RX1_P 23

USB3_TX1_N 23

USB3_TX1_P 23

USB3_RX2_N 23

USB3_RX2_P 23

USB3_TX2_N 23

USB3_TX2_P 23

R118 24_1%_04R118 24_1%_04

USB_OC#01 23

USB_OC#23 25

USB 3.0 PORT0

USB 3.0 PORT1

USB HUB or 3G PORT

TV TUNER PORT

BLUETOOTH

CCD

USB 2.0 PORT(W54/W94)

USB 2.0 PORT(W55/W95) or TOUCH PANEL (W94T)

USB 3.0 MAPING USB2.0

USB 3.0 P1

USB 3.0 P2

USB_OC#01

USB_OC#23

USB_OC#45

USB_OC#67

USB 2.0 P1

USB 2.0 P2

R96 10K_04R96 10K_04

R115 10K_04R115 10K_04

R64 10K_04R64 10K_04

R432 10K_04R432 10K_04

Schematic Diagrams

B.Schematic Diagrams

Sheet 8 of 39

Processor 7/7

3.3VA

HSW_ULT_DDR3L

eDP SIDEBAND

eDP SIDEBAND

PCIE

PCIE

HSW_ULT_DDR3L

9 OF 19

9 OF 19

DISPLAY

DISPLAY

DDPB_CTRLCLK

DDPB_CTRLDATA

DDPC_CTRLCLK

DDPC_CTRLDATA

DDPB_AUXN

DDPC_AUXN

DDPB_AUXP

DDPC_AUXP

DDPB_HPD

DDPC_HPD

EDP_HPD

B9

VGA_CTRLCLK

C9

VGA_CTRLDATA

D9

HDMI2_CTRLCLK

D11

HDMI2_CTRLDATA

C5

B6

DPC_AUX_N

B5

A6

DPC_AUX_P

C8

VGA_HPD

A8

HDMI2_HPD

D6

EDP_HPD

HDMI2_CTRLCLK 20

HDMI2_CTRLDATA 20

VGA_AUX_CH_N 16

VGA_AUX_CH_P 16

VGA_HPD 16

HDMI2_HPD 20

EDP_HPD 15,17

Title

Title

1.05V_USB3PLL10

VDD34,5,6,7,10,19,21,24,25,27,28,29,30,32

3.3VA2,4,5,6,7,10,27

3.3VS2,4,5,6,7,10,13,14,15,16,17,19,20,21,22,23,24,25,26,27,29,30,31

Title

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

A3

A3

Date: Sh eet

Date: Sh eet

Date: Sh eet

VGA_CTRLCLK

VGA_CTRLDATA

HDMI2_CTRLDATA

HDMI2_CTRLCLK

VGA_HPD

HDMI2_HPD

EDP_HPD

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

[08] HASWELL ULT PCIE,USB,eDP

[08] HASWELL ULT PCIE,USB,eDP

[08] HASWELL ULT PCIE,USB,eDP

6-7P-W5S27-005

6-7P-W5S27-005

6-7P-W5S27-005

6-71-W5S20-D03

6-71-W5S20-D03

6-71-W5S20-D03

U20I

B8

A9

C6

U6

P4

N4

N2

AD4

U7

L1

L3

R5

L4

U20I

EDP_BKLCTL

EDP_BKLEN

EDP_VDDEN

PIRQA/GPIO77

PIRQB/GPIO78

PIRQC/GPIO79

PIRQD/GPIO80

PME

GPIO55

GPIO52

GPIO54

GPIO51

GPIO53

3.3VS

R38 10K_04R38 10K_04

R379 10K_04R379 10K_04

R25 10K_04R25 10K_04

R374 10K_04R374 10K_04

R375 *10K_04R375 *10K_04

R368 10K_04R368 10K_04

R36 10K_04R36 10K_04

R367 10K_04R367 10K_04

INT_PIRQA#

INT_PIRQB#

INT_PIRQC#

INT_PIRQD#

PCH_GPIO53

PCH_GPIO54

PCH_GPIO55

PCH_GPIO52

BRIGHTNESS_EDP17

BKLEN_EDP15

NB_ENAVDD15

INT_PIRQA#

23

G_INT1

LAN_WAKEUP#19,24

R41 *0_04R41 *0_04

R44 *0_04R44 *0_04

R61 *0_04R61 *0_04

INT_PIRQB#

INT_PIRQC#

INT_PIRQD#

PCI_PME_N

PCH_GPIO55

PCH_GPIO52

PCH_GPIO54

PCH_GPIO51

PCH_GPIO53

R298 2.2K_04R298 2.2K_04

R297 2.2K_04R297 2.2K_04

R305 2.2K_04R305 2.2K_04

R314 2.2K_04R314 2.2K_04

R576 *100K_04R576 *100K_04

R313 *100K_04R313 *100K_04

R301 100K_04R301 100K_04

839Tuesday, October 29, 2013

839Tuesday, October 29, 2013

839Tuesday, October 29, 2013

3.3VS

1.0

1.0

1.0

of

of

of

Processor 7/7 B - 9

Page 9

Schematic Diagrams

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Power 1

SVID Signals

1.05VS

R372 75_1%_04R372 75_1%_04

R371 110_1%_04R371 110_1%_04

CAD Note: the PU resistors close to CPU

Sheet 9 of 39

Power 1

B.Schematic Diagrams

H_CPU_SVIDALRT#

H_CPU_SVIDDAT_R

VCC_SENSE31

H_CPU_SVIDALRT#31

H_CPU_SVIDCLK31

H_CPU_SVIDDAT31

H_VR_ENABLE31

H_VR_READY31

V_VCCDDQ

R74 100_04R74 100_04

VCCIN

R324 *0_04R324 *0_04

R80 0_04R80 0_04

VCCIOA_OUT

R377 43.2_1%_04R377 43.2_1%_04

R382 *10mil_04R382 *10mil_04

R370 *10mil_04R370 *10mil_04

R312 10K_04R312 10K_04

R87 150_1%_04R87 150_1%_04

1.05VS

R88 *10K_04R88 *10K_04

RESISTOR STUFFING OPTIONS ARE

PROVIDED FOR TESTING PURPOSES

PJ2

PJ2

*OPEN-5mm

*OPEN-5mm

1 2

SHORT

R317 0_04R317 0_04

R316 0_04R316 0_04

PWR_DEBUG_N

1.4A

V_VCCDDQ_R

VCCIN

VCC_SENSE

H_CPU_SVIDALRT#_R

H_CPU_SVIDCLK_R

H_CPU_SVIDDAT_R

H_VCCST_PWRGD

VR_EN

VR_READY

1.05VS

0.5A

VCCIN

L59

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

F59

N58

AC58

E63

AB23

A59

E20

AD23

AA23

AE59

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

AD60

AD59

AA59

AE60

AC59

AG58

U59

V59

AC22

AE22

AE23

AB57

AD57

AG57

C24

C28

C32

J58

U20L

U20L

RSVD

RSVD

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VCC

RSVD

RSVD

VCC_SENSE

RSVD

VCCIO_OUT

VCCIOA_OUT

RSVD

RSVD

RSVD

VIDALERT

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS

PWR_DEBUG

VSS

RSVD_TP

RSVD_TP

RSVD_TP

RSVD_TP

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

VCCST

VCCST

VCCST

VCC

VCC

VCC

VCC

VCC

VCC

HSW_ULT_DDR3L

HSW_ULT_DDR3L

HSW ULT POWER

HSW ULT POWER

12 OF 19

12 OF 19

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

PROCESSOR CORE POWER

VCCIN

VCCIN

32A

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

V_VCCDDQ

C314

C314

C65

C65

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C310

C310

C56

C56

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C318

C318

C43

C43

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C91

C91

10u_6.3V_X5R_06

10u_6.3V_X5R_06

C92

C92

10u_6.3V_X5R_06

10u_6.3V_X5R_06

C35

C35

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C34

C34

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C60

C60

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

4.2A

C95

C95

C97

C97

10u_6.3V_X5R_06

10u_6.3V_X5R_06

C96

C96

C98

C98

10u_6.3V_X5R_06

10u_6.3V_X5R_06

C52

C52

C64

C64

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C72

C72

C40

C40

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C46

C46

C77

C77

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C348

C348

C347

C347

*10u_6.3V_X5R_06

*10u_6.3V_X5R_06

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C342

C342

C341

C341

*10u_6.3V_X5R_06

*10u_6.3V_X5R_06

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C66

C66

C37

C37

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C69

C69

C39

C39

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C50

C50

C323

C323

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C345

C345

C343

C343

*22u_6.3V_X5R_08

*22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

*22u_6.3V_X5R_08

*22u_6.3V_X5R_08

C368

C368

C381

C381

22u_6.3V_X5R_08

22u_6.3V_X5R_08

330uF_2.5V_12m_6.6*6.6*4.2

330uF_2.5V_12m_6.6*6.6*4.2

*330uF_2.5V_12m_6.6*6.6*4.2

*330uF_2.5V_12m_6.6*6.6*4.2

+

+

+

+

C67

C67

C36

C36

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C71

C71

C38

C38

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C30

C30

C53

C53

22u_6.3V_X5R_08

22u_6.3V_X5R_08

1.05VS

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C47

C47

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C59

C59

C325

C325

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C68

C68

22u_6.3V_X5R_08

22u_6.3V_X5R_08

C326

C326

*330uF_2.5V_12m_6.6*6.6*4.2

*330uF_2.5V_12m_6.6*6.6*4.2

330uF_2.5V_12m_6.6*6.6*4.2

330uF_2.5V_12m_6.6*6.6*4.2

+

+

+

+

3.3V 1.05VS

R335

R335

1M_04

1M_04

61

D

D

G

G

1.05VS_PWRGD6,27,30

470p_50V_X7R_04

470p_50V_X7R_04

2

S

S

Q4A

Q4A

MTDK5S6R

C295

C295

MTDK5S6R

5

34

D

D

G

G

S

S

R327

R327

10K_04

10K_04

H_VCCST_PWRGD

Q4B

Q4B

MTDK5S6R

MTDK5S6R

B - 10 Power 1

VCCIOA_OUT2

V_VCCDDQ2,13,14,16,29

1.05VS2,4,5,7,10,30,31

VCCIN31

3.3V2,15,19,21,23,25,27,29,30

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

Title

Title

Title

[09] HASWELL ULT POWER 1

[09] HASWELL ULT POWER 1

[09] HASWELL ULT POWER 1

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

A3

6-7P-W5S27-005

6-71-W5S20-D03

6-71-W5S20-D03

Date: Sheet

Date: Sheet

Date: Sheet

6-71-W5S20-D03

939Monday, October 14, 2013

939Monday, October 14, 2013

939Monday, October 14, 2013

of

of

of

1.0

1.0

1.0

Page 10

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

1.838 A

1.74 A

0.042 A

0.041 A

0.041 A

0.114 A

0.057 A

0.2 A

0.063 A

0.018A

0.003 A

0.658A

0.031 A

0.063 A

0.0017A

VCCRTCEXT

PCH_VCCDSW

V3.3A_VCCPSUS

V1.05S_AXCK_LCPLL

V3.3A_VCCPSUS

V1.05S_AXCK_DCB

V1.05S_VCCSSCF100

V1.05S_VCCSSCF

1.05V_HSIO

VCC1_05

1.05V_HSIO

VCCSDIO

RTCVCC

1.05V_M

1.05VS

1.5VS

3.3VS

3.3VS

1.05VS

1.05VS

3.3VA

1.05VS

1.05VS

3.3VS

3.3VS

1.05VA

1.05VS

1.05DX_MODPHY

1.05VS

1.05DX_MODPHY

1.05DX_MODPHY

1.05VA

VDD3

1.05V_M

1.05V_M

1.05VA

1.05VA

1.05VS

3.3VA

3.3V_SPI

1.05V_USB3PLL

1.05V_SATA3PLL

1.05DX_MODPHY30

1.05VS2,4,5,7,9,30,31

VDD34,5,6,7,19,21,24,25,27,28,29,30,32

3.3VS2,4,5,6,7,8,13,14,15,16,17,19,20,21,22,23,24,25,26,27,29,30,31

1.05V_USB3PLL8

1.05V_SATA3PLL4

3.3V_SPI5

RTCVCC4,6

1.05VA4,30

1.05V_M30

3.3VA2,4,5,6,7,8,27

1.5VS29

Title

Size Document Number Rev

Date: Sheet

of

1.0

[10] HASWELL ULT POWER 2

A3

10 39Monday, October 28, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

6-7P-W5S27-005

6-71-W5S20-D03

Title

Size Document Number Rev

Date: Sheet

of

1.0

[10] HASWELL ULT POWER 2

A3

10 39Monday, October 28, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

6-7P-W5S27-005

6-71-W5S20-D03

Title

Size Document Number Rev

Date: Sheet

of

1.0

[10] HASWELL ULT POWER 2

A3

10 39Monday, October 28, 2013

ᙔ!Ϻ!ႝ!တ!!DMFWP!DP/

6-7P-W5S27-005

6-71-W5S20-D03

R47 *0_04R47 *0_04

L6 HCB1608KF-121T25L6 HCB1608KF-121T25

L51 HCB1608KF-121T25L51 HCB1608KF-121T25

USB2

THERMAL SENSOR

HSIO

HSW_ULT_DDR3L

USB3

OPI

RTC

GPIO/LPC

VRM

HDA

SERIAL IO

SUS OSCILLATOR

SPI

LPT LP POWER

CORE

13 OF 19

U20M

USB2

THERMAL SENSOR

HSIO

HSW_ULT_DDR3L

USB3

OPI

RTC

GPIO/LPC

VRM

HDA

SERIAL IO

SUS OSCILLATOR

SPI

LPT LP POWER

CORE

13 OF 19

U20M

VCCHDA

AH14

VCCTS1_5

J15

DCPSUS1

AD8

DCPSUS1

AD10

DCPSUSBYP

AG20

DCPSUSBYP

AG19

DCPSUS4

AB8

VCCASW

AE9

VCCASW

AF9

VCCASW

AG8

VCCSUS3_3

AH11

VCCRTC

AG10

DCPRTC

AE7

VCCSPI

Y8

VCCASW

AG14

VCCASW

AG13

VCC3_3

K16

VCC3_3

K14

VCCSDIO

T9

VCCSDIO

U8

DCPSUS3

J13

VCCAPLL

W21

VCCHSIO

K9

VCCHSIO

L10

VCCHSIO

M9

VCCAPLL

AA21

RSVD

Y20

VCCSATA3PLL

B11

VCCUSB3PLL

B18

VCC1_05

N8

VCC1_05

P9

VCC1_05

J11

VCC1_05

H11

VCC1_05

H15

VCC1_05

AE8

VCC1_05

AF22

VCCSUS3_3

AE21

VCCSUS3_3

AE20

RSVD

V21

RSVD

M20

RSVD

K18

VCCCLK

T21

VCCCLK

R21

VCCCLK

J17

VCCACLKPLL

A20

VCC3_3

W9

VCC3_3

V8

VCCDSW3_3

AH10

VCCSUS3_3

AC9

RSVD

AC20

VCCSUS3_3

AA9

DCPSUS2

AH13

VCC1_05

AG16

VCC1_05

AG17

VCCCLK

J18

VCCCLK

K19

C264 22 uF_6.3V_X5R_08C264 22 uF_6.3V_X5R_08

C54 1u_6.3V_X5R_04C54 1u_6.3V_X5R_04

L10 HCB1608KF-121T25L10 HCB1608KF-121T25

C29 1u_6.3V_X5R_04C29 1u_6.3V_X5R_04

C58 0.1u_10V_X5R_04C58 0.1u_10V_X5R_04

L12 HCB1608KF-121T25L12 HCB1608KF-121T25

L16 HCB1005KF-121T20L16 HCB1005KF-121T20

R31 *0_04R31 *0_04

C24 1u_6.3V_X5R_04C24 1u_6.3V_X5R_04

L19 HCB1608KF-121T25L19 HCB1608KF-121T25

L11 HCB1608KF-121T25L11 HCB1608KF-121T25

C44 1u_6.3V_X5R_04C44 1u_6.3V_X5R_04

C73 0.1u_10V_X5R_04C73 0.1u_10V_X5R_04 C62 *1u_6.3V_X5R_04C62 *1u_6.3V_X5R_04

C21 1u_6.3V_X5R_04C21 1u_6.3V_X5R_04

L9 HCB1608KF-121T25L9 HCB1608KF-121T25

L13 HCB1005KF-121T20L13 HCB1005KF-121T20

C26 *47uF_6.3V_X5R_08C26 *47uF_6.3V_X5R_08

C85 1u_6.3V_X5R_04C85 1u_6.3V_X5R_04

C33 1u_6.3V_X5R_04C33 1u_6.3V_X5R_04

R126 *0_04R126 *0_04

L40 HCB1608KF-121T25L40 HCB1608KF-121T25

R116 0_04R116 0_04

L4 HCB1608KF-121T25L4 HCB1608KF-121T25

L5 HCB1608KF-121T25L5 HCB1608KF-121T25

C273 *10u_6.3V_X5R_06C273 *10u_6.3V_X5R_06

C41 1u_6.3V_X5R_04C41 1u_6.3V_X5R_04

C61 0.1u_10V_X5R_04C61 0.1u_10V_X5R_04

C51 22u_6.3V_X5R_08C51 22u_6.3V_X5R_08

C94 *10u_6.3V_X5R_06C94 *10u_6.3V_X5R_06 L18 HCB1608KF-121T25L18 HCB1608KF-121T25

L15 HCB1005KF-121T20L15 HCB1005KF-121T20

C80 *10u_6.3V_X5R_06C80 *10u_6.3V_X5R_06

C57 1u_6.3V_X5R_04C57 1u_6.3V_X5R_04

C75 1u_6.3V_X5R_04C75 1u_6.3V_X5R_04

C89 0.1u_10V_X5R_04C89 0.1u_10V_X5R_04

C270 1u_6.3V_X5R_04C270 1u_6.3V_X5R_04

C45 1u_6.3V_X5R_04C45 1u_6.3V_X5R_04

R120 0_04R120 0_04

C48 *47uF_6.3V_X5R_08C48 *47uF_6.3V_X5R_08 L21 HCB1608KF-121T25L21 HCB1608KF-121T25

L8 HCB1608KF-121T25L8 HCB1608KF-121T25

C63 1u_6.3V_X5R_04C63 1u_6.3V_X5R_04

C87 0.1u_10V_X5R_04C87 0.1u_10V_X5R_04

R90 0_04R90 0_04

L42 HCB1608KF-121T25L42 HCB1608KF-121T25

C76 1u_6.3V_X5R_04C76 1u_6.3V_X5R_04

C14 *10u_6.3V_X5R_06C14 *10u_6.3V_X5R_06

C93 *1u_6.3V_X5R_04C93 *1u_6.3V_X5R_04

C25 22 uF_6.3V_X5R_08C25 22 uF_6.3V_X5R_08

C74 1u_6.3V_X5R_04C74 1u_6.3V_X5R_04

C79 1u_6.3V_X5R_04C79 1u_6.3V_X5R_04

C55 1u_6.3V_X5R_04C55 1u_6.3V_X5R_04

C78 1u_6.3V_X5R_04C78 1u_6.3V_X5R_04

C81 1u_6.3V_X5R_04C81 1u_6.3V_X5R_04

L7 HCB1608KF-121T25L7 HCB1608KF-121T25

C27 1u_6.3V_X5R_04C27 1u_6.3V_X5R_04

C32 *1u_6.3V_X5R_04C32 *1u_6.3V_X5R_04

C49 *1u_6.3V_X5R_04C49 *1u_6.3V_X5R_04

L3 HCB1608KF-121T25L3 HCB1608KF-121T25

C28 10u_6.3V_X5R_06C28 10u_6.3V_X5R_06

C31 22u_6.3V_X5R_08C31 22u_6.3V_X5R_08

L20 HCB1608KF-121T25L20 HCB1608KF-121T25

C42 0.1u_10V_X5R_04C42 0.1u_10V_X5R_04

R92 *0_04R92 *0_04

L14 HCB1005KF-121T20L14 HCB1005KF-121T20

C70 1u_6.3V_X5R_04C70 1u_6.3V_X5R_04

C292 1u_6.3V_X5R_04C292 1u_6.3V_X5R_04

Power 2

Schematic Diagrams

B.Schematic Diagrams

Sheet 10 of 39

Power 2

Power 2 B - 11

Page 11

Schematic Diagrams

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Power-VSS

HSW_ULT_DDR3L

HSW_ULT_DDR3L

U20N

U20N

A11

VSS

A14

VSS

A18

VSS

A24

VSS

A28

VSS

A32

VSS

A36

VSS

A40

VSS

A44

VSS

A48

VSS

A52

VSS

A56

VSS

AA1

VSS

AA58

VSS

AB10

VSS

AB20

VSS

AB22

VSS

AB7

VSS

AC61

VSS

AD21

VSS

AD3

VSS

AD63

VSS

AE10

VSS

AE5

VSS

AE58

VSS

AF11

VSS

AF12

VSS

AF14

Sheet 11 of 39

Power-VSS

B.Schematic Diagrams

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

DC_TEST_AY60

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

DC_TEST_B2

DC_TEST_A3_B3

DC_TEST_A61_B61

DC_TEST_B62_B63

DC_TEST_C1_C2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AY2

AY3

AY60

AY61

AY62

B2

B3

B61

B62

B63

C1

C2

14 OF 19

14 OF 19

U20Q

U20Q

DAISY_CHAIN_NCTF_AY2

DAISY_CHAIN_NCTF_AY3

DAISY_CHAIN_NCTF_AY60

DAISY_CHAIN_NCTF_AY61

DAISY_CHAIN_NCTF_AY62

DAISY_CHAIN_NCTF_B2

DAISY_CHAIN_NCTF_B3

DAISY_CHAIN_NCTF_B61

DAISY_CHAIN_NCTF_B62

DAISY_CHAIN_NCTF_B63

DAISY_CHAIN_NCTF_C1

DAISY_CHAIN_NCTF_C2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

HSW_ULT_DDR3L

HSW_ULT_DDR3L

17 OF 19

17 OF 19

DAISY_CHAIN_NCTF_A3

DAISY_CHAIN_NCTF_A4