Clevo W760S, W765S Schematics

Appendix B: Schematic Diagrams

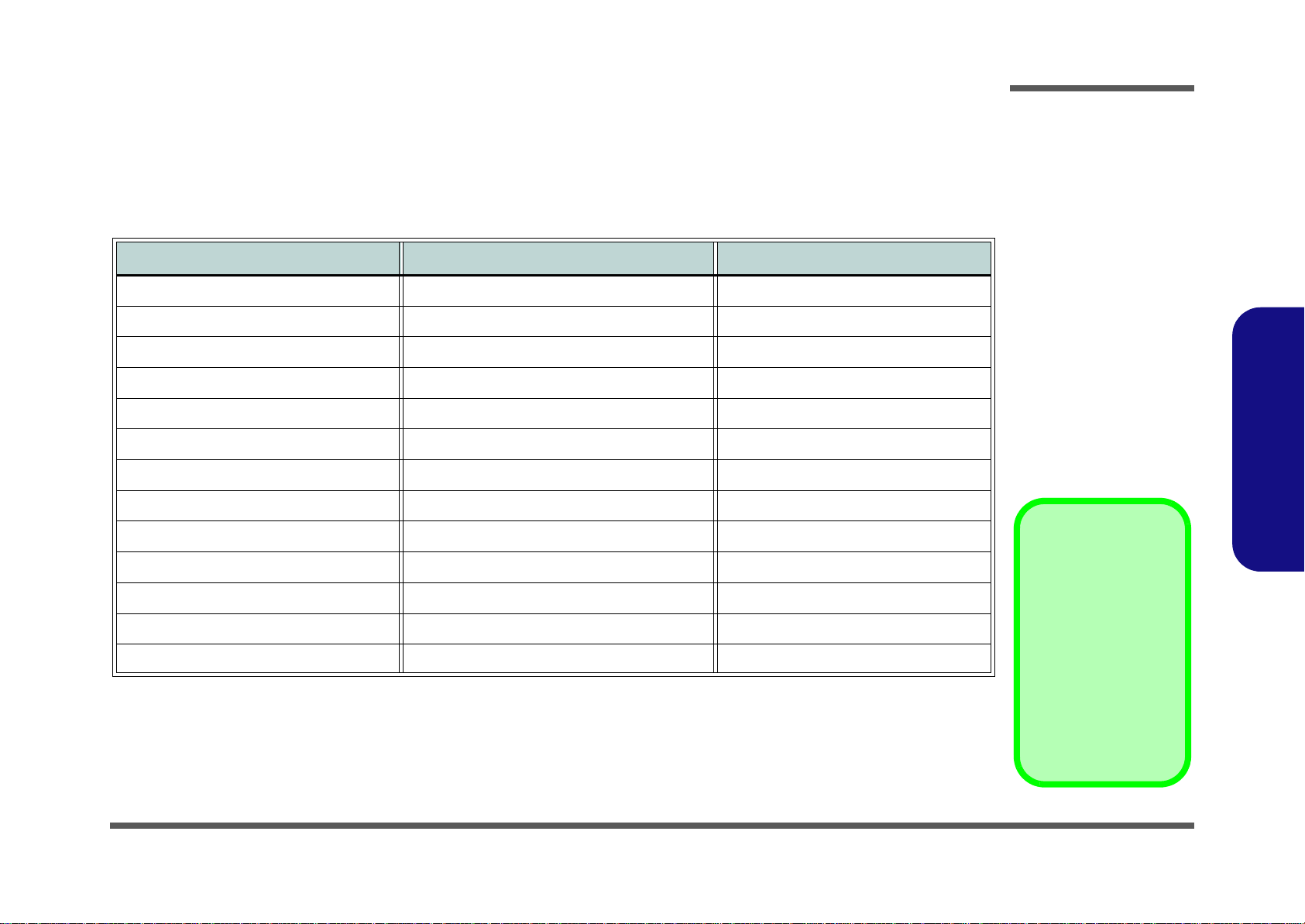

This appendix has circuit diagrams of the W760S/W765S notebook’s PCB’s. The following table indicates where to find

the appropriate schematic diagram.

Schematic Diagrams

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 968 PCI, IDE, MuTIOL, SPI 1/4 - Page B - 15 LED, PC Beep, TP, FP - Page B - 28

Penryn (Socket-P) 1/2 - Page B - 3 968 PCIE, LAN, GPIO 2/4 - Page B - 16 System/Ext-VGA Power - Page B - 29

Penryn (Socket-P) 2/2 - Page B - 4 968 USB SATA 3/4 - Page B - 17 AC-IN, Charger - Page B - 30

SiSM672 Host, PCIE 1/5 - Page B - 5 968 PWR, GND 4/4 - Page B - 18 VCORE - Page B - 31

SiSM672 DRAM 2/5 - Page B - 6 Clock Generator & Clock Buffer - Page B - 19 VDD3, VDD5) - Page B - 32

SiSM672 MuTIOL VGA 3/5 - Page B - 7 PHY Realtek 8201CL - Page B - 20 1.05VS, 1.2V, 1.5V - Page B - 33

SiSM672 PWR 4/5 - Page B - 8 KBC ITE8512E - Page B - 21 1.8V, 0.9VS - Page B - 34

SiSM672 GND 5/5 - Page B - 9 JMB385, Card Reader - Page B - 22 Click BD, Finger BD for M76 - Page B - 35

DDRII SO-DIMM - 1 - Page B - 10 Audio Codec ALC662 - Page B - 23 Multi Function Board - Page B - 36

DDRII SO-DIMM - 2 - Page B - 11 Audio AMP - Page B - 24 Audio Board - Page B - 37

SiS307ELV - Page B - 12 SATA HDD, PWR, LID - Page B - 25 Power Switch Board for M74 - Page B - 38

Panel, CRT - Page B - 13 Multi I/O, ODD, 3G, Click BD for M74 - Page B - 26 External ODD Board for W76 - Page B - 39

Inverter, Bluetooth, Fan - Page B - 14 New Card, Mini PCIE, USB - Page B - 27

Table B - 1

Schematic

Diagrams

B.Schematic Diagrams

Version Note

The schematic diagrams in this chapter

are based upon version 6-7P-M74SA-001.

If your mainboard (or

other boards) are a later version, please

check with the Service

Center for updated diagrams (if required).

B-1

Schematic Diagrams

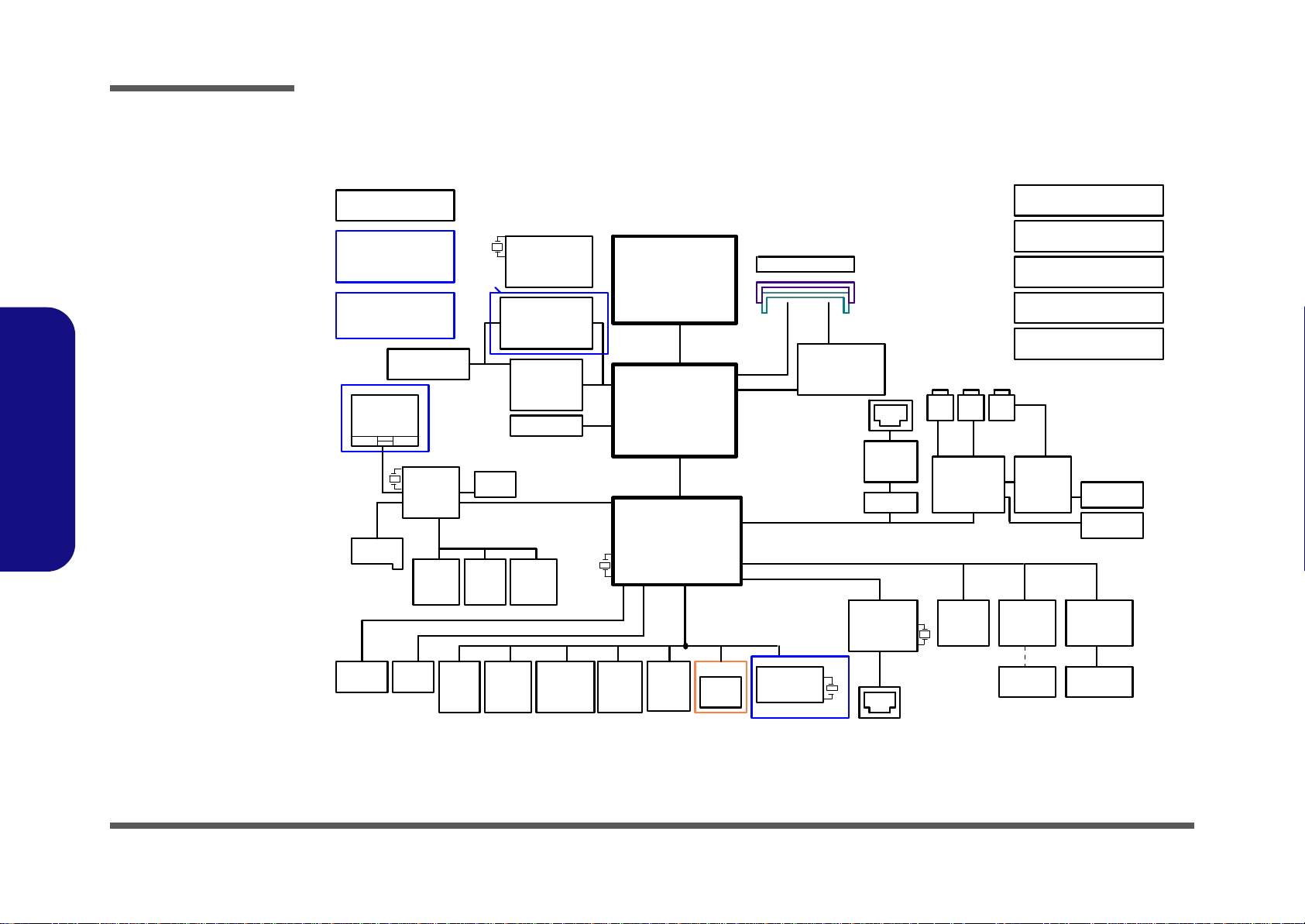

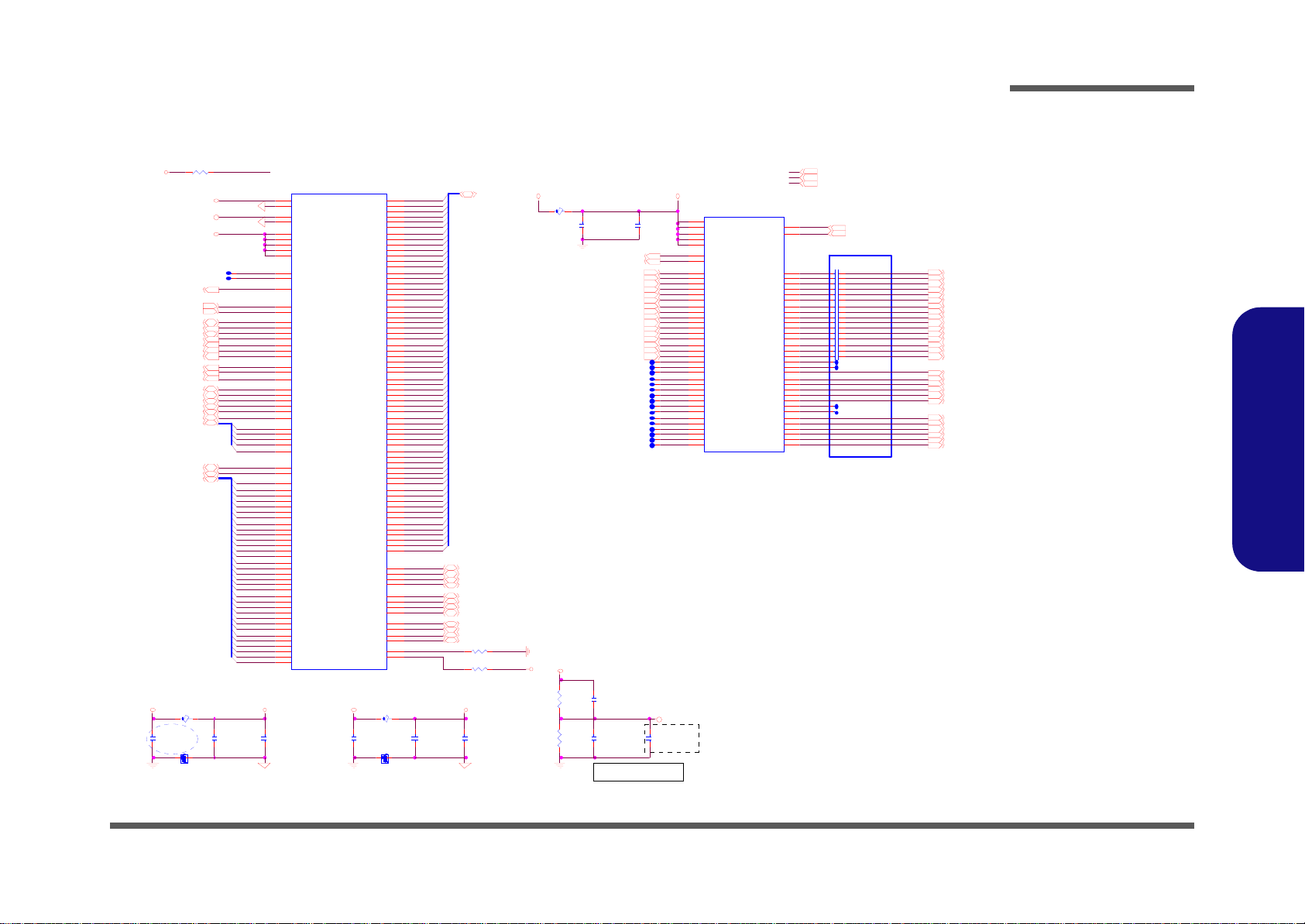

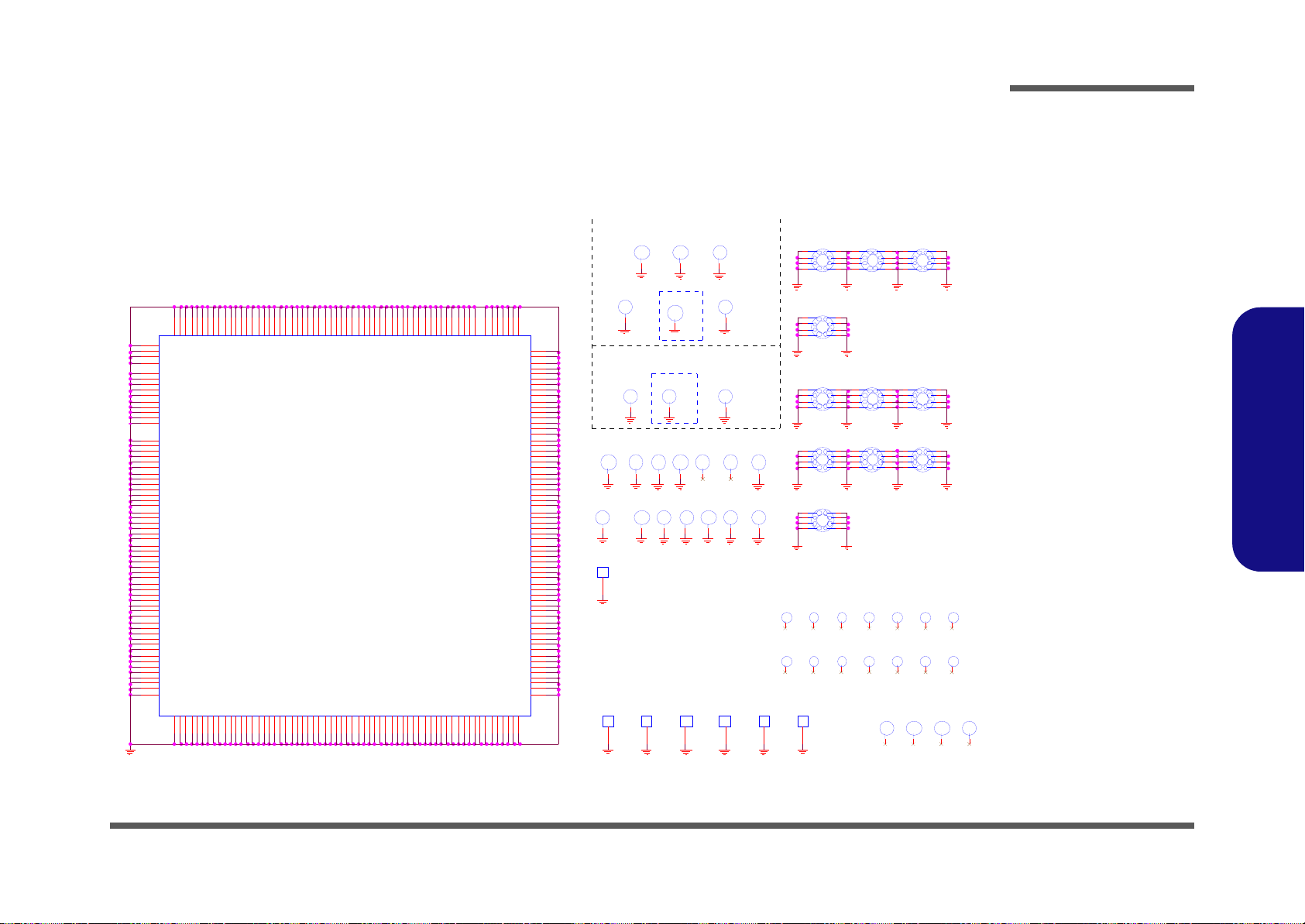

System Block Diagram

Sheet 1 of 38

System Block

Diagram

B.Schematic Diagrams

AC-IN,CHARGER

MULTI I/O BOARD

SPK_R, RJ-11

MODEM, CCD

Audio Board

USB, SPDIF, MIC IN

HEADPHONE

LCD CONNECTOR,

INVERTER

CLICK BOARD

TOUCH PAD

Synaptic

810602-1703

32.768 KHz

EC

ITE 8502E

128 pi ns LQ FP

14*14* 1.6mm

INT. K/B

THERMAL

SENSOR

F75383M

SATA HDD,

LID

SATA ODD

CLEVO M740S System Block Diagram

14 .31 8 MHz

Colck Generator

ICS9LPR600

56 pin s TSS OP

17.1*8.1*1.2m m

M76SU

EXTERNAL VGA

NV N10M-GE1

533 balls BGA

23*23*2.5mm

LVDS (TV)

SiS307ELV

16 9ba ll s B GA

13*13* 1.7mm

SPI

LPC

EC SMBUS

SMART

SMART

FAN

BATTERY

SATA I/II 3.0Gb/s

PATA-133

CCD

(USB7)

U SB6

CRT

3G CARD

Bluetooth

(O pt ion al )

33 MHz

32 .7 68K Hz

Intel Penryn

PROCESSOR

479 pins socket P

35*35*2.7mm

NORTH BRIDGE

SiSM672

852balls TEBGA

35*35*2.4mm

SOUTH BRIDGE

SiS968

570balls mBGA

27*27*2.5mm

(USB5)

(USB3)

FSB

66 7/8 00 MHz

MuTIOL 1G

USB2.0

480 Mbps

U SB & Pho ne

J ack B 'd

M emor y T erm ina tio n

Clock Buffer

ICS9P935

2 8p ins S SOP

17.1*8.1*1.2mm

5 33/6 67( /80 0) MHz

AZALIA LINK

PCIE

GMAC

F ING ER P RIN TE R B OA RD

USB2

FingerPrint

( Opt io na l)

1 2 MHz

DDRII

SO-DIMM0

SHEET 9

DDRII

SO-DIMM1

SHEET 10

AZALIA

MDC

MODULE

MDC CON

24 MHz

1 00 MHz

10/100M PH Y

RTL8201CL

48pins LQF P

9*9*1.7mm

RJ-45

RJ-11

25 MH z

SPD IF

OUT

MIC

IN

Azalia Codec

Realtek

ALC662

48p in s L QF P

9*9*1.6m m

New Card

SOCKET

(USB0)

SYSTEM POWER,GPU CORE

+VCORE

VDD3,VDD5,3.3V,5V

1.05VS,1.5V,1.2V

1.8V,0.9VS

HP

OUT

AUDIO AMP

TPA

6047A4

24 pin s TSS OP

9.8*6.4*1.2m m

Mini PCIE

SOCKET

(USB1)

MINI PCIE

GOLANUSB4

IN T S PK

IN T M IC

CARD READER

JMB385

7IN1

SOCKET

B - 2 System Block Diagram

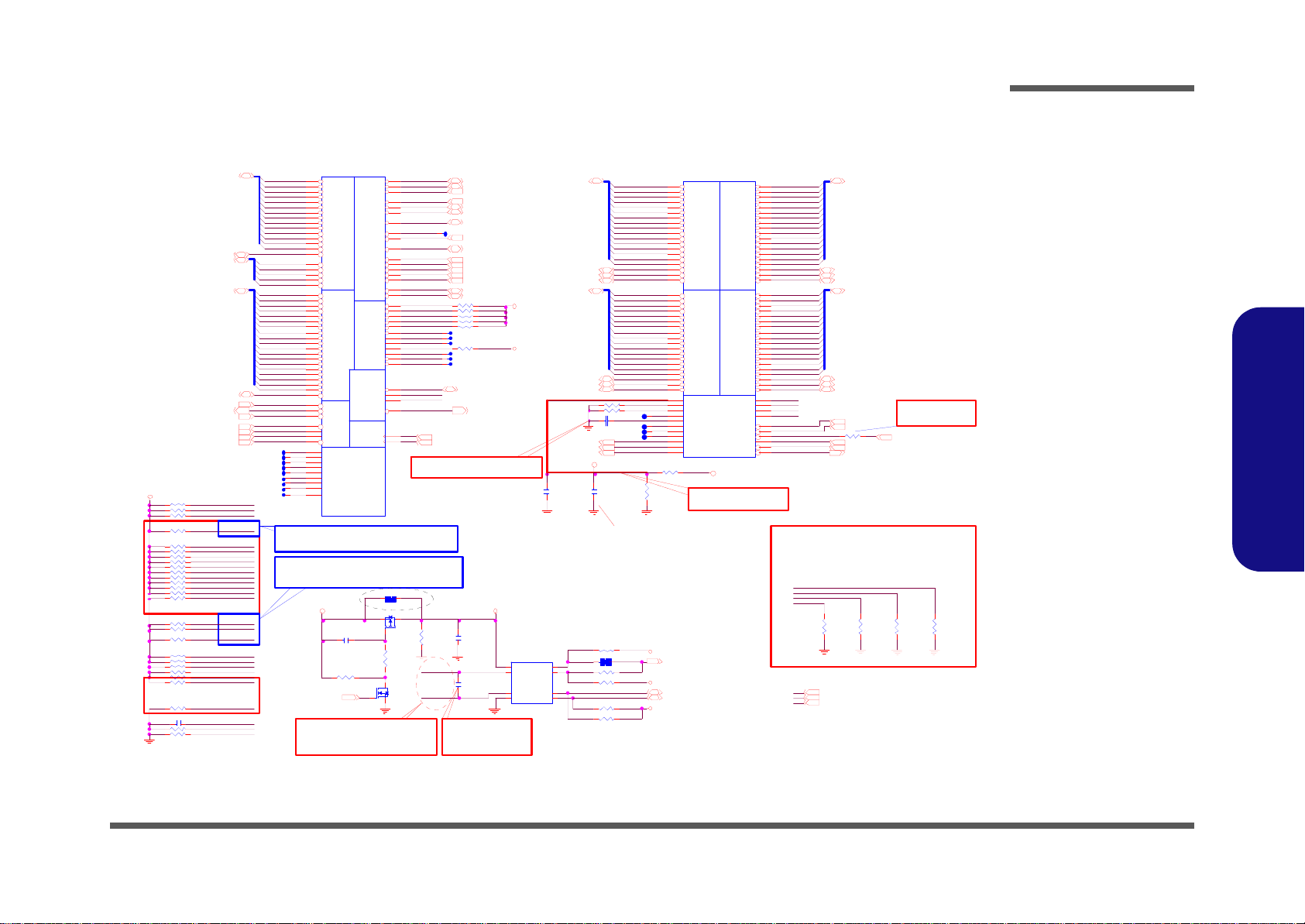

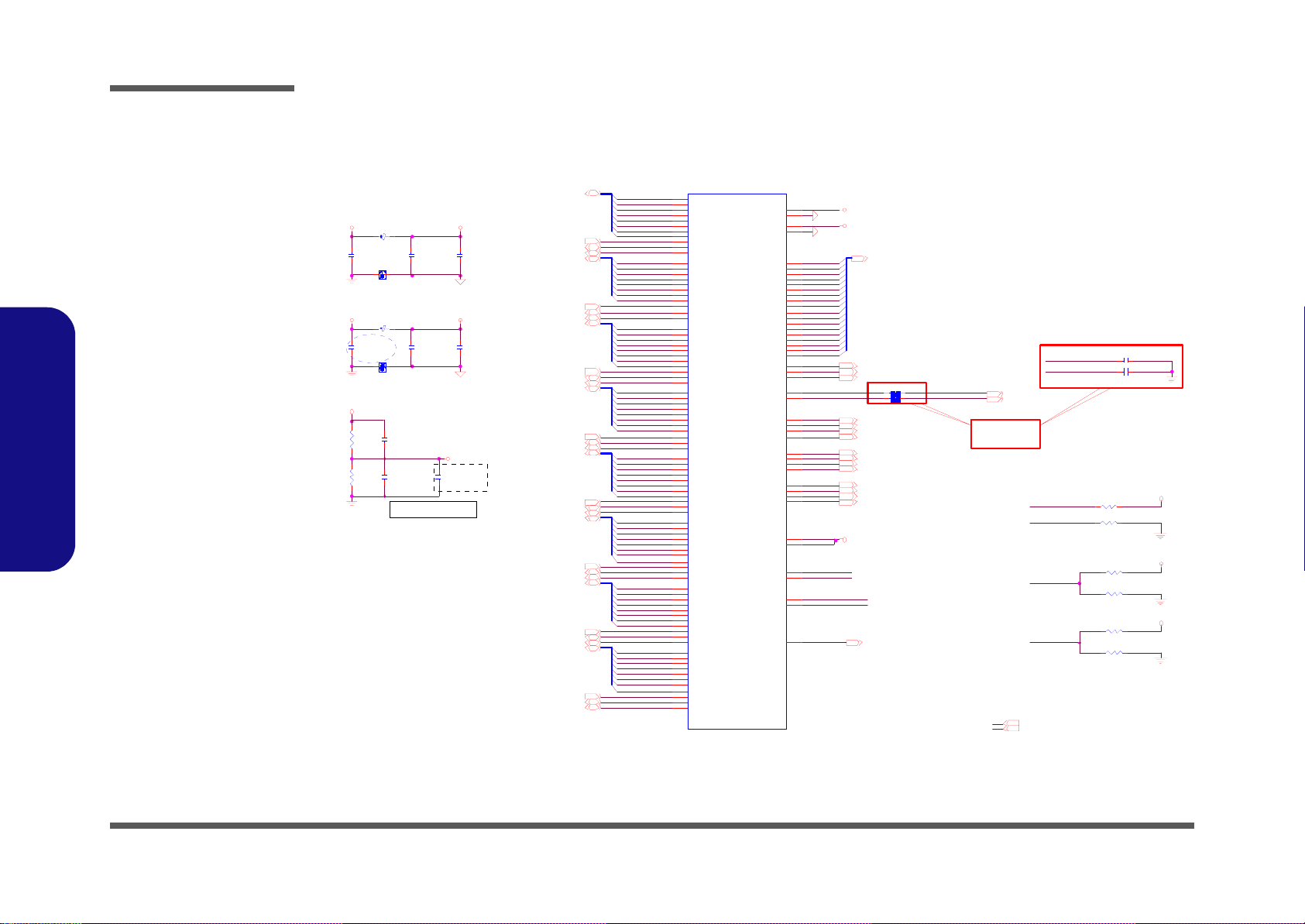

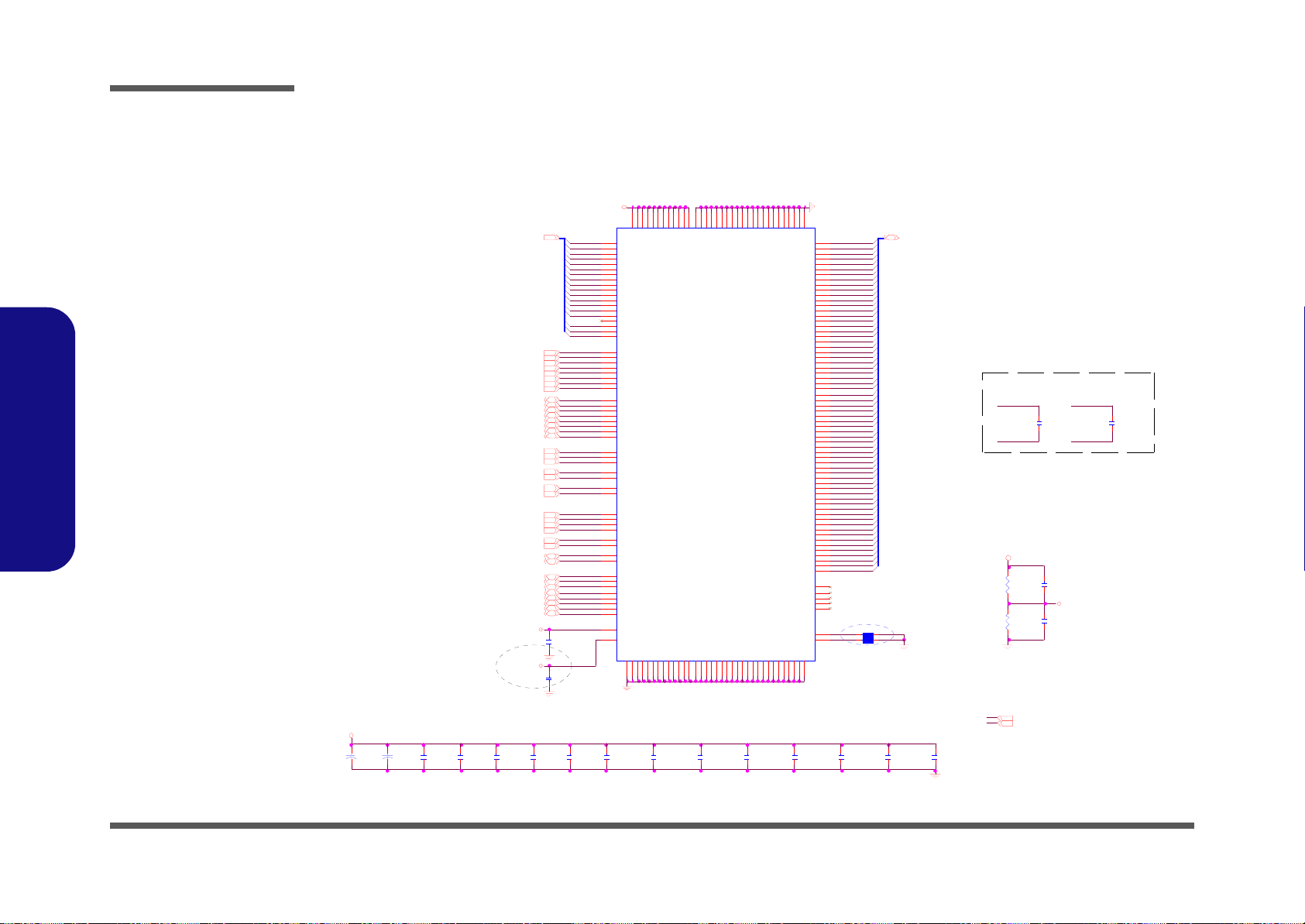

Penryn (Socket-P) 1/2

Schematic Diagrams

5 6_0 4

1. 05 V S

6 -14 -5 60 3B- 11 B

R 1 50 1 K _0 4

R 4 59 1 K _0 4

R 4 60 1 K _0 4

R149 68_04

R125 56_04

R134 56_04

R113 56_04

R131 56_04

R115 56_04

R117 56_04

R132 56_04

R122 56_04

R130 56_04

R114 56_04

R127 56_04

C PU to S B i nt er fac e

R108 *51_04

R116 *330_04

R106 *51_04

R147 56_04

R89 56_ 04

R 7 3 1 50 _1 %_ 04

R58 39.2_1%_04

R148 150_1%_04

R119 *56_04

If u sed M672 than

del R40 and add R42

R118 10_04

C154 100P_50V_04

R65 27.4_1%_04

R57 680 _04

H_RE Q#[4 :0]4

H_ADSTB# 04

H_A#[35:3]4

H_A# [35:3]4

H_ADSTB# 14

H_A2 0M#22

H_FERR#22

H_IGNNE#22

H_STPCLK#22

H_INTR22

H_NMI22

H_SMI#22

CPU_BSEL2

CPU_BSEL1

CPU_BSEL0

H_PROCH OT#

H_THRMTRIP #

H_FE RR#

H_ST PC LK#

H_INIT#

H_IGNN E#

H_SMI#

H_A2 0M#

H_CPUSL P#

H_NMI

H_INTR

H_DPSL P#

H_CPURST #

H_PW RGD

H_BR0 #

H_IERR#

H_PREQ#

H_TDI

H_TMS

H_DBR#

H_DPW R# _R

H_DPW R# _R

H_PW RGD

H_TCK

H_TRS T#

JSKT1A

J4

H_A# 3

H_A# 4

H_A# 5

H_A# 6

H_A# 7

H_A# 8

H_A# 9

H_A# 10

H_A# 11

H_A# 12

H_A# 13

H_A# 14

H_A# 15

H_A# 16

H_REQ #0

H_REQ #1

H_REQ #2

H_REQ #3

H_REQ #4

H_A# 17

H_A# 18

H_A# 19

H_A# 20

H_A# 21

H_A# 22

H_A# 23

H_A# 24

H_A# 25

H_A# 26

H_A# 27

H_A# 28

H_A# 29

H_A# 30

H_A# 31

H_A# 32

H_A# 33

H_A# 34

H_A# 35

H_A2 0M#

H_FE RR#

H_IG NNE#

H_ST PCLK#

H_IN TR

H_N MI

H_SMI#

Z0201

Z0202

Z0203

Z0204

Z0205

Z0206

Z0207

Z0208

Z0209

If P ROCHOT# is route d betwee n CPU, I MVP and MCH,

pull -up resi stor has to be 6 8 ohm ? 5%. If n ot

use, pull-up resisto r has to be 56 o hm ? 5%

IF U SED Desk top CPU, H_CPURS T#,H_PWR GD,H_BRD ,need

add pull hig h resist or

GROUP_ 0

A[3]#

L5

A[4]#

L4

A[5]#

K5

A[6]#

M3

A[7]#

N2

A[8]#

J1

A[9]#

N3

A[10 ]#

P5

A[11 ]#

P2

A[12 ]#

L2

A[13 ]#

P4

A[14 ]#

P1

A[15 ]#

R1

A[16 ]#

M1

ADSTB[0]#

K3

REQ[0]#

H2

REQ[1]#

K2

REQ[2]#

J3

REQ[3]#

L1

REQ[4]#

Y2

A[17 ]#

U5

A[18 ]#

R3

GROUP_1

A[19 ]#

W6

A[20 ]#

U4

A[21 ]#

Y5

A[22 ]#

U1

A[23 ]#

R4

A[24 ]#

T5

A[25 ]#

T3

A[26 ]#

W2

A[27 ]#

W5

A[28 ]#

Y4

A[29 ]#

U2

A[30 ]#

V4

A[31 ]#

W3

A[32 ]#

AA4

A[33 ]#

AB2

A[34 ]#

AA3

A[35 ]#

V1

ADSTB[1]#

A6

A20M#

A5

FER R#

C4

IGNNE#

D5

STPCL K#

C6

LI NT 0

B4

LI NT 1

A3

SMI#

M4

RSVD[01]

N5

RSVD[02]

T2

RSVD[03]

V3

RSVD[04]

B2

RSVD[05]

D2

RSVD[06]

D22

RSVD[07]

D3

RSVD[08]

F6

RSVD[09]

Penryn

3.3V

C180

*.01U_16V_X7R_04

R151

*330K_04

TH E R M_ R S T#27

L ayo ut N ote :

R out e H_ THE RM DA an d

H _TH ER MD C o n sa me la ye r.

1 0 m il t rac e on 10 m il sp ac in g.

ADDR

AD DR

ICH

THERMTRIP#

RESER VED

D05

XDP/I TP SIGNALS

THER MA L

PROCHOT#

TH E R MD A

THERMDC

H CLK

H1

ADS#

E2

BN R #

G5

BPRI#

H5

DEFE R#

F21

DRD Y#

E1

DBSY#

F1

BR0#

D20

IER R#

B3

INIT#

H4

LOCK#

CONTROL

C1

RESET#

F3

RS[0]#

F4

RS[1]#

G3

RS[2]#

G2

TR D Y #

G6

HIT#

E4

HITM#

AD4

BP M [ 0 ] #

AD3

BP M [ 1 ] #

AD1

BP M [ 2 ] #

AC4

BP M [ 3 ] #

AC2

PR D Y #

AC1

PREQ#

AC5

TC K

AA6

TD I

AB3

TDO

AB5

TM S

AB6

TR S T #

C20

DBR#

D21

A24

B25

C7

A22

BC L K [ 0]

A21

BC L K [ 1]

R 14 2 *2 0m il _s ho r t- N MN P

Q9

*NDS352AP_NL

DS

Z0 22 3

G

R15 2

*1 00 K_ 04

Z0 22 4

Q10

DS

*2N7002W

G

H_PRO CHOT#

H_THERMDA

H_THERMDC

H_THRMTRIP #

H_AD S# 4

H_BN R# 4

H_BPRI# 4

H_DE FER# 4

H_DRDY # 4

H_DB SY# 4

H_BR0 #

H_BR 0# 4

H_IERR #

H_INIT#

H_INIT# 22

H_LOCK# 4

H_CPU RST#

H_CP URST# 4

H_RS #0 4

H_RS #1 4

H_RS #2 4

H_TRDY# 4

H_HIT# 4

H_HITM# 4

R100 51_1%_04

H_BPM0#

R101 51_1%_04

H_BPM1#

H_BPM2#

R 6 6 5 1_ 1% _0 4

H_BPM3#

R 9 2 5 1_ 1% _0 4

H_PRD Y#

R 8 8 5 6_ 1% _0 4

H_PREQ#

H_TCK

H_TDI

R80 54.9_1%_04

H_TDO

H_TMS

H_TRST#

H_PROCHOT# 22

H_CL K_CPU 2 5

H_CL K_CPU# 25

La yo ut No te :

C6 86 C los e to TE ST 4 (Pi n AF 26)

R135

C163

*1 00 K_04

.1U_10V_ X7 R_04

H_THERMDA

C164

1000P_50V_04

H_THERMDC

L ayo ut N ote :

C los e to Th er ma l I C

A DM1 03 2 100 0p

F 753 83 M 220 0p

1. 0 5V S

1. 0 5V S

H_THRMTRIP # 2 2

V_THERM

Thermal IC

U7

1

VDD

2

D+

3

D-

5

GND

AS C 7 5 2 5

H_D#[63:0 ]4

H_DS TBN# 04

H_DSTBP#04

H_DINV# 04

H_D#[63:0 ]4

H_DS TBN# 14

H_DSTBP#14

H_DINV# 14

CPU_ BSEL 025

CPU_ BSEL 125

CPU_ BSEL 225

CPU_G TL REF

C553

1U _6 . 3V _X 5R _0 6

( Si S Recomm andation 200p)

Z02 25

4

TH E R M

Z02 26

6

AL E R T

7

SDATA

8

SCLK

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D# 14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

R458 * 1K_04

R126 * 1K_04

C554 * .1U_10V_X7R_04

CPU_ BSEL 0

CPU_ BSEL 1

CPU_ BSEL 2

C552

.01U_16V_X7R_04

R138 10K_04

R137 *10mil_short-NMNP

R155 * 0_04

R156 * 10K_04

R158 4.7K_04

R157 4.7K_04

JSKT1B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

9]#

D[

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

Z0210

TEST1

Z0211

D25

TEST2

Z0212

C24

TEST3

Z0213

AF26

TEST4

Z0214

AF 1

TEST5

Z0215

A26

TEST6

Z0216

C3

TEST7

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

Penryn

R407 1K_1% _04

CP U_ GRF E= 0. 7V

R40 6

La yo ut No te :

2K _ 1%_ 04

0. 5" m ax, Z o= 55 O hm s

V_THERM

THERM_ALERT# 27

VDD3

SMD_CPU_ THERM 2 7

SMC_CPU_ THERM 2 7

VDD3

MISC

DA TA GRP 0

DA TA GRP 1

1. 0 5V S

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

DATA GRP 2DA TA G RP 3

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

CO MP[0]

CO MP[1]

CO MP[2]

CO MP[3]

DPRST P#

DPSLP#

DPW R#

PWRGOOD

SLP#

Y22

H_D #32

AB 2 4

H_D #33

V2 4

H_D #34

V2 6

H_D #35

V2 3

H_D #36

T2 2

H_D #37

H_D #38

U25

U23

H_D #39

H_D #40

Y25

W2 2

H_D #41

Y23

H_D #42

H_D #43

W2 4

H_D #44

W2 5

AA 2 3

H_D #45

AA 2 4

H_D #46

AB 2 5

H_D #47

Y26

AA 2 6

U22

H_D #48

AE 2 4

AD 2 4

H_D #49

H_D #50

AA 2 1

AB 2 2

H_D #51

AB 2 1

H_D #52

H_D #53

AC 2 6

AD 2 0

H_D #54

H_D #55

AE 2 2

AF 2 3

H_D #56

AC 2 5

H_D #57

AE 2 1

H_D #58

H_D #59

AD 2 1

AC 2 2

H_D #60

AD 2 3

H_D #61H_DBR #

AF 2 2

H_D #62

AC 2 3

H_D #63

AE 2 5

AF 2 4

AC 2 0

COMP0

R26

COMP1

U26

COMP2

AA 1

Y1

COMP3

E5

H_DPSLP#

B5

H_DPW R#_R

D24

H_PW RGD

D6

H_CPUSL P#

D7

PS I #

AE 6

PSI#

Lay ou t not e:

COM P0 , COM P2 : 0.5 " Ma x, Zo =2 7.4 O hm s(2 0m il )

COM P1 , COM P3 : 0.5 " Ma x, Zo =5 5 O hm s(5 mi l)

Bes t es tim at e is 18 m ils w id e t ra ce fo r ou ter

lay er s and 1 4 mil s wi de tr ac e i f on in te rn al

lay er s.

COMP0

COMP1

COMP2

COMP3

H_D# [63 :0] 4

H_DST BN #2 4

H_DST BP#2 4

H_DINV# 2 4

H_D# [63 :0] 4

H_DST BN #3 4

H_DST BP#3 4

H_DINV# 3 4

H_DPRST P# 6,37

H_DPSL P# 6

R 1 20 *0 _0 4

H_PW RGD 4

H_CPUSL P # 22

PS I # 3 7

R74

R85

54.9_1%_04

2 7. 4 _1 % _ 04

1.05VS 3,4,6,7,24,39

3.3V 12,19,20,22,23,24 ,26,31,32,33,38,39,40

VDD 3 20,23,27,34,35,36,38,40

If used M672

tha n del R3

H_DP WR# 4

R441

5 4. 9 _1 % _ 04

R44 9

27 . 4_ 1% _0 4

Sheet 2 of 38

Penryn (Socket-P)

1/2

B.Schematic Diagrams

Penryn (Socket-P) 1/2 B - 3

Schematic Diagrams

Sheet 3 of 38

Penryn (Socket-P)

2/2

B.Schematic Diagrams

Penryn (Socket-P) 2/2

VCOR EVC O R E

AB2 0

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE1 0

AE1 2

AE1 3

AE1 5

AE1 7

AE1 8

AE2 0

AF9

AF1 0

AF1 2

AF1 4

AF1 5

AF1 7

AF1 8

AF2 0

Pow er Plan e

G21

V6

J6

K6

M6

J2 1

K21

M21

N21

N6

R21

R6

T2 1

T6

V21

W2 1

B26

Z0301

C26

AD6

H_V ID0

AF5

H_V ID1

AE5

H_V ID2

AF4

H_V ID3

AE3

H_V ID4

AF3

H_V ID5

AE2

H_V ID6

AF7

AE7

.

VCCSENSE

VSSSENSE

VC ORE

130m A

C846

1U_6.3V_X5R_06

D05 10/15

H_VID[6 :0] 3 7

R21

*15 mil_ s hort-NMNP

2A

1.05VS

Layout note:

Ne ar pi n B26

L12

H C B 16 08 K F - 12 1T 25

C161

C159

. 0 1U _1 6V _ X7 R _ 04

*10U_6.3V_X5R_08

VCC SEN SE 37

VSSSENSE 37

R22

Layout note:

*15mil_short-NMNP

Rou te V CCSENSE an d

VSS SENS E traces a t 27. 4

ohm s wi th 50 mils spac ing.

Pla ce P U and PD w ithin 1

inc h of CPU.

AA 1 0

AA 1 2

AA 1 3

AA 1 5

AA 1 7

AA 1 8

AA 2 0

AC10

AB 1 0

AB 1 2

AB 1 4

AB 1 5

AB 1 7

AB 1 8

JS KT 1C

A7

VCC[068]

V C C [ 00 1]

A9

VCC[069]

V C C [ 00 2]

A10

A12

A13

A15

A17

A18

A20

B10

B12

B14

B15

B17

B18

B20

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AB9

VCC[070]

V C C [ 00 3]

VCC[071]

V C C [ 00 4]

VCC[072]

V C C [ 00 5]

VCC[073]

V C C [ 00 6]

VCC[074]

V C C [ 00 7]

VCC[075]

V C C [ 00 8]

VCC[076]

V C C [ 00 9]

B7

VCC[077]

V C C [ 01 0]

B9

VCC[078]

V C C [ 01 1]

VCC[079]

V C C [ 01 2]

VCC[080]

V C C [ 01 3]

VCC[081]

V C C [ 01 4]

VCC[082]

V C C [ 01 5]

VCC[083]

V C C [ 01 6]

VCC[084]

V C C [ 01 7]

VCC[085]

V C C [ 01 8]

C9

VCC[086]

V C C [ 01 9]

VCC[087]

V C C [ 02 0]

VCC[088]

V C C [ 02 1]

VCC[089]

V C C [ 02 2]

VCC[090]

V C C [ 02 3]

VCC[091]

V C C [ 02 4]

VCC[092]

V C C [ 02 5]

D9

VCC[093]

V C C [ 02 6]

VCC[094]

V C C [ 02 7]

VCC[095]

V C C [ 02 8]

VCC[096]

V C C [ 02 9]

VCC[097]

V C C [ 03 0]

VCC[098]

V C C [ 03 1]

VCC[099]

V C C [ 03 2]

E7

VCC[100]

V C C [ 03 3]

E9

V C C [ 03 4]

VCCP[01]

V C C [ 03 5]

VCCP[02]

V C C [ 03 6]

VCCP[03]

V C C [ 03 7]

VCCP[04]

V C C [ 03 8]

VCCP[05]

V C C [ 03 9]

VCCP[06]

V C C [ 04 0]

VCCP[07]

V C C [ 04 1]

F7

VCCP[08]

V C C [ 04 2]

F9

VCCP[09]

V C C [ 04 3]

VCCP[10]

V C C [ 04 4]

VCCP[11]

V C C [ 04 5]

VCCP[12]

V C C [ 04 6]

VCCP[13]

V C C [ 04 7]

VCCP[14]

V C C [ 04 8]

VCCP[15]

V C C [ 04 9]

VCCP[16]

V C C [ 05 0]

V C C [ 05 1]

VCCA[01]

V C C [ 05 2]

VCCA[02]

V C C [ 05 3]

V C C [ 05 4]

VID[0]

V C C [ 05 5]

VID[1]

V C C [ 05 6]

VID[2]

V C C [ 05 7]

VID[3]

V C C [ 05 8]

VID[4]

V C C [ 05 9]

VID[5]

V C C [ 06 0]

VID[6]

V C C [ 06 1]

V C C [ 06 2]

V C C [ 06 3]

VCCSENSE

V C C [ 06 4]

V C C [ 06 5]

V C C [ 06 6]

VSSSENSE

V C C [ 06 7]

Penryn

1.5VS

JS KT 1D

A4

VSS[001]

VSS[08 2 ]

A8

VSS[08 3 ]

VSS[002]

A11

VSS[08 4 ]

VSS[003]

A14

VSS[08 5 ]

VSS[004]

A16

VSS[08 6 ]

VSS[005]

A19

VSS[08 7 ]

VSS[006]

A23

VSS[08 8 ]

VSS[007]

AF2

VSS[08 9 ]

VSS[008]

B6

VSS[09 0 ]

VSS[009]

B8

VSS[09 1 ]

VSS[010]

B11

VSS[09 2 ]

VSS[011]

B13

VSS[09 3 ]

VSS[012]

B16

VSS[09 4 ]

VSS[013]

B19

VSS[09 5 ]

VSS[014]

B21

VSS[09 6 ]

VSS[015]

B24

VSS[09 7 ]

VSS[016]

C5

VSS[09 8 ]

VSS[017]

C8

VSS[09 9 ]

VSS[018]

C11

VSS[10 0 ]

VSS[019]

C14

VSS[10 1 ]

VSS[020]

C16

VSS[10 2 ]

VSS[021]

C19

VSS[10 3 ]

VSS[022]

C2

VSS[10 4 ]

VSS[023]

C22

VSS[10 5 ]

VSS[024]

C25

VSS[025]

VSS[10 6 ]

D1

VSS[10 7 ]

VSS[026]

D4

VSS[10 8 ]

VSS[027]

D8

VSS[10 9 ]

VSS[028]

D11

VSS[11 0 ]

VSS[029]

D13

VSS[11 1 ]

VSS[030]

D16

VSS[11 2 ]

VSS[031]

D19

VSS[11 3 ]

VSS[032]

D23

VSS[11 4 ]

VSS[033]

D26

VSS[11 5 ]

VSS[034]

E3

VSS[11 6 ]

VSS[035]

E6

VSS[11 7 ]

VSS[036]

E8

VSS[11 8 ]

VSS[037]

E11

VSS[11 9 ]

VSS[038]

E14

VSS[12 0 ]

VSS[039]

E16

VSS[12 1 ]

VSS[040]

E19

VSS[12 2 ]

VSS[041]

E21

VSS[12 3 ]

VSS[042]

E24

VSS[12 4 ]

VSS[043]

F5

VSS[12 5 ]

VSS[044]

F8

VSS[12 6 ]

VSS[045]

F11

VSS[12 7 ]

VSS[046]

F13

VSS[12 8 ]

VSS[047]

F16

VSS[12 9 ]

VSS[048]

F19

VSS[13 0 ]

VSS[049]

F2

VSS[13 1 ]

VSS[050]

F22

VSS[051]

VSS[13 2 ]

F25

VSS[052]

VSS[13 3 ]

G4

VSS[053]

VSS[13 4 ]

G1

VSS[054]

VSS[13 5 ]

G2 3

VSS[055]

VSS[13 6 ]

G2 6

VSS[056]

VSS[13 7 ]

H3

VSS[057]

VSS[13 8 ]

H6

VSS[058]

VSS[13 9 ]

H21

VSS[059]

VSS[14 0 ]

H24

VSS[060]

VSS[14 1 ]

J2

VSS[061]

VSS[14 2 ]

J5

VSS[062]

VSS[14 3 ]

J2 2

VSS[063]

VSS[14 4 ]

J2 5

VSS[064]

VSS[14 5 ]

K1

VSS[065]

VSS[14 6 ]

K4

VSS[066]

VSS[14 7 ]

K23

VSS[067]

VSS[14 8 ]

K26

VSS[068]

VSS[14 9 ]

L3

VSS[069]

VSS[15 0 ]

L6

VSS[070]

VSS[15 1 ]

L2 1

VSS[071]

VSS[15 2 ]

L2 4

VSS[072]

VSS[15 3 ]

M2

VSS[073]

VSS[15 4 ]

M5

VSS[074]

VSS[15 5 ]

M2 2

VSS[075]

VSS[15 6 ]

M2 5

VSS[076]

VSS[15 7 ]

N1

VSS[077]

VSS[15 8 ]

N4

VSS[078]

VSS[15 9 ]

N23

VSS[079]

VSS[16 0 ]

N26

VSS[080]

VSS[16 1 ]

P3 A25

VSS[08 1 ] VSS[16 2]

VSS[16 3 ]

Pe n r y n

Check cap for santa rosa platform

VCORE

C564

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF25

.

10U _6.3V_X5R_08

VCORE

C50

10U _6.3V_X5R_08

VCORE

C59

10U _6.3V_X5R_08

VCORE

C584

1U_6.3V_X5R _06

VCORE

C113

1U_6.3V_X5R _06

VCORE

C583

.1U_ 10V_X7R _04

1.05VS

C574

+

150U_4V_B2

1.05VS

C126

.1U_ 10V_X7R _04

PLACE NEAR C PU

C57 7

10 U _ 6. 3 V _X 5R _0 8

C65

10 U _ 6. 3 V _X 5R _0 8

C57 5

10 U _ 6. 3 V _X 5R _0 8

C12 4

*1U_6.3V_X5R_06

C10 0

1U_6.3V_X5R_06

C85

.1U_1 0V_ X7R_ 04

C86

.1U_1 0V_ X7R_ 04

5/10

C11 6

.1U_1 0V_ X7R_ 04

C95

10U_6.3V_X5R_08

C123

*1 0U _6 . 3V _ X5 R _ 08

6-07-10611-7C0

C118

10U_6.3V_X5R_08

C128

1U_6 .3V_X5R_06

C88

*1 U _ 6. 3 V _X 5R _0 6

C572

.1U_10V_X7R_04

C111

.1U_10V_X7R_04

C77

.1U_10V_X7R_04

C565

*10U_6.3V_X5R _08

C61

10U_6.3V_X5R_08

C566

10U_6.3V_X5R_08

C49

1U_6.3V_X5R_06

C585

1U_6.3V_X5R_06

C581

.1U_10V_X7 R_04

P LACE NE AR CPU

C46

.1U_10V_X7 R_04

C141

.1U_10V_X7 R_04

1.05 VS 2,4,6,7,24,39

1.5VS 6,33,35

VCORE 37

C568

10 U _ 6. 3 V _X 5 R _0 8

C593

10 U _ 6. 3 V _X 5 R _0 8

C146

10 U _ 6. 3 V _X 5 R _0 8

C51

1U _6 . 3V _ X5 R _ 06

C68

1U _6 . 3V _ X5 R _ 06

C582

.1U _10V_ X7R_ 04

C62

.1U _10V_ X7R_ 04

C130

*.1U_10V_X7R_04

D05 10/15

C580

10U _6.3V_X5R_08

C594

*10U_6.3V_X5R_08

C129

10U _6.3V_X5R_08

C75

1U_6.3V_X5R _06

C140

1U_6.3V_X5R _06

C155

.1U_ 10V_X7R _04

C67

.1U_ 10V_X7R _04

B - 4 Penryn (Socket-P) 2/2

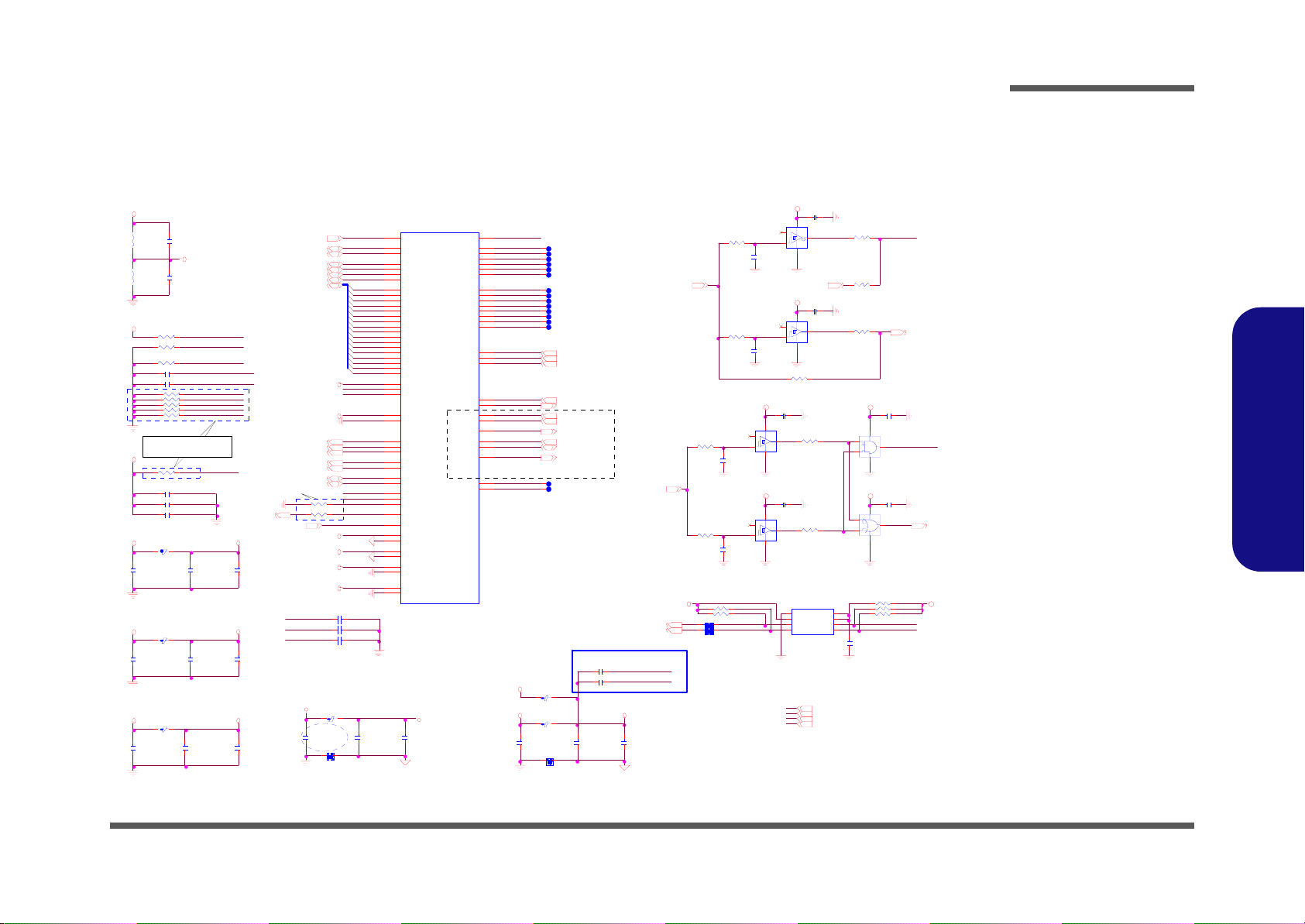

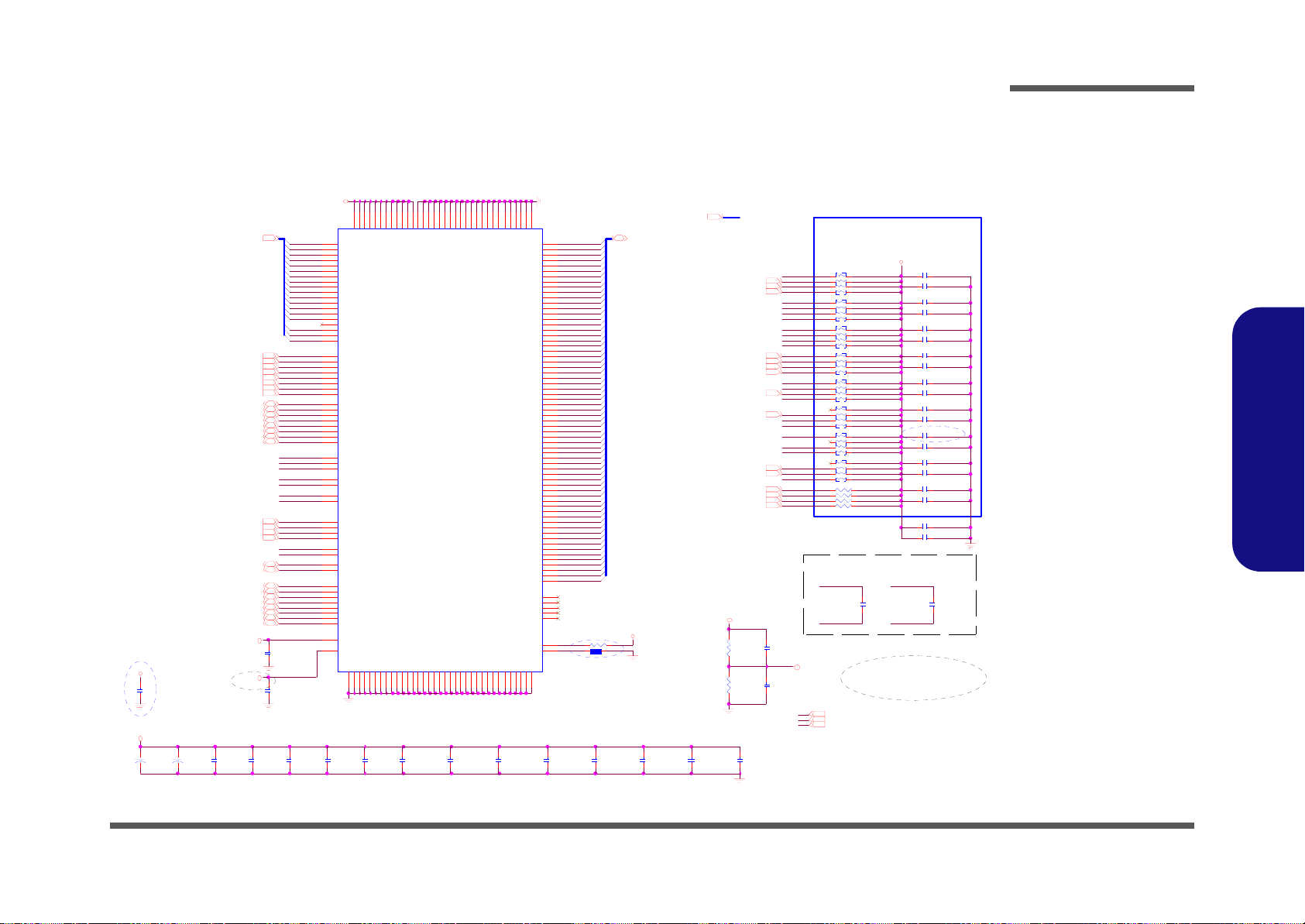

SiSM672 Host, PCIE 1/5

Schematic Diagrams

D05 10/15

1. 0 5V S

1.8VS

R196 *56_04

C1XAVDD

C4XAVDD

NB_GTLREF

H_D PWR #2

H_CL K _NB25

H_CL K _NB#25

H_LO CK#2

H_DEFER#2

H _T RDY#2

H_CPURST#2

H_P W RGD2

H_BPRI#2

H_B R0#2

H_RS #02

H_RS #12

H_RS #22

H_ADS#2

H_H ITM#2

H_HIT #2

H_D RDY#2

H _DBSY#2

H_B NR#2

H_R EQ #[4:0]2

H_AD S TB# 02

H_AD S TB# 12

H_A #[3 5:3]2

L65 HCB1005KF-121T20

C598

*10U_10V_08

NC10 NC_ 04

C605

.1U_10 V_X7R _04

NB_ PC REQ#

U32C

B16

C1XAVDD

C17

C1XAVSS

C4XAVSS

NB_ PC REQ#

Z04 01

H_RE Q#0

H_RE Q#1

H_RE Q#2

H_RE Q#3

H_RE Q#4

H_A #3

H_A #4

H_A #5

H_A #6

H_A #7

H_A #8

H_A #9

H_A #1 0

H_A #1 1

H_A #1 2

H_A #1 3

H_A #1 4

H_A #1 5

H_A #1 6

H_A #1 7

H_A #1 8

H_A #1 9

H_A #2 0

H_A #2 1

H_A #2 2

H_A #2 3

H_A #2 4

H_A #2 5

H_A #2 6

H_A #2 7

H_A #2 8

H_A #2 9

H_A #3 0

H_A #3 1

H_A #3 2

H_A #3 3

H_A #3 4

H_A #3 5

C1XAVSS

A17

C4XAVDD

B18

C4XAVSS

W24

HVREF

U24

HVREF

R24

HVREF

N24

HVREF

L21

HVREF

R34

PCREQ#

P32

EDRD Y#

E21

NC2 (DPW R#)

F18

CPUC LK

G1 8

CPUC LK#

L32

HLOCK#

P30

DEFE R#

P31

HTRDY#

F21

CPUR ST#

P28

CPUPW RG D

N30

BPRI#

P33

BREQ0#

K34

RS0 #

M3 1

RS1 #

K33

RS2 #

M3 4

ADS#

N34

HITM#

N32

HIT#

M3 3

DRD Y#

L34

DBSY#

M3 2

BNR#

T34

HREQ 0#

R30

HREQ 1#

HREQ 2#

HREQ 3#

HREQ 4#

HASTB0#

HASTB1#

HA3 #

HA4 #

HA5 #

HA6 #

HA7 #

HA8 #

HA9 #

HA1 0#

HA1 1#

HA1 2#

HA1 3#

HA1 4#

HA1 5#

HA1 6#

HA1 7#

HA1 8#

HA1 9#

HA2 0#

HA2 1#

HA2 2#

HA2 3#

HA2 4#

HA2 5#

HA2 6#

HA2 7#

HA2 8#

HA2 9#

HA3 0#

HA3 1#

HA3 2#

HA3 3#

HA3 4#

HA3 5#

SiSM672

Ho st

R29

R32

P34

U34

AA34

T32

T28

T31

T33

T30

U32

U30

V34

U29

V33

V32

V28

V31

W34

Y33

W32

V30

W30

Y34

Y28

W29

Y32

Y30

Y31

AA32

AA30

AA29

AB33

AB34

AB32

AC34

AB30

AB31

C1XAVDD 1.8VS C4XAVDD

C606

.01U_16V_X7R_04

C1XAVSS

N29

H_D# 0

HD0#

M30

H_D# 1

HD1#

M28

H_D# 2

HD2#

L30

H_D# 3

HD3#

L29

H_D# 4

HD4#

K28

H_D# 5

HD5#

K31

H_D# 6

HD6#

K30

H_D# 7

HD7#

H31

H_D# 8

HD8#

G34

H_D# 9

HD9#

H32

G32

K32

F34

F33

F32

H28

J30

H30

G29

J29

G30

F30

D33

D34

B32

B33

C34

D31

A32

A31

C31

B30

C30

A30

D28

G28

C29

C28

E28

E27

C27

G26

E26

D26

B26

A26

C26

G22

C24

A25

B24

C25

A24

E23

E25

G24

D22

C22

E22

C23

A23

A22

B22

J32

E32

F27

F23

H33

E31

B28

D24

H34

D32

A28

E24

A21

C21

H_D# 10

H_D# 11

H_D# 12

H_D# 13

H_D# 14

H_D# 15

H_D# 16

H_D# 17

H_D# 18

H_D# 19

H_D# 20

H_D# 21

H_D# 22

H_D# 23

H_D# 24

H_D# 25

H_D# 26

H_D# 27

H_D# 28

H_D# 29

H_D# 30

H_D# 31

H_D# 32

H_D# 33

H_D# 34

H_D# 35

H_D# 36

H_D# 37

H_D# 38

H_D# 39

H_D# 40

H_D# 41

H_D# 42

H_D# 43

H_D# 44

H_D# 45

H_D# 46

H_D# 47

H_D# 48

H_D# 49

H_D# 50

H_D# 51

H_D# 52

H_D# 53

H_D# 54

H_D# 55

H_D# 56

H_D# 57

H_D# 58

H_D# 59

H_D# 60

H_D# 61

H_D# 62

H_D# 63

NB_ COMP

NB_ COMP#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

DBI0#

DBI1#

DBI2#

DBI3#

H DSTBN0#

H DSTBN1#

H DSTBN2#

H DSTBN3#

HDSTB P0#

HDSTB P1#

HDSTB P2#

HDSTB P3#

HPCO MP

HNCO MP

L1 8 HC B 10 0 5K F - 1 21 T2 0

C210

10U_10V_08

NC2 NC_04

C23 0

.1U_10 V_X7R _04

H_D#[63:0] 2

H_DINV # 0 2

H_DINV # 1 2

H_DINV # 2 2

H_DINV # 3 2

H_DS TBN #0 2

H_DS TBN #1 2

H_DS TBN #2 2

H_DS TBN #3 2

H_DS TBP# 0 2

H_DS TBP# 1 2

H_DS TBP# 2 2

H_DS TBP# 3 2

R178 110_1%_06

R183 10_1%_04

C240

. 01 U _ 16 V _X 7R _0 4

C4XAVSS

HCB1005KF-121T20

1. 0 5V S

1.05VS

L23

R195

75_1%_04

R192

150_1%_04

77mA

C260

.01U_16V_X7R_04

PCIE_WAKE#23 , 3 3

PCI_INT#A6,21

PE 0 R X 012

PE 0 R X 0#12

PE 0 R X 112

PE 0 R X 1#12

PE 0 R X 212

PE 0 R X 2#12

PE 0 R X 312

PE 0 R X 3#12

PE 0 R X 412

PE 0 R X 4#12

PE 0 R X 512

PE 0 R X 5#12

PE 0 R X 612

PE 0 R X 6#12

PE 0 R X 712

PE 0 R X 7#12

C264

. 0 1U _1 6V _ X 7R _ 04

NB _GTL RE F=0.7V

C273

. 0 1U _1 6V _ X 7R _ 04

P lac e un der M6 71 MX

so lde r si de

NB_PCIE_ 1.2VS1.2VS

C262

.1U_10V_X7R_04

Z0402

Z0403

Z0404

Z0405

Z0406

Z0407

Z0408

Z0409

Z0410

Z0411

Z0412

Z0413

Z0414

Z0415

Z0416

Z0417

NB_G TL REF

C255

.1U_10V_X7R_ 04

U32D

P7

PCIEAVDD

R7

PCIEAVDD

T7

PCIEAVDD

U7

PCIEAVDD

V7

PCIEAVDD

D7

PME#

G1 6

INTX#

E4

PERP0

E5

PERN0

F1

PERP1

G1

PERN1

H3

PERP2

H2

PERN2

H1

PERP3

J1

PERN3

K1

PERP4

K2

PERN4

L1

PERP5

M1

PERN5

N1

PERP6

N2

PERN6

P1

PERP7

R1

PERN7

T1

PERP8

T2

PERN8

U1

PERP9

V1

PETN9(HDVBN2)

PERN9

W1

PERP10

PETP1 0(HDVBP1)

W2

PETN10(HD VBN 1)

PERN1 0

Y1

PERP11

PETP1 1(HDVBP0)

AA1

PETN11(HD VBN 0)

PERN1 1

AB1 AB6

PERP12 PETP1 2

AB2

PERN1 2

AC 1

PETP1 3(HDVAP2)

PERP13

AD 1

PETN13(HD VAN 2)

PERN1 3

AE1

PETP1 4(HDVAP1)

PERP14

AE2

PETN14(HD VAN 1)

PERN1 4

AF1

PETP1 5(HDVAP0)

PERP15

AG 1

PETN15(HD VAN 0)

PERN1 5

SiSM672

REFCL K +

REFCLK-

PETP0

PETN 0

PETP1

PETN 1

PETP2

PETN 2

PETP3

PETN 3

PETP4

PETN 4

PETP5

PETN 5

PCIE

PETP6

PETN 6

PETP7

PETN 7

PETP8

PETN 8

PETP9 (HDVBP2)

PETN12

T5

T4

G6

H6

G4

G5

J6

K6

J4

J5

L6

M6

M4

M5

P6

R6

P4

P5

V6

W6

W4

W5

Y6

AA6

AA4

AA5

AC6

AC4

AC5

AD6

AE6

AE4

AE5

1 . 05 V S 2,3 , 6,7 , 24 , 39

1.2VS 7,35

1.8VS 5,6,7,11,13,14,15,17,19,21,22,23,24,25,35

PCIE_CLK_NB 25

PCIE_CLK_NB# 25

C 6 16 * . 1U _ 1 0V _ X7 R _ 04

Z0438

C 6 18 * . 1U _ 1 0V _ X7 R _ 04

Z0439

C 6 15 * . 1U _ 1 0V _ X7 R _ 04

Z0440

C 6 17 * . 1U _ 1 0V _ X7 R _ 04

Z0441

C 6 20 * . 1U _ 1 0V _ X7 R _ 04

Z0442

C 6 22 * . 1U _ 1 0V _ X7 R _ 04

Z0443

C 6 19 * . 1U _ 1 0V _ X7 R _ 04

Z0444

C 6 21 * . 1U _ 1 0V _ X7 R _ 04

Z0445

C 6 23 * . 1U _ 1 0V _ X7 R _ 04

Z0446

C 6 24 * . 1U _ 1 0V _ X7 R _ 04

Z0447

C 6 25 * . 1U _ 1 0V _ X7 R _ 04

Z0448

C 6 27 * . 1U _ 1 0V _ X7 R _ 04

Z0449

C 6 28 * . 1U _ 1 0V _ X7 R _ 04

Z0450

C 6 30 * . 1U _ 1 0V _ X7 R _ 04

Z0451

C 6 29 * . 1U _ 1 0V _ X7 R _ 04

Z0452

C 6 31 * . 1U _ 1 0V _ X7 R _ 04

Z0453

Z0454

Z0455

Z0462

Z0463

INT ERNAL VGA( M740S ) : R

EXT ERNAL VGA ( M760SU ) : 0 .1U

PE0TX0 12

PE0TX0# 12

PE0TX1 12

PE0TX1# 12

PE0TX2 12

PE0TX2# 12

PE0TX3 12

PE0TX3# 12

PE0TX4 12

PE0TX4# 12

PE0TX5 12

PE0TX5# 12

PE0TX6 12

PE0TX6# 12

PE0TX7 12

PE0TX7# 12

HDVBP2 11

HDVBN2 11

HDVBP1 11

HDVBN1 11

HDVBP0 11

HDVBN0 11

HDVAP2 11

HDVAN2 11

HDVAP1 11

HDVAN1 11

HDVAP0 11

HDVAN0 11

B.Schematic Diagrams

Sheet 4 of 38

SiSM672 Host,

PCIE 1/5

SiSM672 Host, PCIE 1/5 B - 5

Schematic Diagrams

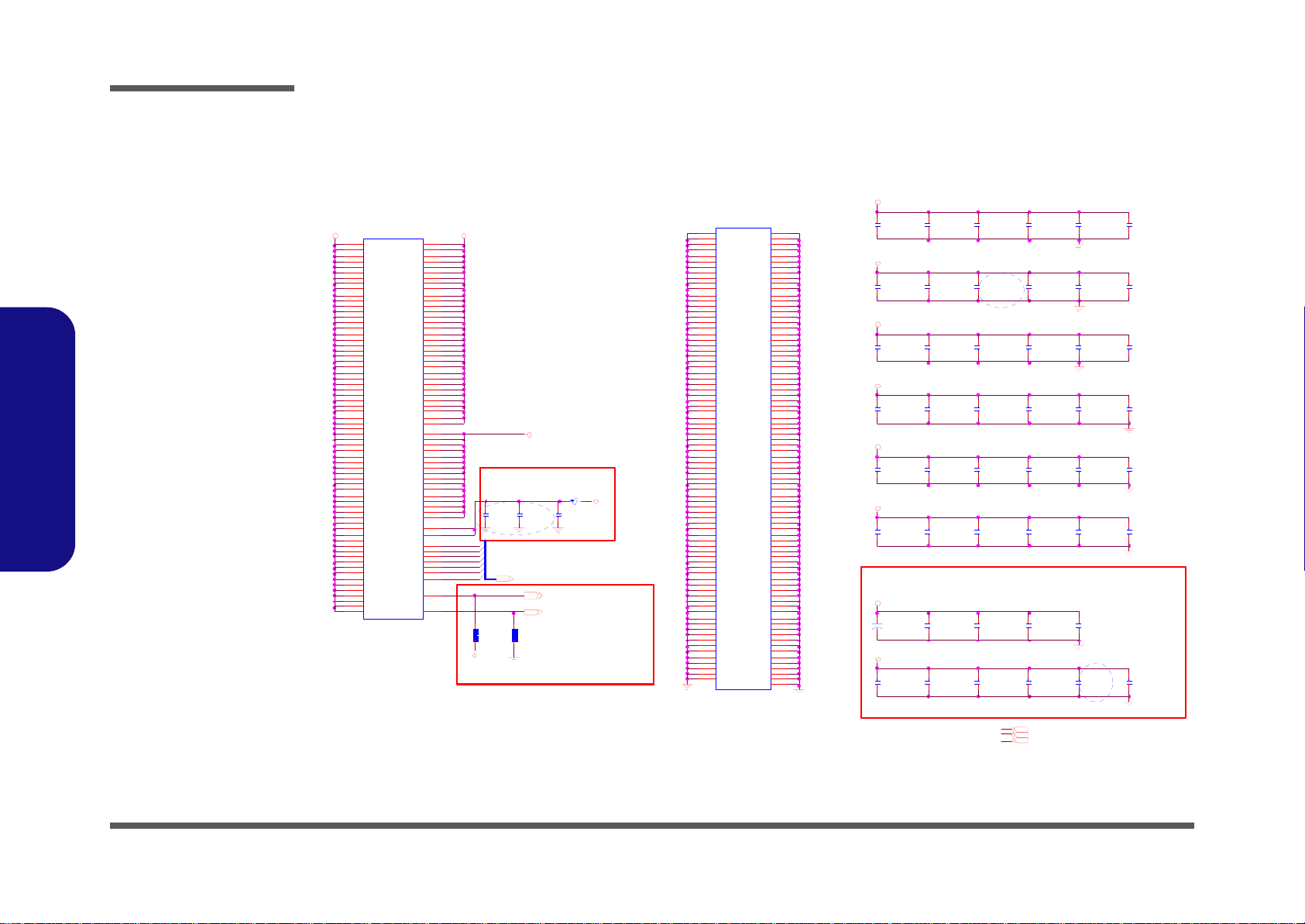

SiSM672 DRAM 2/5

Sheet 5 of 38

SiSM672 DRAM 2/5

B.Schematic Diagrams

1. 8 V S

1. 8 V S

D05 10/15

1. 8 V

L64 HC B1005KF-121T20

C597

10 U _ 10 V_ 0 8

NC12 NC_04

L67 HC B1005KF-121T20

C656

*10U_10V_08

NC13 NC_04

R207

1K_1% _04

R208

1K_1% _04

C611

. 1 U _ 1 0 V_ X7 R _ 0 4

C658

. 1 U _ 1 0 V_ X7 R _ 0 4

C289

.1U_10V_X7R_04

C288

.1U_10V_X7R_04

P la ce un de r M67 1M X

solder side

D1XAV DD

C612

.01 U_16V_X7R_04

D1XAVSS

D4XAV DD

C655

.01 U_16V_X7R_04

D4XAVSS

M_D DR VR EF =0. 9V

M _DDRVREF

C287

. 1U_ 10 V _X 7R_ 04

M_A_ DQ[ 63 :0]9,10

M_DM 09, 1 0

M_ DQS 09, 1 0

M_DQ S0#9, 1 0

M_A_ DQ[ 63 :0]9,10

M_DM 19, 1 0

M_ DQS 19, 1 0

M_DQ S1#9, 1 0

M_A_ DQ[ 63 :0]9,10

M_DM 29, 1 0

M_ DQS 29, 1 0

M_DQ S2#9, 1 0

M_A_ DQ[ 63 :0]9,10

M_DM 39, 1 0

M_ DQS 39, 1 0

M_DQ S3#9, 1 0

M_A_ DQ[ 63 :0]9,10

M_DM 49, 1 0

M_ DQS 49, 1 0

M_DQ S4#9, 1 0

M_A_ DQ[ 63 :0]9,10

M_DM 59, 1 0

M_ DQS 59, 1 0

M_DQ S5#9, 1 0

M_A_ DQ[ 63 :0]9,10

M_DM 69, 1 0

M_ DQS 69, 1 0

M_DQ S6#9, 1 0

M_A_ DQ[ 63 :0]9,10

M_DM 79, 1 0

M_ DQS 79, 1 0

M_DQ S7#9, 1 0

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21 M_ A _A 1 7

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AD31

AD30

AG34

AE29

AE32

AF34

AF31

AE30

AD28

AF32

AF33

AF28

AJ34

AH31

AG30

AF30

AG32

AJ32

AJ31

AH34

AH32

AH33

AK34

AH30

AL32

AM33

AK32

AG29

AM34

AL31

AJ30

AK33

AL34

AM32

AP32

AP31

AM29

AK30

AK29

AJ27

AK28

AN32

AM30

AM31

AK20

AM20

AM19

AJ19

AN20

AJ21

AP19

AH20

AK21

AK19

AL19

AK18

AJ17

AK17

AP16

AH18

AP18

AN18

AP17

AM18

AL17

AM17

AN16

AK16

AN14

AJ15

AP15

AM16

AK15

AP14

AH16

AL15

AM15

AL13

AM13

AM12

AJ13

AM14

AK14

AN12

AH14

AK13

AP12

AP13

U32B

MD0A

MD1A

MD2A

MD3A

MD4A

MD5A

MD6A

MD7A

DQM0 A

DQS0A

DQS0A#

MD8A

MD9A

MD10A

MD11A

MD12A

MD13A

MD14A

MD15A

DQM1 A

DQS1A

DQS1A#

MD16A

MD17A

MD18A

MD19A

MD20A

MD21A

MD22A

MD23A

DQM2 A

DQS2A

DQS2A#

MD24A

MD25A

MD26A

MD27A

MD28A

MD29A

MD30A

MD31A

DQM3 A

DQS3A

DQS3A#

MD32A

MD33A

MD34A

MD35A

MD36A

MD37A

MD38A

MD39A

DQM4 A

DQS4A

DQS4A#

MD40A

MD41A

MD42A

MD43A

MD44A

MD45A

MD46A

MD47A

DQM5 A

DQS5A

DQS5A#

MD48A

MD49A

MD50A

MD51A

MD52A

MD53A

MD54A

MD55A

DQM6 A

DQS6A

DQS6A#

MD56A

MD57A

MD58A

MD59A

MD60A

MD61A

MD62A

MD63A

DQM7 A

DQS7A

DQS7A#

SiSM672

D RAM

D1X AVDD

D1XAV SS

D4X AVDD

D4XAV SS

MA0 A

MA1 A

MA2 A

MA3 A

MA4 A

MA5 A

MA6 A

MA7 A

MA8 A

MA9 A

MA10 A

MA11 A

MA12 A

MA13 A

MA14 A

MA15 A

MA16 A

MA17 A

RASA#

CASA#

WE A#

FWDSDCLKO A

FWDSDC LKOA#

CS0A#

CS1A#

CS2A#

CS3A#

OD T0 A

OD T1 A

OD T2 A

OD T3 A

CKEA0

CKEA1

CKEA2

CKEA3

DDRVREF 0

DDRVREF 1

DDRCOM P

D DRCOMN

OCDVREF P

OC DVREFN

S3AUXSW #

A15

B15

AP11

AP10

AH24

AP25

AM25

AL25

AP26

AM26

AN26

AK25

AP27

AP28

AK24

AN24

AP24

AM28

AM27

AN28

AP21

AP29

AM23

AP22

AJ23

AK12

M_ F WD SD C LK O A _ D_R

AH12

AP23

AH22

AM22

AM21

AK22

AP20

AN22

AL21

AN30

AP30

AH26

AK27

AD18

AD23

AJ25

AK26

AH28

AJ29

B6

D1XAV SS

D4XAV SS

M_ A _A 0

M_ A _A 1

M_ A _A 2

M_ A _A 3

M_ A _A 4

M_ A _A 5

M_ A _A 6

M_ A _A 7

M_ A _A 8

M_ A _A 9

M_ A _A 1 0

M_ A _A 1 1

M_ A _A 1 2

M_ A _A 1 3M_A_DQ17

M_ A _A 1 4

M_ A _A 1 5

M_ A _A 1 6

M_ C OMP_ P

M_ C OMP_ N

M_OCDVREF _ P

M_OCDVREF _ N

D1XAV DD

D4XAV DD

M_ RA S # 9,1 0

M_ CA S # 9,1 0

M_ W E# 9,1 0

M_ C S 0# 9, 1 0

M_ C S 1# 9, 1 0

M_ C S 2# 10

M_ C S 3# 10

M_ ODT 0 9,1 0

M_ ODT 1 9,1 0

M_ ODT 2 10

M_ ODT 3 10

M_ CK E 0 9,1 0

M_ CK E 1 9,1 0

M_ CK E 2 10

M_ CK E 3 10

M_DDRVRE F

NB_ S3AUXSW # 31

M_ A _A [ 17:0 ] 9 ,10

R 2 20 * 1 0m il _ sh or t-N MN P

R 2 19 * 1 0m il _ sh or t-N MN P

M _FW DSDCLKOA_D

M _FW DSDCLKOA_D#M_ F WD SD C LK O A _ D#_ R

M_FWDSDCLKO A_D 25

M_FWDSDCLKO A_D# 25

Pl ac e c lo se t o

M6 71 MX

M_ COMP _N

M_ COMP _P

M_ OC DV RE F_P =0 .8 74V

M_OCDVREF _ P

M_ OC DV RE F_N =0 .9 69V

M_OCDVREF _ N

1.8V 7,9,10,22,23,24,35,39,40

1.8V S 4,6,7,11 ,13,14 ,15 ,17 ,19,21,22,23,24,25,35

M _FW DSDCLKOA_D

M _FW DSDCLKOA_D#

公圖沒有

R205 36_1% _06

R213 36_1% _06

C291 *10P_50V_04

C290 *10P_50V_04

R 2 24 4 0. 2 _1 % _ 04

R222 36_1% _06

R206 36_1% _06

R 2 11 4 0. 2 _1 % _ 04

1.8V

1.8V

1.8V

B - 6 SiSM672 DRAM 2/5

SiSM672 MuTIOL VGA 3/5

1. 8VS

R221

150_1%_04

R214

4 9. 9 _1 %_ 04

1. 8VS

R 467 56_04

R 468 56_04

R 193 4.7K_04

C 237 .1U_10V_X7R_04

C 236 .1U_10V_X7R_04

R189 *0_04

R191 *0_04

R185 *0_04

R184 *0_04

R194 *0_04

N EAR SISM67 2

M760SU

3. 3VS

R186 *4.7K_04

N EAR SISM67 2

C 246 *.1U_16V_04

C 249 *.1U_16V_04

C 251 *.1U_16V_04

L63 HCB1005KF-121T20

C600

10U _10V_08

L17 HCB1005KF-121T20

C208

10U _10V_08

1. 8VS

L26 HCB1005KF-121T20

C333

10U _10V_08

C301

.1U_10V_X7 R_0 4

Z_VREF

C307

.1U_10V_X7 R_0 4

D AC_D DCACL K

D AC_D DCADA T

CLK_14M_671MX

上件

5mA

C610

.1U_10V_X7 R_04

5mA

C224

.1U_10V_X7 R_04

10mA

C331

.1U_10V_ X7R_04

Z_COMP_N

Z_COMP_P

NB_ENTEST

AUX_PWROK

D ELA Y_PWRGD

D AC_ HSY NC

D AC_VSYNC

Z0601

ECLKAVDD1. 8VS

DCLKAVDD1. 8V S

Z4XAVDD

Z_CLK025

ZDREQ21

ZUREQ21

ZSTB_D021

ZSTB_D#021

ZSTB_D121

ZSTB_D#121

ZAD[16:0]21

Z_VREF

Z_ C O MP _ P

Z_ C O MP _ N

Z4XAVDD

CLK_14M_671MX

DACAVDD1

DACAVDD2

DC LKAVD D

ECLKAVDD

C797 *10P_50V_04

C798 *10P_50V_04

C812 *10P_50V_04

L1 9

HCB1005KF-121T20

C21 1

*10 U _1 0V _ 08

NC1 NC_0 4

DAC_RED

DAC_GREEN

DAC_BLU E

VC O M P

VV B W N

DACAVSS1

DACAVSS2

DAC_ RED19

DAC _GREEN19

DAC_BLUE19

DAC_H SYN C19

DAC _VSYNC19

DAC_D DCAC LK19

DAC_D DCAD AT19

M760SU

不上 件

R 18 0 12 1_ 1% _0 4

R 18 7 0_ 04

PC I_ INT#A4,21

C L K _1 4M _ 67 1MX25

C604

.01U _16V_X7R_04

DAC _RED

DAC _GREEN Z06 28

DAC _BLUE

C223

.01U _16V_X7R_04

1. 8 VS

D05 10/15

C329

.01U _16V_X7R_04

U32A

AH 1 0

ZCLK

AP8

ZDRE Q

AN8

ZURE Q

AM7

ZSTB0

AL7

ZSTB0#

AP4

ZSTB1

AP5

ZSTB1#

AK10

ZA D 0

ZAD0

AM6

ZA D 1

ZAD1

AK11

ZA D 2

ZAD2

AJ11

ZA D 3

ZAD3

AP7

ZA D 4

ZAD4

AJ9

ZA D 5

ZAD5

AP6

ZA D 6

ZAD6

AN6

ZA D 7

ZAD7

AK9

ZA D 8

ZAD8

AM4

ZA D 9

ZAD9

AK6

ZA D 1 0

ZAD10

AK8

ZA D 1 1

ZAD11

AN4

ZAD1 2 AUX_PWROK

ZAD12

AK7

ZA D 1 3

ZAD13

AL5

ZA D 1 4

ZAD14

AM5

ZA D 1 5

ZAD15

AM8

ZA D 1 6

ZAD16

ASL

AL9

ZVREF

AP9

ZCMP_P

AM9

ZCMP_N

AM 10

Z4XAVDD

AN 1 0

Z4XAVSS

D13

ROUT

C12

GOUT

C13

BOUT

F12

HSYNC

G12

VSYNC

D11

VGPIO0

E12

VGPIO1

D15

VCOMP

C15

VVBWN

VR SE T

C14

VRSET

Z0 60 1

F13

INTA#

F11

VOSCI

A12

DACAV DD1

B12

DACAVSS1

A13

DACAV DD2

B13

DACAVSS2

B10

DCLKAVDD

A11

DCLKAVSS

A9

ECLKAVDD

B8

ECLKAVSS

Si S M 67 2

73mA

DACAV SS2

DACAV DD2

C22 7

. 01 U_1 6V _X 7R _0 4

C229

. 1U _ 10 V_ X7 R _ 04

ENTEST

TE S T M O D E 0

TE S T M O D E 1

TE S T M O D E 2

TRAP0

TRAP1

TRAP2

TRAP3

TRAP4

TRAP5

TRAP6

TRAP7

TRAP8

TRAP9

TRAP10

AUXOK

PWROK

PC I R S T #

AGPSTOP#

AGPBUSY#

VBVSYNC

VBHSYNC

VBHCLK

VBCLK

VB C A D

VACLK

NC0

NC1

F15

D16

E16

F16

D17

E17

F17

AC32

AD34

AB2 8

AD32

AD33

AE3 4

AC30

AC29

A5

C6

A7

G14

A6

D8

F7

E7

C8

E9

D9

AH2

AG3

NB_ENTEST

NB_TEST MODE0

NB_TEST MODE1

NB_TEST MODE2

Z0602

Z0603

Z0604

Z0605

Z0606

Z0607

Z0608

Z0609

Z0610

Z0611

Z0612

DELAY_ PW RGD

Z0613

Z0614

1. 8 V S

1. 5 V S

AUX_PWROK 22,26

D ELAY_PWRGD 31 ,37

NB_RST# 11,31

AGPSTO P# 22

AGPBUSY# 22

VBVSYNC 11

VBHSYNC 1 1

VBHCLK 11

VBCLK 11

VBCAD 11

VACLK 11

For SiS VB 307

use only

L6 1

HCB1005KF-121T20

L6 2

*HC B10 05 KF -121T20

C59 5

*10U_10V_08

NC11 NC_04

M76 0SU

C245 .1U_ 16 V_04

C242 .1U_ 16 V_04

DACAV DD1

73mA

C608

.1U_10V_X7R_04

DACAVSS1

3.3VS

C526

.1U _10V_X7R_ 04

53

U26

R352

33 _0 4

R139

33 _0 4

R179

49 9_ 1% _0 4

Z0621

C244

10 0P _ 50 V _0 4

CPU_STP#22

R177

33 _0 4

Z0622

C233

*1 00 P_ 50V _0 4

1.05VS 3. 3 VS

R 1 75 15 0_ 1% _0 4

R 1 74 15 0_ 1% _0 4

VCOMP

VVBW N

R 1 73 *1 0m il_s ho r t-NMNP

R 1 76 *1 0m il_s ho r t-NMNP

H_DPRSTP #2, 3 7

H_D PSL P#2

不上件

C60 9

. 1U_ 10 V _X 7R_ 04

1

4

Z06 18

2

1

2

1

2

Z06 17

Z06 19

Z06 27

74LVC1G14GW

C519

*1 00 P_ 5 0V _0 4

S B _ D PR ST P #22SB_ DPRSLPVR22

3.3VS

C168

.1U _10V_X7R_ 04

53

U6

1

Z06 20

4

2

74LVC1G17GW

C169

*1 00 P_ 5 0V _0 4

R 1 41 *0 _0 4

3.3VS 3.3VS

C243

*.1U_1 0V_X7R_04

53

R172

U12

33_04

Z06 23

4

74 L VC 1 G1 7G W

3.3VS 3.3VS

C241

*.1U_1 0V_X7R_04

53

U11

4

74 L VC 1 G1 7G W

Z06 25

R168

33_04

Z06 24

Z06 26

Le ve l S hi tt

1. 05 V < => 3. 3V

U9

1

2

3

4

8

GND

EN

7

VR E F 1

VR E F 2

6

SC L 1

SC L 2

5

SD A 1

SDA2

PCA9306DCUR

1. 0 5V S 2 ,3,4,7,24,39

1. 5 VS 3 ,33,35

1. 8 VS 4 ,5,7,11,13,14,15,17,19,21,22,23,24,25,35

3. 3 VS 9 ,10,11,19,20,21,22,23,24,25,27,28,2 9,3 0,3 1,32,33,34 ,35,37

Z0629

R365

33_04

R364

*3 3_ 04

R146

33_04

*.1U_1 0V_X7R_04

5

U8

1

2

74LVC 1G08GW

3

.1U _10V_X7R _04

53

U10

1

2

74AHC1G32GW

R160 200K_04

R161 1K_1% _04

R162 1K_1% _04

DPRSTP# _INV

H_DPSL P#_LS

C206

.01U_16V_X7R_04

DPRSTP# _INV

PM_DPRSLPVR 37

C228

H_DP SL P#_LS

4

6-01 -74108-Q61

C239

4

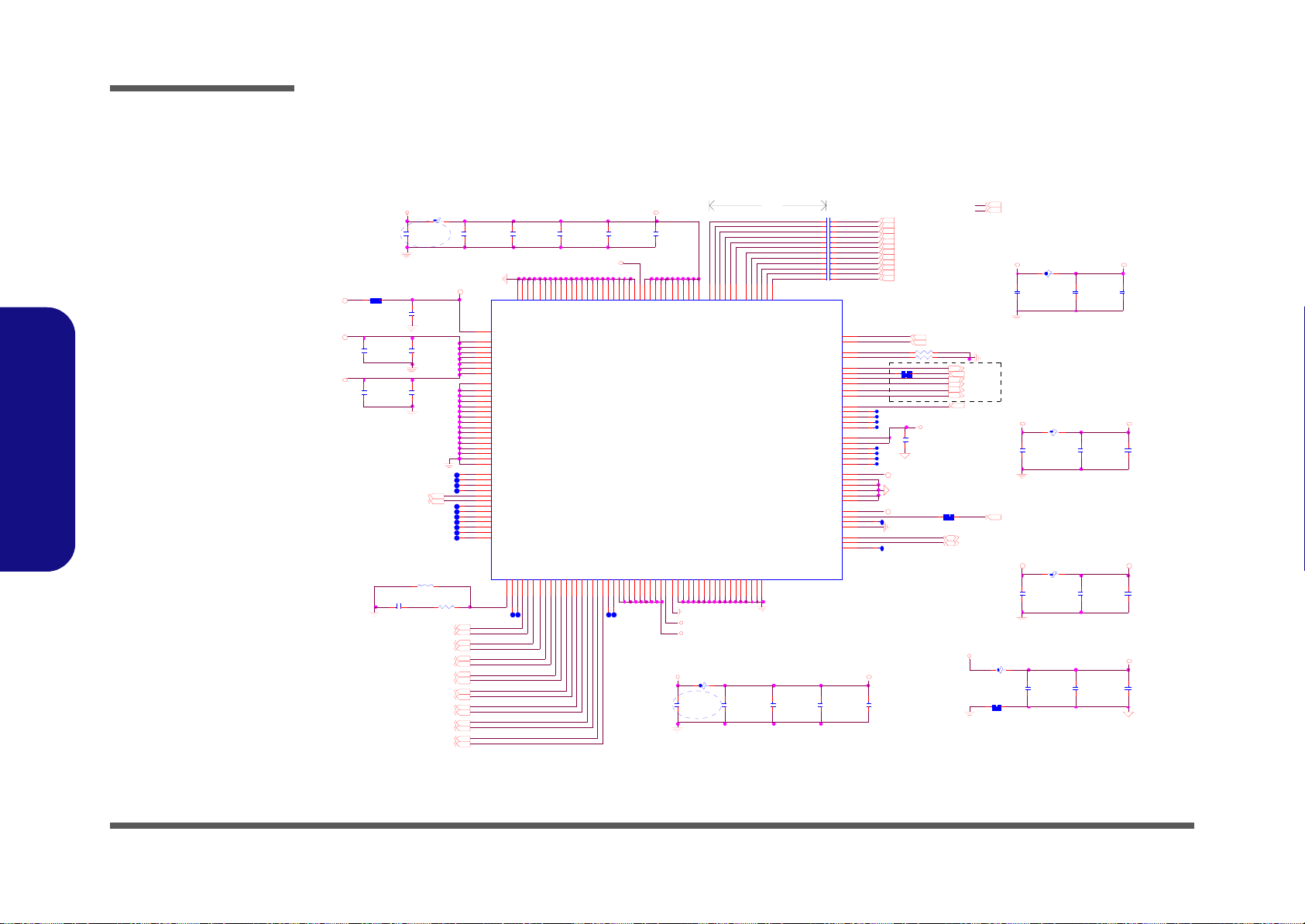

Schematic Diagrams

B.Schematic Diagrams

Sheet 6 of 38

SiSM672 MuTIOL

VGA 3/5

CPUSTP# 25

SiSM672 MuTIOL VGA 3/5 B - 7

Schematic Diagrams

Sheet 7 of 38

SiSM672 PWR 4/5

B.Schematic Diagrams

SiSM672 PWR 4/5

1. 8 V

C268

10 U _1 0 V _ 08

1.8V

C267

C28 3

1U_10V_06

1U _10V_06

1. 8 V S

C664

10 U _1 0 V _ 08

1.8VS

C259

.1U_10V_X7R _04

1.8VS

C662

1U_10V_06

1.8VS

1.2VS

1.2V S

1.2V

C23 5

1U_10V_06

C23 4

1U _10V_06

C277

10U_10V _08

664mA

C285

.1U_10V_X7R_04

392mA

C653

1U_10V_06

392mA

392mA

392mA

C64 9

1U _10V_06

C30 5

10U _10V_08

C274

1U_10V_06

92mA

1. 8 V

C238

.1U_10V_X7R _04

664mA

C29 8

*1U_10V_06

D05 10/15

C65 9

1U_10V_06

C258

.1U_ 1 0V_ X7 R_ 0 4

C265

.1U_ 1 0V_ X7 R_ 0 4

C276

1U_10V_06

876mA

C278

.1U_10V_X7R_04

876mA

C252

.1U_10V_X7R_04

C31 1

.1U_1 0V_X7 R_0 4

C297

1U _10V_06

C284

.1U_10V_X7R_04

C661

1U _10V_06

C261

.1U_10V_X7R_04

C263

.1U_10V_X7R_04

C25 3

.1U_ 1 0V _X7R_ 0 4

C275

1U _10V_06

C256

1U _10V_06

1mA

C248

.01U_16V_X7R _04

W23

AA23

AB23

AC23

AC18

AC20

AC16

AD16

AD17

AD19

AD20

AD21

AD22

AJ2 2

AJ2 4

AL2 3

AL2 6

AN21

AN23

AN25

AN27

AN29

AB12

AB13

AC12

AC13

AC14

AC15

AH 6

AH 7

AN 2

AM 1

AM 2

AM 3

AN 3

AN 5

AN 7

AN 9

W11

AA11

AB11

U32E

C280

10U _10V_08

C306

1U_10V_06

C300

.1U_ 1 0V _X7R_0 4

1.2VS

C648

10U _10V_08

C250

1U_10V_06

1.05V S

C60 1

.1U_ 1 0V _X7R_ 0 4

C309

.1U _10 V_X7R _04

1.2VS

1.2VS

1. 05 V S

1.8V S

C272

10U_10V_08

C254

1U _10V_06

1.2VS

C602

10U_10V_08

C647

.1U _ 10V_ X7R _ 04

C27 1

.1U_10V_X7R_04

FOR EMI

1.8VS 1.8VS

C805

.1U_ 1 0 V_ X7R _04

1.8V 1.8V 1.8V 1.8V

C807

.1U_ 1 0 V_ X7R _04

C80 6

*.1U_10V_X7 R_04

C80 8

.1U_1 0V_X7 R_0 4

C809

*.1U_10V _X7R_04

1.05V S 2,3,4,6,24,39

1.2V 35,39

1.2VS 4,35

1.8V 5,9,10,22,23,24,35,39,40

1.8VS 4,5,6,11,13, 14,15,17,19,21,22,23, 24,25,35

C810

*. 1U _1 0V_X7R _04

VCC M

Y23

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

AP3

PWR

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

AJ4

VCC 1.8

AJ5

VCC 1.8

AJ6

VCC 1.8

AJ7

VCC 1.8

VCC 1.8

AK4

VCC 1.8

AK5

VCC 1.8

AL1

VCC 1.8

AL2

VCC 1.8

AL3

VCC 1.8

AL4

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

VCC 1.8

E8

VDD VB1.8

F9

VDD VB1.8

F8

VDD VB1.8

E10

VDD 1.8

F10

VDD 1.8

N19

PVDD H

N21

PVDD H

P20

PVDD H

P22

PVDD H

R21

PVDD H

T22

PVDD H

U21

PVDD H

V22

PVDD H

M1 1

VDD PEX

N11

VDD PEX

P11

VDD PEX

R11

VDD PEX

T11

VDD PEX

U11

VDD PEX

V11

VDD PEX

VDD PEX

Y11

VDD PEX

VDD PEX

VDD PEX

B5

AUX_IVD D

C5

AUX_IVD D

D6

AUX_IVD D

G8

AUX1.8

SiSM672

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

IV DD

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

M1 3

M1 4

M1 5

M1 6

M1 7

M1 8

M1 9

N16

N17

N18

N20

R22

N22

N13

P13

Y13

Y22

T1 3

U13

U22

V13

W13

W22

AA13

AA22

AB14

AB15

AB16

AB18

AB20

AB22

AF6

AF7

AK3

AG4

AG5

AG6

AG7

R13

AH3

AH4

AH5

AJ1

AJ2

AJ3

AK1

AK2

AC22

AC21

AC19

AC17

A19

VTT

A20

VTT

B19

VTT

B20

VTT

C19

VTT

C20

VTT

D19

VTT

D20

VTT

E19

VTT

E20

VTT

F19

VTT

F20

VTT

G1 9

VTT

G2 0

VTT

L1 8

VTT

L1 9

VTT

L2 0

VTT

M2 0

VTT

M2 1

VTT

M2 2

VTT

M2 3

VTT

N23

VTT

P23

VTT

R23

VTT

T2 3

VTT

U23

VTT

V23

VTT

M1 2

N12

P12

R12

T1 2

U12

V12

W12

Y12

AA12

2024mA

C257

10U_10V_08

C286

1U _10V_06

C266

1U _10V_06

2024mA

C802

10U_10V_08

80mA

C603

1U _10V_06

80mA

C247

.1U_10V_X7R_04

C294

1U _10V_06

2024mA

2024mA

392mA

B - 8 SiSM672 PWR 4/5

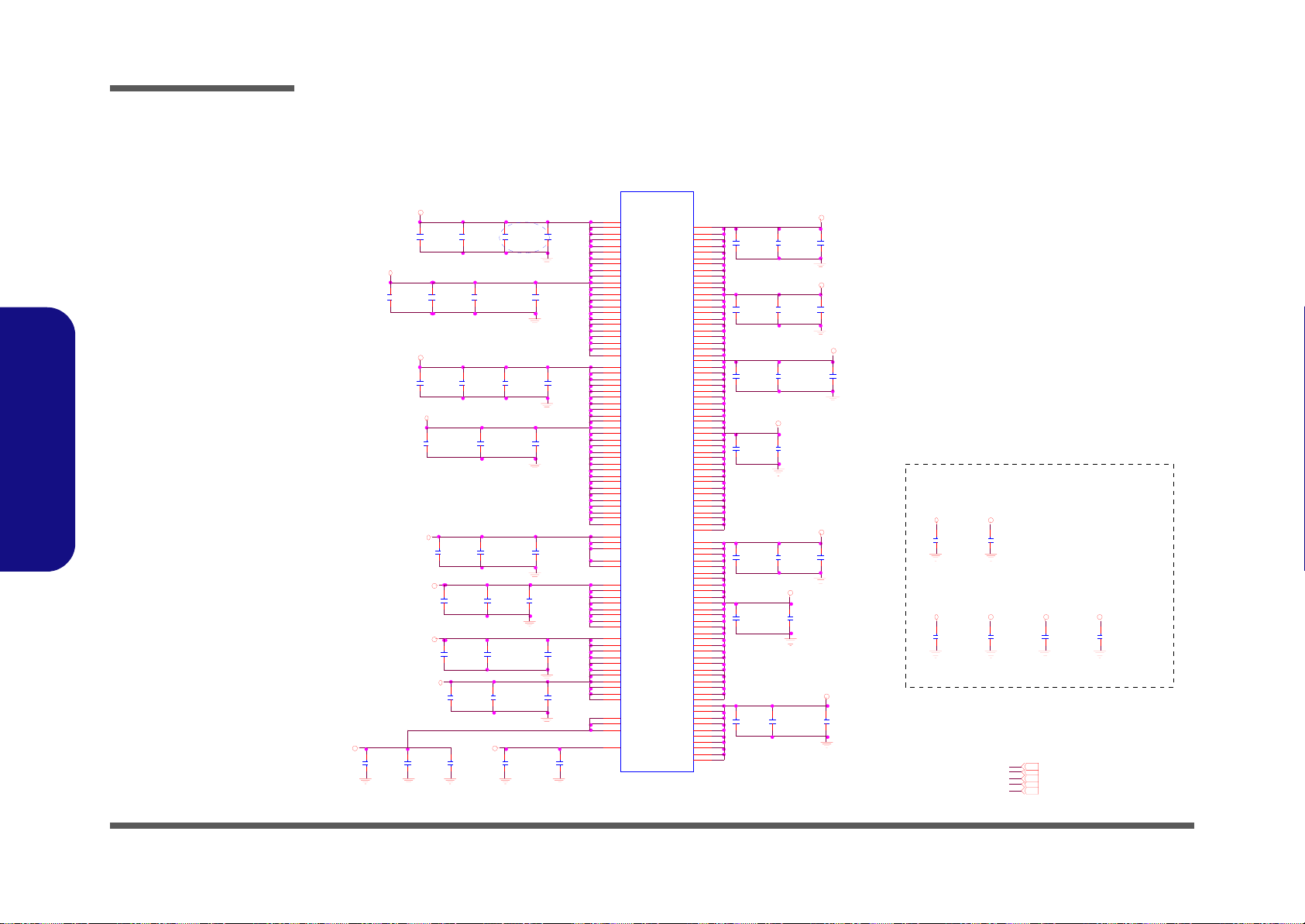

SiSM672 GND 5/5

AA16

AA17

AA18

AA19

AA 2 0

AA21

AA31

AA33

AB3

AB4

AB 5

AB7

AB29

AC2

AC3

AC 31

AC 33

AD2

AD3

AD4

AD5

AD 7

U32F

A3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

J33K3K4K5K29L2L3L4L5L7L31

VSS

VSS

VSS

VSS

VSS

B2

VSS

B3

VSS

B4

VSS

B21

VSS

B23

VSS

B25

VSS

B27

VSS

B29

VSS

B31

VSS

C1

VSS

C2

VSS

C3

VSS

C4

VSS

C9

VSS

C10

VSS

C11

VSS

C16

VSS

C18

VSS

C32

VSS

C33

VSS

D1

VSS

D2

VSS

D3

VSS

D4

VSS

D5

VSS

D10

VSS

D12

VSS

D21

VSS

D23

VSS

D25

VSS

D27

VSS

D29

VSS

E1

VSS

E2

VSS

E3

VSS

E6

VSS

E11

VSS

E13

VSS

E14

VSS

E18

VSS

E29

VSS

E30

VSS

E33

VSS

F2

VSS

F3

VSS

F4

VSS

F5

VSS

F6

VSS

F14

VSS

F22

VSS

F24

VSS

F26

VSS

F28

VSS

G2

VSS

G3

VSS

G7

VSS

G1 0 AB17

VSS VSS

P21

VSS

T2 1

VSS

V21

VSS

VSS

VSS

VSS

VSS

VSS

H5

H29J2J3J7J31

G3 1

G3 3

H4

VSS

VSS

VSS

VSS

VSS

VSS

AD 29

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L33M2M3

AE3

AE31

AE33

AF2

AF3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

M2 9N3N4N5N6N7N14

VSS

VSS

AF 4

AF5

VSS

GN D

VSS

AG2

AG31

AG 33

AH29

AF29

AJ8

AJ10

AJ12

AJ14

AJ 1 6

AJ18

AJ20

AJ26

AJ28

AJ33

AK 3 1

AL6

AL8

AL10

AL12

AL14

VSS

VSS

VSS

VSS

AL16

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

R14

R15

R16

R17

R18

R19

R20

R31

AH 1

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N15

N31

N33P2P3

VSS

P14

P15

P16

P17

P18

P2 9R2R3R4R5

AL18

AL20

VSS

VSS

R33T3T6

VSS

VSS

VSS

Schematic Diagrams

銅柱

6 -34 -M 52 GS -0 20

H33

C355B264D 18 6

H35

C25 6B185D146

AL28

AL30

AL33

AN11

AN13

AN15

AN17

VSS

VSS

VSS

VSS

VSS

VSS

VSS

T29

VSS

U2

VSS

U3

VSS

U4

VSS

U5

VSS

U6

VSS

U14

VSS

U15

VSS

U16

VSS

U17

VSS

U18

VSS

U19

VSS

U20

VSS

U31

VSS

U33

VSS

V2

VSS

V3

VSS

V4

VSS

V5

VSS

V14

VSS

V15

VSS

V16

VSS

V17

VSS

V18

VSS

V19

VSS

V20

VSS

V29

VSS

AN33

VSS

AN31

VSS

AN19

VSS

W3

VSS

W14

VSS

W15

VSS

W16

VSS

W17

VSS

W18

VSS

W19

VSS

W20

VSS

W21

VSS

W31

VSS

W33

VSS

Y2

VSS

Y3

VSS

Y4

VSS

Y5

VSS

Y7

VSS

Y14

VSS

Y15

VSS

Y16

VSS

Y17

VSS

Y18

VSS

Y19

VSS

Y20

VSS

Y21

VSS

Y29

VSS

AA2

VSS

AA3

VSS

AA14

VSS

AA15

VSS

AB19

VSS

AB21

VSS

P19

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

Si S M 6 7 2

T14

T15

T1 6

T17

T18

T19

T20

H30

C217D111

H16

C315D1 11

H12

C276B193D185

S8

S MD 9 8X 17 8 R

1

1

S6

SMD73X136R

1

1

銅柱

6-34 -M 52N S- 020

M74

H29

C354B197D185

H13

H18

C237

C237

H9

H11

C237

C237

S3

SMD192X73SR

1

1

H27

C 3 55 B 26 4 D 18 6

M74

不上件

H31

C354B 19 7D 185

不上 件

H14

C237

H15

C237

S2

SMD 192X73 SR

1

1

H22

C67D67

H10

C237

H28

C 3 55 B 2 64 D 18 6

H34

C256B185D146

H32

C217D111

H26

C67D67

H36

C178D79

S7

SM D192X73SR

1

1

H38

C29 6D16 6

H37

C17 8D79

S5

SM D 1 9 2 X7 3S R

H4

2

3

4

5 6

MT H 3 15 D 1 11

H8

2

3

4

5 6

MT H 3 15 D 1 11

H7

2

3

4

5 6

MT H 3 15 D 1 11

H23

2

3

4

5 6

MT H 3 15 D 1 11

H5

2

3

4

5 6

MT H 3 15 D 1 11

M1

M2

M-M A RK1

M-MA R K1M6M-MA R K1

M9

M1 3

M-M A RK1

M-MA R K1

S4

SMD192X73SR

1

1

1

1

H20

2

9

3

8

1

4

7

5 6

MTH 315D 111

9

8

1

7

H3

9

2

8

3

1

7

4

5 6

MTH 315D 111

H21

9

2

8

3

1

7

4

5 6

MTH 315D 111

9

8

1

7

M7

M-MA R K1

M5

M3

M-MA R K1

M-MA R K1

H19

2

3

1

4

5 6

MTH315D111

9

8

7

9

8

1

7

B.Schematic Diagrams

H6

9

2

3

4

5 6

MTH315D111

H17

2

3

4

5 6

MTH315D111

M11

M-MA RK 1

M14

M-MA RK 1

H24

H4_0H2H4_0

1

1

M10

M-MARK1

M8

M-MARK1

9

8

7

9

8

7

M4

M-M A RK1

M1 2

M-M A RK1

H1

H4_0

8

1

7

9

8

1

7

H25

H4_0

Sheet 8 of 38

SiSM672 GND 5/5

SiSM672 GND 5/5 B - 9

Schematic Diagrams

DDRII SO-DIMM - 1

Sheet 9 of 38

DDRII SO-DIMM - 1

B.Schematic Diagrams

SO-DIMM 1

M_A_ A[ 17:0 ]5,10

M_CL K_DDR025

M_CLK_ DDR0 #25

M_CL K_DDR125

M_CLK_ DDR1 #25

D05 10/2

M_DQS05,10

M_DQS15,10

M_DQS25,10

M_DQS35,10

M_DQS45,10

M_DQS55,10

M_DQS65,10

M_DQS75,10

M_RAS#5,10

M_CAS#5,10

M_ CS0#5,10

M_ CS1#5,10

M_CKE05,10

M_CKE15,10

M_ ODT 05,10

M_ ODT 15,10

M_DQ S0 #5,10

M_DQ S1 #5,10

M_DQ S2 #5,10

M_DQ S3 #5,10

M_DQ S4 #5,10

M_DQ S5 #5,10

M_DQ S6 #5,10

M_DQ S7 #5,10

MVR EF1

3.3VS

1.8V

112

111

1179695

11881828710388104

47

13 3

18 377124818 478717212 1

12 2

J_DIM1

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

139

128

145

16 5

17 1

M_A_A0

102

A0

M_A_A1

101

A1

M_A_A2

100

A2

M_A_A3

99

A3

M_A_A4

98

A4

M_A_A5

97

A5

M_A_A6

94

A6

M_A_A7

92

A7

M_A_A8

93

A8

M_A_A9

91

A9

M_A_A10

105

A1 0 / A P

M_A_A14

90

A1 1

M_A_A15

89

A1 2

M_A_A16

116

A1 3

M_A_A17

86

A1 4

84

A1 5

M_A_A13

85

A1 6/BA2

M_A_A11

107

BA 0

M_A_A12

106

BA 1

10

M_ DM05,10

M_ DM15,10

M_ DM25,10

M_ DM35,10

M_ DM45,10

M_ DM55,10

M_ DM65,10

M_ DM75,10

M_R AS #

M_WE #

M_WE #5,10

M_C AS #

M_C S0 #

M_C S1 #

M_C KE 0

M_C KE 1

M_C LK_D DR0

M_C LK_D DR0#

M_C LK_D DR1

M_C LK_D DR1#

M_O DT0

M_O DT1

S_DAT10,22,25,33

S_CLK10,22,25,33

C359

1U_6.3V_X5R_06

C360

.1U_ 10V_X7R_04

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

108

RAS#

109

WE #

113

CAS#

110

S0 #

115

S1 #

79

CKE0

80

CKE1

30

CK0

32

CK0#

164

CK1

166

CK1#

114

ODT0

119

ODT1

195

SD A

197

SC L

11

DQS#0

29

DQS#1

49

DQS#2

68

DQS#3

129

DQS#4

146

DQS#5

167

DQS#6

186

DQS#7

1

VR EF

199

VD D SP D

VSS

VSS

VSS

VSS

VSS

VSS

VSS

18244153425459656066127

19 6

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VSS

17 2

18 7

17 8

19 09213315 53413 2

17 7

19 3816 2

VS S

VS S

VSS

VSS

VSS

VSS

14 4

15 6

15 0

13 84028

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

16 8231527

161

VSS

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

NCTEST

VSS

VSS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

NC1

NC2

NC3

NC4

VSS

149

VSS

SA 0

SA 1

VSS

39

M_ A_DQ 5

5

M_ A_DQ 2

7

M_ A_DQ 6

17

M_ A_DQ 7

19

M_ A_DQ 4

4

M_ A_DQ 0

6

M_ A_DQ 1

14

M_ A_DQ 3

16

M_ A_DQ 13

23

M_ A_DQ 11

25

M_ A_DQ 15

35

M_ A_DQ 14

37

M_ A_DQ 12

20

M_ A_DQ 8

22

M_ A_DQ 9

36

M_ A_DQ 10

38

M_ A_DQ 16

43

M_ A_DQ 20

45

M_ A_DQ 18

55

M_ A_DQ 19

57

M_ A_DQ 21

44

M_ A_DQ 17

46

M_ A_DQ 23

56

M_ A_DQ 22

58

M_ A_DQ 24

61

M_ A_DQ 25

63

M_ A_DQ 29

73

M_ A_DQ 27

75

M_ A_DQ 28

62

M_ A_DQ 26

64

M_ A_DQ 30

74

M_ A_DQ 31

76

M_ A_DQ 39

123

M_ A_DQ 37

125

M_ A_DQ 35

135

M_ A_DQ 38

137

M_ A_DQ 32

124

M_ A_DQ 36

126

M_ A_DQ 34

134

M_ A_DQ 33

136

M_ A_DQ 47

141

M_ A_DQ 40

143

M_ A_DQ 44

151

M_ A_DQ 43

153

M_ A_DQ 46

140

M_ A_DQ 45

142

152

M_ A_DQ 41

M_ A_DQ 42

154

M_ A_DQ 49

157

M_ A_DQ 48

159

173

M_ A_DQ 50

M_ A_DQ 55

175

158

M_ A_DQ 53

M_ A_DQ 52

160

M_ A_DQ 51

174

M_ A_DQ 54

176

M_ A_DQ 56

179

M_ A_DQ 57

181

189

M_ A_DQ 58

191

M_ A_DQ 62

M_ A_DQ 61

180

M_ A_DQ 60

182

M_ A_DQ 59

192

M_ A_DQ 63

194

83

120

50

69

163

198

Z0901

Z0902

200

AS0A421-N2AN-4F

M_ A _D Q[ 6 3: 0 ] 5, 10

D05 10/15-0255

R258 *10mil_short-NMN P

R259 *10mil_short-NMN P

這部份公圖沒有

M_CLK_ DDR0

M_CLK_ DDR0 # M_CL K_DDR 1#

1.8V

R471

1K_1%_04

R472

1K_1%_04

C364

*3.3P_50V_04

C671

.1U_ 10V_X7 R_ 04

MVR EF 1

C672

.1U_ 10V_X7 R_ 04

!

M_CL K _DDR 1

C366

*3.3P_50V_ 04

B - 10 DDRII SO-DIMM - 1

1. 8 V

+

C712

*150U _4V_B2

C397

+

150U_4V_B2

C367

10U_10V_08

C368

10U_10V_08

C371

10U _10V_08

C39 6

10 U _1 0V _ 08

C39 5

10 U _ 10 V_ 08

C315

.1U _10V_X7R_04

C303

.1U_10V_ X7 R_04

C667

.1U_10V_X7R_04

C66 8

.1U_ 10V_X7R_04

C365

.1U_10V_ X7 R_04

C304

.1U_10V_ X7 R_04

C403

.1U_ 10V_X7R_04

C392

.1U_ 10 V_X7R_04

1.8V 5,7,10,22,23,24,35,39,40

3. 3 V S 6 , 10 ,11 , 19 , 20 , 21 ,22 ,23,24,25,27,28,29,30,31,32,33,34,35,37

DDRII SO-DIMM - 2

Schematic Diagrams

S O-D IMM 2

M_ A_ A [17 : 0]5, 9

M_CL K_DDR225

M_CL K_ DDR2 #25

M_CL K_DDR325

M_CL K_ DDR3 #25

1. 8V

D05 10/15

C84 7

22 U _1 0V _ 08

1. 8V

C310

+

*150U_4V_B2

C29 6

10 U _1 0V _ 08

C67 3

+

15 0U _ 4V _ B2

M_D QS05,9

M_D QS15,9

M_D QS25,9

M_D QS35,9

M_D QS45,9

M_D QS55,9

M_D QS65,9

M_D QS75,9

M_ D QS0#5, 9

M_ D QS1#5, 9

M_ D QS2#5, 9

M_ D QS3#5, 9

M_ D QS4#5, 9

M_ D QS5#5, 9

M_ D QS6#5, 9

M_ D QS7#5, 9

MVR EF2

3.3VS

M_DM05, 9

M_DM15, 9

M_DM25, 9

M_DM35, 9

M_DM45, 9

M_DM55, 9

M_DM65, 9

M_DM75, 9

S_DAT9,22,25,33

S_CLK9,22 ,25,33

C36 1

10 U _1 0 V_ 08

M_ A_A 0

M_ A_A 1

M_ A_A 2

M_ A_A 3

M_ A_A 4

M_ A_A 5

M_ A_A 6

M_ A_A 7

M_ A_A 8

M_ A_A 9

M_ A_A 10

M_ A_A 14

M_ A_A 15

M_ A_A 16

M_ A_A 17

M_ A_A 13

M_ A_A 11

M_ A_A 12

M_ RAS #

M_ WE #

M_ CAS #

M_ CS2 #

M_ CS3 #

M_ CKE 2

M_ CKE 3

M_ CLK_D DR 2

M_ CLK_D DR 2#

M_ CLK_D DR 3

M_ CLK_D DR 3#

M_ ODT2

M_ ODT3

C370

1U _6 .3 V _X 5R _ 06

C374

.1U_ 10 V_X7R_04

C282

10 U _ 10 V_ 08

1.8V

J_DIM2

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A1 0 / A P

90

A1 1

89

A1 2

116

A1 3

86

A1 4

84

A1 5

85

A1 6 / B A 2

107

BA 0

106

BA 1

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

108

RAS #

109