Notebook Computer

W241BU/W241BUQ/W240BU/W245BUQ/W248BUQ/

W249BUQ

Preface

Service Manual

Preface

I

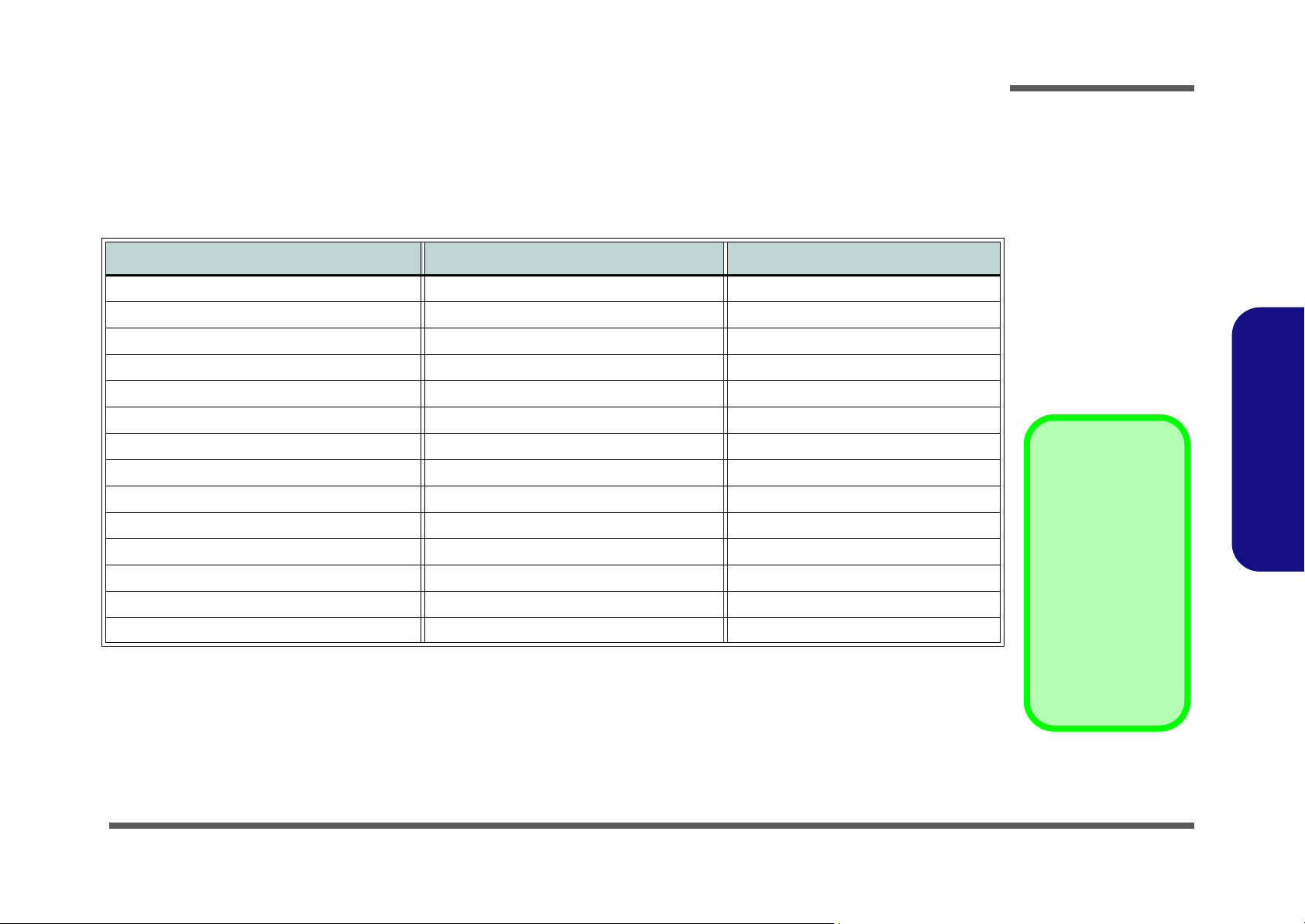

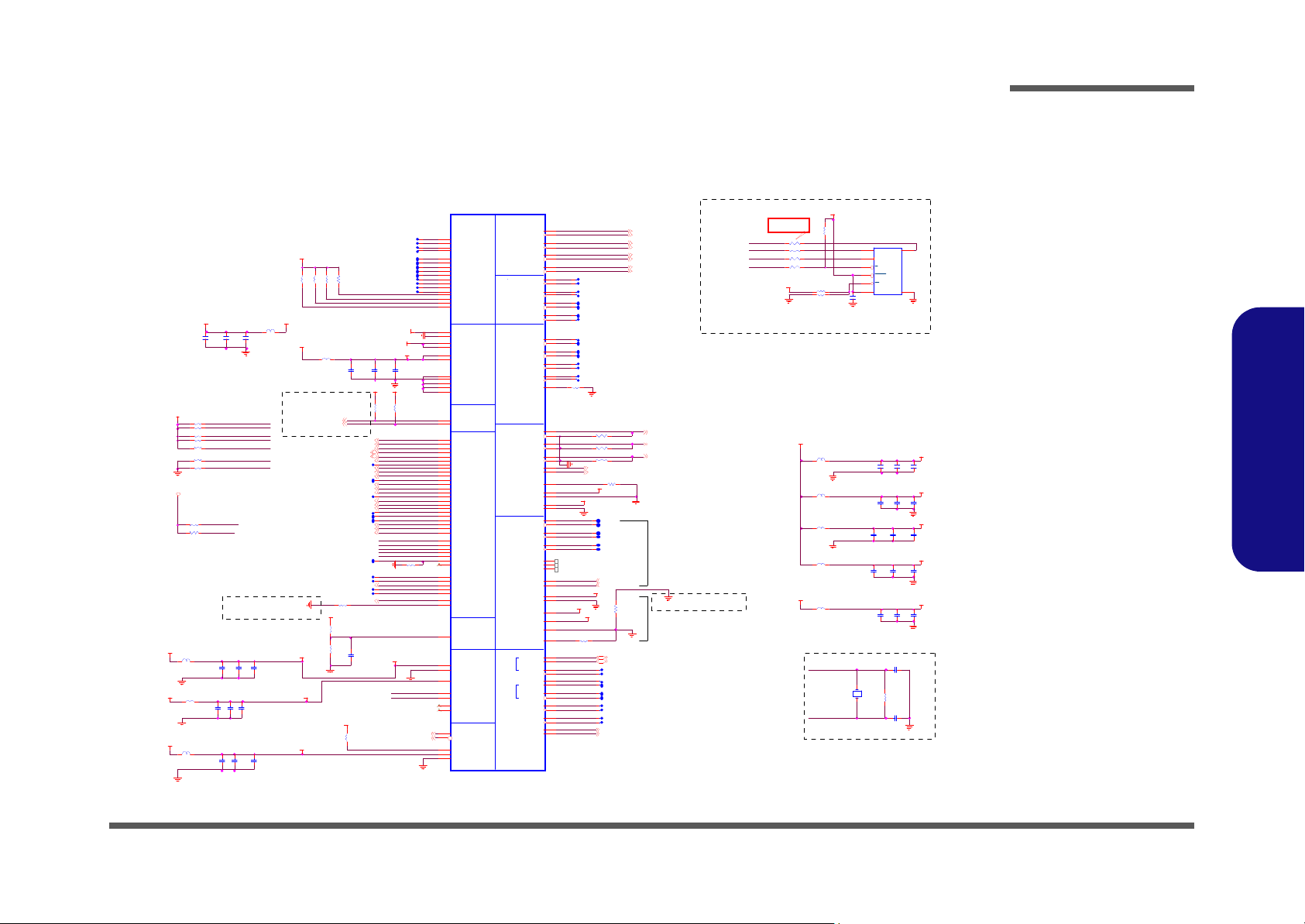

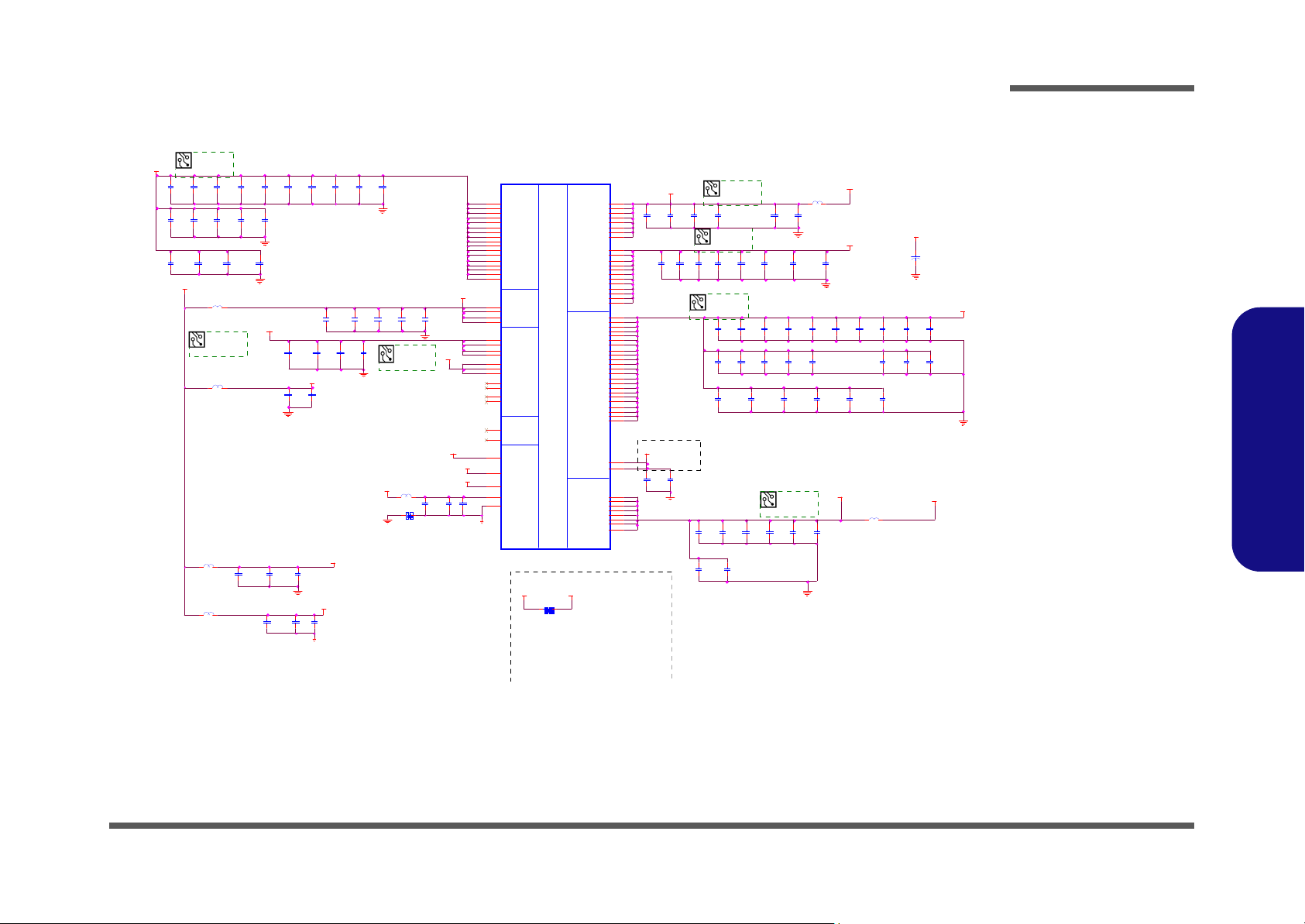

Appendix B: Schematic Diagrams

Table B - 1

Schematic

Diagrams

Version Note

The schematic diagrams in this chapter

are based upon version 6-7P-W2405-

003. If your mainboard (or other

boards) are a later

version, please

check with the Service Center for updated diagrams (if

required).

This appendix has circuit diagrams of the W241BU/W241BUQ/W240BU/W245BUQ/W248BUQ/W249BUQ notebook’s PCB’s. The following table indicates where to find the appropriate schematic diagram.

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 HUDSON PCIE/ PCI/ CLOCK/ FCH - Page B - 16 USB/ FAN/ TP/ MULTI CON - Page B - 30

ONTARIO MEM & PCIE I/F, AP - Page B - 3 HUDSON GPIO/ USB/ STRAP - Page B - 17 5VS/ 3.3VS/ 1.8VS/ 1.5VS/ 1.1VS - Page B - 31

ONTATIO DISPLAY/ CLK/ MISC - Page B - 4 HUDSON SATA/ DEBUG IO/ SPI - Page B - 18 POWER VDD3/ VDD5 - Page B - 32

ONTARIO POWER & DECOUPLING - Page B - 5 HUDSON POWER DECOUPLING - Page B - 19 Power 1.5V/ 0.75 - Page B - 33

INAGUA DDR3 SO-DIMMS A - Page B - 6 POWERGOOD/ TPM - Page B - 20 Power 1.1V/ 1VS - Page B - 34

INAGUA DDR3 SO-DIMMS B - Page B - 7 LVDS, INVERTER - Page B - 21 Power 1.8VS - Page B - 35

Robson S3 PCIE/ LVDS 1/6 - Page B - 8 HDMI/ CRT - Page B - 22 APU CORE/ NB CORE - Page B - 36

Robson S3 MAIN 2/6 - Page B - 9 CCD/ 3G - Page B - 23 VGA POWER - Page B - 37

Robson S3 MEM Interface 3/6 - Page B - 10 Card Reader/ LAN JMC261C - Page B - 24 CHARGER/ DC IN - Page B - 38

Robson S3 Straps 4/6 - Page B - 11 MINI PCIE/ SATA HDD/ ODD - Page B - 25 Click Board - Page B - 39

Schematic Diagrams

B.Schematic Diagrams

Robson S3 Power 5/6 - Page B - 12 AUDIO CODEC ALC261C - Page B - 26 Audio Board/ USB - Page B - 40

Robson S3 Power 6/6 - Page B - 13 USB 3.0 VL800 - Page B - 27 Power Switch & LID Board - Page B - 41

Robson DDR3 MEM CH-A - Page B - 14 KBC- ITE IT8518 - Page B - 28 EXTERNAL ODD Board - Page B - 42

Robson DDR3 MEM CH-B - Page B - 15 LED/ MDC/ BT - Page B - 29

B-1

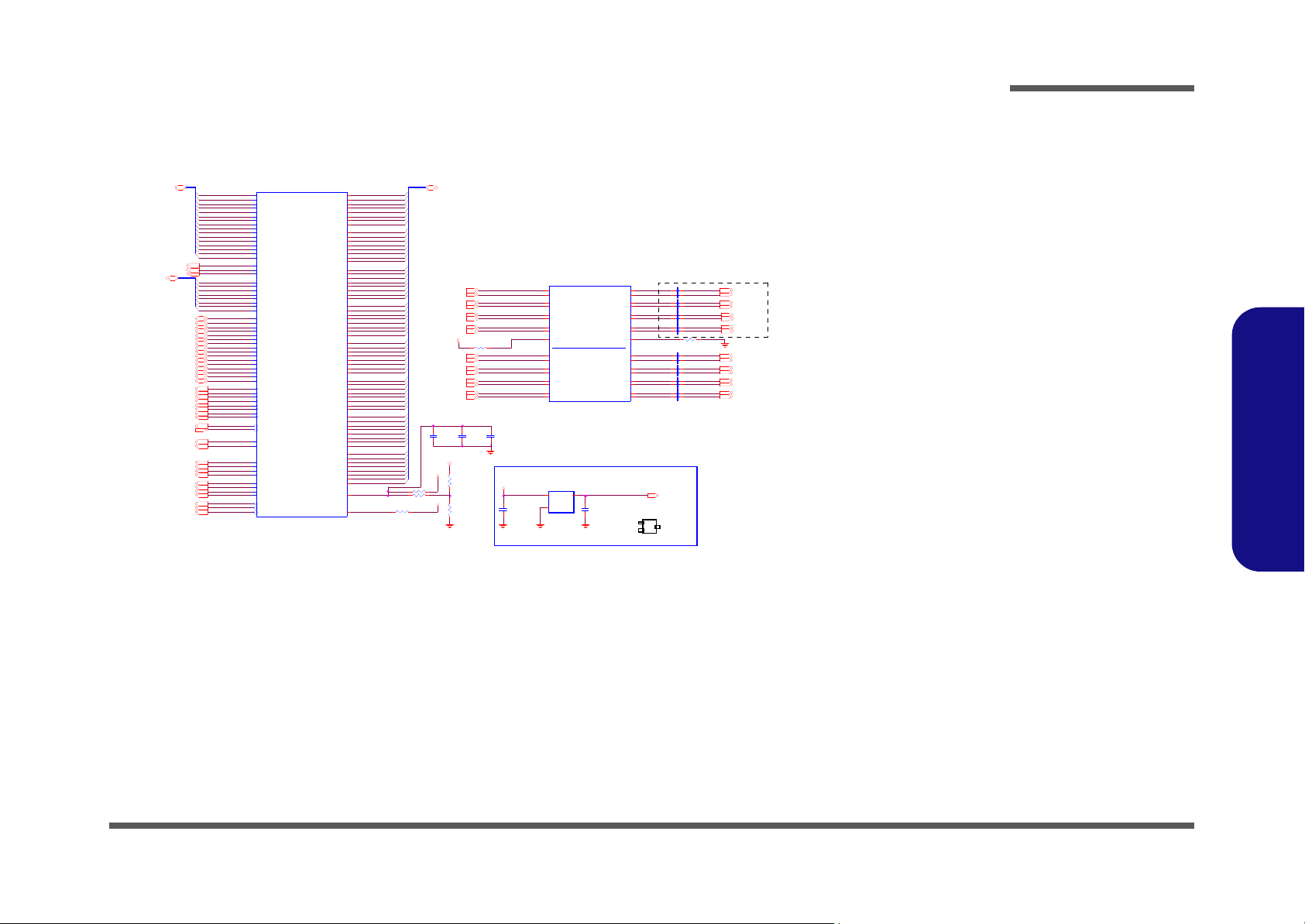

Schematic Diagrams

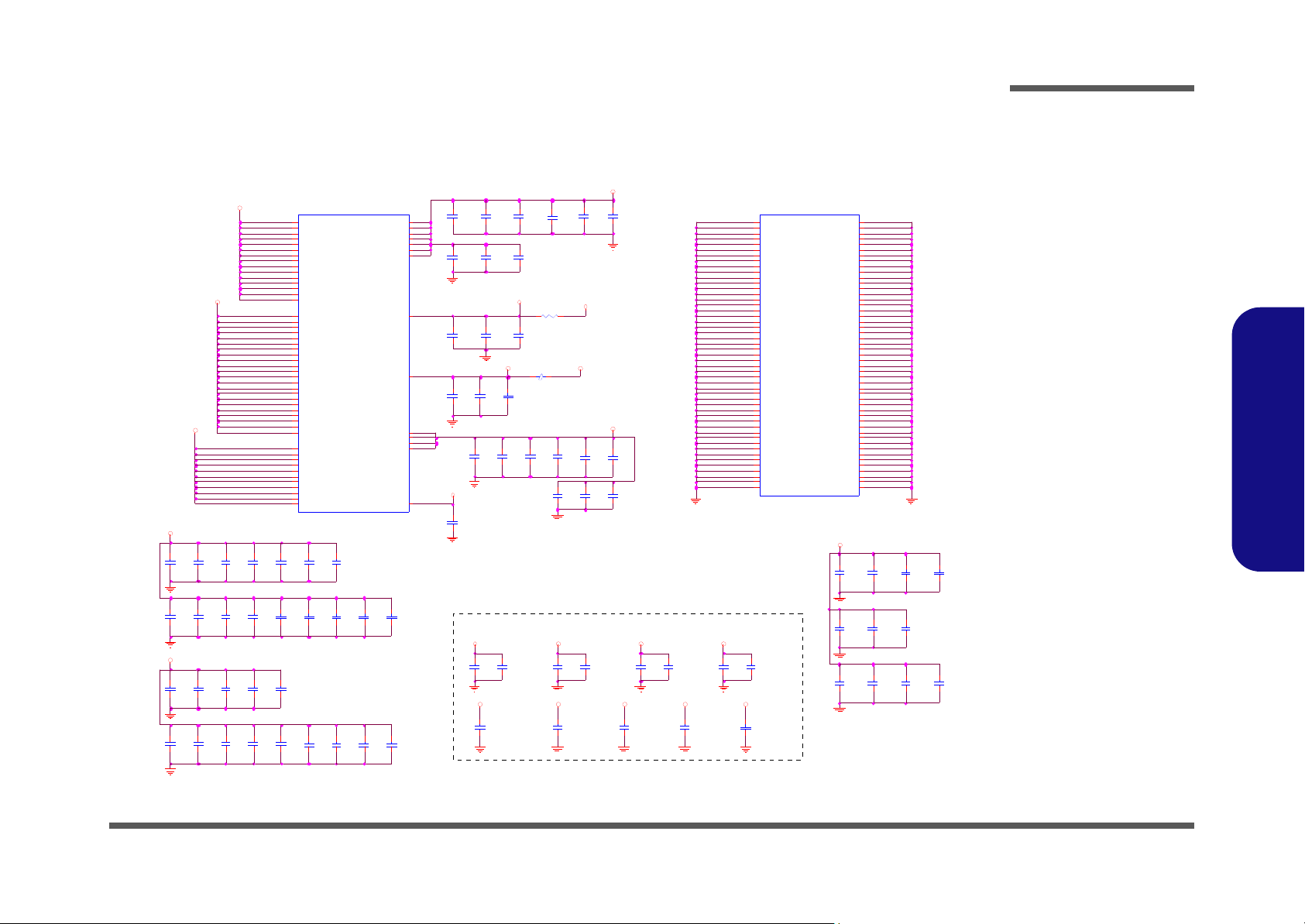

Sheet 1 of 41

System Block

Diagram

5 12MB DDR3

(USB 2)

TOUC H PAD

LPC

CARD

READER

GPU PO WE R, VD DC

SO-DIMM1

HP

OU T

INT SPK R

CLICK BOARD

SOCK ET

PCIE

480 Mbps

DDRIII

Min i PCIE

SPI

DDRIII

INT MIC

25

MHz

LC D CONNECTOR

AMD FUSION APU

CR T Connector

HDMI Conne ctor

24 MHz

SHEET 6

MI C

IN

SHEET 5

128pins LQFP

SO-DIMM2

32.768KHz

(USB6)

Blue toot h

1.1V , 1V S

EC SMBUS

USB PO RT

AZALIA LINK

(USB 0) (USB1)

US B POR T

SATA ODDSATA HDD

BIOS

SPI

LAN

ITE 8518

INT. K/B

Azalia Codec

EC

5V, 3V,5 VS,3.3VS

1.5V,0.75VS(VTT_MEM)

USB2.0

ATI ROBSON

VDD3,VDD5

UMI*4

W8 3L771AWG

32 .768 KHz

JMIC RO

APU_CORE,NB_CORE

SATA I/ II 3.0G b/s

1066MHz

DDR3 / 1.5V

(Reserve)

TPM

CCD

(USB5)

REALTEK

ALC269

33 MHz

THER MAL

SENS OR

100 MHz

14 *14* 1. 6m m

(S3 TYPE)

SMART

FAN

SMART

BATTER Y

AC-IN

PCIE*4

JMC261C

W240BU/W250BUQ/ W250BAQ System Bl ock Diagram

SHEET 38

RJ-4 5 7IN 1

SOCKET

INT SPKER

POWE R SWIT CH+H OTKE Y X 3

6-71 -E51 QS-D 02

CLIC K BOA RD

EXT. ODD

EXTERNAL ODD BOARD

6-71 -W24 02-D 01

POWER SWITCH BOARD

USB+ EARP HONE +EXT .MIC

AUDI O BOA RD

6-71 -E51 QN-D 01

(Reserve)

6-71 -W24 08-D 02

(USB4)

US B PORT

Ontario FT1

41 3-BALL

19 mmX19mm BGA

VGA DAC

DISP LAY P ORT X2

4 X 1 P CIE G E N 2 G P P

1 X4 UMI-LINK GEN1

SINGLE CHANNEL DDR3

D X11 IGP

AMD HUDSON-M1

23mmX23mm BGA

HW MONI TOR

GB M AC

605-BALL

AZALIA HD A UDIO

S PI I/F

IN T . C L K G E N

USB2.0(12) + 1.1 (2)

P CIE GE N 1 I/F (4 x 1)

LPC I/F

SATAII (3 POR TS)

CHARGER,DC IN

USB 3.0 3G CARD

(USB9)

(Optional)

WLAN

1.8VS

1.5 VS,1 .1VS

MVDDQ,1.8V_REG,1.0V_REG

(USB3 )

System Block Diagram

B.Schematic Diagrams

B - 2 System Block Diagram

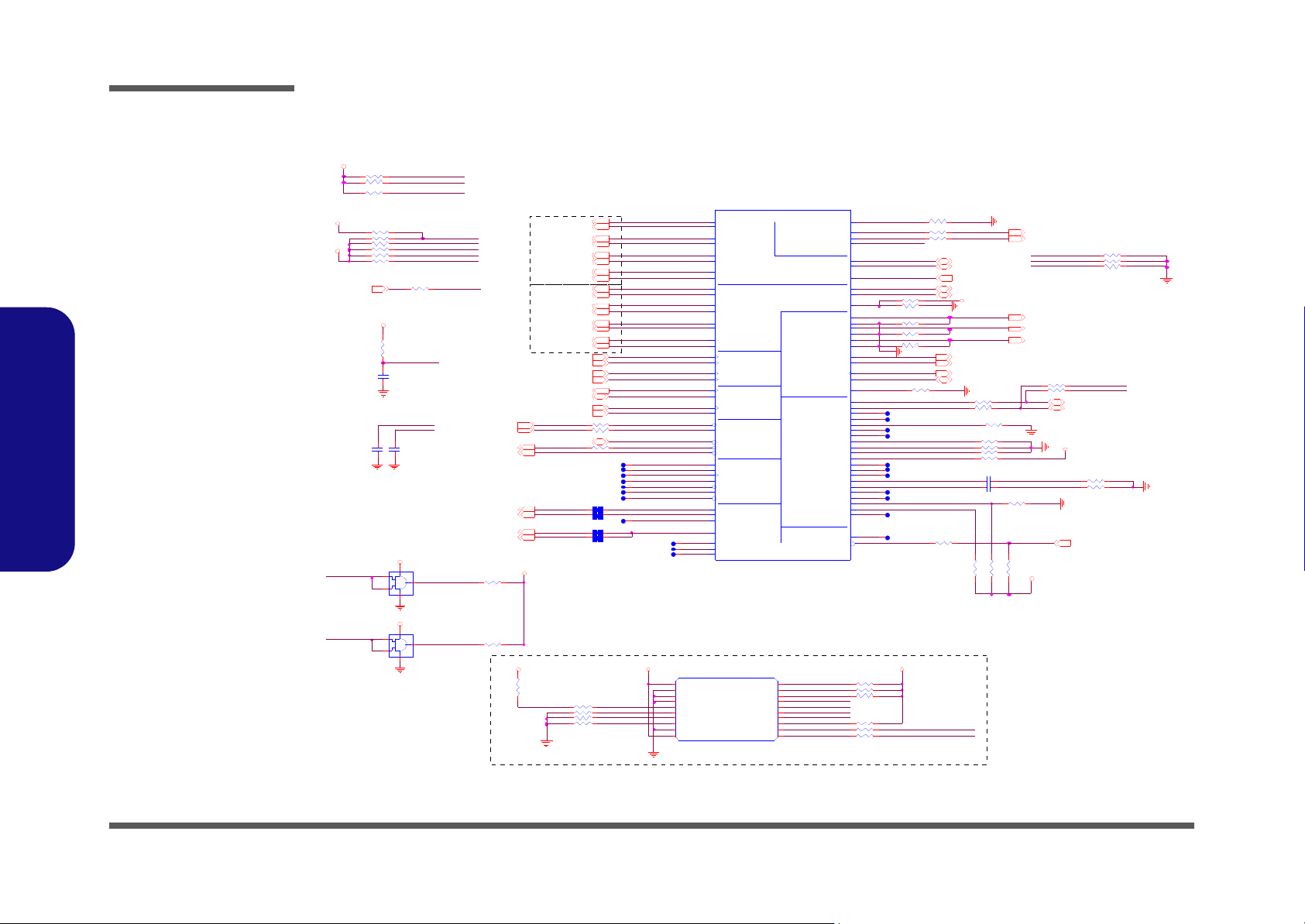

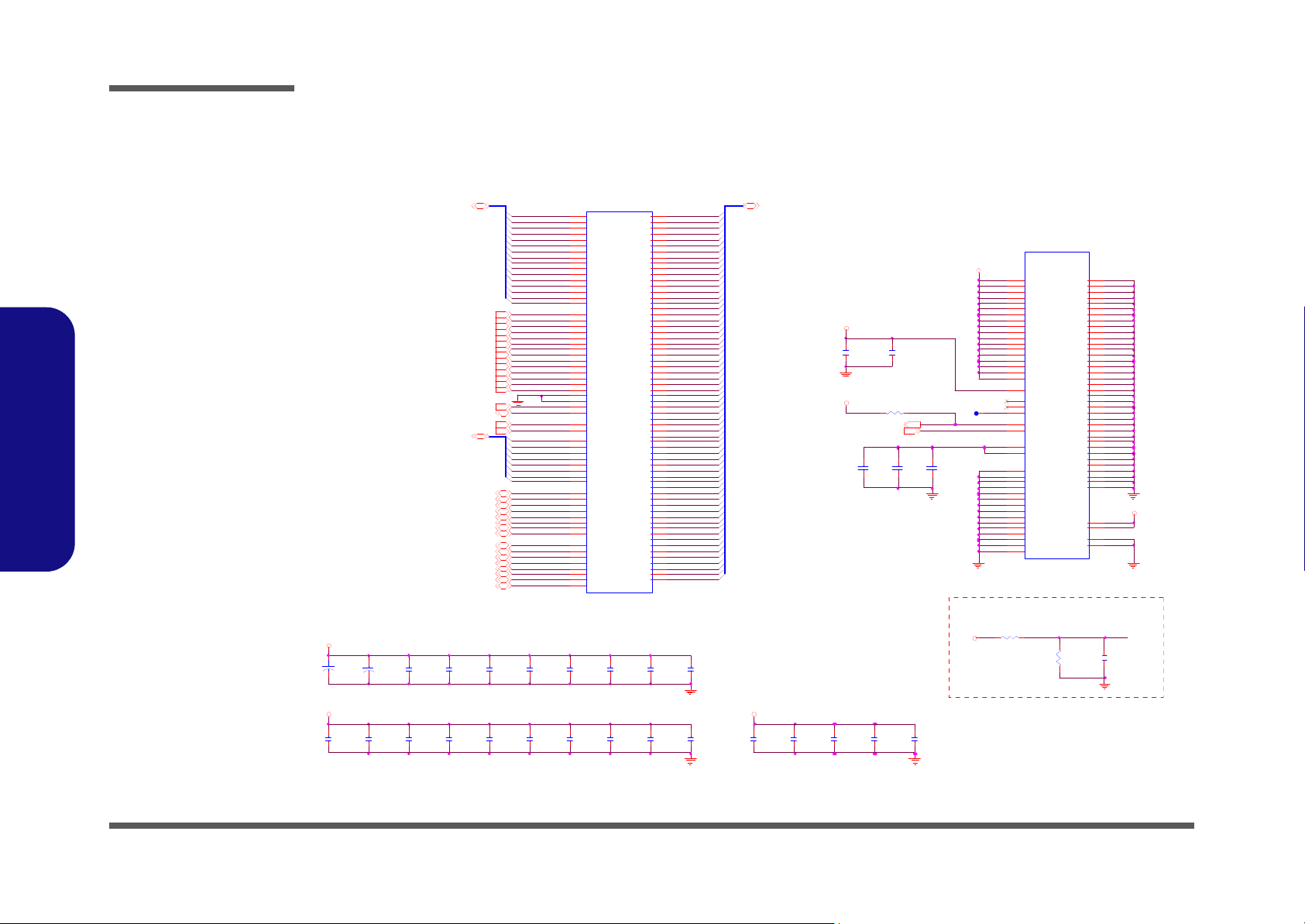

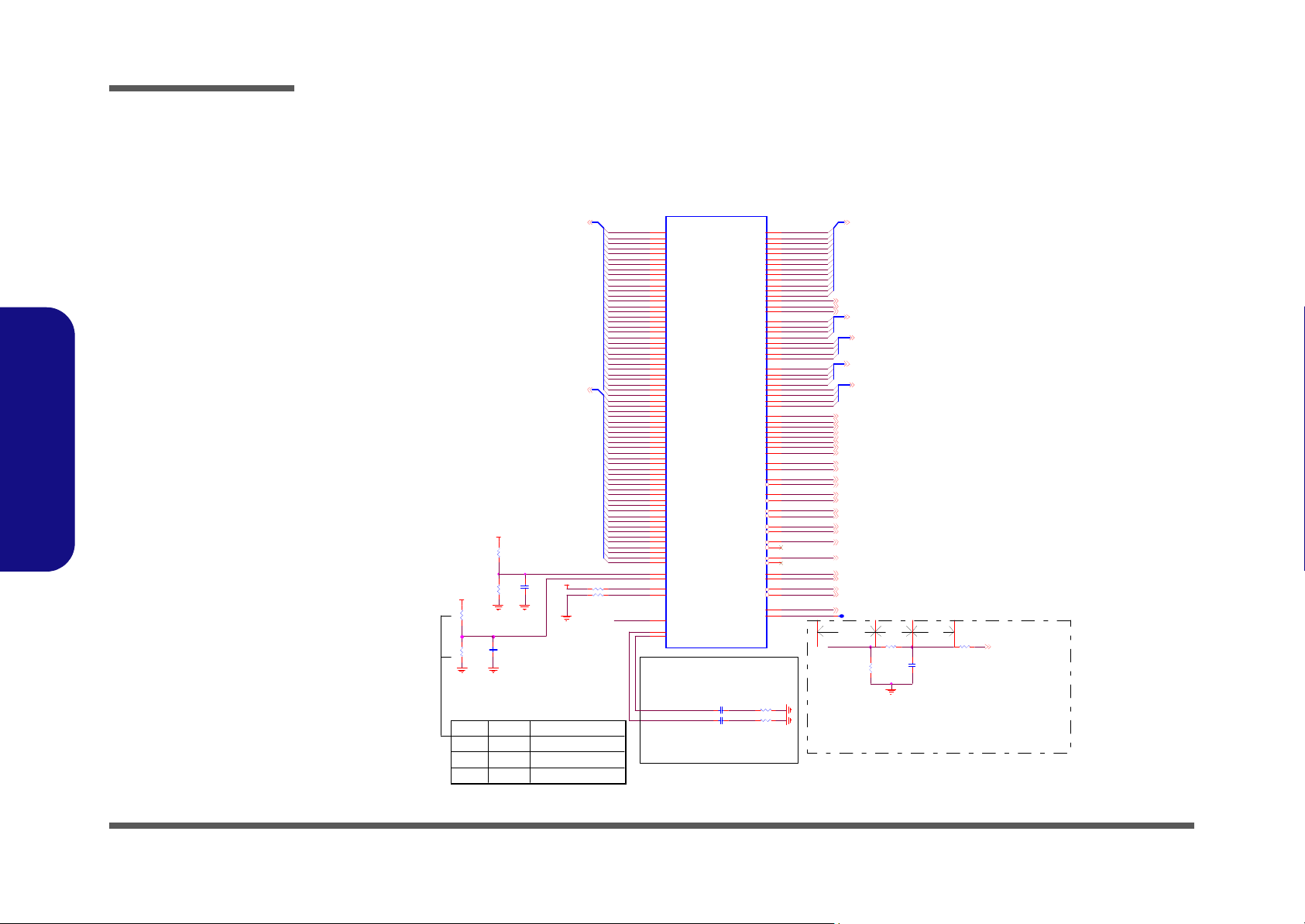

ONTARIO MEM & PCIE I/F, AP

Sheet 2 of 41

ONTARIO MEM &

PCIE I/F, AP

VG A_RXP37

VG A_RXP27

VG A_RXN 27

VG A_RXN 37

MEM _D A TA6 3

C10 0.1u_10V_X7R_04

MEM _D A TA4

C11 0.1u_10V_X7R_04

C12 0.1u_10V_X7R_04

MEM _D A TA3 5

C13 0.1u_10V_X7R_04

C_UMI_P_RX015

C14 0.1u_10V_X7R_04

C_UMI_N_RX015

MEM _D A TA5

C_UMI_P_RX115

C_UMI_N_RX115

C_UMI_N_RX215

C_UMI_P_RX215

C15 0.1u_10V_X7R_04

C_UMI_P_RX315

C_UMI_N_RX315

C16 0.1u_10V_X7R_04

MEM _D A TA3 6

C84 2

10u_6.3V_X5R_06

C_U MI_P_TX0 15

C_U MI_N _ TX0 15

C_U MI_N _ TX1 15

C_U MI_P_TX1 15

C_U MI_N _ TX2 15

C_U MI_P_TX2 15

C_U MI_N _ TX3 15

C_U MI_P_TX3 15

MEM _D A TA6

R 1 1. 27K_1%_04

MEM _D A TA3 7

MEM _D A TA7

MEM _ DQ S_ H05,6

MEM_EVENT#5,6

MEM_ADDR[15:0]5,6

MEM _D A TA3 9

MEM_CLK_H 05

MEM _D A TA8

MEM _D A TA3 8

MEM _D A TA9

MEM_BANK15,6

MEM_BANK25,6

MEM _D A TA4 0

MEM _D A TA1 0

ONTARIO (2. 0)

PA RT 1 O F 5

MEMO RY I/F

U1E

ONTARIO_APU

V17

M_WE_L

V19

M_CA S_L

U18

M_RA S_L

V16

M1_CS _L1

U17

M1_CS _L0

W16

M0_CS _L1

T17

M0_CS _L0

W15

M1_O D T 1

U19

M1_O D T 0

V15

M0_O D T 1

W19

M0_O D T 0

E15

M_CK E1

F15

M_CK E0

N17

M_EV ENT _L

L23

M_RE SET _L

L17

M_C LK_L3

L18

M_CLK_H3

N19

M_C LK_L2

N18

M_CLK_H2

M1 8

M_C LK_L1

M1 9

M_CLK_H1

M1 6

M_C LK_L0

M1 7

M_CLK_H0

AC16

M_DQS_L7

AB16

M_DQS_H7

AC21

M_DQS_L6

AC20

M_DQS_H6

V22

M_DQS_L5

W22

M_DQS_H5

P22

M_DQS_L4

R22

M_DQS_H4

J23

M_DQS_L3

J22

M_DQS_H3

E22

M_DQS_L2

E23

M_DQS_H2

A20

M_DQS_L1

B20

M_DQS_H1

B16

M_DQS_L0

A16

M_DQS_H0

AA16

M_DM7

AB20

M_DM6

V23

M_DM5

P23

M_DM4

H22

M_DM3

D21

M_DM2

B19

M_DM1

D15

M_DM0

F16

M_BA NK2

T18

M_BA NK1

R18

M_BA NK0

G15

M_AD D15

E16

M_AD D14

W17

M_AD D13

E18

M_AD D12

F17

M_AD D11

T19

M_AD D10

E19

M_AD D9

F19

M_AD D8

G18

M_AD D7

H15

M_AD D6

G17

M_AD D5

H17

M_AD D4

H18

M_AD D3

J17

M_AD D2

H19

M_AD D1

R17

M_AD D0

M22

M_ZVDDIO_MEM_S

M23

M_VREF

AC15

M_DATA63

AB15

M_DATA62

AB18

M_DATA61

AC18

M_DATA60

AC14

M_DATA59

AB14

M_DATA58

Y16

M_DATA57

AC17

M_DATA56

Y18

M_DATA55

AB19

M_DATA54

AA20

M_DATA53

AA23

M_DATA52

AA18

M_DATA51

AC19

M_DATA50

AB22

M_DATA49

Y20

M_DATA48

Y21

M_DATA47

W23

M_DATA46

U23

M_DATA45

T21

M_DATA44

Y22

M_DATA43

Y23

M_DATA42

V21

M_DATA41

V20

M_DATA40

T22

M_DATA39

R23

M_DATA38

P20

M_DATA37

M20

M_DATA36

T23

M_DATA35

T20

M_DATA34

P21

M_DATA33

N23

M_DATA32

K23

M_DATA31

K20

M_DATA30

H20

M_DATA29

G23

M_DATA28

K21

M_DATA27

K22

M_DATA26

H23

M_DATA25

H21

M_DATA24

F21

M_DATA23

F20

M_DATA22

D22

M_DATA21

C22

M_DATA20

F22

M_DATA19

F23

M_DATA18

D23

M_DATA17

C23

M_DATA16

C20

M_DATA15

A21

M_DATA14

B18

M_DATA13

A18

M_DATA12

D20

M_DATA11

B21

M_DATA10

A19

M_DATA9

C18

M_DATA8

D16

M_DATA7

C16

M_DATA6

C14

M_DATA5

A14

M_DATA4

D18

M_DATA3

A17

M_DATA2

A15

M_DATA1

B14

M_DATA0

MEM_CLK_L15

MEM_CLK_L26

MEM_CLK_H 26

MEM_CLK_L36

MEM_CLK_H 36

MEM _D A TA4 1

MEM _D A TA1 1

be dir ec tl y to th e pla n e with ou t a long tr ace

R6 c onnecti on to VD DIO_SU S s hou ld

Note: Open the sodlermask for Vias on Mem interface

MEM _D A TA1 2

MEM _D A TA4 2

MEM _ CKE 15, 6

MEM _ CKE 05, 6

ONTARIO (2.0)

PART 2 OF 5

UMI I/F

PCIE I/F

U1A

ONTARIO_APU

AB7

P _UMI _RX N3

AC7

P_UMI_RXP3

AC10

P _UMI _RX N2

AB10

P_UMI_RXP2

Y10

P _UMI _RX N1

AA10

P_UMI_RXP1

Y12

P _UMI _RX N0

AA12

P_UMI_RXP0

Y14

P_ZVDD_10

Y3

P_GPP_ RXN3

Y4

P_GPP_ RXP3

AA2

P_GPP_ RXN2

AA1

P_GPP_ RXP2

AC4

P_GPP_ RXN1

AB4

P_GPP_ RXP1

Y6

P_GPP_ RXN0

AA6

P_GPP_ RXP0

AC8

P _UMI _TX N3

AB8

P_UMI_TXP3

Y8

P _UMI _TX N2

AA8

P_UMI_TXP2

AB11

P _UMI _TX N1

AC11

P_UMI_TXP1

AC12

P _UMI _TX N0

AB12

P_UMI_TXP0

AA14

P_ ZVSS

V4

P_G PP_TX N3

V3

P_G PP_TX P3

Y2

P_G PP_TX N2

Y1

P_G PP_TX P2

AC3

P_G PP_TX N1

AB3

P_G PP_TX P1

AC6

P_G PP_TX N0

AB6

P_G PP_TX P0

C844

0.1u_10V_X7R _04

MEM _D A TA1 3

MEM _D A TA4 3

DIMM0_ODT15

DIMM0_ODT05

DIMM1_ODT16

DIMM1_ODT06

MEM_CLK_L05

D IMM 0_C S#15

D IMM 0_C S#05

D IMM 1_C S#16

D IMM 1_C S#06

MEM _D A TA1 4

MEM _D A TA4 4

PL ACE NEA R U1

An al og The rma l Sen sor

3

2

1

C364

0.1u_10V_X5R _04

Q15

G711ST9U

OU T1VC C

2

GND

3

C365

0.1u_10V_X5R_04

1:2 (4mi ls:8 mils )

THERM_VOLT 27

3. 3V

R679 *0_04

MEM _D A TA1 5

MEM _D A TA4 5

1.5V

MEM _D A TA1 6

MEM _D A TA4 6

C5 * 0. 1u_ 1 0 V _ X7R _04

MEM _D A TA1 7

MEM _D A TA4 7

ON _Z V SSON _Z V DD

RO UTE A- LIN K D IF F P AI R @ 85 O HM + / - 10 %

MEM _ RAS #5, 6

MEM _ WE #5, 6

MEM _ CAS #5, 6

MEM _D A TA1 8

1VS

R680 0_04

MEM _D A TA4 8

MEM _D A TA1 9

MEM _D A TA4 9

MEM _D A TA2 0

MEM_ADDR0

MEM_ADDR10

MEM_ADDR12

MEM_ADDR11

MEM_ADDR13

MEM_ADDR14

MEM_ADDR2

MEM_ADDR3

MEM_ADDR5

MEM_ADDR15

MEM_ADDR4

MEM_ADDR1

MEM_ADDR8

MEM_ADDR7

MEM_ADDR9

MEM_ADDR6

MEM _D A TA5 0

M EM_R ESE T#5,6

MEM_DM1

MEM_DM3

MEM_DM0

MEM_DM2

C843

1000p_50V_X7R _04

MEM_DM7

MEM_DM5

MEM_DM6

MEM_DM4

R2 2K_1%_04

MEM _D A TA2 1

MEM_Z VDDIO

MEM _D A TA5 1

R678

1K_1%_04

MEM _ DQ S_ H15,6

MEM _D Q S_ L05,6

MEM _D Q S_ L25,6

MEM _ DQ S_ H25,6

MEM _D Q S_ L15,6

MEM _ DQ S_ H45,6

MEM _D Q S_ L35,6

MEM _ DQ S_ H35,6

MEM _ DQ S_ H55,6

MEM _D Q S_ L45,6

MEM _D Q S_ L65,6

MEM _ DQ S_ H65,6

MEM _D Q S_ L55,6

MEM _D Q S_ L75,6

MEM _ DQ S_ H75,6

MEM _D A TA2 2

MEM_DM[7:0]5,6

MEM_B ANK05,6

For W250BAQ

MEM_DATA[63:0] 5,6

MEM _D A TA5 2

MEM _D A TA2 3

ONTARIO MEM & PCIE I/F, AP

MEM _D A TA5 3

VGA_R XN07

VGA_R XP17

VGA_R XN17

C6 * 0. 1u_ 1 0 V _ X7R _04

VGA_R XP07

MEM _D A TA2 4

MEM _D A TA5 5

MEM _D A TA2 5

MEM _D A TA5 4

MEM _D A TA2 6

R 6 39.2_1%_04

MEM_CLK_H 15

R681

1K_1%_04

MEM _D A TA5 6

MEM _D A TA2 7

C1 * 0. 1u_ 1 0 V _ X7R _04

C2 * 0. 1u_ 1 0 V _ X7R _04

C3 * 0. 1u_ 1 0 V _ X7R _04

MEM _D A TA2 8

C4 * 0. 1u_ 1 0 V _ X7R _04

MEM _D A TA0

MEM _D A TA5 7

VGA_ TXN 0 7

VGA_ TXP0 7

VTT_MEM

VGA_ TXN 1 7

VGA_ TXP1 7

MEM _D A TA2 9

MEM _D A TA5 8

C7 * 0. 1u_ 1 0 V _ X7R _04

MEM _D A TA3 0

MEM _D A TA5 9

MEM _D A TA3 1

MEM _D A TA6 0

MEM _D A TA1

MEM _D A TA3 2

VGA_ TXP3 7

VGA_ TXN2 7

VGA_ TXN3 7

VGA_ TXP2 7

MEM _D A TA6 1

C8 * 0. 1u_ 1 0 V _ X7R _04

MEM _D A TA2

MEM _D A TA3 3

MEM _D A TA6 2

MEM _D A TA3

1.5V

C9 0.1u_10V_X7R_04

MEM _D A TA3 4

Schematic Diagrams

B.Schematic Diagrams

ONTARIO MEM & PCIE I/F, AP B - 3

Schematic Diagrams

R38

0_04

1.8VS

R51

1K_04

CPU_SVD

APU _ PWR G D

R 593 100K_04

R54 * 1 K_ 04

R53 * 1 K_ 04

R71 *0_04J108_PLLTST1 APU _ TEST18 _P L LT E ST1

APU _ TEST19 _P L LT E ST0J108_PLLTST0 R70 *0_04

R42 51_04

R43 51_04

DBREQ# R69 300_1% _04

R 50 0_04

DBRDY

5V S

ONTARIO DISPLAY/CLK/MISC

APU _TE ST36

R40 510_1%_04

CPU _T HE RM TRIP #16

APU _CL KP15

CPU_SVD35

CP U_S VC35

H DT+ H EAD ER / PLAC E O N TO P

POR TC_H PD 21

APU _CL KN15

1.8VS

LVDS-LCLKP20

LVDS-LCLKN20

R31 *0_04

R32 *0_04

1. 8V S 1.8VS

APU _S ID

APU _P WR GD15, 35

LD T_R ST#15

R35 0_04

R36 0_04

R 65 *0_04

R59

1K_04

LDT_R ST#

R66 *10K_04

R41 510_1%_04

R44 *1K_04

AP U_TA LER T #17,27

R 591 100K_04

A LLO W _LD TSTP 1 5

R 58 1K_04

1. 8V S

1.8VS

C 23 0.1u_16V_Y 5V_04

C 24 0.1u_16V_Y 5V_04

1.8VS

LDT_R ST#

J1

* HD R 10X2 - B LU E - VER TICAL P L UG

1

CP U_ VD DIO

2

CPU_TCK

3

GND

4

CP U_T M S

5

GND

6

CP U_ TD I

7

GND

8

CP U_T DO

9

CP U_ TR ST_ L

10

CP U_P W ROK _B UF

11

CP U_ DB RDY3

12

CPU_RST_L_BUF

13

CP U_ DB RDY2

14

C PU _DB RD Y0

15

CP U_ DB RDY1

16

CPU_DBREQ_L

17

GND

18

CP U_ PLLT ES T0

19

CP U_ VD DIO

20

CP U_ PLLT ES T1

AP U_ SID16

AP U_ SIC16

ONT ARIO (2.0)

PA RT 3 OF 5

TEST VGA DAC

JTAG CT RL

SER

CLK

DP MISC

DISPLAYPORT 0DISPL AYPORT 1

ANALOG/D IS PLAY/MISC

U1B

ON TA R IO_ A PU

V5

RS VD _3

W11

RS VD _2

B4

RS VD _1

F1

VS S_ SENSE

F3

VDDIO_MEM_S_S ENS E

G1

VDDCR_CPU_SENSE

F4

VDDCR_NB_SENSE

M1

DB RE Q _L

M3

DB RD Y

M4

TR ST_L

P2

TMS

P1

TCK

N1

TD O

N2

TD I

T2

AL ER T_L

U2

TH ERM TRIP_L

U1

PR OCH O T_L

T4

PW RO K

T3

RE SE T_L

P4

SI D

P3

SIC

J2

SV D

J1

SVC

D1

DISP_CLKIN_L

D2

DISP_CLKIN_H

V1

CLKIN_L

V2

CLKIN_H

C8

LT DP0_TX N3

D8

LT DP0_TX P3

B6

LT DP0_TX N2

A6

LT DP0_TX P2

C6

LT DP0_TX N1

D6

LT DP0_TX P1

A5

LT DP0_TX N0

B5

LT DP0_TX P0

B10

TD P1_ TXN3

A10

TD P1_ TXP3

C10

TD P1_ TXN2

D10

TD P1_ TXP2

A9

TD P1_ TXN1

B9

TD P1_ TXP1

B8

TD P1_ TXN0

A8

TD P1_ TXP0

T1

DMAACTIVE_L

K3

TEST38

R5

TEST37

N5

TEST36

H4

TEST35

T1 5

T EST34_L

U15

TE S T34_H

J1 9

T EST33_L

J1 8

TE S T33_H

M2 1

TEST31

M5

T EST28_L

L5

TE S T28_H

K2

T EST25_L

K1

TE S T25_H

M2

TEST19

L2

TEST18

L1

TEST17

K4

TEST16

E4

TEST15

T5

TEST14

R6

TEST6

R2

TEST5

R1

TEST4

D12

DAC_ZVSS

D4

DAC _S DA

F2

DAC_SCL

E2

DA C_V SY NC

E1

DA C_H SY NC

B13

DA C_B LU EB

A13

DAC_BLUE

B12

DA C_G REE NB

A12

DAC_GREEN

D13

D AC_ RE DB

C12

DAC_RED

D3

LT DP0_H PD

B3

LTD P0_ AUXN

A3

LTD P0_ AUXP

C1

TDP1_HPD

C2

TD P1_ AUXN

B2

TD P1_ AUXP

H1

DP_VARY_BL

H2

DP_DIGON

G2

DP_ BL ON

H3

DP_ ZV SS

DA C_ H S Y N C 2 1

DA C_ VS YN C 21

DAC_DDCADA TA 21

DAC_DDCACLK 21

APU _ TRST#

APU _S IC

R19 1K _04

R15 *1K_04

3.3VS

APU_THERMTRIP#

APU _ SIC

APU _ SID

3.3V

APU _ TA LERT#

R22 1K _04

R24 1K _04

R20 1K _04

R17 1K _04

PRO C HO T#

HDMIB_D2B P21

ON_VARY

ON_DIGON

ON_BLON

HDMIB_D2B N21

HDMIB_D0B N21

HDMIB_D1B P21

HDMIB_D1B N21

HDMIB_CLKBP21

HDMIB_CLKBN21

HDMIB_D0B P21

LVDS -L2P20

LVDS -L2N20

LVDS -L1P20

LVDS -L0N20

LVDS -L0P20

LVDS -L1N20

HDMI_D D C_CLK 21

HD MI_D D C_D A TA 2 1

HDMI_DDC_DATA

HDMI_DDC_CLK

R67 *10K_04

R68 *10K_04

R56

1K_04

HD MI

LVDS

C22

*150pF_N PO_50V _0402

C21

*150pF_N PO_50V_0402

R52

1K_04

R 598 0_04

LD TRST_R

LD TPWR GD _R

R37 1K _0 4

Rese rve

R25 0_ 0 4

R61 1K_04APU _ TCK

1.8VS

APU _TD I

APU _TM S

APU _TC K

APU _TD O

APU _TR S T#

R63 1K_04APU _ TMS

R64 1K_04

APU _SIC

APU _SID

APU _ TDI

APU _ TDO

R30

499_1% _04

DB RD Y

DB REQ #

SB_PROCHOT#17

CPU_VDDNB_RUN_FB_H35

PROCHOT#

APU_B P1_TSTUPD _US CLK1

AP U_ PW RG D

APU_TE ST18_PLLTEST1

APU_TE ST25_L_BYPASSCLK

APU_TE ST19_PLLTEST0

APU_TE ST25_H _BYPASSC LK

APU_TE ST33_L_M_C LKTST_L

APU_TE ST33_H _M_C LKTST_H

APU _TE ST35

APU _TH ER MD A

R 62 *100K_04

APU _TH ER MD C

APU_THERMTRIP#

CPU_VDDNB_RUN_FB_L35

CPU_VDD0_RUN_FB_L35

LV D S _ D D C _ D A T A 2 0

LV D S _ D D C _ C LK 2 0

LVDS_DDC_DATA

LVDS_DDC_CLK

DAC _RS ET

LDTRST_R

LDTPW RGD_R

ON _ D I GO N

LD T_R ST#

ON _ V A R Y

ON _ B L O N

PR OC HO T #

ONDP_CALR

ON _ D MA A CTI V E #

VDDCR_CPU_S ENSE

VD DIO _SU S_ SEN SE

VD DC R_N B _ SEN SE

VSS_SE NS E

R39 1K _0 4

R 21 150_1% _04

R12 1K_04

R 592 100K_04

R 14 300_1%_04

R 60 *100K_04

PRO C HO T #15

R11 1K_04

APU_PWRGD

U44 *74AHC1G08GW

1

2

5

43LDT_R ST#_BUF

APU _ PWR G D_ BU F

R34 0_04

R33 0_04

LDT_R ST#_B UF

1. 8V S

NB_ENAVDD 20

R13

300_1%_04

S MC _CP U_THE RM 16,17,27

S MD _CP U_THE RM 16,17,27

R 45 *10m il_s hort_04

CPU_VDD0_RUN_FB_H35

C840

0.1u_16V_Y 5V_04

BLO N 20

R 16 0_04

R 46 *10m il_s hort_04

CPU_SVC

H DT_TRST#

DAC_RED 21

DAC_BLUE 21

DAC_GREEN 21

R27 150_1%_04

R28 150_1%_04

R 48 *10m il_s hort_04

R29 150_1%_04

APU _ PWR G D_ BU F

DISP _CLKN15

DISP _CLKP15

R 49 *10m il_s hort_04

U45 *74AHC1G08GW

1

2

5

4

3

1. 8V S

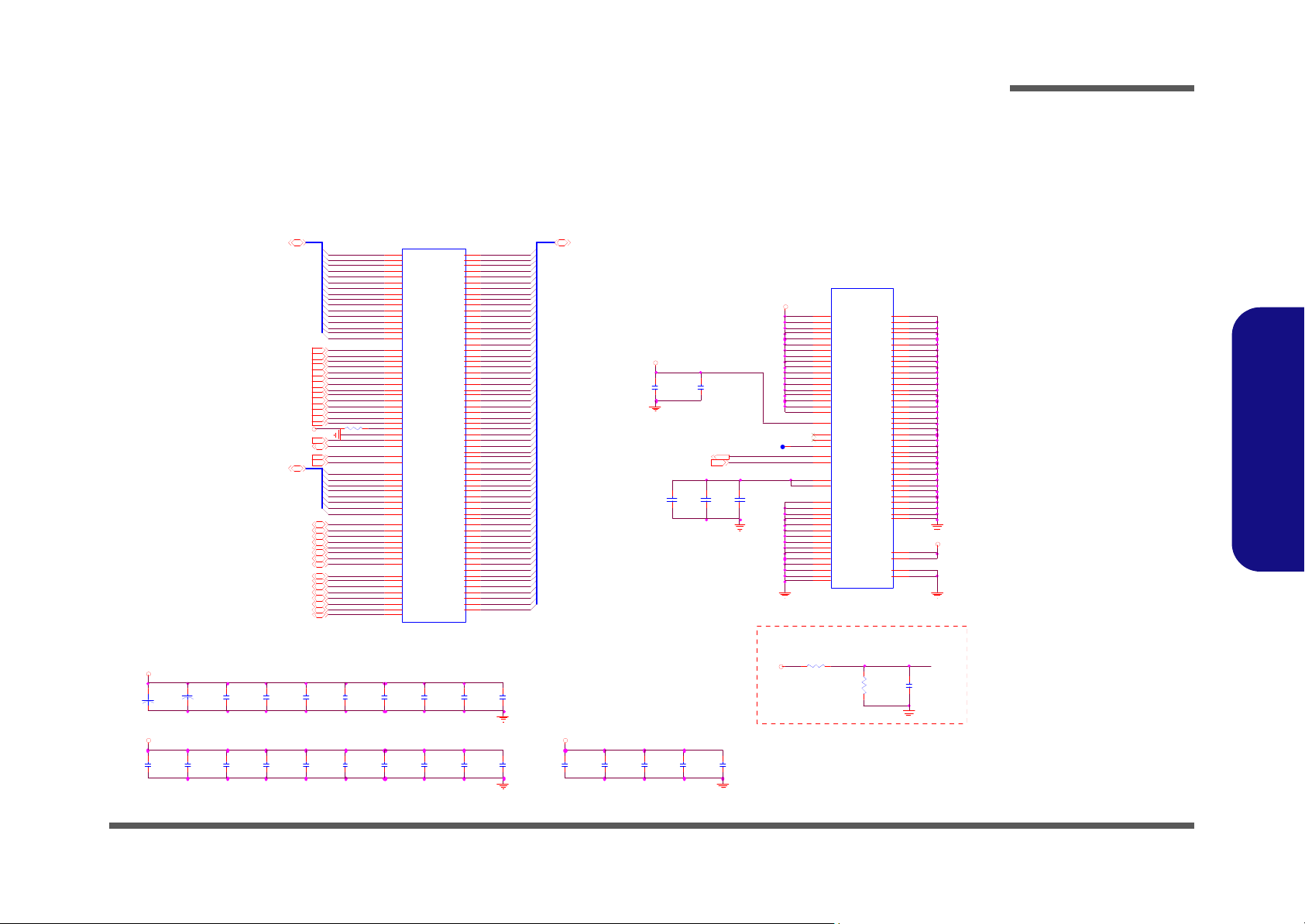

Sheet 3 of 41

ONTATIO

DISPLAY/ CLK/

MISC

ONTATIO DISPLAY/ CLK/ MISC

B.Schematic Diagrams

B - 4 ONTATIO DISPLAY/ CLK/ MISC

ONTARIO POWER & DECOUPLING

1.8VS

C84

180P_50V_N PO_04

C77

10u_6.3V_X5R _06

C76

10u_6.3V_X5R_06

C78

10u_6.3V_X5R _06

C79

10u_6.3V_X5R_06

VD DC R _CP U

C85

180P_50V _NPO_04

C30

10u_6.3V_X5R_06

C89

1u_6.3V_X5R_04

C92

1u_6.3V_X5R_04

C46

10u_6.3V_X5R _06

C45

10u_6.3V_X5R _06

C96

0.1u_10V_X5R_04

C47

10u_6.3V_X5R _06

C94

0.1u_10V_X5R _04

C48

10u_6.3V_X5R_06

C50

10u_6.3V_X5R _06

C49

10u_6.3V_X5R _06

C95

0.1u_10V _X5R _04

C91

1u_6. 3V _X5R _04

C97

0. 1u_10V_X5R_04

C90

1u_6.3V_X5R_04

C68

180P_50V_N PO_04

C86

180P_50V _NPO_04

VD DC R _ CPU

3.3VS

C87

180P_50V_NP O_04

1.5V

C37

10u_6.3V_X5R _06

C38

10u_6.3V_X5R_06

C70

180P _50V_NPO _04

C39

1u_6.3V_X5R_04

C69

180P_50V _NPO_04

C41

0.1u_10V_X5R_04

C40

1u_6.3V_X5R_04

C42

0.1u_10V_X5R_04

.

L63

HCB1608KF-121T25

C43

1u_6.3V_X5R_04

C55

1u_6.3V_X5R_04

C59

0. 1u_10V_X5R_04

C60

0.1u_10V_X5R _04

C61

0.1u_10V _X5R _04

C88

0.1u_10V_X5R_04

C63

0. 1u_10V_X5R_04

C62

0.1u_10V_X5R_04

EMC CAPS

1.5V

VDD PL_10

1V S

1VS

ONTARIO (2.0)

PART 5 OF 5

GR O UN D

U1D

ONTARIO_APU

N11

V SS _49

N8

V SS _48

N6

V SS _47

N4

V SS _46

M7

V SS _45

L22

V SS _44

L20

V SS _43

L13

V SS _42

L11

V SS _41

L8

V SS _40

L6

V SS _39

L4

V SS _38

K14

V SS _37

K10

V SS _36

J20

V SS _35

J7

V SS _34

J5

V SS _33

J4

V SS _32

H13

V SS _31

H11

V SS _30

H6

V SS _29

G2 2

V SS _28

G2 0

V SS _27

G1 2

V SS _26

G9

V SS _25

G7

V SS _24

G5

V SS _23

G4

V SS _22

F13

V SS _21

F11

V SS _20

F8

V SS _19

E20

V SS _18

E12

V SS _17

E9

V SS _16

E7

V SS _15

D19

V SS _14

D17

V SS _13

B15

V SS _12

D14

V SS _11

D11

V SS _10

D9

VSS_9

D7

VSS_8

D5

VSS_7

C4

VSS_6

B22

VSS_5

B17

VSS_4

B11

VSS_3

B7

VSS_2

A7

VSS_1

A11

VSSBG_DAC

AC 1 3

VS S_97

AC 9

VS S_96

AC 5

VS S_95

AB21

VS S_94

AB17

VS S_93

AB13

VS S_92

AB9

VS S_91

AB5

VS S_90

AB2

VS S_89

AA22

VS S_88

AA4

VS S_87

Y19

VS S_86

Y17

VS S_85

Y15

VS S_84

Y13

VS S_83

Y11

VS S_82

Y9

VS S_81

Y7

VS S_80

Y5

VS S_79

W20

VS S_78

W12

VS S_77

W7

VS S_76

W5

VS S_75

W4

VS S_74

W2

VS S_73

W1

VS S_72

V13

VS S_71

V11

VS S_70

V9

VS S_69

V8

VS S_68

U22

VS S_67

U20

VS S_66

U12

VS S_65

U7

VS S_64

U5

VS S_63

U4

VS S_62

T13

VS S_61

T11

VS S_60

T9

VS S_59

T6

VS S_58

R20

VS S_57

R7

VS S_56

R4

VS S_55

P14

VS S_54

P10

VS S_53

N22

VS S_52

N20

VS S_51

N13

VS S_50

ONTARIO (2.0)

PART 4 OF 5

POWER

U1C

ONTARIO_APU

U16

VDDIO_MEM_S_11

W18

VDDIO_MEM_S_10

R19

VDDIO_MEM_S_9

R16

VDDIO_MEM_S_8

N16

VDDIO_MEM_S_7

L19

VDDIO_MEM_S_6

L16

VDDIO_MEM_S_5

J16

VDDIO_MEM_S_4

E17

VDDIO_MEM_S_3

G19

VDDIO_MEM_S_2

G16

VDDIO_MEM_S_1

P13

VDDCR_NB_22

P11

VDDCR_NB_21

N14

VDDCR_NB_20

N12

VDDCR_NB_19

N10

VDDCR_NB_18

M1 3

VDDCR_NB_17

M1 2

VDDCR_NB_16

M1 1

VDDCR_NB_15

L14

VDDCR_NB_14

L12

VDDCR_NB_13

L10

VDDCR_NB_12

K13

VDDCR_NB_11

K11

VDDCR_NB_10

H12

VDDCR_NB_9

H9

VDDCR_NB_8

G13

VDDCR_NB_7

G11

VDDCR_NB_6

F12

VDDCR_NB_5

F9

VDDCR_NB_4

E13

VDDCR_NB_3

E11

VDDCR_NB_2

E8

VDDCR_NB_1

R8

VDDCR_CPU_15

N7

VDDCR_CPU_14

M8

VDDCR_CPU_13

M6

VDDCR_CPU_12

L7

VDDCR_CPU_11

J8

VDDCR_CPU_10

J6

VDDCR_CPU_9

H7

VDDCR_CPU_8

H5

VDDCR_CPU_7

G8

VDDCR_CPU_6

G6

VDDCR_CPU_5

F7

VDDCR_CPU_4

F5

VDDCR_CPU_3

E6

VDDCR_CPU_2

E5

VDDCR_CPU_1

A4

V DD _33

T12

VDD_1 0_4

V12

VDD_1 0_3

W13

VDD_1 0_2

U13

VDD_1 0_1

U11

V DD PL_10

W9

V DD _18_DAC

V7

VDD_1 8_7

T7

VDD_1 8_6

W6

VDD_1 8_5

U9

VDD_1 8_4

U6

VDD_1 8_3

W8

VDD_1 8_2

U8

VDD_1 8_1

C93

1u_6.3V_X5R_04

C56

1u_6.3V_X5R_04

C873

*10u_6.3V_X5R_06

C27

1u_6.3V_X5R_04

VD D CR _ CP U

1.8VS

R73 0_04

C57

1u_6. 3V _X5R _04

VD D CR _ NB

C71

180P_50V_NP O_04

C72

180P _50V _N PO_04

3. 3V S

VD D PL_ 10

C874

*10u_6.3V_X5R _06

1VS

C58

1u_6.3V_X5R_04

VDDA N_18_DA C

C29

1u_6.3V_X5R _04

C51

10u_6.3V_X5R_06

C64

0.1u_10V_X5R_04

C80

1u_6. 3V _X5R _04

C 875

*10u_6.3V _X5R_06

C53

*22u_6.3V_X5R_08

C44

10u_6.3V_X5R_06

1. 5V

C52

10u_6.3V_X5R_06

C73

0.1u_10V_X5R_04

C54

*22u_6.3V_X5R _08

C28

*1u_6.3V _X5R_04

VDDAN_18_DAC

C 872

*10u_6.3V_X5R _06

C75

10u_6.3V_X5R_06

VDDCR_NB

C871

*10u_6.3V_X5R _06

C 869

*10u_6.3V_X5R _06

C870

*10u_6.3V_X5R _06

C74

*0. 1u_10V_X7R_04

C35

1u_6. 3V _X5R _04

C34

10u_6.3V_X5R _06

C36

0.1u_10V_X5R_04

VD DC R _NB

C26

1u_6.3V_X5R _04

ONTARIO POWER & DECOUPLING

1.5V

1.8VS

C31

0. 1u_10V_X5R_04

C67

180P _50V_NPO _04

C65

0.1u_10V_X5R_04

C66

* 0.1u _1 0V_ X7R _04

C81

1u_6.3V _X5R _04

C82

1u_6. 3V _X5R _04

C32

10u_6.3V_X5R _06

C33

1u_6.3V_X5R_04

C83

*1u_6.3V_X5R_04

Sheet 4 of 41

ONTARIO POWER

& DECOUPLING

Schematic Diagrams

ONTARIO POWER & DECOUPLING B - 5

B.Schematic Diagrams

Schematic Diagrams

+

C104

*150u_4V_B _A

MEM_ADDR[15:0]2,6

INAGUA DDR3 SO-DIMMS A

SO-DIMM A

MEM_DATA3

MEM_DATA2

MEM_DATA1

MEM_DATA32

MEM_DATA31

MEM_DATA30

MEM_DATA29

MEM_DATA4

MEM_DATA39

MEM_DATA37

MEM_DATA36

MEM_DATA35

MEM_DATA34

MEM_DATA33

MEM_DATA44

MEM_DATA43

MEM_DATA42

MEM_DATA41

MEM_DATA40

MEM_DATA49

MEM_DATA38

MEM_DATA47

MEM_DATA46

MEM_DATA45

MEM_DATA54

MEM_DATA53

MEM_DATA52

MEM_DATA51

MEM_DATA28

MEM_DATA50

MEM_DATA56

MEM_DATA6

MEM_DATA5

MEM_DATA48

MEM_DATA55

MEM_DATA62

MEM_DATA61

MEM_DATA60

MEM_DATA58

MEM_DATA57

MEM_DATA11

MEM_DATA9

MEM_DATA8

MEM_DATA7

MEM_DATA59

MEM_DATA63

MEM_DATA16

MEM_DATA15

MEM_DATA14

MEM_DATA13

MEM_DATA12

MEM_DATA21

MEM_DATA10

MEM_DATA19

MEM_DATA18

MEM_DATA17

MEM_DATA26

MEM_DATA25

MEM_DATA24

MEM_DATA23

MEM_DATA0

MEM_DATA22

MEM_DATA20

MEM_DATA27

MEM_BANK02,6

MEM_BANK22,6

MEM_BANK12,6

C117

0.1u_16V_Y5V_04

+

C105

*220u_4V_V _A

C123

0.1u_16V_Y5V_04

C111

1u_6.3V_X5R_04

C120

0.1u_16V_Y5V_04

C112

1u_6.3V_X5R_04

C107

10u_10V_Y5V_ 08

C110

1u_6.3 V_X5R_04

C116

0.1u_16V_Y5V_04

C121

0.1u_16V_Y5V_04

C114

0.1u_16V_Y5V_04

C109

1u_6.3 V_X5R_04

C126

1u_6.3V_X5R_04

C119

0.1u_16V_Y5V_04

C99

0.1u_16V_Y5V_04

C106

10u_10V_Y5V_ 08

C127

1u_6.3V_X5R_04

R75 1K_04

C124

10u_10V_Y5V_08

C108

10u_10V_Y5V_ 08

JDI MM1A

DDRRK-2040 1-T R4B

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC#

83

A13

119

A14

80

A15

78

DQ0

5

DQ1

7

DQ2

15

DQ3

17

DQ4

4

DQ5

6

DQ6

16

DQ7

18

DQ8

21

DQ9

23

DQ10

33

DQ11

35

DQ12

22

DQ13

24

DQ14

34

DQ15

36

DQ16

39

DQ17

41

DQ18

51

DQ19

53

DQ20

40

DQ21

42

DQ22

50

DQ23

52

DQ24

57

DQ25

59

DQ26

67

DQ27

69

DQ28

56

DQ29

58

DQ30

68

DQ31

70

DQ32

129

DQ33

131

DQ34

141

DQ35

143

DQ36

130

DQ37

132

DQ38

140

DQ39

142

DQ40

147

DQ41

149

DQ42

157

DQ43

159

DQ44

146

DQ45

148

DQ46

158

DQ47

160

DQ48

163

DQ49

165

DQ50

175

DQ51

177

DQ52

164

DQ53

166

DQ54

174

DQ55

176

DQ56

181

DQ57

183

DQ58

191

DQ59

193

DQ60

180

DQ61

182

DQ62

192

DQ63

194

BA0

109

BA1

108

RAS#

110

WE#

113

CAS#

115

S0#

114

S1#

121

CKE0

73

CKE1

74

CK0

101

CK0#

103

CK1

102

CK1#

104

SDA

200

SCL

202

SA1

201

SA0

197

DM0

11

DM1

28

DM2

46

DM3

63

DM4

136

DM5

153

DM6

170

DM7

187

DQS0

12

DQS1

29

DQS2

47

DQS3

64

DQS4

137

DQS5

154

DQS6

171

DQS7

188

DQS0 #

10

DQS1 #

27

DQS2 #

45

DQS3 #

62

DQS4 #

135

DQS5 #

152

DQS6 #

169

DQS7 #

186

ODT0

116

ODT1

120

BA2

79

C113

1u_6.3 V_X5R_04

C128

1u_6.3V_X5R_04

C9 8

1u_6.3V_X5R_04

C115

0.1u_16V_Y5V_04

C118

0.1u_16V_Y5V_04

C125

1u_6.3V_X5R_04

JD IMM1B

DDRRK-20401-TR4B

VDD1

75

VDD2

76

VDD3

81

VDD4

82

VDD5

87

VDD6

88

VDD7

93

VDD8

94

VDD9

99

VDD10

100

VDD11

105

VDD12

106

VDDSPD

199

NC1

77

NC2

122

NC TEST

125

VREF_DQ

1

V SS1

2

V SS2

3

V SS3

8

V SS4

9

V SS5

13

V SS6

14

V SS7

19

V SS8

20

V SS9

25

V SS10

26

V SS11

31

V SS12

32

V SS13

37

V SS14

38

V SS15

43

VSS1 6

44

VSS1 7

48

VSS1 8

49

VSS1 9

54

VSS2 0

55

VSS2 1

60

VSS2 2

61

VSS2 3

65

VSS2 4

66

VSS2 5

71

VSS2 6

72

VSS2 7

127

VSS2 8

128

VSS2 9

133

VSS3 0

134

VSS3 1

138

VSS3 2

139

VSS3 3

144

VSS3 4

145

VSS3 5

150

VSS3 6

151

VSS3 7

155

VSS3 8

156

VSS3 9

161

VSS4 0

162

VSS4 1

167

VSS4 2

168

VSS4 3

172

VSS4 4

173

VSS4 5

178

VSS4 6

179

VSS4 7

184

VSS4 8

185

VSS4 9

189

VSS5 0

190

VSS5 1

195

VSS5 2

196

G2

GND2

G1

GND1

VTT2

204

VTT1

203

VREF_CA

126

RESET#

30

E VENT#

198

VDD13

111

VDD14

112

VDD16

118

VDD15

117

VDD17

123

VDD18

124

C122

0.1u_16V_Y5V_04

3.3VS

1.5V

1.5V

1.5V

VTT_MEM

VTT_MEM

1.5V

MEM_RAS #2,6

MEM_CLK_H12

MEM_RESET#2,6DI M M0_ODT12

MEM_WE#2,6

MEM_CAS #2,6

MEM_CLK_L12

DI M M0_ODT02

MEM_CKE02,6

MEM_CLK_H02

MEM_DATA[63:0] 2,6

MEM_CKE12,6

MEM_EVENT#2,6

MEM_CLK_L02

SDATA 06,10, 16

MEM_DM[ 7:0]2,6

20mils

MEM_ADDR1

R76 1K_1%_04

R77

1K _1% _04

CLOSE TO S O- DI MM A

C103

0.1u_10V_X5R_04

1.5V MVREF_DIMM0

(REV)4.0mm

MEM_DQS_L02,6

MEM_DQS_L72,6

MEM_DQS_H72,6

MEM_DQS_L52,6

MEM_DQS_L12,6

MEM_DQS_H12,6

MEM_DQS_H22,6

MEM_DQS_H62,6

MEM_DQS_L22,6

MEM_DQS_H42,6

MEM_DQS_H52,6

MEM_DQS_L62,6

MEM_DQS_L32,6

MEM_DQS_H02,6

MEM_DQS_H32,6

MEM_DQS_L42,6

MEM_ADDR2

MEM_ADDR3

MEM_ADDR4

MEM_ADDR5

DI M M0_C S#12

DI M M0_C S#02

MEM_ADDR6

MEM_ADDR7

MEM_ADDR8

MEM_ADDR9

MEM_ADDR10

MEM_ADDR11

MEM_ADDR12

MEM_ADDR13

MEM_ADDR14

SCL K06, 10,16

MEM_ADDR15

MEM_DM5

MEM_DM6

MEM_DM7

MEM_DM0

MEM_DM2

MEM_DM1

MEM_DM3

MEM_DM4

MV REF_DIMM 0

MEM_ADDR0

C100

1u_6.3V_X5R_04

C101

0.1u_10V_X7R_04

C102

1000p_50V_X7R_04

Sheet 5 of 41

INAGUA DDR3 SO-

DIMMS A

INAGUA DDR3 SO-DIMMS A

B.Schematic Diagrams

B - 6 INAGUA DDR3 SO-DIMMS A

INAGUA DDR3 SO-DIMMS B

MEM_ DATA34

MEM_ DATA33

MEM_ DATA32

MEM_ DATA31

MEM_ DATA30

MEM_ DATA29

MEM_ DATA4

MEM_ DATA3

MEM_ DATA2

MEM_ DATA1

MEM_ DATA28

MEM_ DATA50

MEM_ DATA49

MEM_ DATA38

MEM_ DATA47

MEM_ DATA46

MEM_ DATA45

MEM_ DATA44

MEM_ DATA43

MEM_ DATA42

MEM_ DATA41

MEM_ DATA40

MEM_ DATA39

MEM_ DATA37

MEM_ DATA36

MEM_ DATA35

MEM_ DATA59

MEM_ DATA63

MEM_ DATA62

MEM_ DATA61

MEM_ DATA60

MEM_ DATA58

MEM_ DATA57

MEM_ DATA56

MEM_ DATA6

MEM_ DATA5

MEM_ DATA48

MEM_ DATA55

MEM_ DATA54

MEM_ DATA53

MEM_ DATA52

MEM_ DATA51

MEM_ DATA0

MEM_ DATA22

MEM_ DATA21

MEM_ DATA10

MEM_ DATA19

MEM_ DATA18

MEM_ DATA17

MEM_ DATA16

MEM_ DATA15

MEM_ DATA14

MEM_ DATA13

MEM_ DATA12

MEM_ DATA11

MEM_ DATA9

MEM_ DATA8

MEM_ DATA7

MEM_DM0

MEM_DM2

MEM_DM1

MEM_DM3

MEM_DM4

MEM_DM5

MEM_DM6

MEM_DM7

MEM_ DATA20

MEM_ DATA27

MEM_ DATA26

MEM_ DATA25

MEM_ DATA24

MEM_ DATA23

MEM_ADDR0

MEM_ADDR4

MEM_ADDR3

MEM_ADDR2

MEM_ADDR1

MEM_ADDR15

MEM_ADDR14

MEM_ADDR13

MEM_ADDR12

MEM_ADDR11

MEM_ADDR10

MEM_ADDR9

MEM_ADDR8

MEM_ADDR7

MEM_ADDR6

MEM_ADDR5

MVREF_DIM M1

MVREF_DI MM1

R80

1K_1% _04

C156

1u_6.3V_X5R_04

C134

0.1u_10V_X5R_04

C158

1u_ 6.3 V_X5R_04

C142

1u_6.3V_X5R_04

C137

10u_10V_Y5 V_08

C1 38

10u_1 0V_Y5V _08

JDIMM2B

DDRRK- 20401-TP8 D

VDD1

75

VDD2

76

VDD3

81

VDD4

82

VDD5

87

VDD6

88

VDD7

93

VDD8

94

VDD9

99

VDD10

100

VDD11

105

VDD12

106

VDDSPD

199

NC1

77

NC2

122

NC TEST

125

VREF_DQ

1

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VSS1 6

44

VSS1 7

48

VSS1 8

49

VSS1 9

54

VSS2 0

55

VSS2 1

60

VSS2 2

61

VSS2 3

65

VSS2 4

66

VSS2 5

71

VSS2 6

72

VSS2 7

127

VSS2 8

128

VSS2 9

133

VSS3 0

134

VSS3 1

138

VSS3 2

139

VSS3 3

144

VSS3 4

145

VSS3 5

150

VSS3 6

151

VSS3 7

155

VSS3 8

156

VSS3 9

161

VSS4 0

162

VSS4 1

167

VSS4 2

168

VSS4 3

172

VSS4 4

173

VSS4 5

178

VSS4 6

179

VSS4 7

184

VSS4 8

185

VSS4 9

189

VSS5 0

190

VSS5 1

195

VSS5 2

196

G2

GND2

G1

GND1

VTT2

204

VTT1

203

VREF_CA

126

RESET#

30

EVENT#

198

VDD13

111

VDD14

112

VDD16

118

VDD15

117

VDD17

123

VDD18

124

C133

1000p_ 50V_ X7R_ 04

C1 48

0.1u_16V_Y5V_04

C144

1u_6.3V_X5R_04

JDIMM2A

DDRRK-20401-TP8D

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/ AP

107

A11

84

A12/ BC#

83

A13

119

A14

80

A15

78

DQ0

5

DQ1

7

DQ2

15

DQ3

17

DQ4

4

DQ5

6

DQ6

16

DQ7

18

DQ8

21

DQ9

23

DQ10

33

DQ11

35

DQ12

22

DQ13

24

DQ14

34

DQ15

36

DQ16

39

DQ17

41

DQ18

51

DQ19

53

DQ20

40

DQ21

42

DQ22

50

DQ23

52

DQ24

57

DQ25

59

DQ26

67

DQ27

69

DQ28

56

DQ29

58

DQ30

68

DQ31

70

DQ32

129

DQ33

131

DQ34

141

DQ35

143

DQ36

130

DQ37

132

DQ38

140

DQ39

142

DQ40

147

DQ41

149

DQ42

157

DQ43

159

DQ44

146

DQ45

148

DQ46

158

DQ47

160

DQ48

163

DQ49

165

DQ50

175

DQ51

177

DQ52

164

DQ53

166

DQ54

174

DQ55

176

DQ56

181

DQ57

183

DQ58

191

DQ59

193

DQ60

180

DQ61

182

DQ62

192

DQ63

194

BA0

109

BA1

108

RAS#

110

WE#

113

CAS#

115

S0#

114

S1#

121

CKE0

73

CKE1

74

CK0

101

CK0#

103

CK1

102

CK1#

104

SDA

200

SCL

202

SA1

201

SA0

197

DM0

11

DM1

28

DM2

46

DM3

63

DM4

136

DM5

153

DM6

170

DM7

187

DQS0

12

DQS1

29

DQS2

47

DQS3

64

DQS4

137

DQS5

154

DQS6

171

DQS7

188

DQS0#

10

DQS1#

27

DQS2#

45

DQS3#

62

DQS4#

135

DQS5#

152

DQS6#

169

DQS7#

186

ODT0

116

ODT1

120

BA2

79

C143

1u_ 6.3 V_X5R_ 04

C131

1u_6.3V_X5R_04

C151

0.1u_16V_Y5V_0 4

C140

1u_6.3V_X5R_04

C141

1u_6.3V_X5R_04

C145

0.1u_16V_Y5V _04

+

C136

*220u_4 V_V_A

C157

1u_6.3V_X5R_04

C129

1u_6.3V_X5R_04

C139

10u_10V_ Y5V_ 08

C1 59

1u_6.3V_X5R_04

C150

0.1u_16V_Y5V_04

C132

0.1u_10V_X7R_04

C154

0.1u_16V_Y5V_04

C155

10u_10V_Y 5V_ 08

C152

0.1u_16V_ Y5V_04

C130

0.1u_16V_Y5V_04

C149

0.1u_16V _Y5V_04

C146

0.1u_16V_Y5V_04

R79 1K_1%_04

C147

0.1u_16V_Y5V_04

C153

0.1u_16V_Y5V_04

1.5V

3. 3VS

1.5V

VTT_MEM

VTT_MEM

1.5V

1.5V

DIMM1_ODT12

MEM_R A S#2,5

MEM_CLK_H32

MEM_C A S#2,5

MEM_CLK_L32

MEM_RESET#2,5

MEM_CLK_H22

DIMM1_ODT02

MEM_W E #2,5

MEM_D A T A[63:0]2,5

MEM_C KE12,5

MEM_C KE02,5

SDATA05,10,16

MEM_EVENT#2,5

MEM_CLK_L22

MEM_BANK02,5

MEM_ADDR[15:0]2,5

MEM_ DM[7 :0 ]2, 5

DIMM1_CS#12

DIMM1_CS#02

MEM_BANK22,5

MEM_BANK12,5

MEM_DQS_H72,5

MEM_DQS_H62,5

MEM_DQS_H42,5

MEM_DQS_H22,5

MEM_DQS_L62,5

MEM_DQS_L42,5

MEM_DQS_L22,5

MEM_DQS_H32,5

MEM_DQS_L72,5

MEM_DQS_L02,5

MEM_DQS_L12,5

MEM_DQS_H12,5

MEM_DQS_L52,5

MEM_DQS_H52,5

MEM_DQS_L32,5

MEM_DQS_H02,5

C LOSE T O SO-DI MM B

INAGUA DDR3 SO-DIMMS B

20mils

SO-DIMM B

3.3VS

+

C135

560u_2 .5V_6.6*6.6*5.9

SCL K05,10,16

R7 84.7K_04

(REV)8.0mm

SN:6-86-24204-XXX

Sheet 6 of 41

INAGUA DDR3 SO-

DIMMS B

Schematic Diagrams

B.Schematic Diagrams

INAGUA DDR3 SO-DIMMS B B - 7

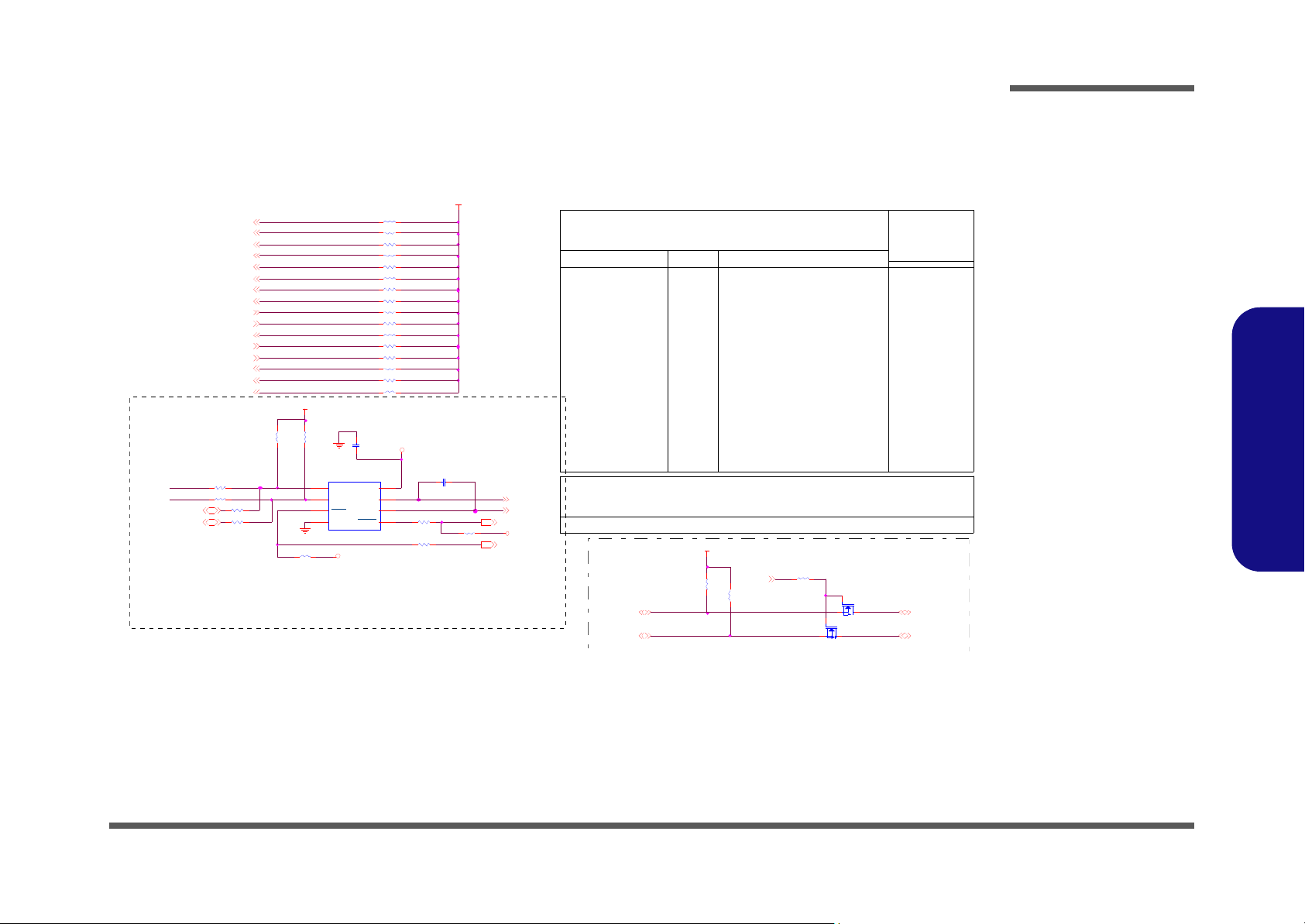

Schematic Diagrams

Sheet 7 of 41

Robson S3 PCIE/

LVDS 1/6

Robson S3 PCIE/ LVDS 1/6

B.Schematic Diagrams

B - 8 Robson S3 PCIE/ LVDS 1/6

Robson S3 MAIN 2/6

VBIOS FLASH RO M

R_DA C1

GPIO8

GPIO2 8_TDO

GPIO2 4_TRSTB

TMD S _T X1 P 2 1

TMD S _T X2 N 21

TMD S _T X2 P 2 1

TMD S _T X1 N 21

GPU_TALERT#10 , 17

TMD S _T X0 P 2 1

TMD S _T XC N 21

TMD S _T XC P 21

TMD S _T X0 N 21

*5.11K_1%_06

R 115

SB_MXM_CLKREQ#

*1 0K_ 04R68 5

ROBSON_GPIO1 6

NOTE: Designs t hat do not include an EEP RO M must still provide

a ccess to the ROM interface signals for debug purposes

GEN_ B

1M b i t SERIAL EEPROM is required for Park/Robson GDDR5 Design

(1.0V@110mA DPC_VDD10)

For P X_E N, ref er to t he BACO

refere n ce sche matics for detail

(1. 8V @2 0m A TSVDD)

(1. 0 V@1 2 5m A DPLL_ VDDC)

(1.8 V@7 5mA DPLL_PVDD)

GND Op t ion If

XO_IN/XO_IN2

not used

TS_FDO

XTALIN

PLA CE VREFG DIVIDER A N D CA P

CLOSE TO ASIC

XTALOUT

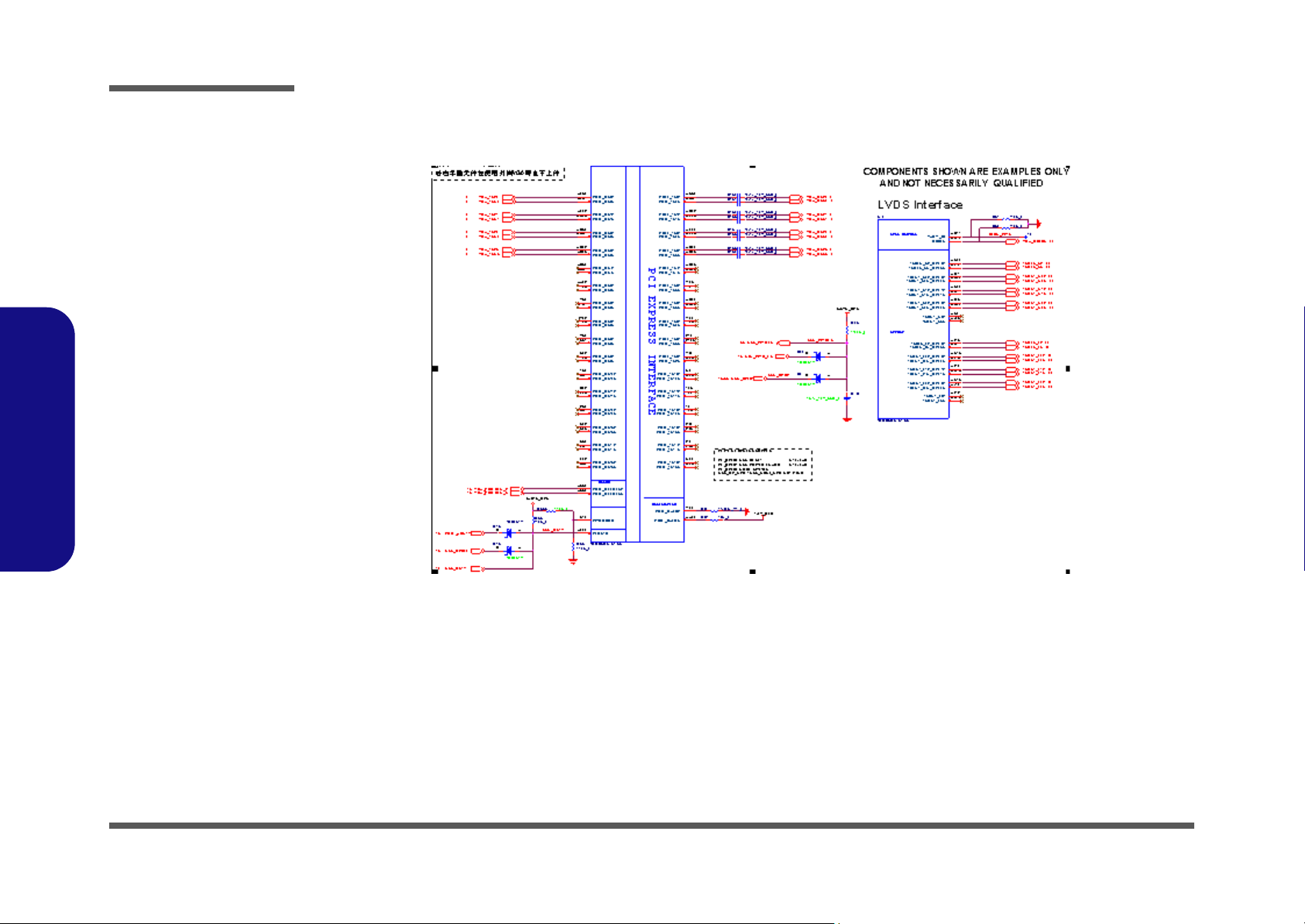

COMPONENTS SH OWN ARE EXAMPLES ONL Y

AND NO T NEC ESS AR ILY QUALIF I ED

HPD121

SC L

SDA

Access to SCL and SDA is

mandatory on BACO designs

for debug purposes

DNI

ROM_SO

HPD_4

GPIO10 SCK/WEb

GPIO22

GPIO9

CSb

SI/A1 6

T E ST EN

0. 1"~ 0.5"

(1. 8 V@1 5 0m A DPC_VDD1 8)

PX_EN

(3.3V@130mA A2VDD)

For Seymour,

DPC_PVDD is DPC_VDD18

DPC_PVSS and all DPC_VSSR are DP_VSSR

(1. 8V @2m A A2VD DQ)

1M b i t SERIAL EEPROM is optional for Sey m our GDDR5 Design

(1.8V @65mA AVDD)

(1. 8V @1 00 mA VDD1DI )

(1.8V@100mA V DD2DI)

MEM_ID1

MEM_ID0

MEM_ID2

MEM_ID3

MEM_ ID 0

MEM_ ID 1

MEM_ ID 2

MEM_ ID 3

B_DAC2

G_DAC2

R_DA C2

NC on Seymour

DDC1DATA 2 1

DDC1CLK 2 1

DDCDATA _AUX3N

AUX2N

AUX2P

DDC1DA TA

DDCDATA _AUX5N

DDCCLK _ AUX 3P

DDC1CL K

AUX1N

AUX1P

DDC6CL K

DDC2DA TA

DDC2CL K

GP I O24 _T R S TB

DDC6DA TA 21

DDC6CL K 21

DDCCLK _ AUX 5P

DDC6DA TA

GP I O25 _T D I

RB_DAC2

GB_DAC2

BB_DAC2

GPIO7_BLON

GP I O26 _T C K

GP I O27 _T MS

SB_MXM_CLKREQ#

GPIO21

GPIO22

GPIO20

GP I O_1 9_ C TF

Se ym ou r

DAC2 is NC on Seymou r

GP I O26 _T C K

GP I O24 _T R STB

GP I O25 _T D I

HPD1

GP I O28 _T D O

GP I O27 _T MS

GPIO6

GPIO0

GPIO7_BLON

GPIO13

GPIO12

GPIO1

GPIO11

GPIO10

MXM_SDA TA

GPIO9

GPIO8

GPIO2

HPD2

ROBSON_GPIO1 5

GPU_TALERT#

GP I O18 _H PD 3

GPIO5

MXM_SCL K

ROBSON _GPIO1536

GEN_ A

R716 *150_1%_04

G_DAC1

*5. 1 1K _1% _ 06R116

512Kbit

XTALOUT

XTALIN

SB_MXM_CLKREQ#16

SB_MXM_CLKR EQ#

*2.2K_04

R16 7

3. 3 V S_GPU

XTAL Opt ion

*1u_6.3 V _X 5 R_0 4

C 179

*1 0K_ 04R10 8

*0 . 1u _10 V_X5 R _0 4

C203

*1 0K_ 04R11 0

*10u_6.3V_X5R_06

C197

*10u_6.3V_X5R_06

C19 3

*1K_04R113

*EN25P05-50GCP

U5

S

1

VCC

8

Q

2

HOLD

7

VSS

4

D

5

C

6

W

3

L64

*H CB 16 08 KF -12 1T 25

*2 2p_ 50 V _NP O _0 4C200

*1u_6.3 V _X5R _0 4

C175

*10u_6.3V_X5R_06

C20 1

*1u_6.3 V _X 5 R_0 4

C 188

R715 *150_1%_04

L67

*HCB1608KF-121T25

*0_04R1 02

*0 _04

R117

*1 0u _6 .3 V_X 5R _0 6

C186

*10 u_6 . 3V_X 5R _ 06

C17 4

*1 0u_ 6. 3 V_X5 R _0 6

C180

*1 0K_ 04

R98

*0.1u_10V_X5R_04

C 182

*1 50_ 1% _0 4R1 03

*4 99 _1% _0 4

R112

*2 2p_ 50 V _NP O _0 4C196

R717 *150_1%_04

BB_DAC1

B_DAC1

R94 * 33_ 04

*0. 1 u_1 0V_ X5R _ 04

C17 6

G_DAC1 21

L70

*HCB1608KF-121T25

*1 0K_ 04R10 9

B_ DAC1 21

R_DA C1 21

*1 u_ 6. 3V_ X5 R _04

C19 8

HSYNC_DAC1 10, 2 1

VSYNC_DAC1 10,21

*1 0K_ 04R10 6

*1u_6.3 V _X 5 R_0 4

C 185

RB_DAC1

GB_DAC1

R92 * 33_ 04

*4 99 _1 %_0 4

R118

*0.1u_10V_X5R_04

C184

X2

*F SX 8L _27M Hz

12

*2 49 _1 %_0 4

R120

*715_1%_04R119

*1 0K _0 4

R99

*4 . 7K _0 4

R104

L68

*HCB1608KF-121T25

*1 u_ 6. 3V_ X5R _ 04

C19 0

*1 0K_ 04R10 7

*0.1u_10V_X5R_04

C17 8

L71

*HCB1608K F-1 21T25

*1 u_ 6. 3V_ X5R _ 04

C18 1

*1K_04R114

*1 0K_ 04R11 1

*1 0u _6 .3 V_X 5R _0 6

C183

*0.1u_10V_X5R_04

C170

L6 5

*HCB16 08KF -121T 25

L73

*HCB1608K F-1 21T25

*1u _6 . 3V_X 5R _ 04

C 194

*0.1u_10V_X5R_04

C187

*0.1u_10V_X5R_04

C171

*1u _6 . 3V_X 5R _ 04

C17 2

GPIO 7_B LON20

DP A

DP B

DVO

I2 C

G ENE RA L PU RPO SE I /O

DA C1

DA C2

DD C/ AU X

THE RM AL

PL L/ CLO CK

DP C

* R O B S O N XT S3

U4B

DMINUS

T2

DPL L_PVDD

AF14

DPLL_PVSS

AE14

DPL L_VD DC

AD14

DPL US

T4

DPC_ VSSR#1

U1

DVDAT A_ 7

AC7

T X2 M_DP C 0N

Y2

TX CC M_D PC 3N

U5

DPC_ VSSR#5

AA1

TX 1P_D P C1 P

Y4

DVDAT A_ 0

Y7

T X0 M_DP C 2N

V2

DPC_ VDD18#1

AC6

DPC_ PVDD

W6

DVDAT A_ 9

AD7

TX 2P_D P C0 P

AA3

DVDAT A_ 8

AC8

DPC_ VDD10#1

AA5

DVDAT A_ 12

AE8

DPC_ VDD10#2

AA6

DVCNTL_0

AE9

DVDAT A_ 3

AB4

DVDAT A_ 1

Y8

DVDAT A_ 11

AD9

DVDAT A_ 2

AB2

DVDAT A_ 10

AC10

DPC_ VDD18#2

AC5

TXCCP _DPC3P

V4

DVDAT A_ 4

AB7

DPC_ VSSR#2

W1

DVDAT A_ 5

AB8

TX 0P_D P C2 P

W3

DVDAT A_ 6

AB9

T X1 M_DP C 1N

W5

GENERICA

AB13

GENERICB

W8

GENERICC

W9

GENERICD

W7

GENERICE_HPD4

AD10

GPIO_ 0

U6

GPIO_ 1

U10

GPIO_10_ROMSCK

P2

GPIO_ 11

N6

GPIO_ 12

N5

GPIO_ 13

N3

GPIO_14_HPD2

Y9

GPIO_ 15_PWRCN TL_ 0

N1

GPIO_16_SSIN

M4

GPIO_17_THERMAL_INT

R6

GPIO_18_HPD3

W1 0

GPIO_ 19_CTF

M2

GPIO_ 2

T1 0

GPIO_ 20_PWRCN TL_ 1

P8

GPIO_21_BB_EN

P7

GPIO_ 22_ROMCSB

N8

GPIO_ 23_CL KREQB

N7

GPIO_ 3_SMBDATA

U8

GPIO_ 4_SMBCLK

U7

GPIO_ 5_AC_B ATT

T9

GPIO_ 6

T8

GPIO_7_BLON

T7

GPIO_ 8_R OMSO

P1 0

GPIO_ 9_R OMSI

P4

H2SYNC

AL1 3

HPD1

AC14

HSYN C

AH26

JT A G_ T CK

L3

JT A G_ T DI

L5

JT A G_ T DO

K4

JT A G_ T MS

L1

JT A G_ T RS TB

L6

DDCDATA_AUX3N

AC20DDCCLK_AUX3 P

AD20

TS _F D O

R5

TSVDD

AD17

TSVSS

AC17

VR E F G

AC16

VSS1 DI

AD23

VSS2 DI

AC19

XT AL I N

AM28

XT AL O U T

AK28

A2VDD

AE20

A2VDDQ

AE17

A2VSSQ

AE19

AUX1N

AD4

AUX1P

AD2

AUX2N

AD11

AUX2P

AD13

AVDD

AG24

AVSSQ

AE22

B

AH24

B2

AK10

B2B

AL9

BB

AG25

C

AH12

COMP

AJ9

DDC1CL K

AE6

DDC1DA TA

AE5

DDC2CL K

AC11

DDC2DA TA

AC13

DDC6CL K

AC1

DDC6DA TA

AC3

DDCDATA_AUX5N

AD16

DDCCLK_AUX5P

AE16

G

AL2 5

G2

AL1 1

G2B

AJ1 1

GB

AJ2 5

R

AM26

R2

AM12

R2B

AK12

R2SET

AG13

RB

AK26

RSET

AD22

SC L

R1

SD A

R3

TX0 M_DPA2N

AG5

TX0P_DPA2P

AG3

TX1 M_DPA1N

AH1

TX1P_DPA1P

AH3

TX2 M_DPA0N

AK1

TX2P_DPA0P

AK3

TX3 M_DPB2N

AM5

TX3P_DPB2P

AK6

TX4 M_DPB1N

AH6

TX4P_DPB1P

AJ7

TX5 M_DPB0N

AL7TX5P_DPB0P

AK8

TXCAM_DPA3N

AF4

TX C AP_ D PA 3 P

AF2

TXCBM_DPB3N

AM3TX CB P_ D PB 3 P

AK5

V2SYNC

AJ1 3

VDD1DI

AE23

VDD2DI

AD19

VSYNC

AJ2 7

Y

AM10

XO _ IN2

AB22 XO _ IN

AC22

TESTEN_LEGACY

AF24

DVCNTL_2

N9

DPC_ VSSR#3

U3

DPC_ PVSS

V6

DPC_ VSSR#4

Y6

DVCNTL_1

L9

DVCL K

Y11

DPC_CALR

J8

PX _E N

AB16

TESTEN

K7

*1 0u _6 . 3V_X 5R _ 06

C173

R95 * 33_ 04

L69

*HCB1608KF-121T25

R93 * 33_ 04

*1 0u _6 .3 V_X 5R _0 6

C189

*0 . 1u _10 V_X5 R _0 4

C195

*4.7K_04

R10 5

*10K_04

R97

*0_04R1 00

*0. 1 u_1 0V_ X5R _ 04

C19 2

L7 2

*HCB1608K F-1 21T25

*1M_0 4

R121

L66

*HCB1608KF-121T25

* 0.1u_10V_X5R_ 04

C199

*1 0u _6. 3 V_X5 R _0 6

C177

*1 0K _0 4

R96

*1 0K_0 4

R10 1

*0.1u_10V_X5R_04

C 191

*1 u_6 . 3V_X 5R _ 04

C20 2

DPC_VDD18

1 . 0V_R EG

DPC_VDD10

1. 0 V _REG

1. 8 V _REG

DPLL_PVDD

1. 8 V _REG

DPLL_PVDD

1 . 8V_R EG

TSVDD

DP LL _V DD C

3. 3VS _GP U

3.3VS_GPU3. 3VS _GP U

3. 3 V S_ G P U

A2VDD

3. 3 V S_G PU

1.8V_REG

DPC_ VD D18

VDD2DI

A2VDDQ

VDD1 DI

AVDD

1.8V_REG

DPC_ VDD18

1. 8V_ R EG

VDD1DI

AV D D

3.3VS_GPU

VD D 2D I

A2VDDQ

A2VDD

GPU_DP LUS10

3. 3 V S_ G P U

SCL20

GPU_DMINUS10

SDA20

GPIO2 110

VSYNC_ DA C2 10

HSYNC_DAC2 10

GPIO010

GPIO510

GPIO2 210

GPIO910

GPIO210

GPIO110

GPIO1310

GPIO1210

GPIO1110

MXM_SDATA10

GENERICC10

GPIO810

ROBSON _GPIO1636

MXM_ SC LK10

Sheet 8 of 41

Robson S3 MAIN 2/

6

Schematic Diagrams

B.Schematic Diagrams

Robson S3 MAIN 2/6 B - 9

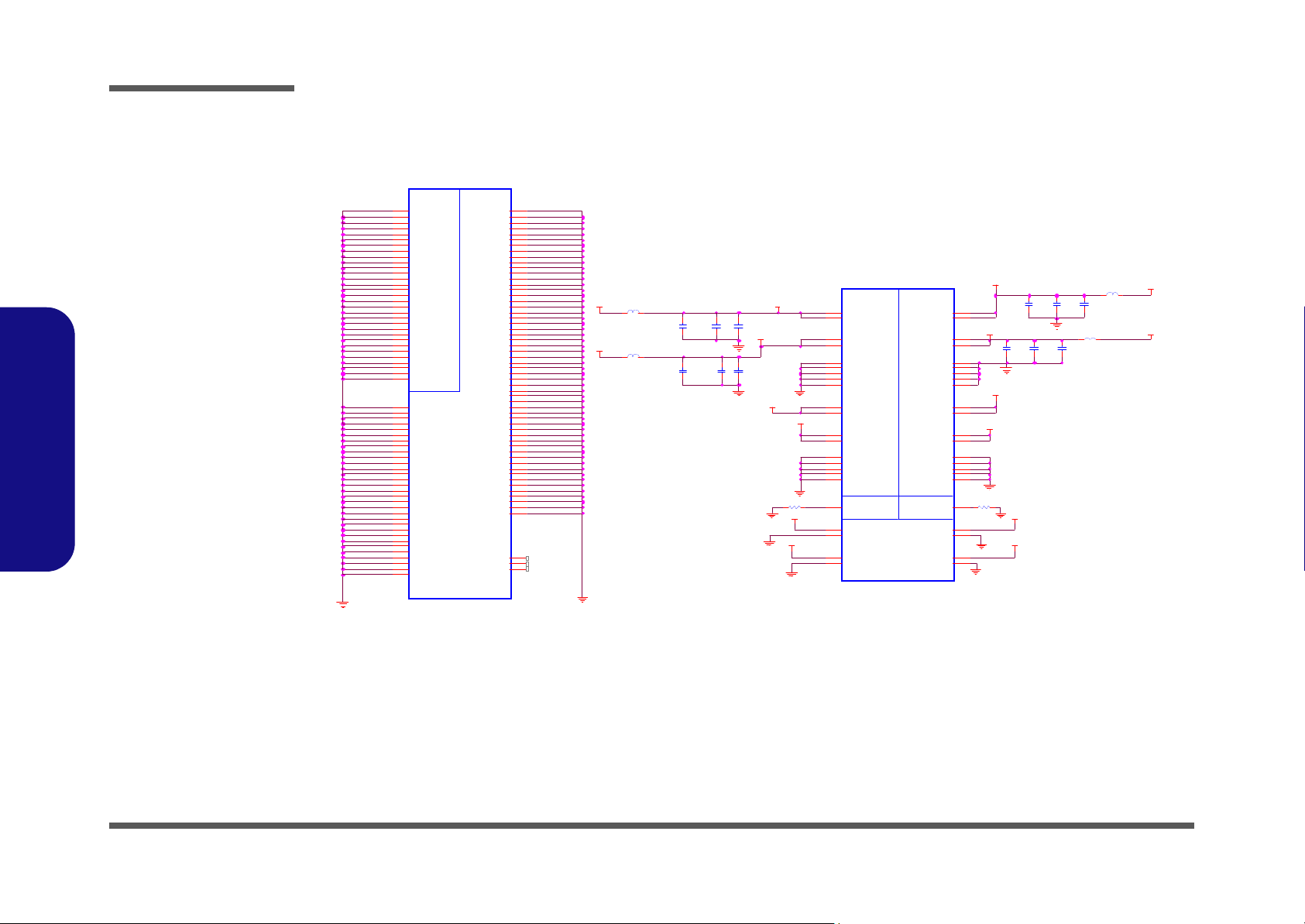

Schematic Diagrams

Sheet 9 of 41

Robson S3 MEM

InTERFACE 3/6

RPD1

*4.99K_1%_04

T9 7

CSHUNT1

*040 2_120pF _50V_ 5%

RSER2

*49. 9_1%_ 04

MEMORY INTERFACE

GDDR5/DDR3

G DDR5 /DD R3

G DDR5/DD R3

*ROBSON XT S3

U4C

DQ A0 _0/ D QA_ 0

K2 7

DQ A0 _1/ D QA_ 1

J29

DQ A 0_10/ DQA_10

A2 8

DQ A 0_11/ DQA_11

C28

DQ A 0_12/ DQA_12

E2 7

DQ A 0_13/ DQA_13

G26

DQ A 0_14/ DQA_14

D26

DQ A 0_15/ DQA_15

F2 5

DQ A 0_16/ DQA_16

A2 5

DQ A 0_17/ DQA_17

C25

DQ A 0_18/ DQA_18

E2 5

DQ A 0_19/ DQA_19

D24

DQ A0 _2/ D QA_ 2

H30

DQ A 0_20/ DQA_20

E2 3

DQ A 0_21/ DQA_21

F2 3

DQ A 0_22/ DQA_22

D22

DQ A 0_23/ DQA_23

F2 1

DQ A 0_24/ DQA_24

E2 1

DQ A 0_25/ DQA_25

D20

DQ A 0_26/ DQA_26

F1 9

DQ A 0_27/ DQA_27

A1 9

DQ A 0_28/ DQA_28

D18

DQ A 0_29/ DQA_29

F1 7

DQ A0 _3/ D QA_ 3

H32

DQ A 0_30/ DQA_30

A1 7

DQ A 0_31/ DQA_31

C17

DQ A1 _0/ D QA_ 32

E1 7

DQ A1 _1/ D QA_ 33

D16

DQ A1 _2/ D QA_ 34

F1 5

DQ A1 _3/ D QA_ 35

A1 5

DQ A1 _4/ D QA_ 36

D14

DQ A1 _5/ D QA_ 37

F1 3

DQ A1 _6/ D QA_ 38

A1 3

DQ A1 _7/ D QA_ 39

C13

DQ A0 _4/ D QA_ 4

G29

DQ A1 _8/ D QA_ 40

E1 1

DQ A1 _9/ D QA_ 41

A1 1

DQ A 1_10/ DQA_42

C11

DQ A 1_11/ DQA_43

F1 1

DQ A 1_12/ DQA_44

A9

DQ A 1_13/ DQA_45

C9

DQ A 1_14/ DQA_46

F9

DQ A 1_15/ DQA_47

D8

DQ A 1_16/ DQA_48

E7

DQ A 1_17/ DQA_49

A7

DQ A0 _5/ D QA_ 5

F2 8

DQ A 1_18/ DQA_50

C7

DQ A 1_19/ DQA_51

F7

DQ A 1_20/ DQA_52

A5

DQ A 1_21/ DQA_53

E5

DQ A 1_22/ DQA_54

C3

DQ A 1_23/ DQA_55

E1

DQ A 1_24/ DQA_56

G7

DQ A 1_25/ DQA_57

G6

DQ A 1_26/ DQA_58

G1

DQ A 1_27/ DQA_59

G3

DQ A0 _6/ D QA_ 6

F3 2

DQ A 1_28/ DQA_60

J6

DQ A 1_29/ DQA_61

J1

DQ A 1_30/ DQA_62

J3

DQ A 1_31/ DQA_63

J5

DQ A0 _7/ D QA_ 7

F3 0

DQ A0 _8/ D QA_ 8

C30

DQ A0 _9/ D QA_ 9

F2 7

MVR EF DA

K2 6

MVR EF SA

J26

MEM_ CAL RN0

J25

MEM_ CAL RP 0

K2 5

CASA0B

G19

CASA1B

G16

CKEA0

K20

CKEA1

J17

CLKA0

H26

CLKA0B

H25

CLKA1

G9

CLKA1B

H9

CS A0 B_0

H22

CS A0 B_1

J22

CS A1 B_0

G13

CS A1 B_1

K13

WCKA0_0/DQMA_0

E32

W CKA 0B _0 /DQ MA_ 1

E30

WCKA0_1/DQMA_2

A21

W CKA 0B _1 /DQ MA_ 3

C21

WCKA1_0/DQMA_4

E13

W CKA 1B _0 /DQ MA_ 5

D12

WCKA1_1/DQMA_6

E3

W CKA 1B _1 /DQ MA_ 7

F4

MAA0 _0/ MAA_ 0

K17

MAA0 _1/ MAA_ 1

J20

MAA1_ 2/ MAA_1 0

J11

MAA1_ 3/ MAA_1 1

J13

MAA1_ 4/ MAA_1 2

H11

MAA1_5/MAA_13/BA2

G11

MAA1_6/MAA_14/BA0

J16

MAA1_7/MAA_15/BA1

L15

MAA0 _2/ MAA_ 2

H23

MAA0 _3/ MAA_ 3

G23

MAA0 _4/ MAA_ 4

G24

MAA0 _5/ MAA_ 5

H24

MAA0_ 6/ MAA0_ 6

J19

MAA0_ 7/ MAA0_ 7

K19

MAA1 _0/ MAA_ 8

J14

MAA1 _1/ MAA_ 9

K14

ADBI A0/OD TA0

L18

ADBI A1/OD TA1

K16

RASA0B

G22

RASA1B

G17

EDCA0_ 0/RDQSA_0

H28

EDCA0_ 1/RDQSA_1

C27

EDCA0_ 2/RDQSA_2

A23

EDCA0_ 3/RDQSA_3

E19

EDCA1_ 0/RDQSA_4

E15

EDCA1_ 1/RDQSA_5

D10

EDCA1_ 2/RDQSA_6

D6

EDCA1_ 3/RDQSA_7

G5

MAA1_8 _RSVD

G14

MAA0_ 8/ MAA_1 3

G20

DDBIA0 _0/WD QSA_0

H27

DDBIA0 _1/WD QSA_1

A27

DDBIA0 _2/WD QSA_2

C23

DDBIA0 _3/WD QSA_3

C19

DDBIA1 _0/WD QSA_4

C15

DDBIA1 _1/WD QSA_5

E9

DDBIA1 _2/WD QSA_6

C5

DDBIA1 _3/WD QSA_7

H4

WEA0B

G25

WEA1B

H10

DR AM_RS T

L10

CLKTESTA

K8

CLKTESTB

L7

* 0.1 u_ 10 V_X5 R_ 04

C206

*51. 1_1 % _04

R 129

*40. 2_1%_0 4

R122

*0. 1u_10V_X 5R_04

C204

*100 _04

R123

RSER1

*10 _04

*0. 1u_10V _X5R_04

C207

*0. 1u_ 10V_X5R_04

C 205

*100_04

R127

*243_1 %_04R125

*51.1 _1%_04R 128

*40 .2_1%_ 04

R126

*243_1 %_04R124

MVDDQ

MVD DQ

MVD DQ

QSA0_2 B 13

MAA[12 ..0] 1 3,14

CKEA0 13

CSA0b_0 13

QSA0_3 B 13

CLKA0 13

DQA0_[ 31. .0]13

DQ MA0_[3.. 0] 13

QSA0_0 B 13

ODTA0 13

MEM_RST 13,14

QSA0_1 B 13

MAA13 1 3, 14

R A SA0# 13

WEA0# 13

C A SA0# 13

CKEA0

RASA0#

CSA0 b_0

CASA0#

CLKA0

ODTA0

QSA1 _[3.. 0] 14

A_BA0 13,14

A_BA2 13,14

A_BA1 13,14

CLKA1#

CASA1#

RASA1#

CLKA0#

CKEA1

WEA1# 14

CKEA1 14

R A SA1# 14

DQMA1_ [3.. 0] 1 4

DQMA1_2

DQMA1_3

DQMA1_0

DQMA1_1

CLKA1# 14

C A SA1# 14

WEA1#

CLKA0# 13

CLKA1 14

CLKA1

ODTA1 14

ODTA1

CSA1b_0 14

CSA1 b_0

DQA1_[ 31. .0]14

25mm (max)

DQA0_10

DQA0_3

DQA0_20

DQA0_19

DQA0_4

DQA0_22

DQA0_21

DQA0_24

DQA0_23

DQA0_5

DQA0_11

DQA0_0

DQA0_26

DQA0_25

DQA0_28

DQA0_27

DQA0_12

DQA0_6

DQA0_30

DQA0_29

DQA0_8

DQA0_1

DQA0_7

DQA0_2

DQA0_9

DQA0_31

DQA0_14

DQA0_13

DQA0_18

DQA0_17

DQA0_16

DQA0_15

COMPONENTS SHOWN ARE EXAMPLE S ONLY

AND NOT NECESSARILY QUALI FIED

DMEM_RST

1 0.0

DDR3 Memory

Interface

Fro m GPU

MAA1 _8

DD R3/ GD DR 3 Me mory Stuff Optio n

WEA0#

MAA6

MAA1

MAA11

MAA9

MAA2

MAA10

MAA0

MAA8

MAA4

MAA7

MAA5

MAA3

DQMA0_3

DQMA0_0

DQMA0_1

DQMA0_2

Place all these components very close to GPU (Within

25mm) and keep all component close to each Other (within

5mm) except Rser2

MAA12

Ra

Ra

Ra

Rb

Rb

Rb

GDDR5

MVDDQ

5m m (m a x)

QSA1_0 B 14

QSA1_3 B 14

QSA1_2 B 14

QSA0_[ 3.. 0] 1 3

QSA1_1 B 14

QSA1_3B

QSA1_1B

QSA1_2B

QSA1_0B

MAA1 3

1.5V/1.8V

25mm (max)

This basic topo logy s hould be use d for DRAM_RST fo r DDR3 /GDDR5.Thes e

Capa citors and Resist or values ar e an example only . The Series R an d

|| C ap values w ill de pend on the DRAM load and wil l have to be

calc ulated for diffe rent Memory ,DRAM Load and bo ard t o pass Rese t

Sign al Spec.

DDR3

DMEM_RST

1.5V

100R

40.2R

40.2R

100R

QSA0_2B

QSA0_3B

QSA0_1B

QSA0 _2

QSA0 _0

QSA0 _1

QSA0 _3

QSA0_0B

CLKTEST A

PL ACE MVREF DIVIDERS

AND CAPS CL OSE T O ASIC

CLKTESTB

r oute 50o hms single- ende d/1 00ohms d iff

a nd keep sho rt

D ebug onl y, for cloc k ob ser vation, if n ot need ed, DNI

DQA1_6

DQA1_3

DQA1_2

DQA1_11

DQA1_10

DQA1_5

DQA1_4

DQA1_7

DQA1_9

DQA1_8

DQA1_13

DQA1_12

DQA1_15

DQA1_14

DQA1_23

DQA1_22

DQA1_19

DQA1_18

DQA1_0

DQA1_1

DQA1_17

DQA1_16

DQA1_21

DQA1_20

DQA1_29

DQA1_28

DQA1_31

DQA1_30

DQA1_27

DQA1_26

DQA1_25

DQA1_24

QSA1 _1

QSA1 _3

QSA1 _2

QSA1 _0

Robson S3 MEM Interface 3/6

B.Schematic Diagrams

B - 10 Robson S3 MEM Interface 3/6

Robson S3 Straps 4/6

Sheet 10 of 41

Robson S3 Straps

4/6

*2. 2K _04

R147

*W83L771AWG

U6

SCLK8VDD

1

ALER T

6

THERM

4

SDATA

7

GND

5

D+

2

D-

3*0_04R152

*0_04R153

*10K_04R145

*10K_04R135

*0_04R155

*0_04R154

R159

*6.8K_1%_04

*2.2K_04R1 5 6

*10K_04R139

R160

*6.8K_1%_04

*10K_04R137

*10K_04R136

*10K_04R140

*2.2K_04

R146

*0_04R151

R158 *0_04

*10K_04R130

Q4

*MTN7002ZHS3

G

DS

*10K_04R134

*10K_04R144

*10K_04R131

Q5

*MTN7002ZHS 3

G

DS

*0_04R150

*10K_04R133

*10K_04R138

*10K_04R132

*1000p_ 50V _X 7R_04

C208

*10K_04R141

*2200p_50V_X 7R _04C209

*2.2K _04R157

*10K_04R143

*10K_04R142

3. 3VS_GPU

3.3VS_ GPU

3.3VS_GP U

3. 3VS_GPU

3.3VS_GPU

GPIO58

GPU_ DM INUS8

GPU_ DPLUS 8

HSYNC_DAC 18,21

VSYN C_DAC18,21

GENERICC8

GPIO228

VSYN C_DAC28

HSY NC_DAC28

GPIO88

GPIO28

GPIO18

GPIO08

GPIO218

GPIO98

GPIO138

GPIO128

GPIO118

MX M_SCLK8

MXM_ SDATA8

SCL K0 5,6,16

SDAT A0 5,6,16

MXM_ RST#7

SMC _VGA_THER M27

SMD _VGA_THER M27

GPU_TALERT# 8,17

W250BAQ

GP IO0 1

GP IO1 1

VGA_ ALERT# 27

GP IO2 0

GP IO8 0

GP IO9 0

GP IO11 1

GP IO12 0

GP IO13 0

V SY NC_ DA C1 1

HSY NC_DAC1 1

GE NERICC 1

V SY NC_ DA C2 0

HSY NC_DAC2 0

GP IO21 0

GP IO22 0

GP IO5 1

MXM _SDATA

MXM _SCLK

MXM_ SCLK

3.3VS_GP U

MX M_SD ATA

SEE DAT ABO OK F O R DE TAIL

S M B us ga ting c irc ui t

XHSY NC

A LL OW FOR PU LL UP PA DS FOR THES E S TRA PS AN D IF T HES E GPI OS ARE US ED,

T HEY MUS T NOT CON FL IC T DURI NG RESET

X

AUD[1]

GPI O1

TX_PWRS_ENBPCIE FULL TX OU TPUT SWINGGPI O0

EN ABLE EXTER NA L BIO S R OM

XXX

PCI E TRAN SMITTER DE- EMPHASIS ENABL EDTX_D EEMPH_ EN

BI F_VG A DIS VGA EN ABLEDGPIO9 0

X

X

IGN ORE VIP DEVICE STRA PS (Removed on Seymour/Whistler)V2SY NCVI P_D EVICE_ STRAP_E NA

PIN D ESCRI PTIO N OF DEFAULT SETTINGSSTR APS

GPIO _22_ROMCSB

RECOM ME NDED SETT I N GS

0 = DO NOT I NSTAL L RESI STOR

1 = INSTALL 3K RESISTO R

X = DES IGN DEPENDANT

NA = NOT A PPLICABLE

SER IAL ROM TYP E O R MEM O RY AP ER TUR E S IZ E S ELEC T

ROMIDC FG(2:0) GPIO[13: 1 1]

BIOS_ROM_EN

C ONFIGUR A T ION STRAP S - - SE E E ACH DA T A BOOK FOR STRAP DETA IL S

H2SYNC

AUD[0] XVSYNC

X

ALLOW FOR P ULLUP PA DS FOR THESE STR APS B UT DO NOT I NSTALL RESISTOR. IF THESE GPI OS A RE USED,

THE Y M US T KEE P " L O W " AND N OT CO N F L IC T D URI NG RE SE T .

NOTE1: AMD RESERV ED CONFIGURATION STRAPS

GPIO21 GENERICC

0RE SERVE DGPI O2RSVD

PIN STRAPS

GPI O8RSVD

GPU Therm al S ens or

GPI O21RSVD

0RE SERVE D

RSVD

0RE SERVE D

GEN ERIC CRSVD

0RE SERVE DH2S YNC

GPIO2

SEE DAT ABO OK F O R DE TAIL

0RE SERVE D

GPIO21 MUST BE LOW DURING PERSTB WHEN BEING USED TO CONTROL MV DDQ

GPIO8

Schematic Diagrams

B.Schematic Diagrams

Robson S3 Straps 4/6 B - 11

Schematic Diagrams

Sheet 11 of 41

Robson S3 Power

5/6

*150_1%_04

R163

GND

*ROBSON XT S 3

U4E

PCI E_ VSS#1

AA27

PCI E_VS S #10

AF32

PCI E_VS S #11

AG27

PCI E_VS S #12

AH3 2

PCI E_VS S #13

K28

PCI E_VS S #14

K32

PCI E_VS S #15

L27

PCI E_VS S #16

M32

PCI E_VS S #17

N25

PCI E_VS S #18

N27

PCI E_VS S #19

P25

PCI E_ VSS#2

AB24

PCI E_VS S #20

P32

PCI E_VS S #21

R27

PCI E_VS S #22

T25

PCI E_VS S #23

T32

PCI E_VS S #24

U25

PCI E_VS S #25

U27

PCI E_VS S #26

V32

PCI E_VS S #27

W25

PCI E_VS S #28

W26

PCI E_VS S #29

W27

PCI E_ VSS#3

AB32

PCI E_VS S #30

Y25

PCI E_VS S #31

Y32

PCI E_ VSS#4

AC2 4

PCI E_ VSS#5

AC2 6

PCI E_ VSS#6

AC2 7

PCI E_ VSS#7

AD2 5

PCI E_ VSS#8

AD3 2

PCI E_ VSS#9

AE27

VSS _MECH#1

A32

VSS _MECH#2

AM1

VSS _MECH#3

AM32

GND#1

A3

GND#10

AD8

GND#11

AE7

GND#12

AG12

GND#13

AH1 0

GND#14

AH2 8

GND#15

B10

GND#16

B12

GND#17

B14

GND#18

B16

GND#19

B18

GND#2

A30

GND#20

B20

GND#21

B22

GND#22

B24

GND#23

B26

GND#24

B6

GND#25

B8

GND#26

C1

GND#27

C32

GND#28

E28

GND#29

F10

GND#3

AA13

GND#30

F12

GND#31

F14

GND#32

F16

GND#33

F18

GND#34

F2

GND#35

F20

GND#36

F22

GND#37

F24

GND#38

F26

GND#39

F6

GND#4

AA16

GND#40

F8

GND#41

G10

GND#42

G27

GND#43

G31

GND#44

G8

GND#45

H14

GND#46

H17

GND#47

H2

GND#48

H20

GND#49

H6

GND#5

AB10

GND#50

J27

GND#51

J31

GND#52

K11

GND#53

K2

GND#54

K22

GND#55

K6

GND#56

M6

GND#57

N11

GND#58

N12

GND#59

N13

GND#6

AB15

GND#60

N16

GND#61

N18

GND#62

N21

GND#63

P6

GND#64

P9

GND#65

R12

GND#66

R15

GND#67

R17

GND#68

R20

GND#69

T13

GND#7

AB6

GND#70

T16

GND#71

T18

GND#72

T21

GND#73

T6

GND#74

U15

GND#75

U17

GND#76

U20

GND#77

U9

GND#78

V13

GND#8

AC9

GND#79

V16

GND#80

V18

GND#81

Y10

GND#82

Y15

GND#83

Y17

GND#84

Y20

GND#9

AD6

GND#85

R11

GND#86

T11

L75

*HCB1608KF-121T25

L74

*HCB1608KF-121T25

*1u_6.3V_X 5R_ 04

C214

*1u_6.3V_X5 R_04

C215

*0.1u_10V_X 5R _04

C221

L77

*HCB1608KF-121T25

*0.1u_10V_X 5R_04

C213

*0.1u_10V_X5R_04

C210

*10u_6.3V_08_H125

C218

*1u_6.3V_X 5R _04

C217

*0.1u_10V_X5R_0 4

C216

*10u_6. 3V _08_H125

C219

*10u_6.3V_08_H 125

C211

DP PLL POWER

DP A/B POWERDP E/F POWER

*RO BSON XT S3

U4 G

DPA_PVDD

AG8

DPA_P VSS

AG7

DPA_VDD10#1

AF 6

DPA_VDD10#2

AF 7

DPA_VDD18#1

AE11

DPA_VDD18#2

AF 1 1

DPA_VSSR# 1

AE1

DPA_VSSR# 2

AE3

DPA_VSSR# 3

AG1

DPA_VSSR# 4

AG6

DPA_VSSR# 5

AH5

DP AB_C ALR

AE10

DPB_PVDD

AG10

DPB_P VSS

AG11

DPB_VDD10#1

AF 8

DPB_VDD10#2

AF 9

DPB_VSSR# 1

AF 1 0

DPB_VSSR# 2

AG9

DPB_VSSR# 3

AH8

DPB_VSSR# 4

AM6

DPB_VSSR# 5

AM8

DPB_VDD18#1

AE13

DPB_VDD18#2

AF 1 3

DPE_PVDD

AG18

DPE_PVSS

AF 1 9

DPE_VDD10#1

AG20

DPE_VDD10#2

AG21

DPE_VDD18#1

AG15

DPE_VDD18#2

AG16

DPE_VSSR#1

AG14

DPE_VSSR#2

AH14

DPE_VSSR#3

AM14

DPE_VSSR#4

AM16

DPE_VSSR#5

AM18

DPEF_CALR

AF 1 7

DPF_PVDD

AG19

DPF_PVSS

AF 2 0

DPF_VDD10#1

AF 2 2

DPF_VDD10#2

AG22

DPF_VDD18#1

AF 1 6

DPF_VDD18#2

AG17

DPF_VSSR #1

AF 2 3

DPF_VSSR #2

AG23

DPF_VSSR #3

AM20

DPF_VSSR #4

AM22

DPF_VSSR #5

AM24

*1u_6.3V_X5R_04

C220

*10u_6.3V_08_H 125

C212

L76

*HCB1608KF -121T25

*150_1%_04R162

DPAB_VDD 18

DPAB_VDD18

1.8V_REG

DPEF _VDD18

DPEF _VDD18

DPEF_VDD1 81.8V_R EG

DPEF_VDD10

1.0V_R EG

DPA B_VD D10

DPA B_VD D10

DPEF _VDD18

1.0V_REG

DPAB_VD D1 8

DPAB _VDD18

DPEF _VDD10

PARK/ROBSON- S3 (DP Power)

(1.8V@300mA DPEF_VDD18)

(1.0V@220mA DPEF_VDD10)

DP mode

LVDS mode

DP mode

LVDS mode

(1.0V@240mA DPEF_VDD10)

(1.8V@440mA DPEF_VDD18)

( 1.8V@ 300m A DP AB_VD D18 )

(1.0V@220 mA DPAB_VDD1 0)

B.Schematic Diagrams

B - 12 Robson S3 Power 5/6

Robson S3 Power 5/6

Robson S3 Power 6/6

1.0V_REG

2A 80mil

*1 u_ 6. 3 V _X 5R _0 4

C28 9

*10u_6.3V_08_H125

C299

*1u_6.3V_X5R_04

C23 2

*1 u_ 6. 3 V _X 5R _0 4

C284

*1 0u _6 . 3V _ 0 8_ H 12 5

C25 2

*0.1u_10V_X5R_04

C24 1

*1u_6.3V_X5R_04

C258

L82

*H C B1 6 08 K F -12 1T 25

*0 .1u_10V_X5R_04

C291

*1 u_ 6. 3 V _X 5 R_0 4

C234

*1u_6.3V_X5R_04

C323

*1 u_ 6. 3 V _X 5 R_0 4

C31 1

*10u_6.3V_08_H125

C24 8

*1u_6.3V_X5R_04

C26 3

*1 u_ 6.3V_X5R_04

C314

*10u_6.3V_08_H125

C298

*0 . 1 u_ 10 V _X 5 R_0 4

C22 7

*1 u_ 6. 3 V _X 5R _0 4

C273

*1u_6.3V_X5R_04

C312

*1 u_ 6. 3 V _X 5 R_0 4

C279

*1u_6.3V_X5R_04

C274

NC1

SH ORT

*10u_6.3V_08_H125

C302

*0.1u_10V_X5R_04

C22 9

*1u _ 6. 3 V _X 5R _0 4

C244

*HCB1608KF-121T25L7 9

*10u_6.3V_08_H125

C24 5

*0.1u_10V_X5R_04

C22 2

*1u_6.3V_X5R_04

C268

*0.1u_10V_X5R_04

C226

C30 5

*1u_6.3V_X5R_04

*1 u_ 6. 3 V _X 5R _0 4

C27 5

*1 u_ 6. 3 V _X 5 R_0 4

C254

*10u_6.3V_08_H125

C260

*0.1u_10V_X5R_04

C223

*1u_6.3V_X5R_04

C307

L78

*HC B1608KF-121T25

*1u_6.3V_X5R_04

C233

*1 u_ 6. 3 V _X 5R _0 4

C262

*1u_6.3V_X5R_04

C310

* 0. 1 u_ 10 V _X 5 R_0 4

C324

*1u_6.3V_X5R_04

C27 1

C304

*1u_6.3V_X5R_04

L80 *HCB1608KF-121T25

*1u_6.3V_X5R_04

C288

*10u_6.3V_08_H125

C316

*1 u_ 6. 3 V _X 5R _0 4

C259

*1u_6.3V_X5R_04

C280

*1u_6.3V_X5R_04

C28 7

*10u_6.3V_08_H125

C27 6

*1 u_ 6. 3 V _X 5R _0 4

C242

*10u_6.3V_08_H125

C32 2

*1u_6.3V_X5R_04

C282

*10u_6.3V_08_H125

C261

*1u_6.3V_X5R_04

C309

*1 u_ 6. 3 V _X 5 R_0 4

C256

*1 u_ 6. 3 V _X 5R _0 4

C255

*10u_6.3V_08_H125

C317

*10u_6.3V_08_H125

C24 9

*10u_6.3V_08_H125

C30 3

R164 * 10mil_short