Page 1

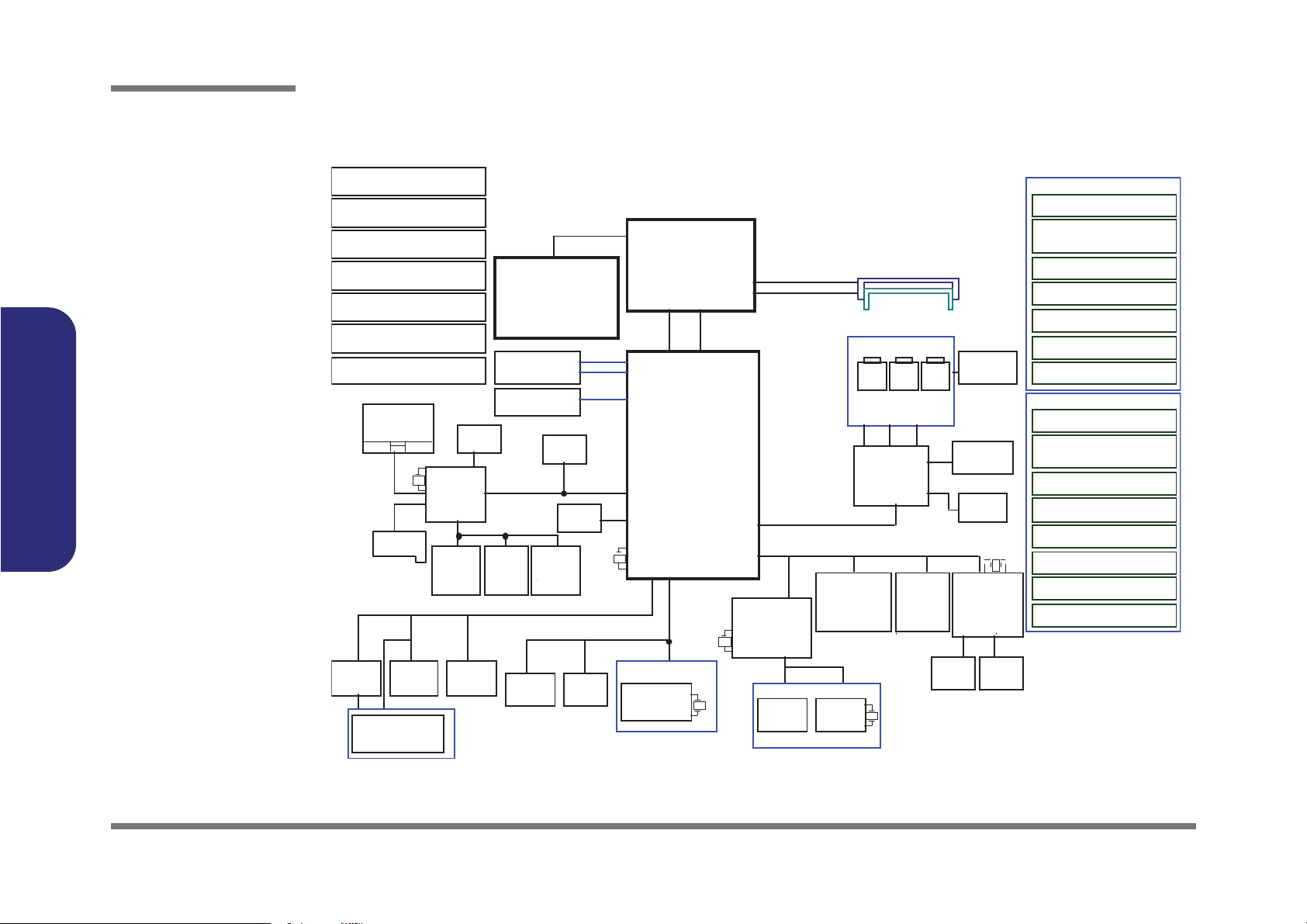

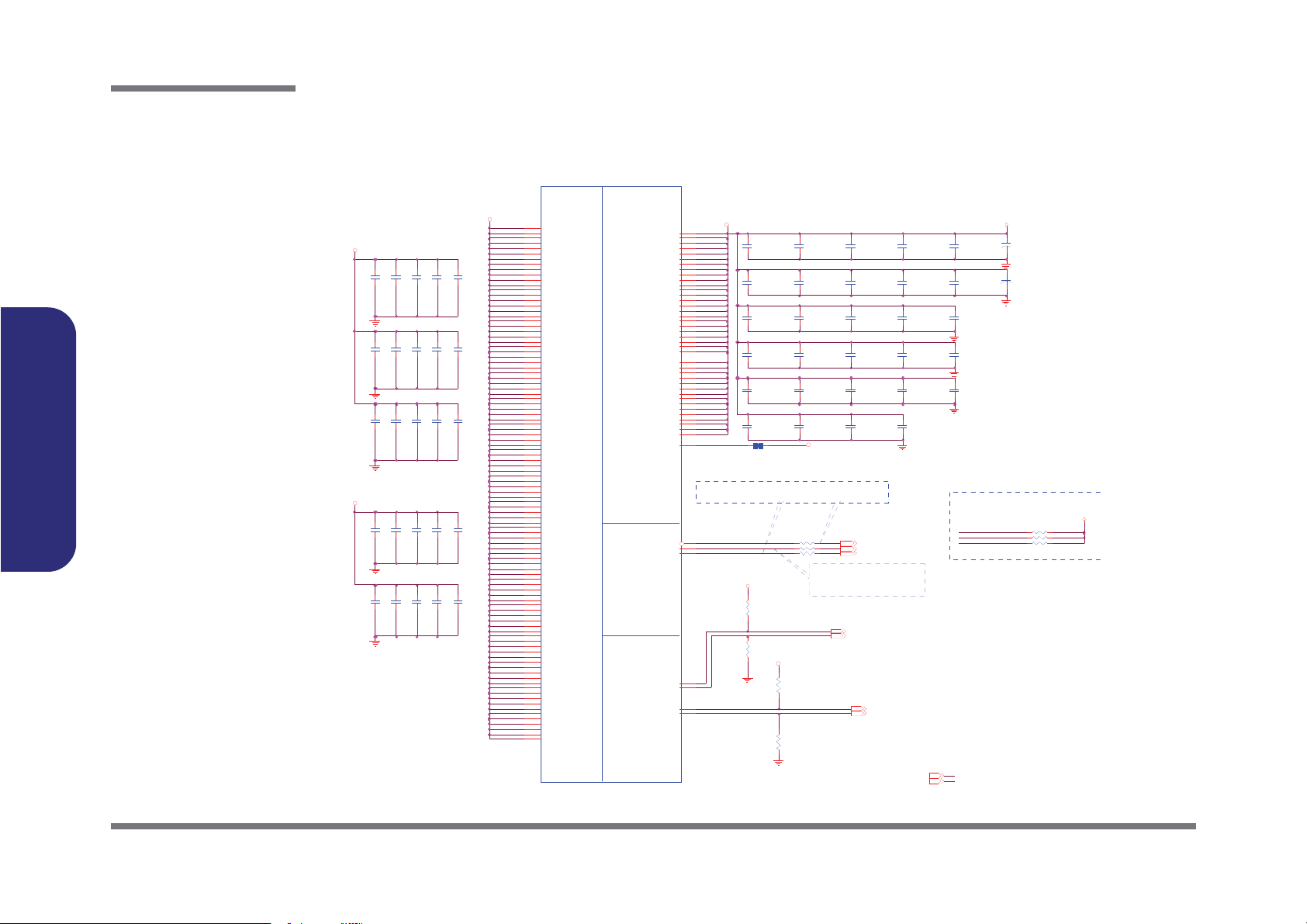

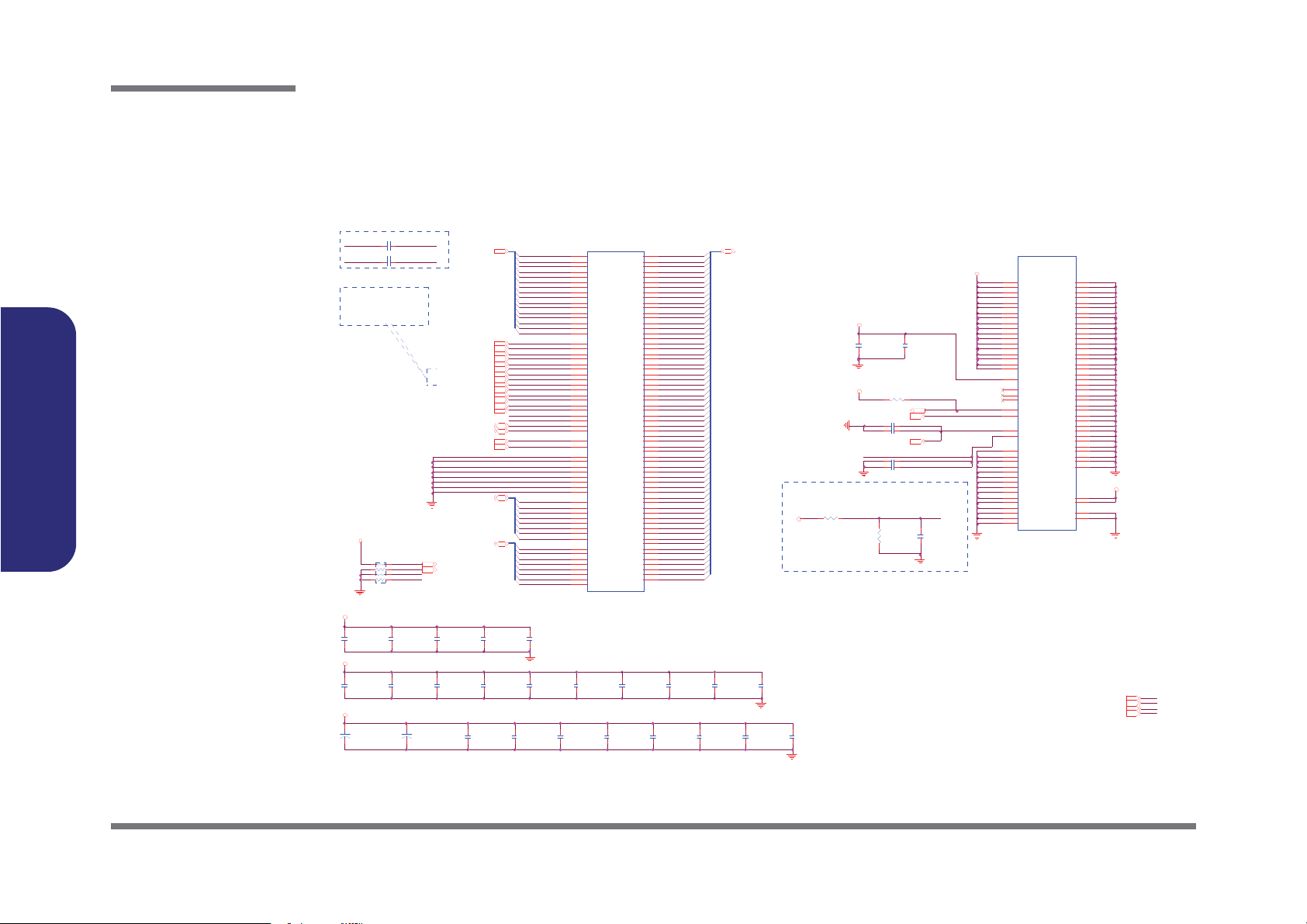

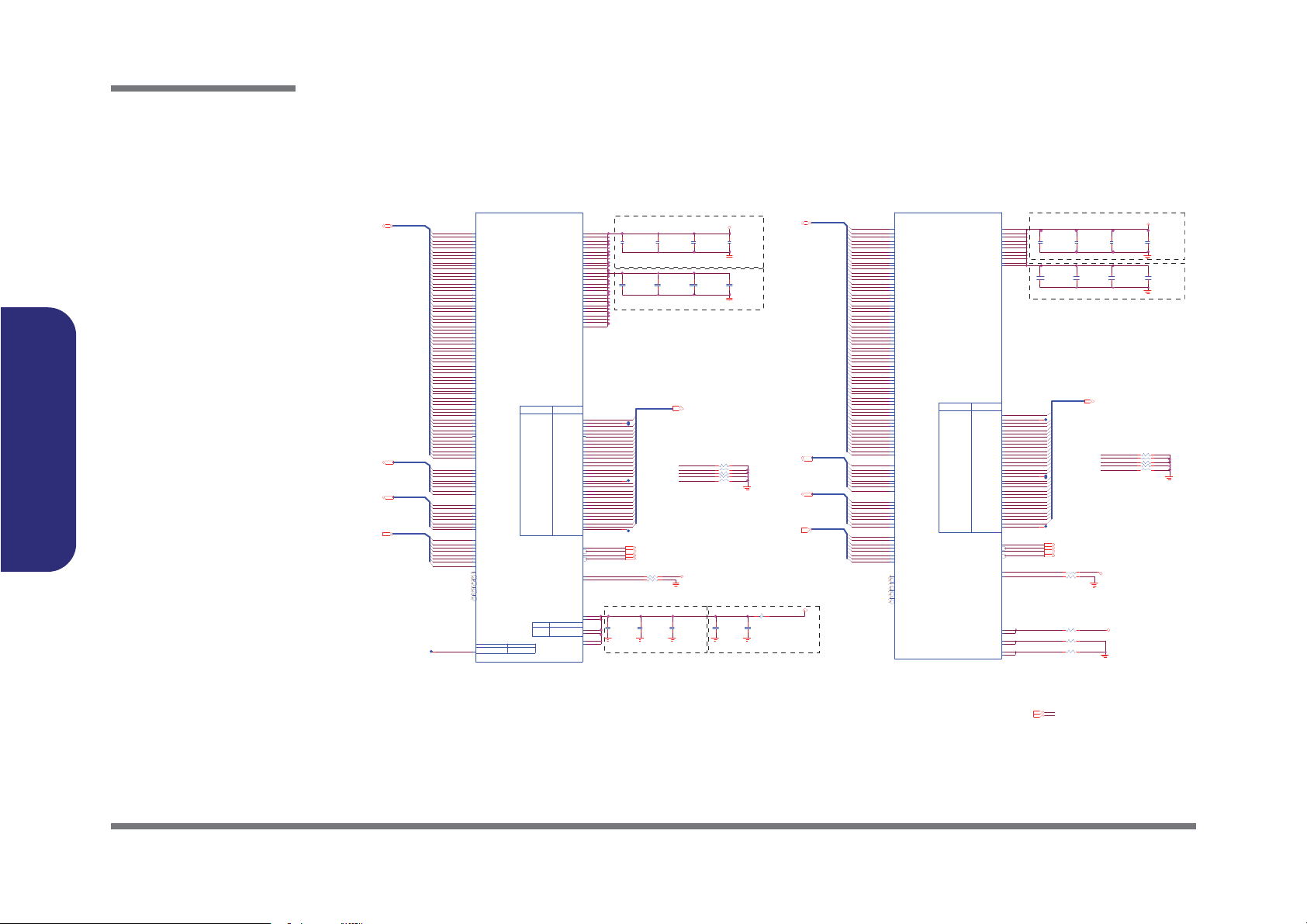

Schematic Diagrams

1005 Balls

Nvidia

Fermi N12E-GE-A1

RAM SIZE:2GB

(128MX16)

VDD3,VDD5

DMI*4

System Block Diagram

Sheet 1 of 49

System Block

Diagram

B.Schematic Diagrams

GPU NVDIDA N12x NVVDD

5V,3V,5VS,3VS,1.5VS,

1.8VS,+1.5S_CPU

1.8V, PEX_VDD,0.85VS

1.5V,0.75VS(VTT_MEM)

FBVDDQ

1.05VS_VTT

VGFX_CORE

SENTELIC

6-49-C4102-010

TO UC H PA D

CLICK BOARD

32 .768 KHz

EC

ITE 8518E

INT. K/B

128pins LQFP

14 *1 4* 1 .6m m

EC SMBUS

THERMAL

SENSOR

W83L771AWG

SATA I/II 3.0Gb/s

W 150HR M/W170H R Hur on Ri ver S ystem Block Diag ram

PCIE*8

SPI

SMART

FAN

LC D CO NNE CT OR

CR T CO NNE CT OR

HDMI Connector

TP M 1. 2

Optional

LPC

0.5"~11"

SMART

BATTERY

AC-IN

33 M H z

BIOS

SPI

<12"

<8"

<15"

32.768KHz

Sandy Bridge

PROCESSOR

rPGA988B

FDI

0.5"~5.5"

CougarPoint

Controller

H ub (P CH)

27x27mm

989 Ball FCBGA

USB2.0

480 Mbps

1"~16"

800/106 7/1333 MHz

DDR3 / 1.5V

SYSTEM SMBUS

<=8"

USB3.0

VLI8012

*NEC uPD720200

0.1"~13

24 MHz

PCIE

AU DI O BO AR D

SPDIF

OUT

W15 0HNM (INT SPK R)

Azalia Codec

REALTAK

ALC269

AZALIA LINK

100 MHz

Mi ni PC IE

SOCKET

3G MS ATA CA RD

(USB2/SATA3)

(Optional)

MI C

IN

(USB8)US B PO RT

<12"

Mini PCIE

SOCKET

WLAN

(USB2)

HP

OU T

DDRIII

SO-DIMM2

SHEET 10

DDRIII

SO-DIMM1

SHEET 9

W150HNM

INT SPKER -R

W150HNM

INT SPKER-L

INT MIC

25

MHz

JMICRO

JMC251_C

CARD

LAN

READER

W150HRM

W150HRM MAIN BOARD

AUDIO BOARD

PHONE JACK x3, USB x1

SE CON D HD D/O DD BOA RD

FI NGE R PR INT ER BOA RD

CLICK BOARD

POWER SWITCH BOARD

LED & VGA S/W BOARD

W170HR

W1 50H N MA IN BO AR D

AUDIO BOARD

PHONE JACK x3, USB x1

SE CON D HD D/O DD BOA RD

K/B TR AN SFER BOARD

CLICK BOARD

POWER SWITCH BOARD

LED & VGA S/W BOARD

DEBUG BOARD

7IN1

RJ-11

8IN1

RJ-11

6-7P-W15R7-002

6-71-W15H0-D02

6-71-W150A-D02

6-71-W150N-D01

6-71-B510F-D02

6-71-B5102-D04

6-71-B510S-D03

6-71-B5134-D01

6-7P-W1708-001

6-71-W1500-D01

6-71-W170A-D01

6-71-W170N-D01

6-71-B7117-D01

6-71-B7112-D02

6-71-B711S-D02

6-71-B7134-D01

6-71-W840TD-D03

W150HNM

S EC ON D HD D BO AR D

B - 2 System Block Diagram

SATA ODDSATA HDD

(B4100M)

eSATA

USB PORT1

(USB0)

CCD

(USB5)

B5 1 0 0

FINGER PRINTER BOARD

(USB4)

FingerPrint

(Optional)

USB PORT3US B PO RT 2

12 MHz

USB3.0

http://hobi-elektronika.net

RJ-45

7IN1

SOCKET

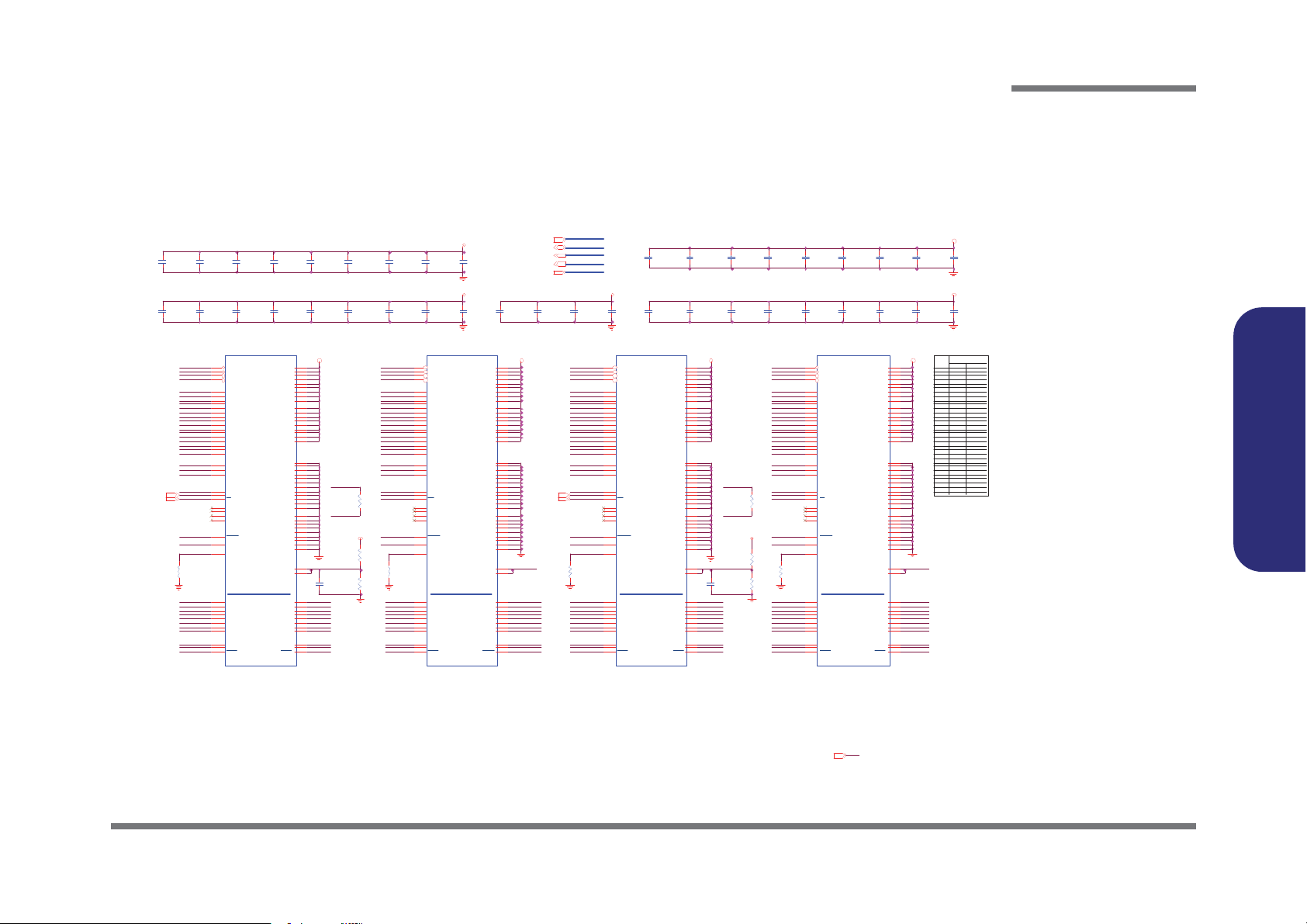

Page 2

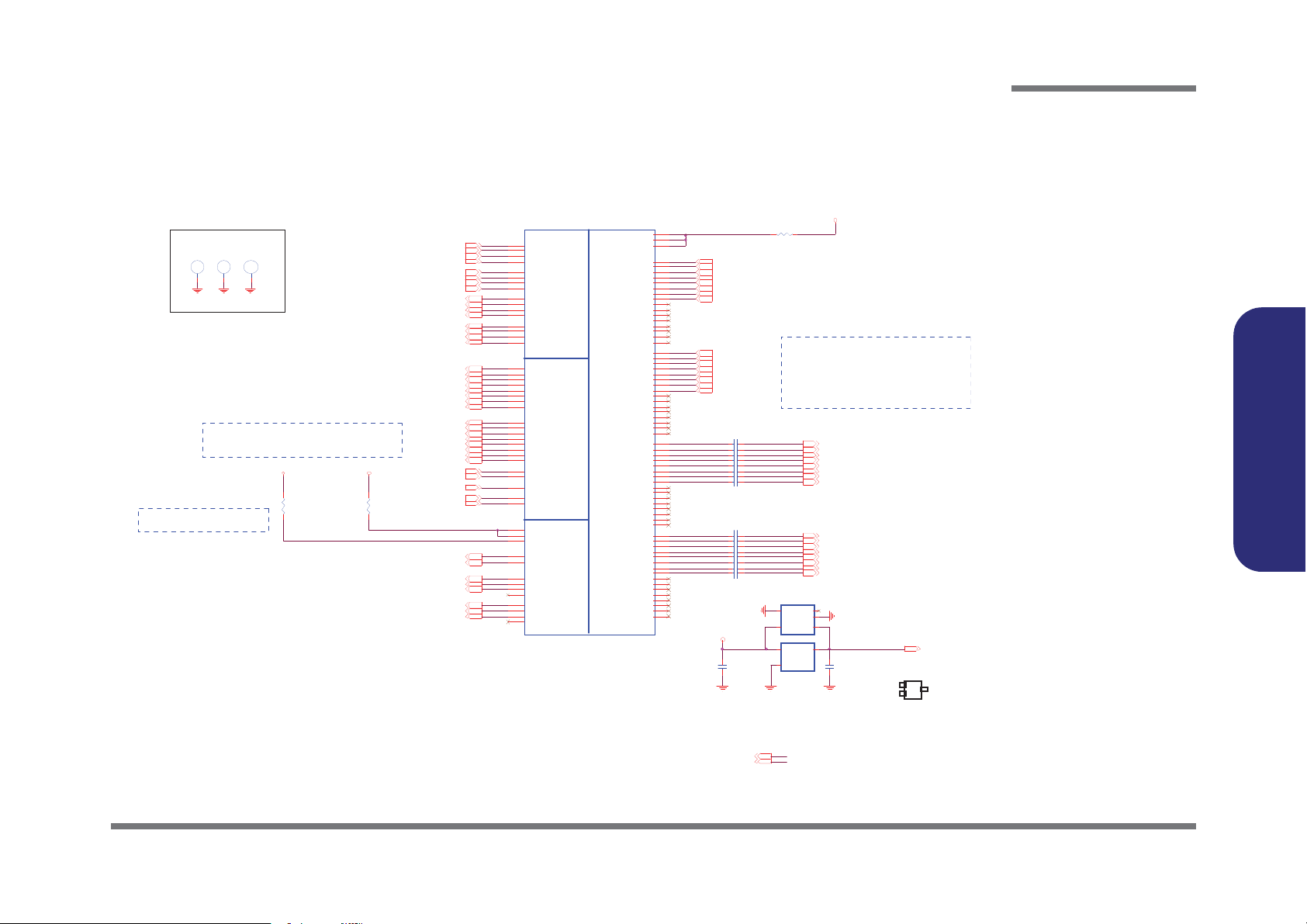

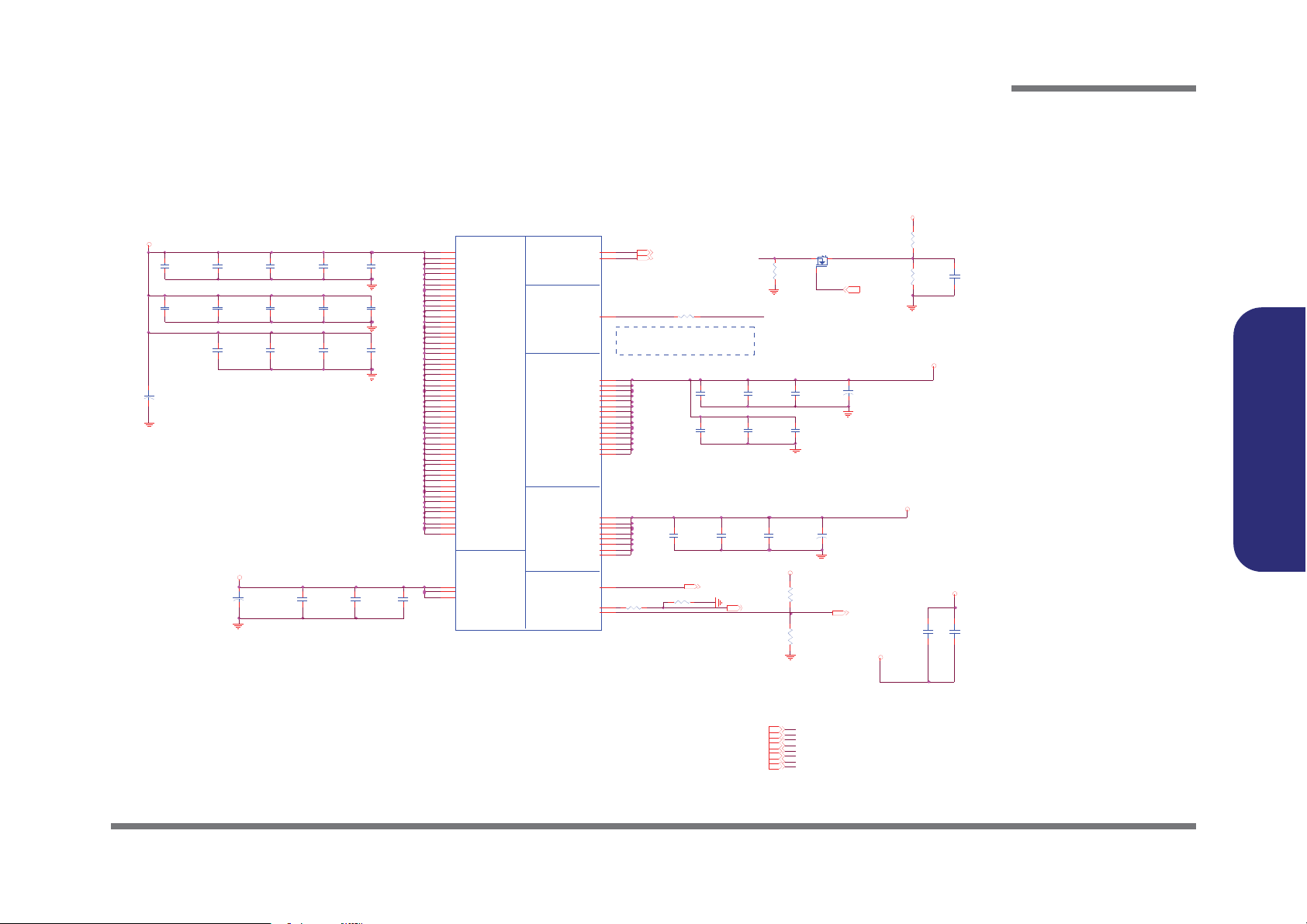

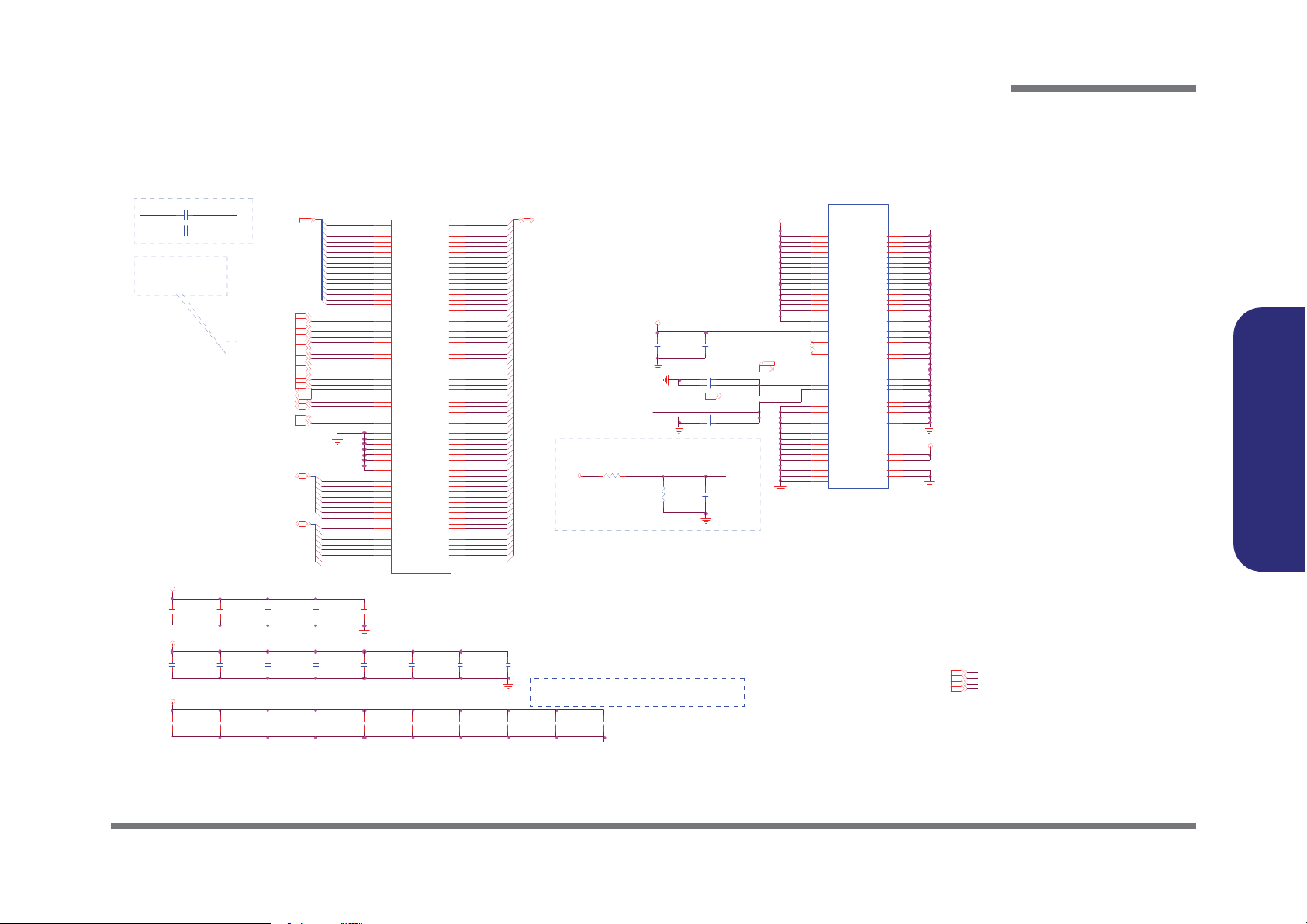

Sandy Bridge Processor 1/7

C 589 0. 22u_10V_X5R _04

C 608 0. 22u_10V_X5R _04

C 598 0. 22u_10V_X5R _04

C 606 0. 22u_10V_X5R _04

C 591 0. 22u_10V_X5R _04

C67 2

0.1u_10V_X7R _04

R51 9

24.9_1%_04

C 596 0. 22u_10V_X5R _04

C 594 0. 22u_10V_X5R _04

R521

1K_1%_04

C 601 0. 22u_10V_X5R _04

Q27

G711ST9U

OUT1VC C

2

GND

3

C67 3

0.1u_10V_X7R _04

R133 24.9_1%_04

1.05V S_VTT

3.3V

DMI_T XP120

DMI_T XP020

1. 05 V S _V TT 1.05VS_VTT

DM I_ TX N020

DMI_T XP320

DMI_T XP220

DM I_ TX N320

DM I_ TX N220

DM I_ TX N120

DM I_ RXN 220

DM I_ RXN 120

DM I_ RXN 020

SC70-5 & SC70-3

Co-lay

DM I_ RXP220

DM I_ RXP120

DM I_ RXP020

DM I_ RXN 320

FDI_FSYNC120

FDI_FSYNC020

DM I_ RXP320

FD I_LS YN C120

FD I_LS YN C020

FD I_ INT20

FDI_TXN220

FDI_TXN120

FDI_TXN020

FDI_TXN520

FDI_TXN420

FDI_TXN320

FDI_TXP120

FDI_TXP020

FDI_TXN720

FDI_TXN620

FDI_TXP420

FDI_TXP320

FDI_TXP220

FDI_TXP720

FDI_TXP620

FDI_TXP520

C 604 0. 22u_10V_X5R _04

3.3V3,8,11,12,16,18, 19,20,22,23, 24,25,27,28, 29,30,33,35, 37,38,39

H15

H8_0D4_4

PE G_R X#4 1 2

PE G_R X#2 1 2

THERM _V OLT 3 4

H8

H8_0D4_4

H16

H8_ 0 D4 _4

PE G_R X#0 1 2

PE G_R X#3 1 2

PE G_R X#7 1 2

PE G_R X#1 1 2

CPU

PE G_R X7 12

PE G_R X#5 1 2

PE G_R X#6 1 2

PE G_R X2 12

PE G_R X4 12

PE G_R X5 12

PE G_R X6 12

PE G_R X0 12

PE G_R X3 12

PE G_TX#2 12

PE G_TX#3 12

PE G_R X1 12

PE G_TX#1 12

PE G_TX#0 12

PE G_TX#7 12

PE G_TX#5 12

PE G_TX6 12

PE G_TX#4 12

PE G_TX#6 12

PE G_TX4 12

PE G_TX0 12

PE G_TX3 12

PE G_TX5 12

PE G_TX1 12

PE G_TX7 12

1.05VS_VTT3,5,23,24, 25,35,39

PE G_TX2 12

EDP_H PD

EDP_C OM PIO

Q26

*TMP20

NC

1

GN D

2

VO

3

GND

5

VC C

4

C 595 0. 22u_10V_X5R _04

8/30

C 607 0. 22u_10V_X5R _04

CAD NOTE: PEG_ICOMPI and RCOMPO signals

should be shorted and routed with

- max length = 500 mils

- typical impedance = 43 mohms

PEG_ICOMPO signals should be routed with

- max length = 500 mils

- typical impedance = 14.5 mohms

DP_TXP_111

DP_TXP_011

DP_TXP_211

DP_T XN_ 011

DP_T XN_ 111

DP_T XN_ 211

DP_A U X_ P11

DP_A U X_ N11

C 597 0. 22u_10V_X5R _04

ED P HP D Fu nc ti o n D is ab l e

ED P_ HP D : Pu ll -u p 10 K- DIS A BL ED HPD

PCI EXPRESS* - GRAPHIC S

DMI

Intel(R) FDI

eDP

U49A

PZ98827- 364B-01F

DM I_ RX# [0 ]

B27

DM I_ RX# [1 ]

B25

DM I_ RX# [2 ]

A25

DM I_ RX# [3 ]

B24

DM I_ RX[0 ]

B28

DM I_ RX[1 ]

B26

DM I_ RX[2 ]

A24

DM I_ RX[3 ]

B23

DM I_ TX#[0]

G21

DM I_ TX#[1]

E22

DM I_ TX#[2]

F21

DM I_ TX#[3]

D21

DM I_ TX[ 0]

G22

DM I_ TX[ 1]

D22

DM I_ TX[ 3]

C21

DM I_ TX[ 2]

F20

FD I0_TX #[0 ]

A21

FD I0_TX #[1 ]

H19

FD I0_TX #[2 ]

E19

FD I0_TX #[3 ]

F18

FD I1_TX #[0 ]

B21

FD I1_TX #[1 ]

C20

FD I1_TX #[2 ]

D18

FD I1_TX #[3 ]

E17

FD I0_TX[0]

A22

FD I0_TX[1]

G19

FD I0_TX[2]

E20

FD I0_TX[3]

G18

FD I1_TX[0]

B20

FD I1_TX[1]

C19

FD I1_TX[2]

D19

FD I1_TX[3]

F17

FD I0_FS YN C

J18

FD I1_FS YN C

J17

FD I_I NT

H20

FD I0_LSY NC

J19

FD I1_LSY NC

H17

PEG _ICO MP I

J22

PEG_ICOMPO

J21

PEG _RC OM PO

H22

PEG _ RX#[0 ]

K33

PEG _ RX#[1 ]

M35

PEG _ RX#[2 ]

L34

PEG _ RX#[3 ]

J35

PEG _ RX#[4 ]

J32

PEG _ RX#[5 ]

H34

PEG _ RX#[6 ]

H31

PEG _ RX#[7 ]

G33

PEG _ RX#[8 ]

G30

PEG _ RX#[9 ]

F35

PEG _RX#[1 0]

E34

PEG _RX#[1 1]

E32

PEG _RX#[1 2]

D33

PEG _RX#[1 3]

D31

PEG _RX#[1 4]

B33

PEG _RX#[1 5]

C32

PEG _R X[0]

J33

PEG _R X[1]

L35

PEG _R X[2]

K34

PEG _R X[3]

H35

PEG _R X[4]

H32

PEG _R X[5]

G34

PEG _R X[6]

G31

PEG _R X[7]

F33

PEG _R X[8]

F30

PEG _R X[9]

E35

PEG _ RX[10 ]

E33

PEG _ RX[11 ]

F32

PEG _ RX[12 ]

D34

PEG _ RX[13 ]

E31

PEG _ RX[14 ]

C33

PEG _ RX[15 ]

B32

PEG_TX# [0]

M29

PEG_TX# [1]

M32

PEG_TX# [2]

M31

PEG_TX# [3]

L32

PEG_TX# [4]

L29

PEG_TX# [5]

K31

PEG_TX# [6]

K28

PEG_TX# [7]

J30

PEG_TX# [8]

J28

PEG_TX# [9]

H29

PEG _T X#[10 ]

G27

PEG _T X#[11 ]

E29

PEG _T X#[12 ]

F27

PEG _T X#[13 ]

D28

PEG _T X#[14 ]

F26

PEG _T X#[15 ]

E25

PEG_TX[0]

M28

PEG_TX[1]

M33

PEG_TX[2]

M30

PEG_TX[3]

L31

PEG_TX[4]

L28

PEG_TX[5]

K30

PEG_TX[6]

K27

PEG_TX[7]

J29

PEG_TX[8]

J27

PEG_TX[9]

H28

PEG_TX[1 0]

G28

PEG_TX[1 1]

E28

PEG_TX[1 2]

F28

PEG_TX[1 3]

D27

PEG_TX[1 4]

E26

PEG_TX[1 5]

D25

eDP_ AU X

C15

eDP_ AU X#

D15

eDP_TX[0]

C17

eDP_TX[1]

F16

eDP_TX[2]

C16

eDP_TX[3]

G15

eDP_TX#[0]

C18

eDP_TX#[1]

E16

eDP_TX#[2]

D16

eDP_TX#[3]

F15

eDP_C OMPIO

A18

eDP_H PD

B16

eDP_ IC OM PO

A17

CAD NOTE: DP_COMPIO and ICOMP O sig nals

should be shorted near balls and routed with

- typical impedance < 25 mohms

PE G_TX# _6

PE G_TX# _2

PE G_TX# _5

PE G_TX# _7

PE G_TX# _3

PE G_TX# _0

PE G_TX# _1

PE G_TX# _4

DP Compensati on Signal

PEG_IRCOMP_R

C 587 0. 22u_10V_X5R _04

C 588 0. 22u_10V_X5R _04

20 mil

Sandy Bridge Processor 1/7 ( DMI,PEG,FDI )

3

2

1

1 :2 (4 mi ls : 8mil s)

PLACE NEAR U3

C 602 0. 22u_10V_X5R _04

PE G_TX_ 0

PE G_TX_ 6

PE G_TX_ 4

PE G_TX_ 2

PE G_TX_ 1

PE G_TX_ 5

PE G_TX_ 3

PE G_TX_ 7

PEG Compensa ti on Signal

C 593 0. 22u_10V_X5R _04

Schematic Diagrams

B.Schematic Diagrams

Sheet 2 of 49

Sandy Bridge

Processor 1/7

Sandy Bridge Processor 1/7 B - 3

http://hobi-elektronika.net

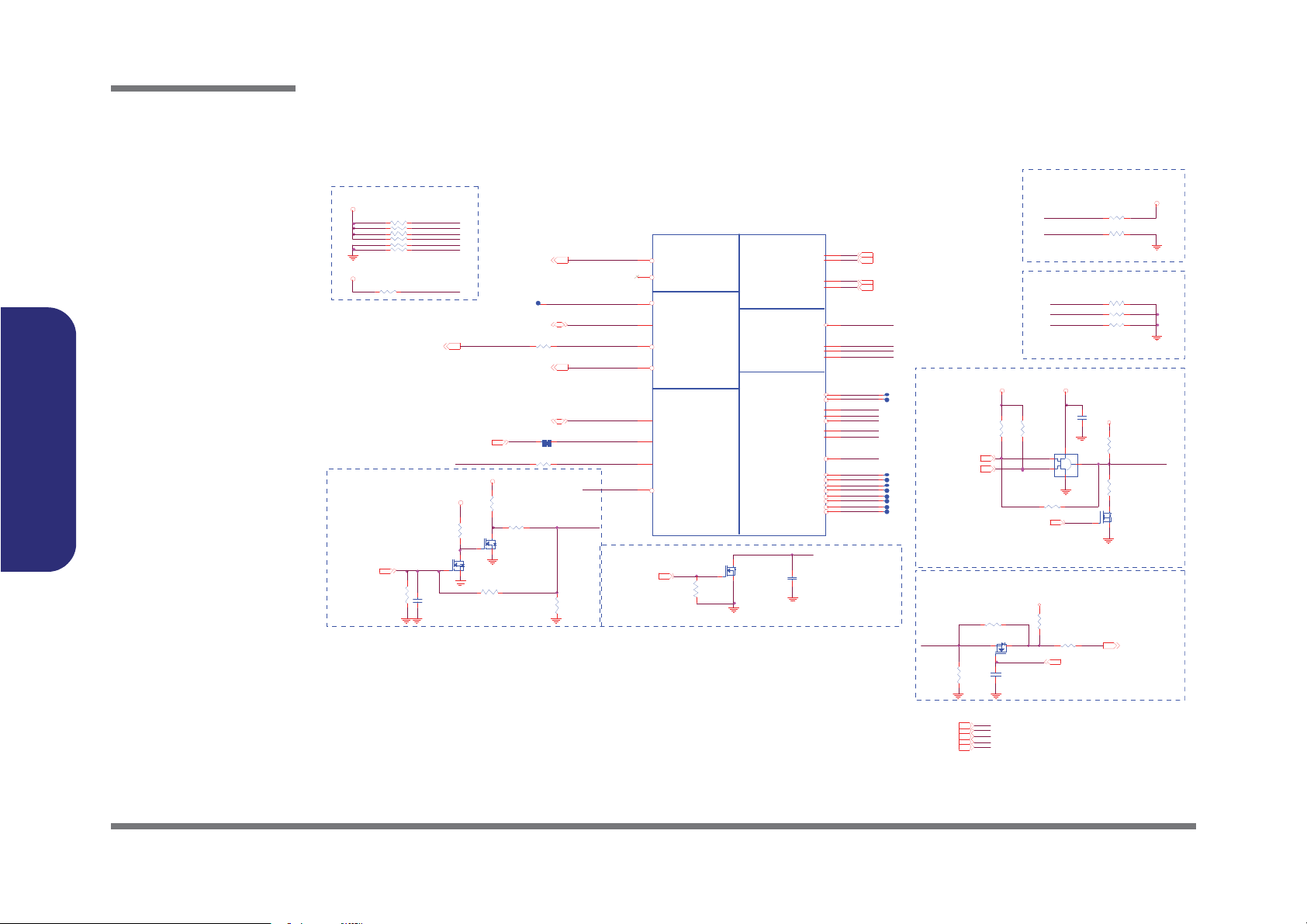

Page 3

Schematic Diagrams

C278

*0.1u_1 6V_ Y5V _0 4

H_PRO CH OT#

C31 5

0.047u_10V_X7R_04

R51 8 *1.5K _ 1%_0 4

R517

*750_1% _04

H_CPU PW R GD _R

S3 circuit:- DRAM PW R GO OD log ic

R17 4 13 0 _ 1%_ 0 4

CAD Note: Capacitor need to be placed

close to buffer output pin

R512

75_04

R529 200_1%_04

R531 140_1%_04

R52 8 25 .5 _ 1 %_0 4

R498 *10mil_short

R11 0 62 _ 0 4

R515 43.2_1%_04

R499 10K_04

1.05VS_VTT

TRACE WIDTH 10MIL, LENGTH <500MILS

H_CPUPWRGD_R

Processor Pul lu ps /P ul l do wn s

H_PROCHOT#

R10 9 56 _ 1 % _04

1.05VS_VTT

3.3VS

1.05V S_V TT2,5,23 ,24,25,35,39

3.3V2,8,11,12,16,18,19,20,22,23,24,25,27,28,29,30,33,35, 37,38,39

CLK_EXP_N 19

CLK_EXP_P 1 9

1.5VS_C PU6,35,38

CLK_DP_P 19

CLK _ DP _ N 19

H_PROCHOT#39

H_THRMTRIP#23

H_P ECI23,34

H_PM_SYNC20

H_CP UPW R GD23

BUF_CPU_RST#

XDP _DBR_R

S

D

G

Q37A

MTD N7002ZH S6R

2

61

S

D

G

Q37B

MTDN7002ZHS6R

5

34

H _ SNB_IVB#23

SM _RCO MP _2

SM _RCO MP _1

SM _RCO MP _0

XDP _TRST#

XDP _TCLK

VDD PWRGOOD_R

H_PRO CH OT# _ D

XDP _TMS

H_PR OC HO T#

CPUDRAMRST#

XDP _PREQ#

XDP _TDI_R

XDP _TDO_R

R524

100K_04

If PROCHOT# is not us ed,

th en it must b e t erminate d

with a 56-O +-5% pull-up

resistor to 1.05VS_VTT .

D DR 3 Co mp ens at io n Sign al s

BUF_ C PU_RS T#

SM_RCOMP_1

SM_RCOMP_0

SM_RCOMP_2

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

U49B

PZ98827-364B-01F

SM _ RC OM P[1]

A5

SM _ RC OM P[2]

A4

SM_DR AMRST #

R8

SM _ RC OM P[0]

AK1

BC L K#

A27

BC LK

A28

DPLL_REF_SSCLK#

A15

DPLL _R EF _ SSC LK

A16

CA TER R#

AL33

PEC I

AN33

PR OC HOT#

AL32

THER MTR IP#

AN32

SM _D RAMPW R OK

V8

RE S ET#

AR33

PR DY #

AP29

PREQ #

AP27

TCK

AR26

TMS

AR27

TR S T #

AP30

TDI

AR28

TDO

AP26

DBR #

AL35

BPM #[0]

AT28

BPM #[1]

AR29

BPM #[2]

AR30

BPM #[3]

AT30

BPM #[4]

AP32

BPM #[5]

AR31

BPM #[6]

AT31

BPM #[7]

AR32

PM _SY NC

AM34

SKTOC C#

AN34

PR OC _SE LEC T #

C26

UN CO REP W RG OO D

AP33

C621

68p_50V_NPO _04

PLT_RST#12,22,28

XDP _BPM0_ R

XDP _BPM1_ R

XDP _BPM2_ R

R658

10K _04

1.5V6,8,9,10,25,29,35,37,38

XDP _BPM4_ R

XDP _BPM3_ R

XDP _BPM5_ R

XDP _BPM6_ R

XDP _BPM7_ R

XDP _PRDY #

PM SYS _PW RG D_BUF

C62 2

47 p _ 50 V _ N P O _ 0 4

R186 0_04

H_PR OCH OT# _ EC34

R203

100K_04

Sandy Bridge Processor 2/7 ( CLK,MISC,JTAG )

3.3VS9,10,11,12, 18,19,20,21,22, 23,24,25,27,28,29,30,31,32,33,34,35,39

Q1 6

MTN7002ZHS3

G

DS

Bu ff er ed re se t to C PU

Q1 7

MTN7002ZHS3

G

DS

R225

4.99K_1% _04

CPU DR AMR ST#

R23 1 * 0 _04

R230

1K_04

1.5V

S3 circuit:- DRAM_ RS T# to me mo ry

should be high during S3

DRAMRST_CNTRL 8,19

R23 5 1K_ 04

DD R3 _ DR AMR ST # 9,1 0

R51 351_0 4

R50 651_0 4

R51 051_0 4

R51 151_0 4

R50 551_0 4

R50 8*51_04

3.3V S

1. 0 5 V S _ V T T

R494 1K_04

XD P _ TD O _ R

XD P_DBR _R

H_CATERR#

PU/PD for J TA G si gn al s

XD P_ TR ST#

XD P _ TM S

H _SNB_ IVB#

XD P_ PREQ #

XD P _ TD I _ R

XD P _ TC L K

U14

* MC 7 4V H C 1 G 08 D F T 1G

1

2

5

4

3

1.8VS_PWRGD20,37

PM _D RA M_PWR GD20

3.3V

R187

*200_04

P MSY S_ PW RG D_ BU F

R18 8

*100K_04

1.5VS_CPU

R175

200_1%_04

R168

*39_04

Q13

*MTN7002ZH S3

G

DS

SU SB35,37, 38

3.3V

Sandy Bridge Processor 2/7

B.Schematic Diagrams

Sheet 3 of 49

Sandy Bridge

Processor 2/7

B - 4 Sandy Bridge Processor 2/7

http://hobi-elektronika.net

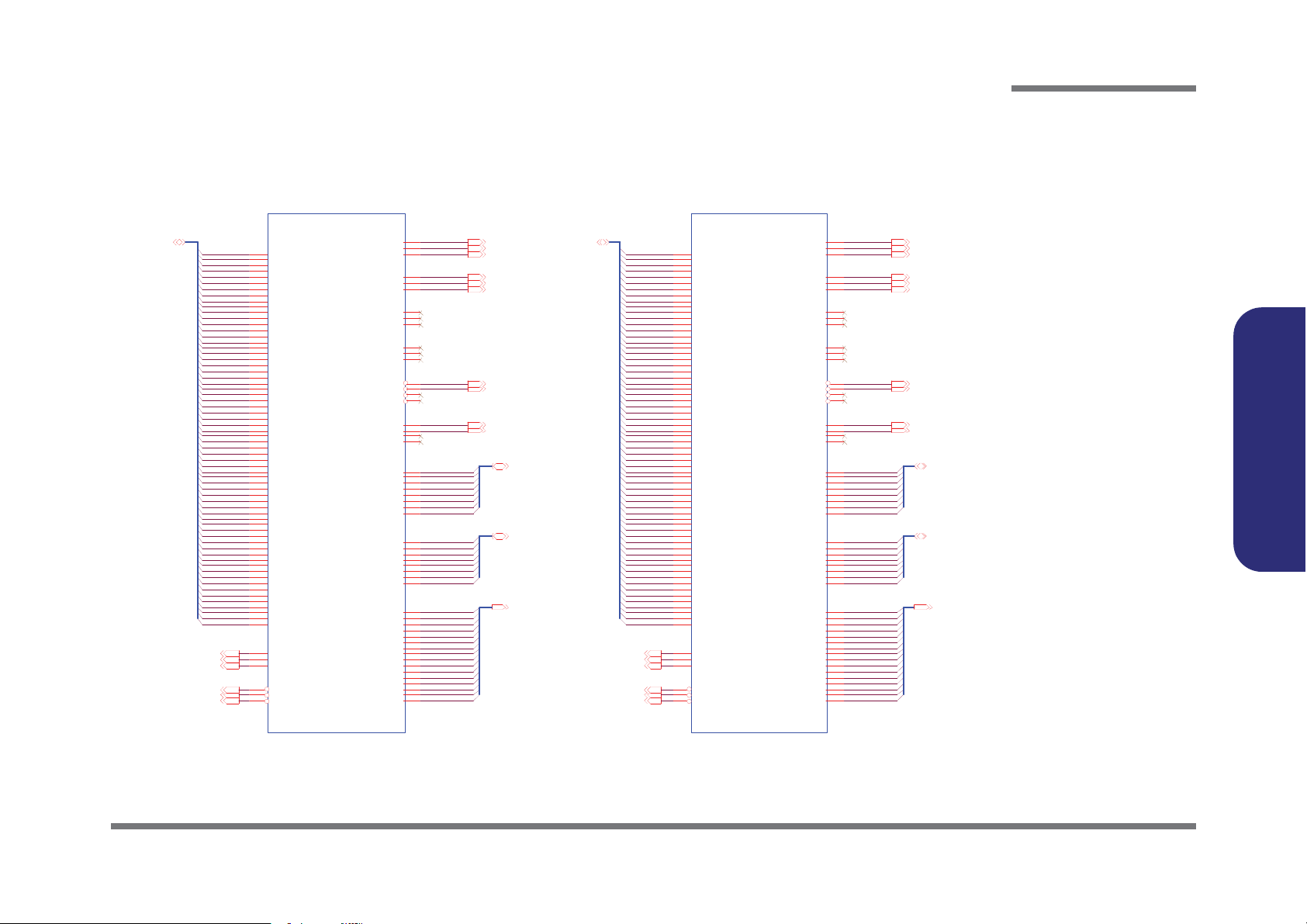

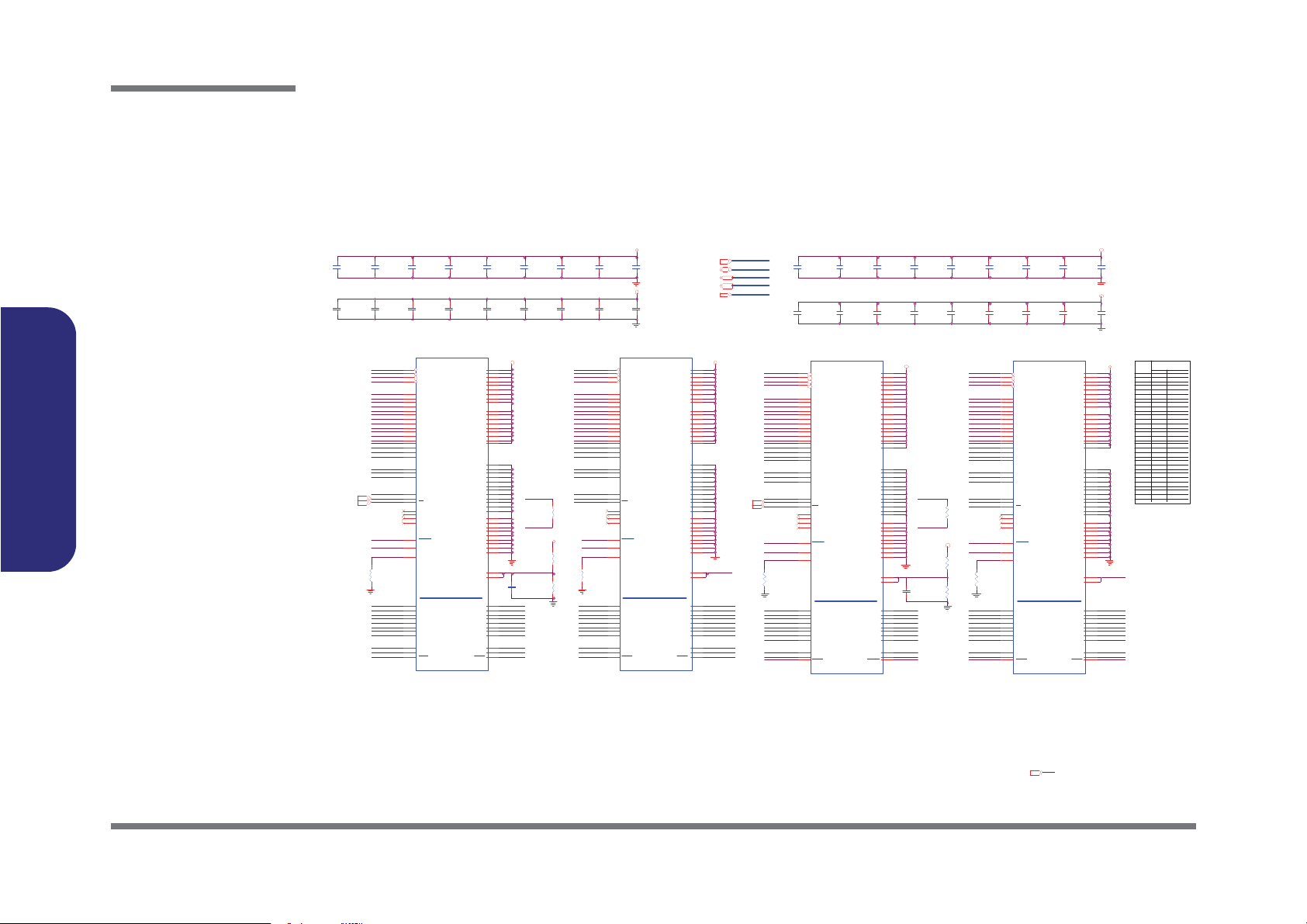

Page 4

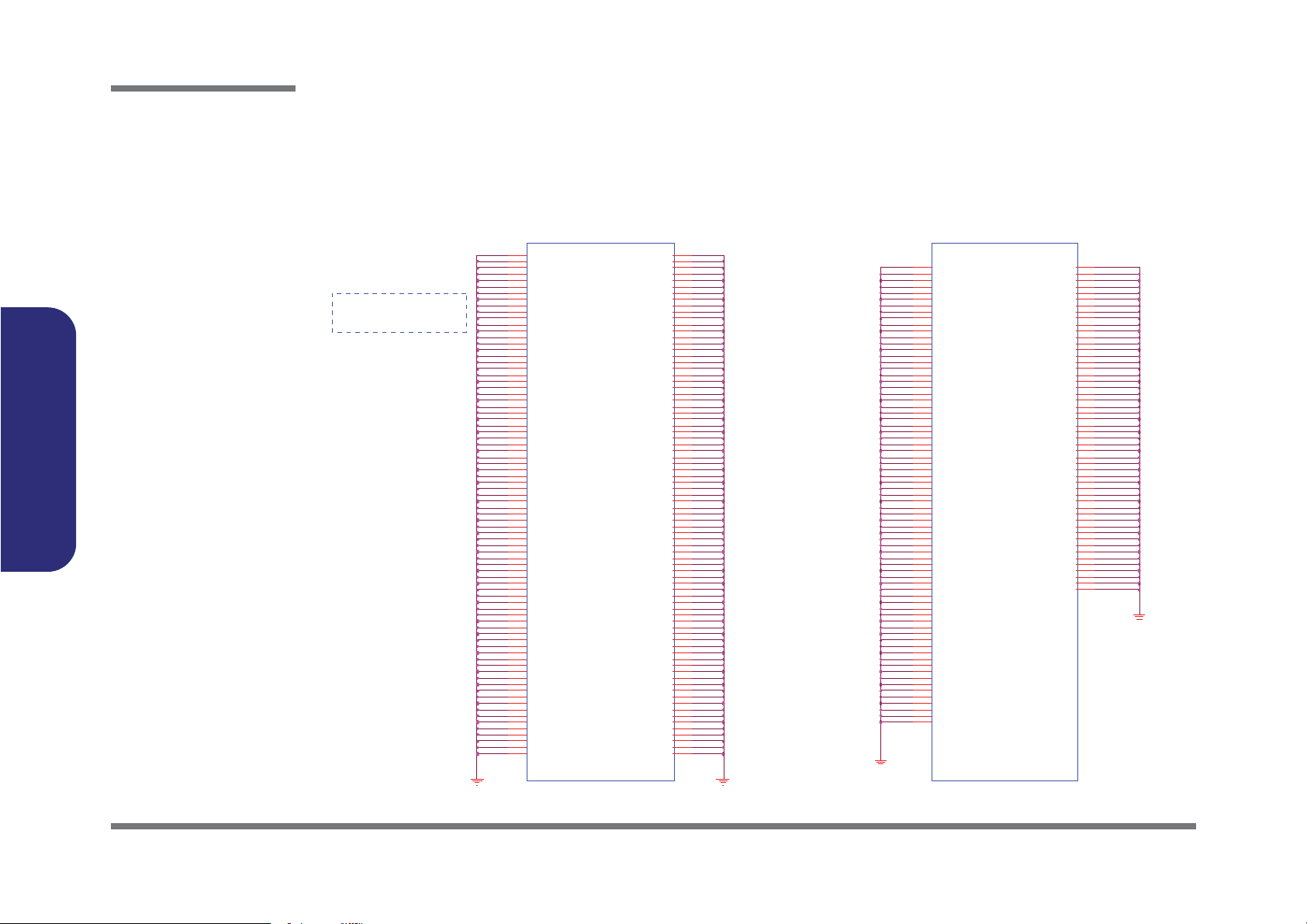

Sandy Bridge Processor 3/7

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS#0

M_A_DQS#2

M_A_DQS#1

M_A_DQS#3

M_A_DQS#4

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS0

M_A_DQS2

M_A_DQS1

M_A_DQS3

M_B_DQS#5

M_B_DQS#4

M_B_DQS#6

M_B_DQS#7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_A6

M_B_A5

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A9

M_B_A10

M_B_A11

M_B_A13

M_B_A12

M_B_A14

M_B_A15

M_B_A7

M_B_A8

M_B_DQS6

M_B_DQS5

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS7

M_B_DQS0

M_B_DQS1

M_B_ BS110

M_B_ BS010

M_A_DQ[63:0]9

M_A_CKE1 9

M_B_DQ[63: 0 ]10

M_B_ BS210

M_A_A[15 :0] 9

M_A_CLK_DDR#1 9

M_A_CLK_DDR19

M_A_CKE0 9

M_A_DQS#[7:0] 9

M_A_CS#1 9

M_A_CS#0 9

M_A_ODT1 9

M_A_CLK_DDR#0 9

M_A_CLK_DDR09

M_A_BS19

M_A_DQS[7:0] 9

M_A_ODT0 9

M_A_RAS#9

M_A_CAS#9

M_A_BS29

M_B_DQS#[7:0] 10

M_A_BS09

M_A_WE#9 M_B_WE#10

M_B_ RAS#10

M_B_DQS[7:0]10

M_B_A[15:0] 10

M_B_ CLK_ DD R310

M_B_CKE 3 1 0

M_B_ CAS#10

M_B_ CLK_ DD R210

M_B_CKE 2 1 0

M_B_ CLK_ DD R#3 10

M_B_OD T2 10

M_B_OD T3 10

M_B_ CLK_ DD R#2 10

M_B_CS#3 10

M_B_CS#2 10

DDR SYSTEM MEMORY A

U49C

PZ 98827-364B -01F

SA_B S[0 ]

AE10

SA_B S[1 ]

AF10

SA_B S[2 ]

V6

SA_C AS#

AE8

SA_R AS#

AD9

SA_W E#

AF9

SA_ CLK[0]

AB6

SA_ CLK[1]

AA5

SA_ CLK#[0]

AA6

SA_ CLK#[1]

AB5

SA_C KE[ 0]

V9

SA_C KE[ 1]

V10

SA_ CS#[0]

AK3

SA_ CS#[1]

AL3

SA_OD T[0]

AH3

SA_OD T[1]

AG3

SA_DQS[0]

D4

SA_DQS#[0]

C4

SA_DQS[1]

F6

SA_DQS#[1]

G6

SA_DQS[2]

K3

SA_DQS#[2]

J3

SA_DQS[3]

N6

SA_DQS#[3]

M6

SA_DQS[4]

AL5

SA_DQS#[4]

AL6

SA_DQS[5]

AM9

SA_DQS#[5]

AM8

SA_DQS[6]

AR11

SA_DQS#[6]

AR12

SA_DQS[7]

AM14

SA_DQS#[7]

AM15

SA_MA[ 0]

AD10

SA_MA[ 1]

W1

SA_MA[ 2]

W2

SA_MA[ 3]

W7

SA_MA[ 4]

V3

SA_MA[ 5]

V2

SA_MA[ 6]

W3

SA_MA[ 7]

W6

SA_MA[ 8]

V1

SA_MA[ 9]

W5

SA_ MA[10]

AD8

SA_ MA[11]

V4

SA_ MA[12]

W4

SA_ MA[13]

AF8

SA_ MA[14]

V5

SA_ MA[15]

V7

SA_D Q[ 0]

C5

SA_D Q[ 1]

D5

SA_D Q[ 2]

D3

SA_D Q[ 3]

D2

SA_D Q[ 4]

D6

SA_D Q[ 5]

C6

SA_D Q[ 6]

C2

SA_D Q[ 7]

C3

SA_D Q[ 8]

F10

SA_D Q[ 9]

F8

SA_D Q[ 10]

G10

SA_D Q[ 11]

G9

SA_D Q[ 12]

F9

SA_D Q[ 13]

F7

SA_D Q[ 14]

G8

SA_D Q[ 15]

G7

SA_D Q[ 16]

K4

SA_D Q[ 17]

K5

SA_D Q[ 18]

K1

SA_D Q[ 19]

J1

SA_D Q[ 20]

J5

SA_D Q[ 21]

J4

SA_D Q[ 22]

J2

SA_D Q[ 23]

K2

SA_D Q[ 24]

M8

SA_D Q[ 25]

N10

SA_D Q[ 26]

N8

SA_D Q[ 27]

N7

SA_D Q[ 28]

M10

SA_D Q[ 29]

M9

SA_D Q[ 30]

N9

SA_D Q[ 31]

M7

SA_D Q[ 32]

AG6

SA_D Q[ 33]

AG5

SA_D Q[ 34]

AK6

SA_D Q[ 35]

AK5

SA_D Q[ 36]

AH5

SA_D Q[ 37]

AH6

SA_D Q[ 38]

AJ5

SA_D Q[ 39]

AJ6

SA_D Q[ 40]

AJ8

SA_D Q[ 41]

AK8

SA_D Q[ 42]

AJ9

SA_D Q[ 43]

AK9

SA_D Q[ 44]

AH8

SA_D Q[ 45]

AH9

SA_D Q[ 46]

AL9

SA_D Q[ 47]

AL8

SA_D Q[ 48]

AP11

SA_D Q[ 49]

AN11

SA_D Q[ 50]

AL12

SA_D Q[ 51]

AM12

SA_D Q[ 52]

AM11

SA_D Q[ 53]

AL11

SA_D Q[ 54]

AP12

SA_D Q[ 55]

AN12

SA_D Q[ 56]

AJ1 4

SA_D Q[ 57]

AH14

SA_D Q[ 58]

AL15

SA_D Q[ 59]

AK15

SA_D Q[ 60]

AL14

SA_D Q[ 61]

AK14

SA_D Q[ 62]

AJ1 5

SA_D Q[ 63]

AH15

SA_ CLK[2]

AB4

SA_ CLK#[2]

AA4

SA_ CLK[3]

AB3

SA_ CLK#[3]

AA3

SA_C KE[ 2]

W9

SA_C KE[ 3]

W10

SA_ CS#[2]

AG1

SA_ CS#[3]

AH1

SA_OD T[2]

AG2

SA_OD T[3]

AH2

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ29

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ49

M_A_DQ38

M_A_DQ47

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ40

M_A_DQ39

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ34

M_A_DQ33

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ6

M_A_DQ5

M_A_DQ48

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ28

M_A_DQ50

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ12

M_A_DQ11

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ59

M_A_DQ63

M_B_DQ48

M_B_DQ47

M_A_DQ20

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ23

M_A_DQ0

M_A_DQ22

M_A_DQ21

M_A_DQ10

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_B_DQ62

M_B_DQ61

M_B_DQ60

M_B_DQ59

M_B_DQ58

M_B_DQ57

M_B_DQ56

M_B_DQ55

M_B_DQ54

M_B_DQ53

M_B_DQ52

M_B_DQ51

M_B_DQ50

M_B_DQ49

M_B_DQ9

M_B_DQ8

M_B_DQ7

M_B_DQ6

M_B_DQ5

M_B_DQ4

M_B_DQ3

M_B_DQ2

M_B_DQ1

M_B_DQ12

M_B_DQ11

M_B_DQ63

M_B_DQ20

M_B_DQ19

M_B_DQ18

M_B_DQ17

M_B_DQ16

M_B_DQ15

M_B_DQ14

M_B_DQ13

M_B_DQ0

M_B_DQ10

M_B_DQ36

M_B_DQ35

M_B_DQ34

M_B_DQ33

M_B_DQ32

M_B_DQ31

M_B_DQ30

M_B_DQ29

M_B_DQ28

M_B_DQ27

M_B_DQ26

M_B_DQ25

M_B_DQ24

M_B_DQ23

M_B_DQ22

M_B_DQ21

M_B_DQ46

M_B_DQ45

M_B_DQ44

M_B_DQ43

M_B_DQ42

M_B_DQ41

M_B_DQ40

M_B_DQ39

M_B_DQ38

M_B_DQ37

Sandy Bridge Processor 3/7 ( DDR3 )

D DR SYSTEM MEMORY B

U49D

PZ98827-364B -01F

SB_B S[0 ]

AA9

SB_B S[1 ]

AA7

SB_B S[2 ]

R6

SB_C AS#

AA10

SB_R AS#

AB8

SB_W E#

AB9

SB_C LK[ 0]

AE2

SB_C LK[ 1]

AE1

SB_CLK#[0]

AD2

SB_CLK#[1]

AD1

SB_CKE[0]

R9

SB_CKE[1]

R10

SB_ODT[0]

AE4

SB_ODT[1]

AD4

SB _DQS[4]

AN6

SB_ DQS#[4]

AN5

SB _DQS[5]

AP8

SB_ DQS#[5]

AP9

SB _DQS[6]

AK11

SB_ DQS#[6]

AK12

SB _DQS[7]

AP14

SB_ DQS#[7]

AP15

SB _DQS[0]

C7

SB_ DQS#[0]

D7

SB _DQS[1]

G3

SB_ DQS#[1]

F3

SB _DQS[2]

J6

SB_ DQS#[2]

K6

SB _DQS[3]

M3

SB_ DQS#[3]

N3

SB_MA[ 0]

AA8

SB_MA[ 1]

T7

SB_MA[ 2]

R7

SB_MA[ 3]

T6

SB_MA[ 4]

T2

SB_MA[ 5]

T4

SB_MA[ 6]

T3

SB_MA[ 7]

R2

SB_MA[ 8]

T5

SB_MA[ 9]

R3

SB_MA[ 10]

AB7

SB_MA[ 11]

R1

SB_MA[ 12]

T1

SB_MA[ 13]

AB10

SB_MA[ 14]

R5

SB_MA[ 15]

R4

SB_D Q[0 ]

C9

SB_D Q[1 ]

A7

SB_D Q[2 ]

D10

SB_D Q[3 ]

C8

SB_D Q[4 ]

A9

SB_D Q[5 ]

A8

SB_D Q[6 ]

D9

SB_D Q[7 ]

D8

SB_D Q[8 ]

G4

SB_D Q[9 ]

F4

SB_D Q[1 0]

F1

SB_D Q[1 1]

G1

SB_D Q[1 2]

G5

SB_D Q[1 3]

F5

SB_D Q[1 4]

F2

SB_D Q[1 5]

G2

SB_D Q[1 6]

J7

SB_D Q[1 7]

J8

SB_D Q[1 8]

K10

SB_D Q[1 9]

K9

SB_D Q[2 0]

J9

SB_D Q[2 1]

J10

SB_D Q[2 2]

K8

SB_D Q[2 3]

K7

SB_D Q[2 4]

M5

SB_D Q[2 5]

N4

SB_D Q[2 6]

N2

SB_D Q[2 7]

N1

SB_D Q[2 8]

M4

SB_D Q[2 9]

N5

SB_D Q[3 0]

M2

SB_D Q[3 1]

M1

SB_D Q[3 2]

AM5

SB_D Q[3 3]

AM6

SB_D Q[3 4]

AR3

SB_D Q[3 5]

AP3

SB_D Q[3 6]

AN3

SB_D Q[3 7]

AN2

SB_D Q[3 8]

AN1

SB_D Q[3 9]

AP2

SB_D Q[4 0]

AP5

SB_D Q[4 1]

AN9

SB_D Q[4 2]

AT5

SB_D Q[4 3]

AT6

SB_D Q[4 4]

AP6

SB_D Q[4 5]

AN8

SB_D Q[4 6]

AR6

SB_D Q[4 7]

AR5

SB_D Q[4 8]

AR9

SB_D Q[4 9]

AJ1 1

SB_D Q[5 0]

AT8

SB_D Q[5 1]

AT9

SB_D Q[5 2]

AH1 1

SB_D Q[5 3]

AR8

SB_D Q[5 4]

AJ1 2

SB_D Q[5 5]

AH1 2

SB_D Q[5 6]

AT11

SB_D Q[5 7]

AN1 4

SB_D Q[5 8]

AR1 4

SB_D Q[5 9]

AT14

SB_D Q[6 0]

AT12

SB_D Q[6 1]

AN1 5

SB_D Q[6 2]

AR1 5

SB_D Q[6 3]

AT15

SB_C LK[ 2]

AB2

SB_CLK#[2]

AA2

SB_CKE[2]

T9

SB_C LK[ 3]

AA1

SB_CLK#[3]

AB1

SB_CKE[3]

T10

SB_C S#[ 0]

AD3

SB_C S#[ 1]

AE3

SB_C S#[ 2]

AD6

SB_C S#[ 3]

AE6

SB_ODT[2]

AD5

SB_ODT[3]

AE5

M_A_A9

M_A_A4

M_A_A6

M_A_A5

M_A_A7

M_A_A8

M_A_A15

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A10

M_A_A12

M_A_A11

M_A_A13

M_A_A14

Schematic Diagrams

B.Schematic Diagrams

http://hobi-elektronika.net

Sandy Bridge Processor 3/7 B - 5

Sheet 4 of 49

Sandy Bridge

Processor 3/7

Page 5

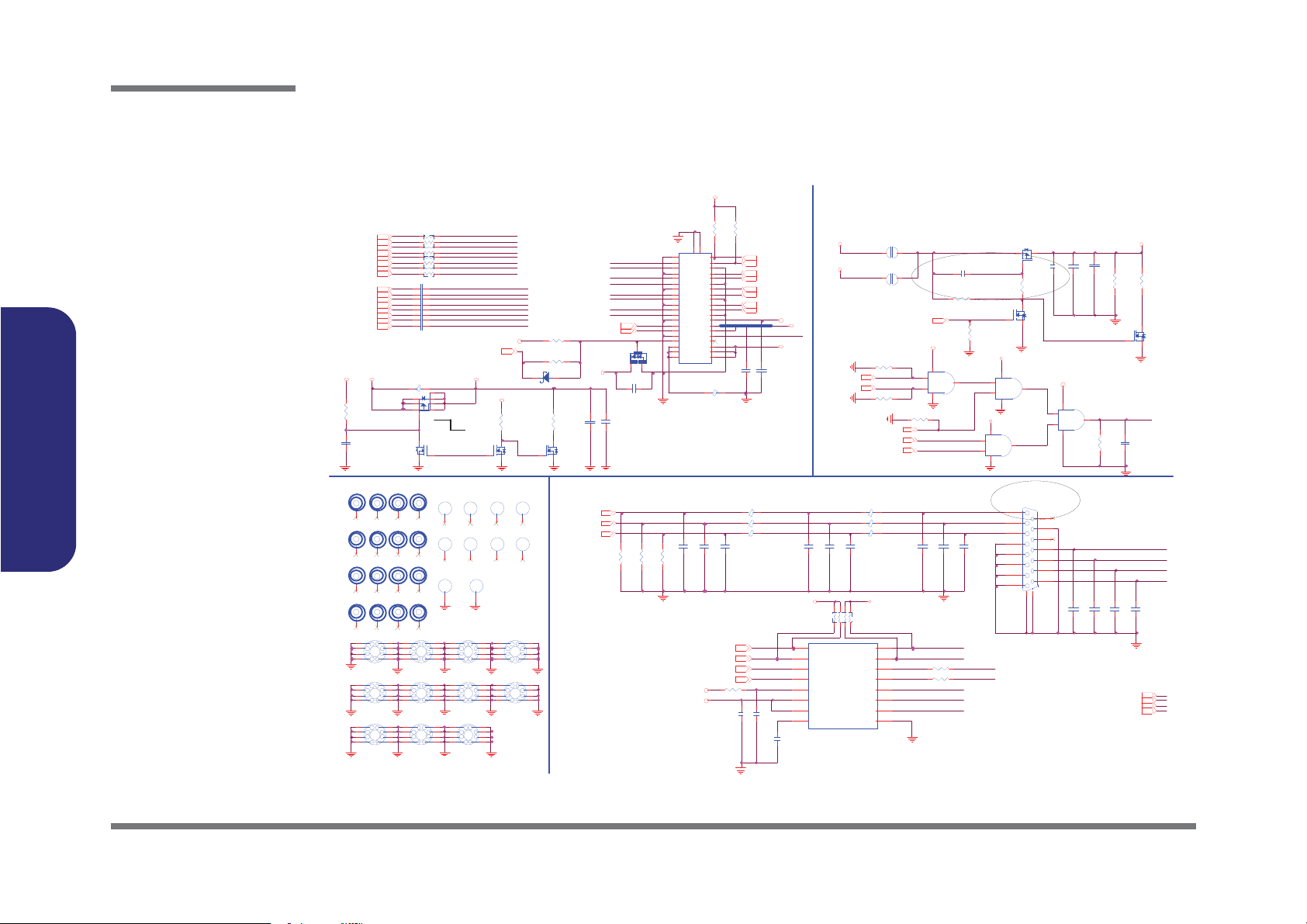

Sandy Bridge Processor 4/7 ( POWER )

PROCESSOR CORE POWER PROCESSOR UNCO RE PO WER

48A

ICCMAX Maximum Processor SV 48

VCCP_SENSE38

CAD Note: H_CPU_SVIDALRT# _R,H_CPU_SVIDDAT_R

Place the PU resistors cl ose to CPU

H_ CPU_SVIDDAT_R

R129 *15mil_s hort_ 06

SVID Signals

CAD Note: H_CPU_SVIDCLK_R

Place the PU

resistors close to VR

C17 4

10u_6.3 V_X5R _06

C230

22u_6.3V_X5R_0 8

C61 8

22u_6.3V_X5R_08

R118 75_04

R94

100_04

C228

*22 u_6 .3V_ X5R_08

C192

*10u_6.3V_ X5R _06

C193

*10u_6.3V_X5R_06

C236

22u_6. 3V_X 5R_0 8

C650

22u_6. 3V_X 5R_0 8

C195

*22 u_6 .3V_ X5R_08

C125

*22u_6.3V_X5R_08

R523

10_04

C17 3

10u_6.3V_X5R_06

C227

*22 u_6 .3V_ X5R_08

C617

22u_6. 3V_X5 R_08

C627

22u_6.3V_X5R_08

C247

22u_6.3V_X5R_0 8

C169

*22u_6.3V_X5R_08

C191

*10u_6.3V_X5R_06

C641

*22 u_6 .3V_ X5R_08

C231

22u_6. 3V_X 5R_0 8

C643

*22u_6. 3V_X5R_08

C644

22u_6.3V_X5R_0 8

C616

22u_6.3V_X5R_08

C652

22u_6.3V_X5R_0 8

C645

22u_6.3V_X5R_0 8

C170

10u_6.3V_X5R_06

C224

*22u_6. 3V_X5R_08

C229

*22u_6. 3V_X 5R _08

C646

22u_6. 3V_X 5R_0 8

C61 5

22u_6.3V_X5R_08

C165

*22u_6.3V_X5R_08

C659

22u_6. 3V_X 5R_0 8

C629

*22u_6. 3V_X5 R_08

C226

*22u_6. 3V_X 5R _08

C223

22u_6. 3V_X 5R_0 8

C171

10u_6. 3V_X5 R_0 6

C19 0

*10u_6.3V_X5R_06

C647

22u_6. 3V_X 5R_0 8

C62 8

22u_6.3V_X5R_08

R116 43.2_1%_04

C61 3

22u_6.3V_X5R_08

R122 130_1% _04

C640

*22u_6. 3V_X 5R _08

C172

10u_6. 3V_X5 R_0 6

C619

22u_6.3V_X5R_08

R526

10_04

R120 0_04

C222

22u_6. 3V_X 5R_0 8

C225

*22u_6. 3V_X5 R_08

C194

*22 u_6 .3V_ X5R_08

C654

22u_6. 3V_X 5R_0 8

C216

*22u_6. 3V_X5R_08

R117 *54.9_1%_04

C161

22u_6.3V_X5R_08

C642

*22 u_6 .3V_ X5R_08

C62 0

22u_6.3 V_X5R _08

R87

100_04

C16 6

*22u_6.3V_X5R_08

C17 5

10u_6.3V_X5R_06

C237

22u_6.3V_X5R_0 8

C162

*22u_6.3V_X5R_0 8

VCO RE

VCORE

1.05VS_VT T

1. 05VS_ VTT

VCORE

1.05VS_VT T

1. 05VS_ VTT

VCOR E40

1.05VS_VTT

VCO RE

VCORE_ VSS_ SENSE 3 9

1.05V S_V T T2, 3,23 ,24,25,35,3 9

H_CPU_SVIDALRT#39

H_CPU_SVIDDAT 39

H_CPU_SVIDCLK 39

VCORE_VCC_SENSE 39

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_ CPU_SVIDALRT#_R

H_ CPU_SVIDCL K_R

H_CPU_SVIDDAT_R

R114 0_04

VSSP_ SENSE 3 8

+

C639

220u_6.3V_6.3*6.3*4.2

+

C668

220u_6.3V_6.3*6.3*4.2

1. 0 5VS_V CC P_F

8.5A

POWER

CO RE SUP PLY

PEG AND DDR

SENSE LINES SVID

U49 F

PZ98827-364B-01F

VCC_SENSE

AJ3 5

VSS_ SENSE

AJ3 4

VIDALERT#

AJ2 9

VIDSCLK

AJ3 0

VID SOU T

AJ2 8

VSSI O_ SENSE

A10

VCC1

AG35

VCC2

AG34

VCC3

AG33

VCC4

AG32

VCC5

AG31

VCC6

AG30

VCC7

AG29

VCC8

AG28

VCC9

AG27

VCC10

AG26

VCC11

AF35

VCC12

AF34

VCC13

AF33

VCC14

AF32

VCC15

AF31

VCC16

AF30

VCC17

AF29

VCC18

AF28

VCC19

AF27

VCC20

AF26

VCC21

AD35

VCC22

AD34

VCC23

AD33

VCC24

AD32

VCC25

AD31

VCC26

AD30

VCC27

AD29

VCC28

AD28

VCC29

AD27

VCC30

AD26

VCC31

AC35

VCC32

AC34

VCC33

AC33

VCC34

AC32

VCC35

AC31

VCC36

AC30

VCC37

AC29

VCC38

AC28

VCC39

AC27

VCC40

AC26

VCC41

AA35

VCC42

AA34

VCC43

AA33

VCC44

AA32

VCC45

AA31

VCC46

AA30

VCC47

AA29

VCC48

AA28

VCC49

AA27

VCC50

AA26

VCC51

Y35

VCC52

Y34

VCC53

Y33

VCC54

Y32

VCC55

Y31

VCC56

Y30

VCC57

Y29

VCC58

Y28

VCC59

Y27

VCC60

Y26

VCC61

V35

VCC62

V34

VCC63

V33

VCC64

V32

VCC65

V31

VCC66

V30

VCC67

V29

VCC68

V28

VCC69

V27

VCC70

V26

VCC71

U35

VCC72

U34

VCC73

U33

VCC74

U32

VCC75

U31

VCC76

U30

VCC77

U29

VCC78

U28

VCC79

U27

VCC80

U26

VCC81

R35

VCC82

R34

VCC83

R33

VCC84

R32

VCC85

R31

VCC86

R30

VCC87

R29

VCC88

R28

VCC89

R27

VCC90

R26

VCC91

P35

VCC92

P34

VCC93

P33

VCC94

P32

VCC95

P31

VCC96

P30

VCC97

P29

VCC98

P28

VCC99

P27

VCC100

P26

VCCIO1

AH1 3

VCCIO12

J11

VCCIO18

G12

VCCIO19

F14

VCCIO20

F13

VCCIO21

F12

VCCIO22

F11

VCCIO23

E14

VCCIO24

E12

VCCIO2

AH1 0

VCCIO3

AG10

VCCIO4

AC1 0

VCCIO5

Y10

VCCIO6

U10

VCCIO7

P10

VCCIO8

L10

VCCIO9

J14

VCCIO10

J13

VCCIO11

J12

VCCIO13

H14

VCCIO14

H12

VCCIO15

H11

VCCIO16

G14

VCCIO17

G13

VCCIO25

E11

VCCIO32

C12

VCCIO33

C11

VCCIO34

B14

VCCIO35

B12

VCCIO36

A14

VCCIO37

A13

VCCIO38

A12

VCCIO39

A11

VCCIO26

D14

VCCIO27

D13

VCCIO28

D12

VCCIO29

D11

VCCIO30

C14

VCCIO31

C13

VCCI O_SENSE

B10

VCCIO40

J23

B.Schematic Diagrams

Schematic Diagrams

Sandy Bridge Processor 4/7

Sheet 5 of 49

Sandy Bridge

Processor 4/7

B - 6 Sandy Bridge Processor 4/7

http://hobi-elektronika.net

Page 6

Sandy Bridge Processor 5/7 ( GRAPHICS POWER )

C220

22u_6.3V_X5R _08

C21 2

22u_6.3V_X5R _08

POWER

GRAPHICS

DDR3 -1.5V RAILS

SENSE

LINES

1.8V RAIL

SA RAIL

VREFMISC

U49G

PZ 98827-364B-01F

SM_VR EF

AL1

VS SAXG_SEN SE

AK 34

VAXG_SEN SE

AK 35

VAXG 1

AT24

VAXG 2

AT23

VAXG 3

AT21

VAXG 4

AT20

VAXG 5

AT18

VAXG 6

AT17

VAXG 7

AR24

VAXG 8

AR23

VAXG 9

AR21

VAXG 10

AR20

VAXG 11

AR18

VAXG 12

AR17

VAXG 13

AP24

VAXG 14

AP23

VAXG 15

AP21

VAXG 16

AP20

VAXG 17

AP18

VAXG 18

AP17

VAXG 19

AN24

VAXG 20

AN23

VAXG 21

AN21

VAXG 22

AN20

VAXG 23

AN18

VAXG 24

AN17

VAXG 25

AM24

VAXG 26

AM23

VAXG 27

AM21

VAXG 28

AM20

VAXG 29

AM18

VAXG 30

AM17

VAXG 31

AL24

VAXG 32

AL23

VAXG 33

AL21

VAXG 34

AL20

VAXG 35

AL18

VAXG 36

AL17

VAXG 37

AK24

VAXG 38

AK23

VAXG 39

AK21

VAXG 40

AK20

VAXG 41

AK18

VAXG 42

AK17

VAXG 43

AJ2 4

VAXG 44

AJ2 3

VAXG 45

AJ2 1

VAXG 46

AJ2 0

VAXG 47

AJ1 8

VAXG 48

AJ1 7

VAXG 49

AH24

VAXG 50

AH23

VAXG 51

AH21

VAXG 52

AH20

VAXG 53

AH18

VAXG 54

AH17

VDD Q11

U4

VDD Q12

U1

VDD Q13

P7

VDD Q14

P4

VDD Q15

P1

VDD Q1

AF 7

VDD Q2

AF 4

VDD Q3

AF 1

VDD Q4

AC 7

VDD Q5

AC 4

VDD Q6

AC 1

VDD Q7

Y7

VDD Q8

Y4

VDD Q9

Y1

VDD Q10

U7

VC CPLL 1

B6

VC CPLL 2

A6

VCC SA1

M27

VCC SA2

M26

VCC SA3

L26

VCC SA4

J26

VCC SA5

J25

VCC SA6

J24

VCC SA7

H26

VCC SA8

H25

VCC SA_SEN SE

H23

VC CS A_ VID1

C24

VC CPLL 3

A2

FC_C22

C22

6A

+

C18 9

22 0 u _ 6.3V_ 6 .3 *6.3 *4.2

10/22

C632

22 u _ 6 . 3V _X 5 R _ 0 8

VC CS A_SENSE 37

C62 4

22u_6.3V_X5R _08

V CC SA_VID1 37

+

C669

560u_2.5V_6.6*6.6*5.9

12A

C211

22u_6.3V_X5R _08

C16 4

10u_6.3V _X5R_08

C68 2

10u_6.3V _X5R_06

C251

10u_6.3V_X5R_06

C183

22 u _ 6 . 3V _X 5 R _ 0 8

C185

22 u _ 6 . 3V _X 5 R _ 0 8

C151

10u_6.3V_X5R_06

C198

22u_6.3V_X5R_08

C656

22u_6.3V_X5R_08

C663

1u_6.3V_X5R_04

C199

22u_6.3V_X5R _08

+

C126

* 3 30 U _ 2. 5 V _ D 2_ D

C65 5

22u_6.3V_X5R _08

C22 1

22u_6.3V_X5R _08

C670

1u_6.3V_Y5 V_0 4

C16 8

22u_6.3V_X5R _08

C679

10u_6.3V_X5R_06

C310

0.1u_10V_X5R _04

C18 4

22u_6.3V_X5R _08

C30 8

0.1u_10V_X5R_04

C 163

10u_6.3V_X5R_08

C678

10u_6.3V_X5R_06

C681

10u_6.3V_X5R_06

C67 7

10u_6.3V _X5R_06

C680

10u_6.3V_X5R_06

1. 5 V S _C P U

0.85VS

VG FX_ CO RE

1.8VS

33A

1.5VS_CPU

1.5V

1.5V3,8,9,10, 25,29,35,37,38

VGFX_CO RE40

VSS _GT _S ENSE 39

VC C_G T_SEN SE 39

1.5V S_C PU3, 3 5 , 3 8

1. 8V S23,24,37

0.85VS37

VC CSA_VID 0 37

R509 10K_04

R648 *0_04

+

C683

560u_2.5V_6.6*6.6*5.9

1.05VS18,19,20, 24,25,29,35,37,38,39

CAD Note: +V_SM_VREF should

have 10 mil trace width

V_SM_VR EF

Q18

*AO 3 402 L

G

DS

R263

1K_1%_04

R266

* 1 00 K _ 1 % _0 4

R265

1K_1%_04

1.5V

SUSB# 2 0,2 9,34 ,35

R123

*1 0 K _ 0 4

1.05VS

R126

10K_04

1.2 A

R53 00_04 V_SM _ VREF_C NT

V_SM_VR EF

V_SM _V REF_C NT

C355

0.1u_10V_X5R _04

3.3VS3,9,10,11, 12,18,19,20,21,22,23,24,25,27,28,29,30,31,32,33,34, 35,39

1.5VS24 , 3 5

VCC SA_SEN SE

Sandy Bridge Processor 5/7

Schematic Diagrams

B.Schematic Diagrams

Sheet 6 of 49

Sandy Bridge Processor 5/7 B - 7

Sandy Bridge

Processor 5/7

http://hobi-elektronika.net

Page 7

Schematic Diagrams

VSS

U49H

PZ 98827 -364B-0 1F

VS S1

AT35

VS S2

AT32

VS S3

AT29

VS S4

AT27

VS S5

AT25

VS S6

AT22

VS S7

AT19

VS S8

AT16

VS S9

AT13

VS S1 0

AT10

VS S1 1

AT7

VS S1 2

AT4

VS S1 3

AT3

VS S1 4

AR25

VS S1 5

AR22

VS S1 6

AR19

VS S1 7

AR16

VS S1 8

AR13

VS S1 9

AR10

VS S2 0

AR7

VS S2 1

AR4

VS S2 2

AR2

VS S2 3

AP 34

VS S2 4

AP 31

VS S2 5

AP 28

VS S2 6

AP 25

VS S2 7

AP 22

VS S2 8

AP 19

VS S2 9

AP 16

VS S3 0

AP 13

VS S3 1

AP 10

VS S3 2

AP7

VS S3 3

AP4

VS S3 4

AP1

VS S3 5

AN30

VS S3 6

AN27

VS S3 7

AN25

VS S3 8

AN22

VS S3 9

AN19

VS S4 0

AN16

VS S4 1

AN13

VS S4 2

AN10

VS S4 3

AN7

VS S4 4

AN4

VS S4 5

AM29

VS S4 6

AM25

VS S4 7

AM22

VS S4 8

AM19

VS S4 9

AM16

VS S5 0

AM13

VS S5 1

AM10

VS S5 2

AM7

VS S5 3

AM4

VS S5 4

AM3

VS S5 5

AM2

VS S5 6

AM1

VS S5 7

AL3 4

VS S5 8

AL3 1

VS S5 9

AL2 8

VS S6 0

AL2 5

VS S6 1

AL2 2

VS S6 2

AL1 9

VS S6 3

AL1 6

VS S6 4

AL1 3

VS S6 5

AL1 0

VS S6 6

AL7

VS S6 7

AL4

VS S6 8

AL2

VS S6 9

AK 33

VS S7 0

AK 30

VS S7 1

AK 27

VS S7 2

AK 25

VS S7 3

AK 22

VS S7 4

AK 19

VS S7 5

AK 16

VS S7 6

AK 13

VS S7 7

AK 10

VS S7 8

AK7

VS S7 9

AK4

VS S8 0

AJ25

VSS81

AJ22

VSS82

AJ19

VSS83

AJ16

VSS84

AJ13

VSS85

AJ10

VSS86

AJ7

VSS87

AJ4

VSS88

AJ3

VSS89

AJ2

VSS90

AJ1

VSS91

AH35

VSS92

AH34

VSS93

AH32

VSS94

AH30

VSS95

AH29

VSS96

AH28

VSS97

AH26

VSS98

AH25

VSS99

AH22

VSS100

AH19

VSS101

AH16

VSS102

AH7

VSS103

AH4

VSS104

AG9

VSS105

AG8

VSS106

AG4

VSS107

AF6

VSS108

AF5

VSS109

AF3

VSS110

AF2

VSS111

AE35

VSS112

AE34

VSS113

AE33

VSS114

AE32

VSS115

AE31

VSS116

AE30

VSS117

AE29

VSS118

AE28

VSS119

AE27

VSS120

AE26

VSS121

AE9

VSS122

AD7

VSS123

AC9

VSS124

AC8

VSS125

AC6

VSS126

AC5

VSS127

AC3

VSS128

AC2

VSS129

AB35

VSS130

AB34

VSS131

AB33

VSS132

AB32

VSS133

AB31

VSS134

AB30

VSS135

AB29

VSS136

AB28

VSS137

AB27

VSS138

AB26

VSS139

Y9

VSS140

Y8

VSS141

Y6

VSS142

Y5

VSS143

Y3

VSS144

Y2

VSS145

W35

VSS146

W34

VSS147

W33

VSS148

W32

VSS149

W31

VSS150

W30

VSS151

W29

VSS152

W28

VSS153

W27

VSS154

W26

VSS155

U9

VSS156

U8

VSS157

U6

VSS158

U5

VSS159

U3

VSS160

U2

Sandy Bridge Processor 6/7 ( GND )

VSS

U49I

PZ98 827-3 64B-01F

VSS161

T35

VSS162

T34

VSS163

T33

VSS164

T32

VSS165

T31

VSS166

T30

VSS167

T29

VSS168

T28

VSS169

T27

VSS170

T26

VSS171

P9

VSS172

P8

VSS173

P6

VSS174

P5

VSS175

P3

VSS176

P2

VSS177

N35

VSS178

N34

VSS179

N33

VSS180

N32

VSS181

N31

VSS182

N30

VSS183

N29

VSS184

N28

VSS185

N27

VSS186

N26

VSS187

M34

VSS188

L33

VSS189

L30

VSS190

L27

VSS191

L9

VSS192

L8

VSS193

L6

VSS194

L5

VSS195

L4

VSS196

L3

VSS197

L2

VSS198

L1

VSS199

K35

VSS200

K32

VSS201

K29

VSS202

K26

VSS203

J34

VSS204

J31

VSS205

H33

VSS206

H30

VSS207

H27

VSS208

H24

VSS209

H21

VSS210

H18

VSS211

H15

VSS212

H13

VSS213

H10

VSS214

H9

VSS215

H8

VSS216

H7

VSS217

H6

VSS218

H5

VSS219

H4

VSS220

H3

VSS221

H2

VSS222

H1

VSS223

G35

VSS224

G32

VSS225

G29

VSS226

G26

VSS227

G23

VSS228

G20

VSS229

G17

VSS230

G11

VSS231

F34

VSS232

F31

VSS233

F29

VS S234

F22

VS S235

F19

VS S236

E30

VS S237

E27

VS S238

E24

VS S239

E21

VS S240

E18

VS S241

E15

VS S242

E13

VS S243

E10

VS S244

E9

VS S245

E8

VS S246

E7

VS S247

E6

VS S248

E5

VS S249

E4

VS S250

E3

VS S251

E2

VS S252

E1

VS S253

D35

VS S254

D32

VS S255

D29

VS S256

D26

VS S257

D20

VS S258

D17

VS S259

C34

VS S260

C31

VS S261

C28

VS S262

C27

VS S263

C25

VS S264

C23

VS S265

C10

VS S266

C1

VS S267

B22

VS S268

B19

VS S269

B17

VS S270

B15

VS S271

B13

VS S272

B11

VS S273

B9

VS S274

B8

VS S275

B7

VS S276

B5

VS S277

B3

VS S278

B2

VS S279

A35

VS S280

A32

VS S281

A29

VS S282

A26

VS S283

A23

VS S284

A20

VS S285

A3

CA D Note : 0 ohm re si stor

should be placed close

to CPU

Sandy Bridge Processor 6/7

B.Schematic Diagrams

B - 8 Sandy Bridge Processor 6/7

Sheet 7 of 49

Sandy Bridge

Processor 6/7

http://hobi-elektronika.net

Page 8

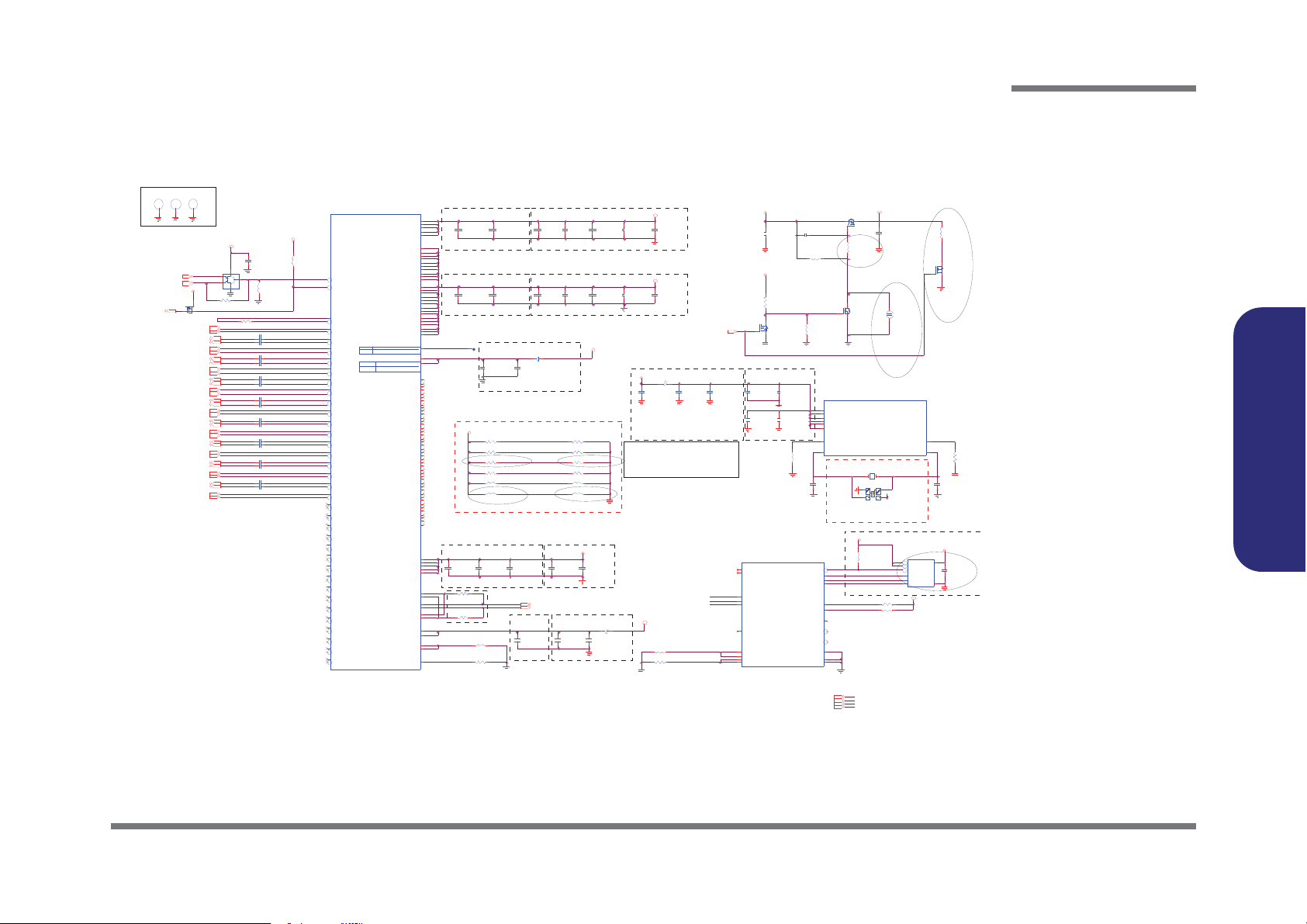

Sandy Bridge Processor 7/7

CFG2

VREF_CH_A_DIMM

R51 4 10K_ 1 %_0 4

3. 3 V

H_SN B_I VB#_PWR CT RL

H_C PU_RSV D 2

H_C PU_RSV D 1

H_C PU_RSV D 4

H_C PU_RSV D 3

MVREF_DQ _DIM1

On CRB

H_SNB_IVB#_PWRCTRL = low, 1.0V

H_SNB_IVB#_PWRCTRL = high/NC, 1.05V

CFG7

PEG DEFER TRAININ G

1: (Default) PEG Tr ain immediately following xx RESETB de assertio n

0: PEG Wait for BIOS for training

R642 *0_04

MVREF_DQ_DIM0

R643 *0_04

C36 7

0.1u_1 0V _X5R_04

CFG6

CFG5

CFG 4

CFG 2

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - Devic e 1 function 1 enabled ; functio n 2 disab led

01: Reserved - (Dev ice 1 function 1 disabled ; function 2 enabled)

00: x8,x 4,x4 - Device 1 functio ns 1 and 2 ena bled

CFG[6:5]

PEG Static Lane Reversal - CFG2 is for the 16x

1:(Default) Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

CFG2

San dy Bri dge Process or 7/7 ( RESERV ED )

PCIE Port Bifurcati on S traps

CFG4

CFG 7

RESERVED

U49E

PZ 98827-364B-01F

CFG[0]

AK28

CFG[1]

AK29

CFG[2]

AL2 6

CFG[3]

AL2 7

CFG[4]

AK26

CFG[5]

AL2 9

CFG[6]

AL3 0

CFG[7]

AM31

CFG[8]

AM32

CFG[9]

AM30

CFG[10]

AM28

CFG[11]

AM26

CFG[12]

AN28

CFG[13]

AN31

CFG[14]

AN26

CFG[15]

AM27

CFG[16]

AK31

CFG[17]

AN29

RSVD34

AM33

RSVD35

AJ27

RSVD38

J16

RSVD42

AT34

RSVD39

H16

RSVD40

G16

RSVD41

AR35

RSVD43

AT33

RSVD45

AR34

RSVD56

AT2

RSVD57

AT1

RSVD58

AR1

RSVD46

B34

RSVD47

A33

RSVD48

A34

RSVD49

B35

RSVD50

C35

RSVD51

AJ32

RSVD52

AK32

RSVD30

AE7

RSVD31

AK2

RSVD28

L7

RSVD29

AG7

RSVD27

J1 5

RSVD16

C30

RSVD15

D23

RSVD17

A31

RSVD18

B30

RSVD20

D30

RSVD19

B29

RSVD22

A30

RSVD21

B31

RSVD23

C29

RSVD24

J2 0

RSVD37

T8

RSVD6

B4

RSVD7

D1

RSVD8

F25

RSVD9

F24

RSVD11

D24

RSVD12

G25

RSVD13

G24

RSVD14

E23

RSVD32

W8

RSVD33

AT26

RSVD25

B18

RSVD44

AP35

RSVD10

F23

RSVD5

AJ2 6

VAXG_VAL_SENS E

AJ3 1

VSSAXG _VA L_ SEN SE

AH31

VC C_VAL _S ENSE

AJ3 3

VSS_VAL_ SENSE

AH33

KEY

B1

VCC _DIE_SENS E

AH27

VC CIO _SEL

A19

RSVD54

AN35

RSVD55

AM35

R516 *10mil_short H_ SNB_IVB#_PW RC TRL _R

CFG7

CFG Straps for Pro cessor

? DIM M ? ? ? & TR AC E? ?

3.3V2,3,11,12,16,18,19,20,22,23,24,25,27,28,29,30, 33,35,37,38,39

CFG5

Display Port Presence Strap

1:(Default) Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG4

VR EF_CH_ A_DIM M

R159

1K_1% _04

R500 *1K_04

Q9

*AO 3 402 L

G

DS

R491 *1K_04

R153

*1 K _04

Q10

*AO 3 402 L

G

DS

R160

1K_1% _04

R149

*1 K _04

R15 5

1K _ 1 % _0 4

R492 *1K_04

R49 3 *1K_04

R50 3 *1K_04

R15 0

1K _ 1 % _0 4

1. 5 V

1.5V

DR AMR ST_C NTRL 3,19

D RAM RST _ CN TR L 3,19

1.5V3,6,9,10, 25,29,35,37,38

CFG0

C357

0.1u_10V_X5R _04

MVRE F_DQ_DIM MA 9

CFG6

MVREF_D Q_DIMMB 10

VREF_CH_B_DIMM

VR EF_CH_ B_DIM M

Schematic Diagrams

B.Schematic Diagrams

Sheet 8 of 49

Sandy Bridge

Processor 7/7

http://hobi-elektronika.net

Sandy Bridge Processor 7/7 B - 9

Page 9

Schematic Diagrams

SO-DIMM A

M_A _DQ3

M_A _DQ2

M_A _DQ1

M_A _DQ32

M_A _DQ31

M_A _DQ30

M_A _DQ29

M_A _DQ4

M_A _DQ39

M_A _DQ37

M_A _DQ36

M_A _DQ35

M_A _DQ34

M_A _DQ33

M_A _DQ44

M_A _DQ43

M_A _DQ42

M_A _DQ41

M_A _DQ40

M_A _DQ49

M_A _DQ38

M_A _DQ47

M_A _DQ46

M_A _DQ45

M_A _DQ54

M_A _DQ53

M_A _DQ52

M_A _DQ51

M_A _DQ28

M_A _DQ50

M_A _DQ56

M_A _DQ6

M_A _DQ5

M_A _DQ48

M_A _DQ55

M_A _DQ62

M_A _DQ61

M_A _DQ60

M_A _DQ58

M_A _DQ57

M_A _DQ11

M_A _DQ9

M_A _DQ8

M_A _DQ7

M_A _DQ59

M_A _DQ63

M_A _DQ16

M_A _DQ15

M_A _DQ14

M_A _DQ13

M_A _DQ12

M_A _DQ21

M_A _DQ10

M_A _DQ19

M_A _DQ18

M_A _DQ17

M_A _DQ26

M_A _DQ25

M_A _DQ24

M_A _DQ23

M_A _DQ0

M_A _DQ22

M_A _DQ20

M_A _DQ27

MVREF_DQ_DIMMA8

CHANGE TO STANDARD

SA1_DIM0

SA0_DIM1

SA1_DIM1

SA0_DIM0

CLOS E TO S O- DIMM _0

MVREF_DIM0

20mils

si gna l/ spa ce /si gna l:

Layout Note:

8 / 4 / 8

C 325 0.1u_16V_Y 5V_04

C33 8

0.1u_16V_Y5V_04

R 251 10K _04

C375 1u_6.3V_X5R_04

C 374 0.1u_16V_Y 5V_04

JDIMM1B

78121-0011

VD D1

75

VD D2

76

VD D3

81

VD D4

82

VD D5

87

VD D6

88

VD D7

93

VD D8

94

VD D9

99

VD D1 0

100

VD D1 1

105

VD D1 2

106

VD DSPD

199

NC1

77

NC2

122

N CTEST

125

VR EF _ DQ

1

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VS S16

44

VS S17

48

VS S18

49

VS S19

54

VS S20

55

VS S21

60

VS S22

61

VS S23

65

VS S24

66

VS S25

71

VS S26

72

VS S27

127

VS S28

128

VS S29

133

VS S30

134

VS S31

138

VS S32

139

VS S33

144

VS S34

145

VS S35

150

VS S36

151

VS S37

155

VS S38

156

VS S39

161

VS S40

162

VS S41

167

VS S42

168

VS S43

172

VS S44

173

VS S45

178

VS S46

179

VS S47

184

VS S48

185

VS S49

189

VS S50

190

VS S51

195

VS S52

196

G2

GND2

G1

GND1

VTT2

204

VTT1

203

VR EF _ CA

126

RESET#

30

EVEN T#

198

VD D1 3

111

VD D1 4

112

VD D1 6

118

VD D1 5

117

VD D1 7

123

VD D1 8

124

C33 4

10 u _ 10 V _ Y 5 V _ 0 8

C330

0.1u_1 6V_Y 5 V_04

C 354 *10p_50V_N PO_04

C36 4

0.1u_16V_Y5V_04

RN 3

10K_8P4R_04

1

2

3

4 5

6

7

8

C33 9

0.1u_16V_Y 5V_04

C376

1u_6.3V_X5R _04

C328 1u_6.3V_X5R_04

C36 0

0.1u_16V_Y 5V_04

C37 1

0.1u_16V_Y5V_04

C34 0

1u _6.3V_X5R_04

JD I MM 1A

78 1 2 1- 0 0 1 1

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC #

83

A13

119

A14

80

A15

78

DQ 0

5

DQ 1

7

DQ 2

15

DQ 3

17

DQ 4

4

DQ 5

6

DQ 6

16

DQ 7

18

DQ 8

21

DQ 9

23

DQ 1 0

33

DQ 1 1

35

DQ 1 2

22

DQ 1 3

24

DQ 1 4

34

DQ 1 5

36

DQ 1 6

39

DQ 1 7

41

DQ 1 8

51

DQ 1 9

53

DQ 2 0

40

DQ 2 1

42

DQ 2 2

50

DQ 2 3

52

DQ 2 4

57

DQ 2 5

59

DQ 2 6

67

DQ 2 7

69

DQ 2 8

56

DQ 2 9

58

DQ 3 0

68

DQ 3 1

70

DQ 3 2

12 9

DQ 3 3

13 1

DQ 3 4

14 1

DQ 3 5

14 3

DQ 3 6

13 0

DQ 3 7

13 2

DQ 3 8

14 0

DQ 3 9

14 2

DQ 4 0

14 7

DQ 4 1

14 9

DQ 4 2

15 7

DQ 4 3

15 9

DQ 4 4

14 6

DQ 4 5

14 8

DQ 4 6

15 8

DQ 4 7

16 0

DQ 4 8

16 3

DQ 4 9

16 5

DQ 5 0

17 5

DQ 5 1

17 7

DQ 5 2

16 4

DQ 5 3

16 6

DQ 5 4

17 4

DQ 5 5

17 6

DQ 5 6

18 1

DQ 5 7

18 3

DQ 5 8

19 1

DQ 5 9

19 3

DQ 6 0

18 0

DQ 6 1

18 2

DQ 6 2

19 2

DQ 6 3

19 4

BA 0

109

BA 1

108

R AS#

110

WE #

113

C AS#

115

S0#

114

S1#

121

C KE0

73

C KE1

74

CK0

101

CK0#

103

CK1

102

CK1#

104

SD A

200

SC L

202

SA 1

201

SA 0

197

DM0

11

DM1

28

DM2

46

DM3

63

DM4

136

DM5

153

DM6

170

DM7

187

DQS0

12

DQS1

29

DQS2

47

DQS3

64

DQS4

137

DQS5

154

DQS6

171

DQS7

188

DQS0#

10

DQS1#

27

DQS2#

45

DQS3#

62

DQS4#

135

DQS5#

152

DQS6#

169

DQS7#

186

ODT0

116

ODT1

120

BA 2

79

C341

1u_6.3V_X5R _04

C337

0.1u_16V_Y 5V_04

C332

0.1u_16V_Y5V_04

R229 1K_1%_04

R239

1K_1%_04

C359

1u_6. 3V_X5R_04

C370

0.1u_16V_Y5V_04

C33 3

0.1u_16V_Y5V_04

C 348 *10p_50V_N PO_04

C33 6

0.1u_16V_Y 5V_04

C36 6

1u _ 6 . 3V _X 5 R _ 0 4

3.3VS

1. 5 V

3.3VS

1.5V

VTT_MEM

VTT_ M EM

1.5V

MVR E F _ DI M 0

M_A_CLK_DDR14

3.3VS

DDR3_DRAMRST#3,10

M_A_ODT14

M_A_RAS#4

M_A_BS14

M_A_CAS#4

M_A_CLK_DDR#14

SM B_C L K10,19

M_A_ODT04

M_A_BS04

M_ A _ W E #4

M_A_CLK_DDR04

1.5V3,6,8,10,25,29,35,37, 38

VTT_M EM10,38

M_A_CKE14

M_A_BS24

M_A_CKE04

M_A_CS#04

M_A_CLK_DDR#04

M_A_CS#14

M_ A _ DQ [63: 0 ] 4

M_A _DQS[7:0]4

SM B_D AT A10,19

TS#_DIMM 0_110

3.3VS3,10,11,12,18,19,20,21,22,23,24,25,27,28,29,30,31,32,33,34,35, 39

M_ A _ A[1 5 :0 ]4

M _ A_ DQS #[7 :0 ]4

SA0_DIM 1 10

SA1_DIM 1 10

MVREF_DQ_DIMMA

SA0_ DIM 0

SA1_ DIM 0

M_A_ CL K_ DD R1 M_A_CLK_DDR#1

M_A_ CL K_ DD R0 M_A_CLK_DDR#0

M_A _A6

M_A _A5

M_A _A7

M_A _A8

M_A _A9

M_A _A0

M_A _A1

M_A _A2

M_A _A3

M_A _A4

M_A _A12

M_A _A11

M_A _A13

M_A _A14

M_A _A15

M_A _A10

M_A _DQS0

M_A _DQS1

M_A _DQS2

M_A _DQS3

M_A _DQS4

M_A _DQS5

M_A _DQS6

M_A _DQS7

M_A _DQS#0

1.5VS24,35

M_A _DQS#1

C368

1u_6.3V_X5R _04

C32 4

10u_6.3V_X5R _06

C365

1u _6 .3V_X5R_0 4

C33 5

10 u_10V_Y5V_ 08

C33 1

1u_6.3V_X5R _04

M_A _DQS#2

C36 3

1u_6.3V_X5R _04

C361

10u_10V_Y 5V_08

C36 9

1u _ 6 . 3V _ X 5 R _ 0 4

1.5V

+

C39 4

22 0 u _6 . 3 V _ 6 . 3* 6. 3* 4. 2

+

C38 2

*220u_6.3V_6.3*6.3*4.2

M_A _DQS#3

C316

0.1u_10V_X5R _04

M_A _DQS#4

M_A _DQS#5

M_A _DQS#6

M_A _DQS#7

Sheet 9 of 49

DDR3 SO-DIMM_0

B.Schematic Diagrams

B - 10 DDR3 SO-DIMM_0

DDR3 SO-DIMM_0

http://hobi-elektronika.net

Page 10

DDR3 SO-DIMM_1

MVR EF_DIM1

CLO SE TO SO -DIMM 1

MVR E F _ D Q _ D I M MB8

SO -DI MM B

CH ANG E TO STA NDA RD

Layout Note:

M_ B _ D Q 3 1

M_ B _ D Q 4 6

M_ B _ D Q 1 3

M_ B _ D Q 2 4

M_ B _ D Q 5 6

M_ B _ D Q 2 8

M_ B _ D Q 1 1

M_ B _ D Q 2 3

M_ B _ D Q 6 1

M_ B _ D Q 6 2

M_ B _ D Q 5 8

M_ B _ D Q 5 0

M_ B _ D Q 1

M_ B _ D Q 1 6

M_ B _ D Q 6 0

M_ B _ D Q 2

M_ B _ D Q 4 0

M_ B _ D Q 5 4

M_ B _ D Q 4 1

M_ B _ D Q 5 7

M_ B _ D Q 3 7

M_ B _ D Q 2 5

M_ B _ D Q 3 0

M_ B _ D Q 2 7

M_ B _ D Q 4 4

M_ B _ D Q 3

M_ B _ D Q 7

M_ B _ D Q 9

M_ B _ D Q 3 4

M_ B _ D Q 5

M_ B _ D Q 4 7

M_ B _ D Q 4 3

M_ B _ D Q 3 8

M_ B _ D Q 1 7

M_ B _ D Q 4 2

M_ B _ D Q 8

M_ B _ D Q 5 9

M_ B _ D Q 3 5

M_ B _ D Q 3 6

8 / 4 / 8

M_ B _ D Q 4

M_ B _ D Q 2 6

M_ B _ D Q 6 3

M_ B _ D Q 3 3

M_ B _ D Q 4 5

M_ B _ D Q 4 8

M_ B _ D Q 5 5

M_ B _ D Q 2 9

M_ B _ D Q 1 5

M_ B _ D Q 1 0

M_ B _ D Q 5 2

M_ B _ D Q 5 3

M_ B _ D Q 6

M_ B _ D Q 1 9

M_ B _ D Q 1 8

M_ B _ D Q 0

M_ B _ D Q 1 2

M_ B _ D Q 2 0

M_ B _ D Q 3 9

M_ B _ D Q 4 9

M_ B _ D Q 5 1

M_ B _ D Q 2 1

M_ B _ D Q 3 2

M_ B _ D Q 1 4

M_ B _ D Q 2 2

SO -D IMM_1 i s pl ace d far ther f r om t he GM CH tha n S O- DIM M _ 0

MVR E F _ D Q _ D I M MB

M _B_ A4

M _B_ A6

M _B_ A5

M _B_ A1 3

M _B_ A1 2

M _B_ A0

M _B_ A1

M _B_ A2

M _B_ A3

M _B_ A7

M _B_ A8

M _B_ A9

M _B_ A1 0

M _B_ A1 1

M _B_ A1 4

20 m ils

Layout Note :

MVR E F _ D I M1

signal/space/signal:

M _B_ A1 5

M _B_ D QS0

M _B_ D QS6

M _B_ D QS5

M _B_ D QS4

M _B_ D QS3

M _B_ D QS2

M _B_ D QS1

M _B_ D QS# 3

M _B_ D QS# 2

M _B_ D QS# 1

M _B_ D QS# 0

M _B_ D QS7

M _B_ D QS# 7

M _B_ D QS# 6

M _B_ D QS# 5

M _B_ D QS# 4

M _B_C LK_ DD R2 M_B_CLK_DDR#2

M _B_C LK_ DD R3 M_B_CLK_DDR#3

C38 6

1u_6.3V_X5R _04

C400

0. 1u _ 1 6V _Y 5 V _ 04

C40 3

10u_10V_Y5V_08

C41 2

0.1u_16V_Y5V_04

C406

10u_10V_Y 5V_08

C405 *10p_50V_NPO _04

C41 0

0.1u_16V _Y 5V_04

C41 4

0.1u_16V_Y5V_04

C409

0. 1 u _ 1 6V _Y 5 V _0 4

C38 8

1u_6.3V_ X5R _04

C38 1

1u_6.3V_X5R _04

C 416 1u_6.3V_X5R_04

C41 8

1u_6.3V_X5R _04

JDIMM2B

78192-0011

VD D1

75

VD D2

76

VD D3

81

VD D4

82

VD D5

87

VD D6

88

VD D7

93

VD D8

94

VD D9

99

VD D10

100

VD D11

105

VD D12

106

VD DSPD

199

NC 1

77

NC 2

122

NC T EST

125

VR EF_ DQ

1

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VSS16

44

VSS17

48

VSS18

49

VSS19

54

VSS20

55

VSS21

60

VSS22

61

VSS23

65

VSS24

66

VSS25

71

VSS26

72

VSS27

127

VSS28

128

VSS29

133

VSS30

134

VSS31

138

VSS32

139

VSS33

144

VSS34

145

VSS35

150

VSS36

151

VSS37

155

VSS38

156

VSS39

161

VSS40

162

VSS41

167

VSS42

168

VSS43

172

VSS44

173

VSS45

178

VSS46

179

VSS47

184

VSS48

185

VSS49

189

VSS50

190

VSS51

195

VSS52

196

G2

GN D 2

G1

GN D 1

VTT2

204

VTT1

203

VR EF_ CA

126

RE SET #

30

EVEN T#

198

VD D13

111

VD D14

112

VD D16

118

VD D15

117

VD D17

123

VD D18

124

C39 1

1u_6.3V_X5R _04

C390

1u_6.3V_X5R _04

C40 8

1u_6.3V_X5R _04

C38 7

0.1u_16V_Y 5V_04

C380

1u _ 6 . 3 V _ X5 R _0 4

C404

0.1u_16V_Y 5V_04

C 402 0.1u_16V_Y5V_04

C385

1u_6.3V_X5R _04

JDIMM2A

78192-0011

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC#

83

A13

119

A14

80

A15

78

DQ 0

5

DQ 1

7

DQ 2

15

DQ 3

17

DQ 4

4

DQ 5

6

DQ 6

16

DQ 7

18

DQ 8

21

DQ 9

23

DQ 1 0

33

DQ 1 1

35

DQ 1 2

22

DQ 1 3

24

DQ 1 4

34

DQ 1 5

36

DQ 1 6

39

DQ 1 7

41

DQ 1 8

51

DQ 1 9

53

DQ 2 0

40

DQ 2 1

42

DQ 2 2

50

DQ 2 3

52

DQ 2 4

57

DQ 2 5

59

DQ 2 6

67

DQ 2 7

69

DQ 2 8

56

DQ 2 9

58

DQ 3 0

68

DQ 3 1

70

DQ 3 2

12 9

DQ 3 3

13 1

DQ 3 4

14 1

DQ 3 5

14 3

DQ 3 6

13 0

DQ 3 7

13 2

DQ 3 8

14 0

DQ 3 9

14 2

DQ 4 0

14 7

DQ 4 1

14 9

DQ 4 2

15 7

DQ 4 3

15 9

DQ 4 4

14 6

DQ 4 5

14 8

DQ 4 6

15 8

DQ 4 7

16 0

DQ 4 8

16 3

DQ 4 9

16 5

DQ 5 0

17 5

DQ 5 1

17 7

DQ 5 2

16 4

DQ 5 3

16 6

DQ 5 4

17 4

DQ 5 5

17 6

DQ 5 6

18 1

DQ 5 7

18 3

DQ 5 8

19 1

DQ 5 9

19 3

DQ 6 0

18 0

DQ 6 1

18 2

DQ 6 2

19 2

DQ 6 3

19 4

BA0

109

BA1

108

RAS #

110

WE#

113

CAS #

115

S0#

114

S1#

121

CKE 0

73

CKE 1

74

CK0

101

CK0 #

103

CK1

102

CK1 #

104

SDA

200

SCL

202

SA1

201

SA0

197

DM 0

11

DM 1

28

DM 2

46

DM 3

63

DM 4

136

DM 5

153

DM 6

170

DM 7

187

DQ S 0

12

DQ S 1

29

DQ S 2

47

DQ S 3

64

DQ S 4

137

DQ S 5

154

DQ S 6

171

DQ S 7

188

DQ S 0 #

10

DQ S 1 #

27

DQ S 2 #

45

DQ S 3 #

62

DQ S 4 #

135

DQ S 5 #

152

DQ S 6 #

169

DQ S 7 #

186

OD T 0

116

OD T 1

120

BA2

79

C38 9

0.1u_16V_Y 5V_04

C 397 1u_6.3V_X5R_04

C398

10u_10V_Y 5V _08

R274

1K_1%_04

C41 3

0.1u_16V_Y5V_04

C407

0.1u_16V_Y 5V _04

C 415 0.1u_16V_Y5V_04

C38 4

0.1u_10V _X5R_04

R270 1K_1% _04

C401 *10p_50V_NPO _04

C 372

10u_10V_Y 5V _08

C411

0.1u_16V_Y5V_04

C41 7

1u _6 .3V_X5R _04

3. 3 V S

1.5V

1. 5V

1.5V

VTT_ M EM

VTT_ M EM

DDR3_DRAMRST#3, 9

1.5V3,6,8,9,25,29,35,37,38

1.5V

SMB _C L K9,19

SMB _D AT A9,19

VTT_MEM9, 3 8

M_B_A[15:0]4 M_B_D Q[63:0] 4

TS#_DIMM0_19

M _B_RAS#4

M_B _BS14

M_B_ CL K_ DD R34

M_B_WE#4

M _B_CAS#4

M_B_ CL K_ DD R# 34

M_B _BS24

M_ B_ CK E 24

M_B_ CL K_ DD R24

M_B _BS04

M_B_ CL K_ DD R# 24

M_B _CS#34

M_ B_ CK E 34

M_B _ODT24

M_B _ODT34

M_B _CS#24

3.3VS3,9,11,12, 18,19,20,21,22,23,24,25, 27,28,29,30,31,32,33,34,35,39

M_B_DQS#[7:0]4

M _B_ D QS[7:0 ]4

SA1_ D IM19

SA0_ D IM19

1.5VS24 , 3 5

Sheet 10 of 49

DDR3 SO-DIMM_1

Schematic Diagrams

B.Schematic Diagrams

http://hobi-elektronika.net

DDR3 SO-DIMM_1 B - 11

Page 11

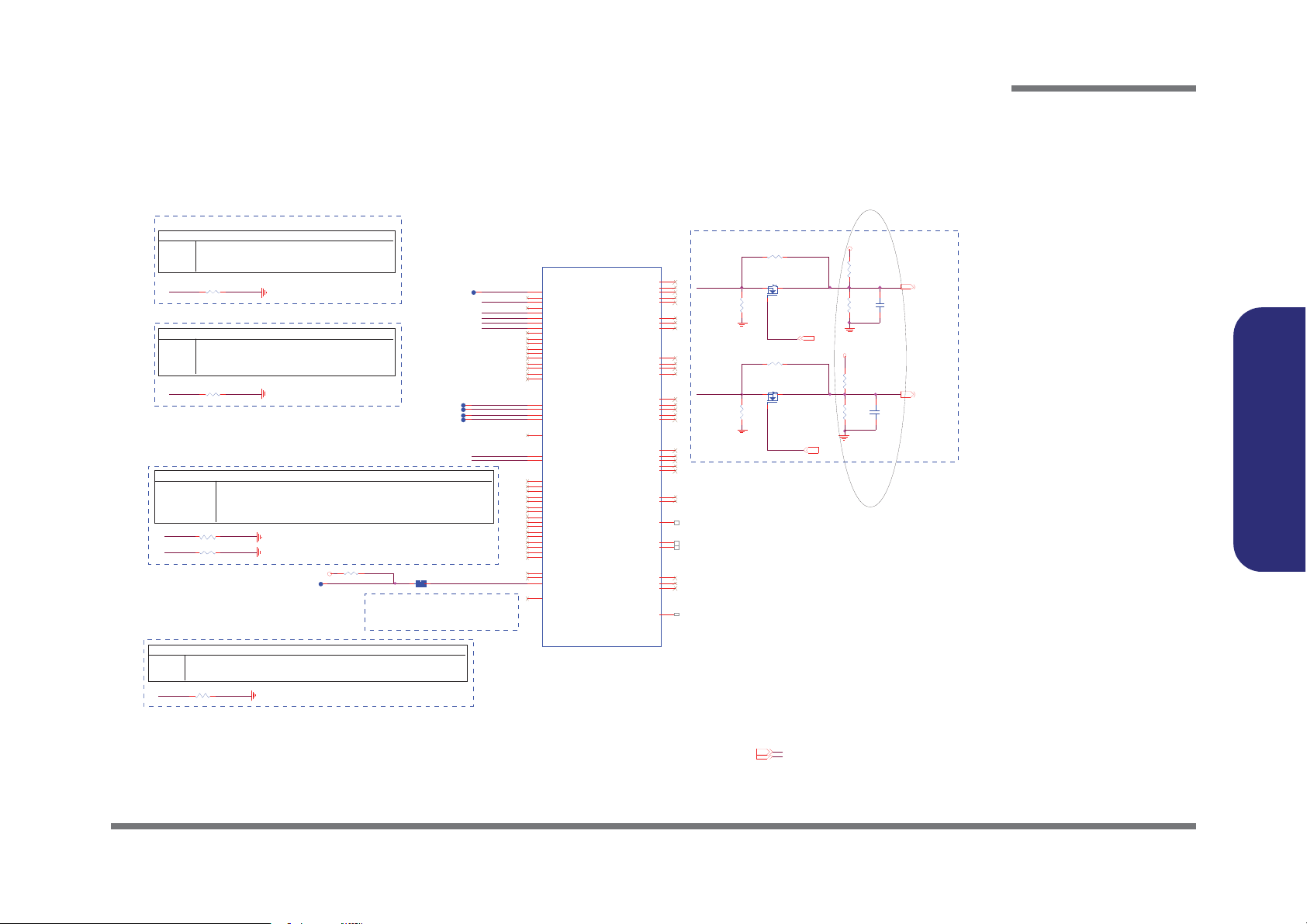

Schematic Diagrams

Sheet 11 of 49

Panel, Inverter,

CRT

H20

C15 8 D1 58

H22

C 158D158

R23 4

*1 0 K _ 04

.

L53 FCM1005MF-600T01

.

L45 FCM1005MF-600T01

.

L56 FCM1005MF-600T01

R228

*200_1%_04

S

D

G

Q49 B

*M TD N7002ZH S6R

5

34

RN 1

2.2K_8P4R_04

123

4 5

678

3. 3 V S 5V S

R27

2.2K_04

3. 3 V S

R28

2.2K _04

R 30 0_04

BLON 1

SB_B LO N1

LV D S - U 0P 2 1

PANEL CONNECTOR (LED+EDP)

LV D S - U 0N 2 1

10/29

PJ2 0

O PEN_2 A

1 2

BKL_EN

R46 0 *10K _04

BLO N

R490 100K_04

U45 B

74 L V C 0 8 P W

4

5

6

147

R486

*1M_04

U45 D

74 L V C 0 8 P W

12

13

11

147

C58 4

0.1u_10V_X5R_04

U45A

74LVC08PW

1

2

3

147

R488 *100K_04

R489 *100K_04

U45C

74LVC08PW

9

10

8

147

3.3V

3.3V

3.3V

3.3V

LVDS-L0P21

LVDS-L0N21

LID_SW#28 , 3 4

ALL_ SYS_ PWR GD20 , 3 4 , 39

BK L_EN34

LV D S - U 2N 2 1

SB_BL ON23

LV DS-L2P 21

LV DS-L2N 21

LV D S - U 2P 2 1

6-20-14X30-015

BLO N21

BLON 2

INV _BLO N

BR IGH TNESS34

1

H26

MTH7_0D2_8

2

3

4

5 6

7

8

9

D24

*B AV99 R ECTIFIER

A

C

AC

Q45

MTN 7 0 0 2Z H S 3

G

DS

D6 *C DBU00 3 40

AC

S

D

G

Q22A

MTD N7002ZHS6R

2

61

S

D

G

Q22 B

MTDN7002Z HS6R

5

34

DAC _G REE N

R N8 0_8P4R _04

1

2

3456

7

8

1

H18

MTH 7_0D2_8

2

3

4

5 6

7

8

9

CM2009-02QR PN:6-02-20090-B60

IP 4772C Z16 PN:6- 02-47 721- B60

C21

*0.1u_16V_Y5V_04

PJ3 3

O PEN_2 A

1 2

.

L43 FCM1005MF -600T01

S

D

G

Q49A

*M TDN7002ZH S6R

2

61

LID_SW #1

P_GND

INV_BLON

M2

M-M A RK

M1 0

M-M A RK

M1 4

M-M A RK

M9

M-M A RKM5M-M A RK

M1 5

M-M A RK

M4

M-M A RK

M3

M-M A RKM8M-M A RK

M7

M-M A RK

R43 2

150_1%_04

M6

M-M A RK

M1

M-M A RK

2A

DAC_BLUE

M1 2

M-M A RK

R434

150_1%_04

M1 3

M-M A RK

R433

150_1%_04

M1 6

M-M A RK

M1 1

M-M A RK

DAC_RED21

D AC_ GR EEN21

DAC_BLUE21

LVDS-U1N21

LVDS-U1P21

LV D S - L 1 N21

LVDS-UC LKN21

LVDS-UCLKP21

1

H24

MTH 7 _ 0D 2 _8

2

3

4

5 6

7

8

9

LV D S - L C L K P21

LVDS -LC LKN21

LVDS-L1P21

BY P

LVDS- LC LK N_CO MBO

LVDS- U1P_COMBO

LVDS- U1N_COMBO

LVDS- UCLKN _C OMBO

LVDS - UCL K P_ C OMBO

LVDS- L1P_COMBO

LVDS- L1N_COMBO

LVDS- LC LK P_C OM BO

LVDS -UCLKP_C OMBO

LVDS -L1P_COMBO

LVDS -L1N_COMBO

LVDS -LC LK P_C OMBO

LVDS -LC LK N_CO MBO

LVDS -U1P_COM BO

LVDS -U1N_COMBO

LVDS -UCLKN _COM BO

>1 0 0 mi l

>1 0 0 mi l

>100mil

C800

4.7u_25V_X5R_08

>100 mil

C48 8

10u_10V_Y5V_08

C24 8

0 . 1u _ 1 6V _Y 5 V _ 0 4

R19 7

*100K_04

PLVD D5V S

PLVDD

LVDS:3.3V 2A

eDP 3D:5V 3A

3.3VS

C12 8

0.1u_16V_Y5V_04

R86 100K_04

R223

10K_04

Q30

AO 3415

G

DS

C144 1u_6.3V_X5R_04

R654

100K_04

GN DGNDGNDGN D

GND

1

H27

MTH7_0D2_8

2

3

4

5 6

7

8

9

1

H12

MTH 7 _ 0D 2 _8

2

3

4

5 6

7

8

9

3.3V

Q46

P2003EVG

4

62

5731

8

C17

0.1u_50V_Y5V_06

.

L1

*0_06

3A

LEDPL_VINVIN

C15

* 0. 1u _50V_Y5 V_0 6

NB_EN AVDD

VIN

R578

1M_04

.

L42 FCM1005MF -600T01

1

H28

MTH 7_0D2_8

2

3

4

5 6

7

8

9

.

L2

H CB1608KF-121T25

C19

0.1u_16V_Y 5V_04

C16

0 . 1u _ 1 6V _Y 5V _0 4

N B_EN AVD D21,34

J_LC D1

87216-4006

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

Gnd 1G1Gnd 2

G2

R N10 0_8P4R _04

1

2

3456

7

8

PLVDD

PLVD D

3.3VS

J_ C R T 1

108AH15FS T04A1CC

8

7

6

5

4

3

2

1

9

10

11

12

13

14

15

GND2

GN D 1

FG RN

24 mil

DD CL K

FBLUE

HSY NC

LEDP L_VIN

FR ED

C3

1000p_50V_X7R_04C5220p_50V_NPO _04

C4

220p_50V_NPO _04

C1

10 0 0 p_ 5 0 V _ X 7R _ 04

CRT

C559

10p_50V_N PO_04

C56 2

10p_50V_N PO_04

P_DDC _CLK 21

P_DDC _ DATA 21

C56 1

10p_50V_N PO_04

DD CD ATA

VSY NC

C2

0.22u_10V_Y5V_0 4

C557

0.22u_10V_Y 5V_04

R 1 33_04

DDCLK

H SYN C

DDC DAT A

VSYN C_ C

HSY NC _C

C6

0.22u_10V_Y5V_04

R13 33_04

DAC _ DDC ADAT A21

DAC_HSYNC21

DAC _VSYN C21

3.3VS

FG RN

DAC _ DDC ACL K21

FR ED

FBLUE

U40

IP4772CZ16

VCC _SY NC

1

VCC _VID EO

2

VIDEO_1

3

VIDEO_2

4

VIDEO_3

5

GN D

6

VCC _DDC

7

BYP

8

DD C_ OU T 1

9

DDC _ IN1

10

DDC _ IN211DD C_ OU T 2

12

SYN C_IN113SYN C_ OU T1

14

SYN C_IN215SYN C_ OU T2

16

5VS

VSYN C

DP_T XP_22

D P_AUX_N2

DP_TXN_02

DP_A UX_ P2

DP_TXN_22

C558

22p_50V_N PO_04

C560

22p_50V_NPO_04

DP_T XP_02

DP_T XP_12

DP_TXN_12

C 214 *0.1u_10V _X7R_04

C563

22p_50V_N PO_04

LVDS- LC LK N_CO MBO

C661

10 p _ 50 V _ N P O _ 04

C 178 *0.1u_10V _X7R_04

C 196 *0.1u_10V _X7R_04

LVDS - UCL K P_ C OMBO

LVDS- U1P_COMBO

C698

10 p _ 50 V _ N P O _ 04

C69 7

10 p _ 50 V _ N P O_ 04

C 167 *0.1u_10V _X7R_04

LVDS- LC LK P_C OM BO

C 186 *0.1u_10V _X7R_04

C 182 *0.1u_10V _X7R_04

LVDS- L1P_COMBO

LVDS- U1N_COMBO

C 197 *0.1u_10V _X7R_04

LVDS- UCLKN _C OMBO

C 179 *0.1u_10V _X7R_04 LVDS- L1N_C OMBO

3.3V2,3,8,12,16,18,19, 20,22,23,24,25,27,28,29,30,33,35,37,38,39

5V S18 ,2 4,25 ,2 7,28,3 1,32,3 3,35 ,3 9, 40,41

VIN35,36,3 7,38,39,40,41,42

3.3VS3,9,10,12,18,19,20,21,22,23,24,25, 27,28,29,30,31,32,33,34,35,39

GNDGN DGND

1

H17

MTH7_0D2_8

2

3

4

5 6

7

8

9

1

H6

MTH 7 _ 0D 2 _8

2

3

4

5 6

7

8

9

PANEL POWER

1108

BR IGH TNESS_ R

.

L41 FCM1005MF -600T01

GN DGND

1

H14

MTH7_0D2_8

2

3

4

5 6

7

8

9

R4 1_04

R226

200_1%_04

DAC_RED

GNDGNDGN D

1

H7

MTH 7_0D2_8

2

3

4

5 6

7

8

9

3.3V

GND

1

H3

MTH7_0D2_8

2

3

4

5 6

7

8

9

H5

MTH 7_0D2_8_O

H19

H6_ 0 D3 _ 7

H21

C146D110

H23

C158D158

H2

C15 8 D1 5 8

H4

C14 6 D1 1 0

H25

C 146D110

H1

C15 8 D1 58

Panel, Inverter, CRT

B.Schematic Diagrams

B - 12 Panel, Inverter, CRT

http://hobi-elektronika.net

Page 12

Schematic Diagrams

PL AC E NEAR BGA

PEX _VD D_ SVD D

FS X8L_25M Hz? ? ? ? ?

P EX_C LKR EQ #

N12P- GS

D 02 CHA NGE

P EX_ RX6#

P EX_ RX2#P EX_ RX2#

P EX_ RX3#

P EX_ RX0#

P EX_ RX5#

P EX_ RX1#

P EX_ RX4#

16mil

P L AC E N EAR BAL LS

1u->0.1u C990525

M_STRAP_REF1

16mil

PERSTB#

PS1 _GND_SENSE

PS1 _VD D_ SEN SE

P L AC E NEAR BGA

P EX_ RX4

PE G_RX2

PE G_RX#0

PE G_RX#5

PE G_RX3

P EX_ RX6

PE G_RX#2

P EX_ RX7

P EX_ RX3

PE G_RX0

P EX_ RX7#

PE G_RX4

PE G_RX1 P EX_ RX1

PE G_RX#3