Clevo W110ER, W110ERF Schematics

Schematic Diagrams

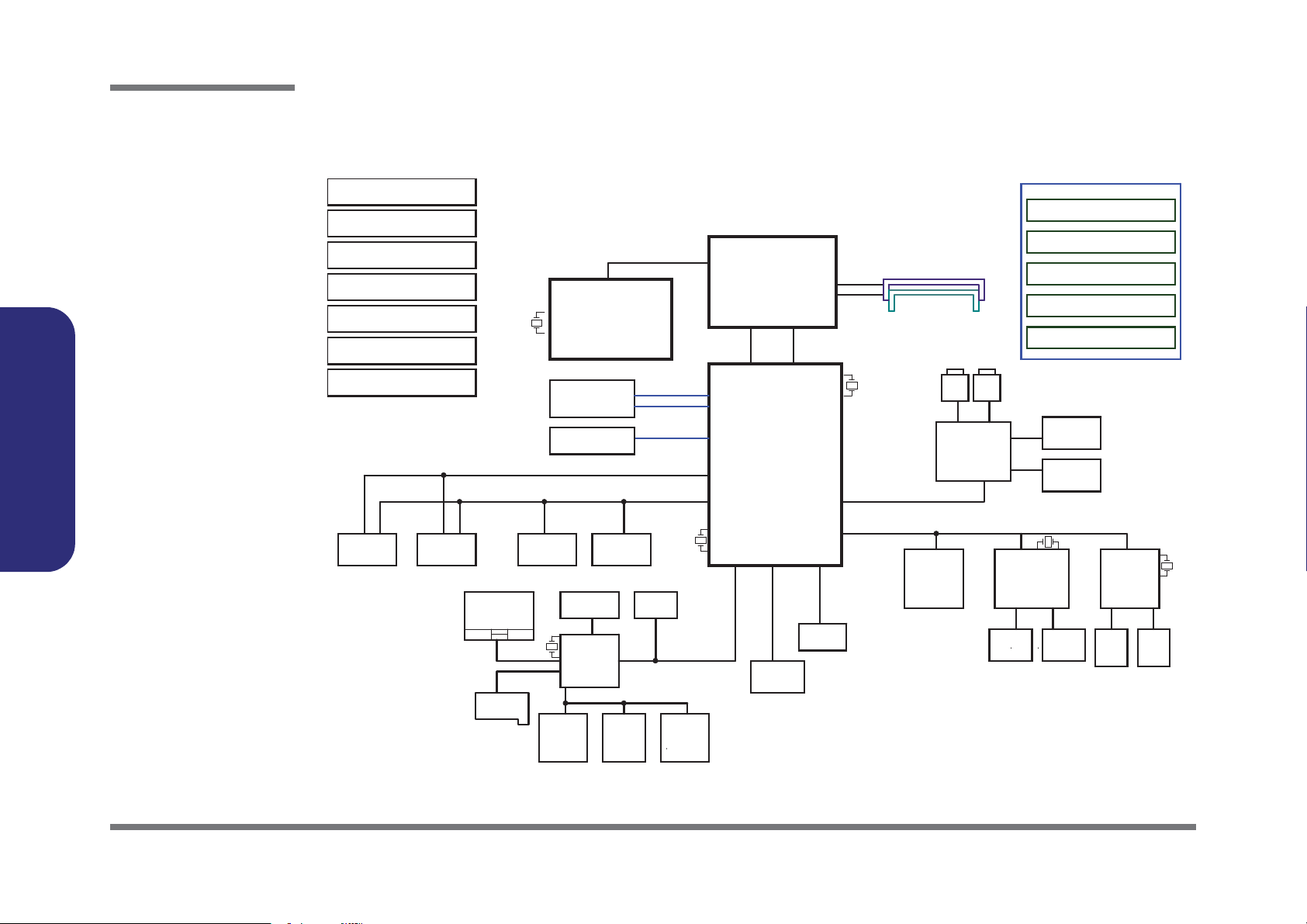

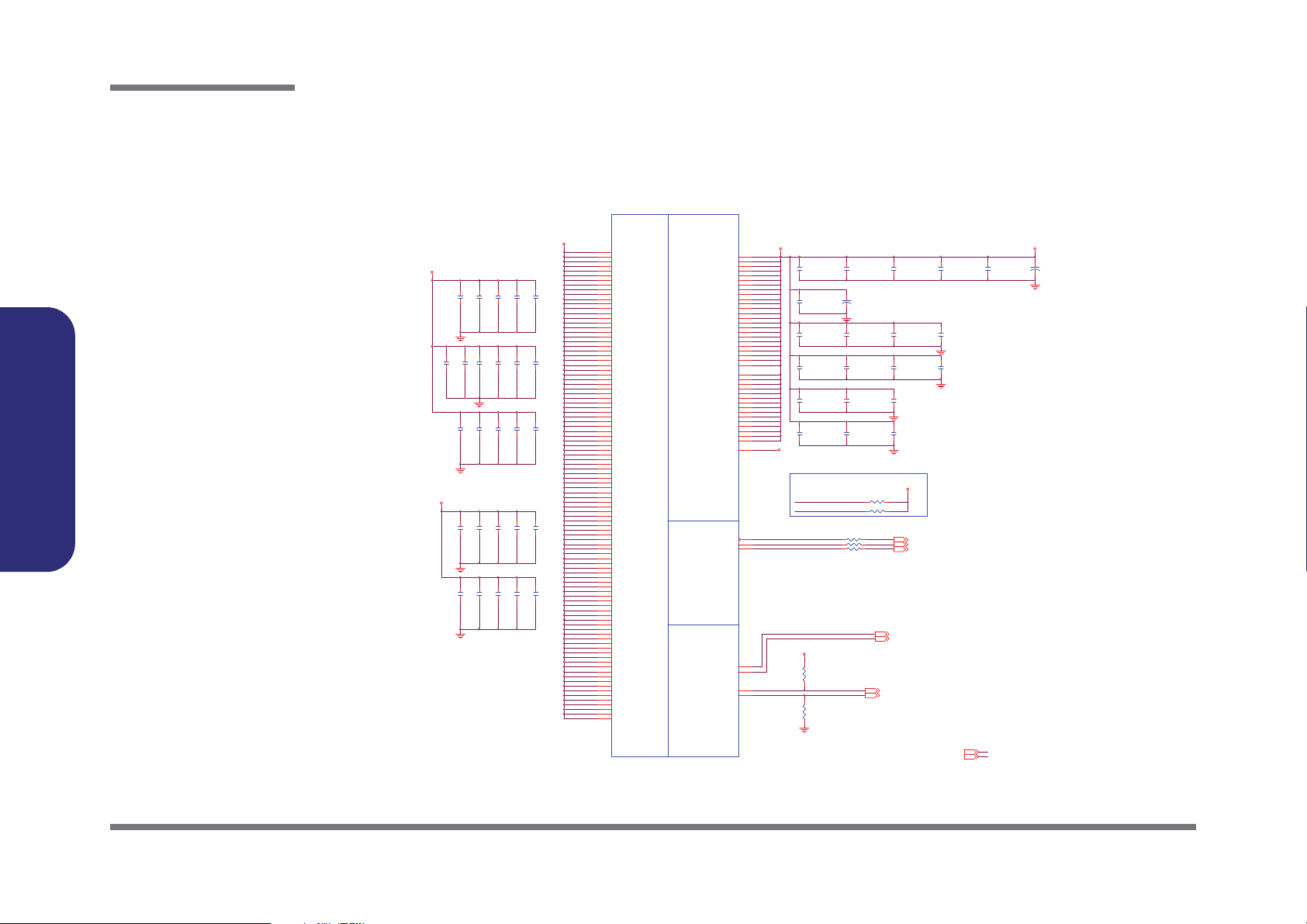

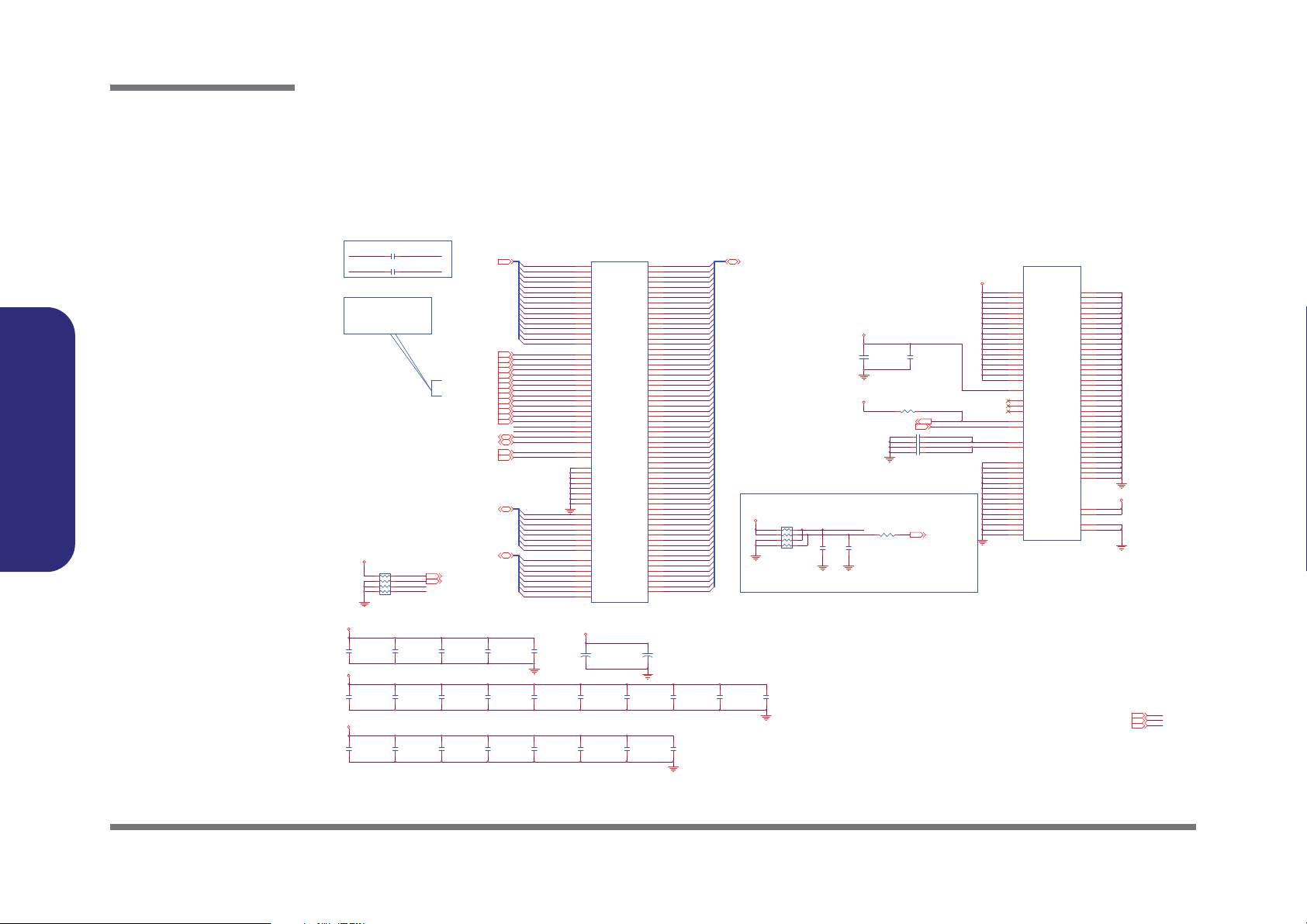

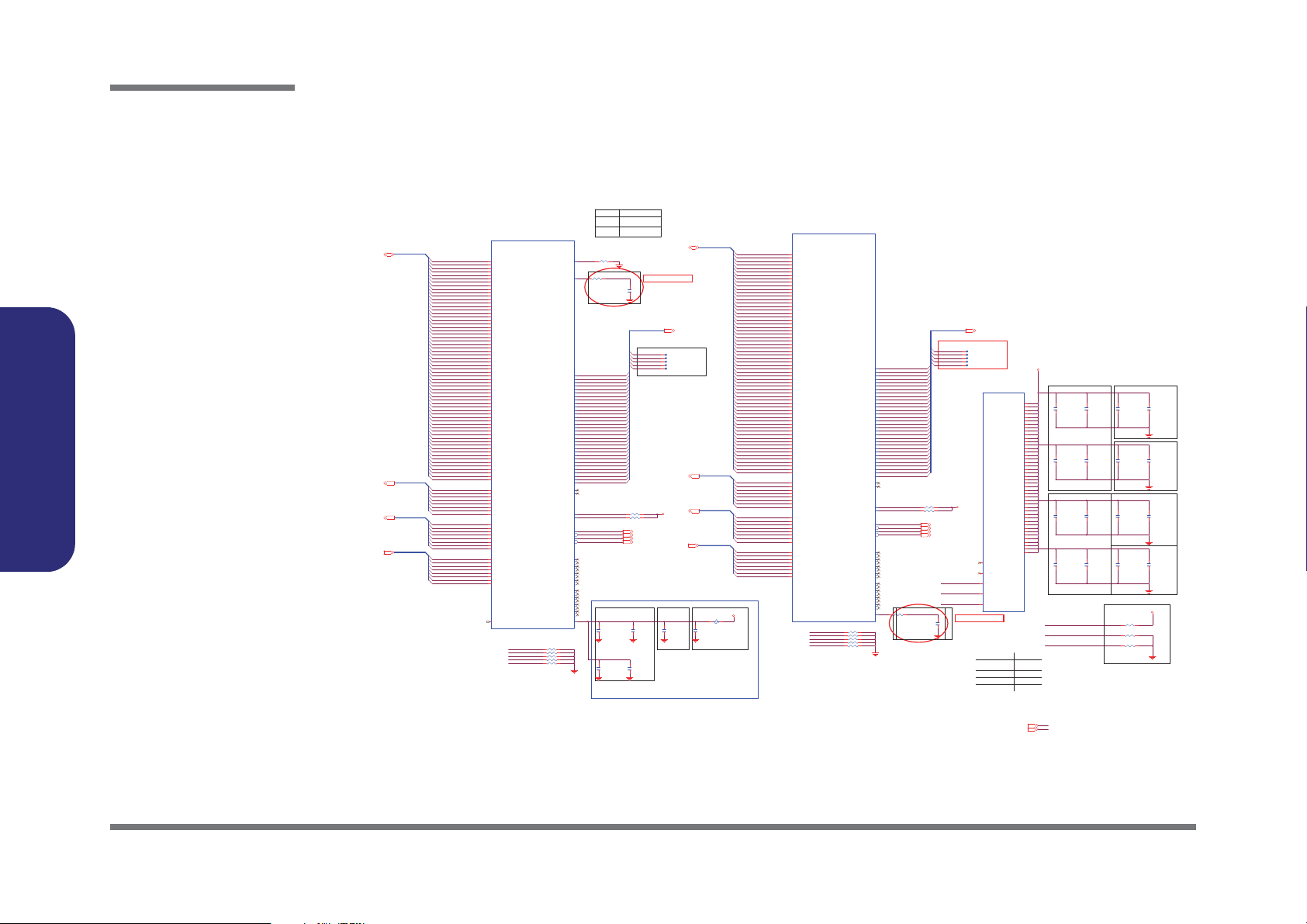

W110ER Chi e f Ri ver System Block Diagram

GPU NVDIDA NVVDD

25x25mm

989 Ball FCBGA

SATA

SPI

32.768KHz

1.05VS_VTT,1.05VS

+1.5S_CPU

Panther Point

Controller

Hub (PCH)

5V,3V,5VS,3VS,1.5VS,

1.5V,0.75VS(VTT_MEM)

USB 2.0

VDD3,VDD5

480 Mbps

CCD

(USB9) (USB5)

USB PORT2

FBVDDQ,1.8VS,PEX_VDD,0.85V S

6-7P-W1105-001

6-71-W1100-D02A

W110ER MAIN BOARD

W110ER

4 Bits Debug Card

6-71-W110D-D01

5IN1

CLICK BOARD

6-71-W1102-D02

6-71-W110S-D02A

W110ER POWER SW B'd

FDI*4

Ivy Bridge

DMI*4

PCIE*8

PROCESSOR

rPGA989/988

908 Balls

Nvidia

Fermi N13P

RAM SIZE:1~2GB

(128Mx16)

DDRIII

DDRIII

1067/1333/1600 MHz

DDR3 / 1.5V

SO-DIMM2

SHEET 9

SO-DIMM1

HDMI Connector

CRT CONNECTOR

LCD CONNECTOR

24 MHz

INT MIC

HP

OUT

Azalia Codec

AZALIA LINK

MIC

IN

VIA

VT1802P

INT SPKER

PCIE

CARD READER

GIGA LAN

25 MHz

100 MHz

RTL 8411

(USB3)

Mini PCIE

SOCKET

WLAN + BT

LPC

EC / BIOS

SPI ROM

128pins LQFP

EC SMBUS

EC

INT. K/B

ITE 8518E

32.768 KHz

G711ST9U

THERMAL

SENSOR

14*14*1.6mm

SMART

FAN

SMART

BATTERY

AC-IN

SATA I/II 3.0Gb/s

33 MHz

TOUCH PAD

SENTELIC

CLICK BOARD

6-49-C4802-010

SATA HDD

USB PORT3USB PORT1

(USB1)(USB0)

5 Gbps

USB 3.0

25 MHz

HDD B'rd

6-71-W110J-D01

RJ-45

7IN1

SOCKET

27 MHz

24 MHz

2M (ME)

SPI ROM

VCORE, VGFX_CORE

USB3.0

TUSB 7320

USB

PORT3

USB

PORT1

(USB1)(USB0)

Optional

TPM 1.2

http://hobi-elektronika.net

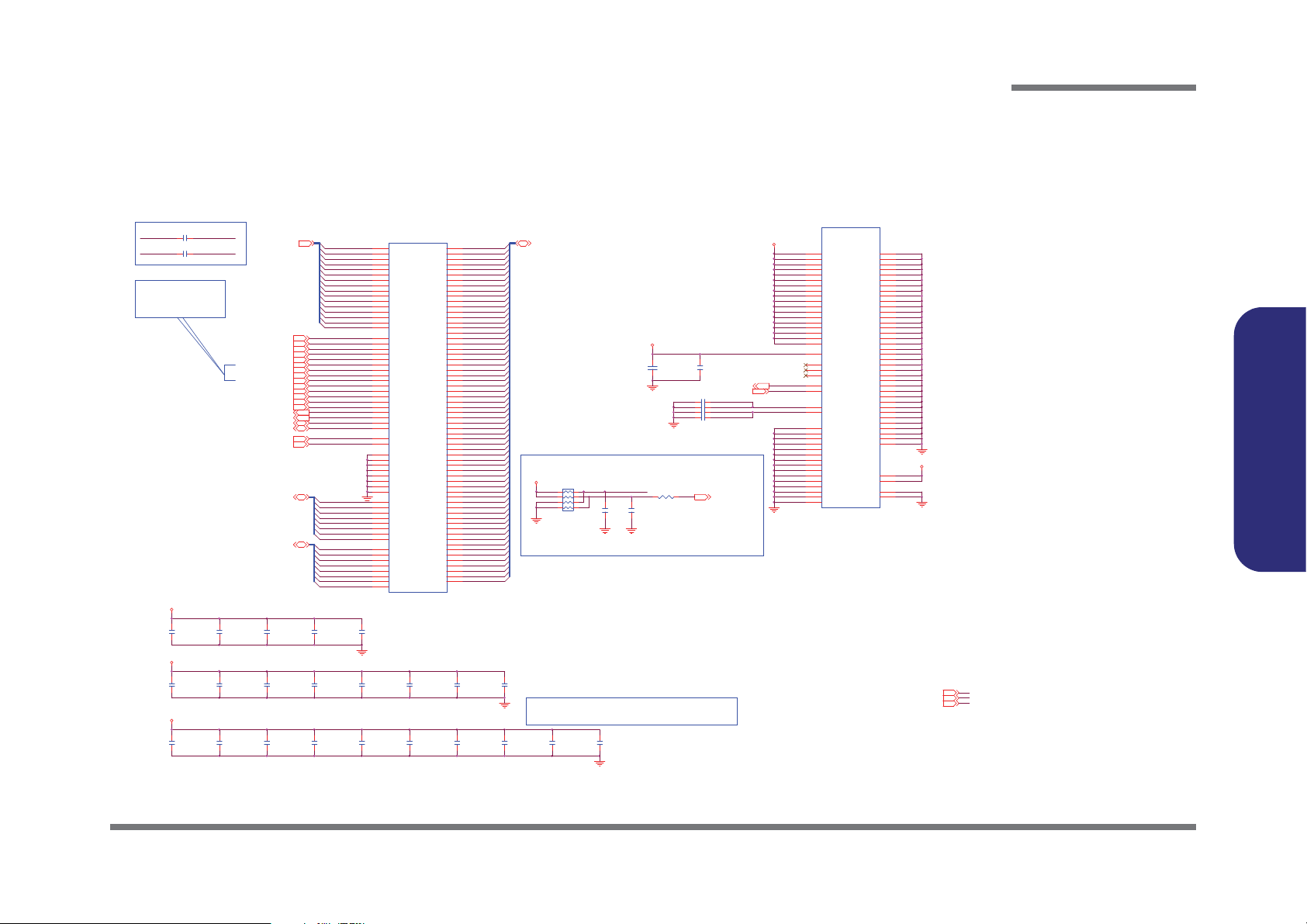

System Block Diagram

B.Schematic Diagrams

B - 2 System Block Diagram

Sheet 1 of 48

System Block

Diagram

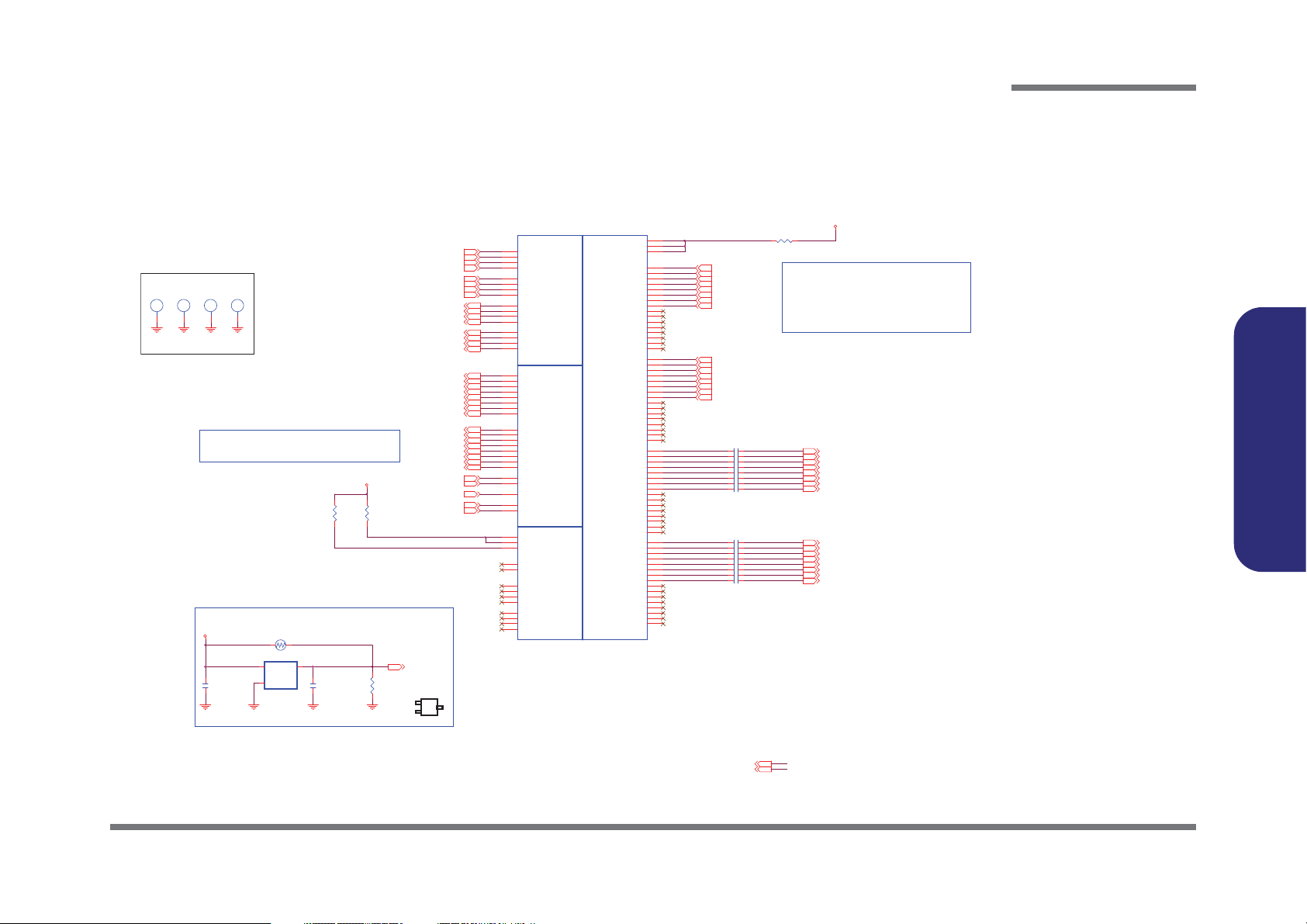

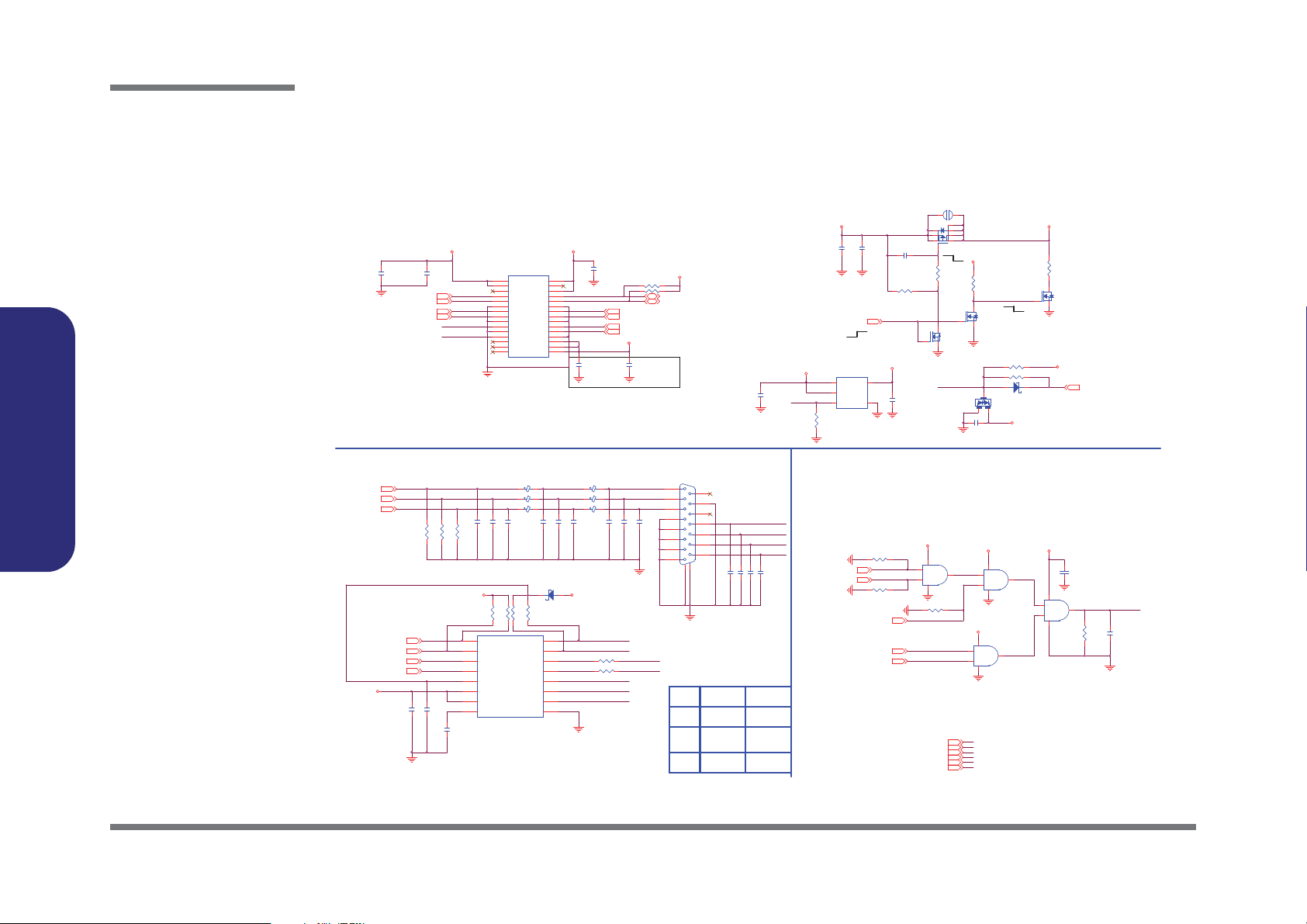

Processor 1/7 - DMI, FDI, PEG

Sheet 2 of 48

Processor 1/7 -

DMI, FDI, PEG

H18

H5_0D4_4

W/O CPU THERMA L IC® É, PCB·Å«× ¶q´ú¥Î

SC70-3

CPU

THERM_VOLT 34

6-17-10300-730

EDP_COMPIO

PCI EXPRESS* - GRAPHICS

DMI

Intel(R) FDI

eDP

U31A

Ivy Bridge_rPGA_2DPC_Rev 0p61

DMI_RX#[0]

B27

DMI_RX#[1]

B25

DMI_RX#[2]

A25

DMI_RX#[3]

B24

DMI_RX[0]

B28

DMI_RX[1]

B26

DMI_RX[2]

A24

DMI_RX[3]

B23

DMI_TX#[0]

G21

DMI_TX#[1]

E22

DMI_TX#[2]

F21

DMI_TX#[3]

D21

DMI_TX[0]

G22

DMI_TX[1]

D22

DMI_TX[3]

C21

DMI_TX[2]

F20

FDI0_TX#[0]

A21

FDI0_TX#[1]

H19

FDI0_TX#[2]

E19

FDI0_TX#[3]

F18

FDI1_TX#[0]

B21

FDI1_TX#[1]

C20

FDI1_TX#[2]

D18

FDI1_TX#[3]

E17

FDI0_TX[0]

A22

FDI0_TX[1]

G19

FDI0_TX[2]

E20

FDI0_TX[3]

G18

FDI1_TX[0]

B20

FDI1_TX[1]

C19

FDI1_TX[2]

D19

FDI1_TX[3]

F17

FDI0_FSYNC

J18

FDI1_FSYNC

J17

FDI_INT

H20

FDI0_LSYNC

J19

FDI1_LSYNC

H17

PEG_ICOMPI

J22

PEG_IC OMPO

J21

PEG_RCOMPO

H22

PEG_RX#[0]

K33

PEG_RX#[1]

M35

PEG_RX#[2]

L34

PEG_RX#[3]

J35

PEG_RX#[4]

J32

PEG_RX#[5]

H34

PEG_RX#[6]

H31

PEG_RX#[7]

G33

PEG_RX#[8]

G30

PEG_RX#[9]

F35

PEG_RX#[10]

E34

PEG_RX#[11]

E32

PEG_RX#[12]

D33

PEG_RX#[13]

D31

PEG_RX#[14]

B33

PEG_RX#[15]

C32

PEG_RX[0]

J33

PEG_RX[1]

L35

PEG_RX[2]

K34

PEG_RX[3]

H35

PEG_RX[4]

H32

PEG_RX[5]

G34

PEG_RX[6]

G31

PEG_RX[7]

F33

PEG_RX[8]

F30

PEG_RX[9]

E35

PEG_RX[10]

E33

PEG_RX[11]

F32

PEG_RX[12]

D34

PEG_RX[13]

E31

PEG_RX[14]

C33

PEG_RX[15]

B32

PEG_TX#[0]

M29

PEG_TX#[1]

M32

PEG_TX#[2]

M31

PEG_TX#[3]

L32

PEG_TX#[4]

L29

PEG_TX#[5]

K31

PEG_TX#[6]

K28

PEG_TX#[7]

J30

PEG_TX#[8]

J28

PEG_TX#[9]

H29

PEG_TX#[10]

G27

PEG_TX#[11]

E29

PEG_TX#[12]

F27

PEG_TX#[13]

D28

PEG_TX#[14]

F26

PEG_TX#[15]

E25

PEG_TX[0]

M28

PEG_TX[1]

M33

PEG_TX[2]

M30

PEG_TX[3]

L31

PEG_TX[4]

L28

PEG_TX[5]

K30

PEG_TX[6]

K27

PEG_TX[7]

J29

PEG_TX[8]

J27

PEG_TX[9]

H28

PEG_TX[10]

G28

PEG_TX[11]

E28

PEG_TX[12]

F28

PEG_TX[13]

D27

PEG_TX[14]

E26

PEG_TX[15]

D25

eDP_AUX

C15

eDP_AUX#

D15

eDP_TX[0]

C17

eDP_TX[1]

F16

eDP_TX[2]

C16

eDP_TX[3]

G15

eDP_TX#[0]

C18

eDP_TX#[1]

E16

eDP_TX#[2]

D16

eDP_TX#[3]

F15

eDP_COMPIO

A18

eDP_HPD

B16

eDP_ICOMPO

A17

C444 0.22u_10V_X5R_04

C454 0.22u_10V_X5R_04

C456 0.22u_10V_X5R_04

C449 0.22u_10V_X5R_04

C448 0.22u_10V_X5R_04

C458 0.22u_10V_X5R_04

C451 0.22u_10V_X5R_04

C443 0.22u_10V_X5R_04

C442 0.22u_10V_X5R_04

C452 0.22u_10V_X5R_04

C447 0.22u_10V_X5R_04

M 6-86-27988-003

C445 0.22u_10V_X5R_04

C446 0.22u_10V_X5R_04

C453 0.22u_10V_X5R_04

H17

H5_0D4_4

DMI_TXP220

DMI_TXP120

DMI_TXP020

1.05VS_VTT

1.05V S_VTT

3.3V

C455 0.22u_10V_X5R_04

DMI_TXN220

DMI_TXN120

DMI_TXN020

DMI_TXP320

FDI_FSYNC120

FDI_FSYNC020

DMI_TXN320

H12

H5_0D4_4

FDI_LSYNC120

FDI_LSYNC020

FDI_INT20

C565

*0.1u_10V_X7R_04

C450 0.22u_10V_X5R_04

H11

H5_0D4_4

C284

*0.1u_10V_X7R_04

Q20

*G711ST9U

OUT1VCC

2

GND

3

R373

24.9_1%_04

R120 24.9_1%_04

PEG_TX#2 12

PEG_TX#3 12

3.3V6,11,16,18,19,20,22,23,24,25,27,28,29,30,35,37,38,39,40,42

PEG_TX#1 12

PEG_TX#0 12

PEG_TX#7 12

PEG_TX#5 12

PEG_TX6 12

PEG_TX#4 12

PEG_TX#6 12

PEG_TX4 12

PEG_TX0 12

PEG_TX3 12

PEG_TX5 12

PEG_TX1 12

PEG_TX7 12

1.05VS_VTT3,5,23,24,25,37,39,40

PEG_TX2 12

CAD NOTE: PEG_ICOMPI and RCOMPO signals

should be shorted and routed with

- max length = 500 mils

- typical impedance = 43 mohms

PEG_ICOMPO signals should be routed with

- max length = 500 mils

- typical impedance = 14.5 mohms

PTH1

10K_1%_NTC_06

1 2

R705

10K_1%_04

R374

1K_04

CAD NOTE: DP_COMPIO and ICOMPO signals

should be shorted near balls and routed with

- typical impedance < 25 mohms

PEG_TX#_6

PEG_TX#_2

PEG_TX#_5

PEG_TX#_7

PEG_TX#_3

PEG_TX#_0

PEG_TX#_1

PEG_TX#_4

DP Compensation Signal

DMI_RXN220

DMI_RXN120

DMI_RXN020

DMI_RXP120

DMI_RXP020

DMI_RXN320

FDI_TXN120

FDI_TXN020

DMI_RXP320

DMI_RXP220

FDI_TXN420

FDI_TXN320

FDI_TXN220

PEG_IRCOMP_R

FDI_TXN720

FDI_TXN620

FDI_TXN520

FDI_TXP220

FDI_TXP120

FDI_TXP020

FDI_TXP520

FDI_TXP420

FDI_TXP320

FDI_TXP720

FDI_TXP620

20 mil

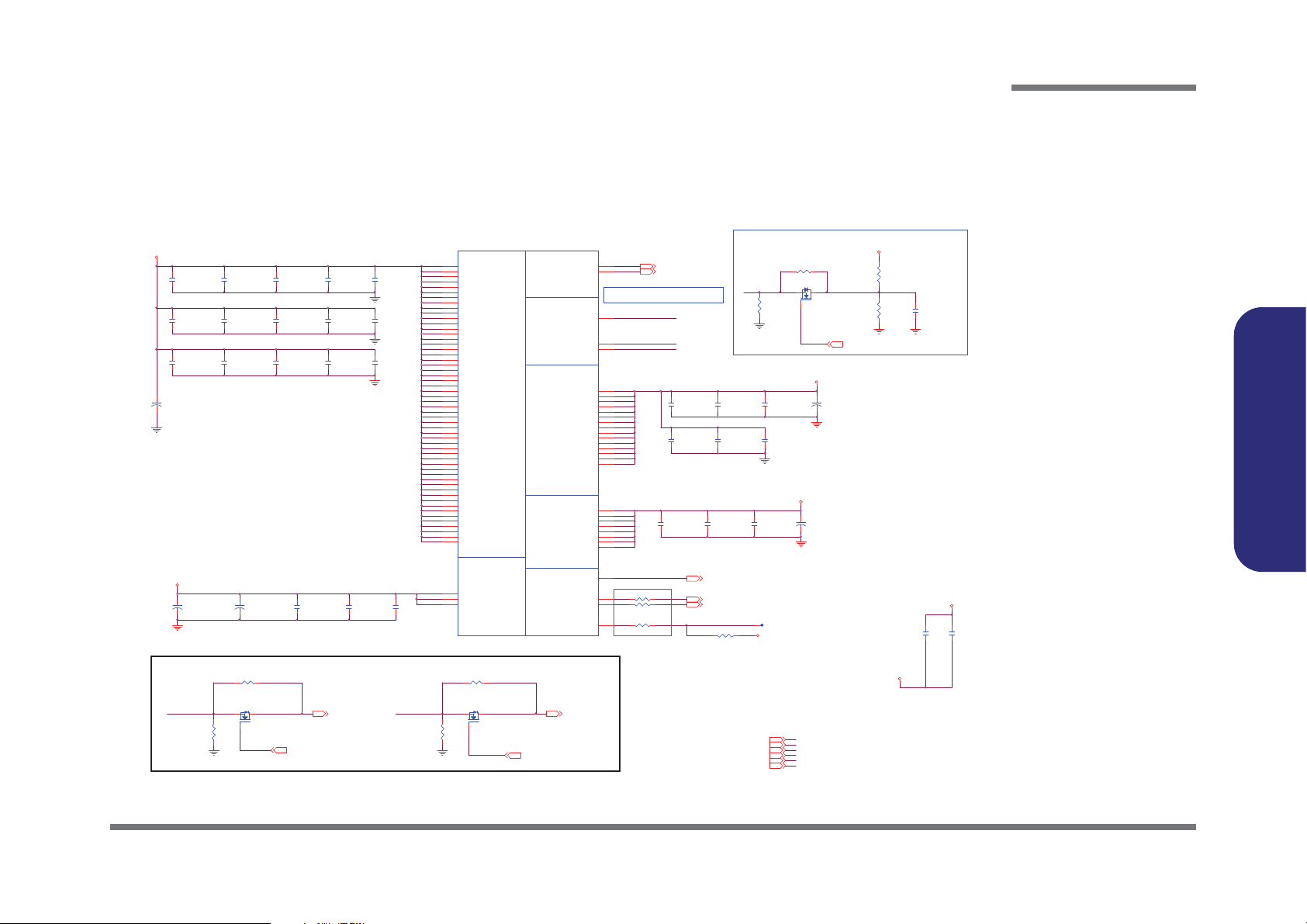

Ivy Bridge Processor 1/7 ( DMI,PEG,FDI )

3

2

1

1:2 (4mils:8mils)

PLACE NEAR U31

PEG_RX#4 12

PEG_RX#2 12

PEG_RX#3 12

PEG_RX#7 12

PEG_RX#1 12

PEG_RX#5 12

PEG_RX#6 12

PEG_RX#0 12

PEG_RX4 12

PEG_RX5 12

PEG_RX7 12

PEG_RX0 12

PEG_RX3 12

PEG_RX2 12

PEG_RX1 12

PEG_RX6 12

PEG_TX_0

PEG_TX_6

PEG_TX_4

PEG_TX_2

PEG_TX_1

PEG_TX_5

PEG_TX_3

PEG_TX_7

PEG Compensation Signal

http://hobi-elektronika.net

Schematic Diagrams

B.Schematic Diagrams

Processor 1/7 - DMI, FDI, PEG B - 3

Schematic Diagrams

Sheet 3 of 48

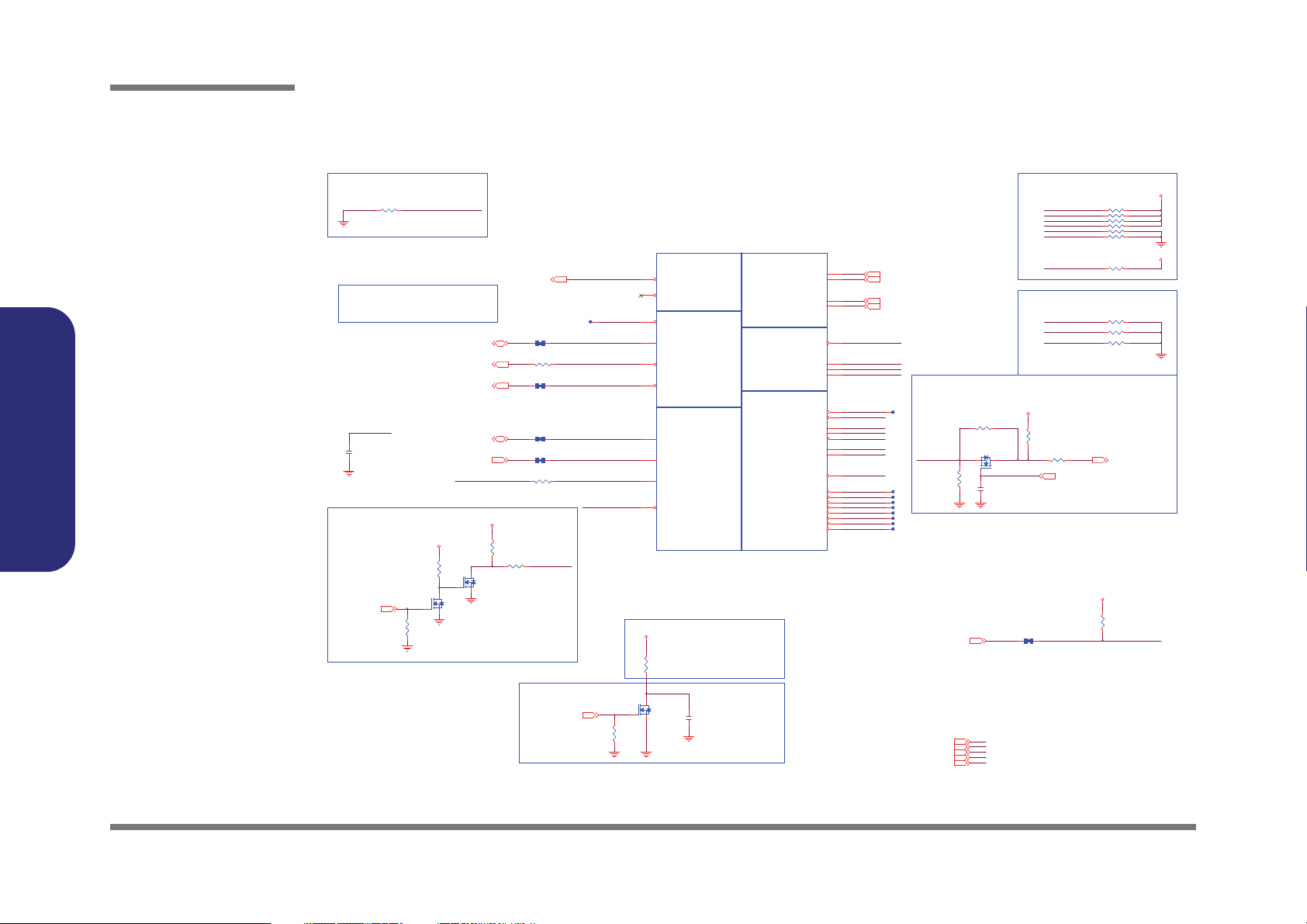

Processor 2/7 -

CLK, MISC

H_PROCHOT#

H_CPUPWRGD_R

PM_DRAM_PW RGD20

1.5V6,9,10,35,37,38

H_PECI34

H_PM_SYNC20

CAD Note: Capacitor

need to be placed

close to buffer

output pin

TRACE WIDTH 10MIL, LENG TH <500MILS

H_CPUPWRGD_R

Processor Pu ll downs

PU/PD for JT AG signals

CLOCKS

MISCTHERMALPWR MANAGEMENT

DDR3

MISC

JTAG & BPM

U31B

Iv y Bridge_rPGA_ 2D PC _R ev 0p61

SM_RCOMP[1]

A5

SM_RCOMP[2]

A4

SM_DRAMRST#

R8

SM_RCOMP[0]

AK1

BCLK#

A27

BCLK

A28

DPLL_REF_CLK#

A15

DPLL_REF _CLK

A16

CATERR#

AL33

PECI

AN33

PROCHOT#

AL32

THERMTRI P#

AN32

SM_DRAMPWROK

V8

RESET#

AR33

PRDY #

AP29

PREQ#

AP27

TCK

AR26

TMS

AR27

TRST#

AP30

TDI

AR28

TDO

AP26

DBR#

AL35

BPM#[0]

AT28

BPM#[1]

AR29

BPM#[2]

AR30

BPM#[3]

AT30

BPM#[4]

AP32

BPM#[5]

AR31

BPM#[6]

AT31

BPM#[7]

AR32

PM_SYNC

AM34

SKTOCC#

AN34

PROC_ SELECT#

C26

UNCOREPWRGOOD

AP33

1.05VS_VTT2,5,23, 24,25,37, 39,40

CLK_BCLK 19

1.5VS_CPU6,35

3.3V2,6,11, 16,18,19, 20,22, 23,24,25, 27,28,29 ,30,35, 37,38,39 ,40,42

CLK_DP 19

CLK_DP# 19

CLK_BCLK# 19

DRAMRST_CNTRL 6,19

3.3VS9,10,11, 12,18, 19,20,21, 22,23,24, 25,27, 28,30,31, 32,33, 34,35,40

H_CPUPWRGD23

H_PROCHOT#_EC34

XDP_DBR_R

H_PROCHOT#40,42

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

XDP _T RS T#

XDP _T CL K

VDDPWRGOOD_R

H_PROCHOT#_R

XDP _T MS

CPU_DRAMRST#

XDP_PREQ#

XDP _T DI _ R

XDP _T DO _R

R341 *10mil_s hort_04

R199 *0_04

C151

47p_50V_NPO_04

R198

1K_04

R87

62_04

R339 1K_04

R342 *10mil_s hort_04

R98 *10mil_short _04

R34310K_04

Q5

MTN7002ZHS3

G

DS

TRACE WIDTH 10MIL, LE NGTH <500MILS

Processor P ull up

H_CPUPWRGD

R99 56_1%_04

C601

*0.1u_16 V_Y5V_04

R363 51_04

R138 200_1%_04

R340 *10mil_s hort_04

R354 51_04

R173 130_1%_04

C433

0.047u_10V_X7R_04

R168

200_1%_04

R362 51_04

R384 140_1%_04

R200 1K_04

Q13

MTN7002ZHS3

G

DS

R361 51_04

R137 25.5_1%_04

R355 *51_04

H_PM_SYNC_R

R449

4.99K_1%_04

R174 *10mil_s hort_04

R348 51_04

R79

100K_04

If PROCHOT# is not used,

then it must be terminated

with a 56-£[ +-5% pull-up

resistor to 1.05VS_VTT .

DDR3 Compensation Signa ls

BUF_CPU_RST#

SM_RCOMP_1

SM_RCOMP_0

SM_RCOMP_2

DDR3_DRAMRST# 9,10

H_SNB_IV B#23

H_TH RMTR IP #23

XDP _B PM 0_ R

XDP _B PM 1_ R

XDP _B PM 2_ R

XDP _B PM 4_ R

XDP _B PM 3_ R

XDP _B PM 5_ R

XDP _B PM 6_ R

XDP _B PM 7_ R

XDP _P R DY #

On CRB

H_SNB_IVB#_PWRCTRL = low, 1.0V

H_SNB_IVB#_PWRCTRL = high/NC, 1.05V

PMSYS_P WRGD _BUF

H_THRMTRIP#_R

S3 circuit:- DRAM PWR GOOD logic

Ivy Bridge Processor 2/7 ( CLK,MISC,JTAG )

1.5VS_CPU

1.5V

1.05VS_VTT

3.3VS

1.05VS_VTT

BUF_CPU_RST#

R356

75_04

R336

100K_04

S

D

G

Q18B

L2N7002DW 1T1G

5

34

H_PECI_R

S

D

G

Q18A

L2N7002DW 1T1G

2

61

R357

43_1%_04

CPU_DRAMRST#

R337

10K_04

1.05VS_VTT

3.3VS

Buffered reset to CPU

PLT_ RST#12,22,28

S3 circuit:- DRA M_RST# to memory

should be high durin g S3

XDP_DBR_R

H_CATERR#

XDP_TRST#

H_SNB_IVB#

XDP _T DO _R

XDP _T CL K

XDP _T DI _ R

XDP _T MS

XDP_PREQ#

PMSYS_PW RGD _BUF

http://hobi-elektronika.net

Processor 2/7 - CLK, MISC

B.Schematic Diagrams

B - 4 Processor 2/7 - CLK, MISC

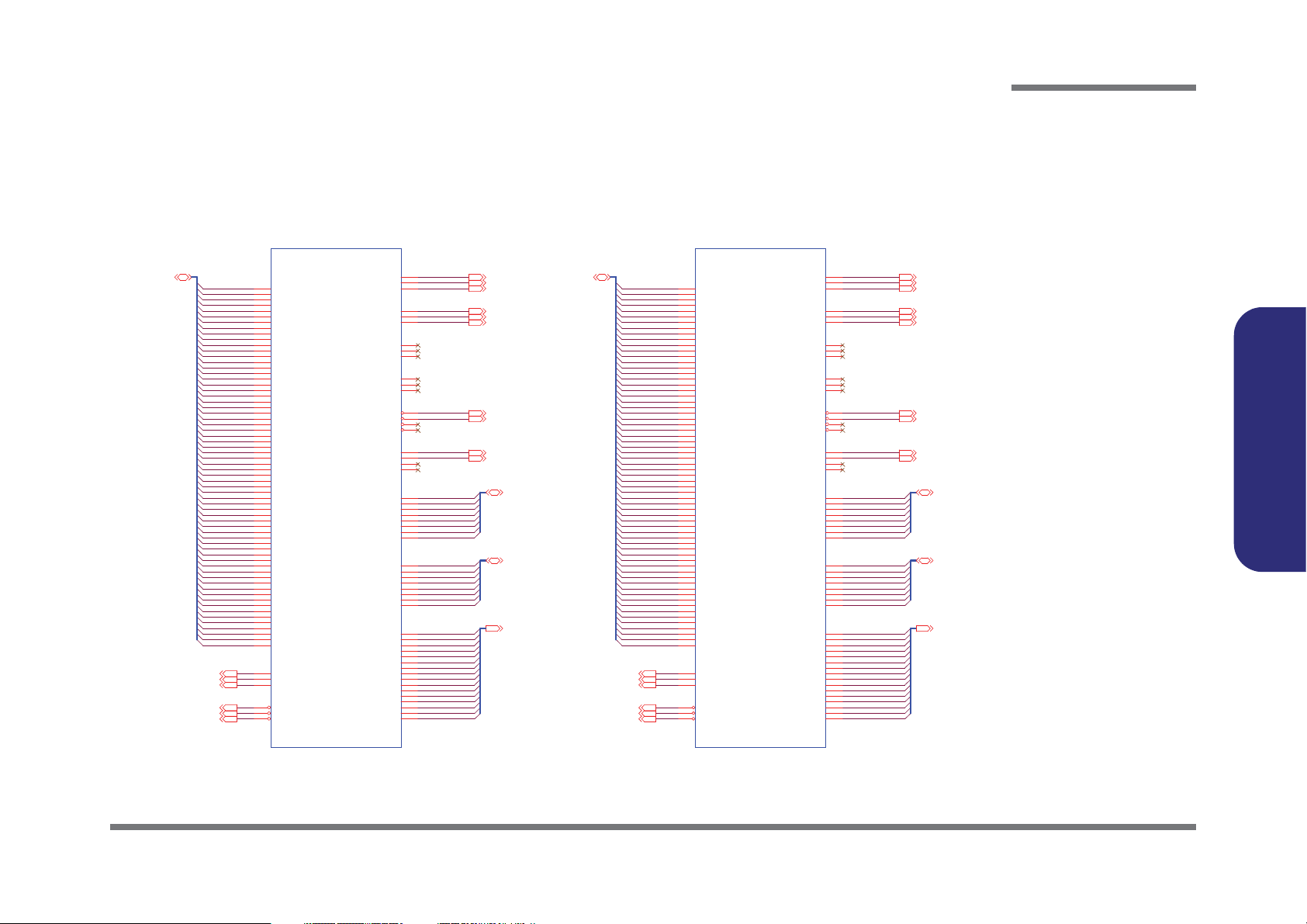

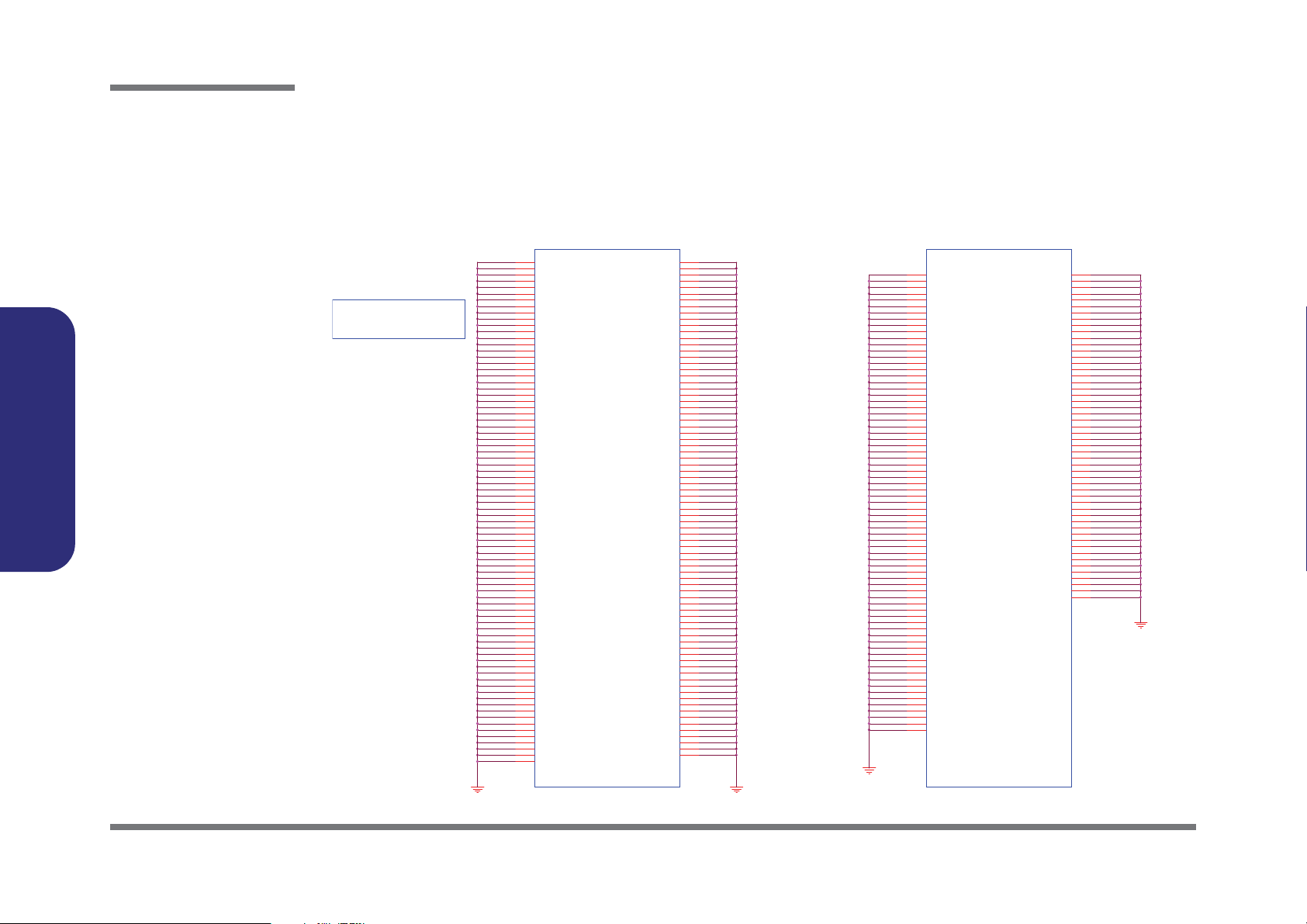

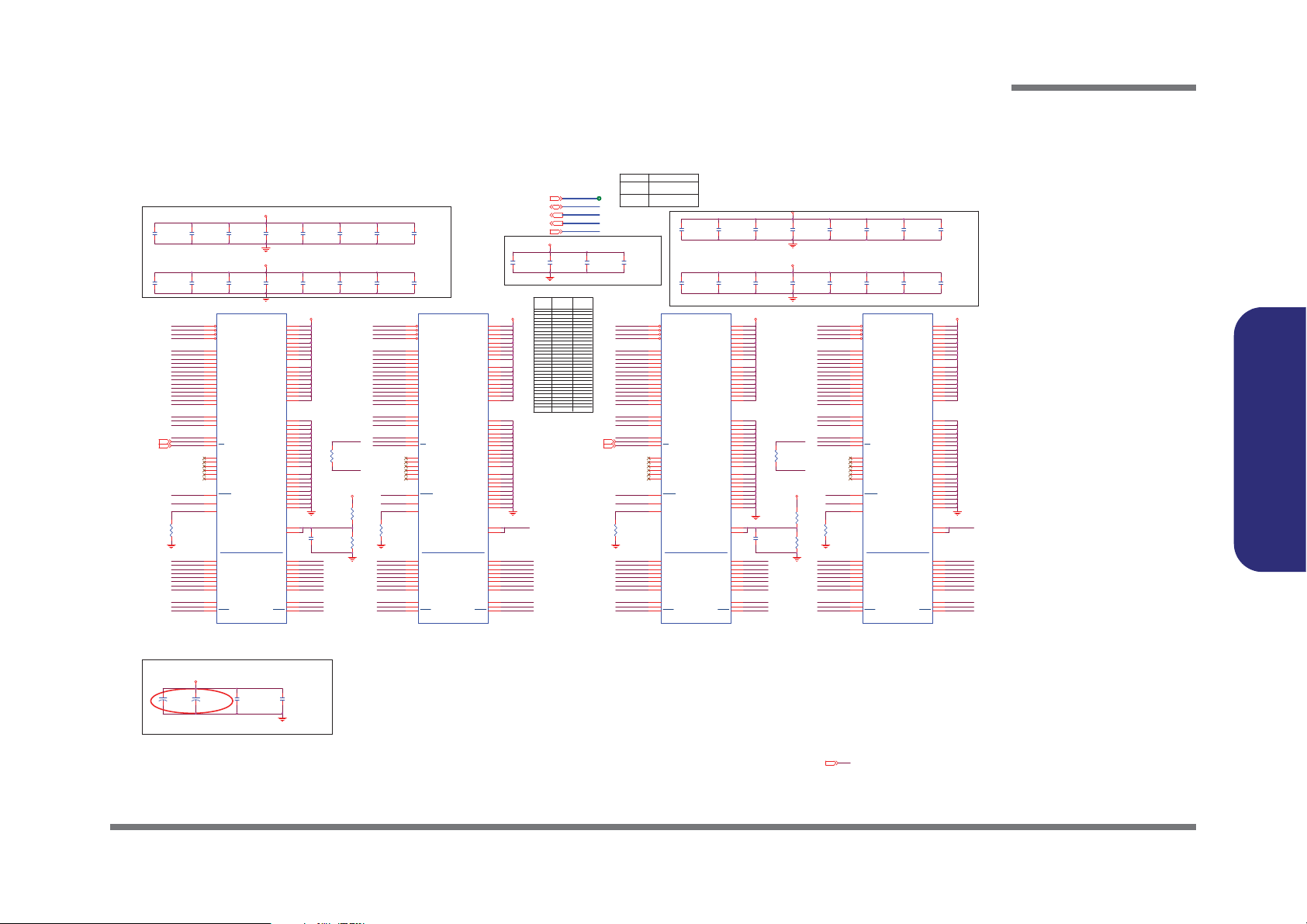

Processor 3/7 - DDR3

M_A_ DQ S#5

M_A_ DQ S#6

M_A_ DQ S#7

M_A_ DQ S#0

M_A_ DQ S#2

M_A_ DQ S#1

M_A_ DQ S#3

M_A_ DQ S#4

M_A_ DQ S4

M_A_ DQ S5

M_A_ DQ S6

M_A_ DQ S7

M_A_ DQ S0

M_A_ DQ S2

M_A_ DQ S1

M_A_ DQ S3

M_B_D QS #5

M_B_D QS #4

M_B_D QS #6

M_B_D QS #7

M_B_D QS #0

M_B_D QS #1

M_B_D QS #2

M_B_D QS #3

M_B_A 6

M_B_A 5

M_B_A 0

M_B_A 1

M_B_A 2

M_B_A 3

M_B_A 4

M_B_A 9

M_B_A 10

M_B_A 11

M_B_A 13

M_B_A 12

M_B_A 14

M_B_A 15

M_B_A 7

M_B_A 8

M_B_D QS 6

M_B_D QS 5

M_B_D QS 2

M_B_D QS 3

M_B_D QS 4

M_B_D QS 7

M_B_D QS 0

M_B_D QS 1

DDR SYSTEM MEMORY A

U31C

Iv y Bridge_rPGA_2DPC_Rev 0p61

SA_BS[0]

AE10

SA_BS[1]

AF10

SA_BS[2]

V6

SA_CAS#

AE8

SA_RAS#

AD9

SA_WE#

AF9

SA_CK[0]

AB6

SA_CK[1]

AA5

SA_CLK#[0]

AA6

SA_CLK#[1]

AB5

SA_CKE[0]

V9

SA_CKE[1]

V10

SA_CS#[0]

AK3

SA_CS#[1]

AL3

SA_ODT[0]

AH3

SA_ODT[1]

AG3

SA_DQS[0]

D4

SA_DQS#[0]

C4

SA_DQS[1]

F6

SA_DQS#[1]

G6

SA_DQS[2]

K3

SA_DQS#[2]

J3

SA_DQS[3]

N6

SA_DQS#[3]

M6

SA_DQS[4]

AL5

SA_DQS#[4]

AL6

SA_DQS[5]

AM9

SA_DQS#[5]

AM8

SA_DQS[6]

AR11

SA_DQS#[6]

AR12

SA_DQS[7]

AM14

SA_DQS#[7]

AM15

SA_MA[0]

AD10

SA_MA[1]

W1

SA_MA[2]

W2

SA_MA[3]

W7

SA_MA[4]

V3

SA_MA[5]

V2

SA_MA[6]

W3

SA_MA[7]

W6

SA_MA[8]

V1

SA_MA[9]

W5

SA_MA[10]

AD8

SA_MA[11]

V4

SA_MA[12]

W4

SA_MA[13]

AF8

SA_MA[14]

V5

SA_MA[15]

V7

SA_DQ[0]

C5

SA_DQ[1]

D5

SA_DQ[2]

D3

SA_DQ[3]

D2

SA_DQ[4]

D6

SA_DQ[5]

C6

SA_DQ[6]

C2

SA_DQ[7]

C3

SA_DQ[8]

F10

SA_DQ[9]

F8

SA_DQ[10]

G10

SA_DQ[11]

G9

SA_DQ[12]

F9

SA_DQ[13]

F7

SA_DQ[14]

G8

SA_DQ[15]

G7

SA_DQ[16]

K4

SA_DQ[17]

K5

SA_DQ[18]

K1

SA_DQ[19]

J1

SA_DQ[20]

J5

SA_DQ[21]

J4

SA_DQ[22]

J2

SA_DQ[23]

K2

SA_DQ[24]

M8

SA_DQ[25]

N10

SA_DQ[26]

N8

SA_DQ[27]

N7

SA_DQ[28]

M10

SA_DQ[29]

M9

SA_DQ[30]

N9

SA_DQ[31]

M7

SA_DQ[32]

AG6

SA_DQ[33]

AG5

SA_DQ[34]

AK6

SA_DQ[35]

AK5

SA_DQ[36]

AH5

SA_DQ[37]

AH6

SA_DQ[38]

AJ5

SA_DQ[39]

AJ6

SA_DQ[40]

AJ8

SA_DQ[41]

AK8

SA_DQ[42]

AJ9

SA_DQ[43]

AK9

SA_DQ[44]

AH8

SA_DQ[45]

AH9

SA_DQ[46]

AL9

SA_DQ[47]

AL8

SA_DQ[48]

AP11

SA_DQ[49]

AN11

SA_DQ[50]

AL12

SA_DQ[51]

AM12

SA_DQ[52]

AM11

SA_DQ[53]

AL11

SA_DQ[54]

AP12

SA_DQ[55]

AN12

SA_DQ[56]

AJ14

SA_DQ[57]

AH14

SA_DQ[58]

AL15

SA_DQ[59]

AK15

SA_DQ[60]

AL14

SA_DQ[61]

AK14

SA_DQ[62]

AJ15

SA_DQ[63]

AH15

SA_CK[2]

AB4

SA_CLK#[2]

AA4

SA_CK[3]

AB3

SA_CLK#[3]

AA3

SA_CKE[2]

W9

SA_CKE[3]

W10

SA_CS#[2]

AG1

SA_CS#[3]

AH1

SA_ODT[2]

AG2

SA_ODT[3]

AH2

M_B_BS210

M_B_BS110

M_B_BS010

M_A_CLK_D DR #1 9

M_A_CLK_D DR 1 9

M_A_CKE1 9

M_A_CS#1 9

M_A_CS#0 9

M_A_A[ 15:0] 9

M_A_CLK_D DR #0 9

M_A_CLK_D DR 0 9

M_A_CKE0 9

M_A_BS19

M_A_ODT0 9

M_A_ODT1 9

M_A_ WE #9

M_A_RAS#9

M_A_CAS#9

M_A_BS29

M_B_RAS#10

M_B_A[ 15:0] 10

M_A_BS09

M_B_CKE3 1 0

M_B_CAS#10

M_B_WE#10

M_B_CKE2 1 0

M_B_CLK_DDR#3 10

M_B_CLK_DDR3 10

M_B_ODT3 10

M_B_CLK_DDR#2 10

M_B_CLK_DDR2 10

M_B_CS#3 10

M_B_CS#2 10

M_B_ODT2 10

M_B_DQ[ 63:0]10M_A_ DQ [6 3:0 ]9

M_B_DQS[7:0] 10

M_B_DQS#[7:0] 10

M_A_DQS[ 7:0] 9

M_A_DQS#[7:0] 9

M_A_DQ 32

M_A_DQ 31

M_A_DQ 30

M_A_DQ 29

M_A_DQ 4

M_A_DQ 3

M_A_DQ 2

M_A_DQ 1

M_A_DQ 49

M_A_DQ 38

M_A_DQ 47

M_A_DQ 46

M_A_DQ 45

M_A_DQ 44

M_A_DQ 43

M_A_DQ 42

M_A_DQ 41

M_A_DQ 40

M_A_DQ 39

M_A_DQ 37

M_A_DQ 36

M_A_DQ 35

M_A_DQ 34

M_A_DQ 33

M_A_DQ 62

M_A_DQ 61

M_A_DQ 60

M_A_DQ 58

M_A_DQ 57

M_A_DQ 56

M_A_DQ 6

M_A_DQ 5

M_A_DQ 48

M_A_DQ 55

M_A_DQ 54

M_A_DQ 53

M_A_DQ 52

M_A_DQ 51

M_A_DQ 28

M_A_DQ 50

M_A_DQ 16

M_A_DQ 15

M_A_DQ 14

M_A_DQ 13

M_A_DQ 12

M_A_DQ 11

M_A_DQ 9

M_A_DQ 8

M_A_DQ 7

M_A_DQ 59

M_A_DQ 63

M_B_ DQ 48

M_B_ DQ 47

M_A_DQ 20

M_A_DQ 27

M_A_DQ 26

M_A_DQ 25

M_A_DQ 24

M_A_DQ 23

M_A_DQ 0

M_A_DQ 22

M_A_DQ 21

M_A_DQ 10

M_A_DQ 19

M_A_DQ 18

M_A_DQ 17

M_B_ DQ 62

M_B_ DQ 61

M_B_ DQ 60

M_B_ DQ 59

M_B_ DQ 58

M_B_ DQ 57

M_B_ DQ 56

M_B_ DQ 55

M_B_ DQ 54

M_B_ DQ 53

M_B_ DQ 52

M_B_ DQ 51

M_B_ DQ 50

M_B_ DQ 49

M_B_ DQ 9

M_B_ DQ 8

M_B_ DQ 7

M_B_ DQ 6

M_B_ DQ 5

M_B_ DQ 4

M_B_ DQ 3

M_B_ DQ 2

M_B_ DQ 1

M_B_ DQ 12

M_B_ DQ 11

M_B_ DQ 63

M_B_ DQ 20

M_B_ DQ 19

M_B_ DQ 18

M_B_ DQ 17

M_B_ DQ 16

M_B_ DQ 15

M_B_ DQ 14

M_B_ DQ 13

M_B_ DQ 0

M_B_ DQ 10

M_B_ DQ 36

M_B_ DQ 35

M_B_ DQ 34

M_B_ DQ 33

M_B_ DQ 32

M_B_ DQ 31

M_B_ DQ 30

M_B_ DQ 29

M_B_ DQ 28

M_B_ DQ 27

M_B_ DQ 26

M_B_ DQ 25

M_B_ DQ 24

M_B_ DQ 23

M_B_ DQ 22

M_B_ DQ 21

M_B_ DQ 46

M_B_ DQ 45

M_B_ DQ 44

M_B_ DQ 43

M_B_ DQ 42

M_B_ DQ 41

M_B_ DQ 40

M_B_ DQ 39

M_B_ DQ 38

M_B_ DQ 37

Ivy Bridge Processor 3/7 ( DDR3 )

DDR SYSTEM MEMORY B

U31D

Iv y Bridge_rPGA_2D PC _ Rev 0p61

SB_BS[0]

AA9

SB_BS[1]

AA7

SB_BS[2]

R6

SB_CAS#

AA10

SB_RAS#

AB8

SB_WE#

AB9

SB_CK[0]

AE2

SB_CK[1]

AE1

SB_CLK#[0]

AD2

SB_CLK#[1]

AD1

SB_CKE[0]

R9

SB_CKE[1]

R10

SB_ODT[0]

AE4

SB_ODT[1]

AD4

SB_DQS[4]

AN6

SB_DQS#[4]

AN5

SB_DQS[5]

AP8

SB_DQS#[5]

AP9

SB_DQS[6]

AK11

SB_DQS#[6]

AK12

SB_DQS[7]

AP14

SB_DQS#[7]

AP15

SB_DQS[0]

C7

SB_DQS#[0]

D7

SB_DQS[1]

G3

SB_DQS#[1]

F3

SB_DQS[2]

J6

SB_DQS#[2]

K6

SB_DQS[3]

M3

SB_DQS#[3]

N3

SB_MA[0]

AA8

SB_MA[1]

T7

SB_MA[2]

R7

SB_MA[3]

T6

SB_MA[4]

T2

SB_MA[5]

T4

SB_MA[6]

T3

SB_MA[7]

R2

SB_MA[8]

T5

SB_MA[9]

R3

SB_MA[10]

AB7

SB_MA[11]

R1

SB_MA[12]

T1

SB_MA[13]

AB10

SB_MA[14]

R5

SB_MA[15]

R4

SB_DQ[0]

C9

SB_DQ[1]

A7

SB_DQ[2]

D10

SB_DQ[3]

C8

SB_DQ[4]

A9

SB_DQ[5]

A8

SB_DQ[6]

D9

SB_DQ[7]

D8

SB_DQ[8]

G4

SB_DQ[9]

F4

SB_DQ[10]

F1

SB_DQ[11]

G1

SB_DQ[12]

G5

SB_DQ[13]

F5

SB_DQ[14]

F2

SB_DQ[15]

G2

SB_DQ[16]

J7

SB_DQ[17]

J8

SB_DQ[18]

K10

SB_DQ[19]

K9

SB_DQ[20]

J9

SB_DQ[21]

J10

SB_DQ[22]

K8

SB_DQ[23]

K7

SB_DQ[24]

M5

SB_DQ[25]

N4

SB_DQ[26]

N2

SB_DQ[27]

N1

SB_DQ[28]

M4

SB_DQ[29]

N5

SB_DQ[30]

M2

SB_DQ[31]

M1

SB_DQ[32]

AM5

SB_DQ[33]

AM6

SB_DQ[34]

AR3

SB_DQ[35]

AP3

SB_DQ[36]

AN3

SB_DQ[37]

AN2

SB_DQ[38]

AN1

SB_DQ[39]

AP2

SB_DQ[40]

AP5

SB_DQ[41]

AN9

SB_DQ[42]

AT5

SB_DQ[43]

AT6

SB_DQ[44]

AP6

SB_DQ[45]

AN8

SB_DQ[46]

AR6

SB_DQ[47]

AR5

SB_DQ[48]

AR9

SB_DQ[49]

AJ11

SB_DQ[50]

AT8

SB_DQ[51]

AT9

SB_DQ[52]

AH11

SB_DQ[53]

AR8

SB_DQ[54]

AJ12

SB_DQ[55]

AH12

SB_DQ[56]

AT11

SB_DQ[57]

AN14

SB_DQ[58]

AR14

SB_DQ[59]

AT14

SB_DQ[60]

AT12

SB_DQ[61]

AN15

SB_DQ[62]

AR15

SB_DQ[63]

AT15

SB_CK[2]

AB2

SB_CLK#[2]

AA2

SB_CKE[2]

T9

SB_CK[3]

AA1

SB_CLK#[3]

AB1

SB_CKE[3]

T10

SB_CS#[0]

AD3

SB_CS#[1]

AE3

SB_CS#[2]

AD6

SB_CS#[3]

AE6

SB_ODT[2]

AD5

SB_ODT[3]

AE5

M_A_ A9

M_A_ A4

M_A_ A6

M_A_ A5

M_A_ A7

M_A_ A8

M_A_ A15

M_A_ A0

M_A_ A1

M_A_ A2

M_A_ A3

M_A_ A10

M_A_ A12

M_A_ A11

M_A_ A13

M_A_ A14

Sheet 4 of 48

Processor 3/7 -

DDR3

http://hobi-elektronika.net

Schematic Diagrams

B.Schematic Diagrams

Processor 3/7 - DDR3 B - 5

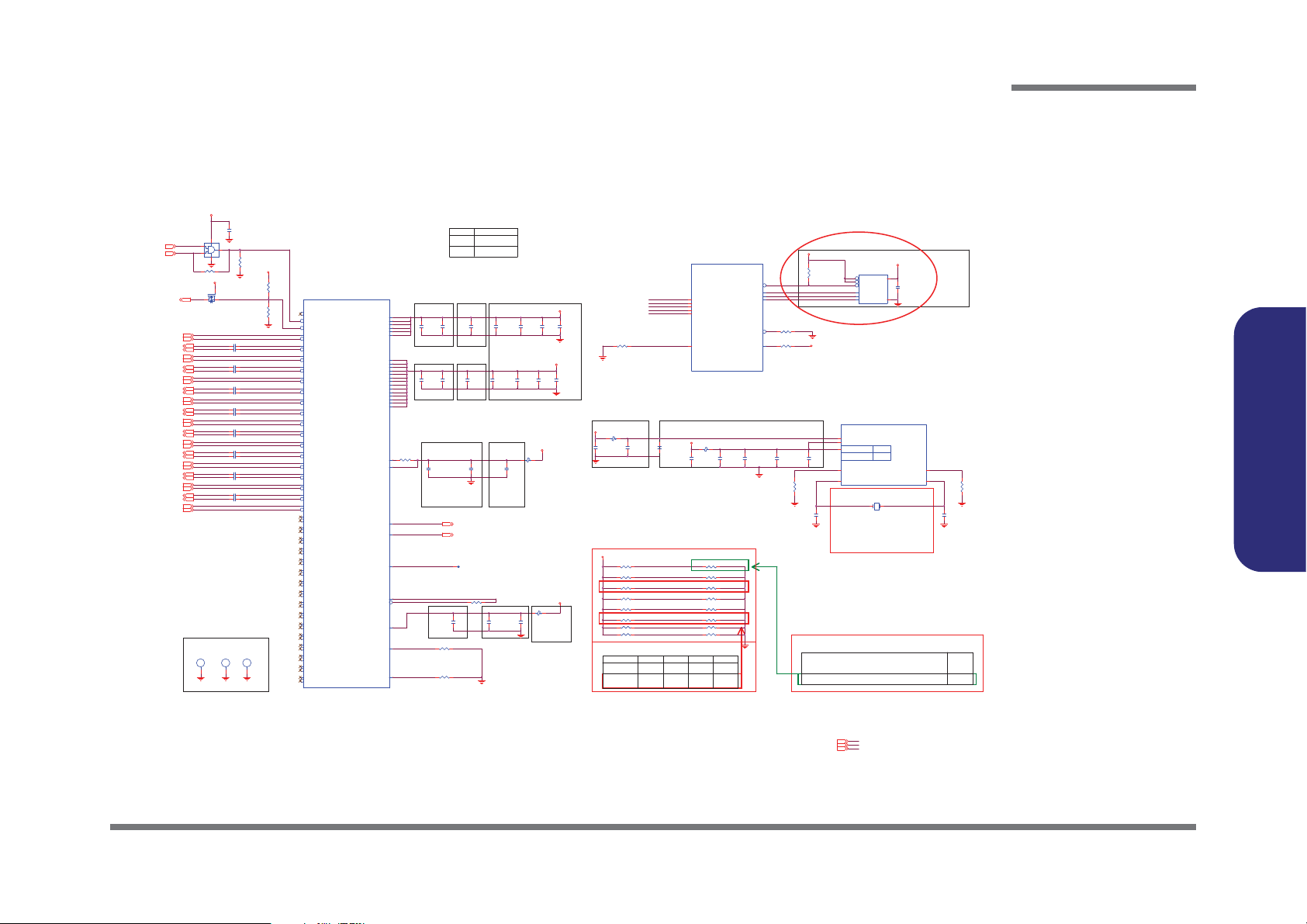

Ivy Bridge Processor 4/7 ( POWER )

PROCESSOR CORE POWER

PROCESSOR UNCORE POWER

48A

ICCMAX Maximum Processor SV

48

H_CPU_SVIDDAT_R

+

C537

330uF_2.5V_9m_6.3*6

VCCIO_SEN SE 39

CLOSE TO CPU

1.05VS _VTT2,3,23,24,25,37,39,40

VCORE40,41

C136

22u_6.3V_X5R_08

H_CPU_SVIDALRT#

+

C513

330uF_2.5V_9m_6.3*6

VSS_SENSE_VCC IO 39

H_CPU_SVIDALRT#_R

VCORE_VSS_SEN SE 40

H_CPU_SVIDALRT# 40

H_CPU_SVIDDAT 40

H_CPU_SVIDCLK 40

VCORE_VCC _SENSE 40

H_CPU_SVIDCLK_R

H_CPU_SVIDDAT_R

C189

*22u_6.3V_X5R_08

C511

22u_6.3V_X5R_08

C529

22u_6.3V_X5R_08

C544

22u_6.3V_X5R_08

C178

*22u_6.3V_X5R_ 08

R88 43_1%_04

C198

*22u_6.3V_X5R_08

C191

22u_6.3V_X5R_08

C170

*10u_6.3V_X5R_ 06

C169

*22u_6.3V_X5R_08

C539

*22u_6.3V_X5R_08

C540

*22u_6.3V_X5R_08

C184

10u_6.3V _X5R_06

R89130_1%_04

C173

*10u_6.3V_X5R_06

C515

22u_6.3V _X5R_08

C534

*10u_6.3V_X5R_06

C174

22u_6.3V_X5R_08

C183

10u_6.3V_X5R_06

C177

*22u_6.3V_X5R_08

C187

22u_6.3V_X5R_08

C541

*22u_6.3V_X5R_08

C514

22u_6.3V _X5R_08

C538

*22u_6.3V_X5R_08

C194

22u_6.3V_X5R_08

R82 0_04

C196

22u_6.3V_X5R_08

C192

22u_6.3V_X5R_08

R376

10_1%_04

C516

22u_6.3V_X5R_08

1.05VS_VTT

R81 0_04

C176

22u_6.3V_X5R_08

R375

*10_1%_04

C542

22u_6.3V_X5R_08

C535

*10u_6.3V_X5R_ 06

C199

22u_6.3V_X5R_08

C197

22u_6.3V_X5R_08

C165

*22u_6.3V_X5R _08

C543

22u_6.3V_X5R_08

C185

10u_6.3V_X5R_06

C171

10u_6.3V _X5R_06

C193

22u_6.3V_X5R_08

C195

*22u_6.3V_X5R_08

POWER

CORE SUPPLY

PEG AND DDR

SENSE LINES SVID

U31F

Ivy Bridge_rPGA_2DPC_Rev0p61

VCC_SENSE

AJ35

VSS_SENSE

AJ34

VIDALERT#

AJ29

VIDSCLK

AJ30

VIDSOU T

AJ28

VSS_SENSE_VCCIO

A10

VCC1

AG35

VCC2

AG34

VCC3

AG33

VCC4

AG32

VCC5

AG31

VCC6

AG30

VCC7

AG29

VCC8

AG28

VCC9

AG27

VCC10

AG26

VCC11

AF35

VCC12

AF34

VCC13

AF33

VCC14

AF32

VCC15

AF31

VCC16

AF30

VCC17

AF29

VCC18

AF28

VCC19

AF27

VCC20

AF26

VCC21

AD35

VCC22

AD34

VCC23

AD33

VCC24

AD32

VCC25

AD31

VCC26

AD30

VCC27

AD29

VCC28

AD28

VCC29

AD27

VCC30

AD26

VCC31

AC35

VCC32

AC34

VCC33

AC33

VCC34

AC32

VCC35

AC31

VCC36

AC30

VCC37

AC29

VCC38

AC28

VCC39

AC27

VCC40

AC26

VCC41

AA35

VCC42

AA34

VCC43

AA33

VCC44

AA32

VCC45

AA31

VCC46

AA30

VCC47

AA29

VCC48

AA28

VCC49

AA27

VCC50

AA26

VCC51

Y35

VCC52

Y34

VCC53

Y33

VCC54

Y32

VCC55

Y31

VCC56

Y30

VCC57

Y29

VCC58

Y28

VCC59

Y27

VCC60

Y26

VCC61

V35

VCC62

V34

VCC63

V33

VCC64

V32

VCC65

V31

VCC66

V30

VCC67

V29

VCC68

V28

VCC69

V27

VCC70

V26

VCC71

U35

VCC72

U34

VCC73

U33

VCC74

U32

VCC75

U31

VCC76

U30

VCC77

U29

VCC78

U28

VCC79

U27

VCC80

U26

VCC81

R35

VCC82

R34

VCC83

R33

VCC84

R32

VCC85

R31

VCC86

R30

VCC87

R29

VCC88

R28

VCC89

R27

VCC90

R26

VCC91

P35

VCC92

P34

VCC93

P33

VCC94

P32

VCC95

P31

VCC96

P30

VCC97

P29

VCC98

P28

VCC99

P27

VCC100

P26

VCCIO1

AH13

VCCIO12

J11

VCCIO18

G12

VCCIO19

F14

VCCIO20

F13

VCCIO21

F12

VCCIO22

F11

VCCIO23

E14

VCCIO24

E12

VCCIO2

AH10

VCCIO3

AG10

VCCIO4

AC10

VCCIO5

Y10

VCCIO6

U10

VCCIO7

P10

VCCIO8

L10

VCCIO9

J14

VCCIO10

J13

VCCIO11

J12

VCCIO13

H14

VCCIO14

H12

VCCIO15

H11

VCCIO16

G14

VCCIO17

G13

VCCIO25

E11

VCCIO32

C12

VCCIO33

C11

VCCIO34

B14

VCCIO35

B12

VCCIO36

A14

VCCIO37

A13

VCCIO38

A12

VCCIO39

A11

VCCIO26

D14

VCCIO27

D13

VCCIO28

D12

VCCIO29

D11

VCCIO30

C14

VCCIO31

C13

VCCIO_SEN SE

B10

VCCIO40

J23

C530

22u_6.3V _X5R_08

C172

10u_6.3V _X5R_06

R8075_04

C186

10u_6.3V _X5R_06

C545

22u_6.3V_X5R_08

C190

22u_6.3V_X5R_08

C517

22u_6.3V_X5R_08

C518

22u_6.3V _X5R_08

C135

22u_6.3V_X5R_08

VCORE

VCORE

1.05VS_VTT

VCORE

1.05VS_VTT

1.05VS_VTT

1.05VS_VTT

8.5A

Sheet 5 of 48

Processor 4/7 -

Power

B.Schematic Diagrams

Schematic Diagrams

Processor 4/7 - Power

B - 6 Processor 4/7 - Power

http://hobi-elektronika.net

Processor 5/7 - GFX PWR

Ivy Bridge Processor 5/7 ( GRAPHICS POWER )

C559

1u_6.3V_X5R _04

C180

22u_6.3V_ X5R_08

R385 0_04

C563

0.1u_10V_X 5R_04

C168

22u_6.3V_X5R_08

C257

10u_6.3V_X5R_ 06

C533

22u_6.3V_X5R_08

C260

10u_6.3V_X5R_ 06

6A

C536

22u_6.3V_X5R _08

C217

10u_6.3V_X5R_ 06

C520

22u_6.3V_ X5R_08

C258

10u_6.3V_X5R_06

C531

22u_6.3V_X5R _08

C259

10u_6.3V_X5R_ 06

C179

22u_6.3V_ X5R_08

C181

22u_6.3V_X5R _08

Q19

*MTN2306AN3

G

DS

C164

22u_6.3V_X5R _08

C561

10u_6.3V_X5R_0 6

C560

1u_6.3V_X5R_04

C166

10u_6.3V_X5R_ 06

R382

*100K_1%_04

+

C546

560u_2.5V_ 6.6*6. 6*5.9

C182

22u_6.3V_X5R _08

C532

22u_6.3V_X5R _08

C564

0.1u_10V_X 5R_04

R386

1K_1%_04

C519

22u_6.3V_X5R _08

C163

22u_6.3V_X5R _08

R369 0_04

C261

10u_6.3V_X5R_ 06

R387

1K_1%_04

C512

22u_6.3V_X5R_08

C175

22u_6.3V_X5R _08

3.3V2,11,16 ,18,19, 20,22, 23,24, 25,27, 28,29, 30,35,37 ,38,39, 40,42

VREF_CH_B_DIMM

+

C566

330uF_2. 5V_9m_6. 3*6

1.5V3,9 ,10,35, 37,38

VGFX_COR E41

0.85VS37

1.5VS_CPU3,35

1.8VS23,24,37

SUSB# 20,34,35

R372 0_04

Near CPU Socke t

12A

+

C558

330uF_2 .5V_9m_6. 3*6

33A

+

C507

560u_2.5V_6 .6*6. 6*5.9

R226

*1K_04

Q14

AO3402L

G

DS

DR AMRS T_C NTR L 3 ,19

VREF_CH_B_DIMM

VREF_ DQ_C HB 10

MVREF_DQ_DIM1

R225 * 0_04

¾aDIMMºÝÂ\©ñ & TRACE¥[¼e

R389

*1K_04

Q22

AO3402L

G

DS

VREF_ DQ_C HA 9

DRAMRST_CNTRL 3,19

VREF_ CH_A _DIMM MVRE F_D Q_D IM0

R390 *0_04

CAD Note: +V_SM_VREF should

have 10 mil trace width

V_SM_VREF V_SM_VREF_CNT

3.3V

R38310K_1%_04

VCCIO_SEL_R

C167

10u_6.3V_X5R_ 06

C162

10u_6.3V_X5R_ 06

VSS_GT_SENSE 40

VCC_GT_SENSE 40

VCCS A_VID 0 37

VCCS A_VID 1 37

VCCS A_SENS E 37

C562

0.1u_16V_Y 5V_04

VREF_CH_A_DIMM

1.2A

V_SM_VREF

+

C262

330u_6.3V _D

POWER

GRAPHICS

DDR3 -1.5V RAILS

SENSE

LINES

1.8V RAIL

SA RAI L

VREFMISC

U31G

Iv y Br i dge _r PG A_ 2D PC_R e v0 p 61

SM_VREF

AL1

VSSAXG_SENS E

AK34

VAXG_SENSE

AK35

VAXG1

AT24

VAXG2

AT23

VAXG3

AT21

VAXG4

AT20

VAXG5

AT18

VAXG6

AT17

VAXG7

AR24

VAXG8

AR23

VAXG9

AR21

VAXG10

AR20

VAXG11

AR18

VAXG12

AR17

VAXG13

AP24

VAXG14

AP23

VAXG15

AP21

VAXG16

AP20

VAXG17

AP18

VAXG18

AP17

VAXG19

AN24

VAXG20

AN23

VAXG21

AN21

VAXG22

AN20

VAXG23

AN18

VAXG24

AN17

VAXG25

AM24

VAXG26

AM23

VAXG27

AM21

VAXG28

AM20

VAXG29

AM18

VAXG30

AM17

VAXG31

AL24

VAXG32

AL23

VAXG33

AL21

VAXG34

AL20

VAXG35

AL18

VAXG36

AL17

VAXG37

AK24

VAXG38

AK23

VAXG39

AK21

VAXG40

AK20

VAXG41

AK18

VAXG42

AK17

VAXG43

AJ24

VAXG44

AJ23

VAXG45

AJ21

VAXG46

AJ20

VAXG47

AJ18

VAXG48

AJ17

VAXG49

AH24

VAXG50

AH23

VAXG51

AH21

VAXG52

AH20

VAXG53

AH18

VAXG54

AH17

VDDQ11

U4

VDDQ12

U1

VDDQ13

P7

VDDQ14

P4

VDDQ15

P1

VDDQ 1

AF7

VDDQ 2

AF4

VDDQ 3

AF1

VDDQ 4

AC7

VDDQ 5

AC4

VDDQ 6

AC1

VDDQ 7

Y7

VDDQ 8

Y4

VDDQ 9

Y1

VDDQ10

U7

VCCPLL1

B6

VCCPLL2

A6

VCCSA1

M27

VCCSA2

M26

VCCSA3

L26

VCCSA4

J26

VCCSA5

J25

VCCSA6

J24

VCCSA7

H26

VCCSA8

H25

VCCSA_SENSE

H23

VCCSA_VID[1]

C24

VCCPLL3

A2

VCCSA_VID[0]

C22

SA_DIMM_VREFDQ

B4

SB_DIMM_VREFDQ

D1

VCCIO_SEL

A19

R368 0_04

1.5VS_CPU

1.5VS_CP U

1.5V

0.85VS

VGFX_COR E

1.8VS

1.5VS_CPU

VCCSA_SENSE

Sheet 6 of 48

Processor 5/7 -

GFX PWR

http://hobi-elektronika.net

Schematic Diagrams

B.Schematic Diagrams

Processor 5/7 - GFX PWR B - 7

Schematic Diagrams

Ivy Bridge Processor 6/7 ( GND )

VSS

U31H

Ivy Bridge_rPGA_2DPC_Rev0p61

VSS1

AT35

VSS2

AT32

VSS3

AT29

VSS4

AT27

VSS5

AT25

VSS6

AT22

VSS7

AT19

VSS8

AT16

VSS9

AT13

VSS10

AT10

VSS11

AT7

VSS12

AT4

VSS13

AT3

VSS14

AR25

VSS15

AR22

VSS16

AR19

VSS17

AR16

VSS18

AR13

VSS19

AR10

VSS20

AR7

VSS21

AR4

VSS22

AR2

VSS23

AP34

VSS24

AP31

VSS25

AP28

VSS26

AP25

VSS27

AP22

VSS28

AP19

VSS29

AP16

VSS30

AP13

VSS31

AP10

VSS32

AP7

VSS33

AP4

VSS34

AP1

VSS35

AN30

VSS36

AN27

VSS37

AN25

VSS38

AN22

VSS39

AN19

VSS40

AN16

VSS41

AN13

VSS42

AN10

VSS43

AN7

VSS44

AN4

VSS45

AM29

VSS46

AM25

VSS47

AM22

VSS48

AM19

VSS49

AM16

VSS50

AM13

VSS51

AM10

VSS52

AM7

VSS53

AM4

VSS54

AM3

VSS55

AM2

VSS56

AM1

VSS57

AL34

VSS58

AL31

VSS59

AL28

VSS60

AL25

VSS61

AL22

VSS62

AL19

VSS63

AL16

VSS64

AL13

VSS65

AL10

VSS66

AL7

VSS67

AL4

VSS68

AL2

VSS69

AK33

VSS70

AK30

VSS71

AK27

VSS72

AK25

VSS73

AK22

VSS74

AK19

VSS75

AK16

VSS76

AK13

VSS77

AK10

VSS78

AK7

VSS79

AK4

VSS80

AJ25

VSS81

AJ22

VSS82

AJ19

VSS83

AJ16

VSS84

AJ13

VSS85

AJ10

VSS86

AJ7

VSS87

AJ4

VSS88

AJ3

VSS89

AJ2

VSS90

AJ1

VSS91

AH35

VSS92

AH34

VSS93

AH32

VSS94

AH30

VSS95

AH29

VSS96

AH28

VSS98

AH25

VSS99

AH22

VSS100

AH19

VSS101

AH16

VSS102

AH7

VSS103

AH4

VSS104

AG9

VSS105

AG8

VSS106

AG4

VSS107

AF6

VSS108

AF5

VSS109

AF3

VSS110

AF2

VSS111

AE35

VSS112

AE34

VSS113

AE33

VSS114

AE32

VSS115

AE31

VSS116

AE30

VSS117

AE29

VSS118

AE28

VSS119

AE27

VSS120

AE26

VSS121

AE9

VSS122

AD7

VSS123

AC9

VSS124

AC8

VSS125

AC6

VSS126

AC5

VSS127

AC3

VSS128

AC2

VSS129

AB35

VSS130

AB34

VSS131

AB33

VSS132

AB32

VSS133

AB31

VSS134

AB30

VSS135

AB29

VSS136

AB28

VSS137

AB27

VSS138

AB26

VSS139

Y9

VSS140

Y8

VSS141

Y6

VSS142

Y5

VSS143

Y3

VSS144

Y2

VSS145

W35

VSS146

W34

VSS147

W33

VSS148

W32

VSS149

W31

VSS150

W30

VSS151

W29

VSS152

W28

VSS153

W27

VSS154

W26

VSS155

U9

VSS156

U8

VSS157

U6

VSS158

U5

VSS159

U3

VSS160

U2

CAD Note: 0 ohm resistor

should be placed close

to CPU

VSS

U31I

Ivy Bridge_rPGA_2DPC_Rev0p61

VSS161

T35

VSS162

T34

VSS163

T33

VSS164

T32

VSS165

T31

VSS166

T30

VSS167

T29

VSS168

T28

VSS169

T27

VSS170

T26

VSS171

P9

VSS172

P8

VSS173

P6

VSS174

P5

VSS175

P3

VSS176

P2

VSS177

N35

VSS178

N34

VSS179

N33

VSS180

N32

VSS181

N31

VSS182

N30

VSS183

N29

VSS184

N28

VSS185

N27

VSS186

N26

VSS187

M34

VSS188

L33

VSS189

L30

VSS190

L27

VSS191

L9

VSS192

L8

VSS193

L6

VSS194

L5

VSS195

L4

VSS196

L3

VSS197

L2

VSS198

L1

VSS199

K35

VSS200

K32

VSS201

K29

VSS202

K26

VSS203

J34

VSS204

J31

VSS205

H33

VSS206

H30

VSS207

H27

VSS208

H24

VSS209

H21

VSS210

H18

VSS211

H15

VSS212

H13

VSS213

H10

VSS214

H9

VSS215

H8

VSS216

H7

VSS217

H6

VSS218

H5

VSS219

H4

VSS220

H3

VSS221

H2

VSS222

H1

VSS223

G35

VSS224

G32

VSS225

G29

VSS226

G26

VSS227

G23

VSS228

G20

VSS229

G17

VSS230

G11

VSS231

F34

VSS232

F31

VSS233

F29

VSS234

F22

VSS235

F19

VSS236

E30

VSS237

E27

VSS238

E24

VSS239

E21

VSS240

E18

VSS241

E15

VSS242

E13

VSS243

E10

VSS244

E9

VSS245

E8

VSS246

E7

VSS247

E6

VSS248

E5

VSS249

E4

VSS250

E3

VSS251

E2

VSS252

E1

VSS253

D35

VSS254

D32

VSS255

D29

VSS256

D26

VSS257

D20

VSS258

D17

VSS259

C34

VSS260

C31

VSS261

C28

VSS262

C27

VSS263

C25

VSS264

C23

VSS265

C10

VSS266

C1

VSS267

B22

VSS268

B19

VSS269

B17

VSS270

B15

VSS271

B13

VSS272

B11

VSS273

B9

VSS274

B8

VSS275

B7

VSS276

B5

VSS277

B3

VSS278

B2

VSS279

A35

VSS280

A32

VSS281

A29

VSS282

A26

VSS283

A23

VSS284

A20

VSS285

A3

Sheet 7 of 48

Processor 6/7 -

GND

http://hobi-elektronika.net

Processor 6/7 - GND

B.Schematic Diagrams

B - 8 Processor 6/7 - GND

Processor 7/7 - RSVD

CFG2

CFG7

PEG DEFER TRAINING

1: (Default) PEG Train immediately following xxRESETB de assertion

0: PEG Wait for BIOS for training

CFG5

CFG6

CFG4

CFG2

PEG Static Lane Reversal - CFG2 is for the 16x

1:(Default) Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

CFG2

Ivy Bridge Processor 7/7 ( RESERVED )

CFG4

H_CPU_RSVD1

H_CPU_RSVD4

H_CPU_RSVD3

H_CPU_RSVD2

CFG7

R112 *1K_04

R113 *1K_04

R106 *1K_04

R111 *1K_04

R105 *1K_04

RESERVED

CFG

U31E

Iv y Bridge_rPGA_2D PC_R ev 0p61

CFG[0]

AK28

CFG[1]

AK29

CFG[2]

AL26

CFG[3]

AL27

CFG[4]

AK26

CFG[5]

AL29

CFG[6]

AL30

CFG[7]

AM31

CFG[8]

AM32

CFG[9]

AM30

CFG[10]

AM28

CFG[11]

AM26

CFG[12]

AN28

CFG[13]

AN31

CFG[14]

AN26

CFG[15]

AM27

CFG[16]

AK31

CFG[17]

AN29

RSVD34

AM33

RSVD35

AJ27

RSVD38

J16

RSVD_NCTF42

AT34

RSVD39

H16

RSVD40

G16

RSVD_NCTF41

AR35

RSVD_NCTF43

AT33

RSVD_NCTF45

AR34

RSVD_NCTF56

AT2

RSVD_NCTF57

AT1

RSVD_NCTF58

AR1

RSVD_NCTF46

B34

RSVD_NCTF47

A33

RSVD_NCTF48

A34

RSVD_NCTF49

B35

RSVD_NCTF50

C35

RSVD51

AJ32

RSVD52

AK32

RSVD27

J15

RSVD16

C30

RSVD15

D23

RSVD17

A31

RSVD18

B30

RSVD20

D30

RSVD19

B29

RSVD22

A30

RSVD21

B31

RSVD23

C29

RSVD37

T8

RSVD8

F25

RSVD9

F24

RSVD11

D24

RSVD12

G25

RSVD13

G24

RSVD14

E23

RSVD32

W8

RSVD33

AT26

RSVD_NCTF44

AP35

RSVD10

F23

RSVD5

AJ26

VAXG_VAL_SENSE

AJ31

VSSAXG_VAL_SENSE

AH31

VCC_VAL_SENSE

AJ33

VSS_VAL_SENSE

AH33

KEY

B1

VCC_DIE_SENSE

AH27

BCLK_ITP

AN35

BCLK_ITP#

AM35

VSS_DIE_SENSE

AH26

RSVD31

AK2

RSVD30

AE7

RSVD29

AG7

RSVD28

L7

RSVD24

J20

RSVD25

B18

CFG7

CFG Straps for Processor

CFG5

Display Port Presence Strap

1:(Default) Disabled; No Physical Display Port

attached to Embedded Display Port

0:Enabled; An external Display Port device is

connected to the Embedded Display Port

CFG4

CFG0

CFG6

PCIE Port Bifurcation Straps

11: (Default) x16 - Device 1 functions 1 and 2 disabled

10: x8, x8 - D evice 1 function 1 enabled ; function 2 disabled

01: Reserved - (Device 1 functio n 1 disabled ; func tion 2 enabled)

00: x8,x4,x4 - Device 1 function s 1 and 2 enabled

CFG[6:5]

Sheet 8 of 48

Processor 7/7 -

RSVD

http://hobi-elektronika.net

Schematic Diagrams

B.Schematic Diagrams

Processor 7/7 - RSVD B - 9

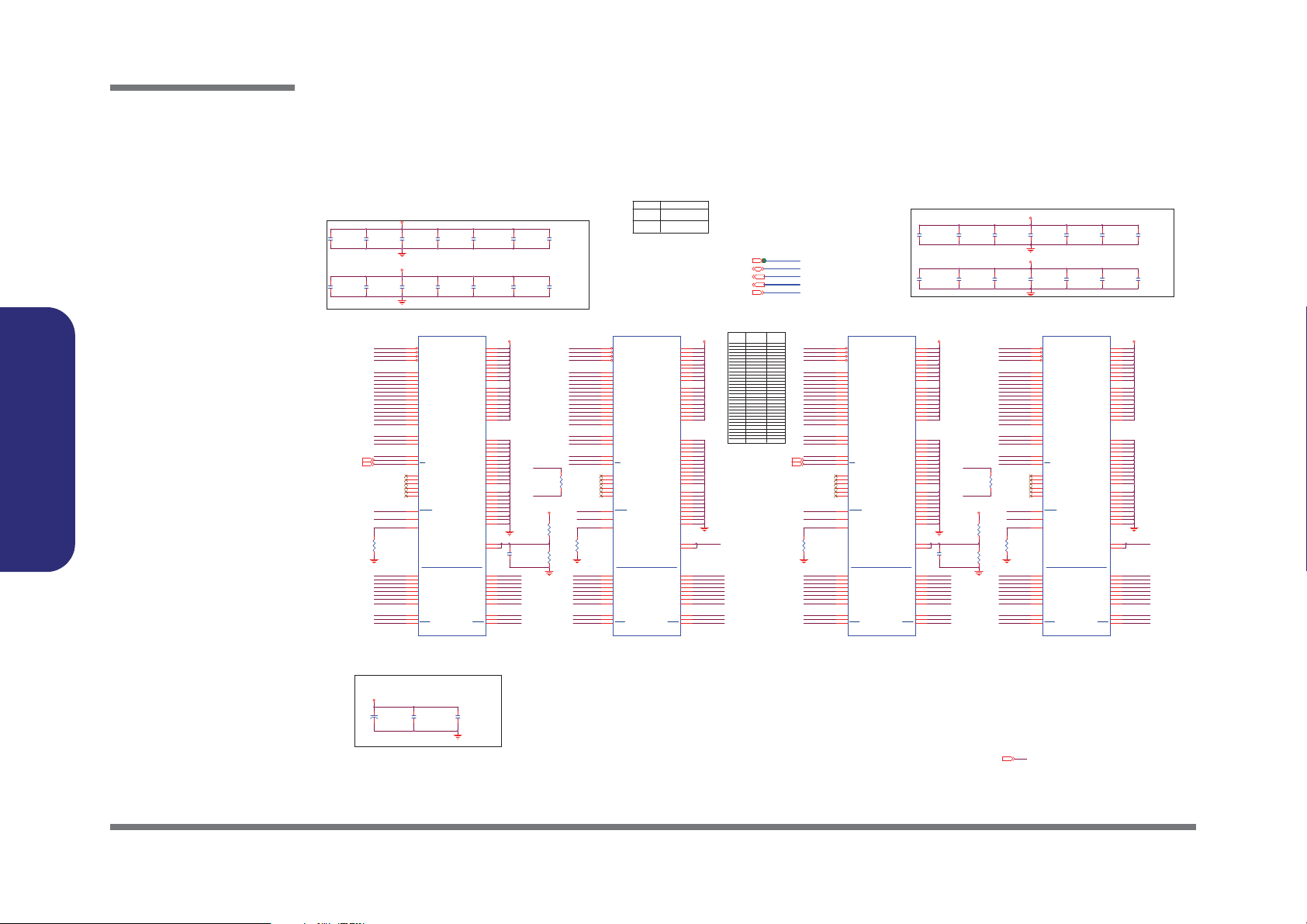

Schematic Diagrams

+

C572

*330u_2. 5V_V_A

SO-DIMM A

M_A_ DQ 3

M_A_ DQ 2

M_A_ DQ 1

°ª«×9.2H REV

M_A_ DQ 32

M_A_ DQ 31

M_A_ DQ 30

M_A_ DQ 29

M_A_ DQ 4

M_A_ DQ 39

M_A_ DQ 37

M_A_ DQ 36

M_A_ DQ 35

M_A_ DQ 34

M_A_ DQ 33

M_A_ DQ 44

M_A_ DQ 43

M_A_ DQ 42

M_A_ DQ 41

M_A_ DQ 40

M_A_ DQ 49

M_A_ DQ 38

M_A_ DQ 47

M_A_ DQ 46

M_A_ DQ 45

M_A_ DQ 54

M_A_ DQ 53

M_A_ DQ 52

M_A_ DQ 51

M_A_ DQ 28

M_A_ DQ 50

M_A_ DQ 56

M_A_ DQ 6

M_A_ DQ 5

M_A_ DQ 48

M_A_ DQ 55

M_A_ DQ 62

M_A_ DQ 61

M_A_ DQ 60

M_A_ DQ 58

M_A_ DQ 57

M_A_ DQ 11

M_A_ DQ 9

M_A_ DQ 8

M_A_ DQ 7

M_A_ DQ 59

M_A_ DQ 63

M_A_ DQ 16

M_A_ DQ 15

M_A_ DQ 14

M_A_ DQ 13

M_A_ DQ 12

M_A_ DQ 21

M_A_ DQ 10

M_A_ DQ 19

M_A_ DQ 18

M_A_ DQ 17

TS#_DIMM0_110

M_A_ DQ 26

M_A_ DQ 25

M_A_ DQ 24

M_A_ DQ 23

M_A_ DQ 0

M_A_ DQ 22

SA0_DIM1 10

SA1_DIM1 10

M_A_ DQ 20

M_A_ DQ 27

VREF_CA_0

1.5V

RN2

1K_8P4R_04

1

2

3456

7

8

VREF_ DQ_0

SA1_DIM0

SA0_DIM0

CLOSE TO S O-DI MM _0

20mils

signal/space/signal:

Layou t Note :

8 / 4 / 8

M_A_CLK_DDR14

M_A _OD T14

M_A_R AS#4

M_A _BS 14

M_A_W E#4

M_A_C AS#4

M_A_CLK_DDR#14

1.5V3,6,10,35,37, 38

VTT_MEM10,38

M_A _OD T04

M_A _BS 04

M_A _BS 24

M_A _CK E04

M_A_CLK_DDR04

M_A_CLK_DDR#04

M_A _CS #14

M_A _CK E14

3.3VS3,10,11, 12,18,1 9,20,21, 22,23, 24,25,2 7,28,30, 31,32,33, 34,35, 40

M_A_A[15 :0]4

M_A _CS #04

1.5V

VREF_DQ_CHA 6

+

C571

*330u_2. 5V_V_A

JDIMM1B

Oceantek 9 1-934 69- 172

VDD1

75

VDD2

76

VDD3

81

VDD4

82

VDD5

87

VDD6

88

VDD7

93

VDD8

94

VDD9

99

VDD10

100

VDD11

105

VDD12

106

VDDSPD

199

NC1

77

NC2

122

NCTEST

125

VREF_DQ

1

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VSS16

44

VSS17

48

VSS18

49

VSS19

54

VSS20

55

VSS21

60

VSS22

61

VSS23

65

VSS24

66

VSS25

71

VSS26

72

VSS27

127

VSS28

128

VSS29

133

VSS30

134

VSS31

138

VSS32

139

VSS33

144

VSS34

145

VSS35

150

VSS36

151

VSS37

155

VSS38

156

VSS39

161

VSS40

162

VSS41

167

VSS42

168

VSS43

172

VSS44

173

VSS45

178

VSS46

179

VSS47

184

VSS48

185

VSS49

189

VSS50

190

VSS51

195

VSS52

196

G2

GND2

G1

GND1

VTT2

204

VTT1

203

VREF_CA

126

RESET#

30

EVENT#

198

VDD13

111

VDD14

112

VDD16

118

VDD15

117

VDD17

123

VDD18

124

C354

0.1u_16V_Y 5V_04

C570

0.1u_10V_X5R_04

C340

1u_6.3V_X5R_04

C577 1u_6.3V_X5R_04

C282

0.1u_10V_X5R_04

C336

1u_6.3V_X5R_04

C578 0.1u_16V_Y5V_04

C297

1u_6.3V_X5R_04

C283

10u_6.3V_X5R_06

C341

0.1u_10V_X5R_04

C338

0.1u_10V_X5R_04

C569

1u_6.3V_X5R_04

C307 * 10p_50V_NPO_04

C327

0.1u_10V_X5R_04

C300 * 10p_50V_NPO_04

C574

0.1u_10V_X5R_04

C319

1u_6.3V_X5R_04

VREF_ CA_0

JDIMM1A

Oceantek 91- 93469- 172

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC#

83

A13

119

A14

80

A15

78

DQ0

5

DQ1

7

DQ2

15

DQ3

17

DQ4

4

DQ5

6

DQ6

16

DQ7

18

DQ8

21

DQ9

23

DQ10

33

DQ11

35

DQ12

22

DQ13

24

DQ14

34

DQ15

36

DQ16

39

DQ17

41

DQ18

51

DQ19

53

DQ20

40

DQ21

42

DQ22

50

DQ23

52

DQ24

57

DQ25

59

DQ26

67

DQ27

69

DQ28

56

DQ29

58

DQ30

68

DQ31

70

DQ32

129

DQ33

131

DQ34

141

DQ35

143

DQ36

130

DQ37

132

DQ38

140

DQ39

142

DQ40

147

DQ41

149

DQ42

157

DQ43

159

DQ44

146

DQ45

148

DQ46

158

DQ47

160

DQ48

163

DQ49

165

DQ50

175

DQ51

177

DQ52

164

DQ53

166

DQ54

174

DQ55

176

DQ56

181

DQ57

183

DQ58

191

DQ59

193

DQ60

180

DQ61

182

DQ62

192

DQ63

194

BA0

109

BA1

108

RAS#

110

WE#

113

CAS#

115

S0#

114

S1#

121

CKE0

73

CKE1

74

CK0

101

CK0#

103

CK1

102

CK1#

104

SDA

200

SCL

202

SA1

201

SA0

197

DM0

11

DM1

28

DM2

46

DM3

63

DM4

136

DM5

153

DM6

170

DM7

187

DQS0

12

DQS1

29

DQS2

47

DQS3

64

DQS4

137

DQS5

154

DQS6

171

DQS7

188

DQS0#

10

DQS1#

27

DQS2#

45

DQS3#

62

DQS4#

135

DQS5#

152

DQS6#

169

DQS7#

186

ODT0

116

ODT1

120

BA2

79

C314

1u_6.3V_X5R_04

C328

1u_6.3V_X5R_04

RN3

10K_8P4R_04

1

2

3

4 5

6

7

8

C299

0.1u_10V_X5R_04

C281

0.1u_10V_X5R_04

C326

1u_6.3V_X5R_04

C287 0.1u_16V_Y5V_04

C280

0.1u_10V_X5R_04

R191 *10K_04

C298

1u_6.3V_X5R_04

C288 1u_6.3V_X5R_04

C573

0.1u_10V_X5R_04

VREF_DQ_0

R391 0_04

SA0_DIM0

SA1_DIM0

M_A_CLK_D DR1 M_A_CLK_DDR#1

M_A_CLK_D DR0 M_A_CLK_DDR#0

SMB_DATA10,19

M_A_ DQ [6 3: 0] 4

SMB_CLK10,19

M_A_DQS #[7: 0]4

M_A_DQ S[7:0 ]4

C305

10u_6.3V_X5R_06

DDR3_DRAMRST#3,10

C318

10u_6.3V_X5R_06

C289

10u_6.3V_X5R_06

M_A_A6

M_A_A5

M_A_A7

M_A_A8

M_A_A9

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A1 2

M_A_A1 1

M_A_A1 3

M_A_A1 4

M_A_A1 5

M_A_A1 0

M_A_D QS0

M_A_D QS1

6-86-24204-031

M_A_D QS2

M_A_D QS3

M_A_D QS4

C367

1u_6.3V_X5R_04

M_A_D QS5

M_A_D QS6

M_A_D QS7

M_A_D QS#0

M_A_D QS#1

C306

0.1u_10V_X 5R_04

C576

0.1u_10V_X5R _04

M_A_D QS#2

M_A_D QS#3

M_A_D QS#4

M_A_D QS#5

M_A_D QS#6

M_A_D QS#7

3.3VS

3.3VS

1.5V

3.3VS

1.5V

VTT_MEM

VTT_MEM

1.5V

Sheet 9 of 48

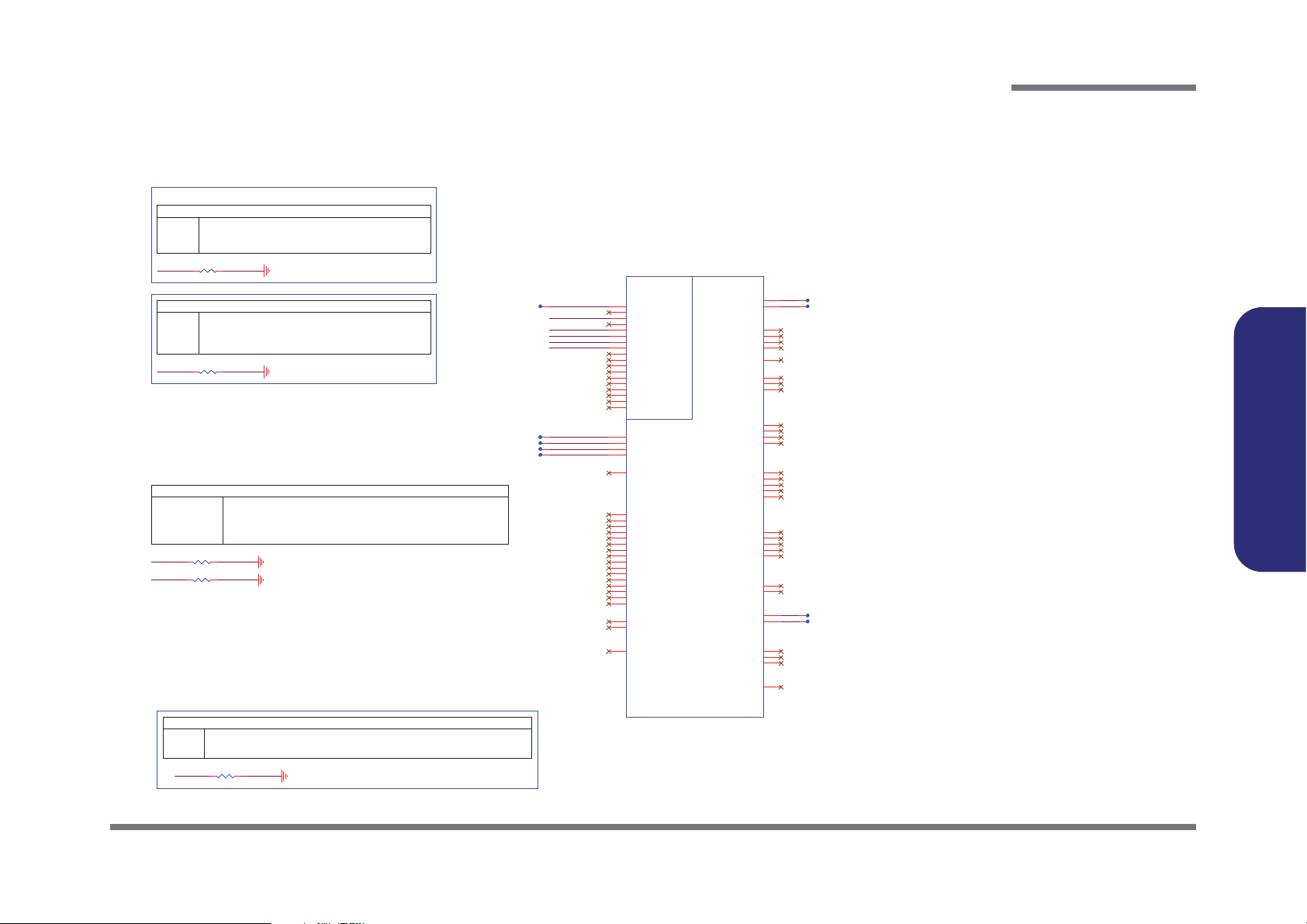

DDR3 SO-DIMM_0

B.Schematic Diagrams

B - 10 DDR3 SO-DIMM_0

http://hobi-elektronika.net

DDR3 SO-DIMM_0

DDR3 SO-DIMM_1

3.3VS

1.5V

VTT_MEM

1.5V

1.5V

VTT_MEM

R403

0_04

M_B_DQ[63:0] 4

°ª«×5.2H REV

SA0_DIM19

TS#_DIMM0_19

SA1_DIM19

SO-DIMM B

Layout Note:

M_B_D Q31

M_B_D Q46

M_B_D Q13

M_B_D Q24

M_B_D Q56

M_B_D Q28

M_B_D Q11

M_B_D Q23

M_B_D Q61

M_B_D Q62

M_B_D Q58

M_B_D Q50

M_B_D Q1

M_B_D Q16

M_B_D Q60

M_B_D Q2

M_B_D Q40

M_B_D Q54

M_B_D Q41

M_B_D Q57

M_B_D Q37

M_B_D Q25

M_B_D Q30

M_B_D Q27

M_B_D Q44

M_B_D Q3

M_B_D Q7

M_B_D Q9

M_B_D Q34

M_B_D Q5

M_B_D Q47

M_B_D Q43

M_B_D Q38

M_B_D Q17

M_B_D Q42

M_B_D Q8

M_B_D Q59

M_B_D Q35

M_B_D Q36

8 / 4 / 8

M_B_D Q4

M_B_D Q26

M_B_D Q63

M_B_D Q33

M_B_D Q45

M_B_D Q48

M_B_D Q55

M_B_D Q29

M_B_D Q15

M_B_D Q10

M_B_D Q52

M_B_D Q53

M_B_D Q6

M_B_D Q19

M_B_D Q18

M_B_D Q0

M_B_D Q12

M_B_D Q20

M_B_D Q39

M_B_D Q49

M_B_D Q51

M_B_D Q21

M_B_D Q32

M_B_D Q14

M_B_D Q22

SO-DIMM _1 i s pla ced fa rther fro m the GM C H tha n SO-DI M M_0

M_B_A4

M_B_A6

M_B_A5

M_B_A13

M_B_A12

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A14

20mils

Layout Note:

SA1_DIM1

signal/space/signal:

M_B_A15

M_B_D QS0

M_B_D QS6

M_B_D QS5

M_B_D QS4

M_B_D QS3

M_B_D QS2

M_B_D QS1

M_B_D QS#3

M_B_D QS#2

M_B_D QS#1

M_B_D QS#0

M_B_D QS7

M_B_D QS#7

M_B_D QS#6

M_B_D QS#5

M_B_D QS#4

M_B_CLK_DDR2 M_B_CLK_DDR#2

M_B_CLK_DDR3 M_B_CLK_DDR#3

C356 0.1u_16V_ Y5V_0 4

C583 0.1u_16V_ Y5V_0 4

C380

0.1u_10V _X5R_04

C347 *10p_50V_NPO _04

C317

0.1u_16V_Y 5V_04

C337

1u_6.3V_X5R_04

C376

0.1u_10V_X5R_04

C368

0.1u_10V_X5R_04

VTT_MEM9,38

1.5V3, 6,9,35,37 ,38

M_B_BS 14

M_B_CLK_D DR34

M_B_A[15:0 ]4

M_B_C AS#4

M_B_CLK_D DR#34

M_B_R AS#4

M_B_CLK_D DR24

M_B_BS 04

M_B_W E#4

M_B_C S#34

M_B_CKE34

M_B_BS 24

M_B_CKE24

M_B_OD T34

M_B_C S#24

M_B_CLK_D DR#24

JDI MM2B

Oceantek 9 1-93469-17 4

VDD1

75

VDD2

76

VDD3

81

VDD4

82

VDD5

87

VDD6

88

VDD7

93

VDD8

94

VDD9

99

VDD10

100

VDD11

105

VDD12

106

VDDSPD

199

NC1

77

NC2

122

NCTEST

125

VREF_DQ

1

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VSS16

44

VSS17

48

VSS18

49

VSS19

54

VSS20

55

VSS21

60

VSS22

61

VSS23

65

VSS24

66

VSS25

71

VSS26

72

VSS27

127

VSS28

128

VSS29

133

VSS30

134

VSS31

138

VSS32

139

VSS33

144

VSS34

145

VSS35

150

VSS36

151

VSS37

155

VSS38

156

VSS39

161

VSS40

162

VSS41

167

VSS42

168

VSS43

172

VSS44

173

VSS45

178

VSS46

179

VSS47

184

VSS48

185

VSS49

189

VSS50

190

VSS51

195

VSS52

196

G2

GND2

G1

GND1

VTT2

204

VTT1

203

VREF_CA

126

RESET#

30

EVENT#

198

VDD13

111

VDD14

112

VDD16

118

VDD15

117

VDD17

123

VDD18

124

3.3VS3,9,11,12, 18,1 9,20,2 1,22, 23,24, 25,2 7,28, 30,31, 32,33 ,34,35 ,40

M_B_OD T24

C316

1u_6.3V _X5R_04

CLOSE TO SO-DI MM1

JDI MM2A

Oceantek 9 1-93469-17 4

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC#

83

A13

119

A14

80

A15

78

DQ0

5

DQ1

7

DQ2

15

DQ3

17

DQ4

4

DQ5

6

DQ6

16

DQ7

18

DQ8

21

DQ9

23

DQ10

33

DQ11

35

DQ12

22

DQ13

24

DQ14

34

DQ15

36

DQ16

39

DQ17

41

DQ18

51

DQ19

53

DQ20

40

DQ21

42

DQ22

50

DQ23

52

DQ24

57

DQ25

59

DQ26

67

DQ27

69

DQ28

56

DQ29

58

DQ30

68

DQ31

70

DQ32

129

DQ33

131

DQ34

141

DQ35

143

DQ36

130

DQ37

132

DQ38

140

DQ39

142

DQ40

147

DQ41

149

DQ42

157

DQ43

159

DQ44

146

DQ45

148

DQ46

158

DQ47

160

DQ48

163

DQ49

165

DQ50

175

DQ51

177

DQ52

164

DQ53

166

DQ54

174

DQ55

176

DQ56

181

DQ57

183

DQ58

191

DQ59

193

DQ60

180

DQ61

182

DQ62

192

DQ63

194

BA0

109

BA1

108

RAS#

110

WE#

113

CAS#

115

S0#

114

S1#

121

CKE0

73

CKE1

74

CK0

101

CK0#

103

CK1

102

CK1#

104

SDA

200

SCL

202

SA1

201

SA0

197

DM0

11

DM1

28

DM2

46

DM3

63

DM4

136

DM5

153

DM6

170

DM7

187

DQS0

12

DQS1

29

DQS2

47

DQS3

64

DQS4

137

DQS5

154

DQS6

171

DQS7

188

DQS0#

10

DQS1#

27

DQS2#

45

DQS3#

62

DQS4#

135

DQS5#

152

DQS6#

169

DQS7#

186

ODT0

116

ODT1

120

BA2

79

C584 1u_6.3V_X5R _04

C373

1u_6.3V_X5R_04

C315

1u_6.3V_X5R_04

C372

1u_6.3V_X5R_04

C335

1u_6.3V_X5R_04

C355 1u_6.3V_X5R _04

C334

1u_6.3V _X5R_04

C339

1u_6.3V_X5R_04

C381

0.1u_10V_X5R_04

C333

0.1u_10V_X5R_04

C377

0.1u_10V_X5R_04

C359

1u_6.3V_X5R_04

C358

0.1u_10V_X5R_04

C342

0.1u_10 V_X5R_04

C378

0.1u_10V_X5R_04

C374

1u_6.3V_X5R_04

C379

0.1u_10V_X5R_04

C357 *10p_50V_NPO _04

VREF_CA_1

1.5V

RN4

1K_8P4R_04

1

2

3456

7

8

VREF_D Q_1

VREF_DQ_CHB 6

SMB_CLK9, 19

SMB_DATA9,19

M_B_DQS#[7:0]4

M_B_DQS[ 7:0]4

VREF_ DQ_1

DDR3_DRAMRST#3, 9

VREF_ CA_1

C375

10u_6.3V_X5R_06

C308

10u_6.3V_X5R_06

C343

10u_6.3 V_X5R_06

C348

10u_6. 3V_X5R_06

6-86-24204-030

SA0_DIM1

C369

0.1u_10V_X5R_04

C370

0.1u_10V_X5R_04

Sheet 10 of 48

DDR3 SO-DIMM_1

http://hobi-elektronika.net

Schematic Diagrams

B.Schematic Diagrams

DDR3 SO-DIMM_1 B - 11

Schematic Diagrams

Sheet 11 of 48

PANEL, INVERTER,

CRT

PJ29»Ýμu¸ô

3.3VS

GPU

Side(3.3VS)

Intel

2K

LVDS-LCLKN21

nVidia

no

CommentnoComme nt

2.2K

10K

2.2K

AMD

Device

Side(5VS)

LVDS-L0P

LVDS-LCLKN

LVDS-L1P

INV_BLON

LVDS-L2N

LVDS-L1N

LVDS-LCLKP

LVDS-L0N

BRIGHTN ESS_R

LVDS-L2P

1A

P_DDC_CLK

BLON1

BLON2

INV_BLO N

PLVDD

C497

1u_16V_X5R_06

C122

1u_16V_X5R _06

PLVDD

R346

100K_04

U28

G5243A

EN

3

VIN

5

VIN/ SS

4

VOUT

1

GND

2

3.3VS

R643

2.2K_04

NB_ENAVDD

P_DDC_ DATA 21

2A

P_DDC_CLK 21

R642

2.2K_04

R644

2.2K_04

2A

LID_SW#1

NB_ENAVD D#

Q3

*P2003EVG

4

62

5731

8

R25

*10K_04

C29

0.1u_50V_Y5V_06

R26

*4.7K_04

R23 *100K_04

S

D

G

Q4B

*MTDN7002ZHS6 R

5

34

R18

*1M_04

S

D

G

Q4A

*MTDN7002ZHS 6R

2

61

Q2

*2N7002W

G

DS

3.3V

NB_ENAVDD21,34

VIN_LC DVIN

C39

*0.22u_50V_Y 5V_06

LVDS-L0N 21

M 6-02-0701 9-B20

S 6-02-4772 1-B60

BYP

C58

0.22u_10V_X5R_04

R24 33_04

R22 33_04

C60

0.22u_10V_X5R_04

C59

0.22u_10V_X5R _04

LVDS-LCLKP21

DAC_DDCACLK21

DAC_DDCADATA21

3.3VS

U4

TPD7S 019

VCC_SY NC

1

VCC_VI DEO

2

VIDEO_1

3

VIDEO_2

4

VIDEO_3

5

GND

6

VCC_DDC

7

BYP

8

DDC_OUT1

9

DDC_IN1

10

DDC_IN211DDC_OUT2

12

SYNC _IN113SYNC_OUT1

14

SYNC _IN215SYNC_OUT2

16

DAC_VSYNC21

DAC_HSYNC21

HSYNCHSYNC_C

VSYNC _C

FRED

FRED

FBLUE

FGRN

FGRN

C38

220p_50V_NPO_04

J_CRT1

108AH15FST04A1CC

8

7

6

5

4

3

2

1

9

10

11

12

13

14

15

GND2

GND1

DDCDATA

VSYNC

C45

1000p_50V_X7R_04

C28

220p_50V_NPO_04

ESD+LEVEL SHIFT+BU FFER

DDCLK

C20

1000p_50V_X7R_04

HSYNC

DDCDATA

DDCLK

FBLUE

VSYNC

C304

0.1u_16V_Y5V_04

U13C

74LVC08PW

9

10

8

147

C471

20p_50V_NPO_04

C575

*0.1u_16V_Y5V_04

R205 *100K_04

C107

0.1u_16V_Y5V _04

C462

20p_50V_NPO_04

C490

10p_50V_NPO_04

C491

0.1u_16V_Y5V_04

R203 *100K_04

L42 F CM1005MF-600T01

R392

100K_04

L44 F CM1005MF-600T01

R282. 2K_04

C467

10p_50V_NPO_04

R320

150_1%_04

L47 F CM1005MF-600T01

2A

7/11 PIN D efineÅܧó(F ollow¦@¥Î½u ¸ô0622)

U13B

74LVC08PW

4

5

6

147

R329

150_1%_04

U13D

74LVC08PW

12

13

11

147

R204 *100K_04

R335

150_1%_04

C74

0.1u_50V_Y5V_0 6

L41 F CM1005MF-600T01

C486

20p_50V_NPO_04

R272. 2K_04

J_LCD1

87216-3006

112

2

334

4

556

6

778

8

9910

10

111112

12

131314

14

151516

16

171718

18

191920

20

212122

22

232324

24

252526

26

272728

28

292930

30

C460

10p_50V_NPO_04

L48 F CM1005MF-600T01

U13A

74LVC08PW

1

2

3

147

C482

10p_50V_NPO_04

BLON

BKL_EN

C73

0.1u_50V_Y5V_06

C500

4.7u_6.3V_X5R_06

L46 F CM1005MF-600T01

C483

10p_50V_NPO_04

C466

10p_50V_NPO_04

VIN_LCD

3.3VS

5VS3.3VS

3.3V 3.3V

3.3V

LVDS-L2N 21

3.3V

DAC_GREEN21

DAC_BLUE21

DAC_RED21

5VS18,24,25, 28,32,33, 35,40,41,42

SYS15V29,35,36,37, 39

3.3VS3,9,10, 12,18,19,20, 21,22,23, 24,25,27, 28,30,31, 32,33,34,35 ,40

VDD316,18,27,28, 29,30,34, 35,36,37, 42,43

VIN35,36,37, 38,39,40,41, 42,43

SB_BLON23

3.3V2,6,16,18, 19,20,22, 23,24,25, 27,28,29, 30,35,37,38, 39,40,42

BLON21

ALL_SYS_ PWRGD20, 34,40

LID_SW#28,34

BKL_EN34

BRIGHTNESS_R

D20 *RB751S-40C2

A C

R333 0_04

R334 *10K_04

D6

*BAV99 RECTIFIER

A

C

AC

C85

*0.1u_1 6V_Y5V_04

BRIGH TNESS 34

3.3V

PLVDD

CRT

LVDS-L1N21

D7

RB751S-40C2

AC

DAC_GREEN

DAC_RED

DAC_BLUE

R641

2.2K_04

P_DDC_DATA

LVDS-L2P 21

PJ29

OPEN_2A

12

LVDS-L0P 21

C25

0.1u_50V_Y5V_06

PANEL CONNECTOR

CLOSE TO LVDS CONN. PIN

LVDS-L1P21

http://hobi-elektronika.net

PANEL, INVERTER, CRT

B.Schematic Diagrams

B - 12 PANEL, INVERTER, CRT

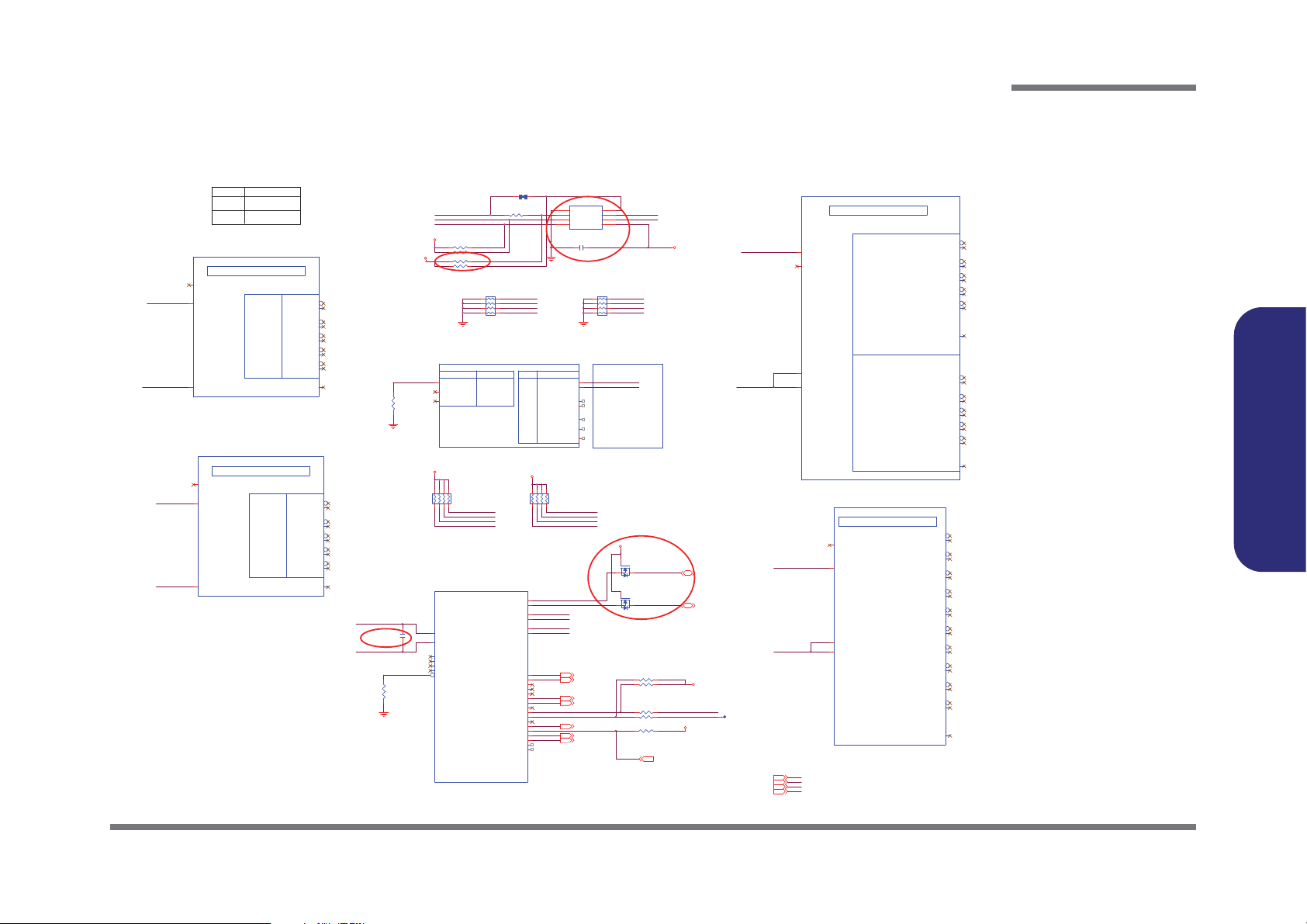

VGA PCI-E Interface

.

L57 FCM1608 KF-181T05

R742 45 .3K_1%_0 4R744 *10K_04

PEX_CLKRE Q#_R

R656

0_04

PEX_VDD_SVDD

VGA_STRAP4

if use the N13P-GS

the L4 need change to 0 ohm

24.9K X

10K

X

1/16 ¤£¤W¥ ó

R48 45.3K_1%_04

C7 0.22u_10V_X5R_04

SP_PLLVDD

U6

*PM25LD010 C-SCE

1

CS

2

SO

3

WP

4

GND

5

SI

6

SCK

7

HOLD8VCC

C69

4.7u_6.3V_X5R_06

R94 45.3K_1%_04

C76

1u_6.3V_X5R _04

C8 0.22u_10V_X5R_04

R100 *20K_1%_04

R93

10K_04

10K

C660

10u_6.3V_ X5R_06

C13 0 .22u_10V_ X5R_04

C5 0.22u_10V_X5R_04

R49 4.99K_1%_04

C656

1u_6.3V_X5R_04

R317

10K_04

C18 0 .22u_10V_ X5R_04

C65

1u_6.3V_X5R _04

C4 0.22u_10V_X5R_04

R72 *30K_1%_04

C34

4.7u_6.3V_X5R_06

C153

18p_50V_NPO_04

C41

1u_6.3V_X5R_04

R109 * 34.8K_1% _04

VGA_ROM_SCLK

R101 4.99K_1%_04

PEX_RX3#

PEX_RX4#

PEX_RX5#

PEX_RX1#

PEX_RX2#

SAMSUNG 1G K4W1G1646G-BC11

SAMSUNG 2G K4W2G1646C-HC11

Default 2G VGA ROM GREEN MARK

6-04-41164-E35

6-04-42164-E30

VGA ROM Type

45.3K

20K

R94

12/19 XTAL_PLL

GF117GF108/GKx

NC

U27O

bga_0908_p 080_p085_p10 0_290x29 0

COMMON

H1

XTALSSIN

AD7

VID_PLLVDD

AE8

SP_PLLVDD

AD8

PLLVDD

H2

XTALOUT

J4

XTALOU TBU FF

H3

XTALIN

M_STRAP_REF

3V3_RUN

3V3_R UN

3V3_RUN

3.3VS

3V3_RUN

3V3_RUN

3V3_RUN

3V3_RUN

VGA_STRAP2

VGA_STRAP1

VGA_STRAP0

PLACE NEAR BGA

PEX_RX4

VGA_ROM_SI

PEG_RX#0

PEG_RX3

PEG_RX2

PEG_RX#5

PEG_RX0

PEX_RX0#

PEG_RX4

PEX_RX3

PEG_RX#2

PEG_RX#3

PEG_RX1 PEX_RX1

PEX_RX5PEG_RX5

PEX_RX2

PEX_RX0

PEG_RX#4

VGA_ROM_SO

PEG_RX#1

PEG_RX#52

PEG_RX#12

PEG_RX32

PEG_RX22

PEG_RX#22

PEG_RX#72

PEG_RX#32

PEG_RX#62

R573 *0_04

C672

4.7u_6.3V_X5R_06

PEG_RX#42

PEG_RX72

PEG_RX#02

VGA_STRAP0

PEG_RX12

PEG_RX52

PEG_RX02

PEG_RX42

PEG_CLKREQ#19

VGA_STRAP1

PEG_RX62

VGA_PEXCLK#

VGA_PEXCLK

VGA_STRAP2

6-04-25010-A91

PEG_TX1

PEG_TX#0

PEG_TX0

PLACE UNDER BALLS

PLACE NEAR BGA

PEG_TX2

PEG_TX#1

PEG_TX3

PEG_TX#2

VID_PLLVDD

PEG_TX#3

PLACE UNDER BALL

PEG_TX#5

PEG_TX5

PEG_TX#4

PEG_TX4

16mil

PEX_TERMP

BIOS ROM

GPU_TESTMODE

GPU

16mil

PLACE NEAR BGA

PS1_GND_SENSE

Crystal 8045 & 3225 Co-lay

PLACE NEAR BGA

PLACE UNDER BALLS

FSX8L_25 MHz¥Ø«e¦@¥Î®Æ

Default N13P-GL RED MARK

PLACE UNDER BALLS

2200 mA

16mil

R54

X34.8KX

R55R109R101

12mil

N13P-GL

N13P-GT

VGA_STRAP3

PS1_VDD_SENSE

PEX_PLLVDD

VGA CARD

C659

10u_6.3V_ X5R_06

XTAL _O UT

PEX_VDD

PEX_VDD

PEX_VDD

PEX_VDD

X_SSIN X_OUTBU FF

PERSTB#

PS1_VDD_SENSE 42

PS1_GND_SENSE 42

C661

22u_6.3V_ X5R_08

VGA_PEXCLK#19

PEG_TX#12

PEG_TX#32

PEG_TX#52

PEG_TX02

PEG_TX#62

3.3VS3,9,10,11,18,19,20,21,22,23,24,25,27,28,30,31,32,33,34,35,40

PEG_TX12

PEG_TX72

PEG_TX52

PEX_VDD13,37

PEG_TX22

PEG_TX62

VGA_PEXCLK19

PEG_TX#22

PEG_TX#42

PEG_TX32

3V3_RUN16,17, 37,42

PEG_TX#02

PEG_TX#72

PLT_RST#3,22,28

dGPU_RST#34

PEG_TX42

VGA_ROM_SO

VGA_ROM_SCLK

NEAR PIN AD8

NEAR PIN D7

PLACE NEAR GPU

VGA_ROM_CS#

VGA_ROM_SI

C11 0 .22u_10V_ X5R_04

C77

0.1u_10V_ X7R_04

R50 *34.8K_1%_04

C149

18p_50V_NPO_04

R71 10K_04

C49

0.1u_16V_Y5V_04

R92

10K_04

C108

*0.1u_16V_Y5V_04

C64

4.7u_6.3 V_X5R_06

C6 0.22u_10V_X5R_04

U1

MC74 VH C1G 08D FT2 G

1

2

5

4

3

C10 0 .22u_10V_ X5R_04

C50

1u_6.3V_X5R_04

R741 4. 99K_1%_0 4R743 *10K_04

C66

22u_6.3V _X5R_08

R13

100K_04

L1

HCB1005KF-121T20

C19 0 .22u_10V_ X5R_04

C657

1u_6.3V_X5R_04

C803

22u_6.3V_X5R_08

C14 0 .22u_10V_ X5R_04

C2

1u_6.3V_X5R_04

C27

0.1u_10V_X5R_04

C17 0 .22u_10V_ X5R_04

PEX_TSTCLK_OUT#

R54 *10K_04

C662

22u_6.3V _X5R_08

R17220_1%_04

PEX_TSTCLK_OUT

C15 0 .22u_10V_ X5R_04

R55 10K_04

R314 10K_04

C12 0 .22u_10V_ X5R_04

C658

4.7u_6.3V_X5R_06

PEG_RX7

PEG_RX#6

R62 40. 2K_1%_04

SNN_3V3AUX

PEG_RX#7

PEG_RX6

R47 * 4.99K_1%_0 4

C63

0.1u_10V_X7R_04

L4

HCB1005KF-121T20

C16 0 .22u_10V_ X5R_04

R83

*10K_04

Q15

MTN7002ZHS3

G

D S

C62

4.7u_6.3V_X5R_06

PEX_RX7

PEX_RX6

PEG_TX#7

PEG_TX6

PEX_RX7#

PEG_TX#6

PEX_RX6#

PEG_TX7

C67

10u_6.3V_ X5R_06

C9 0.22u_10V_X5R_04

C78

0.1u_10V_X7R_04

C75

22u_6.3V_X5R_08

R32 2. 49K_1%_04

R574

*10K_04

L3

FCM1005MF-300T03

Term

Near GPU

Under GPU

The total trace length measured

from GPU ball to capacitor is

no more than 150 mil

Descr iption

CLOSE TO CAPS

Common pads

13/19 M ISC2

U27P

bga_0908_p 080_p085_p10 0_290x290

COMMON

J1

MULTIS TRAP_REF _GND

J3

STRAP4

J5

STRAP3

J6

STRAP2

J7

STRAP1

J2

STRAP0

L3

CEC

L2

BUFRST

H4

ROM_SCLK

H7

ROM_SO

H5

ROM_SI

H6

ROM_CS

C35

22u_6.3V_ X5R_08

PLACE NEAR BGA

The total trace length measured

from GPU ball to capacitor is no

more than 850 mil

Midway between GPU and Power

Supply

R58 *10K_04

C33

10u_6.3V_ X5R_06

GND

H16

H5_0D4_4H6H5_0D4_4

H8

H5_0D4_4

1/19 PCI_EXPRESS

U27A

COMMON

bga_0908 _p080_p085_p 100_290x 290

AM27

PEX_RX15

AN27

PEX_RX15

AK25

PEX_TX15

AL25

PEX_TX15

AP27

PEX_RX14

AP26

PEX_RX14

AJ24

PEX_TX14

AK24

PEX_TX14

AM26

PEX_RX13

AN26

PEX_RX13

AG23

PEX_TX13

AH23

PEX_TX13

AM24

PEX_RX12

AN24

PEX_RX12

AJ23

PEX_TX12

AK23

PEX_TX12

AP24

PEX_RX11

AP23

PEX_RX11

AK22

PEX_TX11

AL22

PEX_TX11

AM23

PEX_RX10

AN23

PEX_RX10

AJ21

PEX_TX10

AK21

PEX_TX10

AM21

PEX_RX9

AN21

PEX_RX9

AG20

PEX_TX9

AH20

PEX_TX9

AP21

PEX_RX8

AP20

PEX_RX8

AJ20

PEX_TX8

AK20

PEX_TX8

AM20

PEX_RX7

AN20

PEX_RX7

AK19

PEX_TX7

AL19

PEX_TX7

AM18

PEX_RX6

AN18

PEX_RX6

AJ18

PEX_TX6

AK18

PEX_TX6

AP18

PEX_RX5

AP17

PEX_RX5

AG17

PEX_TX5

AH17

PEX_TX5

AM17

PEX_RX4

AN17

PEX_RX4

AJ17

PEX_TX4

AK17

PEX_TX4

AM15

PEX_RX3

AN15

PEX_RX3

AK16

PEX_TX3

AL16

PEX_TX3

AP15

PEX_RX2

AP14

PEX_RX2

AJ15

PEX_TX2

AK15

PEX_TX2

AM14

PEX_RX1

AN14

PEX_RX1

AG14

PEX_TX1

AH14

PEX_TX1

AM12

PEX_RX0

AN12

PEX_RX0

AJ14

PEX_TX0

AK14

PEX_TX0

AK13

PEX_REF CLK

AL13

PEX_REF CLK

AK12

PEX_CLKR EQ

AJ12