Page 1

5

4

3

2

1

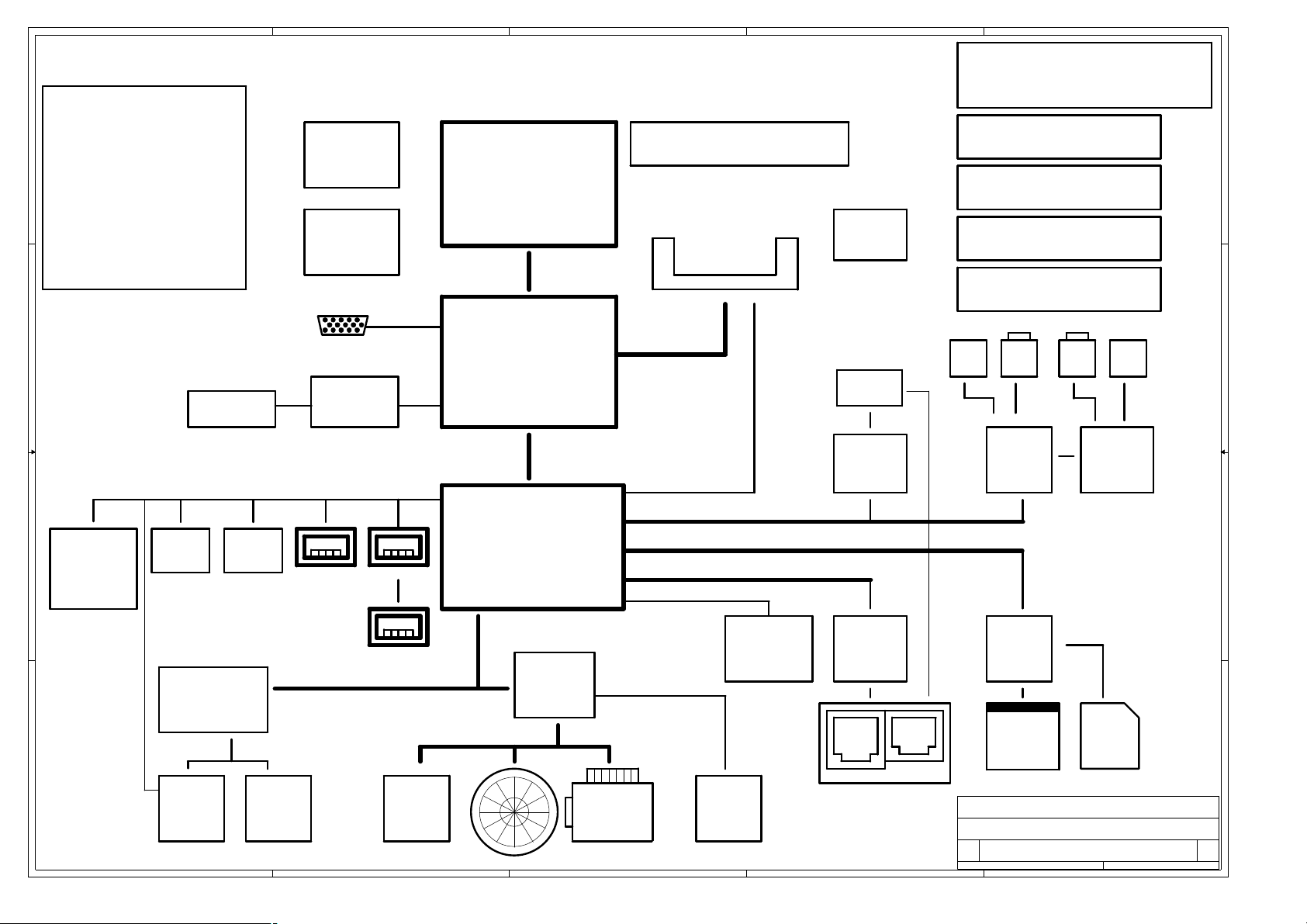

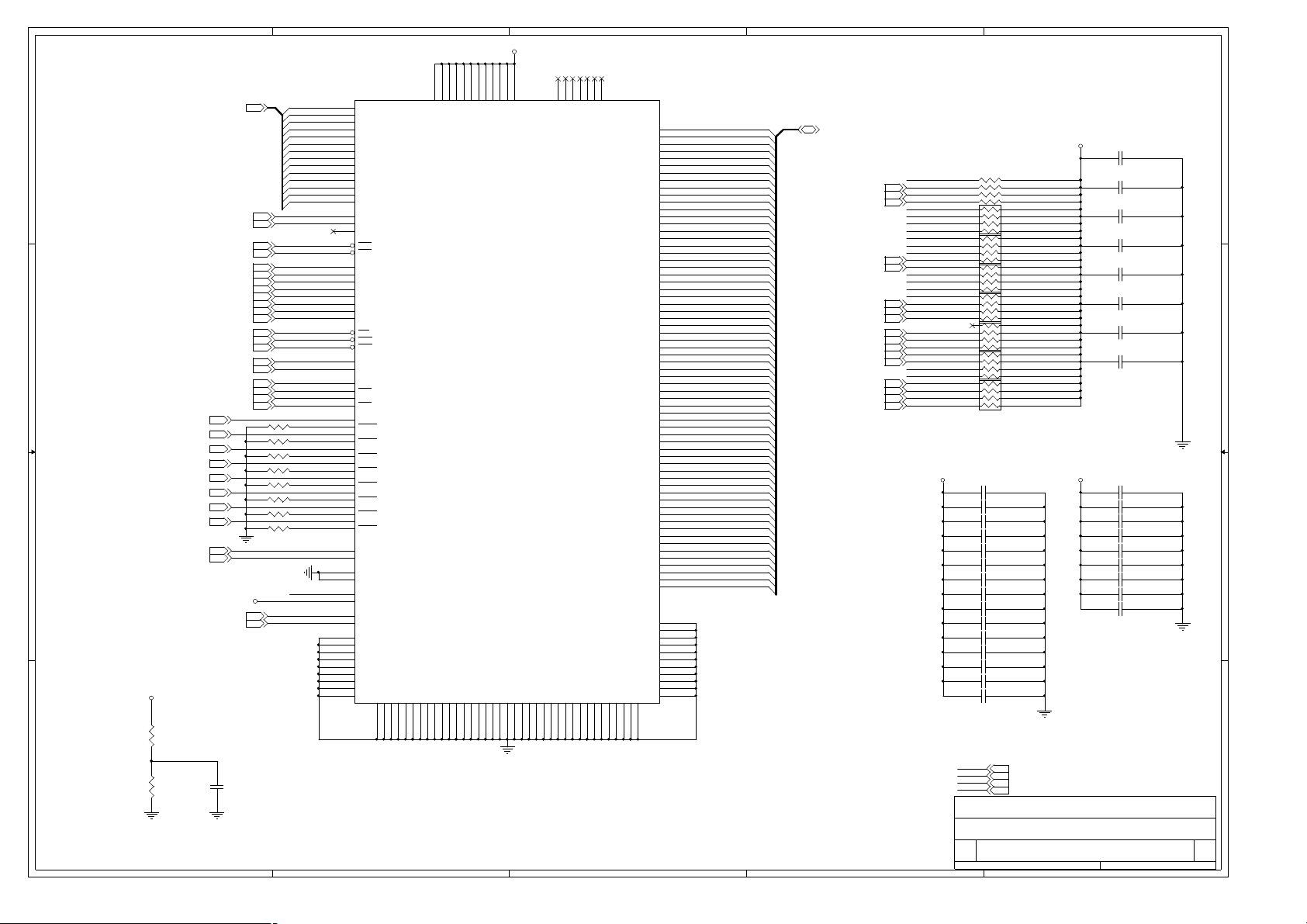

CLEVO TP80V System Block Diagram

1.3.3V,5V,2.5V

2.1.5VS,2.5VS,3.3VS,5VS

SHEET 27

1.Power switch

2.Pop menu switch

D D

3.5 direct key

4.W/LAN ON SWITCH

5.RESET SWITCH

6.HDD/BAT/POWER LED

7.WLAN / BT LED

SHEET 26

MAIN CLOCK

ICS952906

SHEET 9

CLOCK

BUFFER

ICS9P936

SHEET 9

VIA

C7-M

PROCESSOR

nanoBGA2

SHEET 2,3

FSB

MEMORY TERMINATIONS

SHEET 8

DDR2 SDRAM SOCKET

SO-DIMM0

SHEET 8

DDR VR

SHEET 28

CRT

VTT_MEM,1.8V

SHEET 28

VCORE

SHEET 29

1.5V,VCCP

SHEET 30

VDD3,VDD5

SHEET 31

NB

C C

LCD CONN

(LVDS)

SHEET 10 SHEET 4,5,6,7

SHEET 21

LVDS

VT1634AL

SHEET 11

VN800

567 HSBGA

VLINK 533MB/sec

USB2.0

533MHz

SM BUS

JMODEM1

SHEET 18

MDC

MODULE

SHEET 15

INT.

MIC

MIC

IN

CODEC

VT1613

SHEET 22

HP

OUT

AUDIO

AMP.

APA2020A

SHEET 23

INT.

SPK

SHEET 33

3

AC97 LINK

PCI BUS

MII

SPI

CONNECTOR

SPI

ROM

SHEET 19

33MHz

SATA HDD

SHEET 16

PHY

VT6103

SHEET 18

RJ-45

SHEET 18

2

RJ-11

PCMCIA

ENE

CB714B

SHEET 24

PCMCIA

SOCKET*1

SHEET 25

藍 天 電 腦 CLEVO CO.

Title

[01]BLOCK DIAGRAM

Size Document Number Rev

Custom

3843

Date: Sheet of

3 IN 1

CARD

READER

SHEET 25

6-71-T80V0-D02

1 33Saturday, June 02, 2007

1

1.0

SB

MINI PCIE

B B

W/LAN

802.11 b/g

SHEET 15

CCD

SHEET 19

BT

SHEET 15

MINI

USB

USB 0

USB 1

SHEET 16

SUPER I/O

VT1211

SHEET 33

A A

COM PORT

GPS

SHEET 33

5

Touch

Panel

SHEET 17

SM BUS

TEMP

SENSOR

ADM1032

SHEET 2

4

VT8237R+

539 BGA

SHEET 12,13,14

LPC

KBC

ITE 8512

SHEET 20

CPU FAN

SHEET 10

SMART

BATTERY

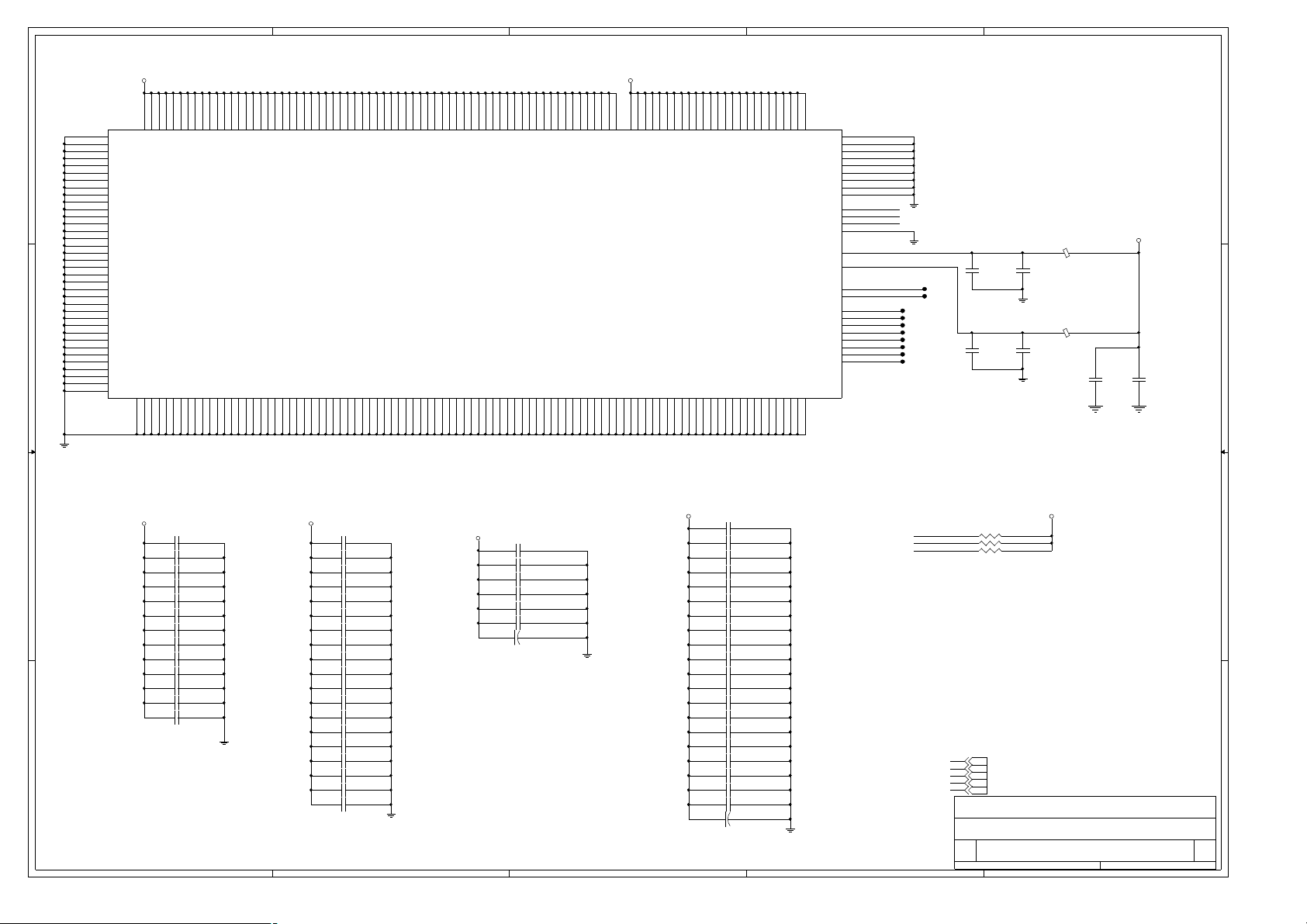

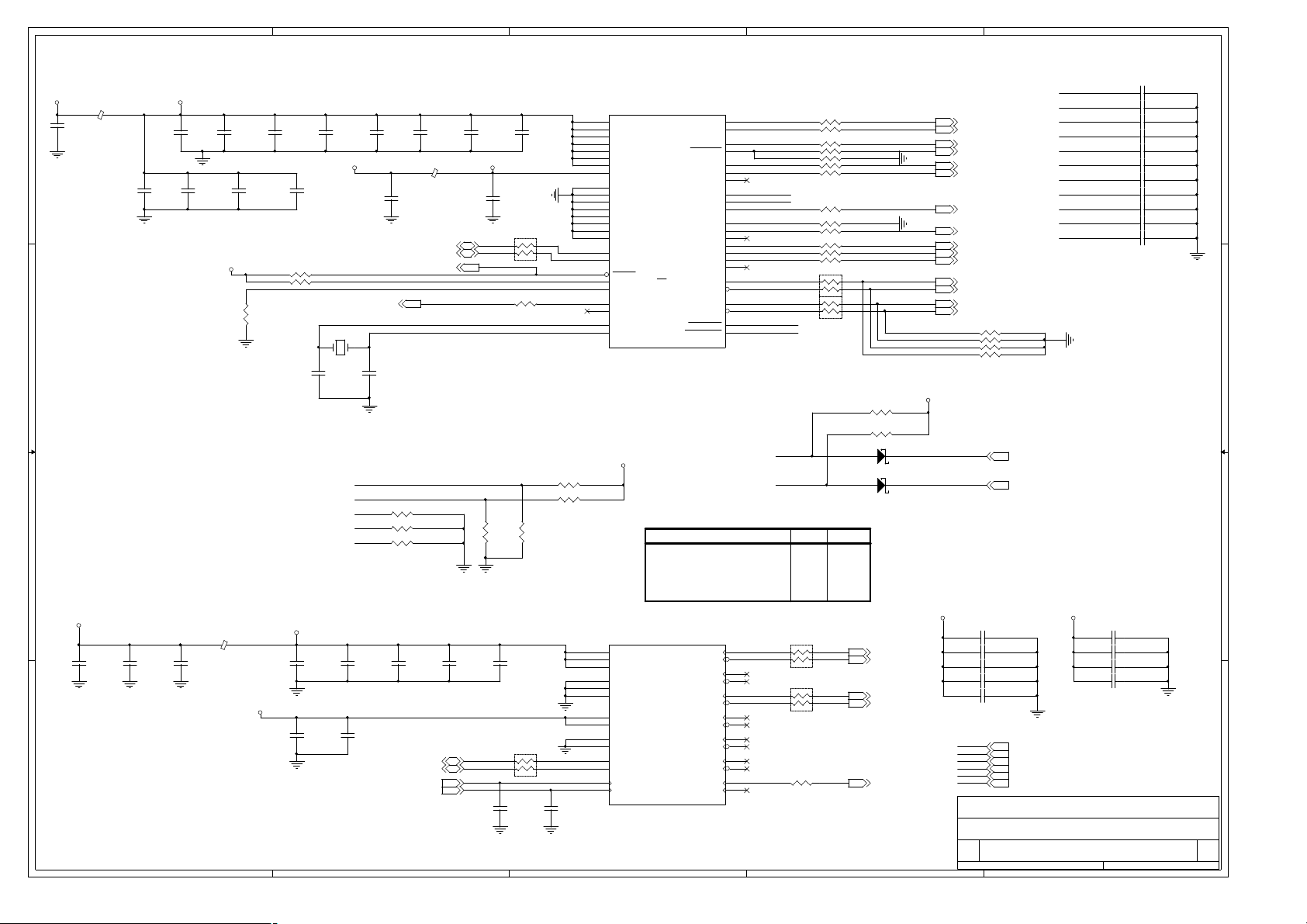

Page 2

H_A#[18:3]4

D D

H_A#304

H_D#[63:0]4

C C

B B

A A

5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#30

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

5

G20

G18

D20

H18

U19

M20

K19

K20

N20

R19

P19

P18

U18

W20

M19

T18

R20

Y12

Y17

W17

Y19

W18

W12

Y14

Y13

Y16

W14

Y11

W10

F3

H3

J1

F2

J2

K1

G3

K3

L2

L3

J3

M3

L1

M1

N2

N3

N1

A20

F18

D18

C19

E18

H20

C20

C18

B19

E20

J18

F20

L19

L18

V19

V13

V16

V18

V12

V14

Y8

V10

W4

W7

Y9

W8

W5

V6

V9

V3

Y3

Y4

V7

V4

V8

U25A

A3#

A4#

A5#

A6#

A7#

A8#

A9#

A10#

A11#

A12#

A13#

A14#

A15#

A16#

A17#

A18#

A30#

21X21

NANO

BGA

D0#

D1#

D2#

D3#

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

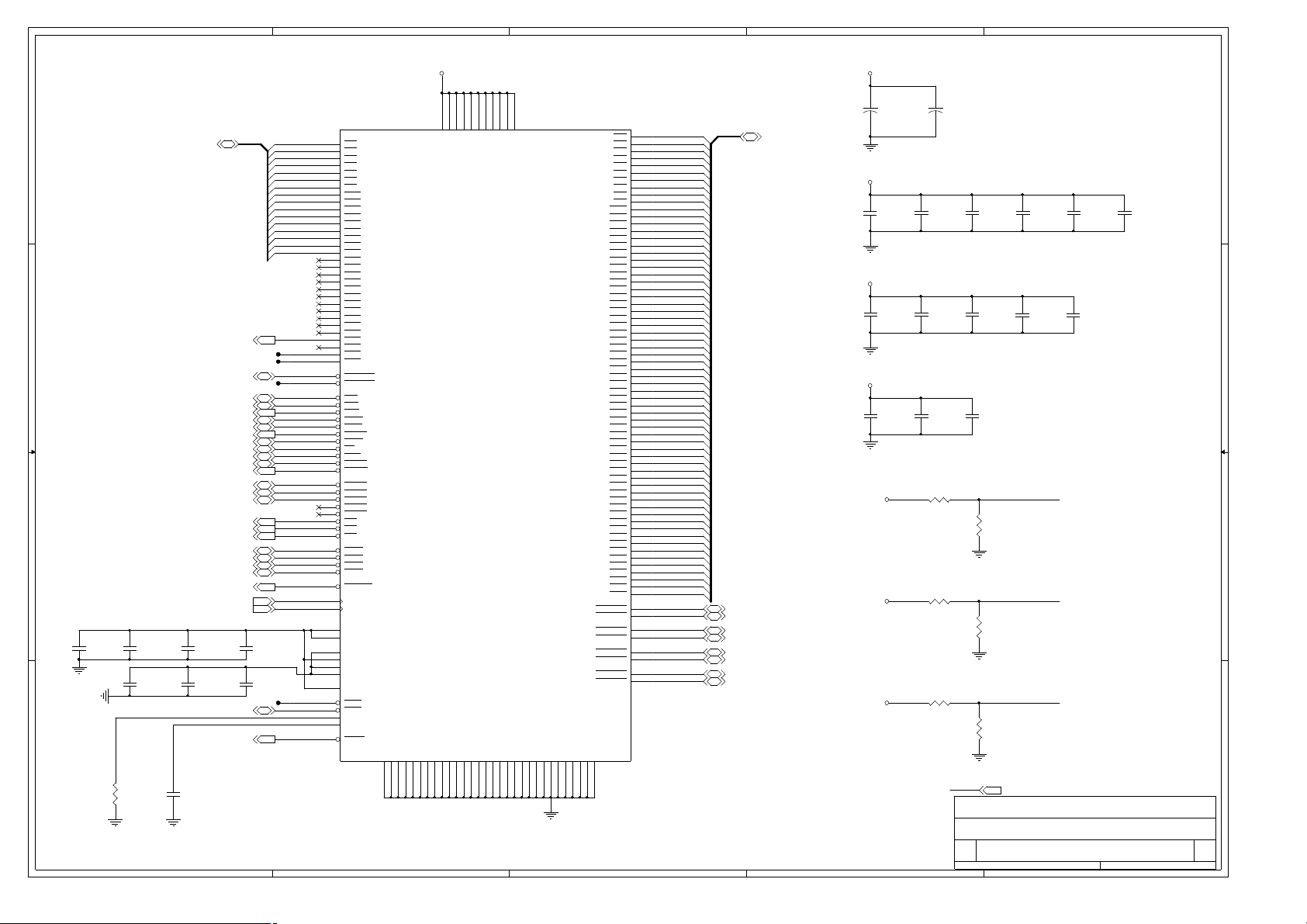

C7-M ULV 770

A20M#

FERR#

INIT#

INTR

IGNNE#

SMI#

SLP#

STPCLK#

DPWR#

ADS#

BNR#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

TRDY#

BPRI#

BREQ0#

BREQ1#

BREQ2#

BREQ3#

LOCK#

REQ0#

REQ1#

REQ2#

RS0#

RS1#

RS2#

ASTBN0#

ASTBP0#

DSTBP0#

DSTBN0#

DSTBP1#

DSTBN1#

DSTBP2#

DSTBN2#

DSTBP3#

DSTBN3#

BCLK

BCLK#

BSEL0

BSEL1

RESET#

PWRGD

PSI#

COMP0

COMP2

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

DP0#

DP1#

DP2#

DP3#

DPSLP#

TDO

TMS

TRST#

TCK

VID0

VID1

VID2

VID3

VID4

VID5

DINV3#

DINV2#

DINV1#

DINV0#

NMI

MPI

TDI

H_A20M#

B9

FERR#

A8

H_INIT#

A10

H_INTR

B8

H_NMI

C9

H_IGNNE#

D9

H_SMI#

C10

H_CPUSLP#

A11

H_STPCLK#

B10

A18

B1

D3

A1

A2

A4

B3

C3

B2

C4

H_BREQ#0

C1

H_BREQ#1

U1

H_BREQ#2

C5

H_BREQ#3

D5

D4

D1

D2

F1

B4

A3

E3

G1

G2

E19

F19

U20

T20

W15

V15

Y6

Y5

A14

A13

CPU_BSEL0

C14

CPU_BSEL1

D14

H_CPURST#

C13

H_PWRGD

C8

H_PSI#

C7

COMP0

H17

COMP2

T3

U5

H_THERMDA

C17

H_THERMDC

A17

PM_THERMTRIP#

A16

H_PROCHOT#

B18

DP#0

J20

DP#1

R18

DP#2

V11

DP#3

Y10

H_DPSLP#

B11

H_TDI

C15

H_TDO

A15

H_TMS

B15

H_TRST#

B16

H_TCK

C16

B7

C6

A7

B6

A6

A5

H_DBI#3

V5

H_DBI#2

V17

H_DBI#1

N18

H_DBI#0

H19

4

H_A20M#14

H_INIT#14

H_INTR14

H_NMI14

H_IGNNE#14

H_SMI#14

H_CPUSLP#14

H_STPCLK#14

H_DPWR#4

H_ADS#4

H_BNR#4

H_DBSY#4

H_DEFER#4

H_DRDY#4

H_HIT#4

H_HITM#4

H_TRDY#4

H_BPRI#4

H_BREQ#04

H_LOCK#4

H_REQ#04

H_REQ#14

H_REQ#24

H_RS#04

H_RS#14

H_RS#24

H_ADSTB#14

H_ADSTB#04

H_DSTBP#04

H_DSTBN#04

H_DSTBP#14

H_DSTBN#14

H_DSTBP#24

H_DSTBN#24

H_DSTBP#34

H_DSTBN#34

CLK_CPU_BCLK9

CLK_CPU_BCLK#9

H_CPURST#4

H_PWRGD21

The resistors need to place within

200mil of the processor.

H_DPSLP#14

H_VID029

H_VID129

H_VID229

H_VID329

H_VID429

H_VID529

H_DBI#34

H_DBI#24

H_DBI#14

H_DBI#04

4

COMP0 COMP2

18 MILS

WIDE

3.3V

H_STPCLK#

H_SMI#

H_CPUSLP#

H_DPSLP#

H_IGNNE#

H_A20M#

H_NMI

H_INIT#

H_PROCHOT#

H_INTR

H_BREQ#1

H_BREQ#2

H_BREQ#3

H_PSI#

FERR#

PM_THERMTRIP#

H_BREQ#0

H_PWRGD

H_CPURST#

H_TDI

H_TDO

H_TMS

COMP0

COMP2

H_TCK

H_TRST#

C78 .1u_X7R_04

R59 100K_04

R27 150_04

R23 150_04

R30 150_04

R31 150_04

R22 150_04

R24 150_04

R28 150_04

R25 150_04

R37 200_1%_04

R19 150_04

R9 100_04

R15 100_04

R11 100_04

R16 51.1_1%_04

R21 51.1_1%_04

R40 51.1_1%_04

R12 220_04

R18 200_1%_04

R43 51.1_1%_04

R34 150_04

R33 150_04

R38 39_04

R42 27.4_1%_04

R10 27.4_1%_04

R35 27.4_1%_04

R39 680_1%_06

Q8

AO3409

G

Layout Note:

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil

spacing.

Z0206

G

R51

20K_1%_04

Z0207

DS

Q9

2N7002

3

VCCP

FERR#

VCCP

VCCP

VCCP

VCCP

Z0205

DS

R48 0_04

VCCP

3.3V

R46

*0_04

R47

100K_04

H_THERMDA

H_THERMDC

R20 10K_04

RESET_NB#6,12

C72

1u_10V_06

C71

1000p_X7R_04

2

Q3

2N3904

E C

B

Z0201

R36 330_1%_06

V_THRM

U1

1

VDD

2

D+

3

D-

5

GND

ADM1032ARM

R53

10K_04

2.5VS

R17

10K_04

H_FERR#14

VCCP

R44

1.3K_1%_04

Z0202PM_THERMTRIP#

C56

*.1u_10V_04

RESET_NB# Z0204

THERM

ALERT

SDATA

SCLK

Z0208

4

Z0209

6

7

8

B

E C

R45 1K_04

R54 0_04

R56 *0_04

Q4

2N3904

Z0203

R58

4.7K_04

VDD3

B

B

R57

4.7K_04

Q5

2N3904

E C

Z0210

Q6

2N3904

E C

R55

*10K_04

D1 SCS751V-40

1

THERMTRIP#31

AC

PM_THRM#13

THERM_ALERT#20

SMD_THERM20THERM_RST#20

SMC_THERM20

Layout Note:

Near to Thermal

IC

3.3V12..15,17..21,27..29

VDD310,14,20,27,31,32

VCCP3,4,29,30

2.5VS9,11..14,27

3.3VS6..16,20..22,24..27,29,30,33

藍 天 電 腦 CLEVO CO.

Title

[02]PROCESSOR1/2

Size Document Number Rev

A3

3843

3

2

Date: Sheet of

6-71-T80V0-D02

2 33Saturday, June 02, 2007

1

1.0

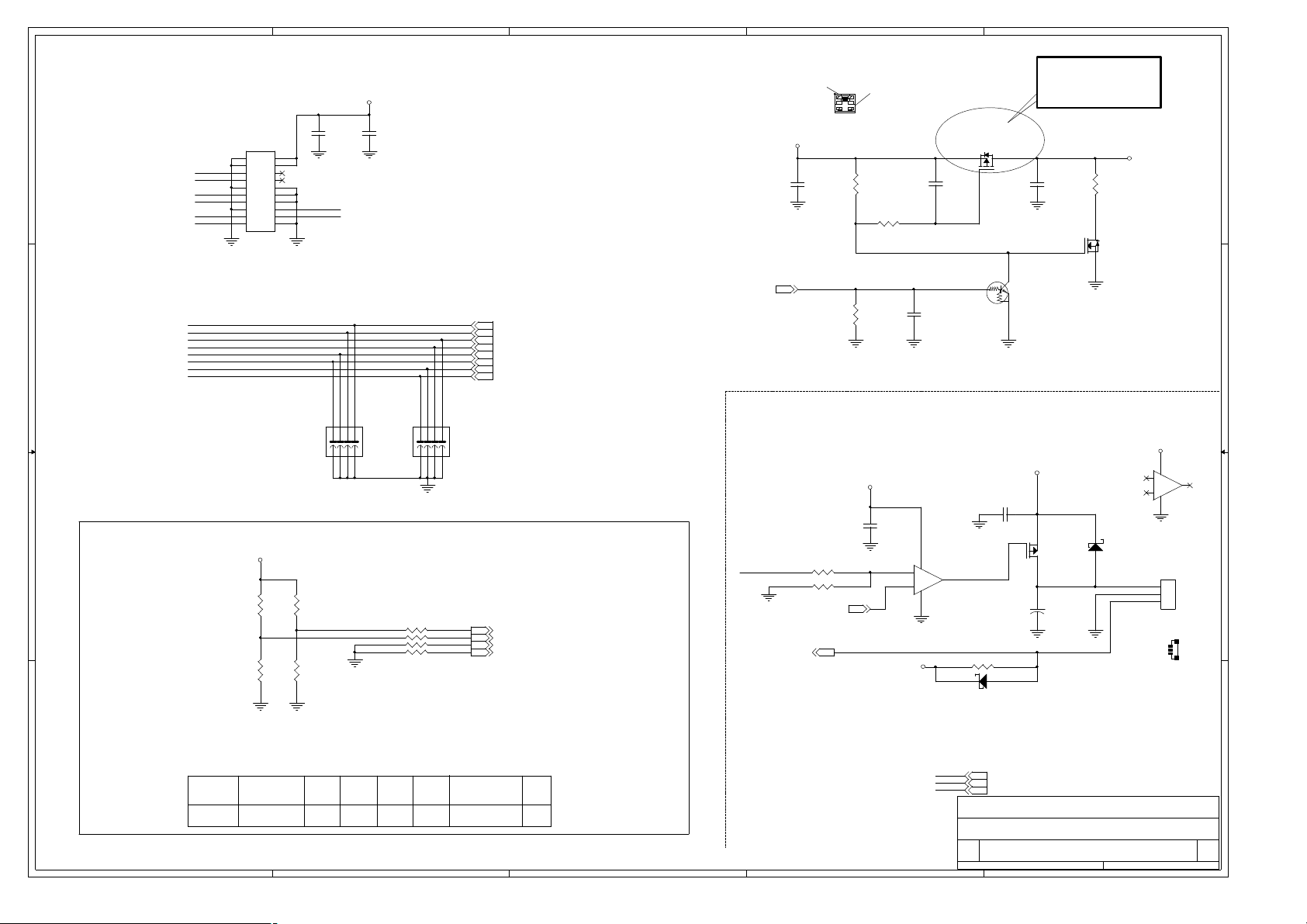

Page 3

5

4

3

2

1

VCC_CORE61

VCC_CORE62

VCC_CORE63

VCC_CORE64

VCC_CORE65

GND

GND

GND

GND

GND

VCCP

E16V1V2E8W2

VCCP1

VCCP2

VCCP3

VCC_CORE66

GND

GND

GND

GND

GND

3

G17

L17

R17

U17

E12

U14

U11U8G4L4R4P5K17D8D12

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

L20

P20

V20

D19

G19

J19

N19

T19

W19

K18

M18

VCCP VCCP

C62 .1u_10V_04

C17 .1u_10V_04

C25 .1u_10V_04

C16 .1u_10V_04

C8 .1u_10V_04

C14 .1u_10V_04

C64 .1u_10V_04

C67 .1u_10V_04

C63 .1u_10V_04

C33 .1u_10V_04

C15 .1u_10V_04

C50 .1u_10V_04

C10 .1u_10V_04

C45 .1u_10V_04

C57 .1u_10V_04

CT10 10u_10V_08

CT7 10u_10V_08

CT8 10u_10V_08

CT9 10u_10V_08

+

C492 100u_6.3V_B

VCCP17

GND

Y18

A19

VCCP18

VCCP19

GND

GND

D17

E17

VCCP20

VCCP21

GND

GND

J17

M17

D16

U13

VCCP22

VCCP23

GND

GND

N17

P17

U9

CF0

CF1

CF2

VCCP24

VCCP25

CF3

CF4

CF5

CF6

CF7

CF8

BEVO0

BEVO1

BEVO2

BEVO3

VCCA0

VCCA1

VCCSENSE

VSSSENSE

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

GND

GND

T17

P1

R1

T1

P2

R2

T2

P3

R3

P4

B12

C12

C11

D11

F17

A9

U3

U4

E1

B5

N4

B17

Y20

U2

W1

Y1

BEVO0

BEVO1

BEVO2

CPUVCCA0

CPUVCCA1

VCCSENSE

VSSSENSE

Z0301

Z0302

Z0303

Z0304

Z0305

Z0306

Z0307

Z0308

2

C68

.1u_10V_04

C39

.1u_10V_04

BEVO0

R32 200_1%_04

BEVO1

R29 200_1%_04

BEVO2

R26 200_1%_04

1.5VS6,11,19,27

VCORE29

VCCP2,4,29,30

3.3V2,12..15,17..21,27..29

3.3VS6..16,20..22,24..27,29,30,33

Title

Size Document Number Rev

A3

3843

Date: Sheet of

C74

1u_10V_06

1.5VS

C73

1000p_X7R_04

L9

HCB1608KF-121T25

C69

10u_10V_08

C49

10u_10V_08

12

L7

HCB1608KF-121T25

12

藍 天 電 腦 CLEVO CO.

[03]PROCESSOR 2/2

6-71-T80V0-D02

3 33Saturday, June 02, 2007

1

1.0

VCORE

G16

J16

L16

N16

R16

F15

H15

K15

M15

P15

T15

E14

G14

J14

L14

N14

R14

F13

H13

K13

M13

P13

T13

G12

J12

L12

N12

R12

F11

H11

K11

M11

P11

T11

E10

G10

J10

L10

N10

U25B

F16

GND

D D

C C

B B

A A

M16

U16

W16

G15

N15

R15

U15

H14

M14

D15

G13

N13

R13

W13

H12

M12

H16

GND

K16

GND

GND

P16

GND

T16

E15

J15

L15

Y15

F14

K14

P14

T14

E13

J13

L13

B14

F12

K12

P12

VCC_CORE1

VCC_CORE2

VCC_CORE3

VCC_CORE4

VCC_CORE5

VCC_CORE6

VCC_CORE7

VCC_CORE8

GND

VCC_CORE9

VCC_CORE10

VCC_CORE11

GND

GND

GND

GND

GND

GND

GND

GND

E11

G11

J11

L11

N11

R11

W11

A12

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

C7-M ULV 770

GND

GND

GND

GND

GND

GND

GND

T12

U12

B13

D13

VCORE VCORE

C22 .1u_10V_04

C53 .1u_10V_04

C52 .1u_10V_04

C13 .1u_10V_04

C66 .1u_10V_04

C61 .1u_10V_04

C34 .1u_10V_04

C28 .1u_10V_04

C41 .1u_10V_04 C24 .1u_10V_04

C55 .1u_10V_04

C38 .1u_10V_04

C23 .1u_10V_04

5

VCC_CORE12

VCC_CORE13

VCC_CORE14

VCC_CORE15

VCC_CORE16

VCC_CORE17

VCC_CORE18

VCC_CORE19

VCC_CORE20

VCC_CORE21

VCC_CORE22

VCC_CORE23

VCC_CORE24

VCC_CORE25

VCC_CORE26

VCC_CORE27

VCC_CORE28

VCC_CORE29

VCC_CORE30

VCC_CORE31

VCC_CORE32

VCC_CORE33

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

F10

H10

K10

M10

P10

T10

U10E9G9J9L9N9R9W9D10F8H8K8M8P8T8E7G7J7L7N7R7U7Y7F6H6K6M6P6T6U6W6E5G5J5L5N5R5D7E4F4H4J4K4M4T4M2D6W3K2H2E2C2H1Y2B20

C21 .1u_10V_04

C32 .1u_10V_04

C58 .1u_10V_04

C9 .1u_10V_04

C65 .1u_10V_04

C59 .1u_10V_04

C11 .1u_10V_04

C26 .1u_10V_04

C60 .1u_10V_04

C47 .1u_10V_04

C31 .1u_10V_04

C51 .1u_10V_04

C42 .1u_10V_04C29 .1u_10V_04

C43 .1u_10V_04

C44 .1u_10V_04

C46 .1u_10V_04

C30 .1u_10V_04

C37 .1u_10V_04

C54 .1u_10V_04

R10F9H9K9M9P9T9G8J8L8N8R8F7H7K7M7P7T7E6G6J6L6N6R6H5K5T5M5F5

VCC_CORE34

VCC_CORE35

VCC_CORE36

VCC_CORE37

VCC_CORE38

VCC_CORE39

VCC_CORE40

VCC_CORE41

VCC_CORE42

VCC_CORE43

VCC_CORE44

VCC_CORE45

VCC_CORE46

VCC_CORE47

VCC_CORE48

VCC_CORE49

VCC_CORE50

VCC_CORE51

VCC_CORE52

VCC_CORE53

VCC_CORE54

VCC_CORE55

VCC_CORE56

21X21

NANO BGA

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VCORE

CT2 *10u_10V_08

CT1 *10u_10V_08

CT5 *10u_10V_08

CT6 *10u_10V_08

CT3 10u_10V_08

CT4 10u_10V_08

+

1 2

C638 *470u_2.5V_D

4

VCC_CORE57

VCC_CORE58

VCC_CORE59

VCC_CORE60

GND

GND

GND

GND

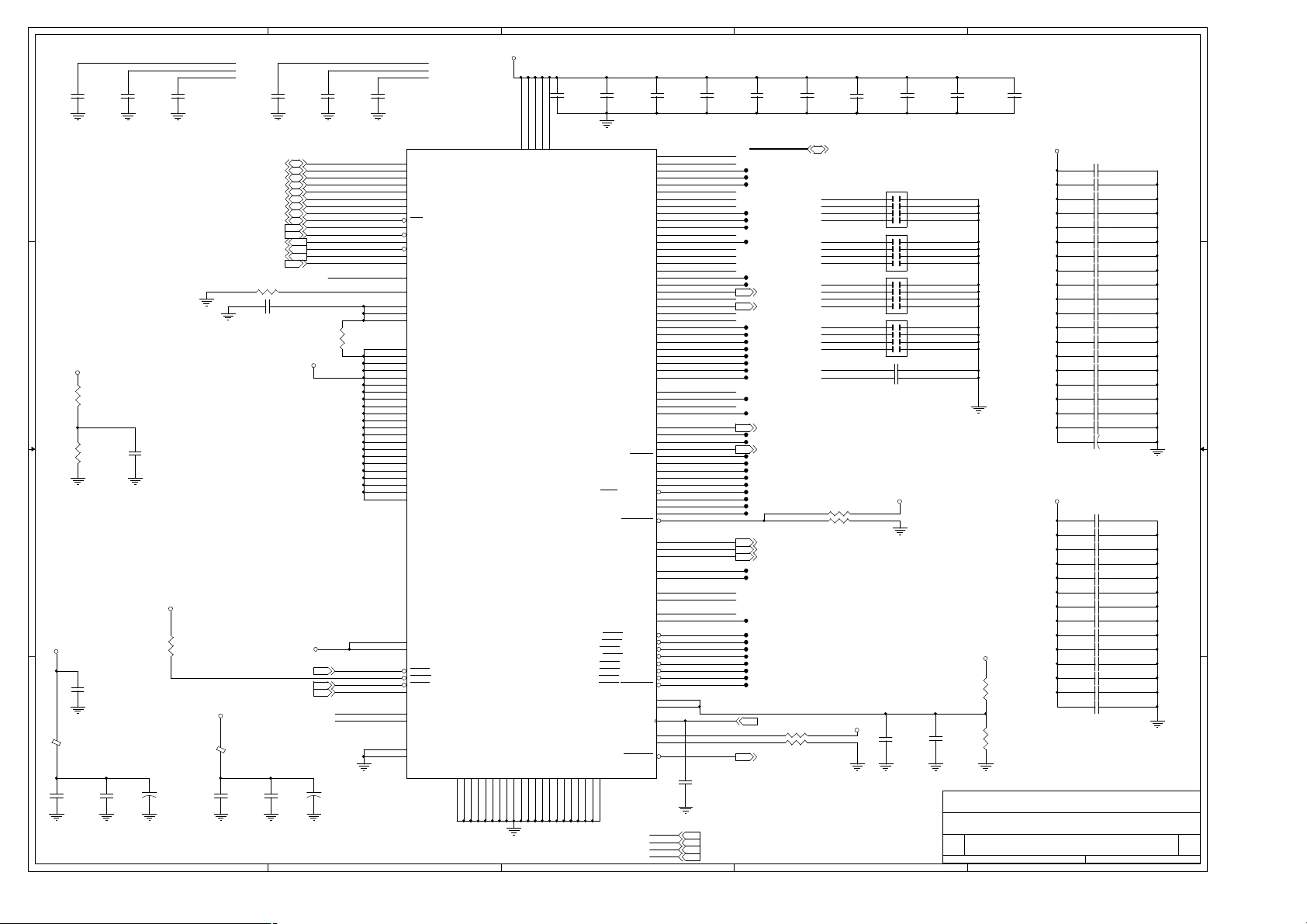

Page 4

5

4

3

2

1

VCCP

U19

T19

R19

P19

N19

M19

L19

L18

L17

L16

L15

GND

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

HDSTB0P

HDSTB0N

HDSTB1P

HDSTB1N

HDSTB2P

HDSTB2N

HDSTB3P

HDSTB3N

GND

GND

GND

GND

AC28

T18

U18

V18

VTT

VTT

VTT

VTT

VTT

VTT

VTT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

H26

H29

L25

L28

P25

P28

U28

U25

Y25

Y28

N18

P18

R18

M18

H_D#0

D27

H_D#1

D26

H_D#2

A29

H_D#3

C26

H_D#4

C28

H_D#5

D28

H_D#6

A27

H_D#7

B29

H_D#8

A26

H_D#9

B26

H_D#10

D25

H_D#11

E24

H_D#12

A25

H_D#13

A28

H_D#14

D24

H_D#15

C25

H_D#16

K28

H_D#17

K29

H_D#18

J28

H_D#19

K27

H_D#20

J26

H_D#21

J29

H_D#22

J25

H_D#23

J27

H_D#24

F28

H_D#25

G29

H_D#26

G27

H_D#27

D29

H_D#28

E27

H_D#29

F27

H_D#30

E28

H_D#31

F29

H_D#32

E23

H_D#33

B24

H_D#34

C24

H_D#35

A24

H_D#36

A23

H_D#37

B23

H_D#38

A22

H_D#39

C23

H_D#40

F21

H_D#41

C22

H_D#42

E21

H_D#43

C21

H_D#44

D20

H_D#45

D21

H_D#46

F20

H_D#47

E20

H_D#48

B19

H_D#49

C19

H_D#50

B20

H_D#51

B18

H_D#52

C20

H_D#53

A20

H_D#54

C18

H_D#55

B17

H_D#56

B16

H_D#57

A17

H_D#58

C14

H_D#59

C15

H_D#60

A18

H_D#61

B15

H_D#62

B14

H_D#63

A15

B27

C27

H28

G28

D23

D22

C17

C16

3

H_D#[63:0]2

H_DSTBP#02

H_DSTBN#02

H_DSTBP#12

H_DSTBN#12

H_DSTBP#22

H_DSTBN#22

H_DSTBP#32

H_DSTBN#32

AA29

AC27

AA28

AB27

AA27

AC29

AB29

AB28

AC26

AD29

R28

N29

N28

R27

N26

R25

N27

N25

R29

U26

W28

R26

M29

M28

M25

U27

M26

U29

M24

W27

W29

M27

C29

H27

D14

W23

R24

G24

N24

W26

G25

G26

Y29

V27

Y27

Y26

T28

P29

P27

T26

P26

T27

T25

T29

K26

L27

L29

V28

V26

V29

L26

K25

B21

A21

Y23

V24

F22

F19

F16

L24

K24

U27A

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HA32

HA33

HADSTB0

HADSTB1

ADS

BNR

BPRI

BREQ

DBSY

DEFER

DRDY

HIT

HITM

HLOCK

HTRDY

HREQ0

HREQ1

HREQ2

HREQ3

HREQ4

RS0

RS1

RS2

HDBI0

HDBI1

HDBI2

HDBI3

CPURST

HCLK+

HCLK-

HAVREF0

HAVREF1

HDVREF0

HDVREF1

HDVREF2

HDVREF3

GTLVREF

HAP0

HAP1

HRCOMP

HCOMPVREF

DPWR

VN800

VTT

VTT

VTT

VTT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

E29

E26

E25

E22

B25

B28

D16

D19

B22

D15

GND

A16

A19

4

C106

.01u_16V_04

C169

.01u_16V_04

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#30

Z0401

Z0402

Z0403

H_REQ#0

H_REQ#1

H_REQ#2

H_DBI#0

H_DBI#1

H_DBI#2

H_DBI#3

Z0404

H_DPWR#

D D

C C

B B

C107

.01u_16V_04

A A

C104

.01u_16V_04

C121

.01u_16V_04

HRCOMP

R73

20.5_1%_06

5

H_A#[18:3]2

H_CPURST#2

GTLVREF_NB

C105

.01u_16V_04

GTLVREF_NB1

C132

.01u_16V_04

HCOMPVREF

C98

.01u_16V_04

H_A#302

H_ADSTB#02

H_ADS#2

H_BNR#2

H_BPRI#2

H_BREQ#02

H_DBSY#2

H_DEFER#2

H_DRDY#2

H_HIT#2

H_HITM#2

H_LOCK#2

H_TRDY#2

H_REQ#02

H_REQ#12

H_REQ#22

H_RS#02

H_RS#12

H_RS#22

H_DBI#02

H_DBI#12

H_DBI#22

H_DBI#32

H_CLK+9

H_CLK-9

H_ADSTB#12

H_DPWR#2

VCCP

+

VCCP

.01u_16V_04

VCCP

1000p_X7R_04

VCCP

10u_10V_08

VCCP

VCCP

VCCP

2

C97

100u_6.3V_B

C143

C188

C176

NEED CLOSEST N.B

C194

+

100u_6.3V_B

C144

.01u_16V_04

C141

.01u_16V_04

22UF M 6.3V08-22611-2B1

C142

1000p_X7R_04

C123

10u_10V_08

R102 49.9_1%_04

R78 49.9_1%_04

R69 100_1%_04

C172

1000p_X7R_04

C155

10u_10V_08

Title

Size Document Number Rev

Custom

3843

Date: Sheet of

C140

.01u_16V_04

C154

.1u_10V_04

GTLVREF_NB1

R97

100_1%_04

GTLVREF_NB

R76

100_1%_04

HCOMPVREF

R70

49.9_1%_04

VCCP2,3,29,30

C163

.01u_16V_04

C139

.1u_10V_04

藍 天 電 腦 CLEVO CO.

[04]VN800 1/4

6-71-T80V0-D02

1

C145

.01u_16V_04

1.0

4 33Saturday, June 02, 2007

Page 5

5

1.8V

4

3

1.8V

2

1

C158

C181

1.8V

1.8V

2

10u_10V_08

C147

.01u_16V_04

R115

150_1%_04

MVREF_NB

R104

150_1%_04

CS0#

CS1#

CS2#

CS3#

1u_10V_06

D D

MD_[0:63]8

C C

B B

CKEA08

CKEA18

CKEA28

CKEA38

DQM0#8

DQM1#8

DQM2#8

DQM3#8

DQM4#8

DQM5#8

DQM6#8

DQM7#8

A A

MD_0

MD_1

MD_2

MD_3

MD_4

MD_5

MD_6

MD_7

MD_8

MD_9

MD_10

MD_11

MD_12

MD_13

MD_14

MD_15

MD_16

MD_17

MD_18

MD_19

MD_20

MD_21

MD_22

MD_23

MD_24

MD_25

MD_26

MD_27

MD_28

MD_29

MD_30

MD_31

MD_32

MD_33

MD_34

MD_35

MD_36

MD_37

MD_38

MD_39

MD_40

MD_41

MD_42

MD_43

MD_44

MD_45

MD_46

MD_47

MD_48

MD_49

MD_50

MD_51

MD_52

MD_53

MD_54

MD_55

MD_56

MD_57

MD_58

MD_59

MD_60

MD_61

MD_62

MD_63

CKEA0

CKEA1

CKEA2

CKEA3

5

AD28

AE27

AF27

AG28

AD27

AE29

AG27

AG29

AH29

AJ29

AG25

AJ25

AJ28

AH27

AH26

AJ26

AJ24

AG24

AJ22

AG21

AH24

AG23

AG22

AJ21

AH21

AJ20

AG18

AH18

AG20

AH19

AJ18

AG17

AJ12

AG12

AJ10

AH12

AJ11

AG10

U27B

AJ9

AH9

AG8

AJ7

AJ6

AH6

AG9

AJ8

AG5

AJ5

AH4

AJ4

AJ2

AH1

AG4

AF4

AG3

AJ1

AG1

AF2

VN800

4

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

BA0

BA1

DMCOMP

MEMDET

SRASA#

SCASA#

SWEA#

CS0#

CS1#

CS2#

CS3#

MCLKIT

M_CLKOM_CLKO+

MCLKO+/- as short as passable

MVREF_NB

MAA[0:13] 8

BA08

BA18

R135 301_1%_06

R79 4.7K_04

HI IS DDR2

ODT0 8

ODT1 8

ODT2 8

ODT3 8

SRASA# 8

SCASA# 8

SWEA#8

CS0#8

CS1#8

CS2#8

CS3#8

DQS0 8

DQS1 8

DQS2 8

DQS3 8

DQS4 8

DQS5 8

DQS6 8

DQS7 8

MCLKIT = DCLKx + 2 "

R72 22_04

R71 22_04

Near to NB chip,reserve for tunning!

MCLKIT

M_CLKO+

M_CLKO-

Test Point

(Place near their respective balls of NB)

3

1.8V

C99

*5p_50V_04

MCLKIT 9

MCLKOC 9

MCLKOT 9

Closed VN800

C184

1u_10V_06

C203

.01u_16V_04

C199

.01u_16V_04

C204

1u_10V_06

C174

1u_10V_06

MVREF_NB:Don't less than 10 miles

C249

1000p_X7R_04

C238

33p_50V_04

C215

1000p_X7R_04

C223

33p_50V_04

Title

Size Document Number Rev

Custom

3843

Date: Sheet of

C152

1000p_X7R_04

C218

33p_50V_04

1.8V6,8,9,28

藍 天 電 腦 CLEVO CO.

[05]VN800 2/4

6-71-T80V0-D02

C120

1000p_X7R_04

C237

33p_50V_04

1

5 33Saturday, June 02, 2007

1.0

Page 6

C277

*10p_50V_04

5

DNCMD

DNSTB

DNSTB#

C280

*10p_50V_04 1u_10V_06

C281

*10p_50V_04

C279

*10p_50V_04

C274

*10p_50V_04

4

UPSTB

UPCMD

UPSTB#

C278

*10p_50V_04

1.5VS

C229

.1u_10V_04

3

C197

.1u_10V_04

C137

.01u_16V_04

C205

.01u_16V_04

C124

1u_10V_06

C125

2

C85

4.7u_10V_08

C129

.1u_10V_04

C126

.1u_10V_04

1

C182

1000p_X7R_04

D D

C C

1.5VS

R138

1.4K_1%_04

LVREF_NB

R140

1K_1%_04

C254

.1u_10V_04

Reserve for Future

VLAD014

VLAD114

VLAD214

VLAD314

VLAD414

VLAD514

VLAD614

VLAD714

VBE#14

UPSTB14

UPSTB#14

DNSTB14

DNSTB#14

UPCMD14

DNCMD14

R145 402_1%_06

C212 .1u_10V_04

1.5VS

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

VBE#

UPSTB

UPSTB#

DNSTB

DNSTB#

UPCMD

DNCMD

LVREF_NB

LCOMPP

Z0607

R128

0_04

LVREF_NB is 0.625V

B B

Strapping For NB_TEST Mode

1.8V

C627

+

100u_6.3V_B

5

R77

1K_04

TESTIN_NB

3.3VS

C629

.1u_10V_04

12

L12

HCB1608KF-121T25

A A

C102

C103

1000p_X7R_04

1u_10V_06

TESTIN RBF WBF

1 x x

Disable all TEST mode

1.5V

SUS_ST#13

RESET_NB#2,12

PWROK_NB#13

3.3VS

12

L11

HCB1608KF-121T25

AVDD1AVDD2

C100

C101

1000p_X7R_04

1u_10V_06

C628

+

100u_6.3V_B

AVDD1

AVDD2

4

W10

AC25

AF25

AA25

AD25

AA26

AD24

V1

U2

Y2

Y3

T2

T3

AA2

AA1

U3

W2

W1

V2

V3

AA3

W3

V4

T4

U11

U10

V10

K10

K11

K12

K13

K15

K17

K19

K20

Y10

Y12

Y14

Y16

Y18

Y20

L10

N10

R10

M20

P20

T20

V20

AB1

AB3

AC1

AB2

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VD7

VBE

UPSTB+

UPSTBDNSTB+

DNSTBUPCMD

DNCMD

VLVREF

VLCOMPP

VCC15VL

VCC15VL

VCC15VL

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VSUS15

VSUS15

SUSST

TESTIN

RESET

PWROK

VCCA33HCK

VCCA33MCK

GNDAHCK

GNDAMCK

VN800

U27C

GND

GND

M12

M13

M14

GND

M11

N11

P11

R11

T11

VCC15AGP

VCC15AGP

VCC15AGP

VCC15AGP

VCC15AGP

GND

GND

GND

GND

GND

GND

GND

P13

N12

N13

N14

P12

GND

GND

GND

GND

GND

GND

P14

R12

T14

U12

T13

R13

R14

T12

U13

GD24/GDVP1D09

GD26/GDVP1D10

GD27/GDVP1D04

GD28/GDVP1D07

GD29/GDVP1D06

GD30/GDVP1D08

GD31/GDVP1DET

GC#BE1/SBPLDAT

GC#BE3/GDVP1D11

GIRDY/SBPLCLK

GDEVSEL/FPVS

GREQ/SBDDCCLK

GGNT/SBDDCDAT

GSBSTBF/GDVP1D01

GSBSTBS/GDVP1D02

GADSTBF0/FPD04

GADSTBS0/FPD02

GADSTBF1/FPD12

GADSTBS1/FPDET

GSBA0/GDVP1VS

GSBA1/GDVP1DE

GSBA2/GDVP1D00

GSBA3/GDVP1HS

GSBA4/GDVP1D05

GSBA5/GDVP1D03

GSBA6/GDVP1CLK

GSBA7/GDVP1CLK

GND

GND

GND

GND

GND

U14

V12

V13

V14

GD0/FPD10

GD1/FPD11

GD2/FP1CLK

GD3/FPD09

GD4/FPD08

GD5/FPD07

GD6/FPD06

GD7FPD05

GD8/FP1DET

GD9/FP1HS

GD10/FPD01

GD11/FPD23

GD12/FPD00

GD13/FPD22

GD14/FPD21

GD15/FPD20

GD16/FPD18

GD17/FPD17

GD18/FPD16

GD19/FPDE

GD20/FPD14

GD21/FPCLK

GD22/FPD13

GD23/FPD15

GD25

GC#BE0/FPD03

GC#BE2/FPD19

GFRAME/FPHS

GTRDY

GSTOP/FP1CLK

GPAR/FP1VS

GDBIH

GRBF

GWBF/FPCLK

GSERR/FP1DE

GDBIL

AGP8XDET

GST0/ENAVEE

GST1/ENAVDD

GST2/ENABLT

AGPVREF1

AGPVREF2

GCLK

AGPCOMPN

AGPCOMPP

AGPBUSY

3

FPD10

P3

FPD11

P4

Z0608

R3

FPD9

R4

FPD8

R1

FPD7

N2

FPD6

P1

FPD5

R2

Z0609

M3

Z0610

M1

FPD1

N4

FPD23

L3

FPD0

L1

FPD22

N5

FPD21

K2

FPD20

R6

FPD18

J2

FPD17

H3

FPD16

H1

FPDE

K4

FPD14

G1

G2

FPD13

K5

FPD15

G3

Z0611

J6

Z0612

K6

Z0613

J4

Z0614

F2

Z0615

J5

Z0616

F3

Z0617

H4

Z0618

E1

FPD3

M2

Z0619

K1

FPD19

J1

Z0620

L6

L4

Z0621

M5

Z0622

K3

J3

Z0623

M4

Z0624

P6

Z0625

G5

Z0626

F4

FPCLK_N

B3

Z0627

D5

Z0628

C4

Z0629

M6

Z0630

H6

AGP8XDET#

C5

AGP8xdet 0=enable

E4

E3

F5

Z0631

C1

Z0632

C2

FPD4

N1

FPD2

N3

FPD12

G4

Z0633

F1

Z0634

A1

Z0635

A2

Z0636

B1

Z0637

C3

Z0638

D1

Z0639

D4

Z0640

D2

Z0641

D3

N6

G6

AGPVREF1

R5

AGPCOMPN

A4

AGPCOMPP

A3

T1

C261

*5p_50V_04

3.3VS7..16,20..22,24..27,29,30,33

1.8V5,8,9,28

1.5V27,30

1.5VS3,11,19,27

Closed

VN800

FPD[0..23]

FPDE 11

FPCLK 11

FPHS 11

FPVS11

ENAVEE 11

ENAVDD 10

BLON 19

GCLK_NB 9

R433 60.4_1%_04

R441 60.4_1%_04

AGPBZ 14

FPD[0..23] 11

FPD20

FPD22

FPD13

FPD23

FPD5

FPD10

FPD11

FPD6

FPD19

FPD18

FPD14

FPD15

FPD4

FPD7

FPD21

FPD12

FPD3

FPD2

R431 4.7K_04

R429 *4.7K_04

1.5VS

2

CP1 *10p_12_8P4C

4 5

3

6

2

7

1

4 5

3

2

1

4 5

3

2

1

6

7

8

1.5VS

C252

.1u_10V_04

8

6

7

8

6

7

8

45

3

2

1

C256

10u_10V_08

Title

Size Document Number Rev

Custom

Date: Sheet of

CP3 *10p_12_8P4C

CP4 *10p_12_8P4C

CP2 *10p_12_8P4C

C276 *10p_50V_04

C275 *10p_50V_04

1.5VS

C211 2.2u_6.3V_06

C207 2.2u_6.3V_06

C192 2.2u_6.3V_06

C209 2.2u_6.3V_06

C208 2.2u_6.3V_06

C210 2.2u_6.3V_06

C122 4.7u_10V_08

C118 4.7u_10V_08

C153 .01u_16V_04

C149 .1u_10V_04

C128 .1u_10V_04

C127 .1u_10V_04

C131 .1u_10V_04

C234 .1u_10V_04

C241 4.7u_10V_08

C86 4.7u_10V_08

C242 4.7u_10V_08

C161 4.7u_10V_08

C136 4.7u_10V_08

+

C639 150u_4V_B

1.5VS

C232 .1u_10V_04

C233 .1u_10V_04

C228 .1u_10V_04

C230 .1u_10V_04

C231 .1u_10V_04

C200 .1u_10V_04

C165 .01u_16V_04

C216 .01u_16V_04

C160 .01u_16V_04

1.5VS

R139

10K_1%_04

R142

10K_1%_04

C214 .01u_16V_04

C219 .01u_16V_04

C220 .01u_16V_04

C226 .01u_16V_04

C227 .01u_16V_04

藍 天 電 腦 CLEVO CO.

[06]VN800 3/4

3843

6-71-T80V0-D02

1

6 33Saturday, June 02, 2007

1.0

Page 7

5

4

3

2

1

M11

M-MARK1

3.3VS

12

L17

HCB1608KF-121T25

C244

22u_6.3V_12

3.3VS

12

L21

HCB1608KF-121T25

C290

22u_6.3V_12

M10

M-MARK1

VCCPLL1

C243

1000p_X7R_04

C260

1000p_X7R_04

M14

M-MARK1

M6

M-MARK1

C236

1u_10V_06

C262

1u_10V_06

M13

M-MARK1

VCCPLL1

VCCPLL2

VCCDAC1

VCCDAC2

D D

LCDID010

LCDID110

LCDID210

LCDID310

C C

TVD11

TVD5

TVD4

TVD5

TVD6

TVD7

TVD8

TVD9

TVD10

TVD11

R130 *4.7K_04

R408 4.7K_04

R575 Place near to NB

VT1637-GPO0

VT1637GPOUT

Z0701

Z0702

Z0703

Z0704

Z0705

Z0706

R421 4.7K_04

R125 4.7K_04

C13

B13

A13

D13

E13

D12

C12

A12

B12

E12

B11

A11

E11

C11

A10

B10

E10

C10

D11

B9

VN800

U27D

DVP0D00/TVD00

DVP0D01/TVD01

DVP0D02/TVD02

DVP0D03/TVD03

DVP0D04/TVD04

DVP0D05/TVD05

DVP0D06/TVD06

DVP0D07/TVD07

DVP0D08/TVD08

DVP0D09/TVD09

DVP0D10/TVD10

DVP0D11/TVD11

GPO0

GPOUT

TVCLKR

DVP0DE/TVDE

DVP0HS/TVHS

DVP0VS/TVVS

DVP0CLK/TVCLK

DVP0DET

E7

D7

D8

C7

VCCA33PLL1

VCCA33PLL2

VCCA33DAC1

VCCA33DAC2

GND

GND

GND

GND

GND

GND

GND

GND

B4E2E5H2H5L2L5P2P5U1U4

B2

A14

L13

L12

L14

VCC33GFX

VCC33GFX

GND

GND

GND

GND

GND

Y1

GFX power up strapping setting:

SW3_2 DVP0D5/TVD5 =>Dedicated DVI Port Configuration

C175

.1u_10V_04

VCC33GFX

HSYNC

VSYNC

SPCLK1

SPCLK2

DISPCLKI

DISPCLKO

GNDAPLL1

GNDAPLL2

GNDADAC2

GNDADAC1

GND

RSET

INTA

SPD1

SPD2

3.3VS

B6

AR

A5

AG

B5

AB

A6

B8

A8

A7

XIN

A9

D9

E9

D10

E8

C8

C9

B7

C6

D6

E6

C167

.1u_10V_04

DAC_RED 21

DAC_GREEN 21

Trace width = 10 mils

RSET

R427 80.6_1%_04

GUICLK

SMBCK2

R134 10K_04

SMBDT2 VCCDAC1

R133 10K_04

Z0707

R424 22_04

DISPCLKI

DISPCLKO

This pin needs to be connected to GND, if spread

spectrum is not implemented.

R426

4.7K_04

DAC_BLUE 21

DAC_HSYNC 21

DAC_VSYNC 21

GUICLK 9

PCI_INTA# 12,24

3.3VS

DAC_DDCACLK 21

3.3VS

DAC_DDCADATA 21

DISPCLKI 11

DISPCLKO 11

Closed U11

M1

M9

M-MARK1

M3

M-MARK1

M-MARK1

M7

M-MARK1

3.3VS

12

3.3VS

12

M4

M-MARK1

L18

HCB1608KF-121T25

C259

22u_6.3V_12

L19

HCB1608KF-121T25

C265

22u_6.3V_12

M12

M-MARK1

VCCDAC2

C251

1000p_X7R_04

VCCPLL2

C258

1000p_X7R_04

M5

M-MARK1

M8

M-MARK1

C264

1u_10V_06

C263

1u_10V_06

M2

M-MARK1

0: TMDS

1: TV Encoder

B B

A A

TVD4

TVD6

TVD8

TVD9

TVD7

TVD10

R95 4.7K_04

R100 *4.7K_04

R398 4.7K_04

R401 4.7K_04

R399 *4.7K_04

R116 *4.7K_04

R109 4.7K_04

R403 *4.7K_04

R404 4.7K_04

R420 *4.7K_04

R413 4.7K_04

3.3VS

3.3VS

SW3_1 DVP0D4/TVD4 =>AGP Port Muxing

0: Two 12-bit FPD interface

1: One 24-bit Panel interface

SW3_3 DVP0D6/TVD6 =>Dedicated TVD Port Selection

0: Disable

1: Enable

SW3_4 DVP0D8/TVD8 =>External AGP Function Enable

0: External AGP

1: Internal AGP

SW3_5 DVP0D9/TVD9 =>PCI Signal Test Output Enable

0: Disable

1: Enable

[Keep 1 as option,for Debug purpose]

DVP0D7/TVD7 =>GFX Clock Select(VCK/LCDCK/ECK)

0: Internal GFX PLL

1: From External

DVP0D10/TVD10 =>CPUCK/MCK Clock Select

0: From NB

H7

C315D91

H1

C158D158

H13

C315D91

H18

C158D158

H5

C315D91

H17

C158D158

H15

C315D91

H19

C276D126

H3

C315D91

H6

C276D126

H12

C229D91

S4

SMD80X80

1

1

1: From External

5

4

3

2

H10

C237D126

S5

SMD80X80

1

1

H8

C118B237D87

H9

C118B237D87

S6

SMD80X80

1

1

Title

Size Document Number Rev

Custom

3843

Date: Sheet of

H16

H11

C237D107

S9

SMD80X80

1

1

H14

C87D87

C237D107

S7

SMD80X80

S8

SMD80X80

1

1

1

1

3.3VS6,8..16,20..22,24..27,29,30,33

藍 天 電 腦 CLEVO CO.

[07]VN800 4/4

6-71-T80V0-D02

1

H4

C87D87

S10

SMD80X80

1

1

7 33Saturday, June 02, 2007

H2

C158D158

S11

SMD80X80

1

1

1.0

Page 8

5

4

1.8V

3

2

1

MAA0

MAA[0:13]5

D D

BA05

BA15

CS0#5

CS1#5

DQM0#5

DQM1#5

DQM2#5

DQM3#5

DQM4#5

DQM5#5

DQM6#5

DQM7#5

SWEA#5

SCASA#5

DQS05

DQS15

DQS25

DQS35

DQS45

DQS55

DQS65

DQS75

SRASA#5

CKEA05

CKEA15

DCLK0+9

DCLK0-9

DCLK1+9

DCLK1-9

3.3VS

ODT05

ODT15

20Mils

C87

.1u_10V_04

R65 0_04

R67 0_04

R74 0_04

R81 0_04

R141 0_04

R144 0_04

R158 0_04

R184 0_04

MVREF_DIM1

C C

SMB_SBDATA9,13

B B

A A

SMB_SBCLK9,13

1.8V

R62

75_1%_04

MVREF_DIM1

R63

75_1%_04

5

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

DQM0#

DQM1#

DQM2#

DQM3#

DQM4#

DQM5#

DQM6#

DQM7#

DCLK0+

DCLK0DCLK1+

DCLK1-

Z0801

Z0802

Z0803

Z0804

Z0805

Z0806

Z0807

Z0808

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

107

BA0

106

BA1

85

BA2

110

CS0

115

CS1

10

DQM0

26

DQM1

52

DQM2

67

DQM3

130

DQM4

147

DQM5

170

DQM6

185

DQM7

109

WE

113

CAS

108

RAS

79

CKE0

80

CKE1

30

CK0

32

CK0

164

CK1

166

CK1

13

DQS0

11

DQS0

31

DQS1

29

DQS1

51

DQS2

49

DQS2

70

DQS3

68

DQS3

131

DQS4

129

DQS4

148

DQS5

146

DQS5

169

DQS6

167

DQS6

188

DQS7

186

DQS7

195

SDA

197

SCL

198

SA0

200

SA1

1

VREF

199

VDDSPD

114

ODT0

119

ODT1

2

GND

3

GND

8

GND

9

GND

12

GND

15

GND

18

GND

21

GND

24

GND

GND

GND

2728333439404142474853545960656671727778121

818795828896103

VDD1

GND

GND

GND

GND

GND

GND

GND

4

VDD2

GND

VDD3

GND

VDD4

GND

VDD5

GND

VDD6

GND

111

VDD7

GND

117

VDD8

GND

104

VDD9

GND

112

VDD10

VDD11

GND

GND

118

VDD12

GND

GND

5069838486

120

163

NC1

NC2

NC3

NC4

NC5

NC6

NC/TEST

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

122

127

128

132

133

138

139

144

145

149

150

155

CN1

5

D0

7

D1

17

D2

19

D3

4

D4

6

D5

14

D6

16

D7

23

D8

25

D9

35

D10

37

D11

20

D12

22

D13

36

D14

38

D15

43

D16

45

D17

55

D18

57

D19

44

D20

46

D21

56

D22

58

D23

61

D24

63

D25

73

D26

75

D27

62

D28

64

D29

74

D30

76

D31

123

D32

125

D33

135

D34

137

D35

124

D36

126

D37

134

D38

136

D39

141

D40

143

D41

151

D42

153

D43

140

D44

142

D45

152

D46

154

D47

157

D48

159

D49

173

D50

175

D51

158

D52

160

D53

174

D54

176

D55

179

D56

181

D57

189

D58

191

D59

180

D60

182

D61

192

D62

194

D63

168

GND

171

GND

172

GND

177

GND

178

GND

183

GND

184

GND

187

GND

190

GND

193

GND

196

GND

GND

GND

GND

GND

156

161

162

165

AS0A421-N2RN-4F

3

MD_0

MD_1

MD_2

MD_3

MD_4

MD_5

MD_6

MD_7

MD_8

MD_9

MD_10

MD_11

MD_12

MD_13

MD_14

MD_15

MD_16

MD_17

MD_18

MD_19

MD_20

MD_21

MD_22

MD_23

MD_24

MD_25

MD_26

MD_27

MD_28

MD_29

MD_30

MD_31

MD_32

MD_33

MD_34

MD_35

MD_36

MD_37

MD_38

MD_39

MD_40

MD_41

MD_42

MD_43

MD_44

MD_45

MD_46

MD_47

MD_48

MD_49

MD_50

MD_51

MD_52

MD_53

MD_54

MD_55

MD_56

MD_57

MD_58

MD_59

MD_60

MD_61

MD_62

MD_63

MD_[0:63]5

VTT_MEM

C168 .01u_16V_04

MAA12

R93 47_04

CKEA05

CKEA25

CKEA35

CKEA15

BA15

ODT05

CS0#5

SRASA#5

CS1#5

SCASA#5

ODT15

BA05

SWEA#5

ODT25

ODT35

CS2#5

CS3#5

2

R90 47_04

R84 47_04

R85 47_04

MAA3

MAA1

MAA8

MAA9

MAA6

MAA7

MAA11

MAA0

MAA2

MAA4

MAA13

MAA10

MAA5

5

RN4

RN19

RN20

RN21

RN6

RN5

RN7

1.8V

C151 .1u_10V_04

C164 .1u_10V_04

C221 .1u_10V_04

C195 .1u_10V_04

C196 .1u_10V_04

C527 .1u_10V_04

C512 .1u_10V_04

C520 .1u_10V_04

C526 .1u_10V_04

C536 .1u_10V_04

C535 .1u_10V_04

C513 .1u_10V_04

C253 .1u_10V_04

Title

Size Document Number Rev

Custom

Date: Sheet of

4

6

3

7 2

8 1

47_04_8P4R

5

4

6

3

72

81

47_04_8P4R

5

4

6

3

72

81

47_04_8P4R

5

4

6

3

72

81

47_04_8P4R

5

4

6

3

7 2

8 1

47_04_8P4R

5

4

6

3

7 2

8 1

47_04_8P4R

5

4

6

3

7 2

8 1

47_04_8P4R

VTT_MEM28

3.3V2,12..15,17..21,27..29

3.3VS6,7,9..16,20..22,24..27,29,30,33

1.8V5,6,9,28

藍 天 電 腦 CLEVO CO.

[08]DDRII DIMM 0

3843

6-71-T80V0-D02

C191 .1u_10V_04

C198 .1u_10V_04

C222 .1u_10V_04

C180 .1u_10V_04

C519 .1u_10V_04

C133 .1u_10V_04

C523 .1u_10V_04

1.8V

C186 10u_10V_08

C150 10u_10V_08

C247 1u_10V_06

C246 1u_10V_06

C187 1000p_X7R_04

C213 1u_10V_06C178 .1u_10V_04

C248 1u_10V_06C173 .1u_10V_04

C515 .1u_10V_04

C514 .1u_10V_04

1

8 33Saturday, June 02, 2007

1.0

Page 9

5

4

3

2

1

CLOCK GENERATOR

SB_OSCCLK

3.3VS 3.3VCLK

L59

HCB2012KF-500T40

C538

10u_10V_08

D D

C C

12

C537

10u_10V_08

C544

1u_10V_06

C582

.01u_16V_04

C554

.01u_16V_04

3.3VCLK

Change 10pf to 27pf.

B B

1.8V

C110

C510

*10u_10V_08

A A

4.7u_10V_08

5

C111

1u_10V_06

L13

HCB2012KF-500T40

12

C555

.01u_16V_04

C553

.01u_16V_04

R447 1K_04

R446 4.7K_04

R444

475_1%_04

2.5VS

3.3VCLK

1.8VBFR

10u_10V_08

.01u_16V_04

C543

*22u_6.3V_12

C109

C93

.01u_16V_04

X6

1 2

14.318MHz

C577

27p_50V_06

1u_10V_06

2.5VS 2.5VCLK

SATA25MHZ13

C571

27p_50V_06

FS0

FS1

FS2

R467 10K_04

FS3

R473 10K_04

FS4

R468 10K_04

1.8VBFR

C96

.01u_16V_04

C89

.01u_16V_04

C545

C557

C542

.1u_16V_04

SMB_SBDATA8,13

SMB_SBCLK8,13

C95

.01u_16V_04

SMB_SBDATA8,13

SMB_SBCLK8,13

4

C584

.01u_16V_04

L60

12

HCB2012KF-500T40

PM_PWROK12,14,19,21

SATA25MHZ

.01u_16V_04

MCLKOT5

MCLKOC5

.01u_16V_04

C90

C585

C556

.01u_16V_04

RN25

0_04_4P2R

2 3

1 4

R439 22_04

R481

10K_04

C94

.01u_16V_04

RN2

*0_04_4P2R

2 3

1 4

C91

*5p_50V_04

C586

.01u_16V_04

2.5VCLK

Z0901

Z0902

Z0903

Z0904

Z0905

Z0906

Z0907

R484 *10K_04

R482 *10K_04

R485

10K_04

Z0914

Z0915

C92

*5p_50V_04

10

17

24

48

27

40

3

34

6

11

18

23

28

37

43

47

32

31

30

36

35

4

5

10

21

27

9

22

28

1

26

2

25

16

15

3

4

U29

VDDPCI1

VDDPCI2

VDD48

VDDA

VDD3V66

VDDCPU

VDDREF

VDD

GND

GND

GND

GND

GND

GND

GND

GND

SDATA

SCLK

RESET

25Mhz_0

25Mhz_1

X1

X2

U4

VDD2.5/1.8-0

VDD2.5/1.8-1

VDD2.5/1.8-2

GND

GND

GND

AVDD2.5-0

AVDD2.5-1

AGND

AGND

SDATA

SCLK

BUF_INT

BUF_INC

ICS952906FLF-T

3.3VS

ICS9P936FLF-T

REF0/FS1

REF1/FS0

48MHZ/FS3

24_48MHZ/SEL24_48

3V66_0

3V66_1

3V66_2

PCI_F0/FS2

PCI_F1/FS4

PCI_F2

MODE/PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

CPUCLKT0VTT_PWRGD/PD

CPUCLKC0IREF

CPUCLKT1

CPUCLKC1

CPUCLKT_ITP/PCI_STOP

CPUCLKC_ITP/CPU_STOP

FS4OFS3 FS0

O

FS2

O

O

O

O

Modufy A1 rev

3

O

O

FB_OUTT

FB_OUTC

DDRT0

DDRC0

DDRT1

DDRC1

DDRT2

DDRC2

DDRT3

DDRC3

DDRT4

DDRC4

DDRT5

DDRC5

O

O

1

2

21

22

29

26

25

7

8

9

12

13

14

15

16

19

20

3933

3846

42

41

45

44

FS1

OO

1O

1

O

5

6

7

8

13

14

18

17

20

19

24

23

11

12

FS1

FS0

FS3

SEL24_48

3V66_0

3V66_1

FS2

FS4

Z0908

MODE

Z0909

Z0911

Z0912

Z0913

HCLK+_

HCLK-_

CPUCLK+__

CPUCLK-__

PCI-STOP#

CPU-STOP#

O

O

1

1

DK0+

DK0-

DK1+

DK1-

Z0916

R68 22_04

R465 22_04

R466 22_04

R474 22_04

R488 22_04

R480 10K_04

R448 22_04

R449 22_04

R486 22_04

R469 1K_04

R470 22_04

R471 22_04

R472 22_04

R487 22_04

PCI-STOP#

CPU-STOP#

CPU

100

133

166

200

RN1

0_04_4P2R

2 3

1 4

2 3

1 4

RN3

0_04_4P2R

RN24

33_04_4P2R

RN23

33_04_4P2R

PCI

33

33

33

33

BUF_SIO_CLK

23

14

23

14

R434 10K_04

R445 10K_04

D34 SCS751V-40

A C

D33 SCS751V-40

A C

DCLK0+8

DCLK0-8

DCLK1+8

DCLK1-8

MCLKIT5

2

SB_OSCCLK13

GUICLK7

BUF_SIO_CLK33

USB_CLK12

GCLK_NB6

VLINKCLK14

PCISBCLK14

APICCLKSB14

PCLK_SIO33

PCLK_PCM24

KBC_PCLK20

H_CLK+4

H_CLK-4

CLK_CPU_BCLK2

CLK_CPU_BCLK#2

R436 51.1_1%_04

R435 51.1_1%_04

R438 51.1_1%_04

R437 51.1_1%_04

3.3VS

PCISTOP#

CPUSTP#

C530 *.1u_16V_04

C529 .1u_16V_04

C528 .1u_16V_04

C532 *.1u_16V_04

C531 *.1u_16V_04

Title

Size Document Number Rev

Custom

Date: Sheet of

PCISTOP#13

CPUSTP#13,29

VCCP2..4,29,30

5VS10,13,16,21..23,25..27

3.3V2,12..15,17..21,27..29

3.3VS6..8,10..16,20..22,24..27,29,30,33

2.5VS2,11..14,27

1.8V5,6,8,28

藍 天 電 腦 CLEVO CO.

[09]CLOCK GENERATOR

3843

BUF_SIO_CLK

1.8V3.3VS

6-71-T80V0-D02

C596 *10p_50V_04

GUICLK

C597 *10p_50V_04

USB_CLK

C602 *10p_50V_04

GCLK_NB

C551 *10p_50V_04

VLINKCLK

C552 *10p_50V_04

APICCLKSB

C599 *10p_50V_04

PCISBCLK

C598 *10p_50V_04

PCLK_PCM

C600 *10p_50V_04

KBC_PCLK

C601 *10p_50V_04

SATA25MHZ

C550 *10p_50V_04

C587 *10p_50V_04

C511 .1u_16V_04

C157 .1u_16V_04

C525 .1u_16V_04

C148 .1u_16V_04

1

9 33Saturday, June 02, 2007

1.0

Page 10

5

4

3

2

1

PANEL

SI3457

D

NDS352AP

6

PLVDD

2A

182736

IDD1

C75

*10u_10V_08

45

CP5

*10p_12_8P4C

182736

R112 1K_04

R119 1K_04

R129 1K_04

R103 1K_04

45

CP6

*10p_12_8P4C

LVDS-L0N11

LVDS-L0P11

LVDS-L1N11

LVDS-L1P11

LVDS-L2N11

LVDS-L2P11

LVDS-LCLKN11

LVDS-LCLKP11

NEAR VN800

LCDID07

LCDID17

LCDID37

LCDID27

Cable Mode

ENAVDD6

FAN CONTROL

FAN_DC_VOL Z1004

CPU_FANSEN20

C81

D D

LVDS-L0N

LVDS-L0P

LVDS-L2N

LVDS-L2P

LVDS-L1N

LVDS-L1P

LVDS-L0N

LVDS-L0P

LVDS-L1N

C C

B B

LVDS-L1P

LVDS-L2N

LVDS-L2P

LVDS-LCLKN

LVDS-LCLKP

J_LCD1

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

87216-2006

3.3VS

R121

*10K_04

R120

0_04

.1u_16V_04

LVDS-LCLKN

LVDS-LCLKP

R114

10K_04

IDD0

R113

*0_04

1

3

GS

3.3VS

C70

.1u_16V_04

R64

4.99K_1%_06

R60 10K_04

CPU_FANON20

4

2A

80mils

R52

100K_04

R50 20K_1%_04

R61

100K_04

5VS

C76

.1u_16V_04

3

2

VDD3

C88

.1u_16V_04

U3A

LM358L

+

-

4 8

.01u_X7R_04

PMOS

Q7

AO3415

C80

G

Z1001

Z1002

B

C77

10u_10V_08

Z1005

1

R66 4.7K_04

D2 SCS751V-40

Layout Note:

1. Pin S & pin D

trace width Min.

80 mils.

2A

DS

C79

.1u_16V_04

CE

Q11

DTD114EK

5VS

G

Q12

NDS352AP_NL

D S

+

C502

100u_10V_D

AC

G

80mils

R49

200_1%_04

Z1003

DS

Q10

2N7002

D3

FM0540-N

A C

FAN_DC_VOL

PLVDD

5VS

5

+

6

U3B

LM358L

-

4 8

JVGAFAN1

1

2

3

85205-03001

JFAN

3

1

7

A A

5

PANLE ID SELECTOR

PANEL

TYPE

PANEL ID

1 800X600

IDD2

IDD1IDD3

0

0

0 1

4

IDD0

Resolution

1

VDD32,14,20,27,31,32

5VS13,16,21..23,25..27

CH

3

2

3.3VS6..9,11..16,20..22,24..27,29,30,33

藍 天 電 腦 CLEVO CO.

Title

[10]PANEL,INVERTER,FAN

Size Document Number Rev

A3

3843

Date: Sheet of

6-71-T80V0-D02

10 33Saturday, June 02, 2007

1

1.0

Page 11

5

2.5VS

L67 HCB1608KF-121T25

1 2

L68 HCB1608KF-121T25

1 2

L34 HCB1608KF-121T25

1 2

D D

1.5VS

R475

1K_1%_04

R476

1K_1%_04

C C

Near CHIP

LVDS_VREF

C590

.1u_10V_04

DVDD

LVDSVCC

2.5VS

PLLVCC

R248 4.7K_04

R247 *4.7K_04

R246 4.7K_04

MODSEL

TYPE

EDGE

4

R506 *4.7K_04

R505 4.7K_04

R504 *4.7K_04

3

FPD[0..23]6

FPD[0..23]

CLOSE TO IC

FPD23

FPD22

RN31 22_04_8P4R

FPD21

FPD20

FPD19

FPD18

RN32 22_04_8P4R

FPD15

FPD14

FPD13

FPD12

RN34 22_04_8P4R

FPD11

FPD10

FPD7

FPD6

RN35 22_04_8P4R

FPD5

FPD4

FPD3

R502 22_04

FPD2

R503 22_04

FPCLK6

FPVS6

FPHS6

FPDE6

653

7 2

8 1

653

7 2

8 1

653

7 2

8 1

653

7 2

8 1

4

4

4

4

R452 22_04

R479 22_04

R478 22_04

R477 22_04

LD17

LD16

LD15

LD14

LD13

LD12

LD11

LD10

LD09

LD08

LD07

LD06

LD05

LD04

LD03

LD02

LD01

LD00

LVDS_CLKIN

LVDS_VSYNC

LVDS_HSYNC

LVDS_DE

LVDS_VREF

EDGE

TYPE

MODSEL

LVDS_PD#

LD00

LD01

LD02

LD03

LD04

LD05

LD06

LD07

LD08

LD09

LD10

LD11

LD12

LD13

LD14

LD15

LD16

LD17

2

U31

3

D0

2

D1

1

D2

48

D3

47

D4

46

D5

44

D6

43

D7

42

D8

41

D9

40

D10

39

D11

36

D12

35

D13

34

D14

33

D15

32

D16

31

D17

45

CLKINP

27

VSYNC

28

HSYNC

29

DE

30

VREF

8

R_FB

9

TYPE

10

MODSEL

11

PDB

CLK1M

CLK1P

DVDD

LVDSVCC

PLLVCC

DGND

DGND

DGND

LVDSGND

LVDSGND

LVDSGND

PLLGND

PLLGND

A0M

A0P

A1M

A1P

A2M

A2P

A3M

A3P

24

23

21

20

19

18

Z1101

14

Z1102

13

16

15

37

22

6

4

26

38

12

17

25

5

7

DVDD

LVDSVCC

PLLVCC

LVDSGND

PLLGND

1

LVDS-L0N 10

LVDS-L0P 10

LVDS-L1N 10

LVDS-L1P 10

LVDS-L2N 10

LVDS-L2P 10

LVDS-LCLKN 10

LVDS-LCLKP 10

VT1634

DISPCLKI7

R146

*22_04

DISPCLKO7

B B

L69 0_06_L

1 2

.1u_10V_04C591

.1u_10V_04C361

L32 0_06_L

1 2

.1u_10V_04C362

.1u_10V_04C363

A A

5

R160 22_04

U11

1

CLKIN

2

3

4

CP0

CP1

VSS

P2040C

LVDSVCC

LVDSGND

PLLVCC

PLLGND

DVDD

2.5VS

VDD

ModOut

SSON#

SR0

MRA SR1

8

7

6

5

C613

*10u_10V_08

C367

*10u_10V_08

C583

*10u_10V_08

C603

*10u_10V_08

SR0

CLKINPSR1

Z1103

3.3VS

C273

.1u_16V_04

R163 *10K_04

C609

.1u_10V_04

C614

.01u_16V_04

C594

.1u_10V_04

C606

.1u_10V_04

C607

.1u_10V_04

C615

.01u_16V_04

C588

.1u_16V_04

C370

.01u_16V_04

4

3.3VS

C608

.01u_16V_04

C366

1u_10V_06

C593

.1u_10V_04

C579

.01u_16V_04

3.3VS

C611

1u_10V_06

C589

.01u_16V_04

R150 *0_04

R162 *0_04

R149 *0_04

C581

1u_10V_06

MRA

SR0

R151 *0_04

R159 0_04

R152 *0_04

3

2.5VS

C580

*.1u_10V_04

L31 *0_06_L

1 2

*.1u_10V_04C353

*.1u_10V_04C350

C592

*.1u_10V_04

PLLGNDLVDSGND

3.3VS 2.5VS

R229

2.2K_04

Z1105

ENAVEE6

2

R232 1K_04

Z1104

B

Q26

C365

*.1u_10V_04

5VS10,13,16,21..23,25..27

3.3VS6..10,12..16,20..22,24..27,29,30,33

2.5VS2,9,12..14,27

1.5VS3,6,19,27

藍 天 電 腦 CLEVO CO.

Title

Size Document Number Rev

Custom

3843

Date: Sheet of

2N3904

E C

[11]VIAVT1634AL

6-71-T80V0-D02

R507

1K_04

LVDS_PD#

Q27

2N7002

G

S D

11 33Saturday, June 02, 2007

1

1.0

Page 12

5

4

3.3VS

3

2

2.5V

1

USB_PP6

USB_PN6

USB_PP3

USB_PN3

USB_PP2

USB_PN2

USB_PP5

USB_PN5

USB_PP0

USB_PN0

USB_PP7

USB_PN7

USB_PP4

USB_PN4

USB_PP1

USB_PN1

USB_OC6#

USB_OC3#

USB_OC2#

USB_OC5#

USB_OC0#

USB_OC7#

USB_OC4#

USB_OC1#

USB_REXT

Z1201

Z1202

GA20

KBC_RST#

Z1203

R293 2.2K_04

Z1204

R270 2.2K_04

3.3V

U13

5

2

1

3

74AHC1G08GW

C359

.1u_10V_04

C324

.01u_16V_04

C563

.01u_16V_04

USB_PP615

USB_PN615

USB_PP316

USB_PN316

USB_PP216

USB_PN216

USB_PP516

USB_PN516

USB_PP015

USB_PN015

USB_PP717

USB_PN717

USB_PP419

USB_PN419

USB_PP117

USB_PN117

USB_OC3#16

USB_OC2#16

USB_OC5#16

USB_CLK9

R457 6.04K_1%_04

R458 *10K_04

ALLPCIRST#

4

C320

.1u_10V_04

SB_USBVCCA

C575

10u_10V_08

SB_USBGNDA

GA2020

KBC_RST#20

3.3V

2

SB_USBVDD

C295

1u_10V_06

L66

HCB1608KF-121T25

12

L64

HCB1608KF-121T25

12

RST#

R332

187_1%_04

3.3V 3.3V

U18A

14

Z1205 Z1208

1 2

74HC14PW

3.3V

U18C

14

Z1206

5 6

74HC14PW

3.3V

U18E

14

Z1207 Z1209

11 10

74HC14PW

Title

Size Document Number Rev

Custom

Date: Sheet of

L22

HCB2012KF-500T40

C309

C321

10u_10V_08

C327

1u_10V_06

2.5VS

C271

.1u_10V_04

1u_10V_06

3.3V

C294

4.7u_10V_08

RN26 4.7K_04_8P4R

1

2

3

4 5

R456 4.7K_04

NEAR CHIPSET

USB_PN5

U18B

14

3 4

74HC14PW

3.3V

U18D

14

9 8

74HC14PW

3.3V

U18F

14

13 12

74HC14PW

USB_PP5

USB_PN3

USB_PP3

USB_PN1

USB_PP1

USB_PN7

USB_PP7

USB_PN4

USB_PP4

USB_PP0

USB_PN0

USB_PN2

USB_PP2

USB_PP6

USB_PN6

3.3V

U20

5

2

1

3

74AHC1G08GW

R274 22_04

Z1210

R511 22_04

R331 22_04

15K_06_8P4R

15K_06_8P4R

15K_06_8P4R

15K_06_8P4R

1

RN28

2

3

4 5

1

RN30

2

3

4 5

8

RN11

7

6

8

RN9

7

6

4

R512

*51_04

RST#

藍 天 電 腦 CLEVO CO.

[12]VT8237 1/3

3843

6-71-T80V0-D02

1

3.3V

12

8

7

6

8

7

6

8

7

6

1

2

3

45

1

2

3

45

PCIRST#20,24

LPCRST_SIO#33

RESET_NB#2,6

12 33Saturday, June 02, 2007

C291

.1u_16V_04

USB_OC4#

USB_OC1#

USB_OC0#

USB_OC7#

USB_OC6#

1.0

3.3VS

C312

D D

1u_10V_06

3.3VS

C338

.1u_10V_04

3.3VS

C C

B B

3.3VS

A A

C335

1u_10V_06

C347

.1u_10V_04

C299

.01u_16V_04

C337

.01u_16V_04

RN12 2.2K_04_8P4R

1

8

2

7

3

6

4 5

RN13 2.2K_04_8P4R

1

8

2

7

3

6

4 5

RN37 2.2K_04_8P4R

1

8

2

7

3

6

4 5

R242 2.2K_04

C336

1u_10V_06

C310

.1u_10V_04

C351

.01u_16V_04

PCI_REQ4#

PCI_STOP#

PCI_GNT1#

PCI_GNT3#

PCI_REQ3#

PCI_INTF#

PCI_INTE#

PCI_INTD#

PCI_INTA#

PCI_INTB#

PCI_INTG#

PCI_INTH#

PCI_REQ5#

5

PCI_AD[15:0]24

PCI_AD[31:16]24

C330

1u_10V_06

PCI_C/BE0#24

PCI_C/BE1#24

PCI_C/BE2#24

PCI_C/BE3#24

PCI_FRAME#24

PCI_DEVSEL#24

PCI_IRDY#24

PCI_TRDY#24

PCI_STOP#24

PCI_SERR#24

PCI_PAR24

PCI_PERR#24

PCI_INTA#7,24

PCI_INTB#24

PCI_INTC#24

PCI_REQ0#24

PCI_GNT0#24

C303

.1u_10V_04

C340

.01u_16V_04

T62

3.3VS

PCI_AD[15:0]

PCI_AD0

PCI_AD1

PCI_AD2

PCI_AD3

PCI_AD4

PCI_AD5

PCI_AD6

PCI_FRAME#

PCI_DEVSEL#

PCI_IRDY#

PCI_TRDY#

PCI_STOP#

PCI_SERR#

PCI_PAR

PCI_PERR#

SB_PCIRST#

PCI_INTA#

PCI_INTB#

PCI_INTC#

PCI_INTD#

PCI_INTE#

PCI_INTF#

PCI_INTG#

PCI_INTH#

PCI_REQ0#

PCI_REQ1#

PCI_REQ2#

PCI_REQ3#

PCI_REQ4#

PCI_REQ5#

PCI_GNT0#

PCI_GNT1#

PCI_GNT2#

PCI_GNT3#

PCI_GNT4#

PCI_GNT5#

1

8

2

7

3

6

4 5

1

8

2

7

3

6

4 5

1

8

2

7

3

6

4 5

PCI_AD7

PCI_AD8

PCI_AD9

PCI_AD10

PCI_AD11

PCI_AD12

PCI_AD13

PCI_AD14

PCI_AD15

PCI_AD16

PCI_AD17

PCI_AD18

PCI_AD19

PCI_AD20

PCI_AD21

PCI_AD22

PCI_AD23

PCI_AD24

PCI_AD25

PCI_AD26

PCI_AD27

PCI_AD28

PCI_AD29

PCI_AD30

PCI_AD31

C311

.1u_10V_04

PCI_AD[31:16]

RN36 2.2K_04_8P4R

R298 2.2K_04

R315 2.2K_04

RN16 2.2K_04_8P4R

RN14 2.2K_04_8P4R

G2

J4

J3

H3

F1

G1

H4

F2

E1

G3

E3

D1

G4

D2

D3

F3

K3

L3

K2

K1

M4

L2

N4

L1

M2

M1

P4

N3

N2

N1

P1

P2

E2

C1

L4

M3

J1

H2

J2

H1

K4

C2

F4

C3

R1

A4

B4

B5

C4

D4

E4

A3

B3

A5

B6

C5

D5

P3

R3

A6

D6

C6

E5

R4

R2

PCI_GNT0#

PCI_REQ1#

PCI_REQ0#

PCI_INTC#

PCI_GNT4#

PCI_GNT5#

PCI_FRAME#

PCI_IRDY#

PCI_TRDY#

PCI_DEVSEL#

PCI_PERR#

PCI_REQ2#

PCI_GNT2#

PCI_SERR#

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD30

AD31

CBE0

CBE1

CBE2

CBE3

FRAME

DEVSEL

IRDY

TRDY

STOP

SERR

PAR

PERR

PCIRST

INTA

INTB

INTC

INTD

INTE/GPIO12

INTF/GPIO13

INTG/GPIO14

INTH/GPIO15

REQ0

REQ1

REQ2

REQ3

REQ4

REQ5/GPI7

GNT0

GNT1

GNT2

GNT3

GNT4

GNT5/GPO7

GND

A1A2B1

4

GND

GND

GND

GND

GND

E8

F25

H9

H10

H12J8K8L8M8N8P8R8R19

H11

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

VCC33

VT8237 (A)

GND

GND

GND

USBGND

USBGND

USBGND

USBGND

USBGND

USBGND

USBGND

H23

J21

J25B2A17

A19

A21

B13

B15

A15

A13

T8

VCC33

VCC33

USBGND

USBGND

B17

B19

T19

U8

VCC33

VCC33

USBGND

USBGND

B21

C13

U19V8V19

VCC33

VCC33

USBGND

USBGND

C14

C15

V21W9W10

VCC33

VCC33

USBGND

USBGND

C16

C17

VCC33

VCC33

USBGND

USBGND

C18

C19

W11

W17

VCC33

USBGND

C20

C21

W18

W19

VCC33

VCC33

VCC33

USBGND

USBGND

USBGND

D13

D15

3

W21

Y21

VCC33

VCC33

USBGND

USBGND

D17

D19

W8

VCC33

USBGND

USBGND

D21

E13

C24

U30A

USBVDD

USBVDD

USBVDD

USBSUS25

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

USBVDD

PLLVDDA1

PLLVDDA2

PLLGNDA1

PLLGNDA2

USBP0+

USBP0-

USBP1+

USBP1-

USBP2+

USBP2-

USBP3+

USBP3-

USBP4+

USBP4-

USBP5+

USBP5-

USBP6+_NC

USBP6-_NC

USBP7+_NC

USBP7-_NC

USBOC0

USBOC1

USBOC2

USBOC3

USBOC4

USBOC5

USBOC6_NC

USBOC7_NC

USBCLK

USB REXT

UDPWR/GPI9_NC

UDPWREN/GPO9_NC

KBCK/KA20G

KBDT/KBRC

MSCK/IRQ1

MSDT/IRQ12

USBGND

USBGND

USBGND

USBGND

USBGND

USBGND

USBGND

USBGND

USBGND

USBGND

E15

E17

E19

E21

H13

H15

H16

H18

H14

H17

SB_PCIRST#

PM_PWROK9,14,19,21

3.3V2,13..15,17..21,27..29

3.3VS6..11,13..16,20..22,24..27,29,30,33

2.5V13,14,27

2.5VS2,9,11,13,14,27

A22

B22

C22

D22

E22

F22

J13

J14

J15

J16

J17

J18

A23

B23

D23

C23

E20

D20

A20

B20

E18

D18

A18

B18

D16

E16

A16

B16

D14

E14

A14

B14

C26

D24

B26

C25

B24

A24

A26

A25

E23

B25

D26

D25

W3

V1

W1