Page 1

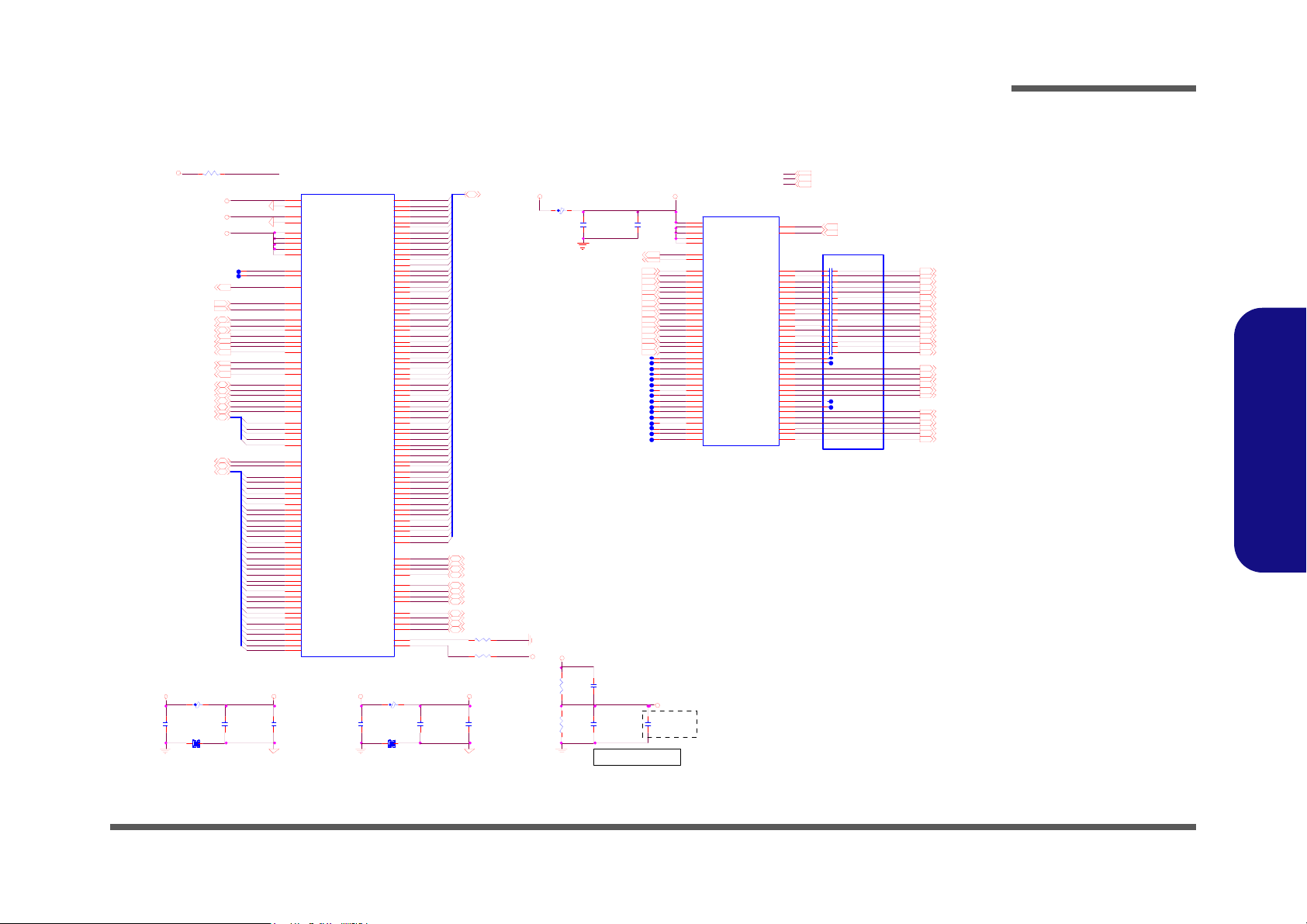

Appendix B: Schematic Diagrams

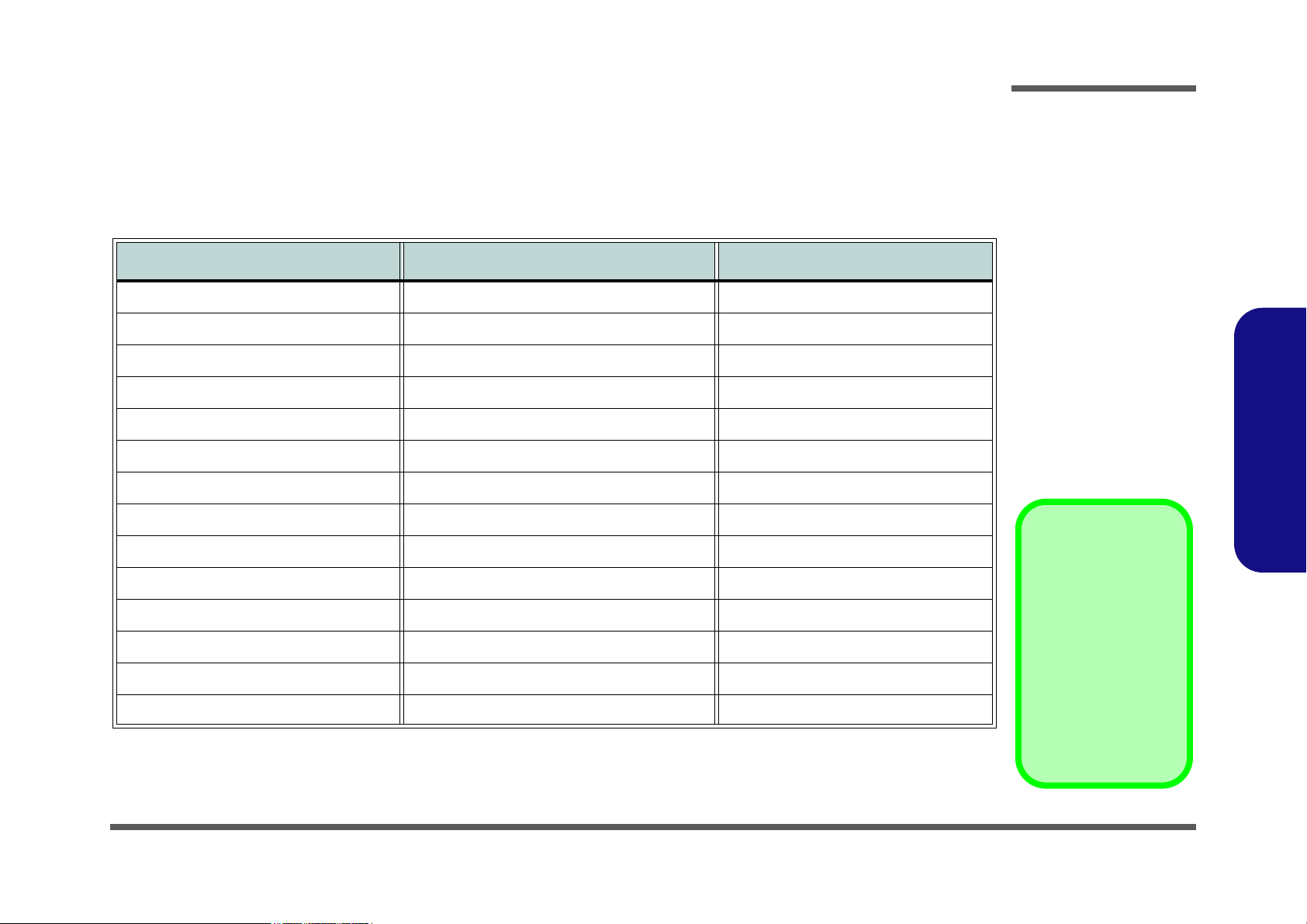

Table B - 1

Schematic

Diagrams

Version Note

The schematic diagrams in this chapter

are based upon version 6-7P-M74S9003A. If your mainboard (or other boards)

are a later version,

please check with the

Service Center for updated diagrams (if required).

This appendix has circuit diagrams of the M740S/M741S/M745S/M760S/M765S/M766S/M767S notebook’s PCB’s.

The following table indicates where to find the appropriate schematic diagram.

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 968 PCIE, LAN, GPIO 2/4 - Page B - 16 AC-IN, Charger - Page B - 30

Penryn (Socket-P) 1/2 - Page B - 3 968 USB SATA 3/4 - Page B - 17 VCORE - Page B - 31

Penryn (Socket-P) 2/2 - Page B - 4 968 PWR, GND 4/4 - Page B - 18 VDD3, VDD5) - Page B - 32

SiSM672 Host, PCIE 1/5 - Page B - 5 Clock Generator & Clock Buffer - Page B - 19 1.05VS, 1.2V, 1.5V - Page B - 33

SiSM672 DRAM 2/5 - Page B - 6 PHY Realtek 8201CL - Page B - 20 1.8V, 0.9VS - Page B - 34

SiSM672 MuTIOL VGA 3/5 - Page B - 7 KBC ITE8512E - Page B - 21 Click BD, Finger BD for M76 - Page B - 35

SiSM672 PWR 4/5 - Page B - 8 ENE MR510, Card Reader - Page B - 22 Multi Function Board - Page B - 36

SiSM672 GND 5/5 - Page B - 9 Audio Codec ALC662 - Page B - 23 Audio Board - Page B - 37

Schematic Diagrams

B.Schematic Diagrams

DDRII SO-DIMM - 1 - Page B - 10 Audio AMP - Page B - 24 Power Switch Board for M74 - Page B - 38

DDRII SO-DIMM - 2 - Page B - 11 SATA HDD, PWR, LID - Page B - 25 External ODD Board for M76 - Page B - 39

SiS307ELV - Page B - 12 Multi I/O, ODD, 3G, Click BD for M74 - Page B - 26 Power Switch Board for M76 - Page B - 40

Panel, CRT - Page B - 13 New Card, Mini PCIE, USB - Page B - 27

Inverter, Bluetooth, Fan - Page B - 14 LED, PC Beep, TP, FP - Page B - 28

968 PCI, IDE, MuTIOL, SPI 1/4 - Page B - 15 System/Ext-VGA Power - Page B - 29

B-1

Page 2

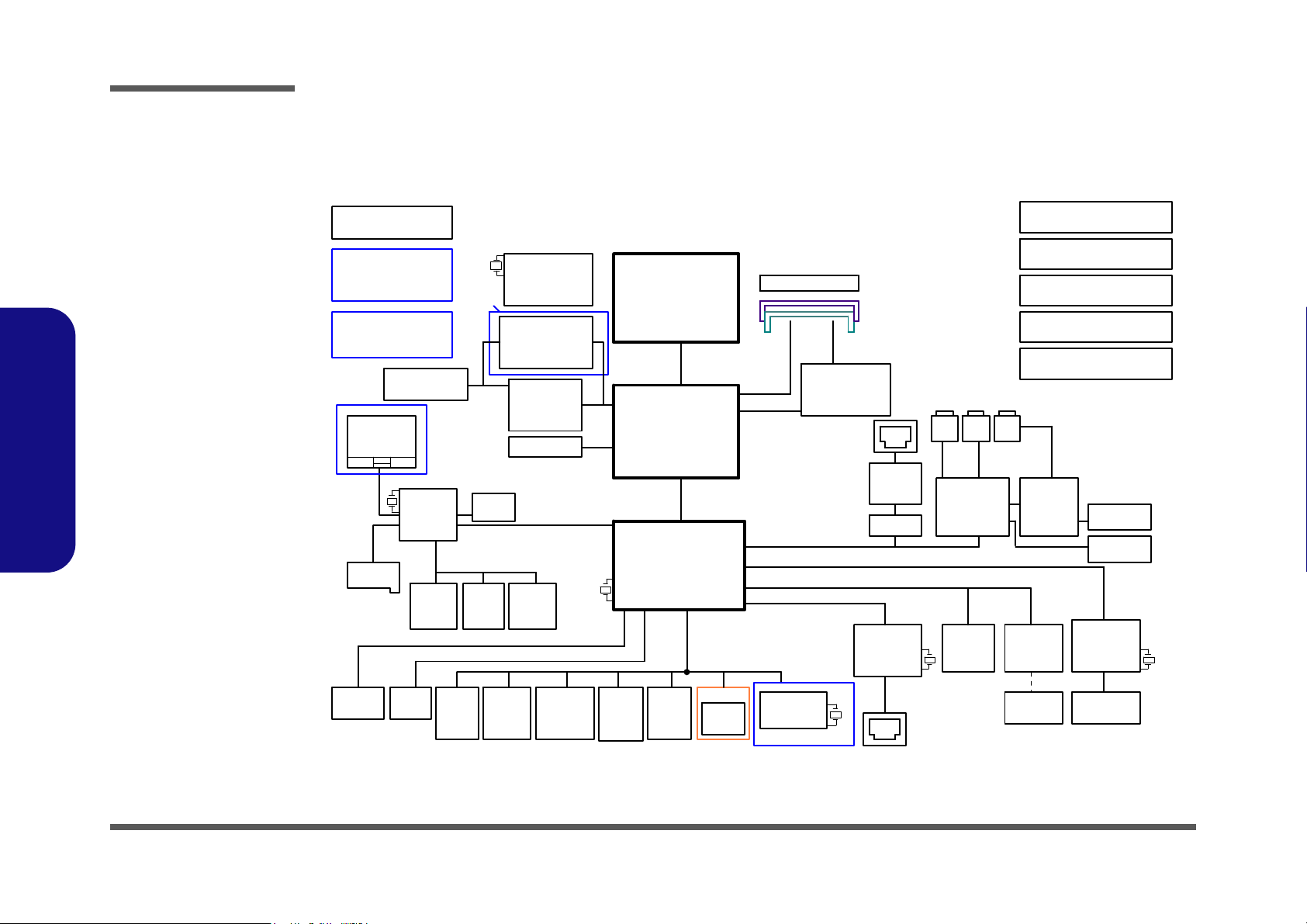

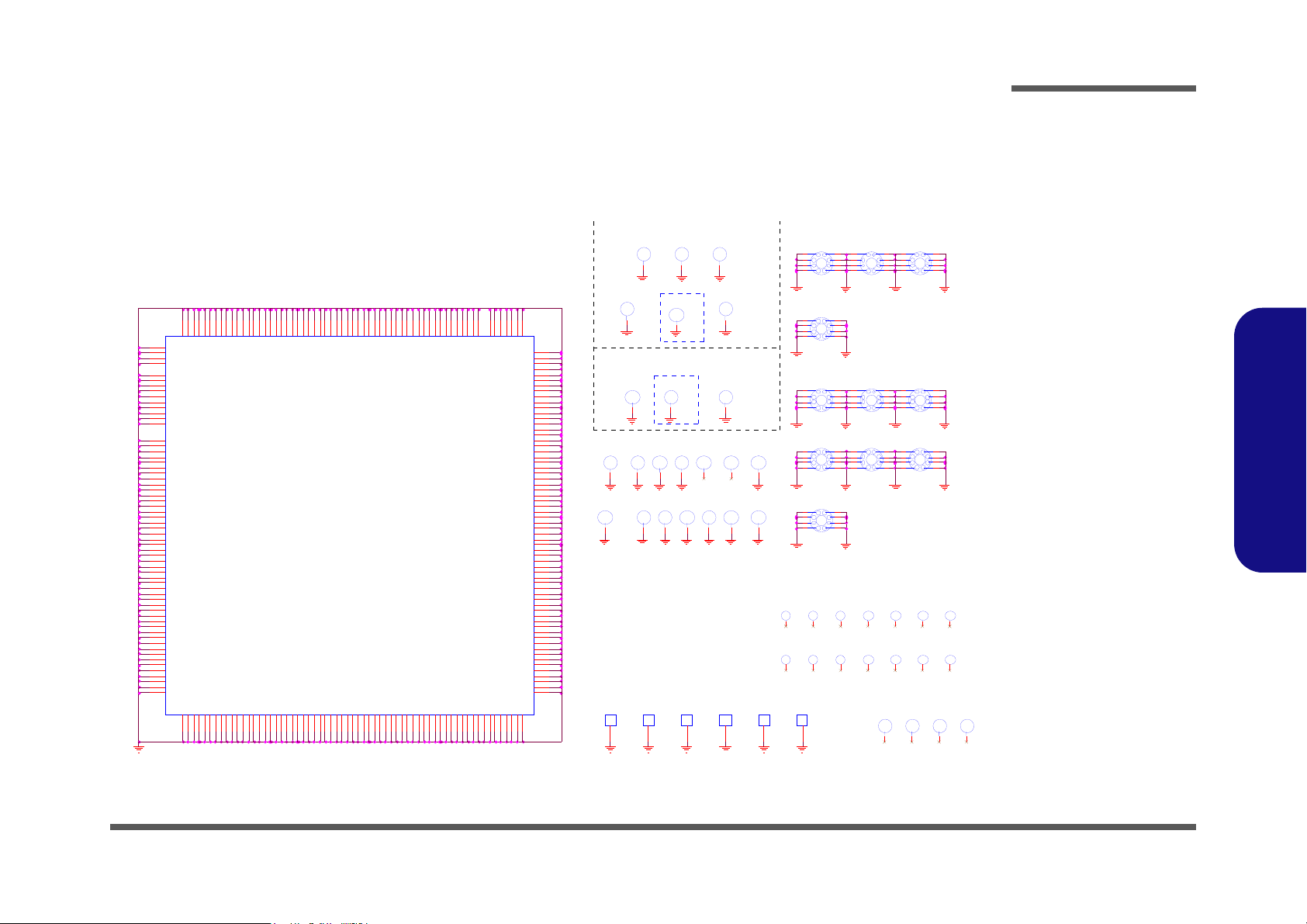

Schematic Diagrams

Sheet 1 of 48

System Block

Diagram

Sy na pt ic

SPI

FING ER PRIN TER BOAR D

28pins SSOP

Intel Penryn

N ew Ca rd

CRT

AUD IO A MP

USB2.0

14 *1 4* 1. 6m m

PCI BUS

32.768 KHz

ICS 9P 93 5

INT . K/ B

SATA HDD,

LID

AC-IN,CHARGE R

10 /1 00 M P HY

LCD C ON NEC TO R,

INV ER TE R

24.576

MHz

35*35*2.7mm

PROCESSOR

33 MHz

Memory Termination

IT E 851 2E

EC SMBUS

Clo ck B uff er

RTL8201CL

M7 6S U

SM AR T

BA TT ERY

13* 1 3* 1.7 m m

GMAC

PCIE

9.8*6.4*1.2mm

5 33/6 67(/ 800) MHz

MODEM, CCD

H EA DPH ON E

12 MHz

1.05VS,1.5V,1 .2V

Si S30 7E LV

48pins LQFP

MIC

IN

AZALIA LINK

CA RD RE AD ER

9*9*1.6mm

169balls BGA

667/800 MHz

SPK_R, RJ-11

USB, SPDIF, MIC IN

LPC

17. 1* 8. 1* 1.2 m m

7 IN1

INT MIC

MuTIOL 1G

INT SPK

Audio Board

F7 538 3M

128-pin LQFP

VDD3,VDD5,3.3 V,5 V

570b alls mBGA

14. 318 MHz

SMART

FAN

USB & Phone

Jack B'd

SOC KET

USB 2

NO RT H BR ID GE

HP

OUT

MULTI I/O BO AR D

128pins LQFP

56p ins TSSO P

SY STE M PO WE R, GPU C OR E

C ol ck Ge ne rat or

32.768KHz

Re al te k

AL C6 62

SiS968

SO CKE T

Mini PCIE

( USB 1)

24pins TSSOP

(Optional)

AZALIA

MDC

MODULE

14 *1 4*1. 4m m

S OCK ET

(US B0)

ICS9LPR600

25 MHz

SPDIF

OUT

(U SB 5)

TO UC H PAD

EC

US B6

MR510

810602-1703

(U SB 3)

852balls TEBGA

DDRII

48 pi ns LQ FP

33 MHz

1 7.1* 8.1*1 .2 mm

GO LAN

En E

U SB4

(USB7)

SiSM672

SO-DIMM0

CC D

3 G CAR D

OD D

27 *2 7* 2. 5m m

LV DS (T V)

479 pins socket P

Az ali a Co dec

RJ-45

2 3* 23* 2. 5mm

FSB

PATA-133

SO-DIMM1

9* 9*1. 7mm

MINI PCIE

RJ-11

24 MHz

CL ICK BOAR D

53 3 bal ls BG A

SOUTH BRIDGE

35*35*2.4mm

(Optional)

CLEVO M740S System Block Diagram

ANPAC

APA2056A

1.8V,0.9VS

100 MHz

NV 9400M-GS

F in ger Pr in t

+VCORE

MDC CON

TH ERM AL

SE NSO R

DDRII

SATA I/II 3.0 Gb /s

Bl ue too th

480 Mbps

EX TE RNA L VGA

System Block Diagram

B.Schematic Diagrams

B - 2 System Block Diagram

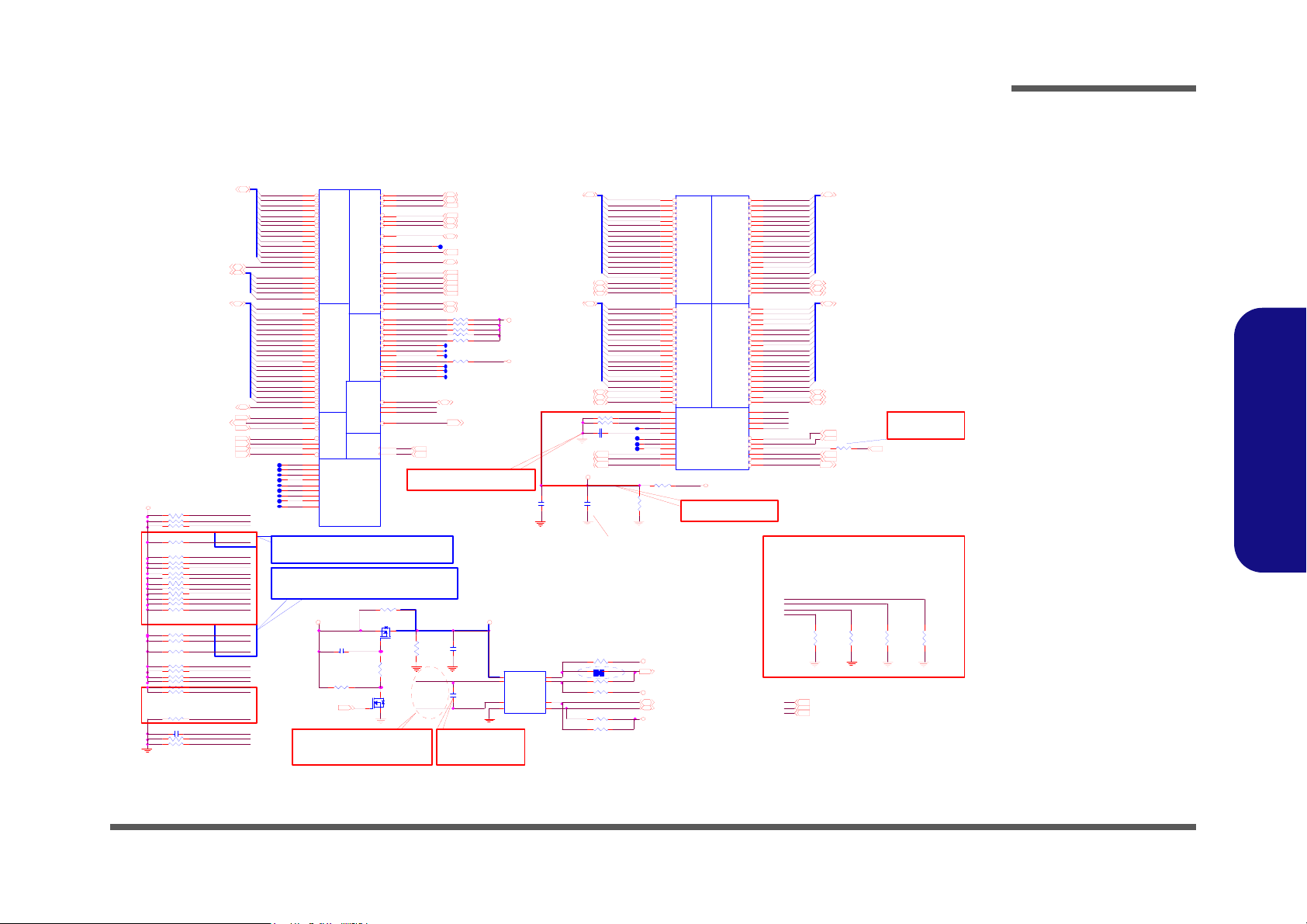

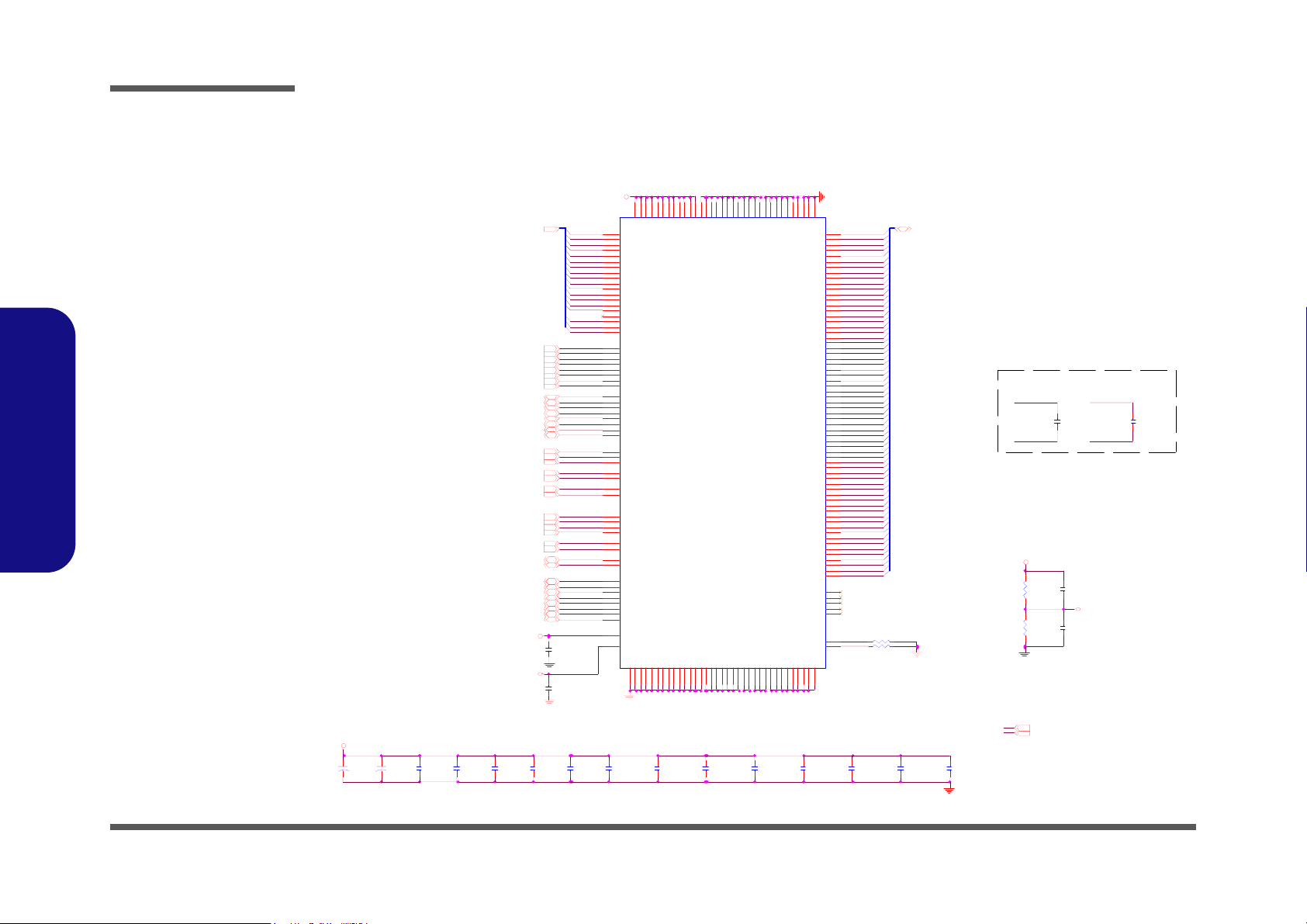

Page 3

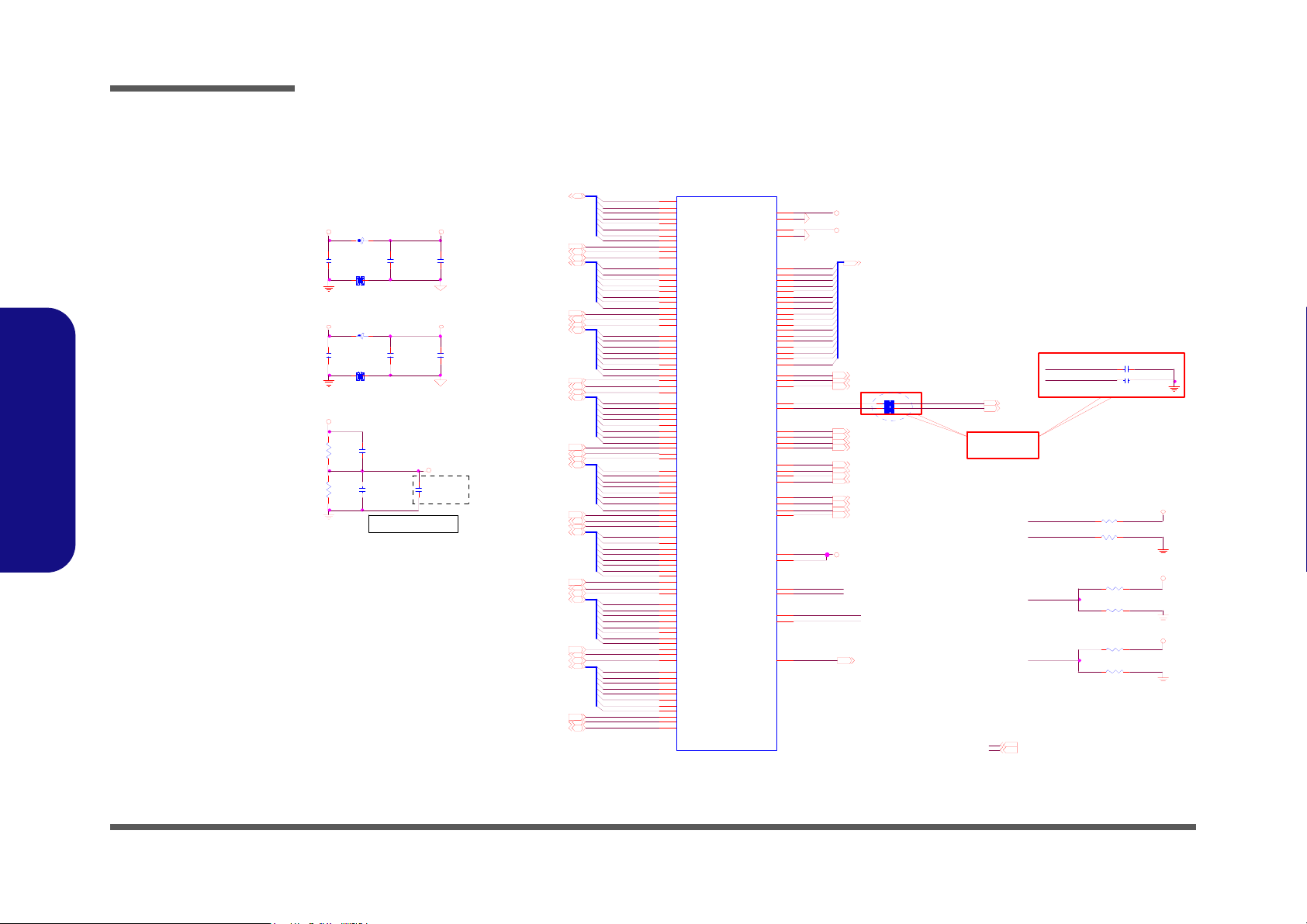

Penryn (Socket-P) 1/2

Sheet 2 of 48

Penryn (Socket-P)

1/2

H_D#[63:0]4

H_SMI#

H_D# 38

H_PW RG D

H_F ER R#

H _D#[63:0] 4

COMP0

H_TMS

H_D# 19

H_D# 18

Z0214

H_ADS TB#04

COM P1

H_T DO

R 1 22 56 _ 0 4

H _DINV #3 4

COMP3

U7

ASC 7525

1

2

3

4

5

6

7

8

VD D

D+

D-

TH ERM

GND

ALERT

SD ATA

SC LK

C 1 54 1 0 0P _5 0 V _ 04

Layout Note:

H _STPC LK #22

H_D# 35

CPU_BSEL1

R151

*330K_04

H_D# 27

H_D# 10

H_D# 6

H_TH RMTR IP#

H_A#33

R 101 51_1%_04

R449

27.4_1% _04

H_DSTBN#2 4

H_PREQ #

R155 *0_0 4

R 1 31 56 _ 0 4

H _DINV #2 4

H_A# 9

DATA GRP 0

DATA GRP 1

DATA GRP 2DATA GRP 3

MISC

JSKT1B

Pen ryn

R26

U26

AA1

Y1

E22

F24

J24

J23

H22

F26

K22

H23

N22

K25

P26

R23

E26

L23

M2 4

L22

M2 3

P25

P23

P22

T24

R24

L25

G22

T25

N25

Y22

AB24

V24

V26

V23

T22

U25

U23

F23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

AE24

AD 24

G25

AA21

AB22

AB21

AC 26

AD 20

AE22

AF23

AC 25

AE21

AD 21

E25

AC 22

AD 23

AF22

AC 23

E23

K24

G24

AF1

H25

N24

U22

AC 20

E5

B5

D24

J26

L26

Y26

AE25

H26

M2 6

AA26

AF24

AD26

AE6

D6

D7

C24

B22

B23

C21

D25

AF26

A26

C23

C3

CO MP[0]

CO MP[1]

CO MP[2]

CO MP[3]

D[0]#

D[1]#

D[10 ]#

D[11 ]#

D[12 ]#

D[13 ]#

D[14 ]#

D[15 ]#

D[16 ]#

D[17 ]#

D[18 ]#

D[19 ]#

D[2]#

D[20 ]#

D[21 ]#

D[22 ]#

D[23 ]#

D[24 ]#

D[25 ]#

D[26 ]#

D[27 ]#

D[28 ]#

D[29 ]#

D[3]#

D[30 ]#

D[31 ]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[4]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

D[48]#

D[49]#

D[5]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[6]#

D[60]#

D[61]#

D[62]#

D[63]#

D[7]#

D[8]#

D[9]#

TEST5

DIN V[0]#

DIN V[1]#

D INV[2]#

D INV[3]#

DPRSTP#

DPSLP#

DPWR#

DSTB N [0]#

DSTB N [1]#

DSTB N[2]#

DSTB N[3]#

DSTBP[0]#

DSTBP[1]#

DSTBP[2]#

DSTBP[3]#

GTL REF

PSI#

PW RG OOD

SLP#

TEST3

BSEL[0]

BSEL[1]

BSEL[2]

TEST2

TEST4

TEST6

TEST1

TEST7

R oute H_TH ERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil spacing.

V_TH ERM

R142 0_06

Close to Thermal IC

3.3V 12,19,20,22,23,24,26,31,32,33,38,39,40

H_A#29

C552

.01U_16V_X7R_04

C686 Close to TEST4 (Pin AF26)

H_DPW R #_ RH_NM I

H_DIN V# 04

H_D# 56

H_IE R R#

H_A#11

R156 *10K_04

H_A#31

Z0201

H_T HER MD A

R 88 56_1%_04

H_D E FER# 4

H_D# 11

H_D# 30

R12 6 *1 K_04

R 1 57 4 . 7K _0 4

ADM1032 1000p

F75383M 2200p

H_DPRS TP# 6,37

H_B N R# 4

H_D# 5

Layout Note:

H_H IT# 4

H_IGN NE#22

H_D# 54

H_D# 4

H_T DI

H_B R 0#

Z0223

H_A#21

1.05VS 3,4,6,7,24,39

H_NM I22

H_D #14

IF US ED D esk to p CPU , H_ CPU RS T# ,H_ PW RG D, H_B RD ,n eed

ad d p ul l hig h re sis to r

H_H ITM# 4

R 1 18 10 _ 0 4

H_DST BP#14

H_PROCHOT# 22

H_NM I

H_D# 20

H_REQ#4

H_IERR #

H_INT R

R 1 32 56 _ 0 4

H_CLK_CPU 25

THER M_AL ERT# 27

H_T MS

Z0212

H_PW RG D

H_A#17

R 1 17 56 _ 0 4

H_T RD Y# 4

H_INTR22

Z0204

Q10

*2N7002W

G

DS

H_DPW R # 4

H_SMI#22

H_D# 29

CPU_BSEL0

H_D# 26

H_A#22

H_A#32

Thermal IC

H_D# 7

H_D# 21

COM P0

H_D#[63:0]4

H_DPW R #_R

H_A#25

C180

* .01U _16V_ X7R _0 4

H_D STB N#14

H_CLK_CPU# 25

H_R S #0 4

C PU_BSEL1

H_THERMDA

H_SM I#

R 1 15 56 _ 0 4

SMC_ CPU_T HER M 27

H_REQ#2

R 92 51_1%_04

H _DSTBP#2 4

H_D# 15

H_A#10

CP U_BSEL225

H_R S #1 4

H_D# 47

H_DPSLP#

H_D# 17

H_T RST#

H_D# 57

C PU_BSEL0

H_P R DY #

H_D STB N#04

H_CPUS LP# 22

H_REQ#1

H_PR OC HOT #

( Si S Re co mma nd at ion 2 00 p)

H_D# 1

H_A#28

Z0216

H_INT R

R44 1

54.9_1%_04

VDD 3

H_D# 12

H_IN IT#

R 1 50 1K _0 4

1.05VS

H_DSTBN#3 4

H_AD S# 4

R 1 30 56 _ 0 4

CPU_GRFE=0.7V

H_B R 0# 4

H_D# 3

H_BR0 #

H_INIT #

H_DPW R #_R

R 89 56_04

R152

*1 00K_ 0 4

Layout Note:

H _AD STB#14

H_PWRGD 4

H_A#35

R 4 60 1K _0 4

H_D# 44

COM P3

R 1 25 56 _ 0 4

R 1 14 56 _ 0 4

H_D# 50

H_STPCLK#

H_TC K

R13 5

*100K_04

R 4 59 1K _0 4

H_D# 59

H_PW RG D

R120 *0_04

PS I# 37

H_A#[35:3]4

H_A#15

R 106 *51_04

H_D# 28

C163

.1U_10V_X7R_04

R 1 27 56 _ 0 4

Lay out note:

R 1 13 56 _ 0 4

H_A20M#22

H_D# 32

C554 * .1U_10V_X7R_04

R 116 *330_04

H_D# 2

H_A# 8

H_A#19

R406

2K_1%_04

H_D# 48

H_A#18

COMP1

H_A#14

CP U_BSEL125

56_04

H_D# 8

R74

54.9_1%_04

C164

1000P_50V _04

1. 05 V S

H_D# 25

H_D# 34

H_A#12

H_A#27

H_DPSLP#

1. 0 5 V S

H_D# 0

H_C P UR ST#

Z0208

H_CPU S LP #

Q9

* NDS 352AP_ NL

G

DS

H_THRMTRIP #

Z0226

H_A#30

H_REQ#0

Z0209

H_CPU S LP #

Z0215

H_P R EQ#

R 1 48 15 0 _ 1% _ 0 4

6-14-5603B-11B

CPU_GTLREF

H_A#[35:3]4

SMD_ CPU_T HER M 27

R 58 39.2_1%_04

C PU_BSEL2

H_D# 49

H_B PM1 #

Z0203

H_D RDY # 4

H_D# 43

R 65 27.4_1%_04

R 1 47 56 _ 0 4

ADDR

GROUP_0

ADDR

GROUP_1

CONTROL

XDP/ITP SIGNALS

H C LK

THERMAL

RESERVED

ICH

JSKT1 A

Penryn

N3

P5

P2

L2

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

J4

U2

V4

M4

N5

T2

V3

B2

D2

D22

L5

L4

K5

M3

N2

J1

A6

H1

M1

V1

D3

A22

A21

E2

AD4

AD3

AD1

AC4

G5

F1

C20

E1

H5

F21

A5

G6

E4

D20

C4

B3

C6

B4

H4

AC2

AC1

D21

K3

H2

K2

J3

L1

C1

F3

F4

G3

A3

D5

AC5

AA6

AB3

C7

A24

B25

AB5

G2

AB6

W3

AA4

AB2

AA3

F6

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[3]#

A[30]#

A[31]#

R SVD[01]

R SVD[02]

R SVD[03]

R SVD[04]

R SVD[05]

R SVD[06]

R SVD[07]

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A20M#

AD S#

AD STB[0]#

AD STB[1]#

R SVD[08]

BC LK[0]

BC LK[1]

BNR #

BPM [0]#

BPM [1]#

BPM [2]#

BPM [3]#

BPR I#

BR0#

DBR #

DBSY #

DEFER #

DR DY #

FER R#

HIT#

HI TM #

IERR #

IG NN E#

IN IT#

LINT0

LINT1

LOCK#

PR DY #

PREQ #

PRO CH OT#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

R ESET#

R S[0]#

R S[1]#

R S[2]#

SM I#

STPC LK#

TCK

TDI

TDO

THE RMTR IP#

THERM DA

TH ERMDC

TMS

TR D Y #

TR S T #

A[32]#

A[33]#

A[34]#

A[35]#

R SVD[09]

H_TR ST#

H_D# 37

R 66 51_1%_04

H_PRO CH OT #

Z0210

H_B PM3 #

H_F ERR #

R 1 49 68 _ 0 4

R 108 *51_04

H_D# 63

H_D# 41

H_D# 51

Z0213

H_DST BP#04

VDD3 20,23,27,34,35,36,38,40

H_D# 45

R45 8 *1 K_04

1.05VS

H_D# 33

H_A# 4

H_D# 42

H _DPSLP# 6

Z0211

H_D# 60

H_A#13

COMP0, COMP2: 0.5" Max, Zo=27.4 Oh ms(20mil)

COMP1, COMP3: 0.5" Max, Zo=55 Oh ms(5mil)

Best estimate is 18 mils wide trac e for outer

layers and 14 mils wide trace if o n internal

layers.

H_IGN NE#

R 1 58 4 . 7K _0 4

3.3V

H_THERMDC

H_A#16

H_A#23

R 80 54.9_1%_04

THERM_RST#27

H_TD I

H _DSTBP#3 4

H_A2 0M #

VDD 3

H_BPR I# 4

H_D# 62

H_D# 13

H_STPCLK#

H_T CK

H_REQ#3

R 1 34 56 _ 0 4

0.5" max, Zo= 55 Ohms

H_DIN V# 14

H_D BSY# 4

H_B PM2 #

H_B PM0 #

H_A#20

R 119 *56_04

CPU to SB interface

H _D#[63:0] 4

H_IGN NE#

COM P2

H_CPU RS T#

H_A# 7

H_DBR #

H_D# 53

Z0205

CP U_BSEL025

H_D# 61

H_A20M#

H_R S #2 4

COMP2

CPU_BSEL2

Z0225

Lay out Note:

H_D# 58

H_D# 39

H_D# 9

H_A#34

R138 10K_0 4

H _ TH RM TR I P # 2 2

If PR OC HO T# is r out ed b etw ee n CPU , IM VP an d MC H,

pu ll- up r esi st or ha s to be 6 8 ohm ? 5 %. If n ot

us e, pu ll -up r es ist or h as to b e 5 6 oh m ? 5 %

If u se d M6 72

th an d el R 3

H_D# 31

H_A# 6

H_C P URS T# 4

H_F ERR #22

H_D# 46

H_D# 52

H_A# 5

H_D# 40

H_D# 55

R 407 1K_1%_04

H_L OC K# 4

H_D# 16

Z0202

Z0224

H_A# 3

H_A#26

R85

27.4_1%_04

H _REQ# [4:0]4

H_D B R#

I f us ed M6 72 th an

d el R 40 an d add R 42

H_D# 22

H_D# 24

R 100 51_1%_04

H_IN IT# 22

PSI#

H_T HER MD C

20MIL

H_D# 36

Z0206

Z0207

H_A#24

C553

1U_6.3V_X5R_06

R 57 680_04

V_THERM

R 1 37 * 1 0m i l_ s h or t

H_D# 23

R 73 150_1% _04

Schematic Diagrams

B.Schematic Diagrams

Penryn (Socket-P) 1/2 B - 3

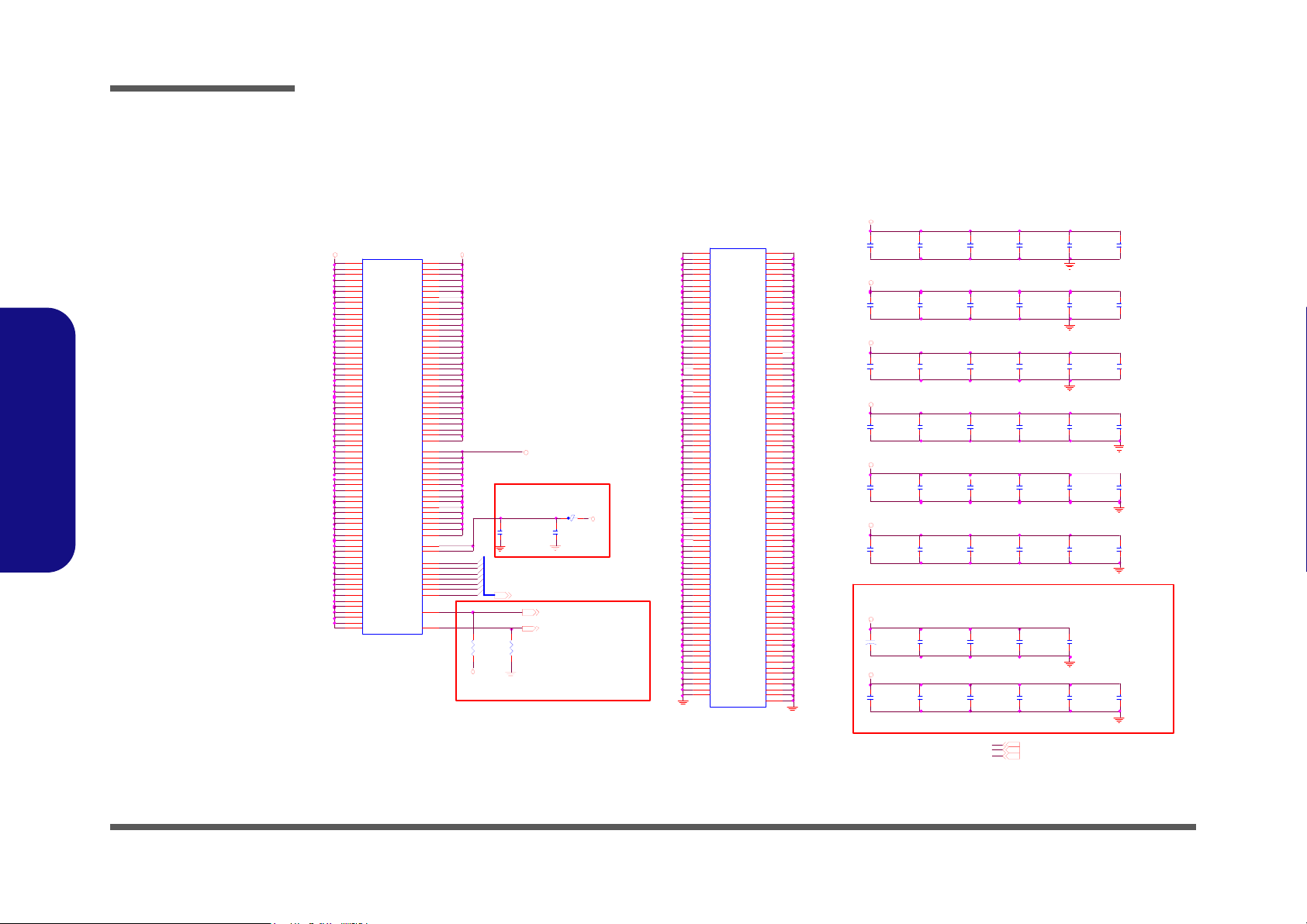

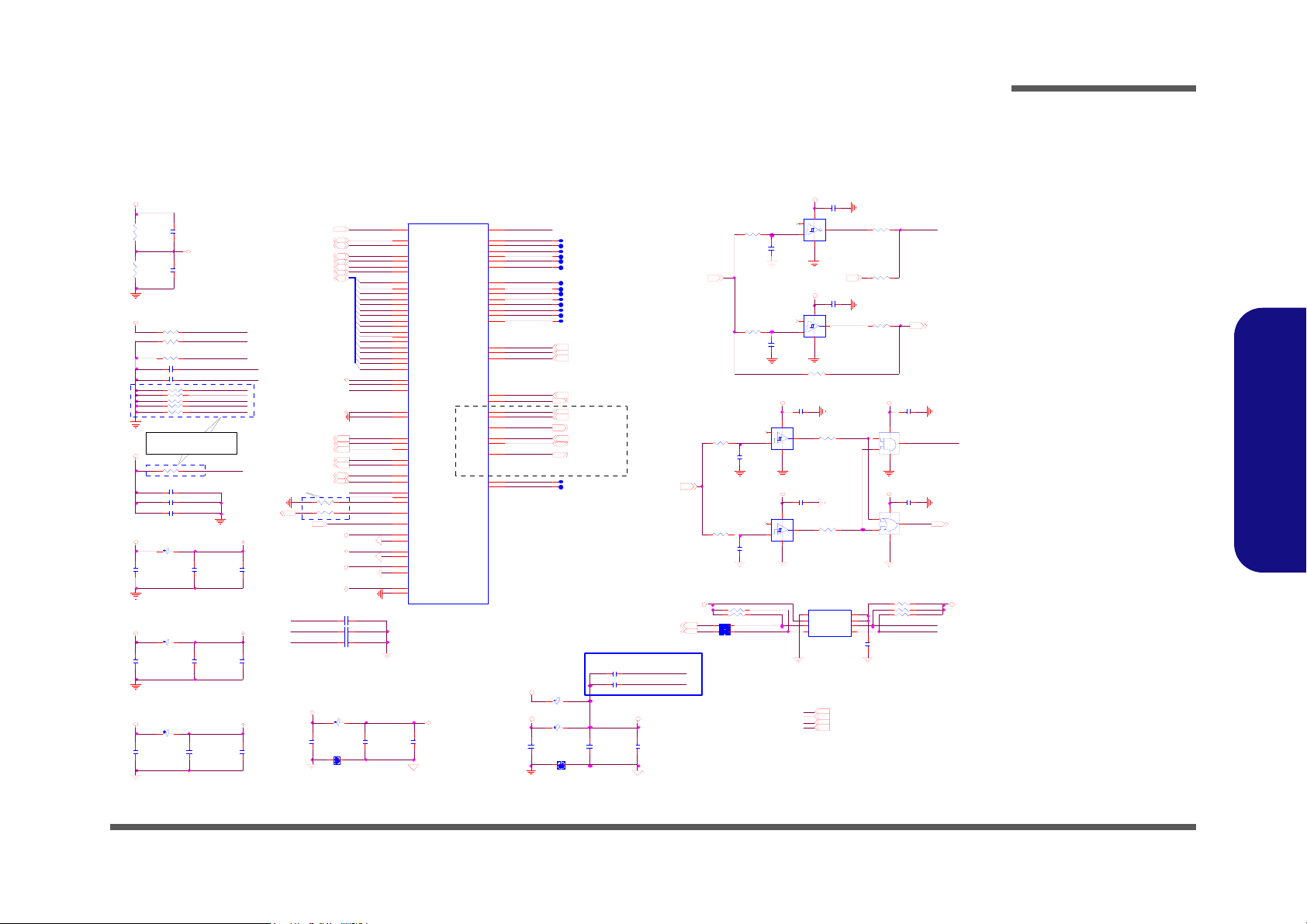

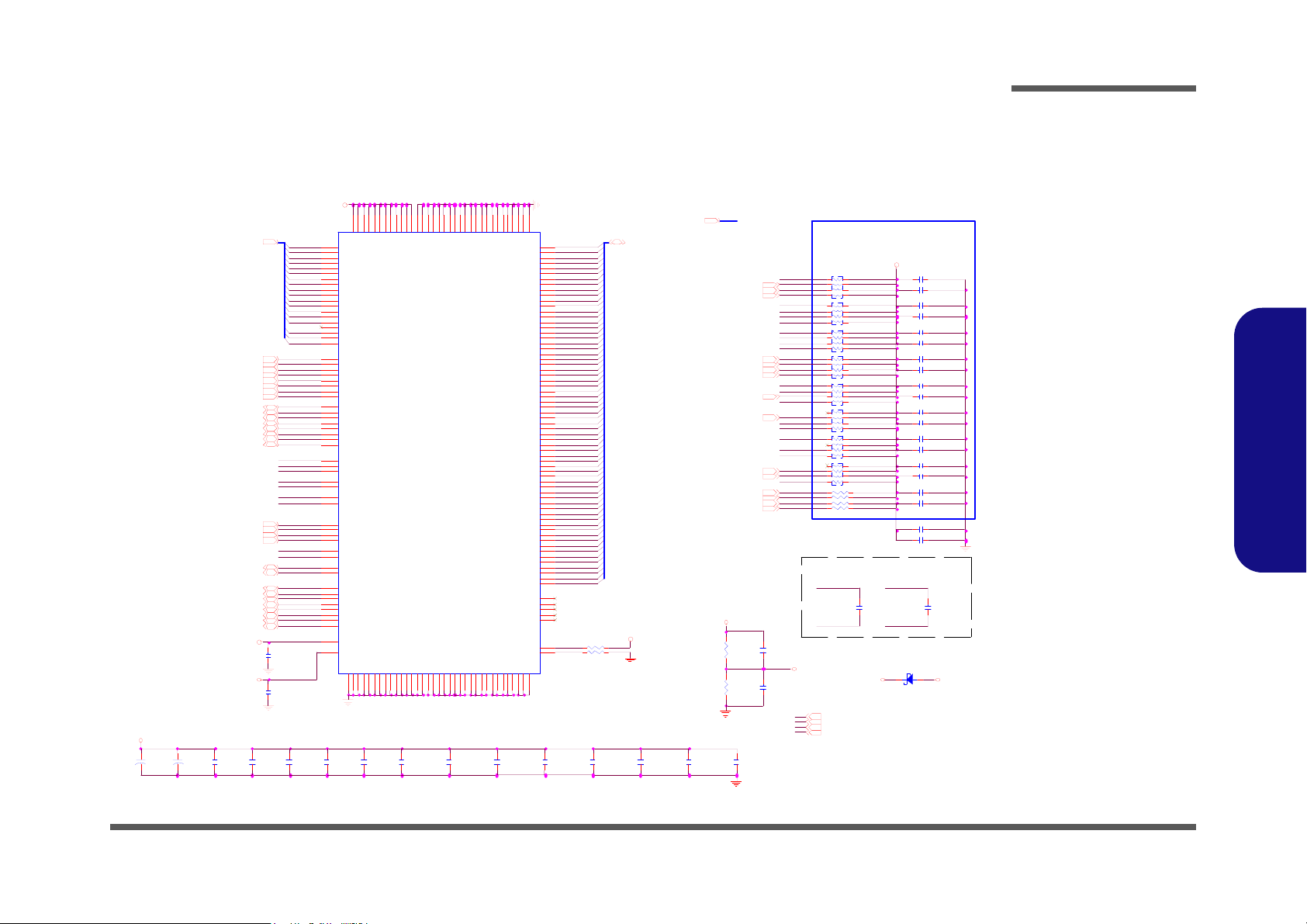

Page 4

Schematic Diagrams

C141

.1U _10V _X7R_04

C88

1U _6.3V_X5R_06

C58 4

1U _ 6 . 3V _X5 R _0 6

VC ORE

Power Plane

C129

10U_6.3V_X5R _08

VSSSEN SE

C56 4

10U_6.3V_X5R_08

H_VID2

C86

.1U_10V_X7R _04

C124

1U_6.3V_X5R _06

C100

1U_6.3V_X5R _06

H _ V I D [6 : 0] 37

C161

.01U_16V_X7R _04

VC ORE

C51

1U_6.3V_X5R _06

PLACE NEAR CPU

C111

.1U_10V_X7R_04

C95

10U_6.3V_X5R _08

C566

10U_6.3V_X5R_08

C85

.1U_10V_X7R _04

H_VID1

C585

1U _ 6. 3V _X 5 R _ 0 6

Check cap for santa rosa platform

VCC SEN SE 3 7

C577

10U_6.3V_X5R _08

C12 6

.1U_10V _X7R _04

1.05VS

C62

.1U_10V_X7R _04

C128

1U _6.3V_X5R_06

H_VID3

C582

.1U_10V_X7R _04

C593

10U_6.3V _X5R_08

C159

10U_6.3V_X5R _08

C50

10U_6.3V_X5R_08

C49

1U _ 6. 3V _X 5 R _ 0 6

H_VID4

C572

.1U_10V_X7R_04

C59

10U_6.3V_X5R_08

C581

.1U _10V _X7R_04

+

C57 4

15 0 U _4 V _ B 2

VSSSEN SE 37

C568

10U_6.3V _X5R_08

VC ORE

VC ORE

R21

100_1%_04

PLACE NEAR CPU

H_VID5

C75

1U_6.3V_X5R _06

C46

.1U _10V _X7R_04

1 . 05 V S 2, 4, 6 , 7 , 2 4 , 3 9

C68

1U_6.3V_X5R _06

2A

6-07-10611-7C0

VCO RE 3 7

C67

.1U_10V_X7R _04

N ea r pi n B2 6

H_VID6

C155

.1U_10V_X7R _04

Ro ut e VC CS EN SE a nd

V SSSE NS E tr ac es at 27.4

oh ms w it h 50 m il s sp ac in g.

Pl ac e PU a nd P D wi th in 1

inch of CPU.

C65

10U_6.3V_X5R _08

L1 2

HCB1608KF-121T25

VC ORE

VC ORE

Layout note:

1.05VS

C580

10U_6.3V_X5R _08

C116

.1U_10V_X7R _04

C61

10U_6.3V_X5R_08

1. 5V S

C565

10U_6.3V_X5R_08

C146

10U_6.3V _X5R_08

Layout note:

C594

10U_6.3V_X5R _08

JSKT1C

Pen ryn

.

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC 10

AB10

AB12

AB14

AB15

AB17

AB18

AB20

AB7

AC 7

AC 9

AC 12

AC 13

AC 15

AC 17

AC 18

AD 7

AD 9

AD 10

AD 12

AD 14

AD 15

AD 17

AD 18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

B26

J6

K6

M6

J21

K21

M2 1

N21

N6

R21

R6

T21

T6

V21

W21

AF7

AD 6

AF5

AE5

AF4

AE3

AF3

AE2

AE7

C26

G21

V6

VCC [00 1]

VCC [00 2]

VCC [00 3]

VCC [00 4]

VCC [00 5]

VCC [00 6]

VCC [00 7]

VCC [00 8]

VCC [00 9]

VCC [01 0]

VCC [01 1]

VCC [01 2]

VCC [01 3]

VCC [01 4]

VCC [01 5]

VCC [01 6]

VCC [01 7]

VCC [01 8]

VCC [01 9]

VCC [02 0]

VCC [02 1]

VCC [02 2]

VCC [02 3]

VCC [02 4]

VCC [02 5]

VCC [02 6]

VCC [02 7]

VCC [02 8]

VCC [02 9]

VCC [03 0]

VCC [03 1]

VCC [03 2]

VCC [03 3]

VCC [03 4]

VCC [03 5]

VCC [03 6]

VCC [03 7]

VCC [03 8]

VCC [03 9]

VCC [04 0]

VCC [04 1]

VCC [04 2]

VCC [04 3]

VCC [04 4]

VCC [04 5]

VCC [04 6]

VCC [04 7]

VCC [04 8]

VCC [04 9]

VCC [05 0]

VCC [05 1]

VCC [05 2]

VCC [05 3]

VCC [05 4]

VCC [05 5]

VCC [05 6]

VCC [05 7]

VCC [05 8]

VCC [05 9]

VCC [06 0]

VCC [06 1]

VCC [06 2]

VCC [06 3]

VCC [06 4]

VCC [06 5]

VCC [06 6]

VCC [06 7]

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCC A[01]

VCC P[03]

VCC P[04]

VCC P[05]

VCC P[06]

VCC P[07]

VCC P[08]

VCC P[09]

VCC P[10]

VCC P[11]

VCC P[12]

VCC P[13]

VCC P[14]

VCC P[15]

VCC P[16]

VCCSENSE

VID [0]

VID [1]

VID [2]

VID [3]

VID [4]

VID [5]

VID [6]

VSS SENS E

VCC A[02]

VCC P[01]

VCC P[02]

1.05VS

Z 0301

C140

1U_6.3V_X5R _06

C130

.1U_10V_X7R _04

C575

10U_6.3V_X5R _08

130mA

1 . 5V S 6 , 3 3, 3 5

VCORE

C11 3

1U _ 6 . 3V _X5 R _0 6

V CC SENSE

C118

10U_6.3V_X5R _08

JSKT 1D

Penryn

.

P6

AE11

A8

A11

A14

A16

A19

A23

AF2

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3 A25

AF21

AF19

AF16

AF13

AF11

AF8

AF6

A2

AE26

AE23

AE19

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

Y6

A4

AE14

AE16

AE8

AF25

VSS [082]

VSS [148]

VSS[002]

VSS[003]

VSS[004]

VSS[005]

VSS[006]

VSS[007]

VSS[008]

VSS[009]

VSS[010]

VSS[011]

VSS[012]

VSS[013]

VSS[014]

VSS[015]

VSS[016]

VSS[017]

VSS[018]

VSS[019]

VSS[020]

VSS[021]

VSS[022]

VSS[023]

VSS[024]

VSS[025]

VSS[026]

VSS[027]

VSS[028]

VSS[029]

VSS[030]

VSS[031]

VSS[032]

VSS[033]

VSS[034]

VSS[035]

VSS[036]

VSS[037]

VSS[038]

VSS[039]

VSS[040]

VSS[041]

VSS[042]

VSS[043]

VSS[044]

VSS[045]

VSS[046]

VSS[047]

VSS[048]

VSS[049]

VSS[050]

VSS[051]

VSS[052]

VSS[053]

VSS[054]

VSS[055]

VSS[056]

VSS[057]

VSS[058]

VSS[059]

VSS[060]

VSS[061]

VSS[062]

VSS[063]

VSS[064]

VSS[065]

VSS[066]

VSS[067]

VSS[068]

VSS[069]

VSS[070]

VSS[071]

VSS[072]

VSS[073]

VSS[074]

VSS[075]

VSS[076]

VSS[077]

VSS[078]

VSS[079]

VSS[080]

VSS[081] VSS[162]

VSS [161]

VSS [160]

VSS [159]

VSS [158]

VSS [157]

VSS [156]

VSS [155]

VSS [154]

VSS [153]

VSS [152]

VSS [151]

VSS [083]

VSS [084]

VSS [085]

VSS [086]

VSS [087]

VSS [088]

VSS [089]

VSS [090]

VSS [091]

VSS [092]

VSS [093]

VSS [094]

VSS [095]

VSS [096]

VSS [097]

VSS [098]

VSS [099]

VSS [100]

VSS [101]

VSS [102]

VSS [103]

VSS [104]

VSS [105]

VSS [107]

VSS [108]

VSS [109]

VSS [110]

VSS [111]

VSS [112]

VSS [113]

VSS [114]

VSS [115]

VSS [116]

VSS [117]

VSS [118]

VSS [119]

VSS [120]

VSS [121]

VSS [122]

VSS [123]

VSS [124]

VSS [125]

VSS [126]

VSS [127]

VSS [128]

VSS [129]

VSS [130]

VSS [131]

VSS [132]

VSS [133]

VSS [134]

VSS [135]

VSS [136]

VSS [137]

VSS [138]

VSS [139]

VSS [140]

VSS [141]

VSS [142]

VSS [143]

VSS [144]

VSS [145]

VSS [146]

VSS [106]

VSS[001]

VSS [149]

VSS [150]

VSS [147]

VSS [163]

H_VID0

C58 3

.1U_10V _X7R _04

C123

10U_6.3V_X5R _08

R22

100_1%_04

5/10

VCO RE

C77

.1U_10V_X7R_04

VC ORE

Sheet 3 of 48

Penryn (Socket-P)

2/2

B.Schematic Diagrams

B - 4 Penryn (Socket-P) 2/2

Penryn (Socket-P) 2/2

Page 5

SiSM672 Host, PCIE 1/5

PE0R X5#12

NB_G T LR EF

H_BNR#2

H _D#61

H _DS TB N# 3 2

Z0406

EXTERNAL VGA ( M760SU ) : 0.1U

H_A#29

H _D#59

NB_COMP#

Z0453

H_CLK_NB#25

H_HITM#2

PE0R X0#12

PE0R X612

H _D#53

H _D#27

H_A# 4

1.8V S 5,6,7,11,13, 14,15,17,19,21, 22,23,24,25,35

HD VAP 0 1 1

Z0401

C4XA VDD

Z0413

C619 *.1U_10V_X7R_04

PE0R X412

HD VBP 1 1 1

C631 *.1U_10V_X7R_04

PE 0TX3# 12

H D VBN2 1 1

H _D#11

H_D#0

H _D#38

H_A#15

H _D#56

Z0444

H _DI NV #3 2

Z0463

PCIE _WAKE #23,33

H _D#32

Z0439

C4XAVSS

PE0R X012

H_A#23

H_A#11

H_A#19

Z0402

PE0R X2#12

H _D#18

H_R EQ #3

H _D#23

H_R S# 12

PCIE_CLK _NB# 25

PE 0TX3 12

H_D#8

H_R EQ #1

H_DSTB P#1 2

H_A#26

H _D#30

H _D#40

C264

.01U_16V_X7R_04

PC I_INT #A6,21,28

Place under M671MX

solder side

H _DI NV #1 2

H_A# 8

Z0452

N C 10 N C _0 4

C624 *.1U_10V_X7R_04

H _D#49

H _D#57

C 1XAVD D

H_R S# 02

H _D#51

H _D#16

C240

.01U_16V_X7R_04

H_PWRGD2

H _D#25

H_AD S#2

H_A#18

Z0451

C620 *.1U_10V_X7R_04

PE0R X4#12

PE 0TX0# 12

PE 0TX6 12

Z0409

1.05VS

H_D#7

H_A# 7

1. 2 V S

H_A#27

Z0405

PE 0TX7# 12

NC2 NC_04

H D VAN2 1 1

H _D#62

Z0438

C23 0

.1U_1 0V_X7R_ 04

H_L OC K#2

PE0R X712

H _D#55

H _A DSTB#12

H _D#28

PE 0TX5# 12

H_A# 5

C606

.01U_16V_X7R_04

H _D#21

H _D#33

H _DI NV #2 2

H_R EQ #0

H _DS TB N# 1 2

Z0443

C 598

10U _10V_08

H_D#9

H_A#32

Z0417

H _DI NV #0 2

H_B R0 #2

PE0R X512

L18 H CB1005KF-121T20

H _D#12

Z0450

C622 *.1U_10V_X7R_04

C255

.1U_10V_X7R_04

NB_PCREQ#

Z0412

L65 H CB1005KF-121T20

H_D#4

H _D#50

H _D#52

C260

. 0 1U _ 1 6V _ X7 R _ 04

H _DR DY #2

H _D#45

H_D#3

C605

.1U_10V_X7R_04

C615 *.1U_10V_X7R_04

C4XAVS S

H_HIT#2

Z0410

Z0416

C617 *.1U_10V_X7R_04

C1XAVDD

PE 0TX2# 12

H _D#44

H_A#10

Z0404

C618 *.1U_10V_X7R_04

H_BPRI#2

PE0R X3#12

HD VAP 2 1 1

R 178 110_1%_06

Z0411

C616 *.1U_10V_X7R_04

1.05VS

H_D#6

H _D#41

Z0447

PE0R X6#12

PE 0TX1 12

H _D#43

Z0446

L23

H CB1005KF-121T20

H _D#39

H _A#[35:3]2

H _CP UR ST #2

PE0R X312

PE 0TX2 12

Host

U32C

SiSM 672

R34

E21

P32

B16

C17

A17

B18

F18

G18

P31

N30

P33

L32

P30

P28

F21

K34

M31

K33

M33

M32

L34

N32

N34

M34

T34

R30

R29

R32

P34

U34

AA 34

N29

M30

M28

L30

L29

K28

K31

K30

H31

G34

H32

G32

K32

F34

F33

F32

H28

J30

H30

G29

J29

G30

F30

D33

D34

B32

B33

C34

D31

A32

A31

C31

B30

C30

A30

D28

G28

C29

C28

E28

E27

C27

G26

E26

D26

B26

A26

C26

G22

C24

A25

B24

C25

A24

E23

E25

G24

D22

C22

E22

C23

A23

A22

B22

T32

T28

T31

T33

T30

U32

U30

V34

U29

V33

V32

V28

V31

W34

Y33

W32

V30

W30

Y34

Y28

W29

Y32

Y30

Y31

AA 32

AA 30

AA 29

AB 33

AB 34

AB 32

AC 34

AB 30

AB 31

J32

E32

F27

F23

H33

E31

B28

D24

H34

D32

A28

E24

A21

C21

W24

U24

R24

N24

L21

PC REQ#

NC 2 (D PW R #)

ED RD Y#

C1XAVD D

C1XAVS S

C4XAVD D

C4XAVS S

CP UC L K

CP UC L K#

HTR DY #

BPR I#

BR EQ0#

HLO CK #

DE FER #

CP UPW RG D

CP UR ST #

RS 0#

RS 1#

RS 2#

DR D Y#

BN R#

DB SY#

HIT#

HITM #

AD S#

HR EQ 0#

HR EQ 1#

HR EQ 2#

HR EQ 3#

HR EQ 4#

HA STB 0#

HA STB 1#

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

H D10#

H D11#

H D12#

H D13#

H D14#

H D15#

H D16#

H D17#

H D18#

H D19#

H D20#

H D21#

H D22#

H D23#

H D24#

H D25#

H D26#

H D27#

H D28#

H D29#

H D30#

H D31#

H D32#

H D33#

H D34#

H D35#

H D36#

H D37#

H D38#

H D39#

H D40#

H D41#

H D42#

H D43#

H D44#

H D45#

H D46#

H D47#

H D48#

H D49#

H D50#

H D51#

H D52#

H D53#

H D54#

H D55#

H D56#

H D57#

H D58#

H D59#

H D60#

H D61#

H D62#

H D63#

HA 3#

HA 4#

HA 5#

HA 6#

HA 7#

HA 8#

HA 9#

HA 10#

HA 11#

HA 12#

HA 13#

HA 14#

HA 15#

HA 16#

HA 17#

HA 18#

HA 19#

HA 20#

HA 21#

HA 22#

HA 23#

HA 24#

HA 25#

HA 26#

HA 27#

HA 28#

HA 29#

HA 30#

HA 31#

HA 32#

HA 33#

HA 34#

HA 35#

DBI0#

DBI1#

DBI2#

DBI3#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

H D STBP0#

H D STBP1#

H D STBP2#

H D STBP3#

HPCOMP

HN CO M P

HV REF

HV REF

HV REF

HV REF

HV REF

NB_P CIE_1.2VS

PE0R X212

Z0448

Z0442

R 1 96 * 5 6 _ 04

H _D#60

H _D#42

H D VBN0 1 1

H_A#21

H _D#46

H_A#34

H _A DSTB#02

PE 0TX1# 12

Z0403

PE0R X7#12

C273

.01U_16V_X7R_04

C627 *.1U_10V_X7R_04Z0449

C210

10U_10V_08

H_D E FER #2

H_A#28

H _DS TB N# 0 2

H_REQ#[4:0]2

1. 2V S 7 , 3 5

H_A#30

H _D#15

H_A#17

PE 0TX5 12

H_R EQ #4

H_A# 6

Z0408

H_A#22

1.8VS

H_D BSY #2

H _D#63

Z0462

HD VAP 1 1 1

H _D#20

H_A#13

H_R S# 22

H _D#54

C1XAVS S

H_A#31

Z0414

C630 *.1U_10V_X7R_04

R19 5

75_1%_04

PCIE

U32D

SiSM 672

E4

E5

F1

G1

H3

H2

H1

J1

V1

V6

W4

W1

W2

Y1

Y6

AA4

AA 1

AB 1 AB6

AC4

AB 2

AC 1

AD 1

AD6

AE4

AE 1

AE 2

AF 1

AG 1

T2

U1

K1

K2

L1

M1

N1

N2

P1

R1

T1

J6

G6

G4

J4

L6

M4

P6

P4

H6

G5

K6

J5

M6

M5

R6

P5

W6

W5

AA6

AA5

AC6

AC5

AE6

AE5

P7

R7

T7

U7

V7

D7

G16

T5

T4

PER P0

PER N 0

PER P1

PER N 1

PER P2

PER N 2

PER P3

PER N 3

PER N 9

PETP8

PETP9(H DV BP2)

PER P10

PER N 10

PER P11

PETP10(H DV BP1)

PETP11(H DV BP0)

PER N 11

PERP12 PETP12

PETP13(H DV AP2)

PER N 12

PER P13

PER N 13

PETP14(H DV AP1)

PETP15(H DV AP0)

PER P14

PER N 14

PER P15

PER N 15

PER N 8

PER P9

PER P4

PER N 4

PER P5

PER N 5

PER P6

PER N 6

PER P7

PER N 7

PER P8

PETP2

PETP0

PETP1

PETP3

PETP4

PETP5

PETP6

PETP7

PE TN 0

PE TN 1

PE TN 2

PE TN 3

PE TN 4

PE TN 5

PE TN 6

PE TN 7

PE TN 8

PETN 9(HD VBN2 )

PE TN 10(HD VBN1 )

PE TN 11(HD VBN0 )

PETN12

PE TN 13(HD VAN2 )

PE TN 14(HD VAN1 )

PE TN 15(HD VAN0 )

PC IEAVD D

PC IEAVD D

PC IEAVD D

PC IEAVD D

PC IEAVD D

PM E#

IN TX#

REFCLK+

REFCLK-

PE 0TX4# 12

1. 05 V S

H D VAN0 1 1

H _D#24

H_A#12

Z0415

PE 0TX0 12

H _D#36

C629 *.1U_10V_X7R_04

R 183 10_1%_04

H_DSTB P#0 2

H D VAN1 1 1

Z0441

Z0454

H_D#5

H _D#31

C625 *.1U_10V_X7R_04

C4XAVDD

H_A#25

NB_GTLREF

PE 0TX4 12

C623 *.1U_10V_X7R_04

1.05VS 2,3,6,7,24, 39

H _D#22

H _D#48

H_A#14

1.8VS

H_D#2

PCIE_CLK _NB 25

H _D#13

H_A#16

Z0407

HD VBP 2 1 1

H_R EQ #2

H _D#29

NB_COMP

C1XAVSS

PE0R X1#12

PE 0TX7 12

H _D#17

C628 *.1U_10V_X7R_04

IN TERN AL VGA ( M 740S ) : R

H _D#58

H _D#[63:0] 2

H _D#19

H _D#34

H _D#35

Z0455

R19 2

150_1%_04

H_DSTB P#3 2

H _D#14

H _DS TB N# 2 2

H_A# 9

H_D#1

H_DPWR#2

HD VBP 0 1 1

H _D#47

H _D#26

Z0445

NB_GTLREF=0.7V

PE 0TX6# 12

H_DSTB P#2 2

H D VBN1 1 1

H_A#35

Z0440

H_A#33

H_T RDY #2

H_A#20

H _D#37

NB_PCREQ#

77mA

H_CLK_NB25

H_A# 3

PE0R X112

H_A#24

C 262

. 1U _10V_X7R _04

C621 *.1U_10V_X7R_04

H _D#10

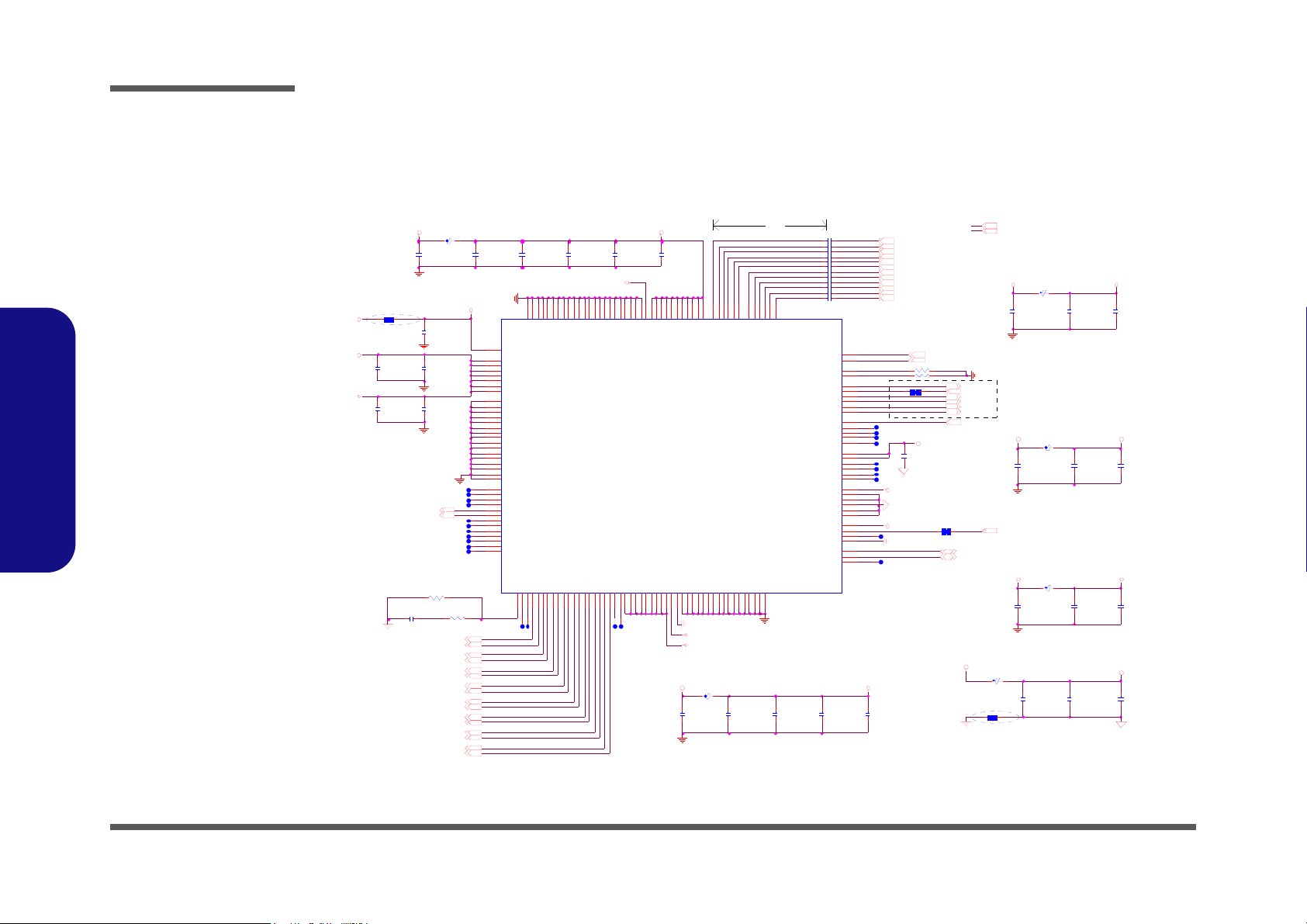

Sheet 4 of 48

SiSM672 Host,

PCIE 1/5

Schematic Diagrams

B.Schematic Diagrams

SiSM672 Host, PCIE 1/5 B - 5

Page 6

Schematic Diagrams

D4XAVSS

D1XAVSS

M_DQS59, 1 0

D 1XAVD D

M_A _D Q36

M_A _D Q25

M_A _D Q6

C 290 *10P_50V_04

M_WE# 9,10

M_A _D Q14

M_A_A4

M_DQS79, 1 0

M_ODT1 9,10

M_A _D Q41

M_A _D Q32

M_A _D Q4

R205 36_1%_06

Place close to

M671MX

M_ O C D V RE F _P

M_COMP_P

M_DDRVREF

M_CKE3 10

M_CKE2 10

M_A _D Q58

M_A _D Q59

M_A_A0

M_ FW D S D CL K OA _D

M_A _D Q11

M_A _D Q42

????

M_DQS69, 1 0

R224 40.2_1%_04

D 1XAV SS

R208

1K_1%_04

M_ D QS 5 #9,10

C 658

. 1U _10V_X7 R_04

M_ A_ DQ [6 3: 0]9,10

M_ A_ DQ [6 3: 0]9,10

M_A _D Q13

M_A _D Q44

M_A _D Q0

NC12 NC_04

M_ D QS 7 #9,10

R211 40.2_1%_04

M_A_A2

M _A_A[1 7: 0] 9,10

M_CS2# 10

M_A_A17

C289

.1U _10V_X7 R_0 4

M_OC DVREF_N

M_A _D Q63

M_A _D Q19

M_A _D Q10

M_A _D Q51

M_A _D Q31

M_A _D Q49

1. 8 V

M_A _D Q55

M_A _D Q2

M_A_A8

M_A _D Q50

D1XAVDD

M_A _D Q61

M_ D QS 6 #9,10

M_DM09, 10

M_A _D Q33

M_CO MP_P

R220 *10mil_short

M_FW DSDCLKOA_D C291 * 10P_50V_04

M_ D QS 0 #9,10

M_CKE1 9,10

M_A _D Q22

1.8V 7, 9,10,22,23,24,35,39,40

M_A_A10

M_DM19, 10

M_A _D Q28

M _FW DS DC LK OA_D _R

M_DM49, 10

M_A _D Q39

DRAM

U32B

SiS M672

AM15

AM17

AM18

AD28

AD30

AD31

AE29

AE30

AE32

AF31

AF32

AF33

AF34

AG34

AH24

AH32

AH33

AH34

AJ25

AK21

AK25

AK26

AK33

AL25

AL34

AM25

AM26

AM30

AM31

AN24

AN26

AN28

AN32

AP21

AP25

AP26

AP29

AJ30

AH16

AL19

AP24

AM28

AM27

AP27

AP28

AK24

AK19

AL17

AL15

AJ29

AH28

AF28

AJ34

AH31

AG30

AF30

AG32

AJ32

AJ31

AK34

AH30

AL32

AM33

AK32

AG29

AM34

AL31

AM32

AP32

AP31

AM29

AK30

AK29

AJ27

AK28

AK20

AM20

AM19

AJ19

AN20

AJ21

AP19

AH20

AK18

AJ17

AK17

AP16

AH18

AP18

AN18

AP17

AN16

AK16

AN14

AJ15

AP15

AM16

AK15

AP14

AL13

AM13

AM12

AJ13

AM14

AK14

AN12

AH14

AK13

AP12

AP13

B15

A15

AP10

AP11

AM23

AP22

AJ23

AK12

AH12

AP23

AH22

AM22

AM21

AK22

AP20

AN22

AL21

AN30

AP30

AH26

AK27

B6

AD18

AD23

D QS6A#

D QS5A#

DQM5A

DQM0A

MD1A

MD0A

MD3A

MD7A

MD4A

MD6A

DQS0A

D QS0A#

MD5A

MD2A

MA0 A

DQS1A

D QS1A#

DQM1A

DDRCOMP

DQM4A

MA7 A

DD RC OM N

DQS2A

MA3 A

D QS2A#

MA2 A

MA5 A

DQS3A

D QS3A#

MA11A

MA6 A

MA15A

DQM3A

MA16A

MA1 A

MA4 A

MA17A

DQM2A

DQM6A

D QS4A#

MA12A

MA13A

MA14A

MA8 A

MA9 A

MA10A

DQS4A

DQS5A

DQS6A

OCDVREFN

OC DV R EF P

MD8A

MD9A

MD10A

MD11A

MD12A

MD13A

MD14A

MD15A

MD16A

MD17A

MD18A

MD19A

MD20A

MD21A

MD22A

MD23A

MD24A

MD25A

MD26A

MD27A

MD28A

MD29A

MD30A

MD31A

MD32A

MD33A

MD34A

MD35A

MD36A

MD37A

MD38A

MD39A

MD40A

MD41A

MD42A

MD43A

MD44A

MD45A

MD46A

MD47A

MD48A

MD49A

MD50A

MD51A

MD52A

MD53A

MD54A

MD55A

MD56A

MD57A

MD58A

MD59A

MD60A

MD61A

MD62A

MD63A

DQM7A

DQS7A

D QS7A#

D1XAVSS

D1X AVD D

D4XAVSS

D4X AVD D

R ASA#

C ASA#

WEA#

FW DS DC LK OA

FWD SDC LKOA#

CS0 A#

CS1 A#

CS2 A#

CS3 A#

ODT0A

ODT1A

ODT2A

ODT3A

C KEA0

C KEA1

C KEA2

C KEA3

S3AUXSW #

DD RV REF 0

DD RV REF 1

Place under M671MX

solder side

M_CAS# 9,10

M_A _D Q26

NB_S3AUXSW# 31

M_A_A11

L67 H CB1005K F-121T20

M_CKE0 9,10

M_A _D Q16

M_A _D Q9

R206 36_1%_06

R207

1K_1%_04

M_OCDVREF_N=0.969V

M_DM59, 10

M_A _D Q15

M_A _D Q60

M_A _D Q43

M_A _D Q40

C65 5

.01U _16V_X7R_04

M_DM39, 10

M_A _D Q7

M_A _D Q1

M_A _D Q48

M_A_A13

C287

.1U_10V_X7R_04

M_ D QS 4 #9,10

M_A _D Q35

M_A _D Q21

M_OCDVREF_P=0.874V

1.8V S

M_A _D Q47

M_A_A14

M_A _D Q18

M_A_A1

M_CS0# 9,10

M _FW DS DC LK OA_D #_ R

M_A _D Q23

M_OD T2 10

M_FW DSDCLKOA_D 25

R219 *10mil_short

R213 36_1%_06

C656

10U_10V _08

M_DDRVREF=0.9V

M_A _D Q34

M_A _D Q20

M_A _D Q8

D4XAVDD

M_DQS19, 1 0

M_OD T3 10

M_A _D Q45

M_A _D Q53

M_DD RV REF

M_ FW DS D C L KO A_ D # 2 5

D 4XAV SS

M_DQS49, 1 0

M_ODT0 9,10

M_DM79, 10

M_OC DVREF_P

M_A _D Q3

M_ D QS 1 #9,10

M_A _D Q56

M_DQS39, 1 0

M_DQS09, 1 0

M_ D QS 3 #9,10

M_A _D Q30

M_A_A7

M_A _D Q24

M_A_A3

M_A_A15

M_A _D Q38

M_CO MP_N

M_A _D Q27

M_A _D Q29

C61 2

.01U _16V_X7R_04

1.8V

M_CS1# 9,10

M_A_A5

L64 H CB1005K F-121T20

D 4XAVD D

M_ O C D V RE F _N

M_A _D Q5

M_ FW D S D CL K OA _D #

M_A_A16

1. 8 V

M_A _D Q46

M_DM29, 10

D03

M_A _D Q37

1.8V S

1.8V S 4,6, 7,11,13,14,15,17,19,21,22,23,24,25,35

NC13 NC_04

M_DM69, 10

M_A_A12

C 611

. 1U _10V_X7 R_04

M_ A_ DQ [6 3: 0]9,10

M_A _D Q57

M_A_A6

M_ A_ DQ [6 3: 0]9,10

M_A _D Q52

M_COMP_N

C288

.1U _10V_X7 R_0 4

1. 8 V

R222 36_1%_06

M_ D QS 2 #9,10

M_CS3# 10

M_FW DSDCLKOA_D#

M_ A_ DQ [6 3: 0]9,10

M_A _D Q12

M_A_A9

M_A _D Q62

C597

10U_10V _08

M_ A_ DQ [6 3: 0]9,10

M_ A_ DQ [6 3: 0]9,10

M_RAS# 9,10

M_A _D Q54

M_ A_ DQ [6 3: 0]9,10

M_DQS29, 1 0

M_A _D Q17

Sheet 5 of 48

SiSM672 DRAM 2/5

SiSM672 DRAM 2/5

B.Schematic Diagrams

B - 6 SiSM672 DRAM 2/5

Page 7

SiSM672 MuTIOL VGA 3/5

Z_CLK025

C331

.1U_10V_X7R _04

AU X_ PWR OK 22,26

VBC AD 1 1

ZAD 14

DPR STP#_IN V

ECLKAVDD

DAC _GR EEN

C60 9

.1U_10V_X7R_04

R162 1K_1%_04

Z_CO MP_N

D AC_ DD CAD AT

Z0625

R172

33_04

Level Shitt

DAC _ RED19

DAC_DDCADAT19

Z0618

Z0622

L17 HCB1005KF-121T20

1.8VS

M7 60 SU ? ? ?

VCOMP

DAC _ RED

C16 9

*100P_50V_04

1. 8V S

3.3VS

ZAD 11

L26 HCB1005KF-121T20

R 468 56_04

DACAVDD2

DAC_DDCACLK19

Z0624

C245 .1U_16V _04

73mA

ZAD 15

C211

10U_10V_08

AU X_PW ROK

D ACAVS S1

VAC LK 1 1

M760SU ? ? ?

3.3VS

H_DP SLP#2

DPRSTP#_INV

VBVSY NC 11

Z0614

VVBWN

U9

P CA9306DCUR

1

2

3

4

8

7

6

5

GND

VR EF1

SC L1

SD A1

EN

VR EF2

SCL2

SD A2

1.05V <=> 3.3V

10mA

1. 8V S

ZSTB_D#021

R177

33_04

ZAD 12

3. 3 V S

Z0613

DAC _GRE E N19

NB_T ESTM OD E1

ZSTB_D#121

C 237 .1U_10V_X7R_04

DAC_HSYNC19

C 812 *10P_50V_04

ZSTB_D021

PCI_INT#A4, 21 , 2 8

Z0619

C20 8

10U_10V_08

73mA

Z_C OMP_N

Z0601

H_DP R STP#2,37

C223

.01U_16V_X7R_04

VBC LK 1 1

C229

.1U_1 0V_X7R_0 4

1. 5 V S

ZAD 6

6- 01 -74 10 8- Q61

5mA

Z_V REF

3.3VS

R141 *0_04

3.3VS

ZAD 9

VRS ET

R21 4

49.9_1%_04

C 236 .1U_10V_X7R_04

R 175 150_1%_04

1.05VS 2,3,4,7,24,39

Z0608

AG PSTO P# 22

R160 200K_04

U8

74LVC1G08G W

1

2

5

4

3

Z4XAVD D

NC 11 N C_ 04

For SiS VB 307

use only

5m A

Z0603

R185 *0_04

C16 8

.1U_ 10V_X 7R_04

C LK_14M_671MX25

ZAD 0

ZAD 8

Z0629

R191 *0_04

Z0623

AU X_ PWR OK

R194 *0_04

C227

.01U_16V_X7R_04

R 1 76 * 1 0m i l_ s h or t

R139

33_04

1.5VS 3,33,35

N EAR S IS M67 2

Z0617

DAC_VSYNC

C 251 *.1U_16V_04

1. 8 V S

C LK_14M_671M X

3. 3V S

C 249 *.1U_16V_04

C329

.01U_16V_X7R_04

1. 8V S

ZAD[16:0]21

NB_T ESTM OD E2

C526

.1U_ 10V_X 7R_04

AG PBUSY # 22

ZAD 16

R189 *0_04

1. 8V S

ZAD 13

Z0607

L63 HCB1005KF-121T20

D ACAVS S2

1.8VS 4,5,7,11,13,14,15,17,19,21,22,23,24,25,35

ZAD 5

C244

100P_50V_04

Z0606ZAD 1

C610

.1U_10V_X7R_04

VBH SYN C 1 1

3. 3 V S

DAC _BLU E19

L1 9

H CB1005KF-121T20

3.3VS 10,11,19,20,21,22,23,24,25,27,28,29,30,31,32,33,34,35,37

H _DPSLP#_LS

NEA R SI SM6 72

DAC AVSS2

Z0605

DELAY_PWRGD

M760SU ? ?

R184 *0_04

U26

74LVC1G14GW

1

2

53

4

ASL

U32A

SiSM 67 2

AM8

AM9

AM10

AN8

AN10

AP4

AP5

AP8

AP9

AH10

AL7

AL9

AM7

AK10

AM6

AK11

AJ11

AP7

AJ9

AP6

AN6

AK9

AM4

AK6

AK8

AN4

AK7

AL5

AM5

D13

C12

C13

G12

F12

D11

E12

D15

C14

C15

F11

F13

A12

B12

A13

B13

B10

A11

A9

F15

D16

E16

F16

D17

E17

F17

AC32

AD34

AB28

AD32

AD33

AE34

AC30

AC29

A5

C6

A7

A6

D9

C8

E9

E7

D8

F7

AH2

AG3

B8

G1 4

ZAD 16

ZCMP_N

Z4XAVDD

ZUREQ

Z4XAVSS

ZSTB1

ZSTB1#

ZDREQ

ZCMP_P

ZCLK

ZSTB0#

ZVR EF

ZSTB0

ZAD 0

ZAD 1

ZAD 2

ZAD 3

ZAD 4

ZAD 5

ZAD 6

ZAD 7

ZAD 8

ZAD 9

ZAD 10

ZAD 11

ZAD 12

ZAD 13

ZAD 14

ZAD 15

RO UT

GO UT

BOU T

VSY NC

HSY NC

VGP IO0

VGP IO1

VCO MP

VRS ET

VVBWN

VOS CI

INTA#

DAC AVDD1

DAC AVSS1

DAC AVDD2

DAC AVSS2

DC LKAVDD

DC LKAVSS

ECLKAVD D

EN TEST

TESTM OD E0

TESTM OD E1

TESTM OD E2

TR AP0

TR AP1

TR AP2

TR AP3

TR AP4

TR AP5

TR AP6

TR AP7

TR AP8

TR AP9

TR A P 1 0

AUXOK

PW ROK

PC IRST#

AG PBUSY #

VAC LK

VBC LK

VBCAD

VBHC LK

VBVSY NC

VBHSY NC

NC 0

NC 1

ECLKAVS S

AGPS TO P#

CPU _STP#22

ZAD 4

ZSTB_D121

DAC _ HSYN C

R187 0_04

1. 8V S

DAC _ GREE N

ZD REQ21

DAC _ RED

H _D PSLP#_LSZ0621

C241

.1U_10V _X7R_04

DC LK AV DD

3.3VS

Z0627

R22 1

150_1% _04

Z0626

Z_CO MP_P

D ACAV DD1

NB_R ST# 11,31

SB_D PRSLPVR22

Z0610

C 798 *10P_50V_04

R168

33_04

U10

74AHC1G32GW

4

53

1

2

Z0602

VVBWN

C239

.1U_10V_X7R _04

R180 121_1%_04

Z_VR EF

C228

.1U_10V_X7R _04

Z0609

ZAD 7

U12

74 L V C 1 G 1 7 G W

1

2

53

4

CPUSTP# 25

C60 0

10U_10V_08

R 467 56_04

Z0620

DAC _ BLU E

NB_ EN TE ST

R365

33_04

C30 7

.1U_10V_X7R_04

DACAVDD1

C604

.01U_16V_X7R_04

Z_C OMP_P

C608

.1U_10V_X7R_04

VCO MP

U11

74 L V C 1 G 1 7 G W

1

2

53

4

NB_ENTEST

R186 *4.7K_04

DAC _V SYN C19

ZAD 10

C224

.1U_10V_X7R_04

N C1 NC_04

PM_DPRSLPVR 37

Z0604

C242 .1U_16V _04

R 193 4.7K_04

C 797 *10P_50V_04

1.05VS

VBH CLK 11

C243

.1U_10V _X7R_04

C 246 *.1U_16V_04

C206

.01U_16V_X7R_04

R179

499_1%_04

C33 3

10U_10V_08

L62

*HC B1005KF-121T20

C51 9

*100P_50V_04

SB_D PRSTP#22

Z0612

DELA Y _PW R GD

R161 1K_1%_04

NB_T ESTM OD E0

R146

33_04

DCLKAVD D

C595

10U_10V_08

Z0611

Z0601

C30 1

.1U_10V_X7R_04

R352

33_04

Z0628

U6

74LVC1G17GW

1

2

53

4

D AC_ DD CAC LK

ECLKAVD D

DAC _ BLU E

L61

H CB1005KF-121T20

R 1 73 * 1 0m i l_ s h or t

ZAD 2

R 174 150_1%_04

Z4XAVD D

ZU REQ21

C LK_14M_671MX

ZAD 3

R364

*33_04

C233

*100P_50V_04

DACAVDD2

D ACA VSS1

DELAY_PWRGD 31,37

Sheet 6 of 48

SiSM672 MuTIOL

VGA 3/5

Schematic Diagrams

SiSM672 MuTIOL VGA 3/5 B - 7

B.Schematic Diagrams

Page 8

Schematic Diagrams

C659

1U_10V_06

C286

1U_10V_06

2024mA

C802

10U_10V_08

C283

1U_10V_06

1.2V 35,39

1.2VS

1.2VS 4,35

C662

1U_10V_06

2024mA

1.2VS

C247

.1U_ 10V_X7R_04

1.8VS

80mA

C808

.1U_10V_X7R_04

C267

1U_10V_06

1.2VS

80mA

C275

1U_10V_06

1.2VS

1 .8V 5,9,10,22,23, 24, 35,39, 40

C261

.1U_10V_X7R_04

1.2VS

1.8V

1 .8VS 4,5, 6, 11,13, 14,15, 17, 19,21,22, 23 ,24, 25,35

C257

10U_10V_08

C664

10U_10V_08

392mA

392mA

1.8VS

1.8VS

1.8VS

C807

.1U_10V_X7R_04

C602

10U_10V_08

1.8VS

664mA

C297

1U_10V_06

C311

.1 U _ 10 V_ X7R _0 4

664mA

876mA

C259

.1U_10V _X7R_04

1.2V

1mA

C278

.1U_1 0V_X7R_04

C284

.1U_10V_X7R_04

1.8V

C274

1U_10V_06

876mA

1 .05VS 2,3, 4, 6,24, 39

92mA

1. 2VS

C306

1U_10V_06

C298

1U_10V_06

C276

1U_10V_06

392mA

C647

.1 U _ 10 V_ X7R _0 4

C253

.1U_10V_X7R_04

C268

10U_10V_08

C653

1U_10V_06

C263

.1U_10V_X7R_04

C234

1U_10V_06

C265

.1U_10V _X7R_04

C272

10U_10V_08

PWR

U32E

Si S M672

AB12

AB13

AC1 2

AC1 3

AC1 4

AC1 5

AH6

AH7

AJ4

AJ5

AJ6

AJ7

AN2

AK4

AK5

AL1

AL2

AL3

AL4

AM1

AM2

AM3

AN3

AN5

AN7

AN9

E8

E10

F9

F10

F8

AB 1 8

AB 2 0

P20

P22

R21

T22

U21

V22

M11

N11

P11

R11

T11

U11

V11

W11

Y11

AA11

AB11

D6

G8

N19

N21

W23

Y23

AA23

AB23

AC2 3

AC1 8

AC2 0

AC1 6

AD1 6

AD1 7

AD1 9

AD2 0

AD2 1

AD2 2

AJ2 2

AJ2 4

AL2 3

AN2 1

AN2 3

AN2 5

AN2 7

AN2 9

AA 1 3

AA 2 2

AB 1 4

AB 1 5

AB 1 6

AB 2 2

AF 6

AF 7

AK 3

AG4

AG5

AG6

AG7

R13

AH3

AH4

AH5

AJ 1

AJ 2

AJ 3

AK 1

AK 2

AC2 2

AC2 1

AC1 9

AC1 7

A1 9

A2 0

B1 9

B2 0

C19

C20

D19

D20

E1 9

E2 0

F1 9

F2 0

G19

G20

L18

L19

L20

M20

M21

M22

M23

N23

P2 3

R23

T23

U23

V2 3

M12

N12

P1 2

R12

T12

U12

V1 2

W12

Y12

AA 1 2

AP3

M13

M14

M15

M16

M17

M18

M19

N16

N17

N18

N20

R22

N22

N13

P1 3

Y13

Y22

T13

U13

U22

V1 3

W13

W22

C5

B5

AL2 6

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VCC1.8

VDDVB1.8

VDD1.8

VDDVB1.8

VDD1.8

VDDVB1.8

IVDD

IVDD

PV D DH

PV D DH

PV D DH

PV D DH

PV D DH

PV D DH

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

VDDPEX

AUX_ I V D D

AUX1 . 8

PV D DH

PV D DH

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

VCCM

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVD

D

IVDD

IVDD

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VCC1.8

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

AUX_ I V D D

AUX_ I V D D

VCCM

C300

.1U_10V_X7R_04

392mA

C256

1U_10V_06

C601

.1U_10V_X7R_04

C805

.1U_10V_X7R_04

C280

10U_10V_08

C810

*. 1U_10V_X7R_04

C285

.1U_10V _X7R_04

C649

1U_10V_06

C271

.1 U _ 10 V_ X7R _0 4

1.8VS

392mA

C238

.1U_10V_X7R_04

C294

1U_10V_06

1.05VS

C648

10U_10V_08

1.8V

C305

10U_10V_08

C277

10U_10V_08

D02

1. 8V

C661

1U_10V_06

1.05VS

1.8V

C809

*. 1U_10V_X7R_04

1.8V

FOR EMI

C252

. 1U_10 V_X7R_04

C603

1U_10V_06

1.8VS

C309

.1U_10V_X7R_04

C806

*.1U_10V_ X7R_04

2024mA

1.8V

C235

1U_10V_06

C250

1U_10V_06

C258

.1U_10V _X7R_04

2024mA

C266

1U_10V_06

C248

.01U_16V_X7R_04

C254

1U_10V_06

Sheet 7 of 48

SiSM672 PWR 4/5

B.Schematic Diagrams

B - 8 SiSM672 PWR 4/5

SiSM672 PWR 4/5

Page 9

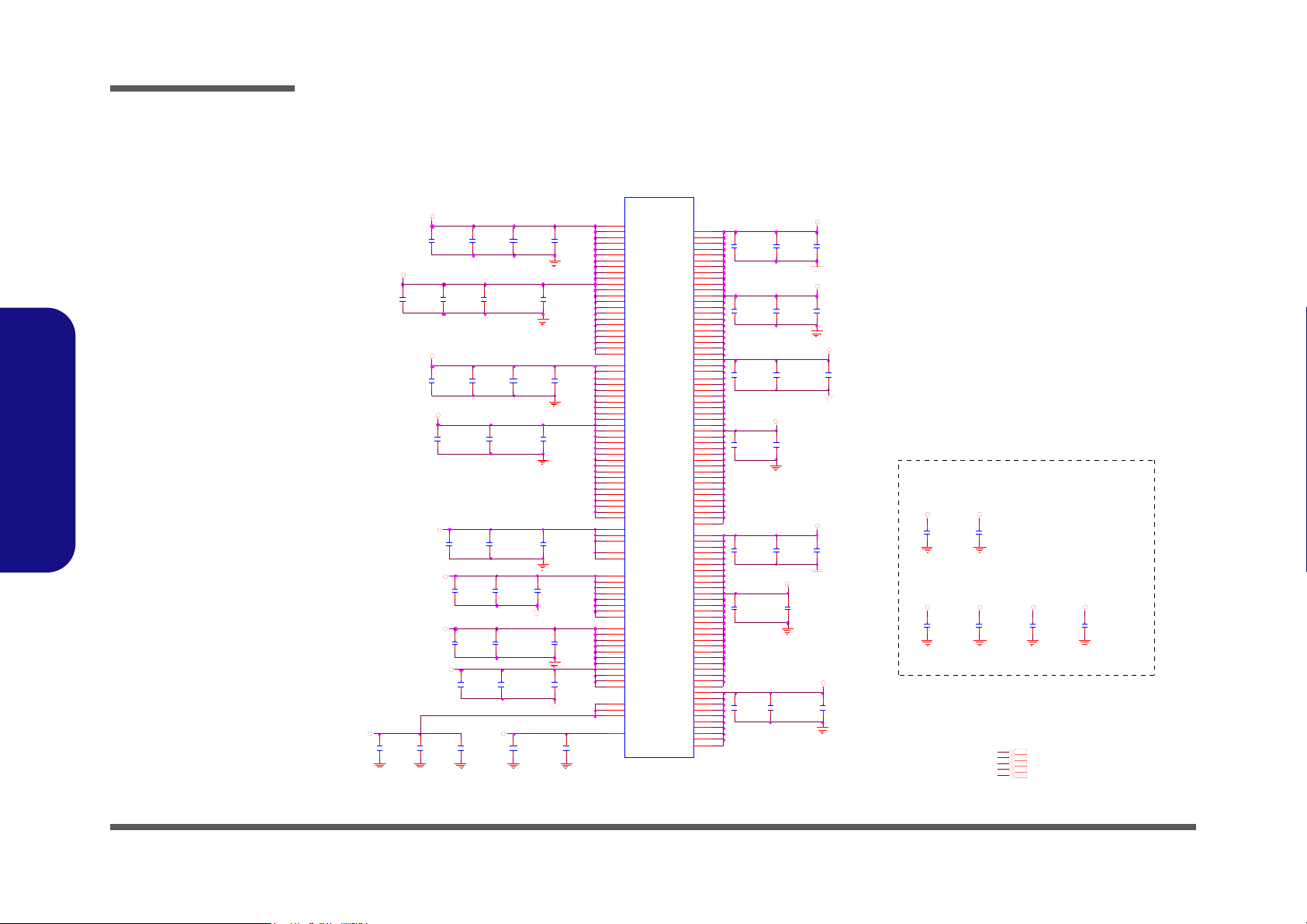

SiSM672 GND 5/5

S5

SMD1 92X73SR

1

1

1

H19

MTH315D111

2

3

4

5 6

7

8

9

M11

M-MARK1

H27

C355B264D 186

M74? ? ?

M1

M-MA RK1M2M-MA RK1

H18

C237

H15

C23 7

S3

SMD192X73SR

1

1

M1 0

M-M A RK 1

1

H4

MTH315D111

2

3

4

5 6

7

8

9

H1

H4_0

1

H17

MTH315D111

2

3

4

5 6

7

8

9

M7

M-MARK1

H34

C256B185D 146

1

H3

MTH 315D 111

2

3

4

5 6

7

8

9

M74? ? ?

H36

C178D79

M5

M-MA RK1

H38

C296D 166

M1 2

M-M A RK 1

M6

M-MA RK1

H28

C 355B264D186

M13

M-MA RK1

H30

C217D111

H2

H 4_0

1

H6

MTH315D111

2

3

4

5 6

7

8

9

H22

C 67D67

H29

C354B197D 185

1

H20

MTH 315D 111

2

3

4

5 6

7

8

9

S7

S MD 192X73SR

1

1

H32

C217D111

1

H8

MTH315D111

2

3

4

5 6

7

8

9

? ? 6-34-M52GS-020

M14

M-MARK1

M9

M-MA RK1

H10

C237

? ? 6-34-M52NS-020

H14

C237

1

H5

MTH315D111

2

3

4

5 6

7

8

9

S6

SMD 73X136R

1

1

1

H21

MTH 315D 111

2

3

4

5 6

7

8

9

M3

M-MARK1

H31

C 354B197D185

H11

C237

H35

C25 6B1 85D 1 46

H12

C276B193D185

1

H23

MTH315D111

2

3

4

5 6

7

8

9

S4

SMD192X73SR

1

1

H33

C35 5B2 64D 1 86

GND

U32 F

SiSM 67 2

A3

B2

B3

B4

AA16

AA 17

AA18

AA19

AA 20

AA21

AA31

AA33

AB3

AB 4

AB5

AG2

AG31

AG 33

AH 29

B21

B23

B25

B27

B29

B31

C1

C2

C3

C4

AB7

AB29

AC2

AC 3

AC 31

AC33

AD 2

AD3

AD4

AD 5

AD7

AD 29

AE3

AE31

AE33

AF2

AF 3

AF4

AF5

AF29

AJ8

AJ10

AJ1 2

AJ14

AJ1 6

AJ1 8

AJ20

AJ2 6

AJ28

AJ3 3

AK31

AL6

AL8

AL1 0

AL12

AL1 4

AL16

AL1 8

AL2 0

AL2 8

AL30

AL3 3

AN 11

AN13

AN 15

AN17

AH1

T29

U2

U3

U4

U5

U6

U14

U15

U16

U17

U18

U19

U20

U31

U33

V2

V3

V4

V5

V14

V15

V16

V17

V18

V19

V20

V29

AN 33

AN 31

AN 19

W3

W14

W15

W16

W17

W18

W19

W20

W21

W31

W33

Y2

Y3

Y4

Y5

Y7

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

Y29

AA2

AA3

AA14

AA15

H5

H29J2J3J7J3 1

J33K3K4K5K29L2L3L4L5L7L31

L33M2M3

M29N3N4N5N6N7N14

N15

N31

N33P2P3

P14

P15

P16

P17

P18

P29R2R3R4R5

R14

R15

R16

R17

R18

R19

R20

R31

R33T3T6

T14

T15

T16

T17

T18

T19

T20

G31

G33

H4

C9

C10

C11

C16

C18

C32

C33

D1

D2

D3

D4

D5

D10

D12

D21

D23

D25

D27

D29

E1

E2

E3

E6

E11

E13

E14

E18

E29

E30

E33

F2

F3

F4

F5

F6

F14

F22

F24

F26

F28

G2

G3

G7

G1 0 AB17

AB19

AB21

P19

P21

T2 1

V21

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VS S

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S VS S

VS S

VS S

VS S

VS S

VS S

VS S

1

H7

MTH315D111

2

3

4

5 6

7

8

9

S2

SM D19 2X73SR

1

1

H37

C17 8D 79

H26

C 67D67

H16

C31 5D1 11

M8

M-M A RK 1

M4

M-M A RK 1

H24

H4_0

H9

C23 7

H25

H4_0

H13

C237

Sheet 8 of 48

SiSM672 GND 5/5

Schematic Diagrams

B.Schematic Diagrams

SiSM672 GND 5/5 B - 9

Page 10

Schematic Diagrams

Sheet 9 of 48

DDRII SO-DIMM - 1

S_C LK10, 22,25,33

M_ A_ DQ 5 1

M_ DM 15,10

M_ DM 45,10

1. 8 V

M_CLK _DD R1#25

M_ A_ DQ 5 6

M_ DM 65,10

M_DQ S3#5,10

M_ A_ DQ 4 7

M_ A_ DQ 6 2

M_DQ S55,10

R471

1K_1%_04

M_ A_ DQ 2 2

M_ CA S #

R472

1K_1%_04

C396

10U_10V_08

M_A_A16

M_ A_ DQ 0

M_ A_ DQ 4 8

M_DQ S35,10

M_ W E#

M_ A_ DQ 5 8

M_ A_ DQ 2 5

M_DQ S05,10

M_CLK_DDR0#

M_ A_ DQ 1 5

M_A_A8

M_ A_ DQ 1 1

J_DIM1

AS0A421-N2AN-4F

102

101

100

99

98

97

94

92

93

91

105

90

89

107

106

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

112

111

1179695

11 881828710 38810 4

149

47

13 3

183771248184787172121

122

196

1938162

150

1384028

1824415342545965606612 7

139

12 8

145

16 5

171

17 2

187

178

1909213315534132

144

156

168231527

83

120

50

69

163

86

39

198

200

16 1

1

177

199

116

11

29

49

68

129

146

167

186

10

26

52

67

130

147

170

185

84

13

31

51

70

131

148

169

188

85

108

109

113

110

115

79

80

30

164

114

32

166

119

195

197

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

BA0

BA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VD D

VDD

VD D

VDD

VD D

VDD

VD D

VDD

VD D

VDD

VD D

VDD

VSS

VSS

VSS

VS S

VSS

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NC1

NC2

NC3

NC4

N CTEST

A14

VSS

SA0

SA1

VSS

VREF

VS S

VDD SPD

A13

DQ S#0

DQ S#1

DQ S#2

DQ S#3

DQ S#4

DQ S#5

DQ S#6

DQ S#7

DM 0

DM 1

DM 2

DM 3

DM 4

DM 5

DM 6

DM 7

A15

DQ S0

DQ S1

DQ S2

DQ S3

DQ S4

DQ S5

DQ S6

DQ S7

A16/BA 2

RAS#

WE#

CAS#

S0#

S1#

CKE0

CKE1

CK0

CK1

OD T0

CK0#

CK1#

OD T1

SDA

SCL

M_A_A9

M_A_A15

M_ A_ DQ 5 0

C365

.1U_10V_X7R _04

M_A_DQ[63:0] 5,10

M_A_A0

C360

.1U _10V_X7 R_0 4

M_ A_ DQ 2 7

C364

*3.3P_50V_04

M_ CS 0#

M_ A_ DQ 3 5

M_A_A17

M_CLK _DD R1#

1.8V

M_ A_ DQ 3

M_ A_ DQ 1 6

M_ CS 1#

M_DQ S1#5,10

M_ A_ DQ 1 9

M_ A_ DQ 1

M_ A_ DQ 8

M_ A_ DQ 6 1

M_A_A13

M_ DM 75,10

M_A_A12

C667

.1U_10V_X7R_04

M_ A_ DQ 6 3

M_ RA S #

MV RE F1

M_ A_ DQ 3 4

Z0901

M _C KE05,10

C395

10U_10V_08

M_ A_ DQ 2 8

M_ DM 25,10

M_CS1#5,10

M_A_A3

M_DQ S4#5,10

M_ A_ DQ 3 6

M_ A_ DQ 2 1

C359

1U_6.3V_X5R_06

M_CLK_DDR0 M_CLK_DDR1

M_ A_ DQ 3 2

M_CLK _DD R0#

M_A_A5

3.3VS_ SPD 1 0

M_DQ S6#5,10

M_ A_ DQ 5 9

C672

.1U_10V_X7R_04

M_ A_ DQ 1 2

M_CLK_DDR1#

+

C397

150U_4V_B2

M_ A_ DQ 3 0

M_ OD T 0

M_CS0#5,10

C304

.1U_10V_X7R_04

C668

.1U _10V_ X7R _04

M_ A_ DQ 5 4

M_ CK E 1

C367

10U_10V _08

M_A_A [17:0]5,10

M_ A_ DQ 1 8

1.8V 5,7,10,22,23,24,35,39,40

M_ A_ DQ 1 7

???????!

M_DQ S15,10

Z0902

M_ A_ DQ 4

M_ OD T 1

M_ A_ DQ 4 0

M_DQ S7#5,10

M_A_A4

M_ A_ DQ 2 4

C366

*3.3P_50V_04

M_DQ S25,10

M_ A_ DQ 2 6

M_ A_ DQ 4 2

M_ A_ DQ 4 3

M_CLK _DD R0

M_DQ S2#5,10

M_ A_ DQ 6

C392

.1U_ 10V _X7R _04

M_ A_ DQ 2 9

M_DQ S65,10

M_A_A2

+

C712

*150U_4V_B 2

C315

.1U_10V_X7R _04

M_CLK _DD R1

M_ A_ DQ 2 3

M_ A_ DQ 9

M_ A_ DQ 5 7

M_A_A14

M_ A_ DQ 2

M_ A_ DQ 1 3

M _C KE15,10

M_CLK_DDR125

MVR E F1

SO-DIMM 1

M_DQ S5#5,10

M_ A_ DQ 2 0

M_ A_ DQ 1 4

M_ A_ DQ 7

M_ A_ DQ 3 8

M_ A_ DQ 5 2

C303

.1U_10V_X7R_04

M_A_A7

R259 10K_04

M_ DM 05,10

M_ DM 55,10

M_DQ S75,10

M_DQ S45,10

M_A_A1

M_ A_ DQ 3 7

M_ODT05,10

M_A_A10

M_ A_ DQ 5

R258 10K_04

M_CLK _DD R0#25

M _CAS#5,10

M_A_A11

M_A_A6

C671

.1U_10V_X7R_04

M_ CK E 0

M_ A_ DQ 1 0

S_D AT10, 22,25,33

M_ A_ DQ 4 9

M_ A_ DQ 5 5

M _RAS#5,10

M_DQ S0#5,10

M_ A_ DQ 3 3

M_ A_ DQ 4 5

M_ W E#5,10

M_ A_ DQ 6 0

M_ A_ DQ 4 6

M_ A_ DQ 5 3

C371

10U_10V_08

M_CLK_DDR025

M_ A_ DQ 4 4

M_ A_ DQ 4 1

3.3VS _SP D

M_ODT15,10

M_ A_ DQ 3 1

C403

. 1U _10V_X7R _04

1.8V

M_ DM 35,10

C368

10U_10V_08

M_ A_ DQ 3 9

DDRII SO-DIMM - 1

B.Schematic Diagrams

B - 10 DDRII SO-DIMM - 1

Page 11

DDRII SO-DIMM - 2

Sheet 10 of 48

DDRII SO-DIMM - 2

M_ A_ A1 6

M_ A_ D Q 60

M_CLK_DDR3#25

M_ A_ D Q 28

M_C LK_ D DR2#

M_ A_ D Q 20

M_ A_ D Q 5

M_ A_ D Q 52

M_ DQ S 65,9

M_ OD T 2

M_A_A4

M_ A_ D Q 51

RN 24

8P4R X56_04

1

2

3456

7

8

M_ A_ D Q 9

M_A _A[17:0]5, 9

M_CLK _DD R225

C296

10U_10V_08

M_ DQ S6 #5,9

M_A_A1

M_A_A2

C695 .1U_10V_X7R_04

M_ A_ D Q 53

C383

*3. 3P_50V_04

R486 10K_04

J_ D IM 2

A S0A421-N2RN -4F

102

101

100

99

98

97

94

92

93

91

105

90

89

107

106

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

11 2

111

1179695

11881828710388104

149

47

133

183771248184787172121

12 2

196

19 3816 2

150

13 84028

18244153425459656066127

139

128

145

165

171

172

18 7

178

19 09213315 53413 2

144

15 6

168231527

83

120

50

69

163

86

39

198

200

161

1

177

199

116

11

29

49

68

129

146

167

186

10

26

52

67

130

147

170

185

84

13

31

51

70

131

148

169

188

85

108

109

113

110

115

79

80

30

164

114

32

166

119

195

197

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

BA0

BA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ 10

DQ 11

DQ 12

DQ 13

DQ 14