Page 1

Appendix B:Schematic Diagrams

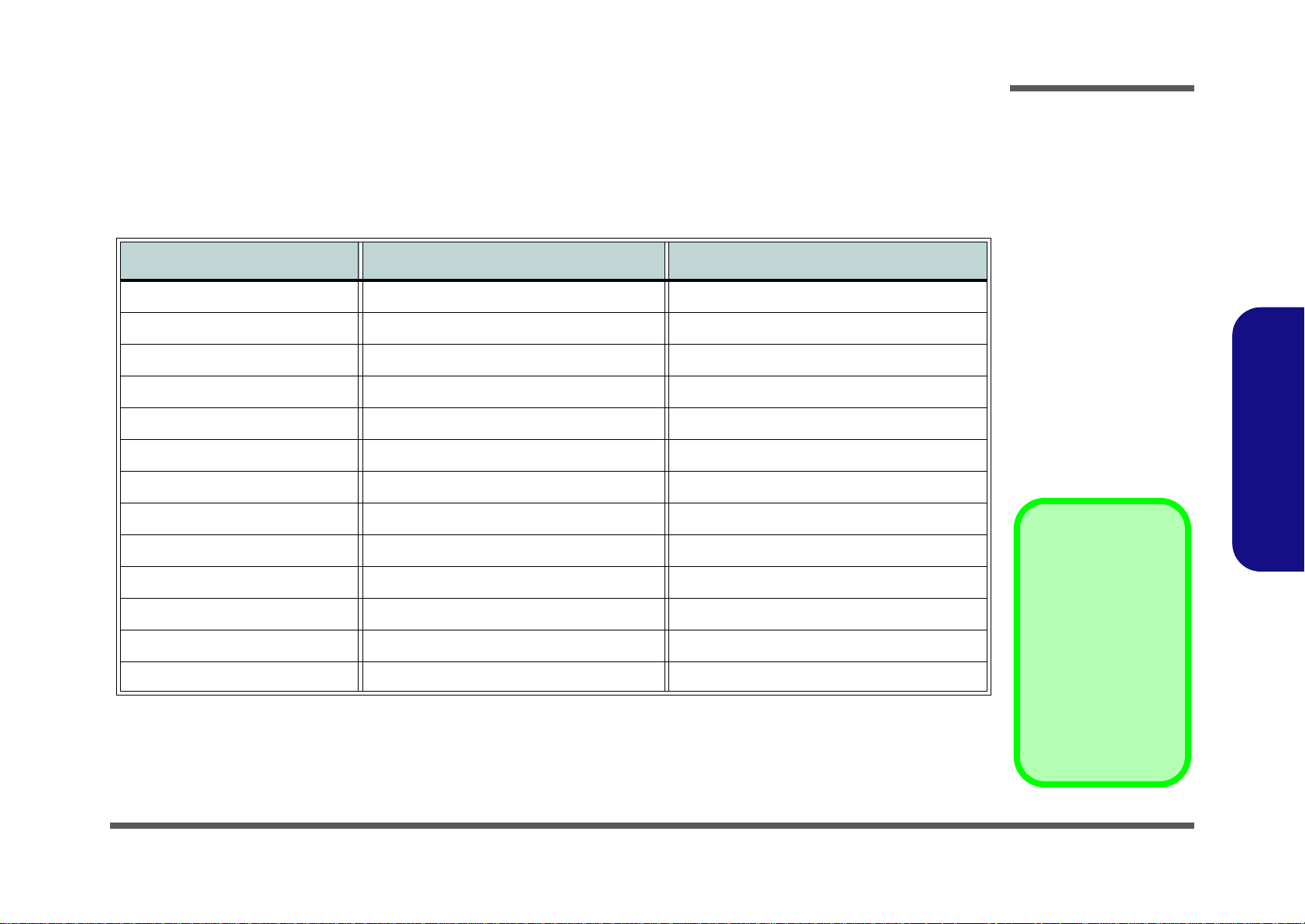

This appendix has circuit diagrams of the M540SE/M550SE notebook’s PCB’s. The following table indicates where to

find the appropriate schematic diagram.

Schematic Diagrams

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 VT8237 2/3 - Page B - 15 +1.8V, +VTT_MEM - Page B - 28

PROCESSOR 1/2 - Page B - 3 VT8237 3/3 - Page B - 16 VCORE - Page B - 29

PROCESSOR 2/2 - Page B - 4 MINI PCI, MINI Card, USB2.0*2, FP - Page B - 17 +1.05VS, 1.5V, 1.5VS - Page B - 30

VN896 1/4 - Page B - 5 SATA HDD, CD-ROM, H8 BEEP, CCD - Page B - 18 +VDD3, +VDD5 - Page B - 31

VN896 2/4 - Page B - 6 LAN PHY - Page B - 19 D/D BD (CRT, INVERTER, CCD, RJ -11) - Page B - 32

VN896 3/4 - Page B - 7 LPC ROM, TOUCH PAD, LED - Page B - 20 D/D BD (CHARGER, DC IN) - Page B - 33

VN896 4/4 - Page B - 8 H8-2111 - Page B - 21 AUDIO BD (PHONE JACK, USB, RJ-11) - Page B - 34

DDR2-1 - Page B - 9 MDC, USB BT, PWRGD, DDB CON - Page B - 22 HOT KEY BD (HOT KEY, LED, LID) - Page B - 35

DDR2-2 - Page B - 10 Audio VT1708A/ALC883 - Page B - 23 LED BOARD - Page B - 36

CLOCK GENERATOR - Page B - 11 AUDIO AMP, USB2.0*2 - Page B - 24 CLICK BOARD - Page B - 37

PANEL, FAN - Page B - 12 PCI ENE MR510 - Page B - 25 RJ-45 BOARD - Page B - 38

VIA LVDS VT-1634AL - Page B - 13 NEW CARD, 3-IN-1 SOCKET - Page B - 26 USB DONGLE BOARD - Page B - 39

VT8237 1/3 - Page B - 14 5V, 3V, 5VS, 3VS, 2.5V, 2.5VS - Page B - 27 FINGERPRINT BOARD - Page B - 40

Table B - 1

Schematic

Diagrams

B.Schematic Diagrams

Version Note

The schematic diagrams in this chapter

are based upon version 6-71-M5E50D02A. If your mainboard (or other boards)

are a later version,

please check with the

Service Center for updated diagrams (if required).

B-1

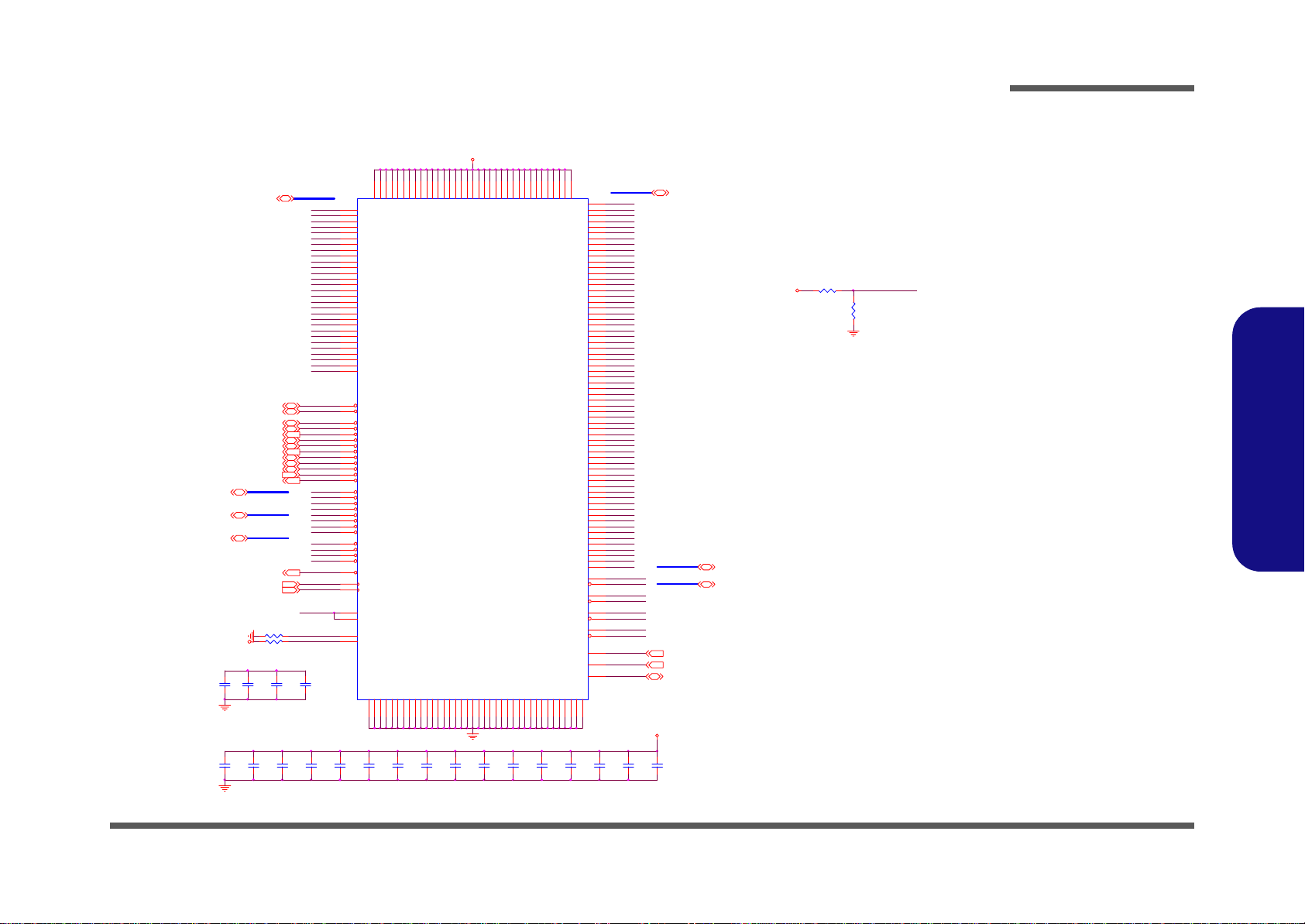

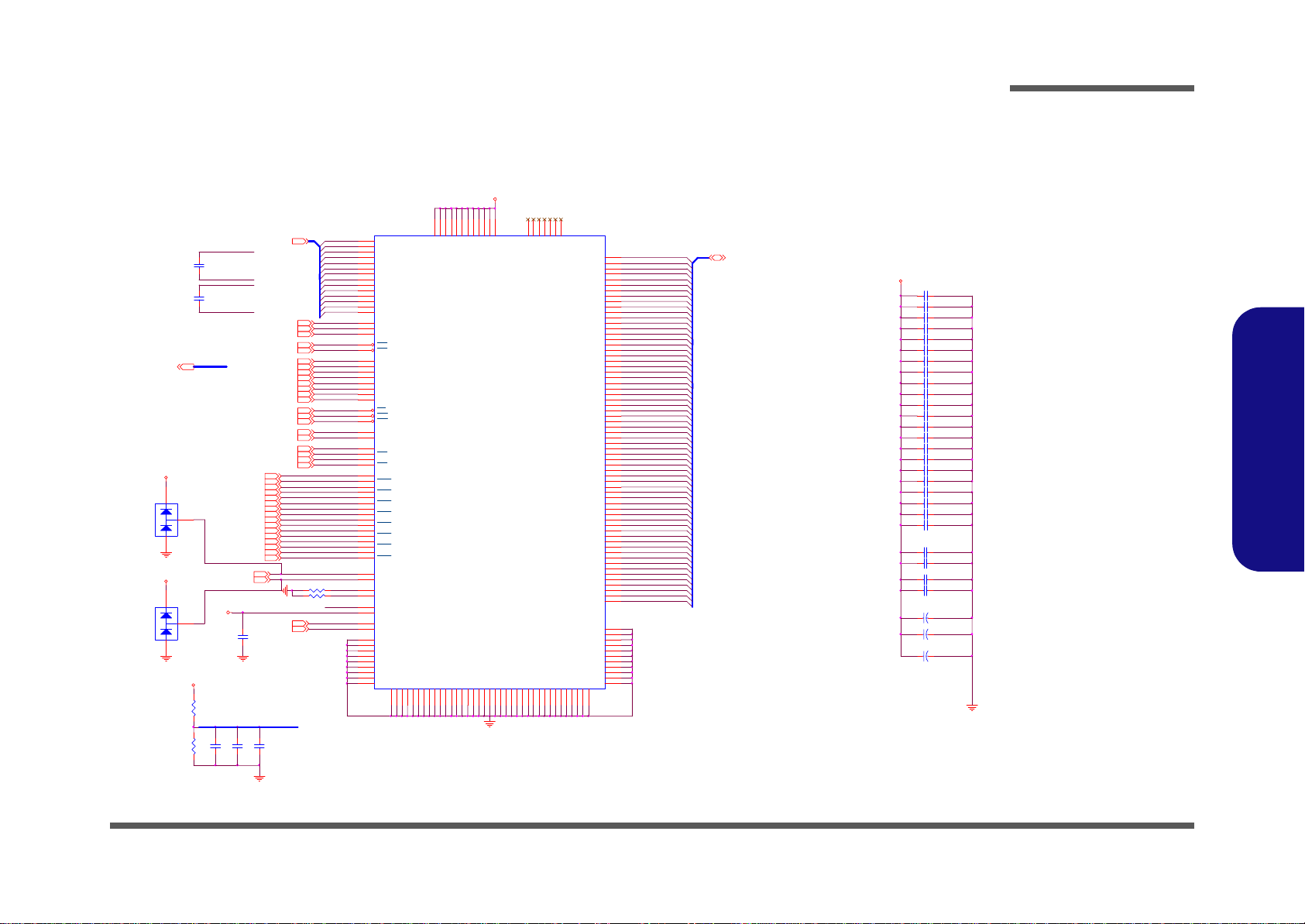

Page 2

Schematic Diagrams

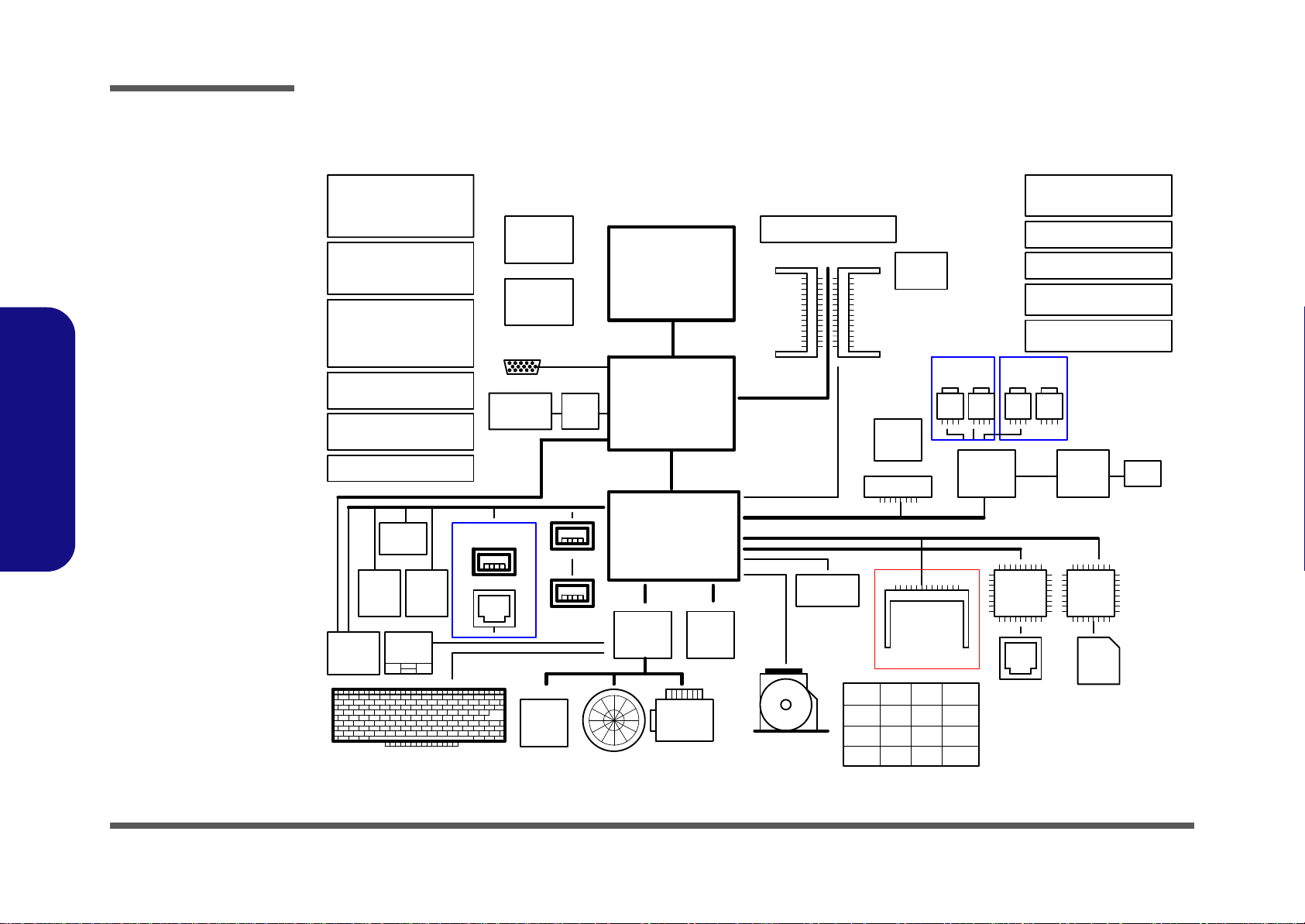

System Block Diagram

Sheet 1 of 39

System Block

Diagram

B.Schematic Diagrams

D/D BOARD

1.CHARGER,DC JACK

2.INVERTER

3.CRT,CCD

4.M550S SPK

PHONE JACK&US B BOARD

1.AUDIO PHONE JACK

2.USB CONNECTOR,RJ11

HOT KEY BOARD&POWER SWITCH

1.POWER BOTTO N

2.INDICATOR L ED

3.LID SWITCH

LED BOARD(FOR M550SE)

1.INDICATOR L ED

CLICK BOARD(FOR M550SE)

1.T/P SWITCH BO TTOM

RJ-45 BOARD

USB2.0

CCD

USB 5

Mini

PCIE

USB 6

NEW CARD

USB 7

USB 1

TOUCH

PAD

BT

MAIN CLOCK

ICS953009AF

ICS9P956AF

CRT

LCD CONN

(LVDS)

PCI-E

PHONE JACK

BOARD

USB 3

RJ-11

(Option)

CLEVO M540SE/M550SE System Block Diagram

MEMORY TERMINATIONS

DDR2 SDRA M SOC KET

SO-DIMM0

667MHz

SM BUS

AZALIA

PCI BUS

33MHz

MII

IDE

SATA HDD

DDR VR

MDC

MODULE

(Option)

(Option)

SO-DIMM1

MDC CONN.

Mini PCI

SOCKET

Debug ?

(35+25 Pin Conn.? ? )

CLOCK

BUFFER

VT1634A

LVDS

USB 0

USB 2

SM BUS

CPU

YONAH/MEROM

PROCESSOR

479 uFCPGA

FSB

NB

VN896

HSBGA-951

VLINK 533MB/sec

SB

VT8237A

HSBGA-541

LPC

KBC

H8/2111

SYSTEM

BIOS

LPC

ON BOARD

BULE

BLACK

LINE

IN

CODEC

VIA 1708A

SPDIF

OUT

1.+3V,+5V

,+2.5V

2.,+3VS,+5VS ,+2. 5VS

1.+VTT_MEM,+1.8V

1.+VCORE

1.+1.05VS,+1.5V,1.5VS

1.VDD3,VDD5

AUDIO BOARD

PINK

GREEN

HP

MIC

OUT

IN

AUDIO

AMP.

APA2020A

PHY

VT6103

RJ-45

CARD READER

ENE

MR510

3 IN 1

CARD

READER

INT.

SPK

B - 2

KBC CONN

TEMP

SENSOR

ADM1032

CPU FAN

SMART

BATTERY

CD-ROM/CD-RW/

DVD-ROM/DVD+-RW

FULL

ON

S3

S4

+VDD

ON

ON

ON

+*V

OFF

+*VS

ON

ON

ON

OFF

OFF

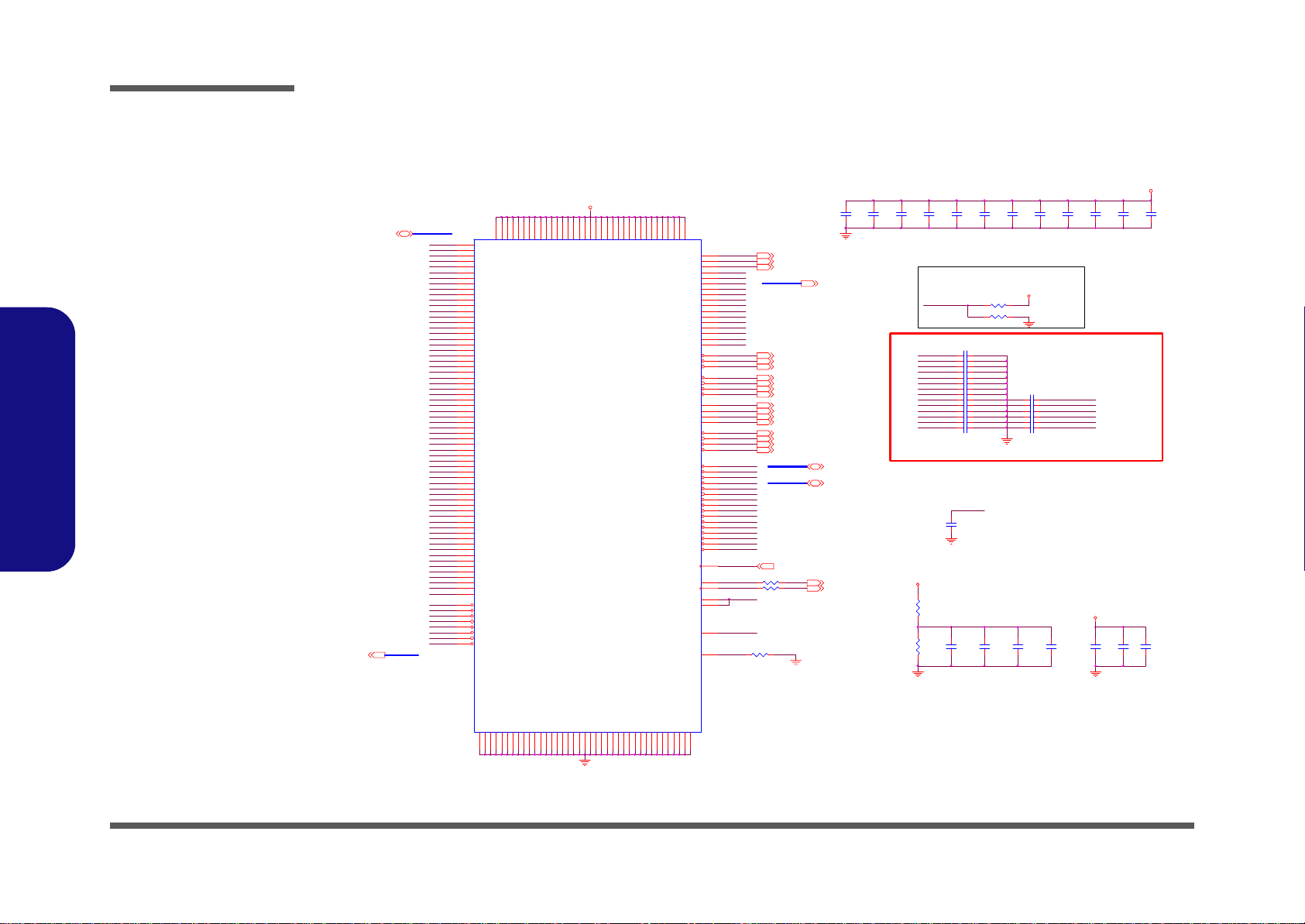

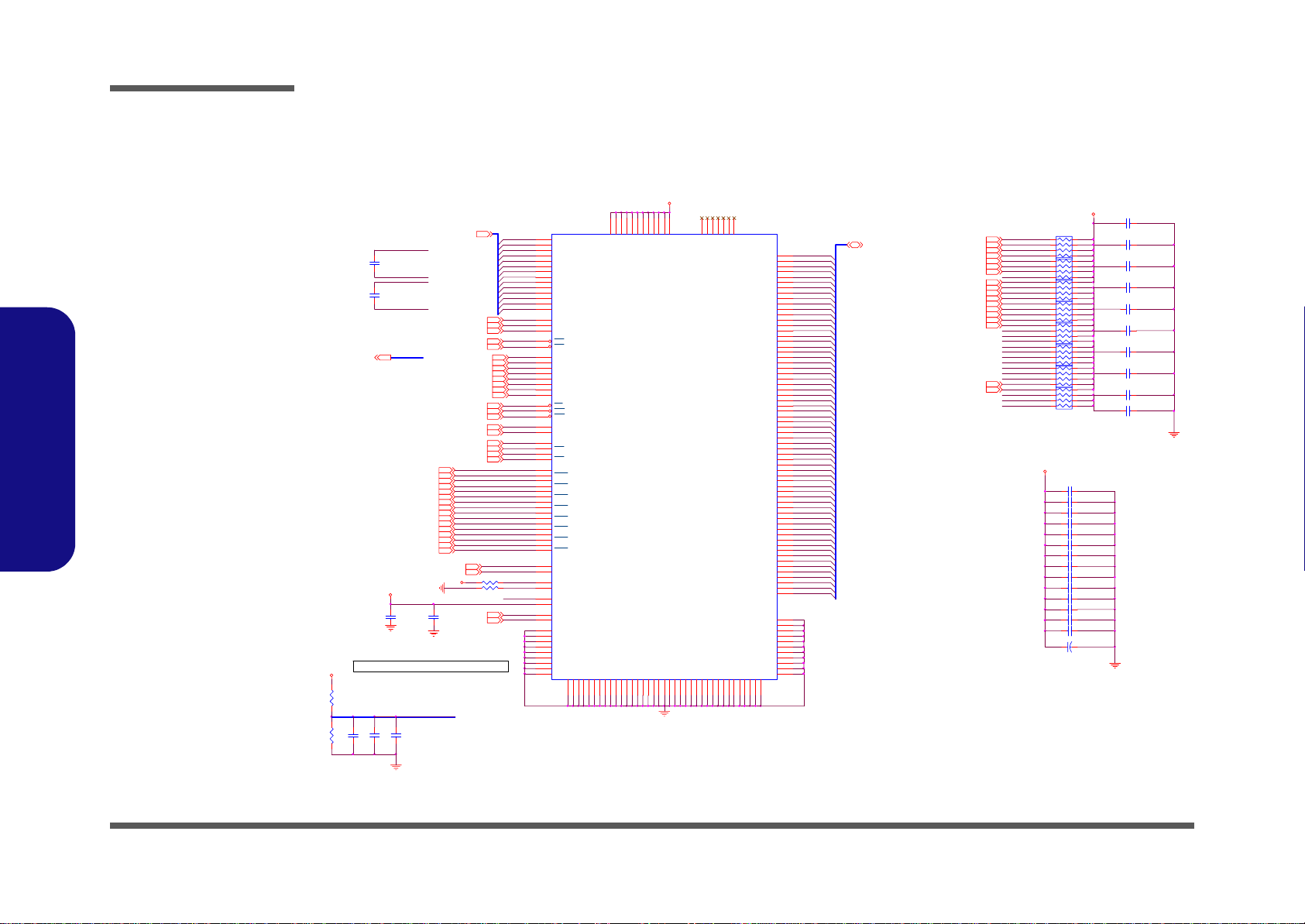

Page 3

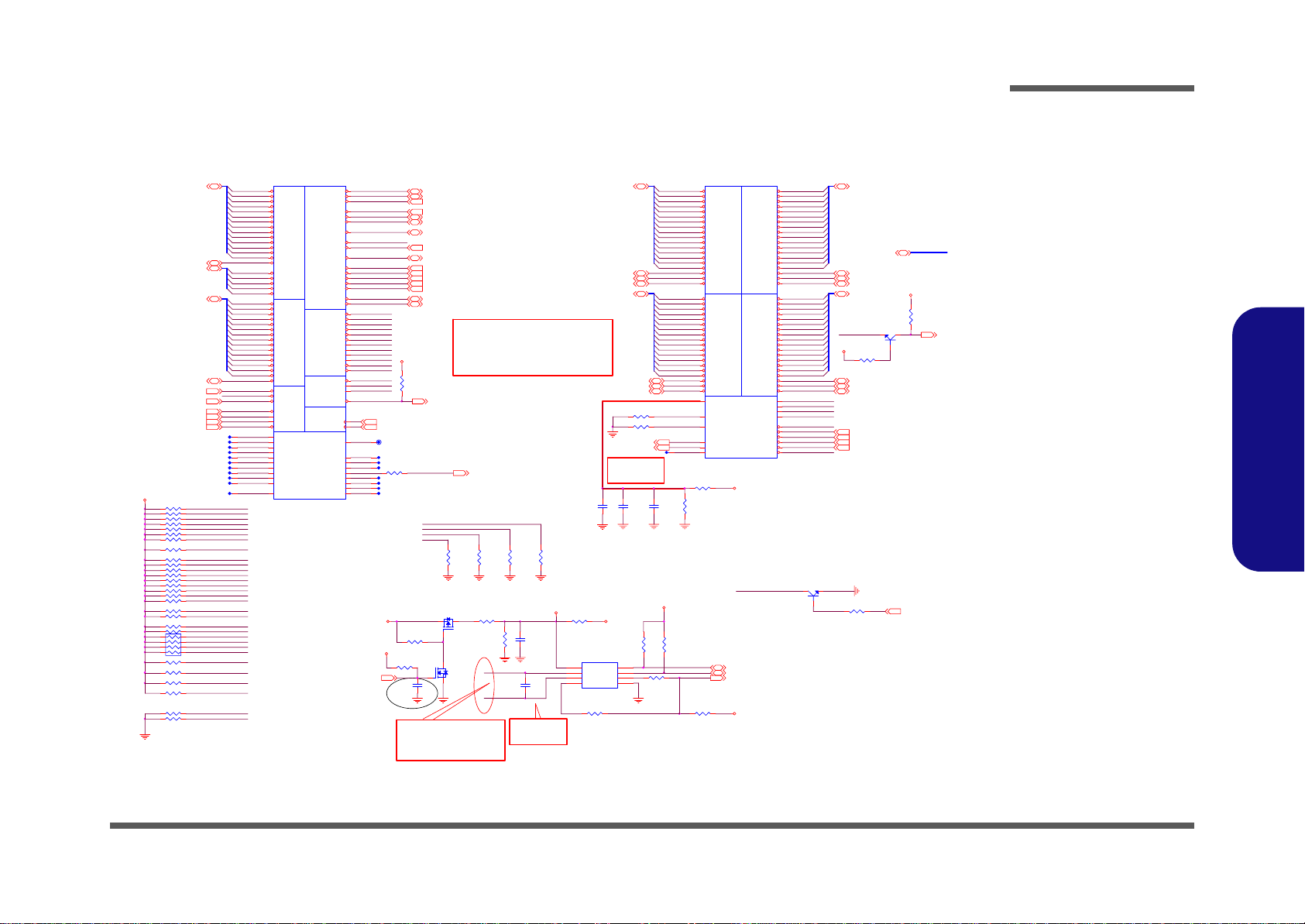

PROCESSOR 1/2

Schematic Diagrams

H_A#[31:3]4

H_ADSTB#04

H_REQ#[4:0]4

H_A#[31:3]4

H_ADSTB#14

H_IGNNE#15

No stub on H_STPCLK# test

point

H_STPCLK#15

+1.0 5VS

R325 54.9_1%_06

R324 54.9_1%_06

R22 54.9_1%_06

R21 75_1%_06

R19 54.9_1%_06

R58 75_1%_06

R59 51_1%_06

R350 51_1%_04

R352 150_04

R344 150_04

R340 150_04

R349 150_04

R339 150_04

R347 150_04

R342 150_04

R353 150_04

R29 220_04

R333 *51_1%_06

R28 150_1%_06

R60 150_04

R49 150_1%_06

653

7 2

8 1

RN2 220_06_8P4R

R14 *150_04

R26 150_04

R433 1K_04

R432 1K_04

Within 2.0" of the CPU

R23 54.9_1%_06

R20 680_1%_06

H_A20M#15

4

H_INTR15

H_NMI15

H_SMI#15

H_PREQ#

H_PRDY#

H_TMS

H_TDO

H_TDI

H_PROCHOT#

H_IERR#

FERR#

H_A20M#

H_IGNNE#

H_INIT#

H_INTR

H_STPCLK#

H_NMI

H_SMI#

H_CPUSLP#

H_BREQ#0

H_CPURST#

H_DPSLP#

ITP_DBRST#

H_PWRGD

H_BPM0#

H_BPM1#

H_BPM2#

H_BPM3#

H_PSI#

H_DPRSLPVR#

CPU_BSEL0

CPU_BSEL1

H_TCK

H_TRST#

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A20M#

FERR#

H_IGNNE#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

Z0201

Z0202

Z0203

Z0204

Z0205

Z0206

Z0207

Z0208

Z0209

Z0210

Z0211

J4

L4

M3

K5

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

JSKT1A

A[3]#

A[4]#

A[5]#

A[6]#

ADDR GROUP 0

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]#

RSVD[02]#

RSVD[03]#

RSVD[04]#

RSVD[05]#

RSVD[06]#

RSVD[07]#

RSVD[08]#

RSVD[09]#

RSVD[10]#

RSVD[11]#

PZ47913-2741-01

CONTROL

XDP/ITP SIGNALS

PROCHO T

THER MDA

THER MDC

THE R MTR IP #

THERMH CLK

RSVD[12]#

RSVD[13]#

RSVD[14]#

RSVD[15]#

RSVD[16]#

RESERVED

RSVD[17]#

RSVD[18]#

RSVD[19]#

RSVD[20]#

ADS#

BNR#

BPRI #

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY #

HITM#

BPM[0] #

BPM[1] #

BPM[2] #

BPM[3] #

PRDY#

PREQ#

TRST#

DBR#

BCLK[ 0]

BCLK[ 1]

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22H_A#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

R364

4.7K_04

Z0220

Z0221

JSKT1B

E22

D[0]#

F24

D[1]#

E26

D[2]#

H22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10

J23

D[11]#

H26

D[12]#

F26

D[13]#

K22

D[14]#

H25

D[15]#

H23

DSTBN[0]#

G22

DSTBP[0]#

J26

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L25

D[20]#

L22

D[21]#

L23

D[22]#

M23

D[23]#

P25

D[24]#

P22

D[25]#

P23

D[26]#

T24

D[27]#

R24

D[28]#

L26

D[29]#

T25

D[30]#

N24

D[31]#

M24

DSTBN[1]#

N25

DSTBP[1]#

M26

DINV[1]#

AD26

GTLREF

C26

TEST1

D25

TEST2

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

PZ47913-2741-01

R379 1K_1%_06

R380

2K_1%_06

R369 10K_04

D[32]#

D[33]#

D[34]#

DATA GRP 0 DATA GRP 1

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

DATA GRP 2

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

DATA GRP 3

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

COMP[0]

MISC

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

+1.05VS

H_DPRSLPVR#

SMC_THER M 20

SMD_THER M 20

H8_THERM_ALERT# 20

+VCC_THRM

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

COMP0

COMP1

COMP2

COMP3

H_DPRSLPVR#

H_DPSLP#

H_PWRGD

H_CPUSLP#

H_PSI#Z0222

Q4

2N3904

Z0225

B

EC

H_D#[63:0] 4

H_DSTBN#2 4

H_DSTBP#2 4

H_DINV#2 4

H_D#[63:0] 4

FERR#

+1.05VS

H_DSTBN#3 4

H_DSTBP#3 4

H_DINV#3 4

H_DPSLP# 15

H_DPWR# 4

H_PWRGD 21

H_CPUSLP# 4,15

R15 10K_04

H_DINV#[3:0]4

R346 10K_04

Q49

2N39 04

E C

Z0223

B

H_DINV#[3:0]

+3VS

R345

10K_06

H_FERR# 15

PM_DPRSLPVR 15,28

Sheet 2 of 39

PROCESSOR 1/2

B.Schematic Diagrams

R359 0_06

U21

1

VDD

2

D+

3

D-

ADT1032ARM

Z0228

SDATA

ALER T#

R363

H_D #[63: 0]4

H_DSTBN#04

H_DSTBP#04

H_DINV#04

H_D #[63: 0]4

H_DSTBN#14

H_DSTBP#14

H_DINV#14

R386 *1K_04

R385 51_1%_06

CPU_BSEL010

CPU_BSEL110

Layout Note:

0.5" max,

Zo= 55 Ohms

CPU_GTLREF

C472

C473

0.1u/ 16V_04

1u_10V_06

+3V

8

SCLK

7

Z0229

6

54

GNDTHE RM#

0_04

10mil

R365

4.7K_0 4

R374 *0_04

C471

0.01u/25V_04

+VDD3

H1

E2

G5

H5

F21

E1

F1

H_IERR#

D20

H_INIT#

B3

H4

H_CPURST#

B1

F3

F4

G3

G2

G6

HIT#

E4

AD4

H_BPM0#

AD3

H_BPM1#

H_BPM2#

AD1

AC4

H_BPM3#

AC2

H_PRDY#

H_PREQ#

AC1

AC5

H_TCK

TCK

H_TDI

AA6

TDI

H_TDO

AB3

TDO

AB5

H_TMS

TMS

AB6

H_TRST#

C20

ITP_DBRST#

H_PROCHOT#

D21

H_THERMDA

A24

A25

H_THERMDC

PM_THRMTRIP#

C7

A22

A21

Z0212

T22

Z0213

D2

Z0214

F6

Z0215

D3

Z0230

C1

Z0216

AF1

Z0217

D22

Z0218

C23

Z0219

C24

THER M_RS T#20

1212

H_ADS# 4

H_BNR# 4

H_BPRI# 4

H_DEFER# 4

H_DRDY# 4

H_DBSY# 4

H_BREQ#0 4

H_INIT# 15

H_LOCK# 4

H_CPURST# 4

H_RS#0 4

H_RS#1 4

H_RS#2 4

H_TRDY# 4

H_HIT# 4

H_HITM# 4

Layout Note:

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms

COMP1, COMP3: 0.5" Max, Zo=55 Ohms

+1.05VS

R351

*680_04

CPU_CLK+ 10

CPU_CLK- 10

T31

R391 *0_06

+3V

R355

+VDD3

R354 100K_04

C714 1u_10V_06

Layout Note: Layout Note:

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil

spacing.

Best estimate is 18 mils wide trace

for outer layers and 14 mils wide

trace if on internal layers.

PM_THRMTRIP# 30

H_ADSTB0#

100K_04

COMP0

COMP1

COMP2

COMP3

G

R328

54.9_1%_06

Q54

NDS352AP_NL

DS

G

Z0227

DS

Q51

2N70 02

H_ADSTB0# 4

R361 *0_06

Z0226

R329

27.4_1%_06

R360

100K_04

H_THERMDA

H_THERMDC

R387

54.9_1 %_06

20mil

C456

C469 CLOSE TO U34.

10u/10V_08

10MIL

C461

1000p/50V

10MIL

ADT1032

R388

27.4_1 %_06

+VCC_THRM

PROCESSOR 1/2 B - 3

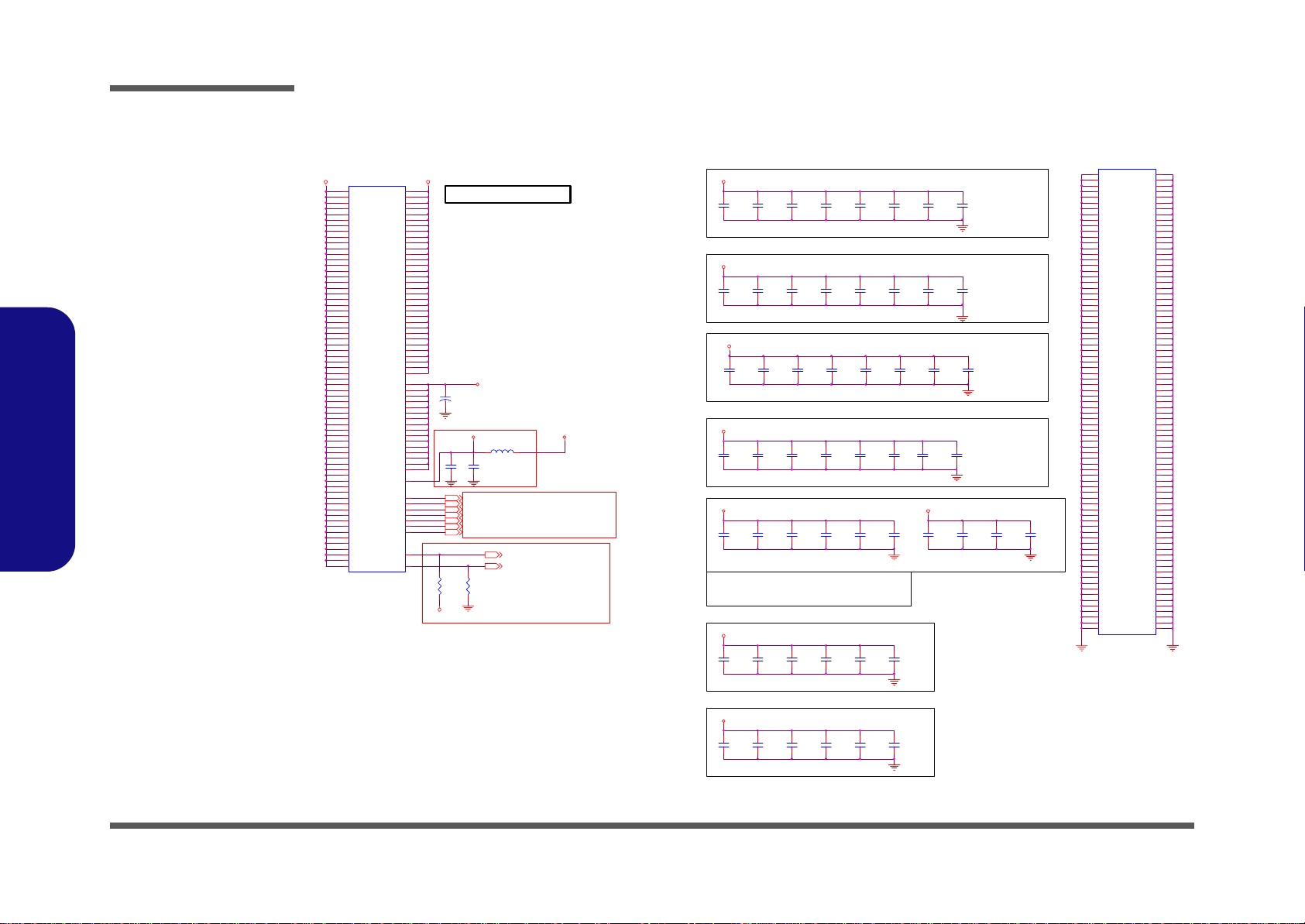

Page 4

Schematic Diagrams

Sheet 3 of 39

PROCESSOR 2/2

B.Schematic Diagrams

PROCESSOR 2/2

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[ 100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENS E

+VCOR E

AB20

Boost Voltage 1.2V

AB7

Deeper Sleep Voltage 0.748V

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

2.5A

V6

G21

J6

C429

+

K6

150U/4V_B

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

+VCOR E

+VCCA_CPU

130mA

C467

10u/10V_08

VCCS ENSE

VSSSEN SE

R25

100_1%_06

+1.05VS

L26 HCB1608KF-121T25

C466

Layout

Near pin B26

note:

0.01u/25V_04

H_VID0 28

Layout note:

H_VID1 28

VID[6..0] trace:space (4:8

H_VID2 28

or 5:10),Zo=55ohm +-15%

H_VID3 28

H_VID4 28

H_VID5 28

H_VID6 28

VCCSENSE 28

VSSSENSE 28

R24

Layout note:

Route VCCSENSE and

100_1%_06

VSSSENSE traces at 27.4Ohm

with 50 mil spacing.

Place PU and PD within 1

inch of CPU.

+VCORE

AC10

AB10

AB12

AB14

AB15

AB17

AB18

AA10

AA12

AA13

AA15

AA17

AA18

AA20

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AB9

JSKT1C

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

PZ47913-2741-01

+1.5VS

+VCORE

Place these inside socket cavity on L8 (North side secondary)

C450

C445

22U_6.3V_08

Layout note:

+VCORE

Place these inside soc ket cavit y on L 8 (South side sec ondary)

C441

22U_6.3V_08

+VCO RE

Place these inside socket cavity on L1 (North side Primary)

C63

10u/10V_08

+VCORE

Place these inside socket cavity on L1 (South si de Primary)

C39

10u/10V_08

+1.05VS

viax20

Place these inside socket cavity on L8 (North side secondary)

C26

0.1u/16V_04

CPUVS Decoupling Guidelines : 1.5mOhm

used 330uF * 6 ( max ESR = 9mOhm / cap. )

& 3mOhm used 22uF * 32 MLCC

+VCORE

Place these inside socket cavity on L1 (South si de Primary)

C434

0.1u/16V_04

22U_6.3V_08

C439

22U_6.3V_08

C64

10u/10V_08

C432

22U_6.3V_08

10A 400MIL

C28

0.1u/16V_04

C453

0.1u/16V_04

C44

10u/10V_08

6 * 330uF (9mohm ESR each, 1.8nH ESL each)

3 on the north , 3 on the south

C438

22U_6.3V_08

C65

10u/10V_08

C61

10u/10V_08

C27

0.1u/16V_04

C452

0.1u/16V_04

C45

10u/10V_08

C448

22U_6.3V_08

C66

10u/10V_08

C436

22U_6.3V_08

C31

0.1u/16V_04

C435

0.1u/16V_04

C46

10u/10V_08

C446

22U_6.3V_08

C42

10u/10V_08

C43

10u/10V_08

C30

0.1u/16V_04

C447

0.1u/16V_04

C47

10u/10V_08

C449

22U_6.3V _08

C67

10u/10V_08

C454

22U_6.3V _08

+1.05 VS

C29

0.1u/16V_04

C433

0.1u/16V_04

C48

10u/10V_08

C442

22U_6.3V_08

C68

10u/10V_08

C60

10u/10V_08

C75

0.1u/16V_04

C62

10u/10V_08

C437

22U_6.3V_08

C444

22U_6.3V _08

C38

10u/10V_08

C73

0.1u/16V_04

C76

0.1u/16V_04

C74

0.1u/16V_04

A4

A8

A11

A14

A16

A19

A23

A26

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3

PZ47913-2741- 01

JSKT1D

VSS[00 1]

VSS[00 2]

VSS[00 3]

VSS[00 4]

VSS[00 5]

VSS[00 6]

VSS[00 7]

VSS[00 8]

VSS[00 9]

VSS[01 0]

VSS[01 1]

VSS[01 2]

VSS[01 3]

VSS[01 4]

VSS[01 5]

VSS[01 6]

VSS[01 7]

VSS[01 8]

VSS[01 9]

VSS[02 0]

VSS[02 1]

VSS[02 2]

VSS[02 3]

VSS[02 4]

VSS[02 5]

VSS[02 6]

VSS[02 7]

VSS[02 8]

VSS[02 9]

VSS[03 0]

VSS[03 1]

VSS[03 2]

VSS[03 3]

VSS[03 4]

VSS[03 5]

VSS[03 6]

VSS[03 7]

VSS[03 8]

VSS[03 9]

VSS[04 0]

VSS[04 1]

VSS[04 2]

VSS[04 3]

VSS[04 4]

VSS[04 5]

VSS[04 6]

VSS[04 7]

VSS[04 8]

VSS[04 9]

VSS[05 0]

VSS[05 1]

VSS[05 2]

VSS[05 3]

VSS[05 4]

VSS[05 5]

VSS[05 6]

VSS[05 7]

VSS[05 8]

VSS[05 9]

VSS[06 0]

VSS[06 1]

VSS[06 2]

VSS[06 3]

VSS[06 4]

VSS[06 5]

VSS[06 6]

VSS[06 7]

VSS[06 8]

VSS[06 9]

VSS[07 0]

VSS[07 1]

VSS[07 2]

VSS[07 3]

VSS[07 4]

VSS[07 5]

VSS[07 6]

VSS[07 7]

VSS[07 8]

VSS[07 9]

VSS[08 0]

VSS[08 1]

VSS[0 82]

VSS[0 83]

VSS[0 84]

VSS[0 85]

VSS[0 86]

VSS[0 87]

VSS[0 88]

VSS[0 89]

VSS[0 90]

VSS[0 91]

VSS[0 92]

VSS[0 93]

VSS[0 94]

VSS[0 95]

VSS[0 96]

VSS[0 97]

VSS[0 98]

VSS[0 99]

VSS[1 00]

VSS[1 01]

VSS[1 02]

VSS[1 03]

VSS[1 04]

VSS[1 05]

VSS[1 06]

VSS[1 07]

VSS[1 08]

VSS[1 09]

VSS[1 10]

VSS[1 11]

VSS[1 12]

VSS[1 13]

VSS[1 14]

VSS[1 15]

VSS[1 16]

VSS[1 17]

VSS[1 18]

VSS[1 19]

VSS[1 20]

VSS[1 21]

VSS[1 22]

VSS[1 23]

VSS[1 24]

VSS[1 25]

VSS[1 26]

VSS[1 27]

VSS[1 28]

VSS[1 29]

VSS[1 30]

VSS[1 31]

VSS[1 32]

VSS[1 33]

VSS[1 34]

VSS[1 35]

VSS[1 36]

VSS[1 37]

VSS[1 38]

VSS[1 39]

VSS[1 40]

VSS[1 41]

VSS[1 42]

VSS[1 43]

VSS[1 44]

VSS[1 45]

VSS[1 46]

VSS[1 47]

VSS[1 48]

VSS[1 49]

VSS[1 50]

VSS[1 51]

VSS[1 52]

VSS[1 53]

VSS[1 54]

VSS[1 55]

VSS[1 56]

VSS[1 57]

VSS[1 58]

VSS[1 59]

VSS[1 60]

VSS[1 61]

VSS[1 62]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

B - 4 PROCESSOR 2/2

+VCORE

Place these inside socket cavity on L1 (South si de Primary)

C41

C440

C69

1U_50V_06

1U_50V_06

1U_50V_06

C70

1U_50V_06

C443

1U_50V_06

C40

1U_50V_06

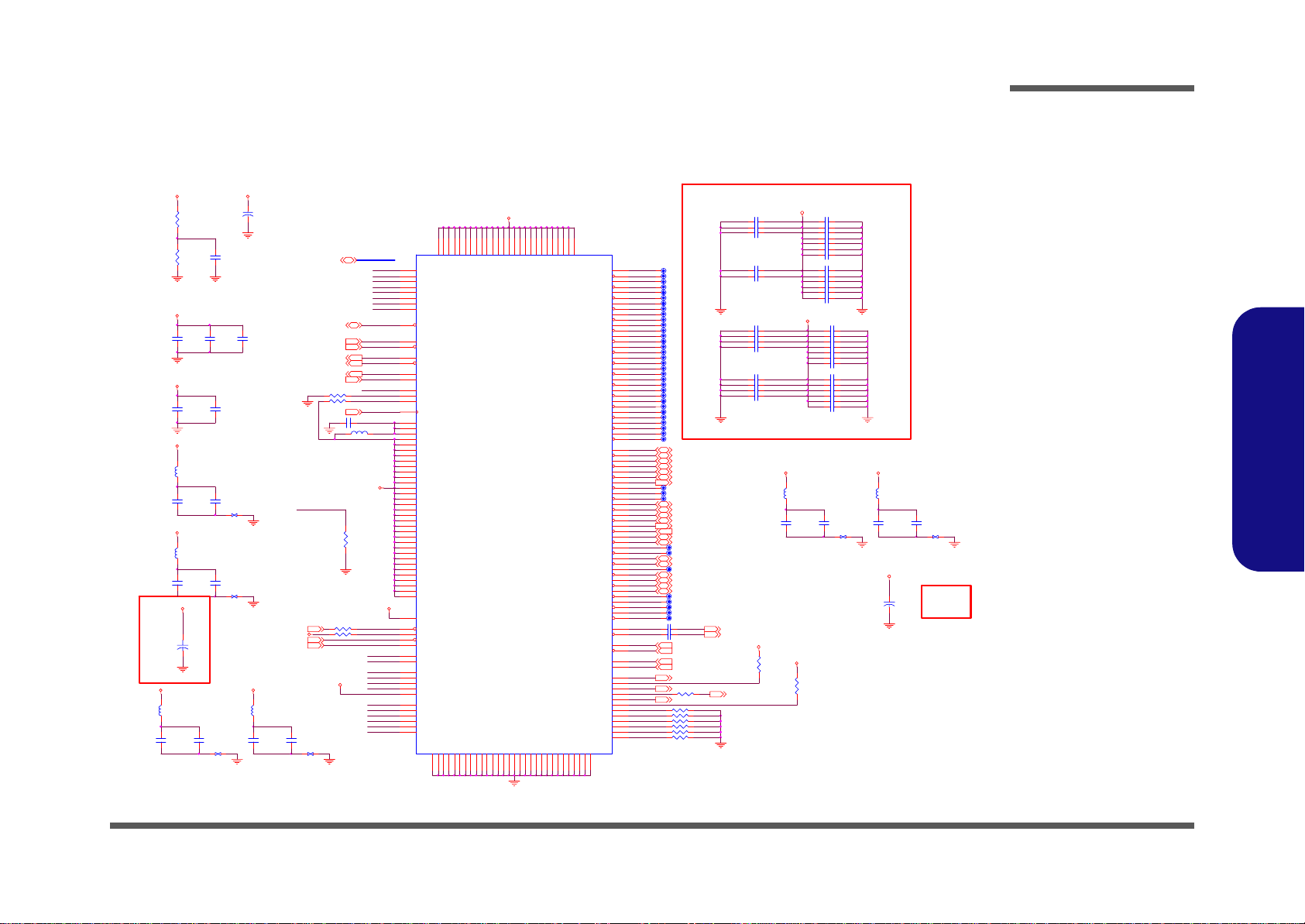

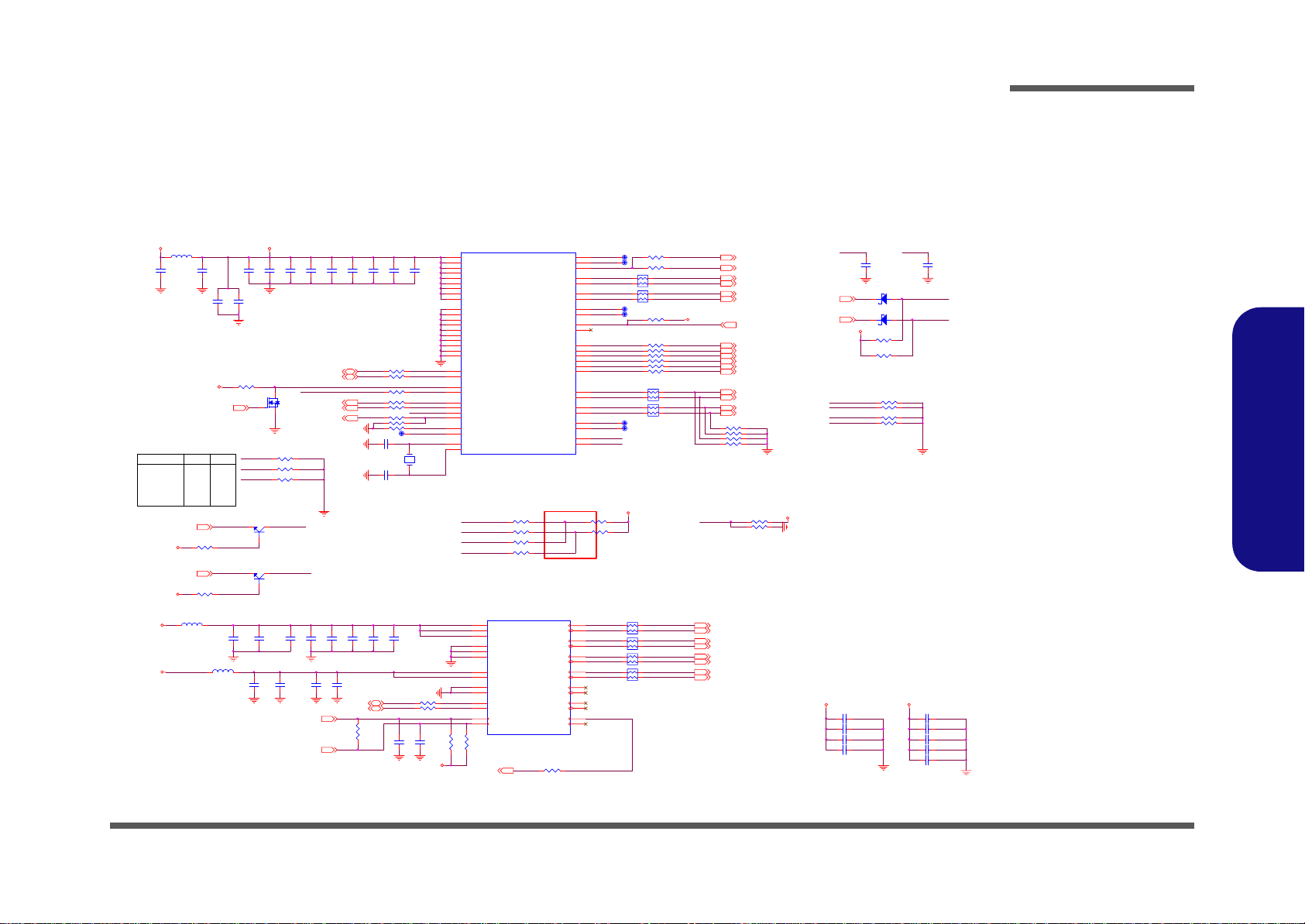

Page 5

VN896 1/4

Schematic Diagrams

+1.05VS

A17

A18

A19

A20

A21

B17

B18

B19

B20

B21

C17

C18

C19

C20

C21

D17

D18

D19

D20

D21

E17

E18

E19

E20

E21

F17

F18

F19

F20

F21

G17

G18

G19

G20

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0

H_RS#1

H_RS#2

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

GTLCOMPP

GTLCOMPN

C107

AA36

AA34

AA32

AC29

AC30

W35

W36

W34

W32

W31

W33

M33

N34

R33

T33

R34

P36

P34

N35

R36

U36

U34

U35

T30

U32

V32

V36

V34

V33

Y35

Y33

V31

R35

L35

K35

J32

M34

K32

J33

K33

L36

L34

J34

M35

T32

T31

R32

M32

M31

J35

N36

J36

C31

E35

G27

D22

F22

U30

J25

G22

H22

BGA1A

HA03#

HA04#

HA05#

HA06#

HA07#

HA08#

HA09#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADSTB0P#

HADSTB1#

ADS#

BNR#

BPRI#

BREQ0#

DBSY#

DEFER#

DRDY#

HIT#

HITM#

HLOCK#

HTRDY#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

RS0#

RS1#

RS2#

HDBI0#

HDBI1#

HDBI2#

HDBI3#

CPURST#

HCLK+

HCLK-

GTLVREF0

GTLVREF1

GTLCOMPP

GTLCOMPN

GND

A1A2A8

VTT

VTT

VTT

VTT

VTT

P4M890 =>HA32,HA33

VN896

GND

GND

GND

GND

GND

A10

A22

A25

A3

VTT

VTT

VTT

VTT

GND

GND

GND

GND

A27

A29

A31

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

P4M890_Rev1.9->remove ha3 2, ha3 3

P4M900_Rev0.2

GND

GND

GND

GND

GND

GND

GND

GND

A33

A35B2B3B4B36C2C3C4C5E6C26

VTT

GND

VTT

VTT

GND

GND

C27

VTT

VTT

VTT

VTT

P4M900 only -->

GND

GND

GND

GND

D3

D4D5D6D8D11

VTT

VTT

GND

GND

H_REQ#[4:0]

H_RS#[2:0]

H_DINV#[3:0]

R107 180_1%_06

R106 360_1%_06

C119

C121

0.01U_25V_04

H_A# [31: 3]

GTLVREF_NB

0.01U_25V_04

H_A#[31:3]2

H_ADSTB#02

H_ADSTB#12

H_ADS#2

H_BNR#2

H_BPRI#2

H_BREQ#02

H_DBSY#2

H_DEFER#2

H_DRDY#2

H_HIT#2

H_HITM#2

H_LOCK#2

CLK_MCH_BCLK10

CLK_MCH_BCLK#10

+1.05VS

C124

0.01U_25V_04

H_TRDY#2

H_CPURST#2

GTLVREF_NB

0.01U_25V_04

H_REQ#[4:0]2

H_RS#[2:0]2

H_DINV#[3:0]2

G21

HD00#

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

HD01#

HD02#

HD03#

HD04#

HD05#

HD06#

HD07#

HD08#

HD09#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HDSTB0P#

HDSTB0N #

HDSTB1P#

HDSTB1N #

HDSTB2P#

HDSTB2N #

HDSTB3P#

HDSTB3N #

HADSTB0N#

CPUSLPIN#

DPWR#

GND

GND

GND

GND

GND

GND

GND

GND

D23

D24

D29

D31

D32

D34E2E4

H_D#[63:0]

B35

H_D#0

A36

H_D#1

VTT

H_D#2

C33

C32

H_D#3

E31

H_D#4

H_D#5

B34

B33

H_D#6

H_D#7

A34

D30

H_D#8

A30

H_D#9

H_D#10

B31

H_D#11

B30

E30

H_D#12

H_D#13

C29

B29

H_D#14

C30

H_D#15

D36

H_D#16

H_D#17

F36

G36

H_D#18

H34

H_D#19

H_D#20

H35

F35

H_D#21

H_D#22

G35

C36

H_D#23

D35

H_D#24

F34

H_D#25

F33

H_D#26

H_D#27

G34

G33

H_D#28

E33

H_D#29

H_D#30

H32

G32

H_D#31

E28

H_D#32

H_D#33

E29

D28

H_D#34

H_D#35

D27

C28

H_D#36

H28

H_D#37

H_D#38

G28

H_D#39

F28

H_D#40

E27

D26

H_D#41

D25

H_D#42

H_D#43

E25

F25

H_D#44

H_D#45

G25

H_D#46

H26

H_D#47

H25

B23

H_D#48

B25

H_D#49

H_D#50

E23

H_D#51

B27

H_D#52

B28

H_D#53

A28

B24

H_D#54

B26

H_D#55

H_D#56

A26

C23

H_D#57

C22

H_D#58

A23

H_D#59

H_D#60

G23

A24

H_D#61

B22

H_D#62

H_D#63

E22

H_DSTBP#0

A32

H_DSTBN#0

B32

H_DSTBP#1

C35

C34

H_DSTBN#1

H_DSTBP#2

G26

H_DSTBN#2

E26

H_DSTBP#3

C24

C25

H_DSTBN#3

H_ADSTB0#

T35

H_CPUSLP#

AB32

H_DPWR#

L31

GND

GND

GND

E5

H_D#[63:0] 2

H_DSTBP#[3:0]

H_DSTBN#[3:0]

H_ADSTB0# 2

H_CPUSLP# 2,15

H_DPWR# 2

+1.0 5V S

H_DSTBP#[3:0] 2

H_DSTBN#[3:0] 2

+1.05VS

R102 49.9_1%_06

R96

100_1%_06

GTLVREF_NB

B.Schematic Diagrams

Sheet 4 of 39

VN896 1/4

C140

1000P_X7R_04

C144

1000P_X7R_04

C148

1U_10V_06

C156

0.1U_16V_04

C147

0.1U_16V_04

C108

0.1U_16V_04

C97

0.1U_16V_04

C469

0.1U_16V_04

C153

0.1U_16V_04

C139

0.1U _16V_04

C104

0.1U _16V_04

C101

0.1U_16V_04

C94

10U_10V_08

C489

10U_10V_08

C487

10U_10V_08

C96

10U_10V_08

VN896 1/4 B - 5

Page 6

Schematic Diagrams

Sheet 5 of 39

VN896 2/4

B.Schematic Diagrams

VN896 2/4

MD_[6 3:0]8, 9

M_DM[0..7]8,9

MD_[63:0]

M_D M[0 . .7 ]

MD_0

MD_1

MD_2

MD_3

MD_4

MD_5

MD_6

MD_7

MD_8

MD_9

MD_10

MD_11

MD_12

MD_13

MD_14

MD_15

MD_16

MD_17

MD_18

MD_19

MD_20

MD_21

MD_22

MD_23

MD_24

MD_25

MD_26

MD_27

MD_28

MD_29

MD_30

MD_31

MD_32

MD_33

MD_34

MD_35

MD_36

MD_37

MD_38

MD_39

MD_40

MD_41

MD_42

MD_43

MD_44

MD_45

MD_46

MD_47

MD_48

MD_50

MD_51

MD_52

MD_53

MD_54

MD_55

MD_56

MD_57

MD_58

MD_59

MD_60

MD_61

MD_62

MD_63

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

AF35

AG34

AK35

AF34

AG35

AK34

AG32

AF32

AH30

AF31

AH32

AH31

AK33

AP35

AM35

AM34

AK24

AM24

AK23

AN24

AM23

AM22

AK20

AK19

AM19

AR18

AM20

AM18

AR17

AN16

AN15

AM17

AP17

AM16

AM15

AN22

AN21

AP19

AR21

AR19

AR14

AM14

AP13

AR11

AP14

AN14

AP12

AH36

AF30

AN36

AN23

AN20

AP21

+1.8V

+1.8V

AC24

AD17

AD19

AD21

AJ28

AK25

AK27

AK29

AL26

AL28

AL30

AM25

AM29

AM31

AN26

AA24

AB24

BGA1B

MD00

MD01

AJ36

MD02

MD03

VCCMEM

MD04

MD05

AJ34

MD06

MD07

MD08

MD09

MD10

AJ31

MD11

MD12

MD13

MD14

AJ32

MD15

MD16

AL36

MD17

MD18

AL34

MD19

AL35

MD20

MD21

AT36

MD22

MD23

MD24

AL23

MD25

MD26

AJ22

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

AL20

MD36

MD37

AL18

MD38

MD39

MD40

AT16

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

AT18

MD51

AT21

MD52

MD53

AT19

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

AT12

MD62

MD63

DQM0#

DQM1#

DQM2#

DQM3#

DQM4#

AT15

DQM5#

DQM6#

AT13

DQM7#

AD23

AD24

AJ26

AD22

AD20

AD16

AD18

VCCM EM

VCCMEM

VCCMEM

VCCM EM

VCCMEM

VCCMEM

VCCM EM

VCCMEM

VCCM EM

VCCM EM

VCCMEM

VCCM EM

VCCM EM

VCCMEM

VCCMEM

AN27

AM27

VCCMEM

VCCMEM

VCCM EM

VCCM EM

VCCMEM

VCCM EM

VCCMEM

VCCMEM

VCCM EM

VCCMEM

AT35

AN31

AN33

AP30

AR26

AR33

AT25

AT28

AT31

AR28

M_BA0

BA0

AP29

M_BA1

BA1

VCCMEM

VCCMEM

VCCMEM

VCCM EM

VCCM EM

VCCMEM

VCCMEM

VCCM EM

VCCMEM

M_BA2

AP33

BA2

MAA0

AT29

MA00

AR30

MAA1

MA01

AR29

MAA2

MA02

AT30

MAA3

MA03

AN30

MAA4

MA04

AP31

MAA5

MA05

MAA6

AR31

MA06

MAA7

AT32

MA07

AP32

MAA8

MA08

AN32

MAA9

MA09

AN29

MAA10

MA10

AR32

MAA11

MA11

MAA12

AT33

MA12

MAA13

AR25

MA13

M_RAS#

AN28

SRAS#

M_CAS#

AR27

SCAS#

AP28

M_WE#

SWE#

AT27

M_CS0#

CS0#

M_CS1#

AP27

CS1#

AT24

M_CS2#

CS2#

AP26

M_CS3#

CS3#

AT34

CKE0

AP34

CKE1

AR34

CKE2

AN34

CKE3

AT26

ODT0

AP25

ODT1

AR24

ODT2

AN25

ODT3

M_DQS+0

AJ35

DQS0+

AH35

M_DQS- 0

DQS0-

M_DQS+1

AH33

DQS1+

M_DQS- 1

AH34

DQS1-

M_DQS+2

AR36

DQS2+

M_DQS- 2

AP36

DQS2-

M_DQS+3

AR22

DQS3+

M_DQS- 3

AP23

DQS3-

M_DQS+4

AP18

DQS4+

M_DQS- 4MD_49

AN18

DQS4-

M_DQS+5

AP15

DQS5+

M_DQS- 5

AR15

DQS5-

M_DQS+6

AP20

DQS6+

M_DQS- 6

AR20

DQS6-

M_DQS+7

AR12

DQS7+

M_DQS- 7

AR13

DQS7-

MCLKI T

AB34

MCL KI

M_CLKO +

AB35

MCLKO+

AB36

M_CLKO -

MCLKO-

MVREF _NB

AG29

MEMVREF 0

AJ18

MEMVREF 1

MEMDET

AF36

MEMDET

Z0501

AM33

DMCOMP

M_BA0 8, 9

M_BA1 8, 9

M_BA2 8, 9

MAA[ 0 :1 3]

M_RAS # 8,9

M_CAS # 8,9

M_WE# 8, 9

M_CS0# 8,9

M_CS1# 8,9

M_CS2# 9

M_CS3# 9

M_CKE 0 8,9

M_CKE 1 8,9

M_CKE 2 9

M_CKE 3 9

M_ODT0 8, 9

M_ODT1 8, 9

M_ODT2 9

M_ODT3 9

M_D QS +[ 0. .7 ]

M_DQS-[0..7]

MCLKIT 10

MCLKIT = DCLKx + 2 "

R398 22 _06

R399 22 _06

MCLKO+/- as short as passable

R109 301_1%_06

MAA[0:13] 8,9

M_DQS+[0..7] 8,9

M_DQS-[0..7] 8,9

MCLKOT 10

MCLKOC 10

C173

0.1U_16 V_04

C215

0.1U_1 6V_04

C218

0.1U_16V_04

+1.8V

150_1%_06

150_1%_06

C181

0.1U_16V_04

MEMDET SEL:

0: DDR1

*

1: DDR2

MEMDE T

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA1 0

MAA1 1

MAA1 2

MAA1 3

R114

R112

C180

0.1U_16 V_04

C528 5P_50V _06

C523 5P_50V _06

C525 5P_50V _06

C522 5P_50V _06

C526 5P_50V _06

C516 5P_50V _06

C521 5P_50V _06

C509 5P_50V _06

C510 5P_50V _06

C513 5P_50V _06

C531 5P_50V _06

C507 5P_50V _06

C504 5P_50V _06

C534 5P_50V _06

MCLKI T

C483

*5P_50V_06

Near to NB chip

MVREF_ NB

C188

1000P_X7R_04

C207

C204

0.1U_1 6V_04

R99 1K_06

R103 *1K_06

0.1U_16V_04

+1.8V

C136

0.1U_16 V_04

CLOSE TO SOD I M M

C530 5P_50V_06

C527 5P_50V_06

C501 5P_50V_06

C532 5P_50V_06

C535 5P_50V_06

C533 5P_50V_06

C199

1000P_X7R_04

C149

1000P_X7R_04

C141

1000P_X7R_04

C217

0.1U_16 V_04

M_BA 0

M_BA 1

M_BA 2

M_R AS #

M_C AS #

M_W E#

C172

0.1U_16V_04

+1.8V

C154

0.1U_16V_04

C165

0.1U_16V_04

C167

0.1U_16V_04

C158

0.1U_16 V_04

C157

0.1U_16 V_04

B - 6 VN896 2/4

GND

GND

E7

E9

VN896

GND

GND

GND

GND

E34

E36F1F2F4F5F6F7

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

F10

F14

F23

F26

F27

F29

F30

F32G1G2G4G7

G11

G29H2H4H7H23

H24

F24

H27

H31

H33

GND

H36J2J4J5J6

GND

J7

Page 7

VN896 3/4

Schematic Diagrams

+1.5VS

R146

1.4K_1%_ 06

LVREF_NB

R149

1K_1%_06

C236

0.1U_16V_04

LVREF_NB => VT8237A =0.625

+1.5VS

C143

C196

0.1U_16V_04

0.1U_16V_04

+1.5VS

C160

C128

0.1U_16V_04

0.1U_16V_04

+3VS

FB1

HCB201 2KF-12 1T30_08

AVDD1

C109

C102

1000P_X7R_04

22U_6. 3V_08

GNDAHCK

FB2

HCB201 2KF-12 1T30_08

AVDD2

C105

1000P_X7R_04

GNDA MCK

+3VS

+

C536

1U_50V_06

S11

S2 SH ORT

C99

22U_6. 3V_08

S1

1206

21

SHORT

C713

*100u/ 6.3V_ B2

+3VS

1000P_X7R_04

+3VS

FB14

HCB2012KF- 121T30_08

VCCA33PEX0

C537

GNDAPEX0

+1.5VS

C549

+

330U_6.3V_D

C166

1000P_X7R_04

21

21

SHORT

+3VS

1000P_X7R_04

CLOSE TO NB

PM_SUS_STAT#14

+1.8V

BUF_PLT_RST#13

SB_PWROK14,30

FB7

HCB2012KF -121T30_08

VCCA3 3PEX1

C226

C225

1U_50V_06

GNDAPEX1

S4

VLAD[0 ..7]15

VBE#15

UPSTB15

UPSTB#15

DNSTB15

DNSTB#15

UPCMD15

DNCMD15

R457 270_1%_06

R456 340_1%_06

GCLK_NB10

C203 0.1U_16V_04

TESTI N_ NB

R105

4.7K_06

R403 0_04

R104 *4.7K_06

+1.5V

21

SHORT

VLAD[0..7]

L15

HCB1608KF-121 _06

+1.5VS

Z0602

TESTI N_N B

VCCA33 PEX0

VCCA33 PEX1

VCCA33 PEXCK

VCCA33 PEX2

VLAD0

VLAD1

VLAD2

VLAD3

VLAD4

VLAD5

VLAD6

VLAD7

UPSTB

UPSTB#

DNSTB

DNSTB#

UPCMD

DNCMD

LVREF_NB

LCOMPP

LCOMPN

Z0601

+1.5V

AVDD1

AVDD2

GNDAHCK

GNDAMCK

GNDAPEX0

GNDAPEX1

GNDAPEXCK

GNDAPEX2

AD13

AD14

AD15

AA12

AB12

AB25

AC12

AC25

AD12

AD31

AD35

AE36

AD36

AD34

AC31

AD30

AC32

AD29

AP1

AN3

AT3

AR4

AN2

AN1

AP5

AN5

AN4

AT2

AR3

AR1

AT1

AR5

AP4

AL6

AM5

AL5

AL4

M12

M13

M14

M15

M16

M20

M21

M22

M23

M24

N12

N25

P12

P25

R12

T12

T25

U12

U25

V12

W12

W25

Y12

Y25

AE6

AH5

AH3

AF7

AE7

AH6

AH4

G6

H6

N13

BGA1C

VD00

VD01

VD02

VD03

VD04

VD05

VD06

VD07

VBE#

UPSTB+

UPSTB-

DNSTB+

DNSTB-

UPCMD

DNCMD

VLVREF

VLCOMPP

VLCOMPN

VCLK

VCC15VL

VCC15VL

VCC15VL

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VSUS15

SUSST#

TESTI N#

RESET#

PWROK

VCCA3 3HCK

VCCA3 3MCK

VCCA3 3PEX0

VCCA3 3PEX1

VCCA3 3PEXCK

VCCA3 3PEX2

VSUS15PEX

GNDAHCK

GNDAMCK

GNDAPEX0

GNDAPEX1

GNDAPEXCK

GNDAPEX2

GND

K4

K2

+3VS

W13

Y13

AA13

AB13

AC13

AJ1

AJ2

AJ3

AJ4

AJ5

VCC33PE X

GND

L32

VCC33PEX

VCC33PEX

GND

GND

L33M5M7

M2

AJ6

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PE X

VCC33PEX

GND

GND

GND

GND

GND

GND

M36N2N5N7P2P7P14

AJ7

AK3

AK4

AK1

AK2

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

PEXRX03-/DVP TVCLKR

GND

GND

GND

GND

P5

P6

AK5

AK6

AK7

PE XTX00 +

PEXTX00-

VCC33PEX

VCC33PEX

VCC33PE X

VCC33PEX

PE XTX01 +

PEXTX01PE XTX02 +

PEXTX02PE XTX03 +

PEXTX03PE XTX04 +

PEXTX04PE XTX05 +

PEXTX05PE XTX06 +

PEXTX06PE XTX07 +

PEXTX07PE XTX08 +

PEXTX08PE XTX09 +

PEXTX09PE XTX10 +

PEXTX10PE XTX11 +

PEXTX11PE XTX12 +

PEXTX12PE XTX13 +

PEXTX13PE XTX14 +

PEXTX14PE XTX15 +

PEXTX15-

PEXRX00+/DVP0D11

PEXRX00-/DVP0D10

PEXRX01+/DVP0D09

PEXRX01-/DVP0D08

PEXRX02+/DVP0D07

PEXRX02-/DVP0D06

PEXRX03+/DVP0CLK

PEXRX04+/DVP0D05

PEXRX04-/DVP0D04

PEXRX05+/DVP0D03

PEXRX05-/DVP0D02

PEXRX06+/DVP0D01

PEXRX06-/DVP0D00

PEXRX07+/DVP0DE

PEXRX07-/DVP0HS

PEXRX08+/DVP1D11

PEXRX08-/DVP1D10

PEXRX09+/DVP1D09

PEXRX09-/DVP1D08

PEXRX10+/DVP1D07

PEXRX10-/DVP1D06

PEXRX11+/DVP1CLK

PEXRX11-/DVP1D05

PEXRX12+/DVP1D04

PEXRX12-/DVP1D03

PEXRX13+/DVP1D02

PEXRX13-/DVP1D01

PEXRX14+/DVP1D00

PEXRX14-/DVP1DE

PEXRX15+/DVP1HS

PEXRX15-/DVP1VS

PE XTX16 +

PEXTX16-

PEXRX16+

PEXRX16PEXCLK+

PEXCLK-

PEXDET

PEXWAKE#

PEXHPSCI#

PEXPMESCI#

TCSE N#

PEXCOMP0

PEXCOMP1

PEXREXT0

PEXREXT1

PEXCOMP2

PEXREXT2

GND

GND

GND

GND

GND

GND

P15

P16

P17

P18

P19

P20

Z0605

B1

Z0606

C1

Z0607

D1

Z0608

E1

Z0609

H1

Z0610

J1

Z0611

K1

Z0612

L1

Z0613

L4

Z0614

M4

Z0615

M1

Z0616

N1

Z0617

N4

Z0618

P4

Z0619

P1

Z0620

R1

Z0621

T1

Z0622

U1

Z0623

U4

Z0624

V4

Z0625

V1

Z0626

W1

Z0627

W4

Z0628

Y4

Z0629

Y1

Z0630

AA1

Z0631

AB1

Z0632

AC1

Z0633

AC4

Z0634

AD4

Z0635

AD1

Z0636

AE1

FPD23

E3

D2

F3

G3

H3

J3

K3

L3

K6

L6

M3

N3

M6

N6

P3

R3

T3

U3

T6

U6

V3

W3

W6

V6

Y3

AA3

AA6

AB6

AB3

AC3

AD3

AE3

AG1

AF1

AF4

AE4

AG6

AF6

B6

INTR#

B5

AC34

AC36

AC33

D7

H5

AD7

G5

AD6

AH1

AH2

GND

VN896

FPD22

FPD21

FPD20

FPD19

FPD18

DVP0CLK

PE0RX3#

PE0RX4

PE0RX4#

FPD15

FPD14

FPD13

FPD12

DVP0DE

DVP0HS

FPD11

FPD10

FPD09

FPD08

FPD07

FPD06

DVP1CLK

FPD05

FPD04

FPD03

FPD02

FPD01

FPD0

DVP1DE

DVP1HS

DVP1VS

Z0603

Z0604

PEXDET

Z0637

PEXMESCI #

TCSE N #

PEXCOMP0

PEXCOMP1

PEXREXT0

PEXREXT1

PEXCOMP2

PEXREXT2

FPD23 12

FPD22 12

FPD21 12

FPD20 12

FPD19 12

FPD18 12

DVP0CLK 12

FPD15 12

FPD14 12

FPD13 12

FPD12 12

DVP0DE 12

DVP0HS 12

FPD11 12

FPD10 12

FPD07 12

FPD06 12

FPD05 12

FPD04 12

FPD03 12

FPD02 12

C542 .1U_X7R_04

C541 .1U_X7R_04

PCIE_RXP2_NC 25

PCIE_ RXN2_NC 25

NB_PEXCLK 10

NB_PEXCLK# 10

PCI_INTH# 13

PCIE_ WAKE# 14, 16,25

R401 *0_04

PEXMESCI# 14

R447 249_ 1%_06

R452 249_ 1%_06

R445 10.7K_1%_06

R454 10.7K_1%_06

R453 249_ 1%_06

R455 10.7K_1%_06

T13

U13

V13

R13

N14

P13

VCC33PEX

VCC33PEX

VCC33PEX

VCC33PEX

VCC33 PEX

VCC33PEX

VCC33PE X

VCC33PEX

VCC33PEX

GND

GND

GND

GND

GND

GND

GND

GND

GND

K5K7K31

K34

K36L2L7

L5

C262 0.1U_16V_04

C264 0.1U_16V_04

C159 0.1U_16V_04

C169 0.01U_25V_04

C263 0.01U_25V_04

C135 0.1U_16V_04

C138 0.1U_16V_04

C131 0.1U_16V_04

C129 0.1U_16V_04

C125 0.01U_25V_04

C120 0.01U_25V_04

C142 0.01U_25V_04

C122 0.01U_25V_04

PCIE_TXP2_NC 25

PCIE_TXN2_NC 25

PEXHPSCI# 15,25

under NB( solder side)

+3VS

R437

4.7K_04

+3VS

+1.5 VS

+3VS

FB8

HCB2012KF -121T30_08

VCCA33PEXCK

C231

1000P_X7R_04

GNDAPEXCK

+3VS

R121

4.7K_04

C220 4.7U_6.3 V_06

C252 4.7U_6.3 V_06

C248 4.7U_6.3 V_06

C247 4.7U_6.3 V_06

C550 4.7U_6.3 V_06

C551 4.7U_6.3 V_06

C552 4.7U_6.3 V_06

C191 2.2U_6.3 V_06

C187 2.2U_6.3 V_06

C171 2.2U_6.3 V_06

C175 2.2U_6.3 V_06

C177 2.2U_6.3 V_06

C183 2.2U_6.3 V_06

C214 4.7U_6. 3V_06

C210 4.7U_6. 3V_06

C186 4.7U_6. 3V_06

C198 4.7U_6. 3V_06

C205 4.7U_6. 3V_06

C182 4.7U_6. 3V_06

C127 4.7U_6. 3V_06

C155 2.2U_6. 3V_06

C216 2.2U_6. 3V_06

C137 2.2U_6. 3V_06

C146 2.2U_6. 3V_06

C152 2.2U_6. 3V_06

C178 2.2U_6. 3V_06

C234

1U_50V_06

S6

+3VS

1000P_X7R_04

21

SHORT

+1.5VS

NEAR NB(VN896)

FB9

HCB2012KF-12 1T30_08

VCCA33 PEX2

C227

C229

1U_50V_06

GNDA PEX2

S5

+

CA1

330U_6.3V_D

21

SHOR T

1201

DEL

B.Schematic Diagrams

Sheet 6 of 39

VN896 3/4

VN896 3/4 B - 7

Page 8

Schematic Diagrams

VN896 4/4

Sheet 7 of 39

VN896 4/4

B.Schematic Diagrams

+3VS

FB11

HCB2012KF-121T30_08

VCCPLL1

C493

1000P_X7R_04

GNDAPLLB16

+3VS

FB12

HCB2012KF-121T30_08

VCCPLL2

C497

1000P_X7R_04

GNDAPLLB15

+3VS

FB13

HCB2012KF-121T30_08

VCCPLL3

C499

1000P_X7R_04

GNDAPLLB14

PCI_INTA#13,24

ENAVEE12

1U_10V_06

C495

1U_10V_06

C498

1U_10V_06

C500

H10

2

3

1

4

5 6

MTH296D111

VCCPLL1

VCCPLL2

VCCPLL3

2 1

2 1

2 1

9

8

7

VPAR15

R110

R435 0_06

GUICK10

S7 SHOR T

S8 SHOR T

S9 SHOR T

2

3

4

5 6

DACGNDB13

DACGNDB12

80.6_1%_06

GNDAPLLB16

GNDAPLLB15

GNDAPLLB14

GND

GND

GND

H14

1

MTH296D111

Z0704

Z0705

Z0706

Z0707

Z0708

Z0709

Z0710

Z0711

VCCDAC1

VCCDAC2

9

8

7

AR

AG

AB

HSYNC

VSYN C

Z0701

Z0702

Z0703

+3VS

+3VS

AM1

VD08

AM3

VD09

AT5

VD10

AM6

VD11

AL2

VD12

AL1

VD13

AN6

VD14

AT6

VD15

AM4

VPAR

C14

AR

D14

AG

E14

AB

E12

HSYNC

F12

VSYN C

A13

VCCA33DAC1

A12

VCCA33DAC2

B13

GNDADAC

B12

GNDADAC

C13

RSET

H13

INTA#

B8

GPO0

A6

GPOUT

D12

XIN

A16

VCCA3 3PLL1

A15

VCCA3 3PLL2

A14

VCCA3 3PLL3

B16

GNDAPLL

B15

GNDAPLL

B14

GNDAPLL

P21

FB4

HCB2012KF-121T30_08

VCCDAC1

C505

C508

1000P_X7R_04

DACGNDB13

FB3

HCB2012KF-121T30_08

VCCDAC2

C151

C145

1000P_X7R_04

DACGNDB12

H12

2

3

1

4

5 6

MTH296D111

GND

GND

P22

1U_10V_06

1U_10V_06

+3VS

N15

N16

N17

VCC33GFX

VCC33GFX

VCC33GFX

GND

GND

GND

P35

P33

S10 SHORT

2 1

S3 SHOR T

2 1

9

2

8

3

7

4

5 6

U18

U19

GND

GND

GND

R5R6R7

R2R4P23

GND

GND

H5

MTH296D111

U20

U21

GND

GND

GND

VN896

GND

GND

GND

1

U22

U23

U31

U33V2V5V7V14

GND

GND

GND

GND

GND

GND

GND

GND

R14

R15

R16

R17

DVP2D02

DVP2D03

LCDI D1

LCDI D0

DVP2D08

DVP2D09

DVP2D11

9

8

7

C355CH512B296D111N

V15

GND

GND

GND

GND

GND

GND

GND

GND

R18

R19

R20

R21

R22

RN8

1

2

3

4 5

10K_06_8P4R

1

2

3

4 5

10K_06_8P4R

H9

2

3

1

4

5 6

C296D111N

H4

2

3

1

4

5 6

GND

GND

V16

V17

V18

V19

V20

V22

V21

V23

V30

V35W2W5W7W14

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

R23

R30

R31T2T4T5T7

T14

T15

T16

+3VS

678

RN7

1K_06_8P4R

123

4 5

Z0718

8

Z0720

7

Z0719

6

Z0717

+3VS

678

RN13

1K_06_8P4R

RN10

Z0721

8 R127 0_04

123

4 5

Z0722

7

Z0723

6

Z0724

H13

9

2

8

3

1

7

4

5 6

C296D111N

H3

2

9

3

8

1

4

7

5 6

C355CH512B296D111N

GND

GND

GND

GND

GND

GND

GND

GND

T17

T18

T19

T20

R113 0_04

R111 0_04

R118 0_04

R117 0_04

R128 0_04

R130 0_04

R133 0_04

9

2

8

3

7

4

5 6

9

8

7

W15

GND

GND

T21

W16

W17

W18

GND

GND

GND

GND

GND

GND

T22

T23

T34

H8

1

C296D111N

W19

GND

GND

GND

GND

T36U2U5U7U14

+1.05VS

BGA1E

M17

M18

M1

M-MARK 1

Y5

Y6

Y7

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

Y22

Y23

Y30

Y32

Y34

Y36

AA2

AA4

AA5

AA7

AA14

AA15

AA16

AA17

AA18

AA19

AA20

AA21

AA22

AA23

AA31

AA33

AA35

AB2

AB4

AB5

AB7

AB14

AB15

AB16

AB17

AB18

AB19

AB20

AB21

AB22

AB23

AC2

AC5

AC6

AC7

AC14

AC15

AC16

AC17

AC18

AC19

AC20

AC21

AC22

AC23

AD2

AD5

AD32

AE2

AE5

AE32

AE34

AF2

AF3

AF5

AG2

AG3

AG4

AG5

AG30

AG31

AG33

AG36

M8

M-MARK 1

GND

VTT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VN896

GND

GND

GND

AJ23

AJ20

AJ19

AJ33

M6

M-MARK1

W20

W21

W22

W23

Y2

D13

F13

C12

GND

GND

GND

GND

GND

GND

GND

GND

LCDID 0

H11

DVP2D00

DVP2D01

DVP2D02

DVP2D03

DVP2D04

DVP2D05

DVP2D06

DVP2D07

DVP2D08

DVP2D09

DVP2D10

DVP2D11

DVPDET

DVP0VS

DVP2CLK

DVP2DE

DVP2DET

DVP2HS

DVP2VS

SPCLK1

SPCLK2

SPD1

SPD2

BUSY#

DISPCLKO

DISPCLKI

ENBLT

ENVDD

GND

GND

GND

GND

GND

GND

GND

U15

U16

U17

+3VS

RN15

DVP2D07

1

2

DVP2D04

3

DVP2D06

4 5

DVP2D05

10K_06_8P4R

R122 10K_ 04

DVP2D10

9

8

7

M12

M-MARK 1

LCDID0 11

LCDID 1

D10

LCDID1 11

DVP2D02

C11

DVP2D03

C10

DVP2D04

E10

DVP2D05

G10

DVP2D06

F11

DVP2D07

C9

DVP2D08

E8

DVP2D09

B7

DVP2D10

F9

DVP2D11

C7

DVPDET

C6

R120 4.7K_04

A5

B9

D9

A9

E11

B10

C8

G13

A7

E13

AC35

H12

G12

A11

B11

123

8

7

6

M10

M-MAR K1

DVP0VS

Z0733

Z0734

DVP2DET

Z0735

Z0736

NB_LVDSCLK

NB_DDC_CLK

NB_LVDSDATA

NB_DDC_DATA

Z0716

AR

AG

AB

HSYNC

VSYNC

DVP0VS 12

R404 4.7K_04

NB_LVDSCLK 11

NB_DDC_CLK 21

NB_LVDSD ATA 11

NB_DDC_DATA 21

AGP_BU SY# 15

R116 22_04

DISPCLKO

DISPCLKI

R115 4.7K_04

L_BKLTEN 11,21

NB_ENAVDD 11

L11 HCB1608KF-121T25

L12 HCB1608KF-121T25

L14 HCB1608KF-121T25

C133

22P_50V _04

L9 HCB1608KF-121T25

L10 HCB1608KF-121T25

678

4 5

R123 1K_04

22P_50V_04

RN16

1K_06_ 8P4R

Z0728

R163 0_04

Z0725

R162 *0_04

Z0727

R161 *0_04

Z0726

R160 *0_04

Z0729

R125 0_04

+3VS

GFX power up strapping setting:

SW1_1 FD4 =>Po rt Mux ing

0: Two 12-bi t DV I in te rf a ce

1: One 24 -b it Pa nel

interf ace

SW1_2 F D5 =>Dedicated DVI Port Configuration

0: TMDS

1: TV

SW1_3 FD6 =>De dicat ed DVI Po rt S ele cti on

Encoder

0: Dis a bl e

1: Enab le

SW1_4 FD7 =>GFX Clock Select(V CK/LCDCK/ECK)

0: Refer Internal PLL(Default)

1: From External

SW1_ 5 F D10 = >CPUC K/M C K Clo ck Se l ec t

0: From NB(Default)

1: From External

FD[0: 1:2:3 :8:9 :11] Res e r ve d

M14

M13

M5

M-MARK 1

M-MARK1

M-MARK 1

+3VS

+3VS

22P_50V_04

C123

*4.7K_04

NB_LVDSCLK

NB_LVDSDATA

C130

22P_50V_04

C114

22P_50V_04

M7

M-MARK 1

+3V

R434

DISPCLKO 12

DISPCLKI 12

C126

M2

M-MAR K1

+3V

R436

*4.7K_04

DAC_RED 21

DAC_GREEN 21

DAC_BLUE 21

DAC_HSYNC 21

DAC_VSYNC 21

M9

M-MARK 1

T24

R24

N22

N23

N24

P24

M19

N18

N19

N20

N21

U24

V24

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AK17

AK18

AK22

AK32

AL24

AL22

AL19

AL17

AL16

AL15

AK36

AL3

AL7

+1.5VS

W24

Y24

VTT

VTT

VTT

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

AN13

AN12

AM36

AL33

AM2

+3VS

C390

0.1U_16V_04

+1.5 VS

C192

0.1U_16V_04

H7

C296D185N

AE14

AE16

AE18

AE20

AE21

AE22

AJ10

AJ11

AJ12

AJ13

AJ14

AK9

AK10

AK11

AK12

AK13

AK15

AL8

AL9

AL10

AL11

AL12

AL14

AM7

AM8

AM9

AM10

AM11

AM12

AM13

AN7

AN8

AN9

AN10

AN11

AP7

AP8

AP9

AP10

AP11

AR7

AR8

AR9

AR10

AT7

AT8

AT9

AT10

AN17

AN19

AN35

AP2

AP3

AP6

AP16

AP22

AP24

AR2

AR6

AR16

AR23

AR35

AT4

AT11

AT14

AT17

AT20

AT22

AT23

C224

0.1U_16V_04

C553

C213

12

0.1U_16V_04

+

H24

C236D106

EP1

SMD79X197R

*220u_4V_V

H20

C355B158D158

H23

C236D106

M4

M-MARK 1

EP3

SMD79X197R

For EMI

H18

C355B 158D 158

H21

H6_0D2_3

EP2

SMD79X197R

M11

M-MARK 1

EP4

SMD79X197R

H17

C237D83

M3

M-MARK1

H11

C67D67

H6

H7_5D2_8

H2

C158D158

EP5

SMD118X197R

H22

C236D106

H1

C158D158

H15

C158D158

H16

C158D158

H19

C355B158D158

B - 8 VN896 4/4

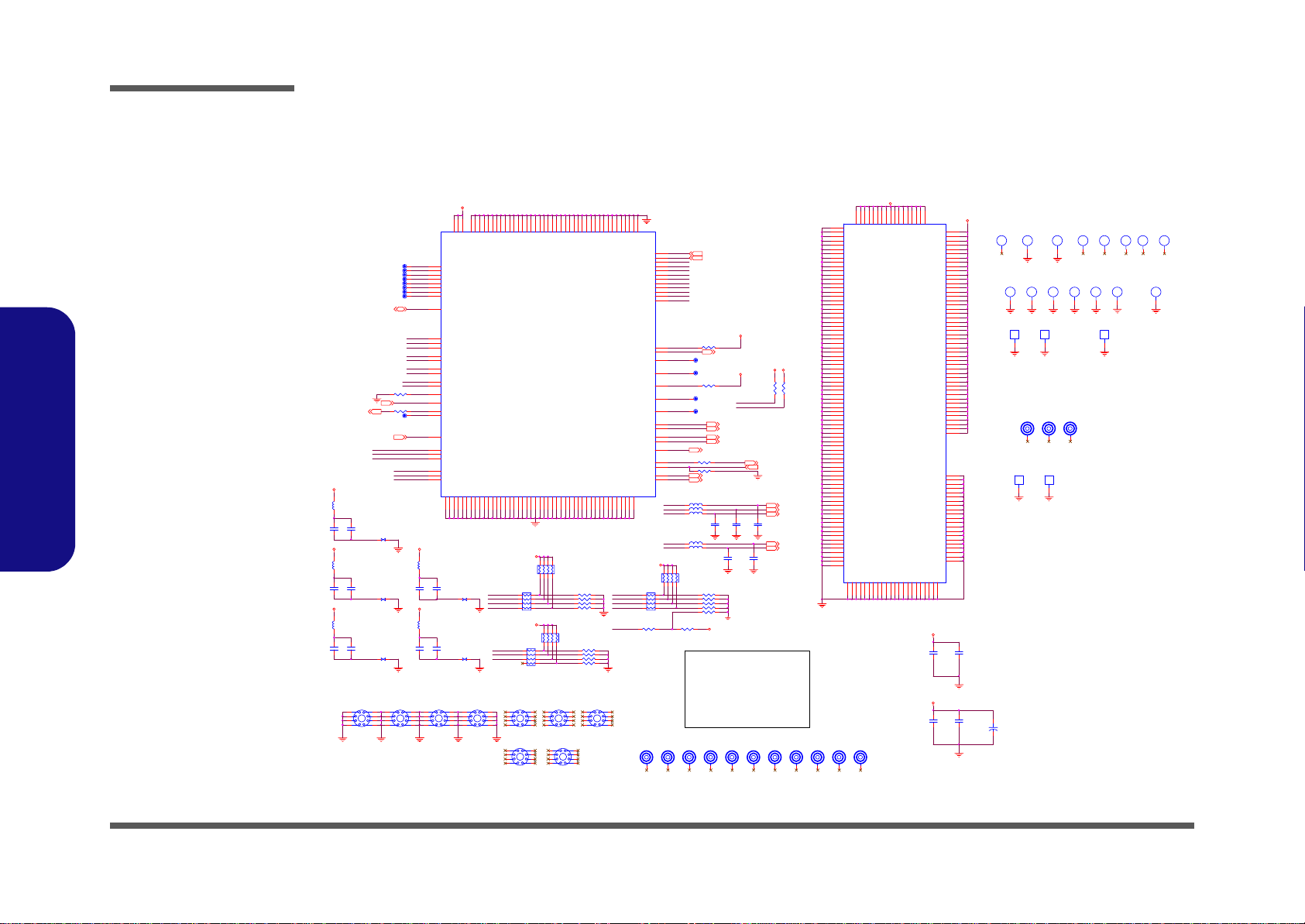

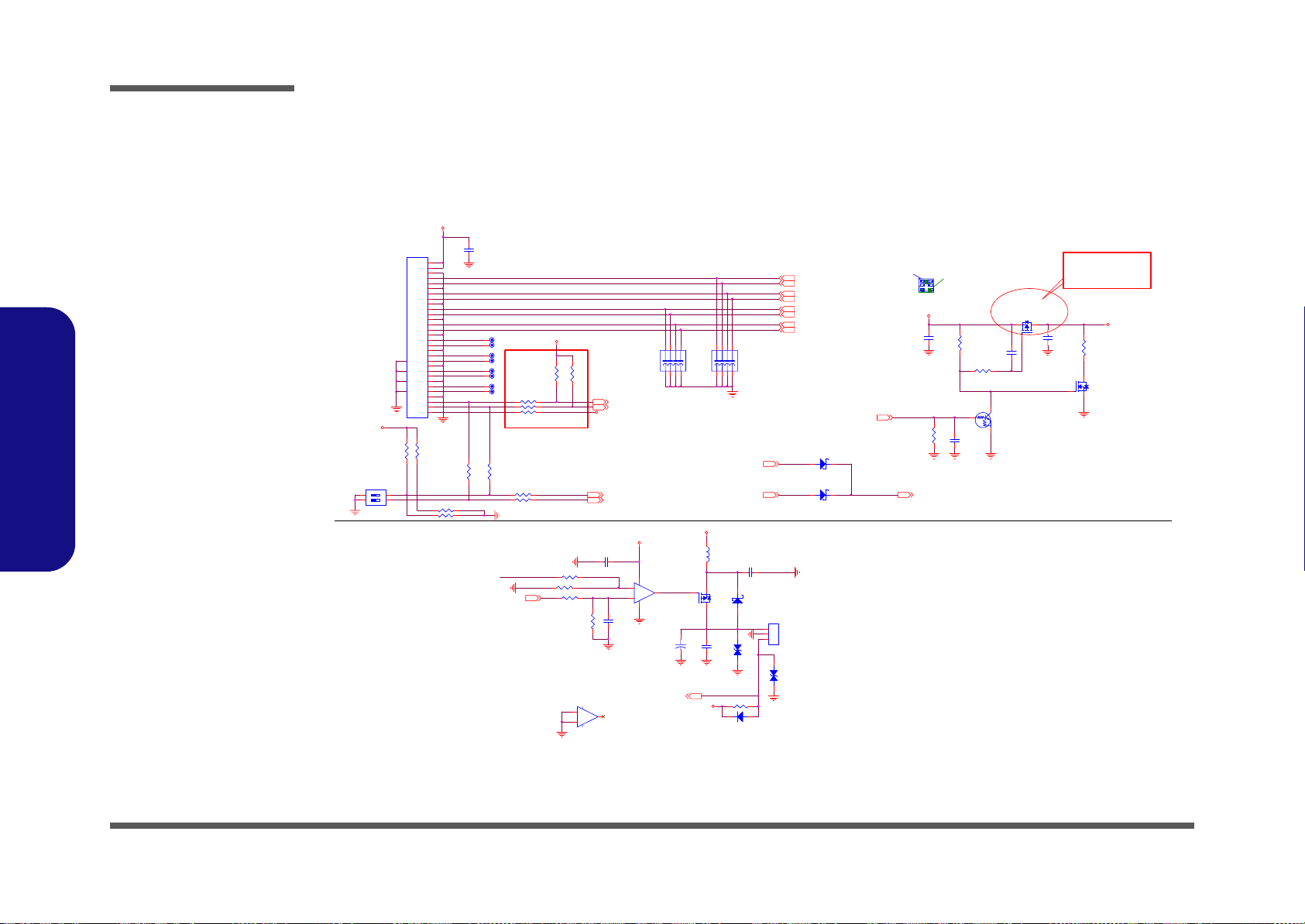

Page 9

DDR2-1

C267

*2.7p/ 50V_04

C268

*2.7p/ 50V_04

Closed to S ODI M M

M_DM[ 0.. 7]5,9

Closed to CN2.

+3V

D11

C

BAV99

AC

A

+3V

D8

C

BAV99

AC

A

+1.8V

M_CLK_DDR0

M_CLK_DDR#0

M_CLK_DDR1

M_CLK_DDR#1

M_DM[0 .. 7]

M_C LK _D D R010

M_C LK _D D R# 010

M_C LK _D D R110

M_C LK _D D R# 110

M_DQS +05, 9

M_DQS -05,9

M_DQS +15, 9

M_DQS -15,9

M_DQS +25, 9

M_DQS -25,9

M_DQS +35, 9

M_DQS -35,9

M_DQS +45, 9

M_DQS -45,9

M_DQS +55, 9

M_DQS -55,9

M_DQS +65, 9

M_DQS -65,9

M_DQS +75, 9

M_DQS -75,9

SMB_SBDATA9,10,14, 16,25

SMB_SBCLK9,10,14, 16,25

+3VS

C261

0.1U_10V_04

DDRVREF GEN. & DECOUPL ING

R147

Trace Width 12 Mil

Space 20 Mil

75_1%_06

SDREFD

C251

C249

R148

2.2U_6.3V_06

75_1%_06

.1U_10V_04

2.2U_6. 3V_06

Schematic Diagrams

+1.8V

818795828896103

111

117

104

112

MAA0

M_DM0

M_DM1

M_DM2

M_DM3

M_DM4

M_DM5

M_DM6

M_DM7

M_DQS +0

M_DQS -0

M_DQS +1

M_DQS -1

M_DQS +2

M_DQS -2

M_DQS +3

M_DQS -3

M_DQS +4

M_DQS -4

M_DQS +5

M_DQS -5

M_DQS +6

M_DQS -6

M_DQS +7

M_DQS -7

SDREFD

MAA1

MAA2

MAA3

MAA4

MAA6

MAA7

MAA8

MAA9

MAA10

MAA11

MAA12

MAA13

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

107

BA0

106

BA1

85

BA2

110

CS0

115

CS1

10

DQM0

26

DQM1

52

DQM2

67

DQM3

130

DQM4

147

DQM5

170

DQM6

185

DQM7

109

WE

113

CAS

108

RAS

79

CKE0

80

CKE1

30

CK0

32

CK0

164

CK1

166

CK1

13

DQS0

11

DQS0

31

DQS1

29

DQS1

51

DQS2

49

DQS2

70

DQS3

68

DQS3

131

DQS4

129

DQS4

148

DQS5

146

DQS5

169

DQS6

167

DQS6

188

DQS7

186

DQS7

195

SDA

197

SCL

Z0801

198

SA0

Z0802

200

SA1

1

VREF

199

VDDSPD

114

ODT0

119

ODT1

2

GND

3

GND

8

GND

9

GND

12

GND

15

GND

18

GND

21

GND

24

GND

GND

GND

2728333439404142474853545960656671727778121

VDD1

VDD2

GND

GND

GND

GND

GND

GND

GND

GND

MAA[0:13]5,9

M_BA05,9

M_BA15,9

M_BA25,9

M_CS0#5,9

M_CS1#5,9

M_DM05,9

M_DM15,9

M_DM25,9

M_DM35,9

M_DM45,9

M_DM55,9

M_DM65,9

M_DM75,9

M_WE#5,9

M_CAS #5,9

M_RAS #5,9

M_CKE 05,9

M_CKE 15,9

R166 10K_04

R167 10K_04

M_OD T05,9

M_OD T15,9

C250

VDD3

GND

VDD4

VDD5

GND

GND

VDD6

VDD7

VDD8

VDD9

GND

GND

GND

GND

1185069838486120

VDD10

VDD11

VDD12

GND

GND

GND

GND

GND

GND

GND

GND

122

127

128

132

133

NC1

NC2

NC3

NC4

NC5

NC6

GND

GND

GND

GND

GND

GND

138

139

144

145

149

CN1

163

NC/TEST

GND

150

7

D1

17

D2

19

D3

4

D4

6

D5

14

D6

16

D7

23

D8

25

D9

35

D10

37

D11

20

D12

22

D13

36

D14

38

D15

43

D16

45

D17

55

D18

57

D19

44

D20

46

D21

56

D22

58

D23

61

D24

63

D25

73

D26

75

D27

62

D28

64

D29

74

D30

76

D31

123

D32

125

D33

135

D34

137

D35

124

D36

126

D37

134

D38

136

D39

141

D40

143

D41

151

D42

153

D43

140

D44

142

D45

152

D46

154

D47

157

D48

159

D49

173

D50

175

D51

158

D52

160

D53

174

D54

176

D55

179

D56

181

D57

189

D58

191

D59

180

D60

182

D61

192

D62

194

D63

168

GND

171

GND

172

GND

177

GND

178

GND

183

GND

184

GND

187

GND

190

GND

193

GND

196

GND

GND

GND

GND

GND

GND

155

156

161

162

165

5

D0

MD_0

MD_1

MD_2MAA5

MD_3

MD_4

MD_5

MD_6

MD_7

MD_8

MD_9

MD_10

MD_11

MD_12

MD_13

MD_14

MD_15

MD_16

MD_17

MD_18

MD_19

MD_20

MD_21

MD_22

MD_23

MD_24

MD_25

MD_26

MD_27

MD_28

MD_29

MD_30

MD_31

MD_32

MD_33

MD_34

MD_36

MD_37

MD_38

MD_39

MD_40

MD_41

MD_42

MD_43

MD_44

MD_45

MD_46

MD_47

MD_48

MD_49

MD_50

MD_51

MD_52

MD_53

MD_54

MD_55

MD_56

MD_57

MD_58

MD_59

MD_60

MD_61

MD_62

MD_63

DDR SODIMM AAA-DDR-016-001

MD_[0:63] 5,9

+1.8 V

C257 0.1u /16V_04

C241 0.1u /16V_04

C242 0.1u /16V_04

C254 0.1u /16V_04

C244 0.1u /16V_04

C245 0.1u /16V_04

C243 0.1u /16V_04

C255 0.1u /16V_04

C276 0.1u /16V_04

C274 0.1u /16V_04

C280 0.1u /16V_04

C284 0.1u /16V_04

C275 0.1u /16V_04

C258 0.1u /16V_04

C256 0.1u /16V_04MD_35

C281 0.1u /16V_04

C283 0.1u /16V_04

C279 1000p/ 50V_04

C299 0.1u /16V_04

C240 0.1u /16V_04

C259 0.1u /16V_04

C282 0.1u /16V_04

C286 10u/ 10V_08

C260 10u/ 10V_08

C253 10u/ 10V_08

C277 10u/ 10V_08

C197 150u/ 4V_B

+

C212 150u/ 4V_B

+

C287 150u/ 4V_B

+

B.Schematic Diagrams

Sheet 8 of 39

DDR2-1

DDR2-1 B - 9

Page 10

Schematic Diagrams

DDR2-2

Sheet 9 of 39

DDR2-2

B.Schematic Diagrams

M_CLK_DDR2

C560

*2.7p/50V_04

*2.7p/50V_04

+1. 8V

R164

75_1%_06

R159

75_1%_06

M_CLK_DDR#2

M_CLK_DDR3

C293

M_CLK_DDR#3

Close d to SODI M M

2.2UU_6.3V_06

M_DM[0..7]

M_D QS+05, 8

M_D QS-05,8

M_D QS+15, 8

M_D QS-15,8

M_D QS+25, 8

M_D QS-25,8

M_D QS+35, 8

M_D QS-35,8

M_D QS+45, 8

M_D QS-45,8

M_D QS+55, 8

M_D QS-55,8

M_D QS+65, 8

M_D QS-65,8

M_D QS+75, 8

M_D QS-75,8

+3VS

C285

.1U_10V_06

M_DM[0..7]5,8

Layout Note:Place these Caps near So- Dimm0

DDRVREF GE N. & DECOUPLING

Trace Width 12 Mil

Space 20 Mil

C270

.1U_10V_06

C269

2.2U_6.3V_06

SDREFC

C266

2.2U_ 6.3V _06

+1. 8V

818795828896103

111

117

104

112

118

5069838486

MAA[0 :1 3]5,8

M_BA05, 8

M_BA15, 8

M_BA25, 8

M_CS 2#5

M_CS 3#5

M_D M05,8

M_D M15,8

M_D M25,8

M_D M35,8

M_D M45,8

M_D M55,8

M_D M65,8

M_D M75,8

M_WE #5,8

M_CAS#5, 8

M_RAS#5, 8

M_CKE25

M_CKE35

M_CLK_DDR210

M_CLK_DDR#210

M_CLK_DDR310

M_CLK_DDR#310

SMB_SBDATA8,10,14,16,25

SMB_SBCLK8,10,14,16,25

R178 10K_04

+3V

R179 10K_04

Bruce 5/08

C265

M_OD T25

M_OD T35

MAA0

MAA1

MAA2

MAA3

MAA4

MAA5

MAA6

MAA7

MAA8

MAA9

MAA10

MAA1 1

MAA1 2

MAA1 3

M_D M0

M_D M1

M_D M2

M_D M3

M_D M4

M_D M5

M_D M6

M_D M7

M_DQS +0

M_DQS -0

M_DQS +1

M_DQS -1

M_DQS +2

M_DQS -2

M_DQS +3

M_DQS -3

M_DQS +4

M_DQS -4

M_DQS +5

M_DQS -5

M_DQS +6

M_DQS -6

M_DQS +7

M_DQS -7

SDREFC

Z0901

Z0902

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

107

BA0

106

BA1

85

BA2

110

CS0

115

CS1

10

DQM0

26

DQM1

52

DQM2

67

DQM3

130

DQM4

147

DQM5

170

DQM6

185

DQM7

109

WE

113

CAS

108

RAS

79

CKE0

80

CKE1

30

CK0

32

CK0

164

CK1

166

CK1

13

DQS0

11

DQS0

31

DQS1

29

DQS1

51

DQS2

49

DQS2

70

DQS3

68