Appendix B: Schematic Diagrams

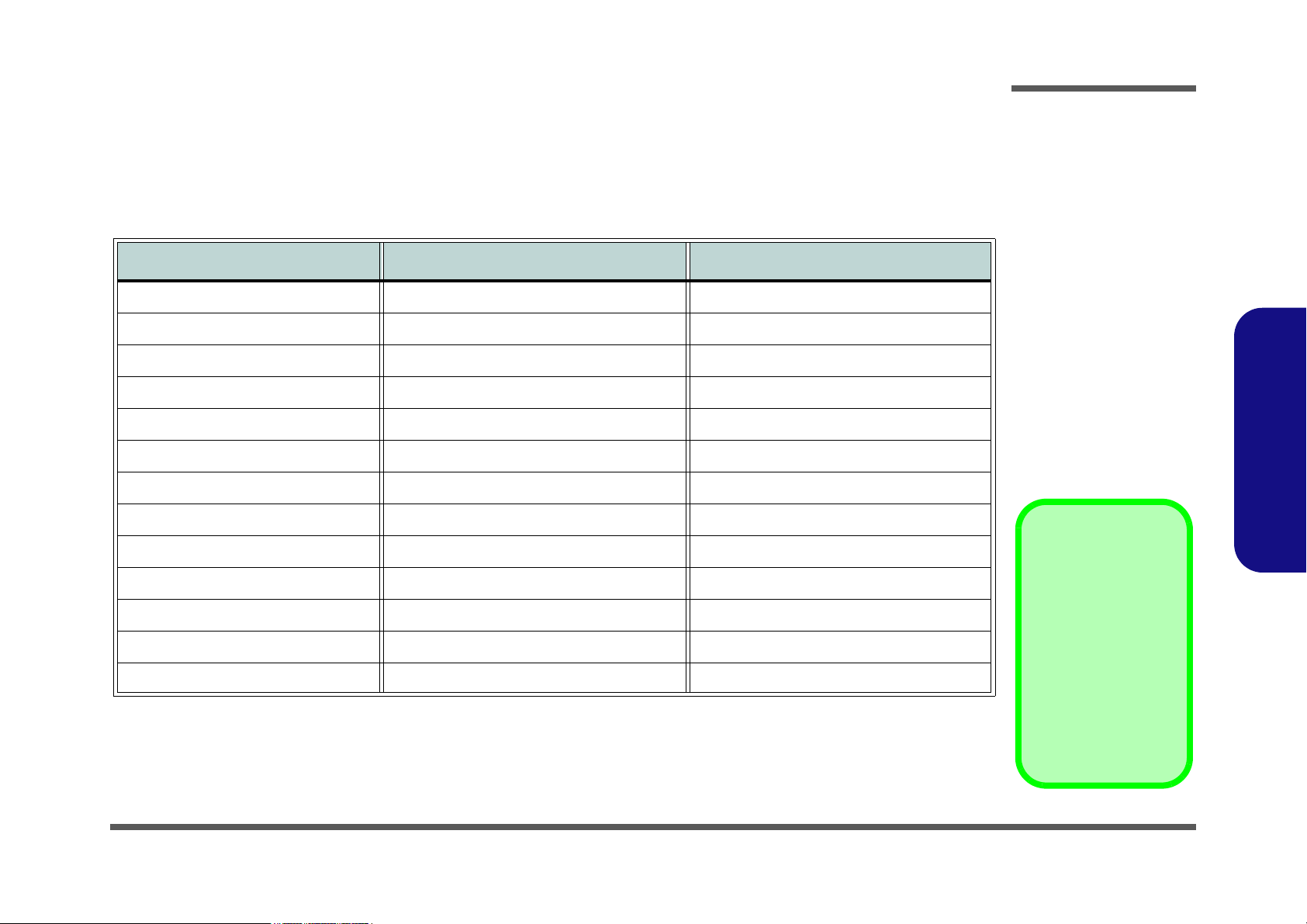

Table B - 1

Schematic

Diagrams

Version Note

The schematic diagrams in this chapter

are based upon version 6-7P-M5SS6-002.

If your mainboard (or

other boards) are a later version, please

check with the Service

Center for updated diagrams (if required).

This appendix has circuit diagrams of the M540SS/M548SS/M549SS notebook’s PCB’s. The following table indicates

where to find the appropriate schematic diagram.

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 968 PCIE LAN GPIO 2/4 - Page B - 15 System Power - Page B - 28

Processor 1/2 - Page B - 3 968 USB SATA 3/4 - Page B - 16 VCORE - Page B - 29

Processor 2/2 - Page B - 4 968 PWR GND 4/4 - Page B - 17 VDD3, VDD5 - Page B - 30

SiSM672 HOST PCIE 1/5 - Page B - 5 Clock Generator & Clock Buffer - Page B - 18 1.05VS, 1.2V, 1.5V - Page B - 31

SiSM672 DRAM 2/5 - Page B - 6 SiS307ELV - Page B - 19 1.8V, 0.9VS - Page B - 32

SiSM672 MuTITOL VGA 3/5 - Page B - 7 ODD, SATA, USB2.0 *2 - Page B - 20 D/D BD (CRT, S-Video, RJ-11) - Page B - 33

SiSM672 PWR 4/5 - Page B - 8 Card Reader JMB385 - Page B - 21 D/D BD (Charger, DC-In) - Page B - 34

SiSM672 GND 5/5 - Page B - 9 KBC-ITE IT8512E - Page B - 22 Audio BD (Phone Jack, RJ-11, USB) - Page B - 35

Schematic Diagrams

B.Schematic Diagrams

DDRII SO-DIMM - 2 - Page B - 10 Mini Card, New Card, TPM, FGPT - Page B - 23 Hot key BD (Hot key, LED) - Page B - 36

DDRII SO-DIMM - 1 - Page B - 11 AZALIA Codec ALC883 - Page B - 24 RJ-45 Board - Page B - 37

Panel, Fan - Page B - 12 Audio AMP2056A - Page B - 25 FingerPrint Board - Page B - 38

LAN PHY Realtek 8201CL - Page B - 13 MDC, BT, PWRGD, DDB CON - Page B - 26

968 PCI IDE MuTIOL SPI 1/4 - Page B - 14 TouchPad, LED - Page B - 27

B-1

Schematic Diagrams

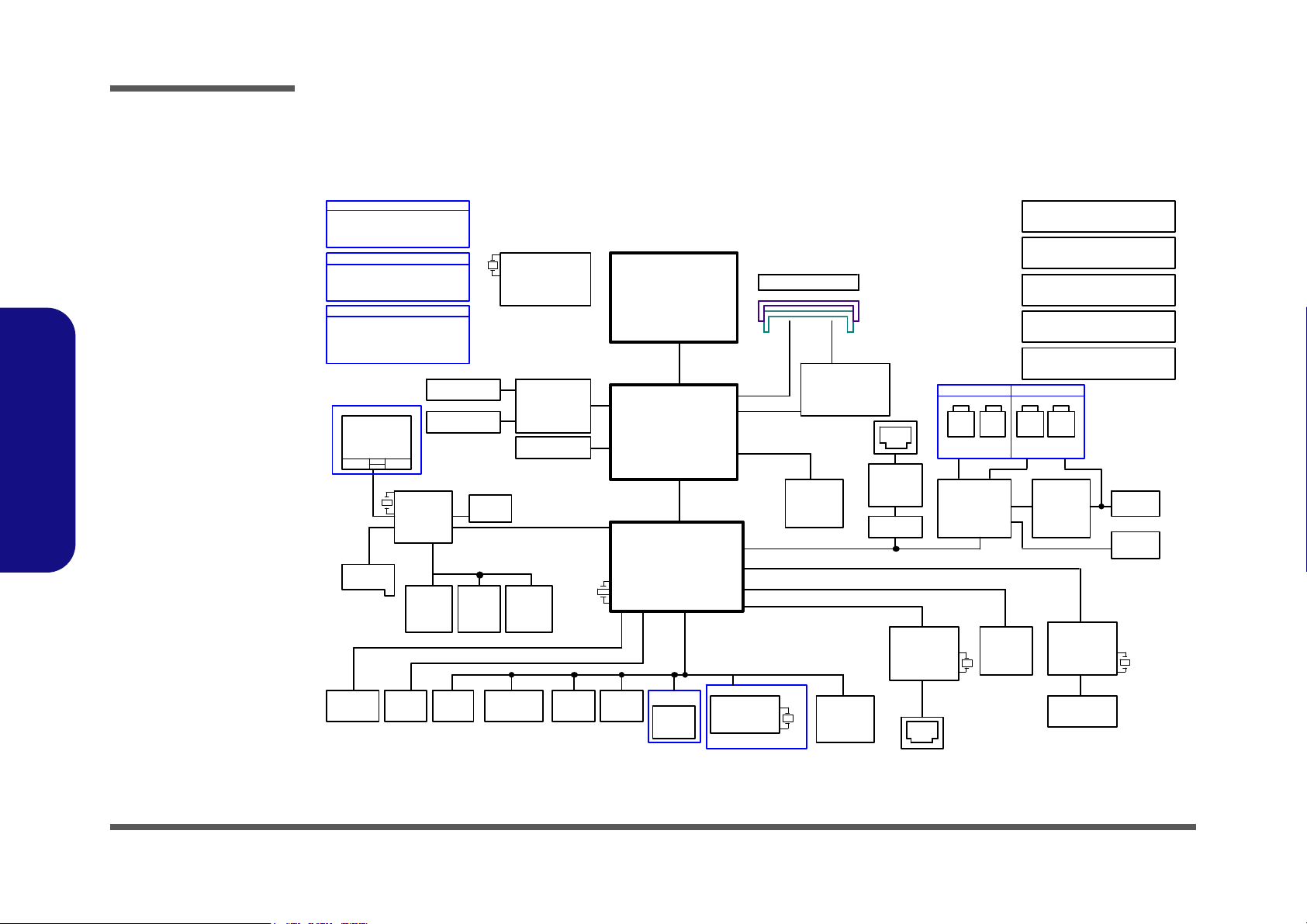

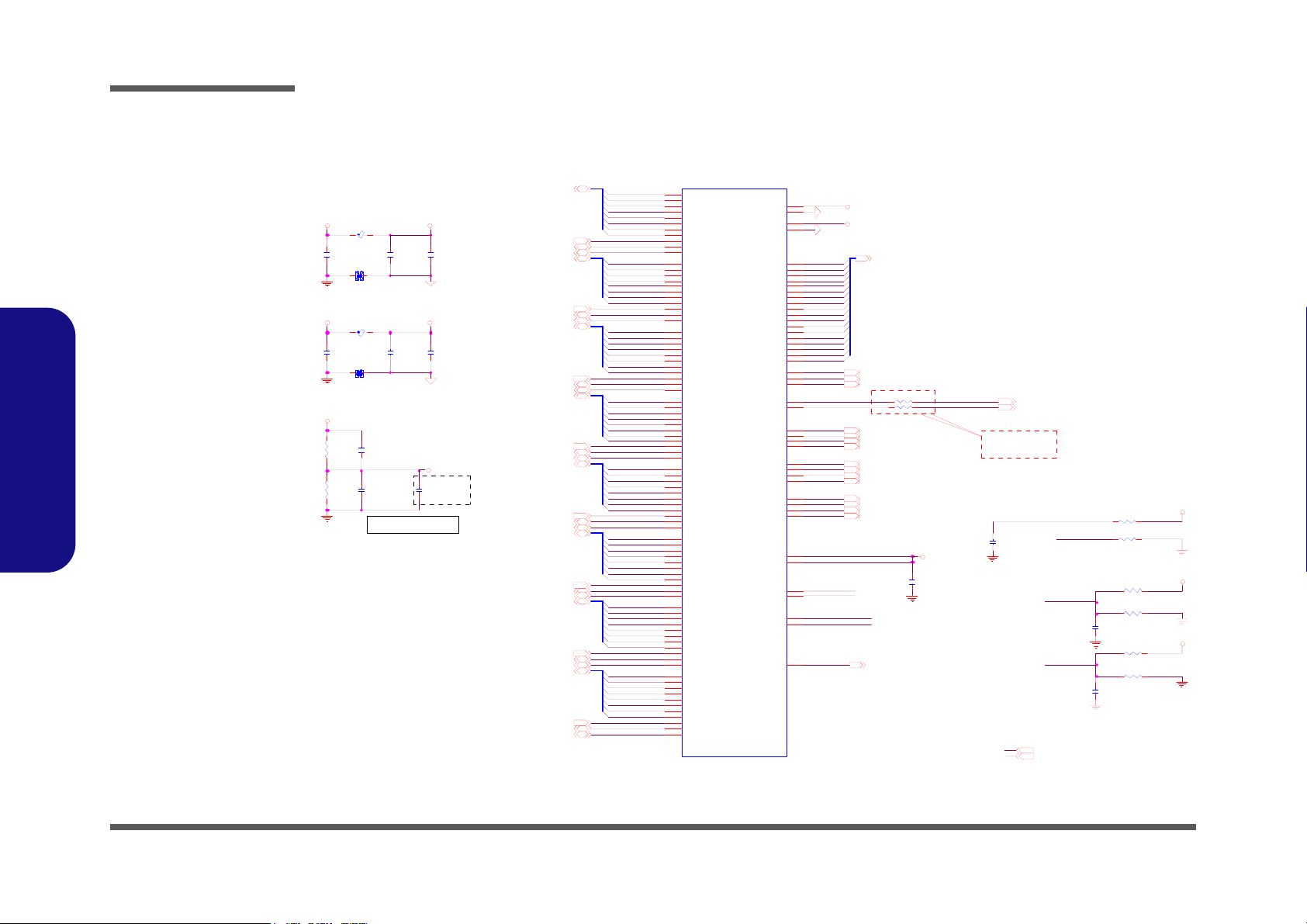

Sheet 1 of 37

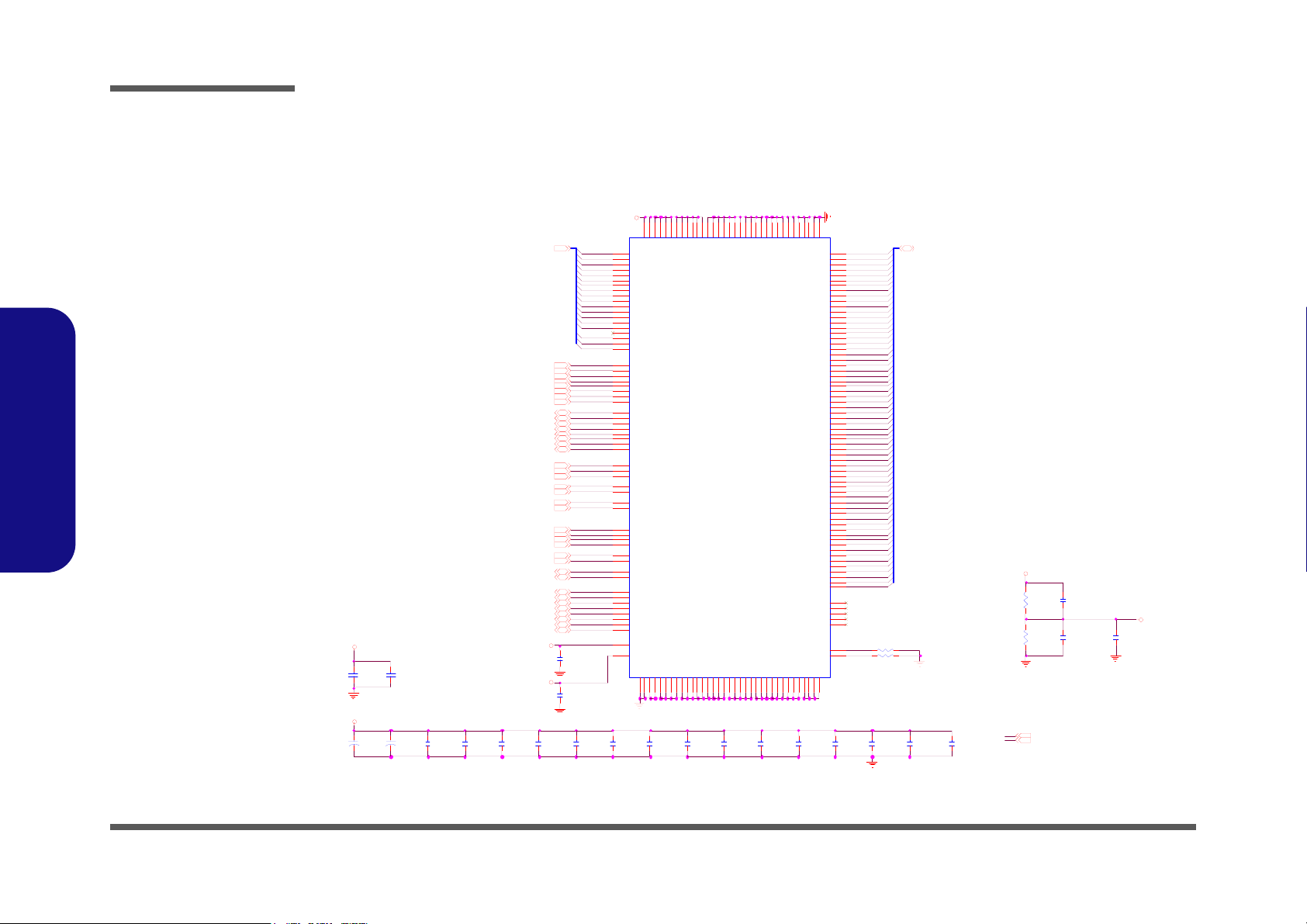

System Block

Diagram

SO-DIMM0

35*35*2.4mm

+VCORE

SATA I/II 3.0Gb/s

USB0

SPI

D/D BOARD

(USB2)

SiS968

1.8V,0.9VS

CARD READER

LID SWITCH

32.768 KHz

N ew Card

28pins SSOP

Realtek

ALC883

10/100M PHY

4IN1

IN T. K/B

14.318 MHz

570b alls mBGA

ITE 8512E

ICS9P935

24pins TSSOP

L CD CONN ECTO R

USB1

VDD3,VDD5,3.3V,5V

RTL8201CL

ANPAC

APA2056A

SOCKET

EC SMBUS

32.768KHz

13*13*1.7mm

EC

SMART

FAN

Clo ck Buff er

14*14*1.6m m

SPDIF

OUT

SYSTEM POWER,2 .5V

MDC CON

IVERTER

HOT KEY BOARD

SiS307ELV

33 MHz

TOUCH PAD

810602-1703

12 MHz

PCIE

(Optional)

35*35*2.7mm

(USB4)

PCIE

1.05VS,1.5V,1.2V

JMB385

FingerPrint

9.8*6.4*1.2mm

CCD

(USB5)

SOCKET

F75383M

AU DIO AMP

USB CONNECTOR

ODD

9*9*1.6mm

PATA-133

(USB2)

Synaptic

SOUTH BRIDGE

24 MHz

AUDIO Board

AZALIA LINK

FINGER PRINTER BOARD

INDICATOR LED,

LVDS (TV)

INT MIC

Mi ni PCIE

Colck Generator

SMART

BATTERY

Mini PCIE

Memory Termination

(USB4)

533/667 MHz

SO-DIMM1

17.1*8.1*1.2mm

100 MHz

USB & Phone

Jack B'd

(USB6)

NORTH BRIDGE

667/800 MHz

Bluetooth

CRT,RJ-11

480 Mbps

CHARGER,DC JACK,

25 MHz

CRT

MAIN Board

DDRII

POWER BOTTON,

47 9 pi ns s oc ke t P

48pins LQFP

INT SPK

GMAC

THERMAL

SENSOR

USB2.0

RD111 Design

ICS9LPR600

48pins LQFP

CLICK BOARD

CLEVO M540SS System Block Diagram

24.576

MHz

AUDIO BOARD

PROCESSOR

LINE

IN

17.1*8.1*1.2mm

852balls TEBGA

DDRII

Azalia Codec

RJ-45

9* 9 * 1. 7m m

PCIE

AZALIA

MDC

MODULE

27*27*2.5mm

SOCKET

SiSM672

RJ-11

LPC

169balls BGA

SATA HDD

SOCKET

AUDIO PHONE JACK,

Intel Merom

100 MHz

MIC

IN

FSB

56pins TSSOP

HP

OUT

USB3

MuTIOL 1G

128pins LQFP

System Block Diagram

B.Schematic Diagrams

B - 2

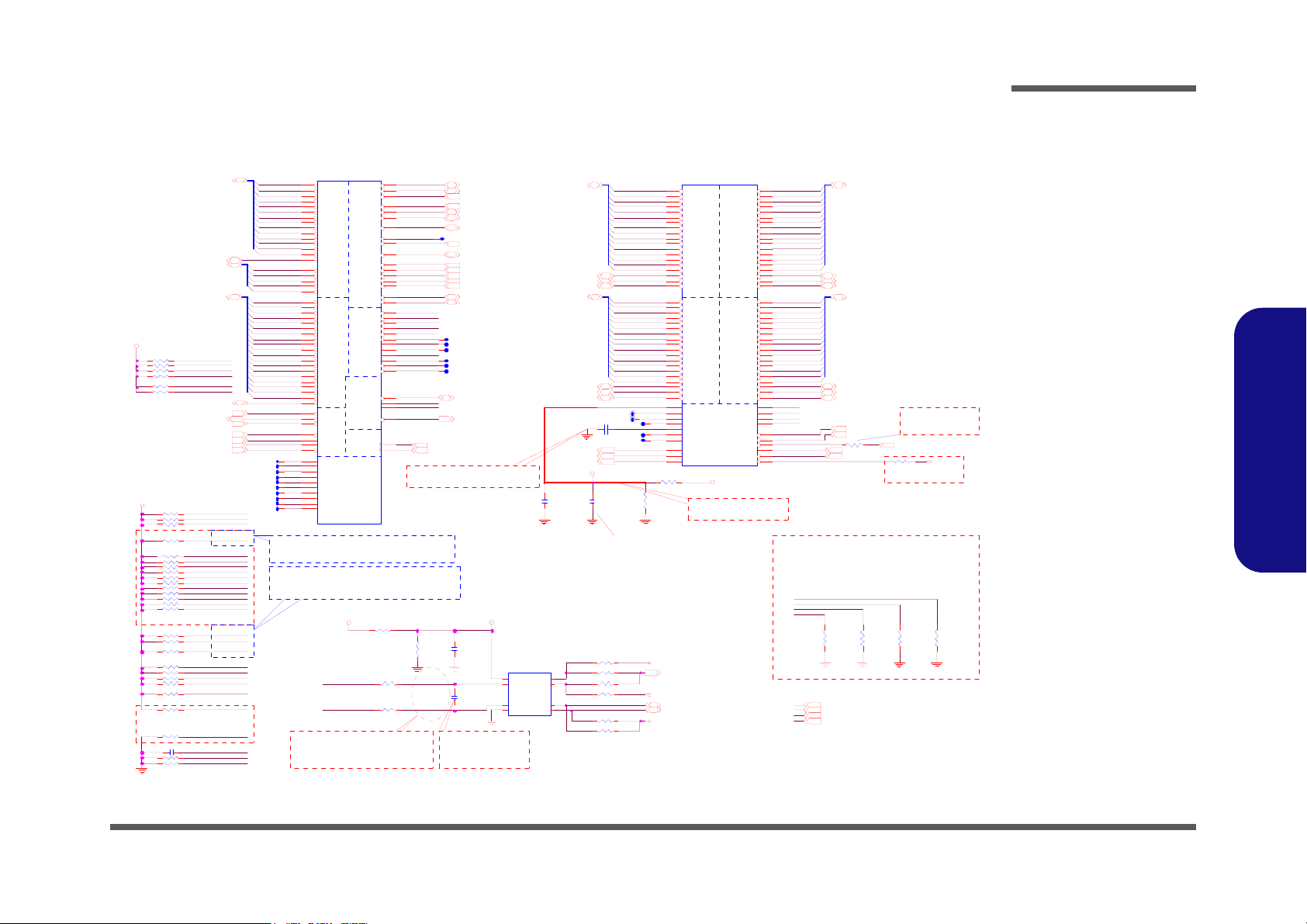

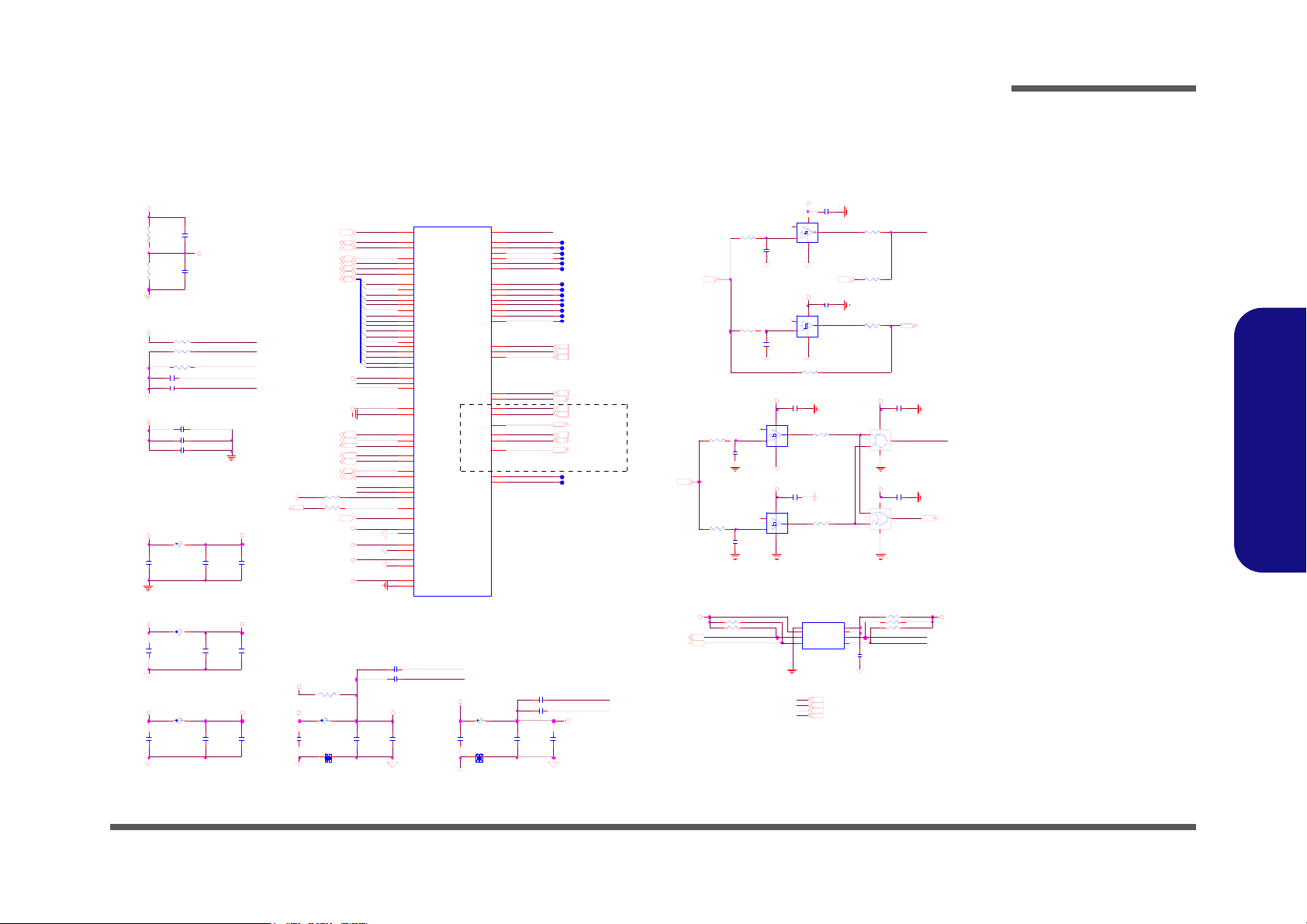

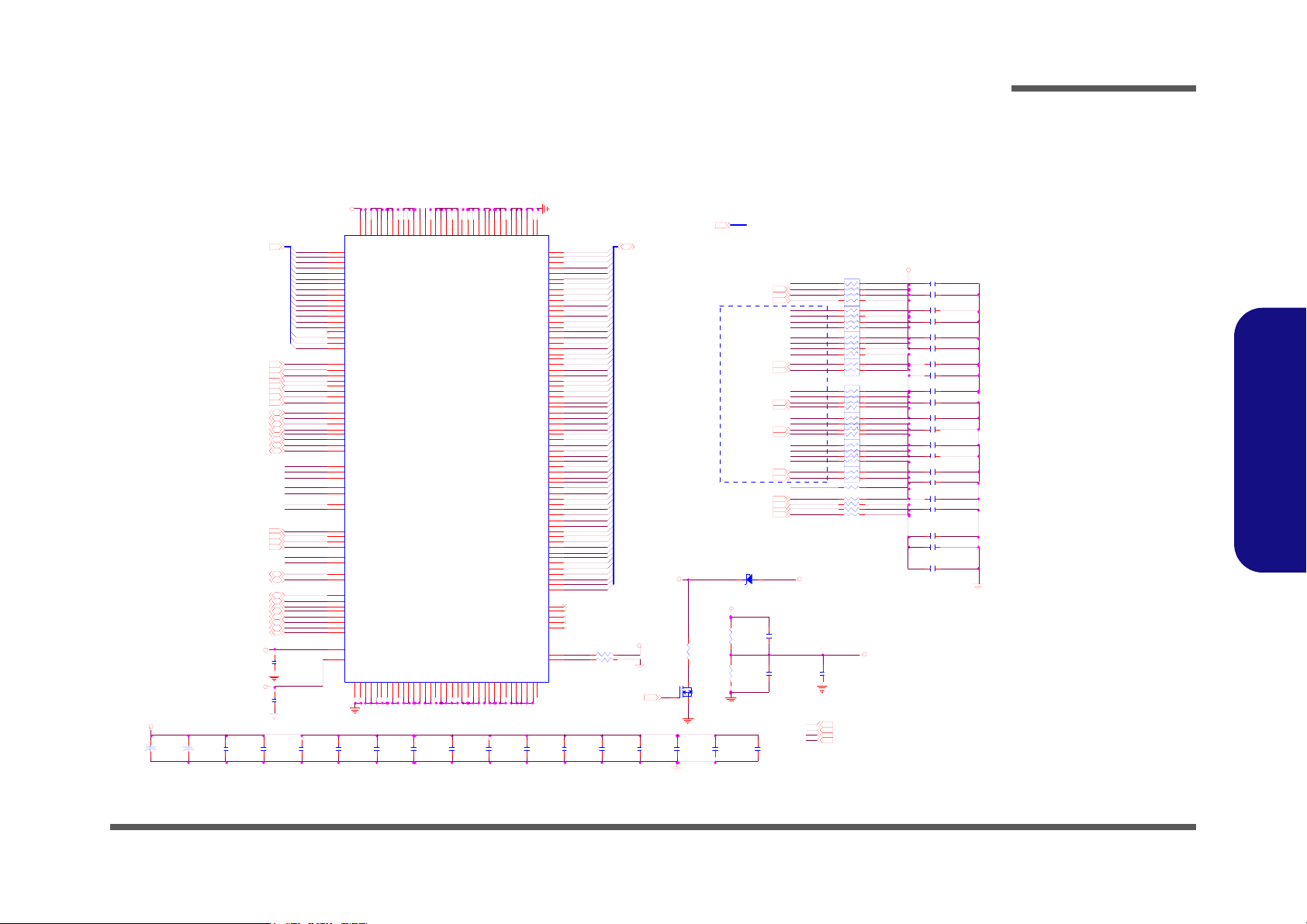

Processor 1/2

Sheet 2 of 37

Processor 1/2

H_BP RI# 4

VDD 3

H_N MI

H_D#22

H_TCK

H_ST P CLK#

H_A#4

H_THRMD

H_PWRGD 4

H_D # 42

CO M P1

H_A# 23

H_D # 57

H_A# 20

H_FERR#14

H_D#8

CO MP 2

H_R EQ #1

H_D#3

If PROCHOT# is routed between CPU, IMVP and MCH,

pull-up resistor has to be 68 ohm ? 5%. If not

use, pull-up resistor has to be 56 ohm ? 5%

C454

1000p_50V_04

R 217 1K_04

R224 4. 7K _04

H_D#10

CPU_BSEL1

R229 10K _04

H_R S# 2 4 H_D STBP#2 4

H_H IT # 4

H_BR 0 #

H_A# 33

R 202 56_04

H_DINV#14 H_D INV # 3 4

R222 0_06

H _BPM 3#

ADDR GROUP 0 ADDR GROUP 1

CONTROLXDP/ITP SIGNALS

H CLK

THERMAL

RESERVED

IC H

JSKT1 A

Mero m B all-ou t R ev 1 a

N3

P5

P2

L2

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

J4

U2

V4

M4

N5

T2

V3

B2

C3

D2

D22

L5

L4

K5

M3

N2

J1

A6

H1

M1

V1

D3

A22

A21

E2

AD4

AD3

AD1

AC4

G5

F1

C20

E1

H5

F21

A5

G6

E4

D20

C4

B3

C6

B4

H4

AC2

AC1

D21

K3

H2

K2

J3

L1

C1

F3

F4

G3

A3

D5

AC5

AA6

AB3

C7

A24

B25

AB5

G2

AB6

W3

AA4

AB2

AA3

F6

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[3]#

A[30]#

A[31]#

RS VD[ 01]

RS VD[ 02]

RS VD[ 03]

RS VD[ 04]

RS VD[ 05]

RS VD[ 06]

RS VD[ 07]

RS VD[ 08]

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A20M#

AD S#

AD STB[0]#

AD STB[1]#

RS VD[ 09]

BC LK[0]

BC LK[1]

BNR #

BPM [0]#

BPM [1]#

BPM [2]#

BPM [3]#

BPR I#

BR0#

DBR #

D BSY #

DEFER#

DR DY #

FER R#

HIT#

HI TM #

IERR#

IGNNE#

IN IT#

LINT0

LINT1

LOCK#

PR DY #

PREQ#

PROCHOT#

RE Q[0]#

RE Q[1]#

RE Q[2]#

RE Q[3]#

RE Q[4]#

RE SET #

RS[0]#

RS[1]#

RS[2]#

SM I#

STPC LK#

TC K

TD I

TDO

TH ER MTR IP#

TH ERMD A

THERM DC

TMS

TR DY #

TR ST#

A[32]#

A[33]#

A[34]#

A[35]#

RS VD[ 10]

H_D#19

H_D#24

H_A#5

R228 0_04

H _A20M#14

1.05VS

H_DPRSTP# 6,28

H_D#25

Z0226

R 53 150_1%_04

CPU_GTLREF

H_DINV#04

H_D#15

C453

10U_10V_08

CPU_GRFE=0.7V

H_CPURST# 4

H_D INV # 2 4

H_PR EQ #

U12

ASC 7525

1

2

3

4

5

6

7

8

VDD

D+

D-

THERM

GN D

ALER T

SDA TA

SC LK

CO M P2

Close to Thermal IC

H_REQ#[4:0]4

H_D#31

H_DB R#

H_A# 28

H_A# 31

Z 0208

R 219 1K_04

H_NMI14

H_D # 52

Z 0207

Z0225

IF USED Desktop CPU, H_CPURST#,H_PWRGD,H_BRD,need

a dd pul l hig h r es ist or

H_D PW R# 4

H_IN T R

H_D#30

H_D#23

H_D#4

H_D#21

Z 0203

H_IGNNE#

R78

27. 4_1%_04

H_A#8

H_A# 26

R225

*100K_04

CPU_BSEL2

H_A# 24

H_A#14

CO MP 3

Layout Note:

VDD 3

CPU_BSEL217

H_IG N NE#

H_IN IT # 14

H_DPWR #_R

H_TMS

R 20 51.1_1%_04

T22

H_A#[35:3]4

H_D#16

H_D#28

H_NMI

H_A# 32

H_ST P CLK#14

H_CPURST#

R 231 *0_04

1. 05 V S

CPU_BSEL0

H_A#6

Z0213

H_D # 58

H_A#13

H_D#18

CO MP 0

CP U_B S EL2

H_D ST BN #3 4

H_D # 32

H_T MS

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms(20mil)

COMP1, COMP3: 0.5" Max, Zo=55 Ohms(5mil)

Best estimate is 18 mils wide trace for outer

layers and 14 mils wide trace if on internal

layers.

H_SMI#14

H_DPWR #_R

H_CP URST#

V DD3 11,15,21,25,26,27, 29,31

H_D # 38

Z 0201

H_R EQ #4

H_A#12

H_A#10

H_D#5

R 206 56_04

H_D # 62

H_BR0#

PS I#

H_D # 50

H_D PSLP#

H_D#17

H_BPM2#

H_F ERR#

H _BPM 0#

H_D STBP#3 4

H_F E RR #

Thermal IC

ASC7525: 6-02-07525-LD0

H_THRMTRIP# 14

H_D#[63:0] 4

H_A# 17

R 34 51.1_1%_04

H_D BSY # 4

H_A#16

3.3VS

H_BNR# 4

Z 0209

H_IE RR #

H_A# 35

H_TDO

H _A#[35:3]4

CO M P3

H_D # 41

H_SMI#

H_D#20

H_D # 47

H_PW RG D

C105 *0.1u_X7R_04

H_CLK_CPU# 17

H_D#27

H_A#9

R 210 56_04

H_D # 46

H_R EQ #2

H_A# 21

H_DPWR#_R

Layout Note:

CPU_BSEL017

H _D#[63:0]4

H_PWRGD

R 19 27.4_1%_04

H_D # 40

Z 0205

Layout note:

H_D EF E R# 4

H_BR 0 # 4

H_D#12

H_D # 45

C104

1U _6.3V_04

TH ERM_ ALER T# 2 1

H_CPUSLP#

R 36 680_04

H_T C K

H_D # 56

H_TRS T#

R 54 39.2_1%_04

R 35 51.1_1%_04

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil spacing.

3. 3V

Z0212

R 199 56_04

R 29 51.1_1%_04

Layout Note:

H _DP SLP#

R 33 56.2_1%_04

H_D # 34

Z 0202

H_INTR

R 208 56_04

H_T R DY # 4

CP U_B S EL1

R221 *10K_04

DATA GRP 0 DATA GRP 1

DATA GRP 2DATA GRP 3

MISC

JSKT1B

Merom Ball- out Rev 1a

R26

U26

AA1

Y1

E22

F24

J24

J23

H22

F26

K22

H23

N22

K25

P26

R23

E26

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

G22

T25

N25

Y22

AB24

V24

V26

V23

T22

U25

U23

F23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

AE24

AD24

G25

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

E25

AC22

AD23

AF22

AC23

E23

K24

G24

AF 1

H25

N24

U22

AC20

E5

B5

D24

J26

L26

Y26

AE25

H26

M26

AA26

AF24

AD 26

AE6

D6

D7

C24

B22

B23

C21

D25

AF26

A26

C23

CO MP [0]

CO MP [1]

CO MP [2]

CO MP [3]

D[0]#

D[1]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

D[16]#

D[17]#

D[18]#

D[19]#

D[2]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[3]#

D[30]#

D[31]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[4]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

D[48]#

D[49]#

D[5]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[6]#

D[60]#

D[61]#

D[62]#

D[63]#

D[7]#

D[8]#

D[9]#

TEST5

D INV [0 ]#

D INV [1 ]#

DINV[2]#

DINV[3]#

DPRSTP#

DP SLP#

DPWR#

DSTBN[0]#

DSTBN[1]#

DSTBN[2]#

DSTBN[3]#

DSTBP[0]#

DSTBP[1]#

DSTB P [2]#

DSTB P [3]#

GTLREF

PSI#

PW RGOOD

SLP#

TEST3

BS EL[0]

BS EL[1]

BS EL[2]

TEST2

TEST4

TEST6

TEST1

H_D # 36

H_T H RMT RI P#

H_A# 22

R77

54.9_1%_04

V_THER M

H_A# 30

R 232 10_1% _04

R 203 56_04

1.05VS

H_DSTBP#04

3.3V 12,14,15,16,22,25,26,27,29,30,31

H_A#3

R 211 56_04

( SiS R eco mma nd ati on 20 0p)

H_R S# 1 4

H_PW RG D

H_PRDY#

R 215 75_1% _04

R 52 680_04

C107

0.01u_16V_X7R _04

H_D#0

H_D # 49

H_D # 39

H_T H ER MD C

R 201 56_04

H_D#7

Z 0206

H_TH RMTRI P#

H_A# 25

H_THERMDC

R223 4. 7K _04

H_T D I

H_D # 54

H_D # 51

H_PRDY#

If used M672

than del R3

H_DRDY# 4

H_H IT M# 4

H_IGNNE#14

R 218 1K_04

R 17 51.1_1%_04

56_04

SMC_CPU_THERM 21

H_TDO

H_DPSLP# 6

H_D # 37

H _BPM 2#

H_PR O CH O T# 14

C1 Close to TEST4 (Pin AF26)

H_PREQ#

C 449 *.1U _16V_04

R 205 56_04

H_T R ST#

H_D # 61

H_A#7

If used M672 than

de l R40 an d add R4 2

R220 *0_04

R 204 56_04

H_INTR14

H_R EQ #3

H_THRMC

6-14-5603B-11B

H_D # 59

H_INIT#

H_A2 0M #

Z0211

H_LOCK# 4

H_D#2

H_IERR#

R30

54.9_1%_04

1.05VS 3,4,6,7,16,30

H_AD S# 4

H_D # 55

H_STPCLK#

CO M P0

CP U_B S EL0

H_A#15

R81

2K_1%_04

H_SM I#

H_D#14

H_D # 63

H_IN IT #

H_A# 19

H_A# 34

R 213 * 330_04

H_R EQ #0

H_A# 27

R 207 56_04

R31

27.4_1%_04

3.3VS 6,10,11,13,14,15,16, 17,18,19,20,21,22,23,24,25,26,27,28

H_D # 48

H_A# 18

R 200 * 51_04

R 32 54.9_1%_04

H_DSTBP#14

H_D#11

V_TH ER M

0.5" max, Zo= 55 Ohms

CO MP 1

H_D # 44

H_D#1

H_D # 60

H_D # 35

H_TDI

H_THERMDA

H_D#29

H_BPM3#

H_BPM1#

H_CPUSLP#

H_R S# 0 4

H_CP USLP# 14

H_D#9

T20

H_DS TBN#14

H_D#[63:0] 4

H_DS TBN#04 H_D ST BN #2 4

H_D#26

Z 0204

H_A#11

H_D # 53

H _BPM 1#

R 214 54.9_1%_04

Layout Note:

H_BPM0#

R80 1K_1% _04

R 18 56_04

H_DBR#

H_D#13

ADM1032 1000p

F75383M 2200p

R 227 0_04

CPU to SB interface

H_CLK_CPU 17

H_T H ER MD A

R 230 * 56_04

SMD_CPU_THERM 21

H_ADSTB #04

H_PR O CH O T#

R 226 0_04

H _D#[63:0]4

H_D # 43

H_D#6

H_P R OC H O T#

Z 0210

R 216 56_04

CPU_BSEL117

H_AD STB#14

H_D # 33

H_A# 29

H_A20M#

Schematic Diagrams

B.Schematic Diagrams

Processor 1/2 B - 3

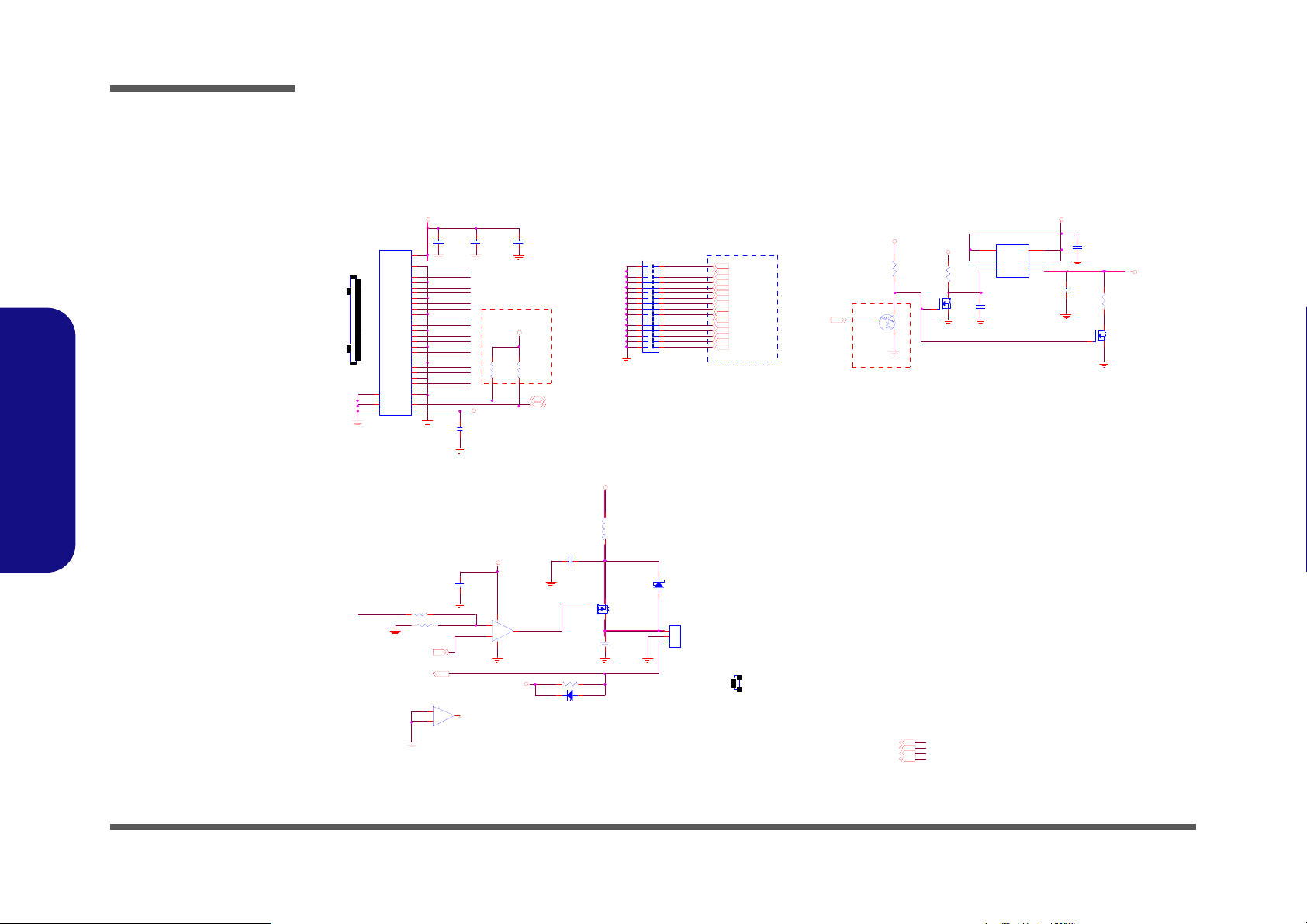

Schematic Diagrams

VS SSE NSE 28

H_V ID 4 28

VCORE 28

VCC SEN SE 2 8

C73

22U_6.3V_08

1. 05VS

Power Plane

JSKT1D

Merom Ball-out Rev 1a

.

P6

AE 11

A8

A11

A14

A16

A19

A23

AF2

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3 A25

AF 2 1

AF 1 9

AF 1 6

AF 1 3

AF 1 1

AF 8

AF 6

A2

AE 26

AE 23

AE 19

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y21

Y24

AA 2

AA 5

AA 8

AA 11

AA 14

AA 16

AA 19

AA 22

AA 25

AB 1

AB 4

AB 8

AB 11

AB 13

AB 16

AB 19

AB 23

AB 26

AC3

AC6

AC8

AC1 1

AC1 4

AC1 6

AC1 9

AC2 1

AC2 4

AD2

AD5

AD8

AD1 1

AD1 3

AD1 6

AD1 9

AD2 2

AD2 5

AE 1

AE 4

Y6

A4

AE 14

AE 16

AE 8

AF 2 5

VSS[082]

VSS[148]

VS S[ 0 0 2]

VS S[ 0 0 3]

VS S[ 0 0 4]

VS S[ 0 0 5]

VS S[ 0 0 6]

VS S[ 0 0 7]

VS S[ 0 0 8]

VS S[ 0 0 9]

VS S[ 0 1 0]

VS S[ 0 1 1]

VS S[ 0 1 2]

VS S[ 0 1 3]

VS S[ 0 1 4]

VS S[ 0 1 5]

VS S[ 0 1 6]

VS S[ 0 1 7]

VS S[ 0 1 8]

VS S[ 0 1 9]

VS S[ 0 2 0]

VS S[ 0 2 1]

VS S[ 0 2 2]

VS S[ 0 2 3]

VS S[ 0 2 4]

VS S[ 0 2 5]

VS S[ 0 2 6]

VS S[ 0 2 7]

VS S[ 0 2 8]

VS S[ 0 2 9]

VS S[ 0 3 0]

VS S[ 0 3 1]

VS S[ 0 3 2]

VS S[ 0 3 3]

VS S[ 0 3 4]

VS S[ 0 3 5]

VS S[ 0 3 6]

VS S[ 0 3 7]

VS S[ 0 3 8]

VS S[ 0 3 9]

VS S[ 0 4 0]

VS S[ 0 4 1]

VS S[ 0 4 2]

VS S[ 0 4 3]

VS S[ 0 4 4]

VS S[ 0 4 5]

VS S[ 0 4 6]

VS S[ 0 4 7]

VS S[ 0 4 8]

VS S[ 0 4 9]

VS S[ 0 5 0]

VS S[ 0 5 1]

VS S[ 0 5 2]

VS S[ 0 5 3]

VS S[ 0 5 4]

VS S[ 0 5 5]

VS S[ 0 5 6]

VS S[ 0 5 7]

VS S[ 0 5 8]

VS S[ 0 5 9]

VS S[ 0 6 0]

VS S[ 0 6 1]

VS S[ 0 6 2]

VS S[ 0 6 3]

VS S[ 0 6 4]

VS S[ 0 6 5]

VS S[ 0 6 6]

VS S[ 0 6 7]

VS S[ 0 6 8]

VS S[ 0 6 9]

VS S[ 0 7 0]

VS S[ 0 7 1]

VS S[ 0 7 2]

VS S[ 0 7 3]

VS S[ 0 7 4]

VS S[ 0 7 5]

VS S[ 0 7 6]

VS S[ 0 7 7]

VS S[ 0 7 8]

VS S[ 0 7 9]

VS S[ 0 8 0]

VS S[ 0 8 1] VS S[ 16 2]

VSS[161]

VSS[160]

VSS[159]

VSS[158]

VSS[157]

VSS[156]

VSS[155]

VSS[154]

VSS[153]

VSS[152]

VSS[151]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[106]

VS S[ 0 0 1]

VSS[149]

VSS[150]

VSS[147]

VSS[163]

R212

0_04

H_V ID 4

C55

10U_6.3V_08

L39

HCB2012KF-500T40

C75

10U_6.3V_08

C79

0.01u_16V_X7R_04

C52

10U_6.3V_08

C4 6 & C73 8 Co -lay ou t

VCORE

H_V ID 1

H_V ID 3

C32

10U_6.3V_08

C84

0. 1u_10V_X7R_04

C58

1U_6.3V_04

1.05VS 2,4, 6, 7,16,30

VCCA20

+

C63

*150U_4V_B2

H_V ID 2 28

H_V ID 2

C24

0.1u_10V_X7R_04

C45

1U_6.3V_04

C37

10U_6.3V_08

1.05VS

VCO RE

VCO RE

C83

0.1u_10V_X7R_04

Ro ute VCC SENS E and

VSSSENSE traces at 27.4

ohms with 15.5mils width

10mils spacing.

Pl ace PU and PD withi n 1

inch of CPU.

C50

10U_6.3V_08

C29

1U_6.3V_04

C80

0. 1u_10V_X7R_04

PLACE NEAR CPU

H_V ID 0

1.5VS

H_V ID 1 28

C81

0.1u_10V_X7R_04

VCORE

C30

0.1u_10V_X7R_04

H_V ID 5

C452

10U_6.3V_08

Ne ar pin B26

H_V ID 0 28

JSKT1C

Merom Ball-out Rev 1a

.

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

AB20

AB7

AC7

AC9

AC1 2

AC1 3

AC1 5

AC1 7

AC1 8

AD7

AD9

AD1 0

AD1 2

AD1 4

AD1 5

AD1 7

AD1 8

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

B26

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

AF7

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AE7

C26

G21

V6

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCA[01]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCSENSE

VID [ 0 ]

VID [ 1 ]

VID [ 2 ]

VID [ 3 ]

VID [ 4 ]

VID [ 5 ]

VID [ 6 ]

VS SSE NSE

VCCA[02]

VCCP[01]

VCCP[02]

C74

10U_6.3V_08

C36

10U_6. 3V_08

Layout note:

H_V ID 6

C65

1U_6.3V_04

C27

0. 1u_10V_X7R_04

C57

0.1u_10V_X7R_04

PLACE NEAR CPU

C26

0. 1u_10V_X7R_04

V SSS EN SE

C35

*10U_6.3V _08

C28

1U_6. 3V_04

6-0 7-10611- 7C0

C56

1U_6.3V_04

C72

10U_6.3V_08

C82

0.1u_10V_X7R_04

VCO RE

C450

10U_6.3V_08

Check cap for santa rosa platform

C456

10U_6.3V_08

C69

1U_6.3V_04

VCO RE

C42

1U_6. 3V_04

Layout note:

VCORE

13 0mA

C23

0.1u_10V_X7R_04

C25

0.1u_10V_X7R_04

C54

10U_6.3V_08

C48

0.01u_16V_X7R_04

H_V ID 3 28

C70

10U_6.3V_08

C34

10U_6. 3V_08

C44

1U_6.3V_04

C78

0. 1u_10V_X7R_04

H_V ID 5 28

C43

0.01u_16V_X7R_04

C64

22U_6.3V_12

C71

10U_6. 3V_08

R209

0_04

C76

1U_6.3V_04

C458

0.01u_16V_X7R_04

C31

0. 1u_10V_X7R_04

C77

1U_6.3V_04

VCO RE

C33

10U_6.3V_08

VCO RE

H_V ID 6 28

VCC SE NSE

C51

10U_6.3V_08

C451

10U_6.3V_08

2A

1.5VS 6,22, 27

1. 05VS

C41

1U_6.3V_04

C40

*10U_6.3V _08

Sheet 3 of 37

Processor 2/2

Processor 2/2

B.Schematic Diagrams

B - 4 Processor 2/2

SiSM672 HOST PCIE 1/5

1.05VS

H_D#14

H_D#61

H_A#4

PCI E_W AKE#15,22

Host

U13C

SiSM672

R34

E21

P32

B16

C17

A17

B18

F18

G18

P31

N30

P33

L32

P30

P28

F21

K34

M31

K33

M33

M32

L34

N32

N34

M34

T34

R30

R29

R32

P34

U34

AA34

N29

M30

M28

L30

L29

K28

K31

K30

H31

G34

H32

G32

K32

F34

F33

F32

H28

J30

H30

G29

J29

G30

F30

D33

D34

B32

B33

C34

D31

A32

A31

C31

B30

C30

A30

D28

G28

C29

C28

E28

E27

C27

G26

E26

D26

B26

A26

C26

G22

C24

A25

B24

C25

A24

E23

E25

G24

D22

C22

E22

C23

A23

A22

B22

T32

T28

T31

T33

T30

U32

U30

V34

U29

V33

V32

V28

V31

W34

Y33

W32

V30

W30

Y34

Y28

W29

Y32

Y30

Y31

AA32

AA30

AA29

AB33

AB34

AB32

AC3 4

AB30

AB31

J32

E32

F27

F23

H33

E31

B28

D24

H34

D32

A28

E24

A21

C21

W24

U24

R24

N24

L21

PCREQ#

NC2 (DPWR#)

EDRDY#

C1 XA VD D

C1 XA VSS

C4 XA VD D

C4 XA VSS

CPUCLK

CPUCLK #

HTRDY #

BPRI#

BREQ0 #

HLOCK#

DEFER#

CPUPWRGD

CPURST#

RS0#

RS1#

RS2#

DRDY#

BNR#

DBSY #

HIT#

HITM#

ADS#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HASTB 0#

HASTB 1#

HD0#

HD1#

HD2#

HD3#

HD4#

HD5#

HD6#

HD7#

HD8#

HD9#

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

H

D21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HA34#

HA35#

DBI0#

DBI1#

DBI2#

DBI3#

HDSTBN0#

HDSTBN1#

HDSTBN2#

HDSTBN3#

HDSTBP0#

HDSTBP1#

HDSTBP2#

HDSTBP3#

HPCO MP

HNCOMP

HVREF

HVREF

HVREF

HVREF

HVREF

C158

0.1u_10V_X7 R_ 04

H_D#45

Z0409

C153 0.1u_10V_X7R_04

C4 XA VS S

1.05VS

H_D BSY #2

H_D#27

H_D#34

H_D#58

H_A#13

Z0442

H_DSTBN#0 2

1.8VS 5,6,7,13,14, 15,16, 17,18, 27

H_DINV# 3 2

H_BR0#2

H_A#29

Z0445

Z0449

H_D#53

HDVBP0 18

H_D#40

C4 XA VSS

Z0416

C208

0.01u_16V_X7R _ 04

Z0401

Z0412

Z0423

H_D#8

C147 0.1u_10V_X7R_04

H_CPURST#2

H_A#24

H_TRDY#2

H_DSTBN#1 2

HDVAP1 18

H_D#3

Z0444

Z0430

PCIE

U13D

SiSM 6 72

E4

E5

F1

G1

H3

H2

H1

J1

V1

V6

W4

W1

W2

Y1

Y6

AA4

AA1

AB1 AB6

AC4

AB2

AC1

AD1

AD6

AE4

AE1

AE2

AF1

AG1

T2

U1

K1

K2

L1

M1

N1

N2

P1

R1

T1

J6

G6

G4

J4

L6

M4

P6

P4

H6

G5

K6

J5

M6

M5

R6

P5

W6

W5

AA6

AA5

AC6

AC5

AE6

AE5

P7

R7

T7

U7

V7

D7

G16

T5

T4

PERP0

PERN0

PERP1

PERN1

PERP2

PERN2

PERP3

PERN3

PERN9

PETP8

PET P 9 (HDVBP2)

PERP1 0

PERN10

PERP1 1

PET P1 0( HDVBP1)

PET P1 1( HDVBP0)

PERN11

PERP12 PETP12

PET P1 3( HDVAP2)

PERN12

PERP1 3

PERN13

PET P1 4( HDVAP1)

PET P1 5( HDVAP0)

PERP1 4

PERN14

PERP1 5

PERN15

PERN8

PERP9

PERP4

PERN4

PERP5

PERN5

PERP6

PERN6

PERP7

PERN7

PERP8

PETP2

PETP0

PETP1

PETP3

PETP4

PETP5

PETP6

PETP7

PETN0

PETN1

PETN2

PETN3

PETN4

PETN5

PETN6

PETN7

PETN8

PETN9(HDVBN2)

PETN10(HDVBN1)

PETN11(HDVBN0)

PETN12

PETN13(HDVAN2)

PETN14(HDVAN1)

PETN15(HDVAN0)

PCI EAV DD

PCI EAV DD

PCI EAV DD

PCI EAV DD

PCI EAV DD

PME#

INTX#

REFCLK+

REFCLK-

H_A#8

Z0440

Z0420

C1XAVDD

H_A#33

NB_GTLREF

H_D#18

1.2VS 7,27

Z0457

H_D#13

Z0426

H_DEFER#2

NB_PCREQ#

H_BPRI#2

PCIE_CLK_NB17

H_REQ#0

H_CLK_NB#17

H_D#33

H_D#44

H_D#26

H_A#12

H_DINV# 2 2

PCI_INTA#6,13

H_A#17

H_REQ#4

H_A#28

Z0448

H_D#52

H_RS#22

H_D#39

1.05VS 2,3,6,7,16,30

Z0418

Z0433

Z0452

C161

0.01u_16V_X7R_04

HDVAP0 18

H_D#0

H_D#57

Z0411

H_CLK_NB17

H_D#2

H_A#23

Z0450

HDVAN018

H_A#32

Z0432

H_D#48

H_D#30

H_DSTBP#0 2

H_D#12

H_D#7

H_ADS#2

H_REQ#[4:0]2

HDVBP1 18

HDVBN118

H_D#25

H_D#43

NC4 NC_04

H_A#[35:3]2

H_A#7

H_BNR#2

H_D#17

H_A#16

H_ADSTB#12

H_D#37

H_D#38

H_DINV# 1 2

Z0456

1.8VS

H_A#21

Z0454

R101

150_1%_04

H_D#56

H_A#11

Z0410

R242 *56_04

1.2VS

H_D#[63:0] 2

H_A#22

Z0441

C1 XA VSS

H_D#51

H_A#27

H_D#63

NB_COMP

H_D#11

H_D#29

Z0446

NB_GTLREF= 0.7V

H_DPWR#2

PCIE_CLK_NB# 17

H_D#6

H_A#20

H_RS#12

C174

0.01u_16V_X7R_04

H_D#1

H_DSTBP#3 2

H_D#24

H_D#21

H_D#42

C171

0. 1u_10V_X7R_04

1.8VS

H_DINV# 0 2

H_DSTBN#3 2

H_A#6

Z0425

R94 10_1%_04

HDVBN218

H_D#16

H_D#47

Z0428

H_A#15

L15 HCB1005KF-121T20

C4 XA VD D

1.05VS

H_HITM#2

H_PWRGD2

H_REQ#2

H_RS#02

H_D#36

R99

75_1%_04

H_A#31

Z0434

Z0453

Z0419

Z0431

C128

10U_10V_08

Place under M671MX

solder side

H_HIT#2

H_A#10

H_A#35

Z0427

Z0436

C145

10U_10V_08

HDVAP2 18

H_D#55

C4XAVDD

HDVBN018

H_D#50

NC3 NC_04

H_D#62

H_A#26

H_D#10

Z0437

Z0413

H_D#28

C1 XA VD D

PCIE_RXN1_WLAN22

NB_PCREQ#

H_D#5

H_D#60

Z0421

H_A#19

C1 XA VS S

NB_GTLREF

H_D#31

H_DSTBP#2 2

H_D#23

NB_PCIE_1.2VS

HDVAN118

HDVAN218

H_A#3

H_D#20

Z0417

H_D#15

H_A#5

Z0424

H_REQ#1

H_D#46

PCI E_R XP1_WLAN22

H_D#59

H_A#14

Z0414

Z0408

H_D#35

PCIE_TXN1 _WLAN 22

PCIE_TXP 1_WLAN 22

H_A#30

Z0455

H_D#32

Z0447

L14 HCB1005KF-121T20

H_DSTBN#2 2

Z0429

Z0422

H_D#41

H_D#54

R92 110_1%_06

H_D#49

Z0415

C166

0.01u_16V_X7R_04

H_DSTBP#1 2

HDVBP2 18

NB_COMP#

H_D#9

H_A#25

H_DRDY#2

H_D#4

H_A#9

Z0443

Z0451

Z0435

H_REQ#3

H_A#18

H_A#34

C203

0.1u_10V_X7R_04

C200

0.01u_16V_X7R _ 04

C163

0.1u_10V_X7 R_ 04

H_LOCK#2

H_D#22

H_ADSTB#02

H_D#19

L17

HCB1005KF-121T20

Sheet 4 of 37

SiSM672 HOST

PCIE 1/5

Schematic Diagrams

B.Schematic Diagrams

SiSM672 HOST PCIE 1/5 B - 5

Schematic Diagrams

M_COMP_N

M_A_D Q9

M_OCDVREF_P

C253

0.1u_10V_X7R_04

M_DQ S1#9,10

C265

*0. 1u_10V_X7R_04

1.8V

M_A_D Q25

M_A_A5

M_A_D Q57

M_DQS39,10

M_CKE 2 10

D1 XAVD D

M_DM09,10

M_A_D Q39

M_A_D Q56

M_FWDSDCLKOA_D#

M_F WDSDCLKOA_D 17

M_A_D Q15

M_A_A0

M_A_A13

L21 H CB1005KF-121T20

M_DQS79,10

R109

1K_1%_04

M_OD T3 10

M_A_D Q0

M_A_D Q20

M_A_D Q42

M_DDRVREF

M_DM49,10

R124 36_1%_06

M_A_DQ[63: 0]9,10

M_A_A17

Plac e clos e to

M671 MX

1.8VS

M_A_D Q30

M_A_D Q4

M_COMP_N

M_A_DQ[63: 0]9,10

M_DQS59,10

M_A_A[17:0] 9,10

M_DQ S7#9,10

M_A_D Q28

M_A_A12

M_A_D Q60

D1XAVDD

M_A_A9

NB_S3AUXSW# 26

M_A_D Q27

M_A_D Q32

D4 XA VSS

M_A_DQ[63: 0]9,10

M_A_D Q54

M_DM29,10

M_A_A3

M_A_D Q23

M_A_D Q29

M_A_D Q18

C232

0.1u_10V_X7R_04

R103 0_04

M_A_A1

M_DQ S6#9,10

1. 8V 7,9, 10,14,15, 16,20, 27,30,31

M_A_D Q53

M_A_D Q21

M_A_D Q51

D4 XAVD D

M_A_D Q63

M_A_D Q49

M_COMP_P

M_A_D Q35

Plac e und er M67 1MX

sold er si de

M_A_DQ[63: 0]9,10

M_DQ S0#9,10

M_A_D Q41

C154

0.01u_16V_X7R_04

M_A_DQ[63: 0]9,10

M_A_D Q24

M_DM59,10

M_FWDSDCLKOA_D_R

M_A_D Q44

1.8VS

M_A_D Q62

C242

0.1u_10V_X7R_04

M_A_D Q19

M_FWDSDCLKOA_D

1.8V

M_CS0# 9,10

M_A_D Q26

M_A_A4

M_A_D Q40

NC5 NC_04

M_A_D Q11

C150

0.1u_10V_X7R_04

M_A_D Q12

M_A_D Q48

D4XAVDD

M_A_D Q50

R121 40.2_1%_04

R123 40.2_1%_04

R108

1K_1%_04

R106 0_04

M_A_D Q14

M_A_A15

M_DQS19,10

M_A_A11

DRAM

U13B

Si SM672

AM15

AM17

AM18

AD28

AD30

AD31

AE 2 9

AE 3 0

AE 3 2

AF 31

AF 32

AF 33

AF 34

AG34

AH2 4

AH32

AH33

AH34

AJ2 5

AK 2 1

AK25

AK26

AK 3 3

AL25

AL34

AM25

AM26

AM30

AM31

AN2 4

AN2 6

AN2 8

AN32

AP21

AP25

AP26

AP29

AJ30

AH16

AL19

AP24

AM28

AM27

AP27

AP28

AK24

AK 1 9

AL17

AL15

AJ2 9

AH2 8

AF 28

AJ34

AH31

AG30

AF 30

AG32

AJ32

AJ31

AK 3 4

AH30

AL32

AM33

AK 3 2

AG29

AM34

AL31

AM32

AP 3 2

AP 3 1

AM29

AK 3 0

AK 2 9

AJ27

AK 2 8

AK 2 0

AM20

AM19

AJ19

AN20

AJ21

AP 1 9

AH20

AK 1 8

AJ17

AK 1 7

AP 1 6

AH18

AP 1 8

AN18

AP 1 7

AN16

AK 1 6

AN14

AJ15

AP 1 5

AM16

AK 1 5

AP 1 4

AL13

AM13

AM12

AJ13

AM14

AK 1 4

AN12

AH14

AK 1 3

AP 1 2

AP 1 3

B15

A15

AP10

AP11

AM23

AP22

AJ2 3

AK12

AH1 2

AP23

AH2 2

AM22

AM21

AK22

AP20

AN2 2

AL21

AN3 0

AP30

AH2 6

AK27

B6

AD1 8

AD2 3

DQS6A#

DQS5A#

DQM5A

DQM0A

MD1A

MD0A

MD3A

MD7A

MD4A

MD6A

DQS0A

DQS0A#

MD5A

MD2A

MA0A

DQS1A

DQS1A#

DQM1A

DDRCOMP

DQM4A

MA7A

DDRCOMN

DQS2A

MA3A

DQS2A#

MA2A

MA5A

DQS3A

DQS3A#

MA1 1A

MA6A

MA1 5A

DQM3A

MA1 6A

MA1A

MA4A

MA1 7A

DQM2A

DQM6A

DQS4A#

MA1 2A

MA1 3A

MA1 4A

MA8A

MA9A

MA1 0A

DQS4A

DQS5A

DQS6A

OCDVREFN

OCDVREFP

MD8A

MD9A

MD10A

MD11A

MD12A

MD13A

MD14A

MD15A

MD16A

MD17A

MD18A

MD19A

MD20A

MD21A

MD22A

MD23A

MD24A

MD25A

MD26A

MD27A

MD28A

MD29A

MD30A

MD31A

MD32A

MD33A

MD34A

MD35A

MD36A

MD37A

MD38A

MD39A

MD40A

MD41A

MD42A

MD43A

MD44A

MD45A

MD46A

MD47A

MD48A

MD49A

MD50A

MD51A

MD52A

MD53A

MD54A

MD55A

MD56A

MD57A

MD58A

MD59A

MD60A

MD61A

MD62A

MD63A

DQM7A

DQS7A

DQS7A#

D1 XA VSS

D1 XAVD D

D4 XA VSS

D4 XAVD D

RASA#

CASA#

WEA#

FWDSDCLK OA

FWDSDCLK OA#

CS0A#

CS1A#

CS2A#

CS3A#

ODT0A

ODT1A

ODT2A

ODT3A

CKEA0

CKEA1

CKEA2

CKEA3

S 3 AU XSW #

DDRVREF0

DDRVREF1

C247

0.01u_16V_X7R_04

M_DQS29,10

M_DQ S2#9,10

M_OCDVREF_N

M_A_DQ[63: 0]9,10

C258

1U_6.3V_04

M_DM39,10

M_A_D Q33

M_FWDSDCLKOA_D#_R

M_DQ S3#9,10

M_A_D Q5

M_OCDVREF_P

C236

0.1u_10V_X7R_04

M_ODT0 9, 10

1. 8VS 4, 6,7, 13,14,15, 16, 17, 18,27

M_A_D Q45

M_CKE1 9, 10

M_DM19,10

M_OCDVREF_N

M_A_D Q52

M_A_D Q59

M_ODT1 9, 10

M_CS1# 9,10

M_DQS09,10

M_A_D Q43

C278

*0. 1u_10V_X7R_04

M_CKE 3 10

M_DQS69,10

M_A_D Q31

M_A_A14

C281

*0. 1u_10V_X7R_04

M_A_A7

M_OCD VREF_ N=0.96 9V

M_CS2# 10

M_WE# 9 , 10

M_A_D Q8

R118 36_1%_06

M_A_A2

M_DQ S5#9,10

M_DQ S4#9,10

M_A_A16

M_OCD VREF_ P=0.87 4V

D1XAVSS

M_A_D Q61

M_DDRVREF

M_DM79,10

M_A_D Q58

M_OD T2 10

M_A_D Q13

M_A_A6

M_F WDSDCLKOA_D # 17

M_A_D Q10

M_DDR VREF=0 .9V

M_DQS49,10

M_A_A8

M_A_DQ[63: 0]9,10

M_A_D Q37

1.8V

1.8V

M_CAS# 9, 10

M_RAS# 9, 10

M_A_D Q2

NC2 NC_04

M_CKE0 9, 10

M_A_D Q38

C124

10U_10V_08

D1 XA VSS

M_A_D Q47

M_A_D Q55

M_A_DQ[63: 0]9,10

M_DM69,10

M_A_D Q1

M_A_D Q6

R119 36_1%_06

M_CS3# 10

M_A_D Q46

C256

10U_10V_08

M_A_D Q16

M_A_D Q17

L12 H CB1005KF-121T20

M_A_D Q3

M_A_A10

M_A_D Q36

D4XAVSS

M_A_D Q7

M_A_D Q22

R112 36_1%_06

M_A_D Q34

M_COMP_P

Sheet 5 of 37

SiSM672 DRAM 2/5

SiSM672 DRAM 2/5

B.Schematic Diagrams

B - 6 SiSM672 DRAM 2/5

SiSM672 MuTITOL VGA 3/5

U33

74AHC1G32GW

4

53

1

2

VCOMP

R 107 56_04

N B_TESTM OD E2

ZAD 11

NC15 N C _04

1.8VS

ZAD 13

Z_COMP_N

R362 *0_04

1.8VS

AU X_PWR O K 12 ,14

Z0601

AU X_PWR O K

DA CAV DD 1

ZSTB_D#013

C466 * 0.1u_10V _X7R _04

C 457 0.1u_10V_X7R_04

DAC_DDCACLK25

Z0610

Z0605

Z0603

Z0621

ASL

U13A

SiSM 672

AM8

AM9

AM 10

AN8

AN 10

AP4

AP5

AP8

AP9

AH 10

AL7

AL9

AM7

AK 10

AM6

AK 11

AJ11

AP7

AJ9

AP6

AN6

AK9

AM4

AK6

AK8

AN4

AK7

AL5

AM5

D13

C12

C13

G12

F12

D11

E12

D15

C14

C15

F11

F13

A12

B12

A13

B13

B10

A11

A9

F15

D16

E16

F16

D17

E17

F17

AC 32

AD 34

AB28

AD 32

AD 33

AE34

AC 30

AC 29

A5

C6

A7

A6

D9

C8

E9

E7

D8

F7

AH 2

AG 3

B8

G14

ZAD 16

ZC MP _N

Z4XAVDD

ZU RE Q

Z4XAVSS

ZSTB1

ZSTB1#

ZD RE Q

ZC MP _P

ZC LK

ZSTB0#

ZVR EF

ZSTB0

ZAD 0

ZAD 1

ZAD 2

ZAD 3

ZAD 4

ZAD 5

ZAD 6

ZAD 7

ZAD 8

ZAD 9

ZAD 10

ZAD 11

ZAD 12

ZAD 13

ZAD 14

ZAD 15

RO U T

GO U T

BO UT

VSY N C

HS YN C

VG PIO 0

VG PIO 1

VC OMP

VR SET

VVB WN

VO SCI

IN TA #

DA CA VDD 1

DA CA VSS1

DA CA VDD 2

DA CA VSS2

DC LKAV DD

DC LKAV SS

EC LKAVD D

EN TEST

TESTMO DE0

TESTMO DE1

TESTMO DE2

TR AP0

TR AP1

TR AP2

TR AP3

TR AP4

TR AP5

TR AP6

TR AP7

TR AP8

TR AP9

TR A P 10

AU XO K

PW RO K

PC IRS T#

AGP BU SY#

VA CLK

VB CLK

VBCAD

VBHCLK

VBVSYNC

VB HSY N C

NC0

NC1

EC LKAVS S

AGPSTOP#

R389 1K _1%_04

C 455 0.1u_10V_X7R_04

C462

0.01u_16V_X7R_04

C 632 *.1U _16V _04

1.05V <=> 3.3V

DC LKAV DD

VVBWN

3. 3V S

AG PS TO P# 14

R363

33_04

1. 5V S

VR SET

Z0608

L19 HCB1005KF-121T20

C14 6

1U_6.3V_04

3. 3V S

DAC_HSYNC25

Z_VR EF

Z0609

C211

10U _10V _08

C58 5

*100P_ 50V_0 4

C46 5

0.1u_10V_X7R _04

C467

0.01u_16V_X7R _04

L40 HCB1005KF-121T20

Z0602

VB VSY NC 18

VB CLK 18

VB HS YN C 1 8

Z_C LK017

DAC_VSYNC25

Z0622

C119

10U _10V _08

C464 * 0.1u_10V _X7R _04

DA CAV S S2

Z0620

Z0604

H_DPSLP#_LS

H_DPSLP#_LS

R 400 3.3_06

SB _DPR STP#14

DELAY_PWRGD

Z0612

VCOMP

R100

49.9_1%_04

Z4XAVDD

ZAD 2

DP RSTP #_IN V

PC I_IN TA#4,13

U24

74LVC1G17GW

1

2

53

4

C584

100p_50V _04

NB_ENTEST

C63 0

0.1u_16V _04

DA CAV DD 2

ZD RE Q13

R93 0_04

ZAD 1

R 105 56_04

C463

0.01u_16V_X7R_04

R376

*33_04

1.8 VS 4,5 ,7,13 ,14,1 5, 16,17 ,18 ,27

N B_TESTM OD E1

ZAD 3

C635 0.1u_10V_X7R_04

ZSTB_D#113

Z0619

R 390 150_1%_04

3.3VS

3. 3V S

C620

0.01u_16V _X7R _04

AG PB USY# 1 4

C130

0.1U_16V_04

N B_TESTM OD E0

C46 8

0.1u_10V_X7R_04

U32

74LVC1G08GW

1

2

5

4

3

Z0626

DACAVDD1

C PU _STP#14

C21 8

0.1u_10V_X7R _04

R385 200K_04

3.3VS

C239

0.01u_16V_X7R_04

NB_ENTEST

R 391 150_1%_04 R384 1K _1%_04

N B_RST# 18,27

1.05VS 2,3,4,7,16,30

C614

0.1u_16V_04

1.05VS

VB CA D 1 8

Z0629

C21 5

0.1u_10V_X7R _04

ECLKAVDD

1.8VS

ZSTB_D 013

DAC_DDCADAT25

ZAD 15

ZAD 10

R 236 130_1%_04

ZAD 14

L44

H CB1005KF-121T20

L41 HCB1005KF-121T20

DELAY_PWRGD

C 633 *.1U _16V _04

CPUSTP# 17

ZA D[16:0]13

Z0623

Level Shitt

ZAD 7

Z0618

1.5VS 3,22,27

ZAD 8

3.3VS

U26

74LV C1G17GW

1

2

53

4

C461

*10U _10V_08

C22 9

0.1u_10V_X7R _04

R102

150_1%_04

1.8VS

P M_D PRSL PVR 28

Z0613

Z_C OMP_P

C58 6

*100P_ 50V_0 4

6-01-74108-Q61

DAC_BLUE25

Z0624

C469

10U _10V _08

ZAD 9

C634 0.1u_10V_X7R_04

R361

33_04

DAC_RED25

ZAD 12

Z0617

Z_C OMP_N

C61 1

0.1u_16V _04

For SiS VB 307

use only

3.3VS

R346

33_04

R347

33_04

C613

0.1u_16V_04

U31

PC A9306 DC U R

1

2

3

4

8

7

6

5

GND

VR EF1

SC L1

SD A1

EN

VR EF2

SC L2

SDA2

Z4XAVD D

SB_D PR SLPVR14

Z0614

C61 2

0.1u_16V _04

D ACA VSS2

VVBWN

L43

*HC B1005KF-121T20

1.8VS

ZU RE Q13

C459

10U _10V _08

R34 4

33_04

C 629 *.1U _16V _04

Z0611

ZAD 4

Z0625

1.8VS

DCLKAVDD

R34 5

499_1% _04

R35 9

33_04

ZSTB_D 113

DPRSTP#_INV

R36 0

33_04

VA CLK 18

ZAD 6

VCOMP

D ACA VSS1

Z_VR EF

Z_COMP_P

VVBWN

H_DPSLP#2

DACAVSS1

VBHC LK 18

DAC_GREEN25

NC1 NC_04

C46 0

0.1u_10V_X7R _04

3. 3V S

C63 1

0.1u_16V _04

U25

74LVC1G17GW

1

2

53

4

H_D P R STP#2,28

U27

74LV C1G14GW

1

2

53

4

1. 8V S

ZAD 0

EC LKAVD D

ZAD 16

Z0606

Z0607

C583

*100P_50V_04

DACAVDD2

R91 4.7K_04

ZAD 5

D ELAY _PWR GD 27,28

AU X_PWR O K

3.3VS 2,10,11,13, 14,15,16,17,18,19,20,21,22,23,24,25,26,27,28

CLK_14M _671M X17

Sheet 6 of 37

SiSM672 MuTITOL

VGA 3/5

Schematic Diagrams

B.Schematic Diagrams

SiSM672 MuTITOL VGA 3/5 B - 7

Schematic Diagrams

C194

0. 1u_1 0V_ X7R_04

1.2VS

+

C152

*15 0U _4V_B 2

C160

1U_6.3V_04

C248

0.1u _10V _X7R_ 04

1.05 VS

C172

1 0U_10V _08

C280

1U_6.3V_04

C 151

2 2U_6. 3V_ 12

C181

1U_6. 3V _04

1.8 VS

1.8 VS

C188

10U_10 V_0 8

C289

0 .1u_1 0V_ X7R_0 4

C276

1U_6. 3V_ 04

C129

1U_6 .3V _04

C249

1 U_6.3 V_0 4

1.2VS

C187

1U _6.3V _04

1.8 VS

C125

1U_6. 3V_ 04

1.8V

C191

1U_6. 3V_ 04

C164

1U _6.3V _04

1. 8V S

C176

10U_ 10V _08

1.0 5VS 2,3,4, 6 , 16, 30

C190

0. 1u_10V _X7R _04

C189

0. 1u_10V _X7R _04

C170

10U_10 V_0 8

1.8VS

1.8V

1.2 V 27, 30

C195

0.1 u_10V _X7R _04

C240

1 0U_10V _08

C185

0. 1u_10V _X7R _04

C138 & C739 Co-layout

C225

1U_6.3V_04

C205

10 U_10V _08

C182

0.1 u_10V _X7R _04

C180

22U_6 .3V _12

C220

0.1 u_10V _X7R _04

C197

1U _6.3V _04

C148

0. 1u_10V _X7R _04

C246

10U_ 10V _08

1.8 VS 4,5 ,6, 1 3, 14 ,15, 16,17 ,18, 27

C167

0.1 u_10V _X7R _04

C186

22 U_6.3V _12

1.8V

1.2 VS 4,2 7

1.8 V 5, 9 ,10, 14,1 5, 16, 20, 2 7,30 , 31

C126

0 .1u_1 0V_ X7R_04

C234

0.1u _10V _X7R_ 04

1.2VS

C169

0.1u _10V _X7R_ 04

C 165

0 .1u_ 10V _X7R_0 4

1.0 5VS

C217

0.1 u_10V _X7R _04

C177

1U_6.3V_04

C162

0. 01u_1 6V_ X7R_04

C223

1U_6 .3V _04

C210

1 U_6.3 V_0 4

PWR

U13E

SiSM672

AB12

AB13

AC12

AC13

AC14

AC15

AH6

AH7

AJ4

AJ5

AJ6

AJ7

AN2

AK4

AK5

AL1

AL2

AL3

AL4

AM1

AM2

AM3

AN3

AN5

AN7

AN9

E8

E10

F9

F10

F8

AB18

AB20

P20

P22

R21

T22

U21

V22

M11

N11

P11

R11

T11

U11

V11

W11

Y11

AA11

AB11

D6

G8

N19

N21

W23

Y23

AA23

AB23

AC23

AC18

AC20

AC16

AD16

AD17

AD19

AD20

AD21

AD22

AJ22

AJ24

AL23

AN21

AN23

AN25

AN27

AN29

AA13

AA22

AB14

AB15

AB16

AB22

AF6

AF7

AK3

AG4

AG5

AG6

AG7

R13

AH3

AH4

AH5

AJ1

AJ2

AJ3

AK1

AK2

AC22

AC21

AC19

AC17

A19

A20

B19

B20

C19

C20

D19

D20

E19

E20

F19

F20

G1 9

G2 0

L1 8

L1 9

L2 0

M2 0

M2 1

M2 2

M2 3

N23

P23

R23

T2 3

U23

V23

M1 2

N12

P12

R12

T1 2

U12

V12

W12

Y12

AA12

AP3

M1 3

M1 4

M1 5

M1 6

M1 7

M1 8

M1 9

N16

N17

N18

N20

R22

N22

N13

P13

Y13

Y22

T1 3

U13

U22

V13

W13

W22

C5

B5

AL26

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VCC 1 .8

VDD VB 1 . 8

VDD 1 .8

VDD VB 1 . 8

VDD 1 .8

VDD VB 1 . 8

IVDD

IVDD

PV D D H

PV D D H

PV D D H

PV D D H

PV D D H

PV D D H

VDD PE X

VDD PE X

VDD PE X

VDD PE X

VDD PE X

VDD PE X

VDD PE X

VDD PE X

VDD PE X

VDD PE X

VDD PE X

AUX _ I V D D

AUX 1 . 8

PV D D H

PV D D H

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

VCC M

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VTTP

VCC 1 .8

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

AUX _ I V D D

AUX _ I V D D

VCC M

C198

1U_6. 3V_ 04

C228

1U _6.3V _04

C204

0.1u _10V _X7R_ 04

C175

1U_6 .3V _04

C192

0 .1u_1 0V_ X7R_0 4

C209

1U_6 .3V _04

1.2 VS

1.2VS

C173

1U_6. 3V _04

1.2 VS

C202

1U_6 .3V _04

1. 2V

C201

1 0U_10V _08

C273

1U_6 .3V _04

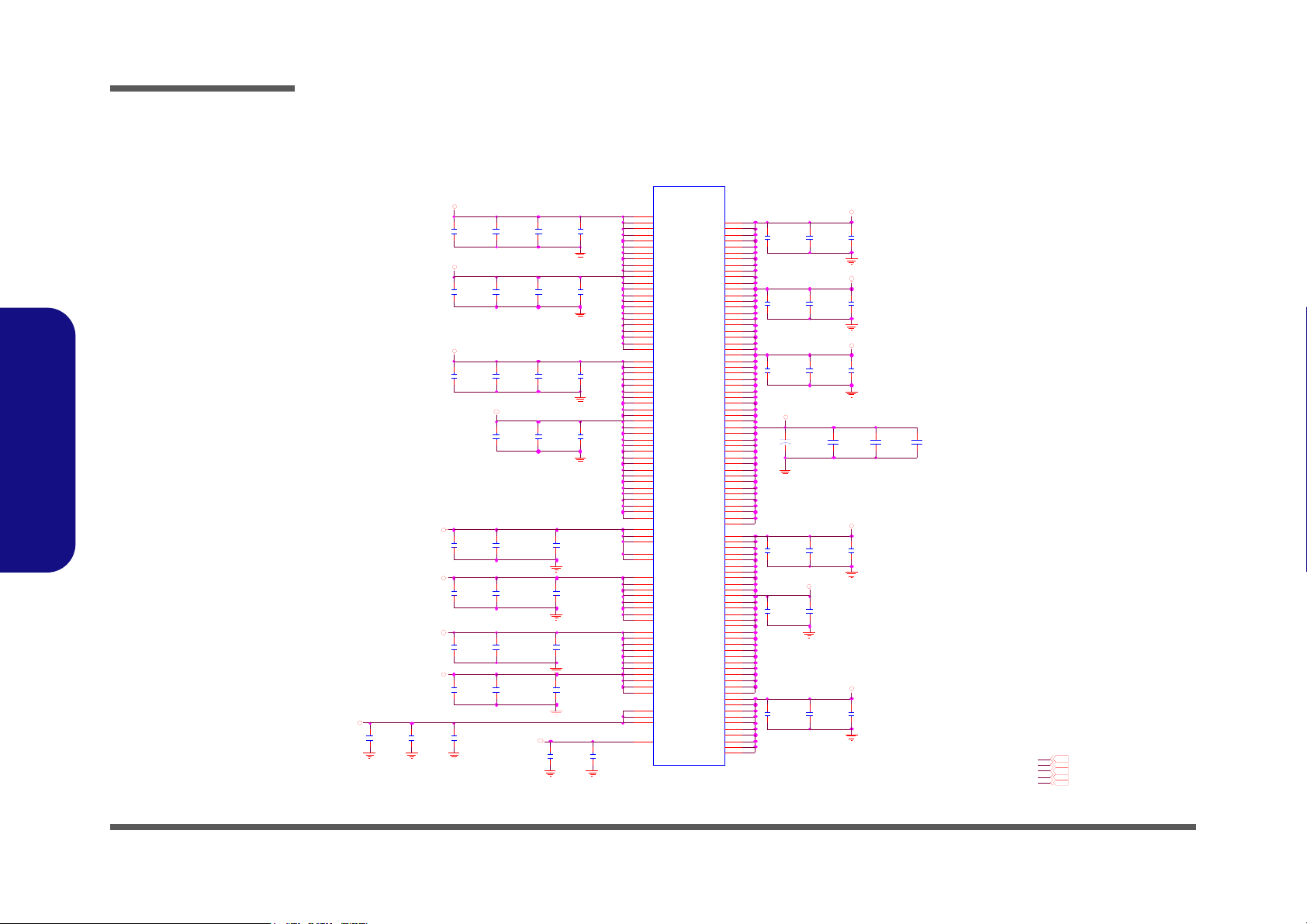

Sheet 7 of 37

SiSM672 PWR 4/5

B.Schematic Diagrams

B - 8 SiSM672 PWR 4/5

SiSM672 PWR 4/5

SiSM672 GND 5/5

H25

C367B 158D158

M11

M-MARK1

1

H8

MTH29 6D 111A

2

3

4 7

8

9

H23

C367B158D158

H28

C237B128D107

M10

M-MARK 1

M2

M-MARK1

1/10

H11

C237D 107A

H1

C158D 158

M1

M-MARK1

1

H20

MTH296D111A

2

3

4 7

8

9

M6

M-MARK1

H14

C237D107A

M9

M-MA RK1

H2

C158D158

1

H13

C296D111N

2

3

4 7

8

9

M14

M-MA RK1

1

H7

C355CH512B 296D111N

2

3

4 7

8

9

H15

C237D107A

1

H10

C296D185N

2

3

4 7

8

9

1

H22

C296D111N

2

3

4 7

8

9

M8

M-MARK 1

H9

C296D111

GND

U13F

Si S M672

A3

B2

B3

B4

AA 1 6

AA 1 7

AA 1 8

AA 1 9

AA 2 0

AA 2 1

AA31

AA33

AB3

AB4

AB5

AG2

AG3 1

AG3 3

AH2 9

B21

B23

B25

B27

B29

B31

C1

C2

C3

C4

AB7

AB29

AC2

AC3

AC31

AC33

AD2

AD3

AD4

AD5

AD7

AD29

AE3

AE31

AE33

AF 2

AF 3

AF 4

AF 5

AF 29

AJ8

AJ1 0

AJ1 2

AJ1 4

AJ1 6

AJ1 8

AJ2 0

AJ2 6

AJ2 8

AJ3 3

AK31

AL6

AL8

AL10

AL12

AL14

AL16

AL18

AL20

AL28

AL30

AL33

AN1 1

AN1 3

AN1 5

AN1 7

AH1

T29

U2

U3

U4

U5

U6

U14

U15

U16

U17

U18

U19

U20

U31

U33

V2

V3

V4

V5

V14

V15

V16

V17

V18

V19

V20

V29

AN3 3

AN3 1

AN1 9

W3

W14

W15

W16

W17

W18

W19

W20

W21

W31

W33

Y2

Y3

Y4

Y5

Y7

Y14

Y15

Y16

Y17

Y18

Y19

Y20

Y21

Y29

AA2

AA3

AA14

AA15

H5

H29J2J3J7J31

J33K3K4K5K29L2L3L4L5L7L31

L33M2M3

M29N3N4N5N6N7N14

N15

N31

N33P2P3

P14

P15

P16

P17

P18

P29R2R3R4R5

R14

R15

R16

R17

R18

R19

R20

R31

R33T3T6

T14

T15

T16

T17

T18

T19

T20

G31

G33

H4

C9

C10

C11

C16

C18

C32

C33

D1

D2

D3

D4

D5

D10

D12

D21

D23

D25

D27

D29

E1

E2

E3

E6

E11

E13

E14

E18

E29

E30

E33

F2

F3

F4

F5

F6

F14

F22

F24

F26

F28

G2

G3

G7

G10 AB17

AB19

AB21

P19

P21

T21

V21

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S

VS S VS S

VS S

VS S

VS S

VS S

VS S

VS S

M3

M-MARK1

Add Through Hole fix Thermal Issue.

M13

M-MARK1

H18

C158D158

H24

C367B158D158

1

H21

MTH296D111A

2

3

4 7

8

9

M7

M-MARK1

1

H6

C355CH512B296D111N

2

3

4 7

8

9

H17

C67D67

H19

C158D158

H26

C237D91

M12

M-MARK1

1

H16

MTH29 6D111A

2

3

4 7

8

9

H5

C237D83A

H29

C237B128D107

M4

M-MARK1

H27

C237B128D107

1

H12

C296D111N

2

3

4 7

8

9

M5

M-MARK1

Sheet 8 of 37

SiSM672 GND 5/5

Schematic Diagrams

B.Schematic Diagrams

SiSM672 GND 5/5 B - 9

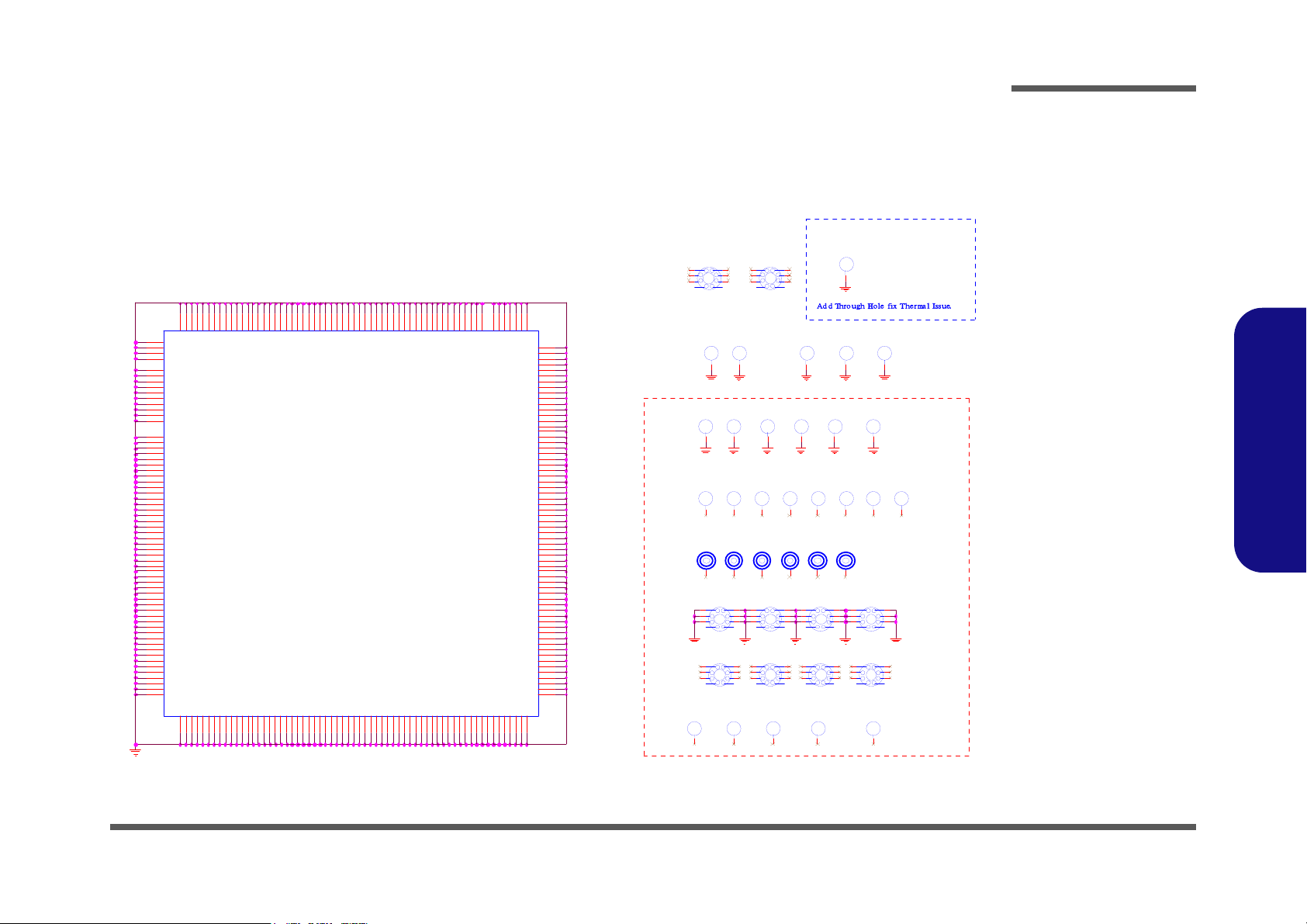

Schematic Diagrams

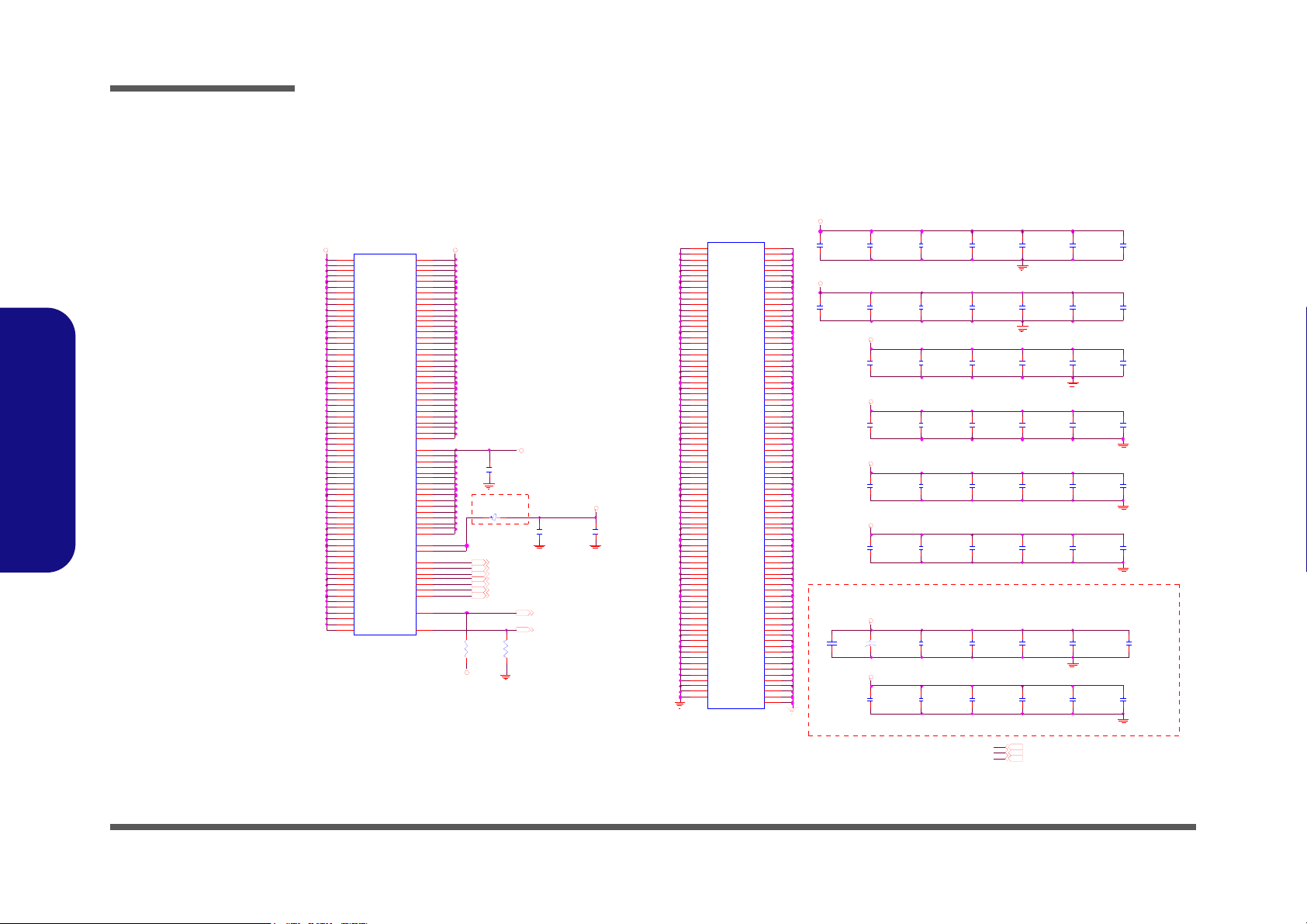

Sheet 9 of 37

DDRII SO-DIMM - 2

M_A_DQ52

M_A_DQ7

M_CS1#5,10

Z0902

M_CLK_DDR 1

M_A_DQ22

M_A_DQ29

M_A_DQ34

M_A_DQ47

M_DQS4#5,10

M_A_DQ30

S_C LK10,14,17,22

M_A_DQ1

M_A_A13

M_DM05,10

M_CS0#5,10

M_CAS#5, 10

3.3VS_SPD

M_A_DQ44

C305

0.1u_10V_X7R_04

M_ODT15,10

M_DQS2#5,10

M_A_DQ12

M_A_A4

M_A_DQ2

M_A_DQ39

M_CLK_DDR 0

M_A_DQ10

M_CLK_DDR017

M_A_DQ63

1.8V

M_A_DQ32

M_A_DQ43

M_A_DQ33

M_A_DQ36

1.8V 5,7,10,14,15,16, 20,27, 30, 31

M_A_A8

M_A_DQ56

M_A_DQ53

M_DQS65,10

M_A_A3

C243

0. 22u_10V_04

+

C283

*150U_4V_B2

C222

0.22u_10V_04

M_A_A [ 17 : 0]5,10

C303

0.1u_10V_X7R_04

M_A_A15

S_D AT10, 14,17,22

M_A_DQ9

C274

0.1u_16V_04

C213

0.1u_16V_04

M_DQS25,10

M_A_DQ62

M_A_DQ0

M_CA S#

C171 & C743 Co-layout

M_A_DQ18

M_A_DQ15

M_A_A12

C310

1U_6.3V_04

M_A_DQ[63:0] 5, 10

M_A_DQ3

M_A_A11

M_A_DQ35

M_CLK_DDR0#17

M_A_DQ55

M_A_DQ8

C170 & C742 Co-layout

M_A_A16

M_A_A1

M_A_A9

M_DQS75,10

M_A_DQ45

R130

1K_1%_04

C179

22U_6.3V_12

1.8V

M_CS 0#

M_A_DQ25

M_RAS#5, 10

M_A_DQ42

M_A_A0

M_A_DQ31

C193

4. 7U_10V_08

C260

0.1u_16V_04

M_A_DQ59

M_A_A17

C224

0. 1u_16V_04

Closed to NB(Solt

lower).

M_DQS35,10

M_DM15,10

M_DQS6#5,10

M_A_DQ5

M_A_DQ41

M_A_DQ11

M_DM75,10

M_DQS3#5,10

Z0901

M_DQS55,10

M_DQS1#5,10

M_A_DQ13

M_WE#5,10

M_A_DQ46

M_A_DQ17

M_A_DQ26

C237

10U_10V_08

M_A_DQ23

M_A_DQ50

R132

1K_1%_04

M_A_DQ27

C230

10U_10V_08

M_CKE05, 10

M_A_DQ21

C291

10U_10V_08

M_DM55,10

M_CLK_DDR 1#

M_A_DQ54

M_DQS7#5,10

M_A_A10

M_A_DQ6

M_CS 1#

1.8V

M_A_DQ51

R86 10K_04

M_CK E0

M_A_DQ19

M_CLK_DDR 0#

M_ODT05,10

M_WE#

M_DQS0#5,10

M_A_A14

MVREF 1

MVREF1

M_A_DQ49

M_DQS5#5,10

JDIMM2

AS0A421-NARN-4F

102

101

100

99

98

97

94

92

93

91

105

90

89

107

106

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

112

111

1179695

11881828710388104

149

47

133

183771248184787172121

122

196

1938162

150

1384028

18244153425459656066127

139

128

145

165

171

172

187

178

1909213315534132

144

156

168231527

83

120

50

69

163

86

39

198

200

161

1

177

199

116

11

29

49

68

129

146

167

186

10

26

52

67

130

147

170

185

84

13

31

51

70

131

148

169

188

85

108

109

113

110

115

79

80

30

164

114

32

166

119

195

197

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

BA0

BA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VS S

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VS S

VS S

VS S

VSS

NC1

NC2

NC3

NC4

NCTEST

A14

VSS

SA0

SA1

VSS

VREF

VSS

VDD SPD

A13

DQS #0

DQS #1

DQS #2

DQS #3

DQS #4

DQS #5

DQS #6

DQS #7

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

A15

DQS 0

DQS 1

DQS 2

DQS 3

DQS 4

DQS 5

DQS 6

DQS 7

A16/BA2

RAS#

WE#

CAS#

S0#

S1#

CKE0

CKE1

CK0

CK1

ODT0

CK0#

CK1#

ODT1

SDA

SCL

M_A_DQ20

M_DM25,10

M_A_A2

M_A_DQ16

M_CLK_DDR117

M_A_DQ4

M_A_DQ40

M_A_DQ14

M_ODT0

C282

22U_6.3V_12

M_A_A6

C287

4.7U_10V_08

M_CLK_DDR1#17

M_A_A7

M_A_A5

M_A_DQ37

M_CK E1

M_RA S#

M_A_DQ60

C271

0.1u_16V_04

R84 10K_04

SO-DIMM 0

M_A_DQ57

M_DQS15,10

C262

0.1u_16V_04

1.8V

M_A_DQ61

M_A_DQ58

M_A_DQ48

C216

0.1u_16V_04

M_DM35,10

M_ODT1

M_DM45,10

C250

0.1u_16V_04

M_A_DQ38

3.3VS_SPD 10

C118

0.1u_16V_04

+

C178

*150U_4V_B2

M_DQS05,10

M_DQS45,10

M_A_DQ24

C306

1U_6.3V_04

M_CKE15, 10

M_DM65,10

M_A_DQ28

DDRII SO-DIMM - 2

B.Schematic Diagrams

B - 10 DDRII SO-DIMM - 2

DDRII SO-DIMM - 1

Sheet 10 of 37

DDRII SO-DIMM - 1

M_DM65,9

M_A_DQ24

M_A_DQ0

M_A_DQ11

M_A_A11

R98 56_04

D6 S CS751V-40

AC

M_D QS05,9

M_A_DQ59

M_A_DQ10

M_A_A2

C199 1U_6.3V_04

C263 0.1u_16V_04

C1 83 & C184 Co-la yout

1.8V

M_D QS15,9

C254

10U_10V_08

M_CLK_DDR3#17

C311

1U_6.3V_04

0.9VS 31

M_CKE05,9

M_A_DQ62

RN2

4P2RX56_04

14

23

M_ODT25

M_A_DQ27 M_A_A15

C312

0.1u_10V_X7R_04

3.3VS 2,6,11,13,14, 15,16,17, 18,19,20,21,22, 23,24,25, 26,27,28

M_A_DQ43

M_CLK_DDR3

M_A_DQ2

C235 0.1u_16V_04

M_D QS25,9

M_A_DQ21

M_DQS5#5,9

M_CS2#5

M_CKE25

RN8

4P2RX56_04

14

23

SUSB27

M_A_A14

M_DM35,9

M_CKE35

Z1002

M_A_DQ22

M_RAS#

RN7

4P2RX56_04

14

23

M_DQS1#5,9

S_DAT9,14,17,22

M_CAS#5,9

C482 0.1u_16V_04

M_A_A1

M_A_A2

C241

0.1u_16V_04

C261

0.1u_16V_04

M_A_DQ26

M_A_DQ6

3. 3 V S_ SPD

M_RAS#5,9

M_ODT05,9

MVREF2

M_A_DQ55

C275

4.7U_10V_08

C486 0.1u_16V_04

SO-DIMM 1

M_A_A1

C206 0.22u_10V_04

M_A _A[17:0]5,9

M_A_A5

M_A_A4

MVREF2

M_A_DQ34

M_A_A9

M_A_A13

+

C296

150U_4V_B2

M_A_DQ52

M_CLK_DDR2

RN21

4P2RX56_04

14

23

RN4

4P2RX56_04

14

23

M_CAS#

M_A_A15

M_A_DQ16

Q30

2N7002W

G

DS

M_A_A17 M_A_A17

M_CLK_DDR2#

M_D QS65,9

M_A_DQ30

M_A_A3

M_A_DQ31

M_A_A8

C120

0.1u_16V_04

M_A_DQ17

M_A_A6

C245

0. 22u_10V_04

M_A_DQ28

M_A_DQ14

M_WE#

M_A_A3

R97 56_04

M_A_A5

RN9

4P2RX56_04

14

23

M_DQS6#5,9

M_A_DQ38

M_A_DQ39

C196

10U_10V_08

3. 3 VS_S PD 9

M_DQS7#5,9

M_A_A0

M_A_DQ61

C227 0.1u_16V_04

M_A_DQ53

R241 56_04

M_A_DQ[63: 0] 5,9

JDIMM1

AS0A421-N2RN-4F

102

101

100

99

98

97

94

92

93

91

105

90

89

107

106

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

112

111

1179695

11881828710388104

149

47

133

183771248184787172121

122

196

1938162

150

1384028

18244153425459656066127

139

128

145

165

171

172

187

178

1909213315534132

144

156

168231527

83

120

50

69

163

86

39

198

200

161

1

177

199

116

11

29

49

68

129

146

167

186

10

26

52

67

130

147

170

185

84

13

31

51

70

131

148

169

188

85

108

109

113

110

115

79

80

30

164

114

32

166

119

195

197

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

BA0

BA1

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

NC1

NC2

NC3

NC4

NCT EST

A14

VSS

SA0

SA1

VSS

VREF

VSS

VDDSPD

A13

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

A15

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

A16/BA2

RAS#

WE#

CAS#

S0#

S1#

CKE0

CKE1

CK0

CK1

ODT0

CK0#

CK1#

ODT1

SDA

SCL

M_CLK_DDR217

3.3VS

0.9VS

M_A_DQ57