Page 1

Appendix B:Schematic Diagrams

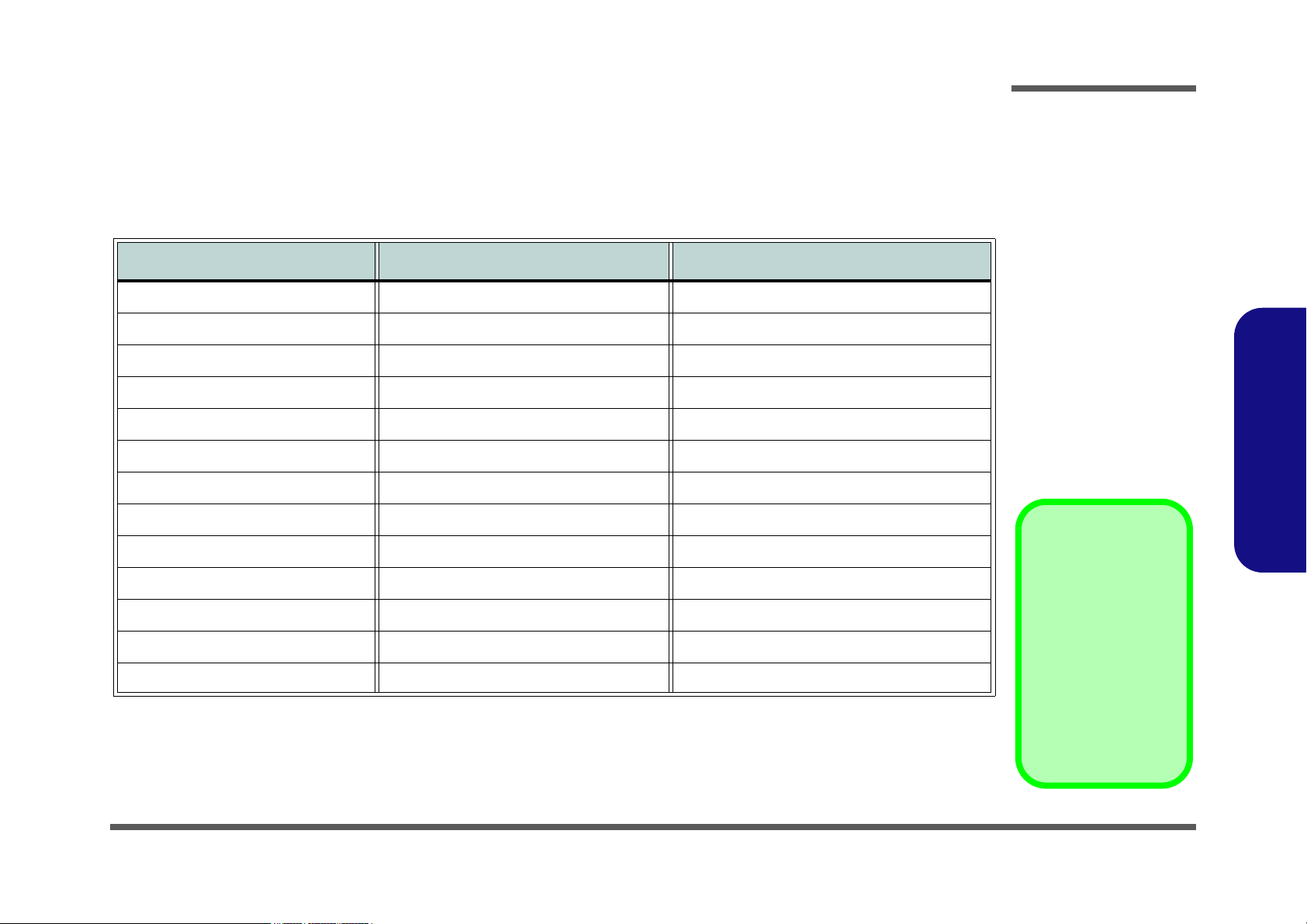

Table B - 1

Schematic

Diagrams

Version Note

The schematic diagrams in this chapter

are based upon version 6-71-M55S0-

003A. If your mainboard (or other boards)

are a later version,

please check with the

Service Center for updated diagrams (if required).

This appendix has circuit diagrams of the M540S/M545S/M550S/M555S notebook’s PCB’s. The following table indicates where to find the appropriate schematic diagram.

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 VT8237 2/3 - Page B - 15 +1.8V, +0.9V - Page B - 28

PROCESSOR 1/2 - Page B - 3 VT8237 3/3 - Page B - 16 VCORE - Page B - 29

PROCESSOR 2/2 - Page B - 4 MINI PCI, MINI Card, USB2.0*2 - Page B - 17 VCCP, +1.5VS - Page B - 30

VN800 1/4 - Page B - 5 PATA HDD, CD-ROM, H8 BEEP - Page B - 18 +VDD3, +VDD5 - Page B - 31

VN800 2/4 - Page B - 6 LAN PHY - Page B - 19 D/D BD (CRT, INVERTER, CCD) - Page B - 32

VN800 3/4 - Page B - 7 LPC ROM, TOUCH PAD, LED - Page B - 20 D/D BD (CHARGER, DC IN) - Page B - 33

VN800 4/4 - Page B - 8 H8-2111 - Page B - 21 AUDIO BD (PHONE JACK, USB, RJ-11) - Page B - 34

DDR2-1 - Page B - 9 MDC, USB BT, PWRGD, DDB CON - Page B - 22 HOT KEY BD (HOT KEY, LED) - Page B - 35

Schematic Diagrams

B.Schematic Diagrams

DDR2-2 - Page B - 10 AC97 CODEC VT1613 - Page B - 23 LED BOARD - Page B - 36

CLOCK GENERATOR, CCD - Page B - 11 AUDIO AMP, USB2.0*2 - Page B - 24 CLICK BOARD - Page B - 37

PANEL, INVERTER, FAN - Page B - 12 PCMCIA ENE CB714B - Page B - 25 RJ-45 BOARD - Page B - 38

VIA LVDS VT-1637 - Page B - 13 PCM SOCKET, 3-IN-1 SOCKET - Page B - 26 USB DONGLE BOARD - Page B - 39

VT8237 1/3 - Page B - 14 3VS, 5VS, 2.5VS, 1.8VS - Page B - 27 DEBUG PORT - Page B - 40

B-1

Page 2

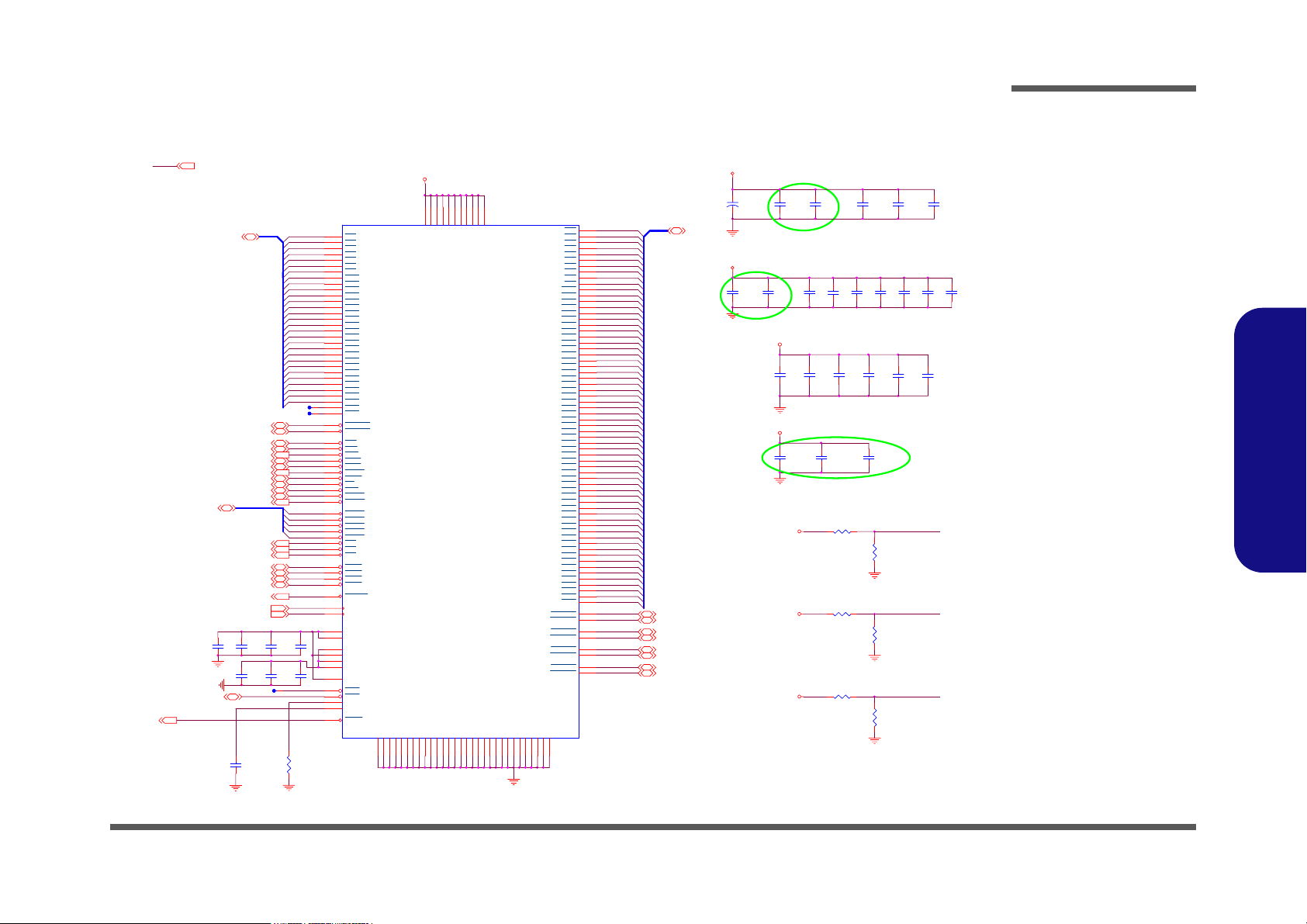

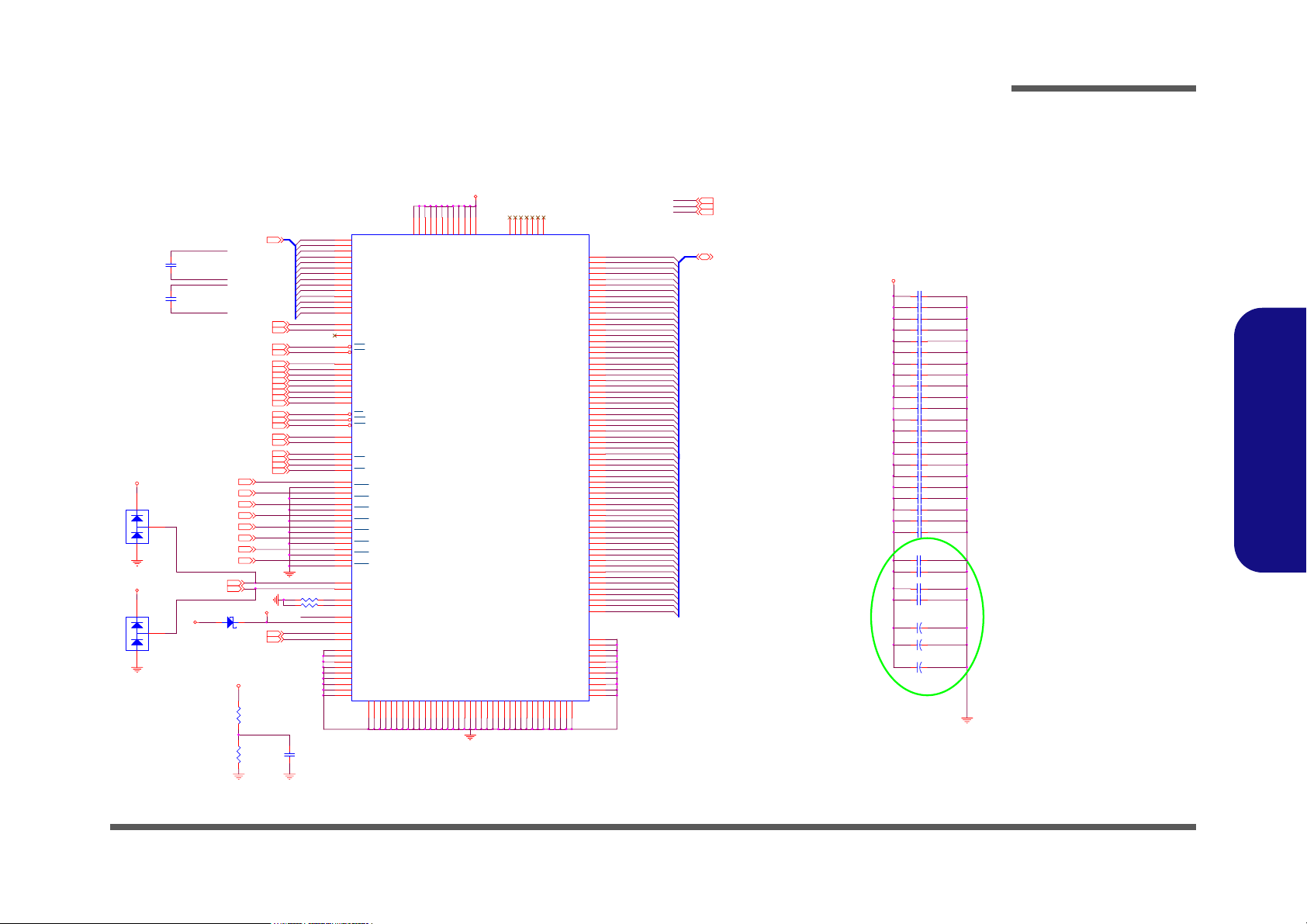

Schematic Diagrams

Sheet 1 of 39

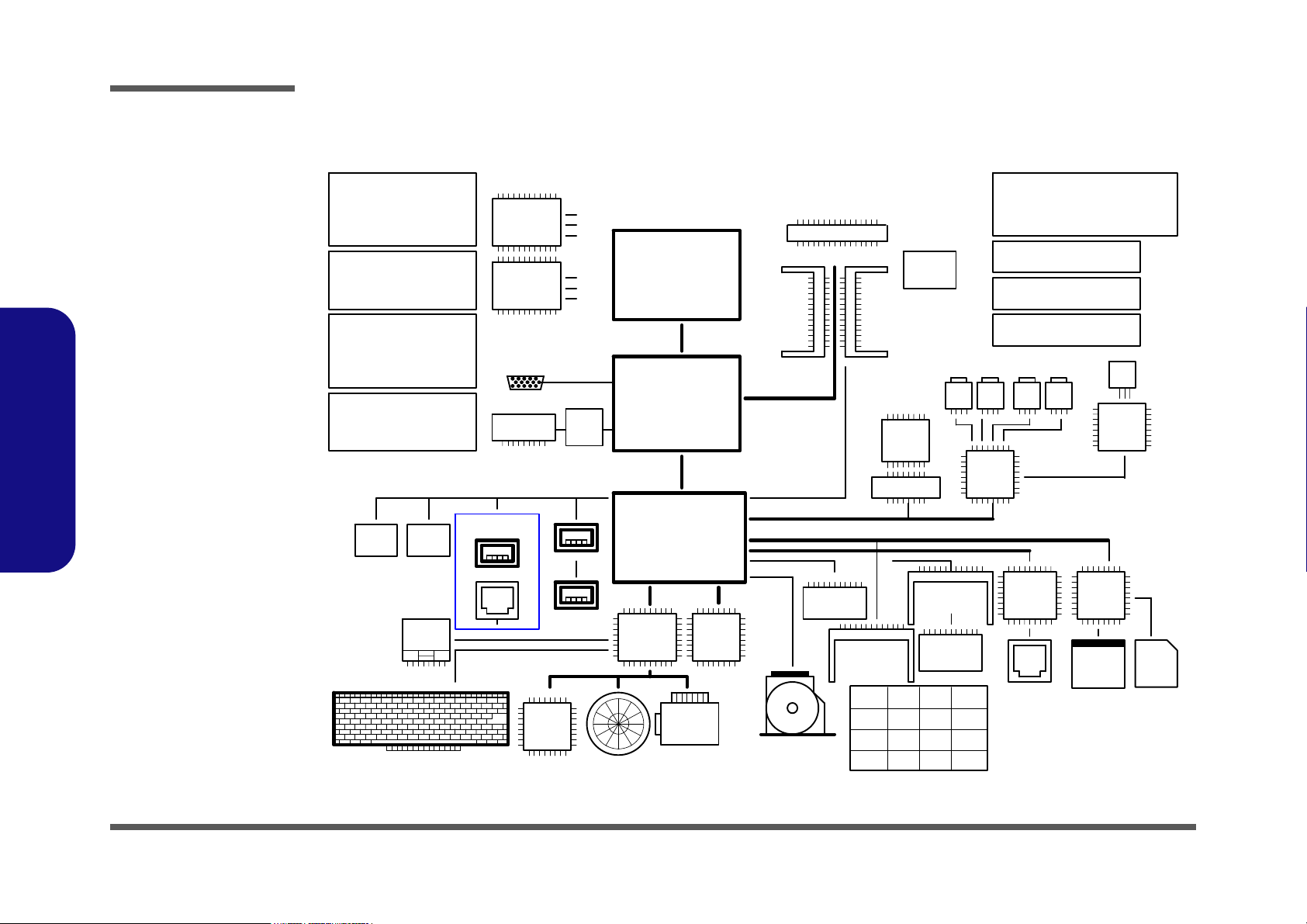

System Block

Diagram

RJ-11

CEN/SUB

ON

AMP.

MIC

S5

PCMCIA

SOCKET

LPC

1.+VCORE

2.INDICATOR LED

MII

533MHz

ENE

CB714B

1.POWER BOTTON

4 IN 1

KBC CONN

OFF

CCD

MEMORY TERMINATIONS

+*V

SYSTEM

BIOS

567 HSBGA

F75383M

1.CHARGER,DC JACK

LINE

IN

CODEC

FRONT

1.+1.05V,+1.5V

1.+VTT_MEM,+1.8V

MDC

DDR VR

2.CRT,RJ-11

CARD

READER

3.LID SWITCH

ICS952906

3.+VDD3,+VDD5,

CPU FAN

PCI BUS

+*VS

33MHz

VT1637

LVDS

SO-DIMM1

HDD

CONNECTOR

PROCESSOR

+VDD

CPU

FSB

VT1613

SENSOR

HOTKEY BOARD

H8/2111

SM BUS

802.11 b/g

HP

OUT

2.USB CONNECTOR

,+2.5V

+2.5VS

(Option)

479 uFCPGA

APA2020A

Mini PCI

PCMCIA

SHEET 30

VN800

539 BGA

USB 1

RJ-45

USB2.0

POWER SWITCH BOARD

AUDIO

TOUCH

CLEVO M540S/M550S System Block Diagram

ON

KBC

2.INDICATOR LED

SMART

1.+3V,+5V

(Option)

CRT

MULTI FUNCTION BOARD

DDR2 SDRAM SOCKET

USB2.0

PHONE JACK

BOARD

IN

SB

MODULE

TEMP

OFF

LPC

MINI CARD

(Option)

LCD CONN

(LVDS)

CLOCK

BUFFER

NB

USB 0

OFFS3

BT

FULL

ON

2.+1.5VS,+3VS,+5VS ,

ON

USB 2

ON

SPDIF

OUT

SO-DIMM0

MDC CONN.

SURR

PHY

SOCKET

SHEET 16

VLINK 533MB/sec

CD-ROM/CD-RW/

Mini PCIE

PHONE JACK BOARD

YONAH

INT.

SPK

VT8237R+

BATTERY

DVD-ROM/DVD+-RW

1.AUDIO PHONE JACK

ON

VT6103

ON

PATA HDD

3.+3VH8,+5VH8

ICS9P936

MULTI FUNCTION

BOARD

IDE

MAIN CLOCK

SM BUS

1.HOT KEY

AC97 LINK

SOCKET*1

PAD

SHEET 16

System Block Diagram

B.Schematic Diagrams

B - 2

Page 3

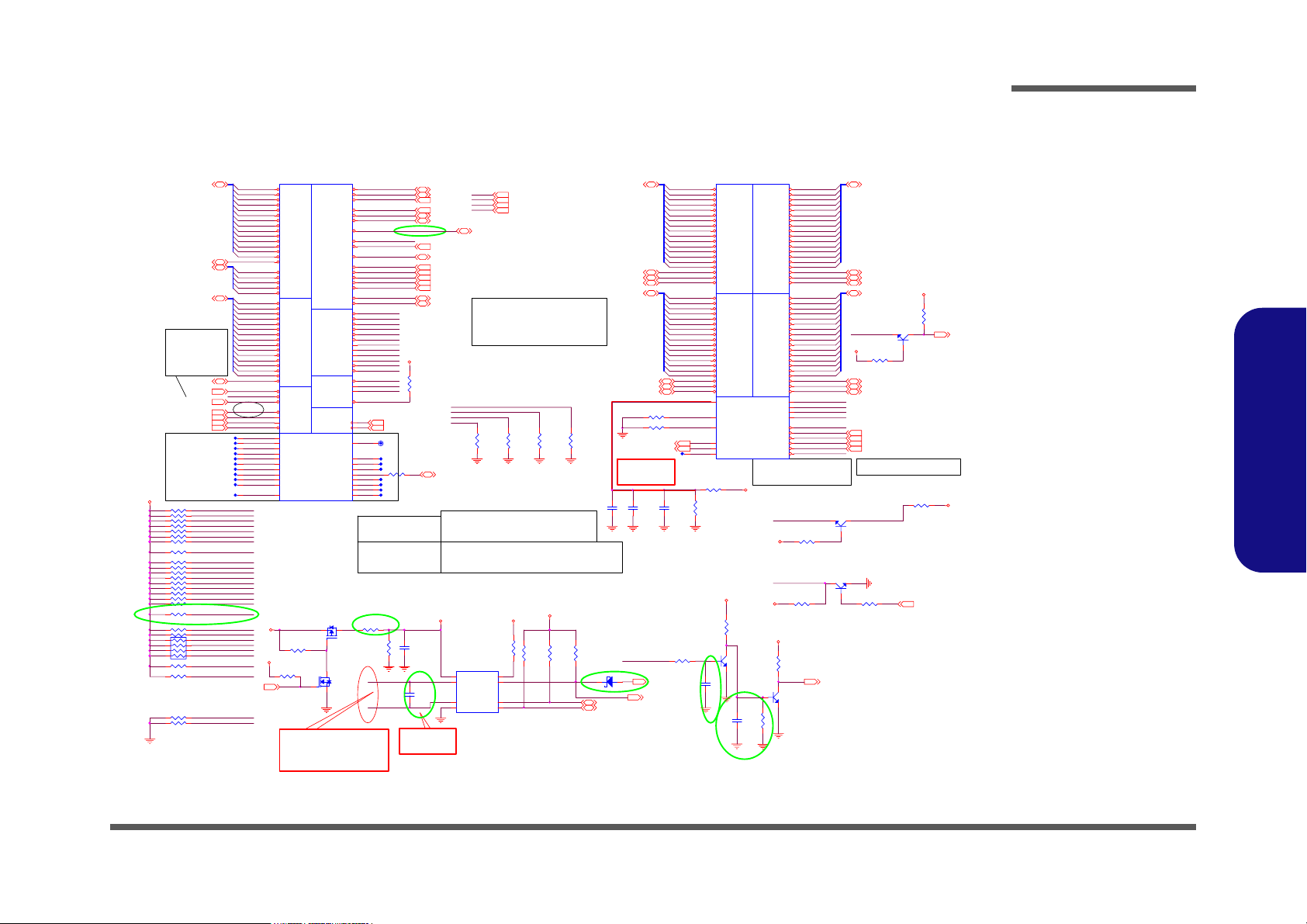

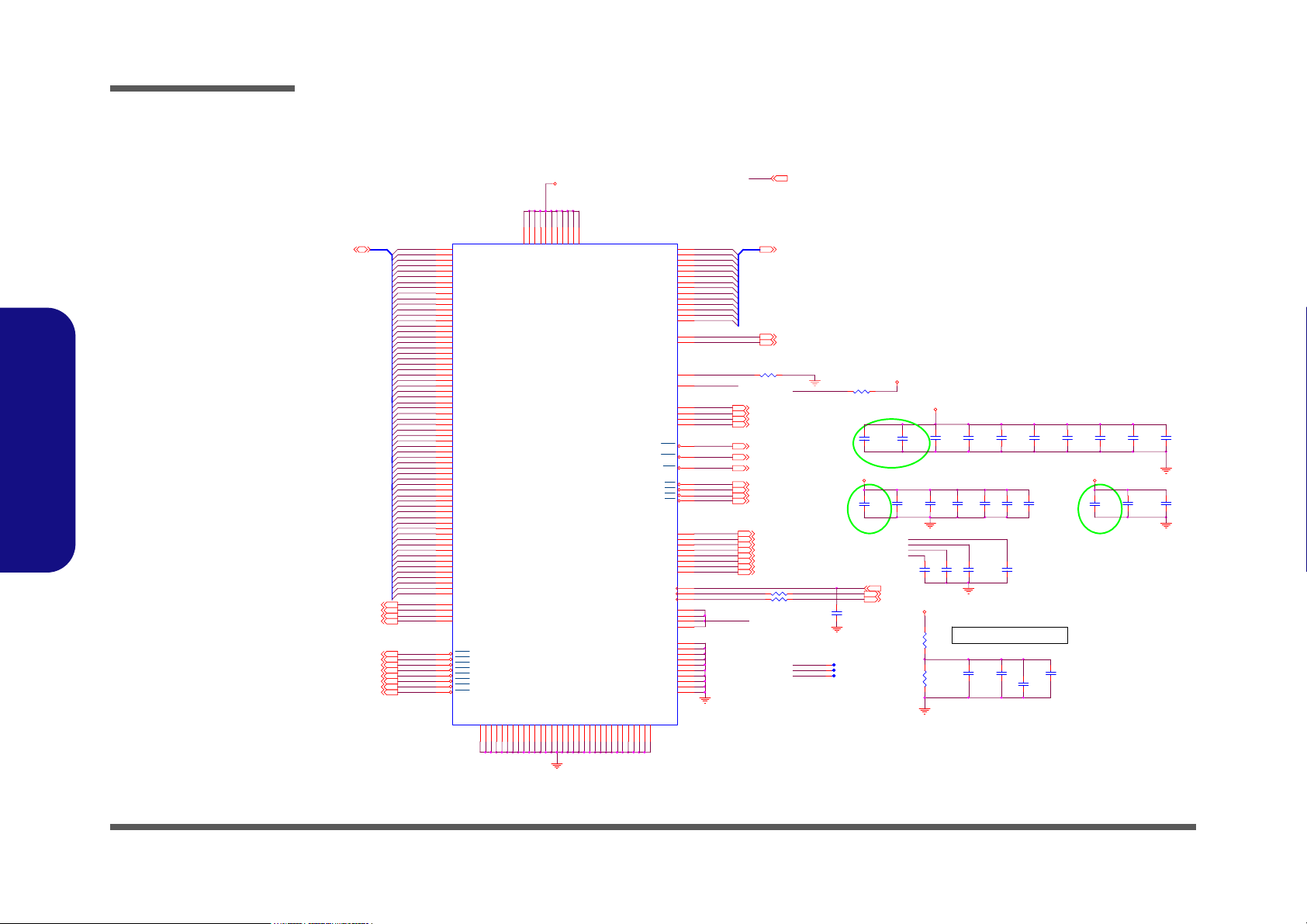

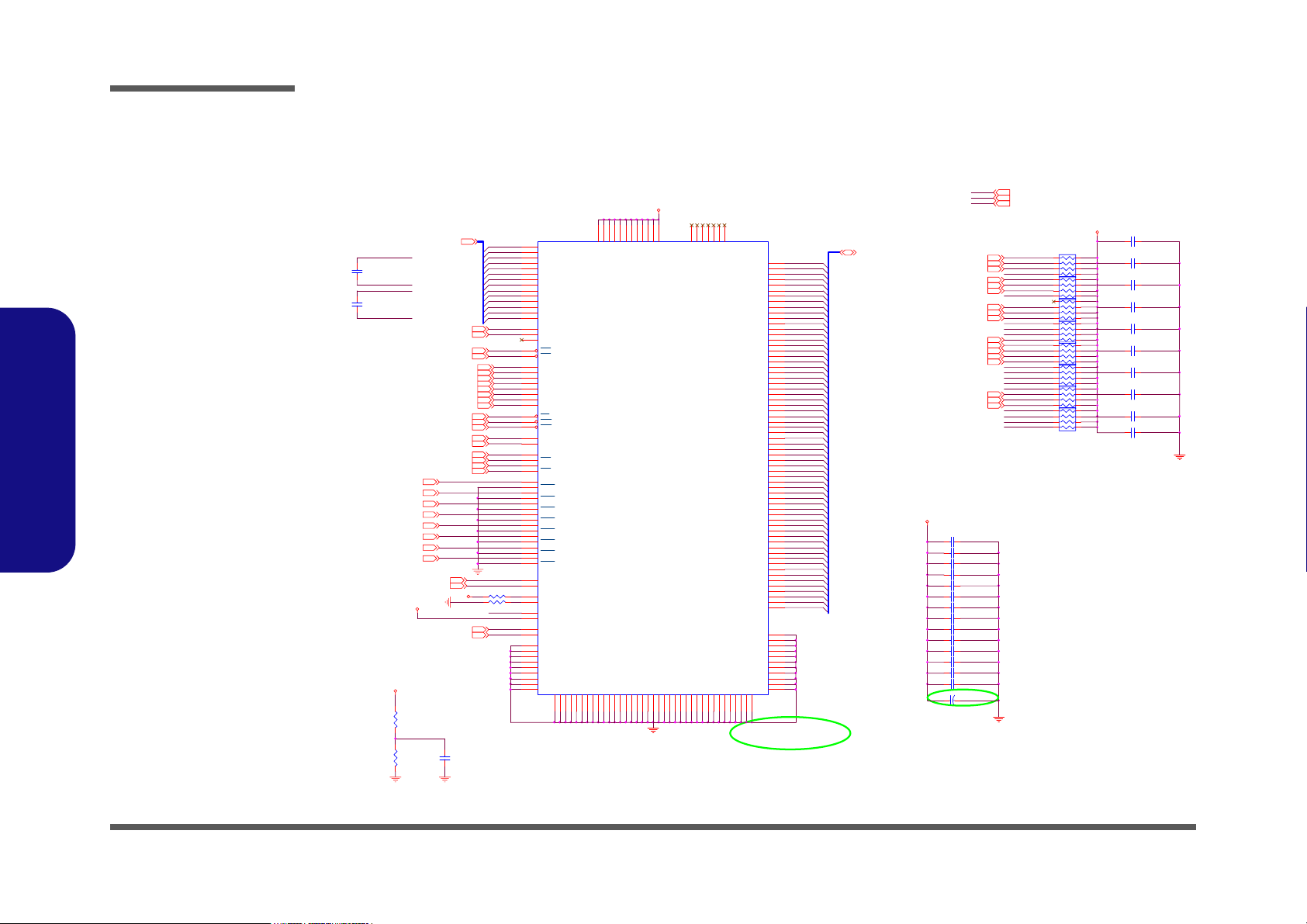

PROCESSOR 1/2

Sheet 2 of 39

PROCESSOR 1/2

H_D#35

D32

*SCS751V-40

AC

H_SMI#

R303 10K_04

H_D#51

H_THERMDA

If PROCHOT# is not used, it must be pull-up 56

Ohm to Vccp; if PROCHOT# is routed between CPU,

IMVP6 VR & GMCH, Rtt has to be 75ohm+-5%

Layout Note:

+VCCP

R23 200 _04

H_RS#1 4

FERR#

H_A#18

H_A#14

H_A#21

R26 10K_04

H_DPWR# 4

R575 *0_04

Layout Note:

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms

COMP1, COMP3: 0.5" Max, Zo=55 Ohms

Best estimate is 18 mils wide trace

for outer layers and 14 mils wide

trace if on internal layers.

H_D#60

H_D#57

H_DPRSLPVR

+2.5VS 10,12, 13,14, 15,21, 26,28, 29

H_D#12

CLK_CPU_BCLK 10

H_INTR15

H_A#22

H_CPURST#

H_INTR

R326

100K_04

+VCC P

H_D#40

COMP2

H_BPM0#

Layout Note:

ITP_DBRST#

H_D#21

C469

10u/10V_ 08

R581

*6.8K_04

+VDD3

H_A#3

H_HIT# 4

H_D#53

R47 51_ 1%_06

H_BREQ0# 4

H_PWRGD

H_A#15

H_REQ#0

H_A#20

R323

4.7K_04

CPU_GTLREF

H_D#6

H_D#17

H_PSI#

R546 150_04

A#[32-39],

APM#[0-1]:

Leave escape

routing on

for future

functionality

H_D#20

R321 0_06

R315 10K_04

H_IERR#

H_D#9

H_D#36

H_A#24

RN2 220_06_8P 4R

8 1

7 2

653

4

H_PREQ#

H_INTR

H_D#8

Within 2.0" of the CPU

R18 75_ 1%_06

T31

R299 150_04

+3VS

H_D#7

R17 680 _1%_06

C481

0.01u/ 25V_04

H_CPUSLP# 15

COMP3

H_DSTBP#3 4

H_D#41

H_D#52

H_D#15

H_D#10

H_D#19

H_REQ#1

H_A#30

R67 150 _04

H_ADSTB#04

H_A#27

R301 150_04

H_DSTBN#14

Layout Note:

0.5" max,

Zo= 55 Ohms

+VC CP

H_D#34

H_D#54

No st ub on H_STPC LK# test

point

C469 CLOSE TO U19.

H_DSTBN#04

H_TDO

H_D#28

H_PRDY#

R16 54. 9_1%_06

R547 150_04

+VCC P

H_IGNNE#15

H_A20M#

H_A#19

H_INIT#

+VCC_THRM

H_REQ#[4:0]4

H_TRDY# 4

R65 75_ 1%_06

R302 150_04

H_DSTBP#14

H_DSTBP#2 4

+VCCP 3,4,10,15,28,29

COMP2

H_THERMDC

R341 51_1%_06

R304

10K_06

R13 10K_04

H_DSTBP#04

H_RS#2 4

+VDD3 15,20,21,26,27,30

H_PRDY#

R286

27.4_1 %_06

H_D#31

R25 10K _04

H_D#23

H_D#22

H_D#4

H_DBI#3 4

H_NMI15

H_D#[63:0]4

H_D#61

+VCCP

H_SMI#15

PM_DPRSLPVR 15,28

H_TRST#

H_PREQ#

H_DPRSLPVR

H_BPM3#

H_D#42

H_A#12

H_REQ#4

[13]

+3VS 6 ,7,8, 10,11,1 2,13,1 4,15,16 ,17, 19,21,2 2,24,2 5,26,28 ,29

H_CPUSLP#

H_D#55

R310 51_1%_04

Near to

F75383M

H_D#16

PM_THRMTRIP#

H_A#28

H_A20M#15

H_DPSLP# 15

H_D#33

COMP1

H_A#7

R340 *1K_04

H_ADSTB0# 4

FERR#

PSI#

C717

*0.1u/16V_04

H_LOCK# 4

H_D#32

H_D#26

RESERVED

ADDR GROUP 0

CONTROL

XDP/ITP SIGNALS

THERMH CLK

JSKT1A

PZ47913-2741-01

J4

L4

M3

K5

M1

N2

J1

N3

P5

P2

L1

P4

P1

R1

L2

K3

H2

K2

J3

L5

Y2

U5

R3

W6

U4

Y5

U2

R4

T5

T3

W3

W5

Y4

W2

Y1

V4

A6

A5

C4

D5

C6

B4

A3

AA1

AA4

AB2

AA3

M4

N5

T2

V3

B2

C3

B25

T22

D2

F6

D3

C1

AF1

D22

C23

C24

A22

A21

D21

A24

A25

C7

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

G6

E4

B1

F3

F4

G3

G2

D20

B3

H4

F1

H5

F21

E1

H1

E2

G5

A[3] #

A[4] #

A[5] #

A[6] #

A[7] #

A[8] #

A[9] #

A[10] #

A[11] #

A[12] #

A[13] #

A[14] #

A[15] #

A[16] #

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17] #

A[18] #

A[19] #

A[20] #

A[21] #

A[22] #

A[23] #

A[24] #

A[25] #

A[26] #

A[27] #

A[28] #

A[29] #

A[30] #

A[31] #

ADSTB[1]#

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD[01]#

RSVD[02]#

RSVD[03]#

RSVD[04]#

RSVD[05]#

RSVD[06]#

RSVD[07]#

RSVD[08]#

RSVD[09]#

RSVD[10]#

RSVD[11]#

RSVD[12]#

RSVD[13]#

RSVD[14]#

RSVD[15]#

RSVD[16]#

RSVD[17]#

RSVD[18]#

RSVD[19]#

RSVD[20]#

BCLK[ 0]

BCLK[ 1]

PROC HOT

THE RM DA

THE RMD C

THER MTRIP#

BPM[0] #

BPM[1] #

BPM[2] #

BPM[3] #

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST #

DBR#

HIT#

HITM#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY #

IERR#

INIT#

LOCK#

BR0#

DEFER#

DRDY#

DBSY#

ADS#

BNR#

BPRI #

R14 *10K_04

H_BREQ0#

DATA GRP 3

DATA GRP 0 DATA GRP 1

MISC

DATA GRP 2

JSKT1B

PZ47913-2741-01

E22

F24

E26

H22

F23

G25

E25

E23

K24

G24

J24

J23

H26

F26

K22

H25

H23

G22

J26

N22

K25

P26

R23

L25

L22

L23

M23

P25

P22

P23

T24

R24

L26

T25

N24

M24

N25

M26

AD26

C26

D25

B22

B23

C21

R26

U26

U1

V1

E5

B5

D24

D6

D7

AE6

AC22

AC23

AB22

AA21

AB21

AC25

AD20

AE22

AF23

AD24

AE21

AD21

AE25

AF25

AF22

AF26

AD23

AE24

AC20

AA23

AB24

V24

V26

W25

U23

U25

U22

AB25

W22

Y23

AA26

Y26

Y22

AC26

AA24

W24

Y25

V23

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

BSEL[0]

BSEL[1]

BSEL[2]

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

Layout note:

H_D#[63:0] 4

H_D#38

H_A#6

R316

100K_04

R335

10K_04

U19

ADM1032ARM

1

2

3

4

5

6

7

8

VDD

D+

D-

THE RM

GND

ALERT

SDATA

SCLK

R339 1K_1%_06

Change Q4,Q5, Q4 7 from FDN 337 N to 390 4

H_D#25

Q48

2N3904

B

E C

+VDD 3

H_CPURST# 4

H8_THERM_ALERT# 20

H_PROCHOT#

H_DSTBN#3 4H_ADSTB#14

H_D#50

H_DPSLP#

H_TCK

H_TCK

R312 330_04

H_DBSY# 4

SMD_THERM 20

PM_THRMTRIP#

R306

680_04

H_HITM# 4

H_D#39

H_TDI

H_STPCLK#

R19 54. 9_1%_06

THE RMT RI P# 30

H_D#45

[13]

H_REQ#2

H_A#31

FERR#

R285

54.9_1 %_06

R20 54. 9_1%_06

Q47

2N3904

B

E C

Zo=55ohm, 0. 5" max for GT LR E F, S pa ce an y othe r switch

signal s aw ay from GT LREF with a m i nimum of 25mi ls.

SMC_THERM 20

H_BPM3#

H_A#23

H_THERMDC

H_CPUSLP#

If FERR# isn' t us ed,

then it must be

terminated wi th a 56

Ohm +-5% pull - up to

Vccp(1.05V)

H_D#14

R298 150_04

H_D#[63:0] 4

H_D#18

H_D#49

COMP0

H_BPM2#

R307 150_04

+VCC P

H_DBI#14

THERM_AL ERT# 14

H_BPM0#

H_A#11

H_TDO

R336

2K_1%_06

[13]

H_IERR#

H_A20M#

Q4

2N3904

B

EC

Don't al low th e GTLRE F routin g to create sp lits or

discontinu i tie s in the ref eren ce p lane s of th e FS B

signals

H_D#27

H_DSTBN#2 4

THER M_RST#20

H_D#46

H_D#2

H_CPURST#

H_STPCLK#

+VC CP

H_D#24

H_A#16

H_DRDY# 4

H_D#47

R309 150_04

R284 54.9_1%_06

R344

27.4_1 %_06

R320

100K_04

H_TDI

Q5

2N3904

B

E C

+VC C_TH RM

Com p 1, 3 con ne ct wi th Zo =55o h m, m a ke trace

le ngth shorter than 0. 5" and w i d th is 5mils

C482

0.1u/16V_04

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil

spacing.

H_DBI#2 4

H_D#29

COMP3

H_BPM2#

R305

*10K_04

Place testpoint on

H_IERR# with a GND

0.1" away.

H_PWRGD 21

H_A#5

H_TMS

H_D#11

H_D#56

H_NMI

H_DPRSLPVR

R313 150_04

H_D#58

H_BPM1#

C443

*10u/10V_08

H_A#[31:3]4

H_TRST#

R283 54.9_1%_06

+VDD 3

H_RS#0 4

H_PWRGD

H_IGNNE#

H_A#10

R324

4.7K_04

If PROCHOT# is routed

between CPU, IMVP and

MCH, pull-up resistor

has to be 75 ohm ? 5%

+2.5 VS

H_BPRI# 4

H_DBI#04

R314 150_04

CLK_CPU_BCLK# 10

H_D#48

H_D#0

H_PSI#

H_D#63

H_BNR# 4

H_TMS

H_D#13

H_A#9

H_A#13

R294 *51_1%_06

R343

54.9_1%_06

H_A#29

PSI# trace:space (4:8 or

5:10),Zo=55ohm +-15%

Comp0,2 connect with Z o =27.4ohm, make trace

len gth shorter than 0. 5" an d w id th i s 18mils.

H_PROCHOT#

H_A#25

H_THERMDA

CPU_BSEL110

H_STPCLK#15

H_ADS# 4

H_IGNNE#

H_INIT#

H_D#44

H_DEFER# 4

H_NMI

H_A#26

H_D#1

Place Series Resistor on

H_PWRGD_XDP Without Stub

C483

1u/10V

+VD D3

H_D#37

COMP1

Q46

2N3904

B

E C

R66 51_ 1%_06

Q49

2N7002

G

DS

Com p 0~3 traces shou ld be at least 25mil s

away from any other togging signal

H_SMI#

H_D#[63:0]4

H_BPM1#

H_A#4

H_A#8

H_D#30

H_PSI#

H_INIT# 15

H_D#62

C473

1000p/ 50V

R311

680_04

Q50

NDS352AP

G

DS

H_A#[31:3]4

H_D#43

H_D#5

COMP0

H_REQ#3

ITP_DBRST#

H_D#59

H_A#17

CPU_BSEL010

H_FERR# 15

H_D#3

Schematic Diagrams

B.Schematic Diagrams

PROCESSOR 1/2 B - 3

Page 4

C448

22u/10V_12

H_VID6

C80

10u/10V_08

JSKT1D

PZ47913- 2741-01

A4

A8

A11

A14

A16

A19

A23

A26

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

AF3

AF6

AF8

AF11

AF13

AF16

AF19

AF21

AF24

VSS[00 1]

VSS[00 2]

VSS[00 3]

VSS[00 4]

VSS[00 5]

VSS[00 6]

VSS[00 7]

VSS[00 8]

VSS[00 9]

VSS[01 0]

VSS[01 1]

VSS[01 2]

VSS[01 3]

VSS[01 4]

VSS[01 5]

VSS[01 6]

VSS[01 7]

VSS[01 8]

VSS[01 9]

VSS[02 0]

VSS[02 1]

VSS[02 2]

VSS[02 3]

VSS[02 4]

VSS[02 5]

VSS[02 6]

VSS[02 7]

VSS[02 8]

VSS[02 9]

VSS[03 0]

VSS[03 1]

VSS[03 2]

VSS[03 3]

VSS[03 4]

VSS[03 5]

VSS[03 6]

VSS[03 7]

VSS[03 8]

VSS[03 9]

VSS[04 0]

VSS[04 1]

VSS[04 2]

VSS[04 3]

VSS[04 4]

VSS[04 5]

VSS[04 6]

VSS[04 7]

VSS[04 8]

VSS[04 9]

VSS[05 0]

VSS[05 1]

VSS[05 2]

VSS[05 3]

VSS[05 4]

VSS[05 5]

VSS[05 6]

VSS[05 7]

VSS[05 8]

VSS[05 9]

VSS[06 0]

VSS[06 1]

VSS[06 2]

VSS[06 3]

VSS[06 4]

VSS[06 5]

VSS[06 6]

VSS[06 7]

VSS[06 8]

VSS[06 9]

VSS[07 0]

VSS[07 1]

VSS[07 2]

VSS[07 3]

VSS[07 4]

VSS[07 5]

VSS[07 6]

VSS[07 7]

VSS[07 8]

VSS[07 9]

VSS[08 0]

VSS[08 1]

VSS[0 82]

VSS[0 83]

VSS[0 84]

VSS[0 85]

VSS[0 86]

VSS[0 87]

VSS[0 88]

VSS[0 89]

VSS[0 90]

VSS[0 91]

VSS[0 92]

VSS[0 93]

VSS[0 94]

VSS[0 95]

VSS[0 96]

VSS[0 97]

VSS[0 98]

VSS[0 99]

VSS[1 00]

VSS[1 01]

VSS[1 02]

VSS[1 03]

VSS[1 04]

VSS[1 05]

VSS[1 06]

VSS[1 07]

VSS[1 08]

VSS[1 09]

VSS[1 10]

VSS[1 11]

VSS[1 12]

VSS[1 13]

VSS[1 14]

VSS[1 15]

VSS[1 16]

VSS[1 17]

VSS[1 18]

VSS[1 19]

VSS[1 20]

VSS[1 21]

VSS[1 22]

VSS[1 23]

VSS[1 24]

VSS[1 25]

VSS[1 26]

VSS[1 27]

VSS[1 28]

VSS[1 29]

VSS[1 30]

VSS[1 31]

VSS[1 32]

VSS[1 33]

VSS[1 34]

VSS[1 35]

VSS[1 36]

VSS[1 37]

VSS[1 38]

VSS[1 39]

VSS[1 40]

VSS[1 41]

VSS[1 42]

VSS[1 43]

VSS[1 44]

VSS[1 45]

VSS[1 46]

VSS[1 47]

VSS[1 48]

VSS[1 49]

VSS[1 50]

VSS[1 51]

VSS[1 52]

VSS[1 53]

VSS[1 54]

VSS[1 55]

VSS[1 56]

VSS[1 57]

VSS[1 58]

VSS[1 59]

VSS[1 60]

VSS[1 61]

VSS[1 62]

499_1%

+VCCP

CPUVS Decoupling Guidelines : 1.5mOhm

used 330uF * 6 ( max ESR = 9mOhm / cap. )

& 3mOhm used 22uF * 32 MLCC

C51

10u/10V_08

4 & 8 mils

Default

viax20

C77

10u/10V_08

C459

22u/10V_1 2

C477

10u/10V_0 8

C79

10u/10V_08

C30

0.1u/16V_04

C455

22u/10V_1 2

+

C442

150U/4V _B

+VCCA_CPU

30A, 2000mils

R21

100_1%_06

C451

22u/10V_12

C27

0.1u/ 16V_04

C447

22u/10V_12

Route VCCSENSE and

VSSSENSE traces at 27.4Ohm

with 50 mil spacing.

Place PU and PD within 1

inch of CPU.

Micro-strip(Ext. Layer)

+VCORE +VCORE+VCO RE

Pl ace th ese inside socket cavity on L1 (South side Prim ary)

55+/-15%

C52

10u/10V_08

H_VID0 28

C32

0.1u/16V_0 4

C57

10u/10V_08

5 & 10 mils

H_VID1 28

C54

10u/10V_08

AME8804AEEY(Without RA)

C450

22u/10V_12

H_VID6 28

L40 H CB1608KF -121T25

C456

22u/10V_12

+1.5VS 6,12,16,21,29

V

C75

10u/10V_08

VCCS ENSE

C446

22u/10V_12

C444

22u/10V_12

C449

22u/10V_12

Load line slope : -2.1mV/A

10A 400MIL

+VCO RE

1K+ 1K

C49

10u/10V_08

Place these inside soc ket cav ity on L8 (South side s econdary )

+1.5 VS

IMVP6 VID TABLE

Deeper Sleep Voltage 0.748V

Normal Impedance

VSSSEN SE

H_VID4 28

H_VID3 28

VCORE_CPU 36A

For Yonah CPU

C78

10u/10V_0 8

VID[6:0], PSI#

Transmission Line Type

6 * 330uF (9mohm ESR each, 1.8nH ESL each)

3 on the north , 3 on the south

130mA

VCCSENSE 28

+VCO RE 28,29

C29

0.1u/16V_04

Pl ace th ese inside socket cavity on L1 (North side Primary)

+VCORE

+VCCP 2,4,10,15,28,29

H_VID0

+VCC P

Layout

note:

C76

10u/10V_08

C33

0.1u/1 6V_04

+VCO RE

H_VID2 28

C454

22u/10V_12

+1.5V

Near pin B26

Layout note:

C74

10u/10 V_08

H_VID1

H_VID5 28

C50

10u/10V_08

C31

0.1u/16V _04

Strip-line(Int. Layer)

C452

22u/10V_12

Place these inside socket cavity on L8 (North side secondary)

2.5A

H_VID5

VID[6..0] trace:space (4:8

or 5:10),Zo=55ohm +-15%

C453

22u/10V_12

C55

10u/10V_0 8

Place these inside socket cavity on L8 (North side secondary)

Layout note:

H_VID3

VSSSENS E 28

C56

10u/10V_08

Boost Voltage 1.2V

Layout note:

+VCC A_C PU

C476

0.01u/25V_04

R1

+3V 8,9,10,13,14,15,16,18,20,21,26,28

H_VID2

C73

10u/10V_08

+VCORE

JSKT1C

PZ47913-27 41-01

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

V6

G21

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

AD6

AF5

AE5

AF4

AE3

AF2

AE2

AF7

AE7

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

VCC[68]

VCC[69]

VCC[70]

VCC[71]

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

VCC[77]

VCC[78]

VCC[79]

VCC[80]

VCC[81]

VCC[82]

VCC[83]

VCC[84]

VCC[85]

VCC[86]

VCC[87]

VCC[88]

VCC[89]

VCC[90]

VCC[91]

VCC[92]

VCC[93]

VCC[94]

VCC[95]

VCC[96]

VCC[97]

VCC[98]

VCC[99]

VCC[ 100]

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

VCCA

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

H_VID4

C53

10u/10V_08

C72

10u/10V_08

Spacing (mils)

C445

22u/10V_12

R22

100_1%_06

IMVP IV

(+1.52V)

R2

Sheet 3 of 39

PROCESSOR 2/2

B.Schematic Diagrams

Schematic Diagrams

PROCESSOR 2/2

B - 4 PROCESSOR 2/2

Page 5

VN800 1/4

H_D#0

H_A#4

C127

10u/10V_08A

H_DSTBN#1 2

H_D#44

H_D#16

R104

20.5_1%_06

H_REQ#0

C150

10u/10V_08A

H_BPRI#2

H_D#43

C168

0.01u/25V_04

22UF M 6.3V

H_A#17

R106

49.9_1%_06

H_A#9

H_A#21

C131

0.01u/25V_04

H_A#18

H_D#41

HRCOMP

H_REQ#4

+VCC P

H_BREQ0#2

H_D#50

H_D#46

H_HITM#2

H_D#27

H_DSTBP#0 2

NEED CLOSEST N.B

H_DBI#1

HCOMPVREF

H_D#13

H_A#5

R107 49.9_1%_06

H_LOCK#2

H_D#37

U23A

VN800

D27

D26

A29

C26

C28

D28

A27

B29

A26

B26

D25

E24

A25

A28

D24

C25

K28

K29

J28

K27

J26

J29

J25

J27

F28

G29

G27

D29

E27

F27

E28

F29

E23

B24

C24

A24

A23

B23

A22

C23

F21

C22

E21

C21

D20

D21

F20

E20

B19

C19

B20

B18

C20

A20

C18

B17

B16

A17

C14

C15

A18

B15

B14

A15

Y23

E29

H26

H29

L25

L28

P25

P28

U28

U25

Y25

Y28

E26

E25

E22

B25

B28

D16

D19

A16

A19

B22

C27

H28

D23

C17

B27

G28

D22

C16

Y29

V27

AA29

Y27

Y26

AC27

AA28

AB27

AA27

AC29

AB29

AB28

AC26

AD29

T28

R28

N29

N28

P29

P27

R27

N26

T26

P26

R25

N27

N25

R29

T27

W28

R26

M29

M28

T29

K26

M25

U27

M26

L27

U29

L29

M24

W27

V28

V26

W29

V29

L26

M27

K25

C29

H27

B21

A21

D14

L24

W23

U26

T25

G25

G26

F22

G24

F19

F16

U19

T19

R19

P19

N19

M19

L19

L18

L17

L16

L15

R24

V24

AC28

N18

P18

R18

M18

T18

U18

V18

D15

K24

N24

W26

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

HCLK+

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

HDSTB0N

HDSTB1P

HDSTB2P

HDSTB3P

HDSTB0P

HDSTB1N

HDSTB2N

HDSTB3N

HA3

HA4

HA5

HA6

HA7

HA8

HA9

HA10

HA11

HA12

HA13

HA14

HA15

HA16

HA17

HA18

HA19

HA20

HA21

HA22

HA23

HA24

HA25

HA26

HA27

HA28

HA29

HA30

HA31

HADSTB0

HADSTB1

ADS

BNR

BPRI

BREQ

DBSY

DEFER

DRDY

HIT

HITM

HLOCK

HTRDY

HREQ0

HREQ1

HREQ2

HREQ3

HREQ4

RS0

RS1

RS2

HDBI0

HDBI1

HDBI2

HDBI3

CPURST

GTLVREF

HCLK-

HA32

HA33

HRCOMP

HCOMPVREF

HDVREF 0

HDVREF 1

HDVREF 2

HDVREF 3

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

HAVREF0

HAVREF1

GND

GND

GND

GND

GND

GND

GND

GND

GND

DPWR

HAP0

HAP1

C142

0.01u/25V_04

H_DBI#12

H_D#31

H_D#58

H_A#27

H_A#26

H_D#21

H_D#4

R109 49.9_1%_06

H_D#29

C86

1000p/50V_04

C88

1000p/50V_04

C87

1000p/50V_04

H_DSTBN#3 2

H_D#42

H_D#62

GTLVREF_NB1

+VCCP

H_A#11

H_D#32

H_DSTBP#1 2

H_D#59

H_A#[31:3]2

H_ADSTB#12

H_DBI#3

C162

0.01u/25V_04

H_D#61

H_A#24

H_A#20

H_A#23

H_D#39

H_D#63

H_D#45

H_A#13

H_ADS#2

H_CLK-10

H_ADSTB0#2

C144

10u/10V_08A

C84

0.1u/16V_04

H_D#12

H_A#15

C135

0.01u/25V_04

H_DSTBP#2 2

H_D#35

H_A#12

H_D#3

H_A#14

C28

0.01u/25V_04

H_A#8

H_A#31

R108 100_1%_06

+VCCP

C171

0.01u/25V_04

H_CPURST#2

H_D#14

C133

0.01u/25V_04

H_D#36

H_D#20

H_A#6

H_D#8

C146

0.01u/25V_04

H_DEFER#2

H_DSTBN#0 2

+VCCP 2, 3,10,15,28,29

H_D#34

H_DPWR#

H_DBI#0

GTLVREF_NB

+

C497

100u/6.3V_B

C132

10u/10V_08A

H_HIT#2

H_D#60

H_D#10

C129

10u/10V_08A

H_CLK+10

H_D#15

C34

0.1u/16V_04

H_DPWR#2

H_D#28

H_A#3

H_D#26

H_DBI#2

H_DSTBP#3 2

H_D#[63:0] 2

H_DBI#32

H_REQ#2

C699

10u/10V_08A

H_DBI#02

H_REQ#1

H_D#19

C141

0.01u/25V_04

C85

0.01u/25V_04

C35

1000p/50V_04

+VCC P

H_A#30

H_D#38

C156

1u/10V

H_D#2

H_D#23

+VCCP

H_D#33

H_A#10

H_D#1

H_DRDY#2

H_D#55

H_D#24

H_D#53

R105

100_1%_06

H_D#47

H_A#25

C149

0.01u/25V_04

H_D#22

C145

0.01u/25V_04

H_DBI#22

H_D#52

H_D#49

H_D#54

H_D#57

H_D#9

H_A#29

H_D#25

H_D#11

H_A#22

H_REQ#[4:0]2

GTLVREF_NB1

H_RS#22

H_ADSTB#02

H_A#7

R110

100_1%_06

H_D#51

H_BNR#2

H_D#48

H_D#18

C165

0.01u/25V_04

+VCC P

GTLVREF_NB

+VCCP

H_DSTBN#2 2

H_D#5

H_RS#02

H_RS#12

H_D#17

H_D#40

H_D#7

H_D#6

C700

10u/10V_08A

H_A#19

H_DBSY#2

H_A#28

H_D#56

H_D#30

HCOMPVREF

H_REQ#3

+VCCP

08-22611-2B1

C136

0.01u/25V_04

C159

0.01u/25V_04

H_TRDY#2

C158

0.01u/25V_04

H_A#16

Sheet 4 of 39

VN800 1/4

Schematic Diagrams

B.Schematic Diagrams

VN800 1/4 B - 5

Page 6

Schematic Diagrams

MD_3

MD_2 8

C233

0.01u/25V_04

+1.8V

MCLKIT

MD_3 6

MD_1 6

C199

1000p/50V_04

MD_3 0

BA0

-CS3 9

-SWEA 8,9

C180

1000p/50V_04

-SCASA 8,9

C269

0.01u/25V_04

DQS5 8,9

MAA0

CKEA1

R131

150_1%_06

MD_2

MAA6

-DQM18,9

MAA3

MCLK OC 10

C253

1000p/50V_04

MD_3 4

C212

0.1u/16V_04

MD_4 7

MVREF_NB

DQS3 8,9

-DQM58,9

C251

0.01u/25V_04

MD_4 9

R114 22_04

R133

150_1%_06

MCLK IT

MD_1 9

C207

1000p/50V_04

MD_4 3

MAA8

C271

10u/10V_08

C259

33p/50V_04

ODT1 8,9

-DQM68,9

MCLK OT 1 0

DQS2 8,9

MD_2 0

MD_5 4

MD_5 8

BA1

-CS1

MD_1

MD_5 9

C191

1000p/50V_04

C225

0.1u/16V_04

BA1 8,9

MD_3 8

MD_1 5

+1.8V

ODT3 9

-SCASA

-DQM28,9

MAA12

MAA1

C241

0.01u/25V_04

MD_4 6

MD_3 7

CKEA0

MD_2 6

C197

0.01u/25V_04

C193

0.01u/25V_04

M_CL KO-

MAA11

C266

10u/10V_08

-DQM78,9

DQS1 8,9

M_CL KO-

+1.8V

DMCOMP

MD_6 3

-SWEA

MD_3 9

C175

0.01u/25V_04

MVREF_NB

MD_3 3

-SRASA 8,9

MAA[0:13] 8,9

ODT2 9

MD_3 1

C265

10u/10V_08

C272

33p/50V_04

-CS2

MCLKIT = DCLKx + 2 "

DQS6 8,9

MD_1 4

MD_6 1

C248

33p/50V_04

-CS2 9

M VREF_NB:Do n't le ss than 10 m ile s

C268

0.01u/25V_04

MD_2 9

MD_6

+1.8V

M_CL KO+

-CS1

MD_2 5

MEMDE T

MD_5 1

MD_1 1

MD_2 7

MD_2 1

MD_2 2

MD_2 4

MD_9

-CS3

MD_5 7

-CS0 8,9

MD_1 7

MD_4 0

MD_4 2

+1.8V

MD_5 2

MD_5

-CS0

MAA5

C270

10u/10V_08

MD_1 8

DQS0 8,9

C267

0.01u/25V_04

CKEA39

CKEA2

MD_5 5

ODT0 8,9

C257

1000p/50V_04

C254

0.01u/25V_04

Near to NB chip,reserve for tunning!

C153

*5p/50V_04

R113 22_04

-DQM48,9

MD_5 0

-SRASA

MD_5 3

Test Point

MD_3 5

MD_2 3

R119 4.7K_06

MD_1 2

MD_1 3

HI IS DDR2

+1. 8V

U23B

VN800

AD28

AE27

AF27

AG28

AD27

AE29

AG27

AG29

AH29

AJ29

AG25

AJ25

AJ28

AH27

AH26

AJ26

AJ24

AG24

AJ22

AG21

AH24

AG23

AG22

AJ21

AH21

AJ20

AG18

AH18

AG20

AH19

AJ18

AG17

AJ12

AG12

AJ10

AJ9

AH12

AJ11

AG10

AH9

AG8

AJ7

AJ6

AH6

AG9

AJ8

AG5

AJ5

AH4

AJ4

AJ2

AH1

AG4

AF4

AG3

AJ1

AG1

AF2

AD3

AD1

AG2

AF3

AE1

AD2

AF13

AD15

AJ15

AJ16

AJ17

AF16

AG15

AE18

AF17

AE19

AJ14

AF12

AJ13

AF20

AE21

AH8

AD26

AE26

AF21

AF23

AE22

AF24

AF28

AJ27

AJ23

AJ19

AG11

AH7

AJ3

AF1

AF9

AF11

AE12

AD9

AF8

AG7

AF7

AF29

AG26

AH22

AG19

AH10

AG6

AH3

AE3

W12

W13

W14

W15

W16

W17

W18

W19

V19

M16

N16

P16

R16

T16

V16

AD23

AD17

AD11

AD8

V11

W11

M17

N17

P17

R17

T17

U17

V17

M15

N15

P15

U16

AF26

AH11

AH14

AH17

AH20

AH23

AH25

AH28

AF5

AH5

AH2

AE28

AE25

AE23

AE20

AE17

AE16

AE14

AE11

AE8

AE2

AD7

V15

U15

T15

R15

AE5

AE24

AE9

AE10

AF6

AD6

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

MA0

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

BA0

BA1

MA11

MA12

GND

MCLK I A

MCLK O-

CKE0

CKE1

CKE2

CKE3

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

SCAS

SWE

SRAS

CS0

CS1

CS2

CS3

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

VCC18MEM

VCC18MEM

VCC18MEM

VCC18MEM

VCC18MEM

VCC18MEM

VCC18MEM

VCC18MEM

VCC18MEM

GND

GND

GND

GND

GND

GND

MEMVR EF 1

MEMVR EF 2

MEMVR EF 3

MEMVR EF 4

VCC18MEM

VCC18MEM

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

MCLK O+

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

MA13

GND

GND

GND

GND

DMCOMP

MEMDE T

ODT0

ODT1

ODT2

ODT3

MD_5 6

R134 301_1%_06

C192

0.1u/16V_04

MD_4

M_CL KO+

MD_4 1

C221

0.1u/16V_04

MAA10

MAA7

-CS3

CKEA18, 9

MAA9

(Place near their respective balls of NB)

MD_6 2

C289

33p/50V_04

-CS0

CKEA29

+1.8V 6,8,9,10,27,29

MD_0

Closed U11

BA0 8,9

DQS4 8,9

MAA2

MD_7

MCLKO+/- as short as passable

-DQM38,9

MD_4 5

CKEA3

-CS2

CKEA08, 9

MD_1 0

MD_6 0

MEMDE T

MAA4

-CS1 8,9

MD_4 8

MD_[0:63]8,9

MD_8

MD_3 2

DQS7 8,9

MAA13

MCLK IT 10

-DQM08,9

MD_4 4

Sheet 5 of 39

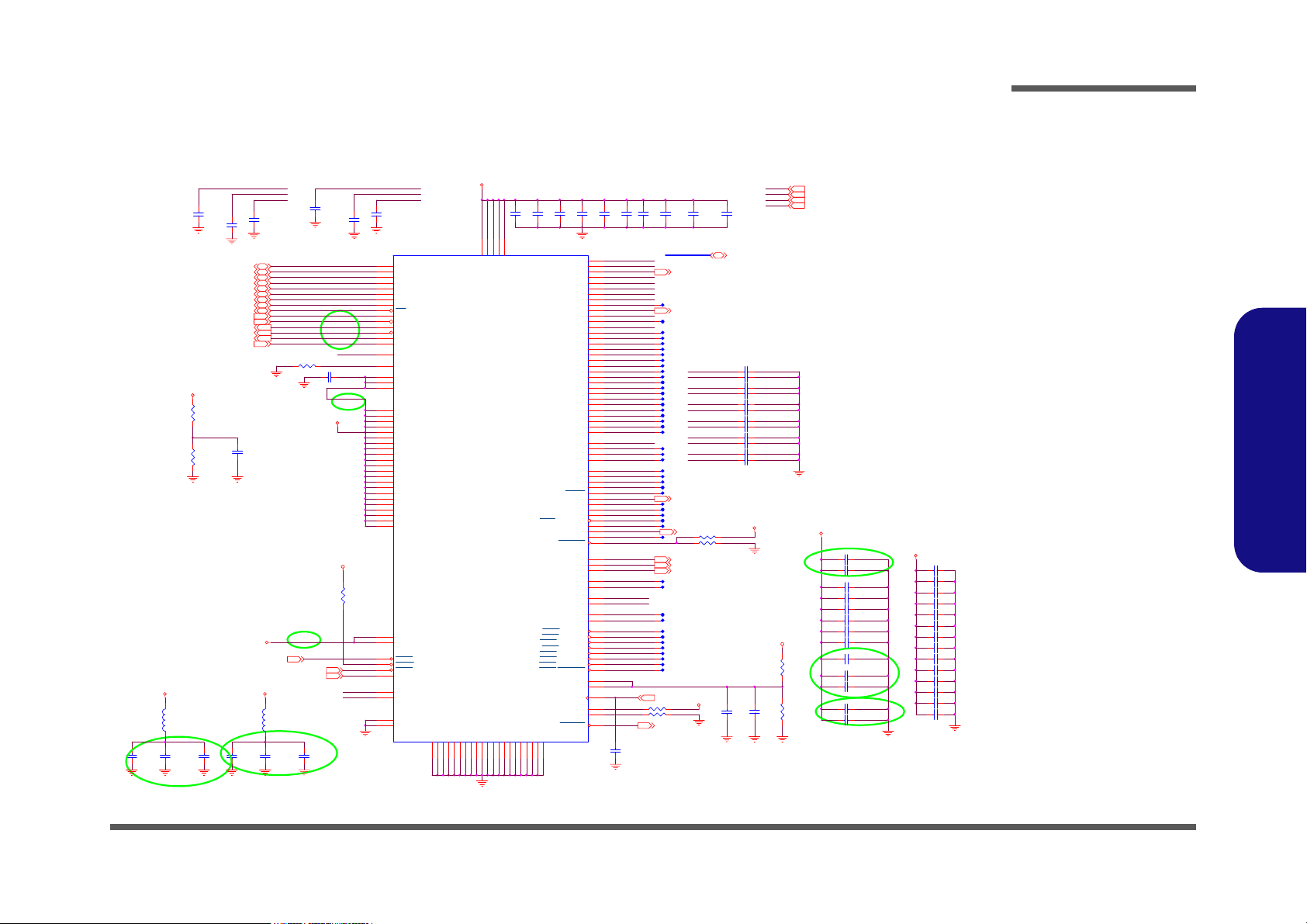

VN800 2/4

VN800 2/4

B.Schematic Diagrams

B - 6 VN800 2/4

Page 7

VN800 3/4

Sheet 6 of 39

VN800 3/4

DNCMD

FPD0

C243 0.01u/ 25V_04

R123 *4.7K_04

UPSTB15

FPVS 12

FPD10

C702 10u/10V_08A

C507 10u/10V_08A

DNCMD15

C188 0.1u/16V_04

C198 0.01u/ 25V_04

C155 10u/10V_08A

C261 *10p/50V_04

LVREF _NB is 0.625V

+3VS

ENAVEE 12

FPD4

FPD3 FPD9

+1.5 VS

FPCLK 12

C232

0.1u/16 V_04

R125

10K_1%_06

VLAD515

AVDD2

AGPCOMPP

FPD4

+1.5VS

C694

10u/10V_08

UPCMD

C502 10u/10V_08A

C260 *10p/50V_04

C161 0.1u/16V_ 04

FPD10

U23C

VN800

P3

P4

R3

R4

R1

N2

P1

R2

M3

M1

N4

L3

L1

N5

K2

R6

J2

H3

H1

K4

G1

G2

K5

G3

J6

K6

J4

F2

J5

F3

H4

E1

M2

K1

J1

L6

L4

M5

K3

J3

M4

P6

G5

F4

B3

N1

G4

N3

F1

A1

A2

B1

C3

D1

D4

D2

D3

N6

R5

P13

P14

M12

M13

M14

N12

N13

N14

D5

C4

C1

C2

E4

E3

F5

V1

U2

Y2

Y3

T2

T3

AA2

U3

W2

W1

V2

V3

AA3

W3

V4

T4

M11

N11

P11

R11

T11

AA1

AA26

AD24

AB1

R12

P12

AB3

AF25

AC1

AB2

Y14

Y16

Y18

Y20

L10

N10

R10

W10

AA25

AD25

H6

C5

G6

A3

T14

U12

T13

R13

R14

T12

Y10

Y12

M20

P20

T20

V20

K19

K17

K15

K13

K12

K20

U11

U10

V10

U13

U14

V12

V13

V14

M6

T1

K11

K10

AC25

A4

GD0/FPD10

GD1/FPD11

GD2/FP 1CLK

GD3/FPD09

GD4/FPD08

GD5/FPD07

GD6/FPD06

GD7FPD 05

GD8/FP 1DET

GD9/F P1HS

GD10/FPD01

GD11/FPD23

GD12/FPD00

GD13/FPD22

GD14/FPD21

GD15/FPD20

GD16/FPD18

GD17/FPD17

GD18/FPD16

GD19/F PDE

GD20/FPD14

GD21/FPCLK

GD22/FPD13

GD23/FPD15

GD24/G DVP1D09

GD25

GD26/G DVP1D10

GD27/G DVP1D04

GD28/G DVP1D07

GD29/G DVP1D06

GD30/G DVP1D08

GD31/GDVP1DET

GC#BE0/ FPD 03

GC#BE1/SBP LDAT

GC#BE2/ FPD 19

GC#BE3/GDVP1D11

GFRAME/FPHS

GIRDY /SBPLCLK

GTRDY

GDEVSEL/FPVS

GSTOP/FP1CLK

GPAR/FP1VS

GDBIH

GRBF

GWBF/FPCLK

GADSTBF0/FPD04

GADSTBF1/FPD12

GADSTBS0/ FPD 02

GADSTBS1/FPDET

GSBA0/GDVP1VS

GSBA1/GDVP1DE

GSBA2/GD VP1D00

GSBA3/GDVP1HS

GSBA4/GD VP1D05

GSBA5/GD VP1D03

GSBA6/G DVP1C LK

GSBA7/G DVP1C LK

AGPVREF1

GCLK

GND

GND

GND

GND

GND

GND

GND

GND

GREQ/SBDDCCLK

GGNT/SBDDCDAT

GSBSTBF/GDVP1D01

GSBSTBS/GDVP1D02

GST0/ENAVEE

GST1/ENAVDD

GST2/ENABLT

VD0

VD1

VD2

VD3

VD4

VD5

VD6

VBE

UPSTB+

UPSTBDNSTB+

DNSTBUPCMD

DNCMD

VLVREF

VLCOMPP

VCC15AG P

VCC15AGP

VCC15AG P

VCC15AGP

VCC15AG P

VD7

GNDAHCK

GNDAMCK

VSUS15

GND

GND

SUSST

TESTI N

RESET

PWROK

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCCA33HCK

VCCA33MCK

GDBIL

AGP8XDET

AGPVREF2

AGPCOMPP

GND

GND

GND

GND

GND

GND

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15

VCC15VL

VCC15VL

VCC15VL

GND

GND

GND

GND

GND

GSERR/FP1DE

AGPBUSY

VCC15

VCC15

VSUS15

AGPCOMPN

C250 0.01u/ 25V_04

R132 402_1%_06

C695

10u/10V_08

AVDD1

C224 0. 1u/16V_04

+3VS

FPD7

Closed U11

UPCMD15

VLAD4

C526

*10p/5 0V_04

VLAD115

FPD11

C504

0.1u/16V _04

VLAD615

DNCMD

C263 *10p/50V_04

C286 *10p/50V_04

FPD8

C167 0.1u/16V_ 04

C244

*5p/50V _04

+1.5VS

AVDD1

SUS_ST#14

FPDE

FPD1

AGP8xdet 0=enable

BLON 2 1

+1.5 VS

PWROK_NB#14

VLAD1

C170 0.1u/16V_04

C215

0.1u/16 V_04

VLAD6

C216

10u/10V_08

AGPCOMPN

C258

0.1u/16 V_04

R124

10K_1%_06

FPD11

C148 0.1u/16V_04

UPSTB#

+1.5V

VLAD715

R116

1K_04

C262 *10p/50V_04

+1.8V

C275 *10p/50V_04

FPD3

ENAVD D 11

DNSTB

C249 0.01u/ 25V_04

FPD7

C505

0.1u/1 6V_04

C255 *10p/50V_04

Strapping For NB_TEST Mode

TESTIN RBF WBF

1 x x

Disable all TEST mode

C202

0.1u/16V _04

VBE#

UPSTB#15

C223

0.1u/ 16V_04

C226 0.01u/ 25V_04

C247 *10p/50V_04

DNSTB#15

FPCLK_N

C264 *10p/50V_04

C237 0.1u/16V_04

Reserve for Future

VLAD315

C152 0.1u/16V_ 04

VLAD215

C528

*10p/50V_04

LCOMPP

C185 0.1u/16V_ 04

+1.8V 5 ,8,9,1 0,27,29

UPSTB

FPD6

VLAD7

VBE#15

C529

*10p/50 V_04

C172 0.01u/ 25V_04

+1.5VS

+1.5VS 3, 12,16, 21,29

C506

0.1u/1 6V_04

C238 0.1u/16V_ 04

FPHS 12

C157 0.1u/16V_04

C701 10u/10V_08A

GCLK_NB 10

LVREF_NB

FPD2

+1.5V S

C210

0.1u/16 V_04

FPD6

C203

0.01u/ 25V_04

C222

1000p/50V_04

L13

HCB1608 KF-121T25

R130

442_1%_04

C530

*10p/5 0V_04

L14

HCB1608KF-121T25

VLAD0

C211 0.01u/ 25V_04

C163

10u/10V_08

C166 0.01u/ 25V_04

+3VS 2,7, 8,10, 11,12,13, 14,15, 16,17,19 ,21,22, 24,25,2 6,28,29

DNSTB#

C246 *10p/50V_04

C151

10u/10V_08

C160

10u/10V_08

VLAD2

R120 4.7K_04

FPDE 12

C531

*10p/50V_04

C208

0.01u/25V_04

UPSTB#

FPD[0. .11]

TESTI N _N B

UPSTB

DNSTB#

C242 0.01u/ 25V_04

+1.5V 29

VLAD3

+1.5VS

FPD1

R129

619_1%_06

C273 *10p/50V_04

FPD[0..11] 12

DNSTB

C527

*10p/50V_04

AGP8XDET#

C252 10u/10V_08A

FPD5

C179 0.1u/16V_04

VLAD015

C256 *10p/50V_04

FPD9

AGPVREF 1

For EMI.

DNSTB15

AVDD2

FPD0

LVREF_NB

R126 60.4 _1%_06

VLAD415

FPD2

FPD8

FPD5

C176

10u/10V_08

AGPBZ 15

6-13-61901-26C

+1.5V S

VLAD5

RESET_NB#13

C703 10u/10V_08A

UPCMD

R122 60.4 _1%_06

Schematic Diagrams

B.Schematic Diagrams

VN800 3/4 B - 7

Page 8

Schematic Diagrams

Sheet 7 of 39

VN800 4/4

DISPCLKO 12

M9

M-MAR K 1

M12

M-MAR K1

EP4

SMD79X197R

TVD7

DISPCLKI

H7

H7_5D2_8

VCCDAC2

C169

22p/50V

1: One 24-bit Panel interface

R365

*4.7K_04

0: External AGP

SW3_3 DVP0D6/TVD6 =>Dedicate d TVD Port Selection

GUICL K

R111

4.7K_04

ID1

C177

0.1u/16V_04

EP1

SMD79X197R

TVD6

1

H15

MTH296D111

2

3

4

5 6

7

8

9

VCCPLL1

VCCPLL2

H8

C296D185N

DAC_GREEN 21

TVD4

R363

4.7K_04

0: Disable

M7

M-MAR K1

H3

C237D83

0: Disable

TVD9

L22

HCB1608KF-121T25

TVD8

R362

4.7K_04

M10

M-MARK1

+3VS

LCDID311

AR

C187

0.1u/16V_04

0: TMDS

+3VS

H20

C158D158

1: TV Encoder

M6

M-MAR K1

U23D

VN800

D6

E6

B7

C6

A9

B6

A5

B5

A6

B8

A8

E11

C11

C10

E10

D11

B10

A10

A7

D9

E9

D10

E8

E7D7D8

C7

L13

L12

C13

B13

A13

D13

E13

D12

C12

A12

B12

E12

B11

A11

B4E2E5H2H5L2L5P2P5U1U4

Y1

B2

A14

C8

C9

L14

B9

GNDADAC2

GNDADAC1

GNDAPLL1

GNDAPLL2

INTA

AR

AG

AB

RSET

HSYNC

VSYNC

GPO0

GPOUT

DVP0VS/TVVS

DVP0HS/TVHS

DVP0CLK/TVCL K

DVP0DE/TVDE

TVCLK R

XIN

SPCLK1

SPCLK2

SPD1

SPD2

VCCA33DAC1

VCCA33DAC 2

VCCA33PLL1

VCCA33PLL2

VCC33GFX

VCC33GFX

DVP0D00/ TVD00

DVP0D01/ TVD01

DVP0D02/ TVD02

DVP0D03/ TVD03

DVP0D04/ TVD04

DVP0D05/ TVD05

DVP0D06/ TVD06

DVP0D07/ TVD07

DVP0D08/ TVD08

DVP0D09/ TVD09

DVP0D10/ TVD10

DVP0D11/ TVD11

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

DISPCLKI

DISPCLKO

VCC33GFX

DVP0DET

R112 4.7K_04

R364 4.7K_04

0: Inte rnal GFX PLL

SW3_1 DVP0D4/TVD4 =>AGP Port M uxing

L23

HCB1608KF-121T25

C201

1000p/50V_04

L20 BK1608HS121

1 2

M5

M-MAR K1

1

H6

MTH296D111

2

3

4

5 6

7

8

9

H2

C158D158

M14

M-MAR K1

R367

4.7K_04

H23

C355B158D158

1

H12

C296D111N

2

3

4

5 6

7

8

9

1

H19

MTH296D111

2

3

4

5 6

7

8

9

Trace wi dth = 10 m ils

VCCDAC1

H16

C67D67

This pin needs to be connected to GND, if spread

spectrum is not implemented.

EP5

SMD118X197R

C173

22p/50V

C178

22p/50V

+3VS

R563 4.7K_04

TVD10

ID2

M2

M-MAR K 1

L15

HCB1608KF-121T25

TVD9

C219

1000p/50V_04

VCCDAC1

EP2

SMD79X197R

DVP0D7/TVD7 =>GFX Clock Sele ct(VCK/LCDCK/ECK)

C196

1000p/50V_04

TVD10

1

H18

C296D111N

2

3

4

5 6

7

8

9

DISPCLKO

EP3

SMD79X197R

+3VS

ID3

DAC_HSYNC 21

1

H11

C296D111N

2

3

4

5 6

7

8

9

R534

4.7K_04

TVD8

0: From NB

+3VS

H1

C158D158

SMBCK2 11

DAC_BLUE 21

LCDID011

M11

M-MAR K1

H10

C236D106

AG

R562 *4.7K_04

1

H17

MTH296D111

2

3

4

5 6

7

8

9

DISPCLKI 12

VT1637GPOUT

H14

C236D106

C200

0.1u/16V_04

GFX power up strapping setting:

TVD6

[Kee p 1 as option,for Debug purpos e]

C189

0.1u/16V_04

H22

C355B158D158

LVDS_DUAL11,12

VCCPLL1

LCDID111

DAC_RED 21

R121 80.6_1%_06

DAC_DDCACLK 21

0: Two 12-bit FPD interface

TVD5

VCCPLL2

H13

C236D106

1: From External

Closed U11

C213

0.1u/16V_04

H24

C355B158D158

TVD5

M13

M-MARK1

1

H5

C355CH512B296D111N

2

3

4

5 6

7

8

9

C228

0.1u/16V_04

M8

M-MAR K1

SW3_2 DVP0D5/TVD5 =>Dedicated DVI Port Co nfigur ation

LCDID211

AB

1: From External

L19 BK1608HS121

1 2

+3VS 2,6,8,10,11, 12,13,14,15,16, 17,19,21,22,24,25, 26,28,29

M1

M-MAR K1

GUICL K 10

1

H4

C355CH512B296D111N

2

3

4

5 6

7

8

9

C205

1000p/50V_04

1: Enable

For EMI

R368 4.7K_04

M3

M-MAR K1

R115 *4.7K_04

PCI_IN TA# 13,24

VCCDAC2

TVD4

SW3_4 DVP0D8/TVD8 =>Extern al AGP Function Enable

H21

C158D158

R535 *4.7K_04

SMBDT2 11

VT1637-GPO0

R361 *4.7K_04

1: Internal AGP

DAC_DDCADATA 21

DVP0D10/TVD10 =>CPUCK/MCK Clock Se lect

TVD7

R117

4.7K_04

SW3_5 DVP0D9/TVD9 =>PCI Signal Te st Outpu t Enable

RSET

R360 *4.7K_04

R372 22_04

L18 BK1608HS121

1 2

M4

M-MAR K1

+3VS

DAC_VSYNC 21

TVD11

L16

HCB1608KF-121T25

1: Enable

+3VS

TVD11

H9

H6_0D2_3

R575 Place near to NB

VN800 4/4

B.Schematic Diagrams

B - 8 VN800 4/4

Page 9

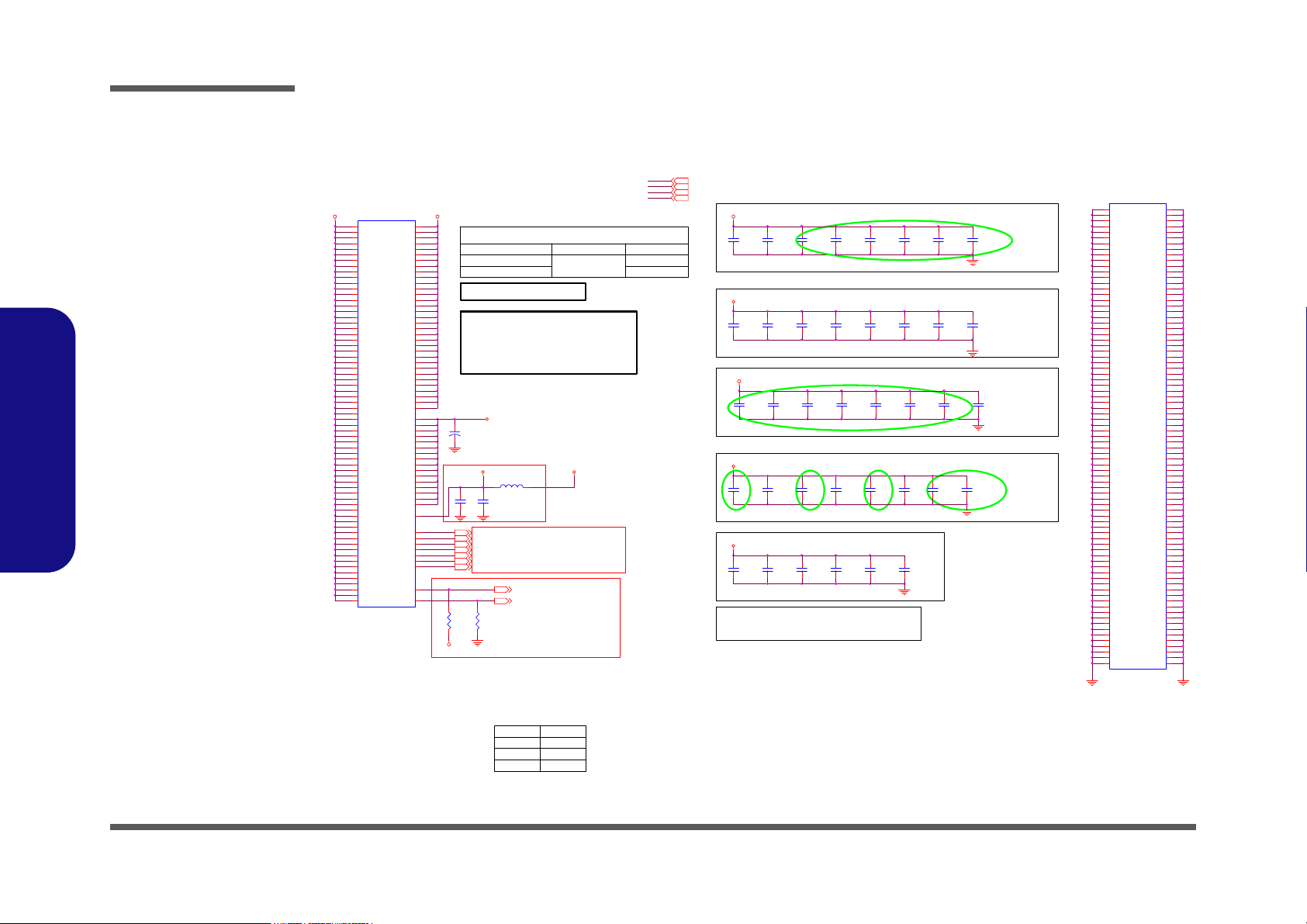

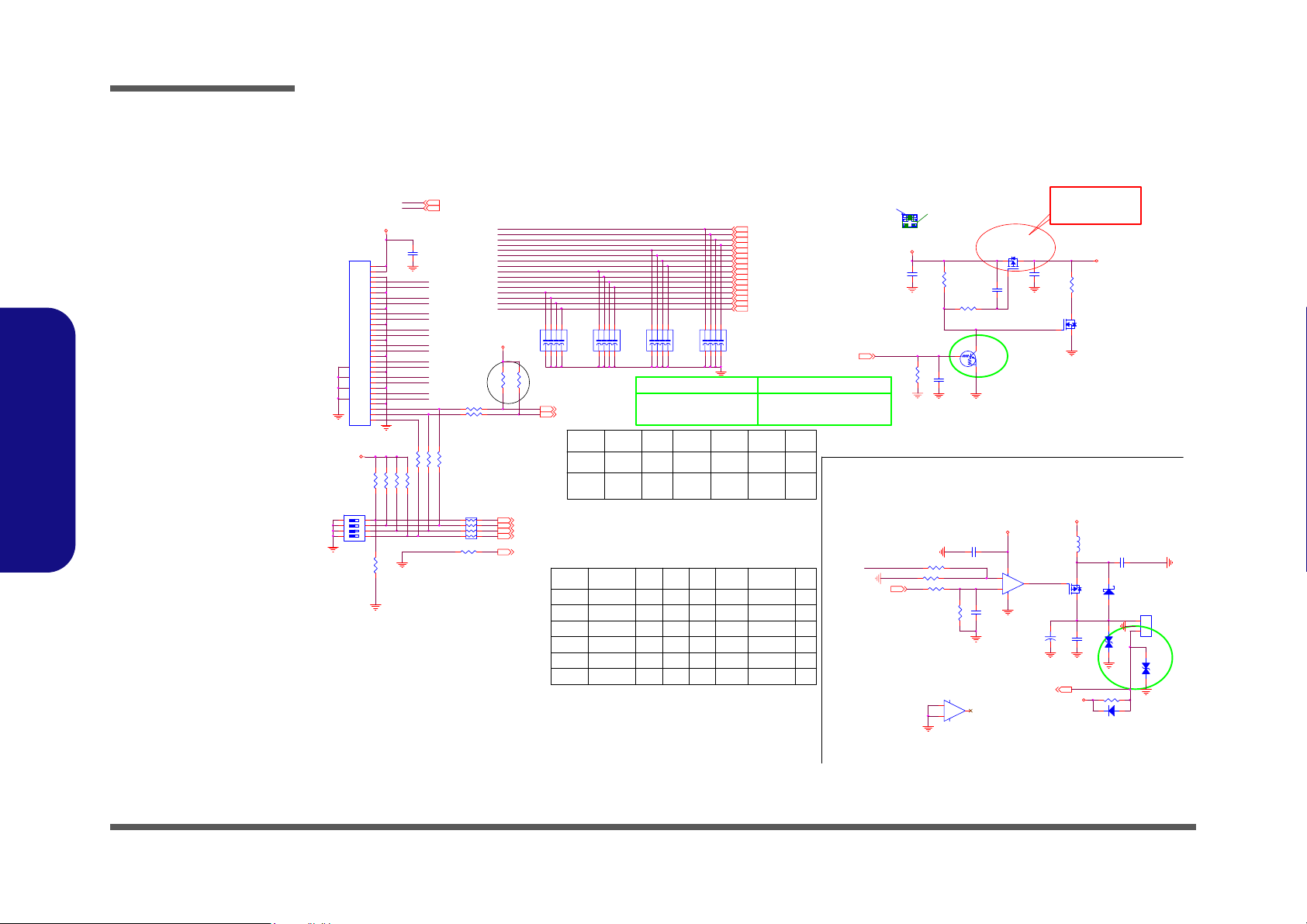

DDR2-1

Sheet 8 of 39

DDR2-1

DCLK1-10

+1.8V

-CS05,9

MD_60

CKEA05,9

DQS65,9

MAA1 2

C293 0.1u/ 16V_04

MD_25

MD_0

D8

BAV99

C

AC

A

MD_30

SMB_SBCLK9,10,1 4,16

MD_36

-DQM1

CKEA15,9

MVREF_DIM1

-DQM3

+

C339 150u/4V_B

MD_59

+3V

SMB_SBDATA9,10,1 4,16

MAA8

MAA1 1

MD_15

MD_51

VDDSPD

MD_31

C190 0.1u/ 16V_04

MD_42

-SCAS A5,9

-DQM25,9

MAA1

MAA5

MAA6

MD_12

MAA4

C302 0.1u/ 16V_04

CN1

DDR SODIMM AAA-DDR-016-001

102

101

100

99

98

97

94

92

93

91

105

90

89

116

107

106

85

110

115

10

26

52

67

130

147

170

185

109

113

108

79

80

30

32

164

166

13

11

31

29

51

49

70

68

131

129

148

146

169

167

188

186

195

197

198

200

1

199

114

119

2

3

8

9

12

15

18

21

24

818795828896103

111

117

104

112

118

5069838486

120

163

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

168

171

172

177

178

183

184

187

190

193

196

2728333439404142474853545960656671727778121

122

127

128

132

133

138

139

144

145

149

150

155

156

161

162

165

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

BA0

BA1

BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

DQS0

DQS0

DQS1

DQS1

DQS2

DQS2

DQS3

DQS3

DQS4

DQS4

DQS5

DQS5

DQS6

DQS6

DQS7

DQS7

SDA

SCL

SA0

SA1

VREF

VDDSPD

ODT0

ODT1

GND

GND

GND

GND

GND

GND

GND

GND

GND

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

NC1

NC2

NC3

NC4

NC5

NC6

NC/TEST

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

MD_20

C301 0.1u/ 16V_04

-SRAS A5,9

-DQM2

MVREF_DIM1

MD_56

MD_54

MD_53

DCLK0+

MD_9

MD_10

C278 0.1u/ 16V_04

-DQM7

ODT05,9

-DQM65,9

MD_62

MD_21

MD_4

C217 0.1u/ 16V_04

D12

BAV99

C

AC

A

MD_1

DCLK0+10

-DQM6

DQS45,9

-DQM5

R147

75_1%_06

+3VS 2,6 ,7,10, 11,12,1 3,14,15, 16,17,19, 21,22, 24,25,26, 28,29

MD_40

MD_29

C307

2.7p/ 50V_04

MD_19

MD_49

MD_23

MD_6

C277 1000p/50V_04

MD_2

C691 10u/10V _08

MAA[ 0 : 1 3]5,9

C282 0.1u/ 16V_04

R149 10K_04

MAA2

MD_22

DCLK0-

C296 0.1u/ 16V_04

C539 0.1u/ 16V_04

MD_43

+1.8V 5,6,9,10,27,29

MD_38

C283 0.1u/ 16V_04

C280 0.1u/ 16V_04

MD_46

-DQM75,9

-DQM55,9

R150 10K_04

MD_61

20Mils

MD_[0: 63] 5,9

-DQM0

+

C713 150u/4V_B

C274 10u/10V _08

DCLK1+10

MD_5

C279 0.1u/ 16V_04

DQS75,9

+

C714 150u/4V_B

MAA3

BA15,9

MD_13

MD_44

C184 0.1u/ 16V_04

C291

0.1u/16V _04

C281 0.1u/ 16V_04

C284 0.1u/ 16V_04

+3V

MD_24

C711 10u/10V _08

+3V 9, 10,13,14, 15,16,1 8,20,21, 26,28

DCLK0-10

C295 0.1u/ 16V_04

-CS15,9

MD_16

MAA1 3

MD_58

MD_3

-DQM4

DCLK1-

Closed to CN2.

DQS35,9

MAA1 0

-SWEA5,9

C229 0.1u/ 16V_04

MD_35

MD_34

MD_52

MD_11

D5 SCS7 51V-40

A C

+1.8V

BA05,9

MD_26

MAA9

R145

75_1%_06

MD_41

MD_18

MD_45

MD_63

MD_57

Close d to SODI MM

+3VS

MD_50

MD_7

+1.8V

MD_48

C308 0.1u/ 16V_04

DQS55,9

MAA0

MAA7

C245 0.1u/ 16V_04

-DQM35,9

MD_55

MD_17

DCLK1+

MD_37

C304

2.7p/ 50V_04

C712 10u/10V _08

MD_39

-DQM45,9

MD_47

MD_8

MD_32

C540 0.1u/ 16V_04

ODT15,9

MD_28

MD_33

DQS15,9

DQS25,9

C297 0.1u/ 16V_04

DQS05,9

-DQM05,9

MD_27

MD_14

-DQM15,9

Schematic Diagrams

DDR2-1 B - 9

B.Schematic Diagrams

Page 10

Sheet 9 of 39

DDR2-2

-DQM05,8

MD_4

C306 0.1u/16V_04

-DQM35,8

MD_36

MAA9

R154

75_1%_06

DCLK3+10

MD_6

MAA5

ODT35

DCLK2-

MAA9

VDDSPD

MD_21

C519 0.1u/16V_04

C538 0.1u/16V_04

-CS35

MAA6

+VTT_M EM 2 7

MD_55

C557 0.1u/16V_04

RN26

47_04_8P4R

8 1

7 2

653

4

R153

75_1%_06

CKEA25

C558 0.1u/16V_04

MD_22

MD_44

C537 0.1u/16V_04

MD_14

MD_49

MD_25

BA05,8

MAA2

MAA0

MD_34

MD_56

C555 0.1u/16V_04

MAA1 3

C522 0.1u/ 16V_04

DCLK3-

RN27

47_04_8P4R

8 1

7 2

653

4

ODT05,8

BA05, 8

MD_11

C543 0.1u/16V_04

MD_16

MD_62

C317

2.7p/50V_04

MD_28

MD_13

-DQM7

MD_5

C523 0.1u/16V_04

MAA4

MD_53

R165 10K_04

-DQM65,8

DQS35,8

MAA7

MD_59

MD_31

RN29

47_04_8P4R

8 1

7 2

653

4

-SRASA5,8

+1.8V

SMB_SBDATA8, 10,14,16

MD_54

MD_7

MD_39

MAA6

+3V

-DQM55,8

MAA1 2

MAA8

MAA10

MD_38

C556 0.1u/16V_04

DQS05,8

R166 10K_04

MAA[ 0: 13 ]5, 8

-DQM25,8

DQS45,8

MAA3

-SRASA5,8

MD_29

MAA2

-SWEA5,8

MD_2

MD_60

MD_63

DQS75,8

MD_47

MD_17

CKEA15,8

CN2

*DDR SODIMM AAA -DDR-014-001

102

101

100

99

98

97

94

92

93

91

105

90

89

116

107

106

85

110

115

10

26

52

67

130

147

170

185

109

113

108

79

80

30

32

164

166

13

11

31

29

51

49

70

68

131

129

148

146

169

167

188

186

195

197

198

200

1

199

114

119

2

3

8

9

12

15

18

21

24

818795828896103

111

117

104

112

118

5069838486

120

163

5

7

17

19

4

6

14

16

23

25

35

37

20

22

36

38

43

45

55

57

44

46

56

58

61

63

73

75

62

64

74

76

123

125

135

137

124

126

134

136

141

143

151

153

140

142

152

154

157

159

173

175

158

160

174

176

179

181

189

191

180

182

192

194

168

171

172

177

178

183

184

187

190

193

196

2728333439404142474853545960656671727778121

122

127

128

132

133

138

139

144

145

149

150

155

156

161

162

165

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

BA0

BA1

BA2

CS0

CS1

DQM0

DQM1

DQM2

DQM3

DQM4

DQM5

DQM6

DQM7

WE

CAS

RAS

CKE0

CKE1

CK0

CK0

CK1

CK1

DQS0

DQS0

DQS1

DQS1

DQS2

DQS2

DQS3

DQS3

DQS4

DQS4

DQS5

DQS5

DQS6

DQS6

DQS7

DQS7

SDA

SCL

SA0

SA1

VREF

VDDSPD

ODT0

ODT1

GND

GND

GND

GND

GND

GND

GND

GND

GND

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

NC1

NC2

NC3

NC4

NC5

NC6

NC/TEST

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

MD_8

-CS25

DQS65,8

-CS35

ODT25

MD_20

+1.8V 5,6,8,10,27,29

MD_9

MAA3

MD_37

MAA0

MD_58

C520 0.01u/25V_04

C299 1000p/50V_04

CKEA35

MD_57

MD_15

-DQM4

MD_1

MAA1

MD_48

-DQM0

MAA1 3

-CS15,8

MD_61

C303 0.1u/16V_04

MD_27

MD_12

C300 0.1u/16V_04

MAA1 2

C305 0.1u/16V_04

DQS25,8

MD_42

MD_26

DCLK2+

BA15,8

-SCASA5,8

RN33

47_04_8P4R

8 1

7 2

653

4

-DQM1

DCLK2+10

+3V 8,10,13,14 ,15,16,18,2 0,21,26,28

DCLK3+

+VTT_MEM

MD_33

C521 0.01u/ 25V_04

C544 0.1u/16V_04

MAA4

MAA1

RN32

47_04_8P4R

8 1

7 2

653

4

MD_18

MAA5

-DQM75,8

SMB_SBCLK8, 10,14,16

-CS05,8

BA15, 8

C298 0.1u/16V_04

C542 0.1u/16V_04

MD_[0:63] 5,8

MD_32

-DQM5

MVREF_DIM2

MAA1 0

Bruce 5/08

MAA8

MD_10

MAA7

MD_40

+1.8V

-DQM6

-DQM2

DQS55,8

MD_43

+

C548 *150u/4V_B

CKEA25

MD_19

DCLK3-10

C545 0.1u/16V_04

RN34

47_04_8P4R

8 1

7 2

653

4

C547

2.7p/50V_04

RN35

47_04_8P4R

8 1

7 2

653

4

20Mils

MD_3

ODT35

MD_46

MD_52

MVREF_DIM2

-DQM3

-SCASA5,8

MAA1 1

-CS25

MD_50

CKEA05,8

-DQM45,8

RN28

47_04_8P4R

8 1

7 2

653

4

MD_45

CKEA35

-SWEA5,8

MD_0

C292 0.1u/16V_04

DCLK2-10

MAA1 1

MD_41

C554 0.1u/16V_04

+1.8V

MD_51

MD_30

Clo sed to SOD IM M

-DQM15,8

MD_35

ODT25

MD_24

MD_23

C541 0.1u/16V_04

C309

0.1u/16V_04

DQS15,8

ODT15,8

B.Schematic Diagrams

Schematic Diagrams

B - 10 DDR2-2

DDR2-2

Page 11

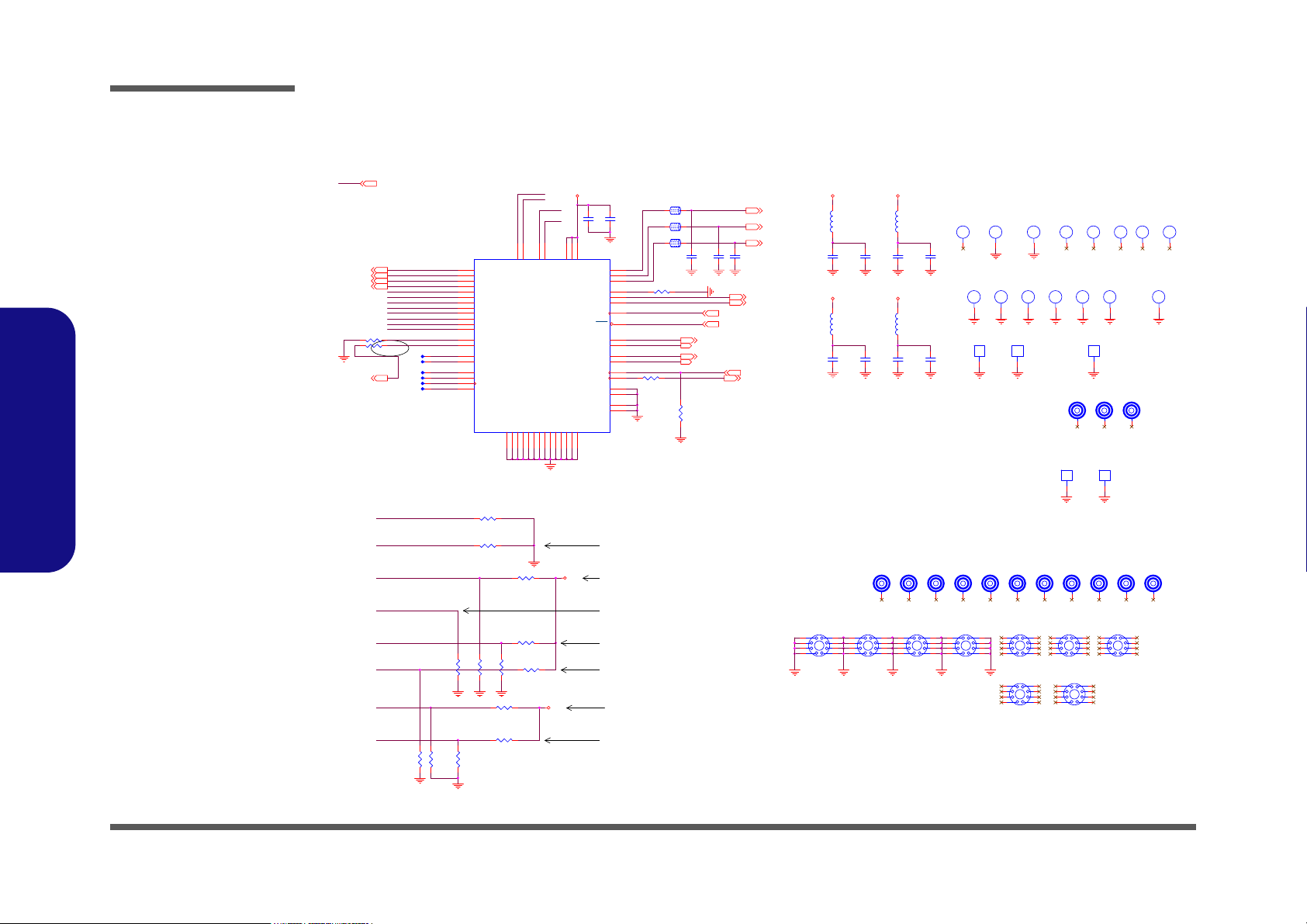

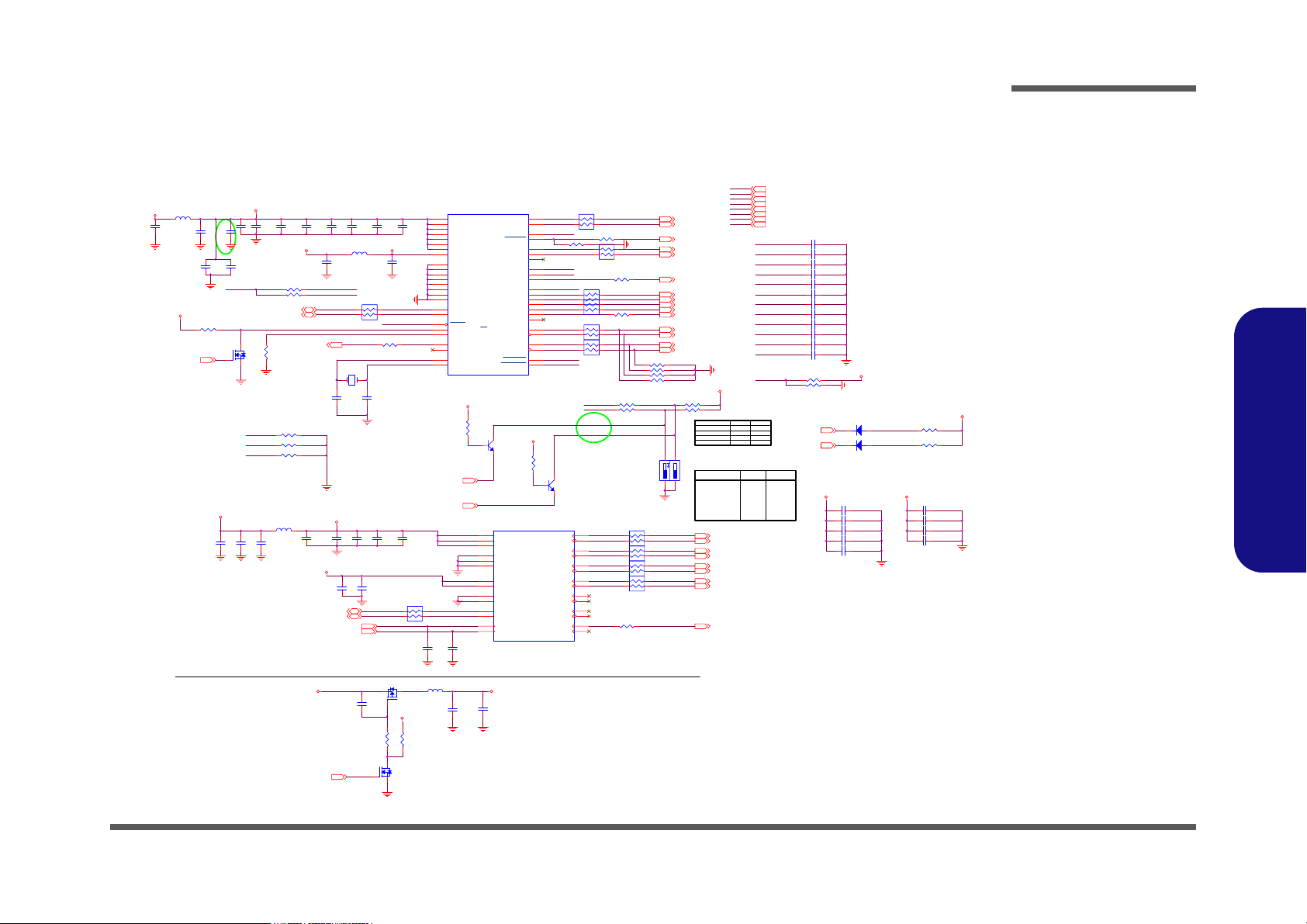

CLOCK GENERATOR, CCD

Sheet 10 of 39

CLOCK

GENERATOR, CCD

C41 0.1u/16V_04

C214

0.01u/25V_04

FS0

C209

10u/10V_08

C44

0.01u/ 25V_04

H_CLK- 4

DK1-

DK2-

C37

0.01u/25V_04

+3VS

DK0+

48mils

133

+2.5V S

C97

0.1u/1 6V_04

R48 51_1%_06

L4 HCB2012KF-500T40

C182

0.01u /25V_04

C114 10p/50V_04

C96

0.01u/ 25V_04

L

1

USB_CLK 13

RN16 0_04_4P 2R

1 4

2 3

CPU_BSEL02

C231 0.1u/16V_04

48mi ls

ON

DK3-

Change 10pf to 27pf.

RN12 22_04_4P2R

1 4

2 3

+1.8V

DCLK2- 9

C239

0.01u/25V_04

100

3V66_0

L1

HCB2012KF-500T40

SATA25MHZ

R51 51_1%_06

C24 0.1u/16V_04

RN6

33_04_ 4P2R

14

23

YONAH

PCLK_MPCI

C23

10u/10V_08

C43

0.01u/ 25V_04

C123 0.1u/16V_04

+1.8V

CLK_PWRGD

C115 10p/50V_04

2

DK2+

C113 10p/50V_04

C111 10p/50V_04

RN11

22_04_4 P2R

1 4

2 3

SATA25MHZ

Q22

2N3904

B

E C

RN9

22_04_4P2R

1 4

2 3

C69

0.1u/16V_04

L3

HCB2 012KF -500T40

OFF

C117 10p/50V_04

R87 *1K_04

AUTOS0

RN5

33_04_ 4P2R

14

23

RN8

22_04_4P2R

14

23

ON

+VCCP 2,3,4,15,28,29

R57 22_04

R15

100K_04

+3VS

R81 22_04

H

133

C99

0.01u/25V_04

FS1

VLINKCLK 15

CLK_RESET

C220

0.1u/16V_04

R92 10K_04

FS3

GUI CLK

R80 10K_04

+2.5VS

+1.8VBFR

Q19

2N39 04

B

E C

166

CLK_PWRGD

L17 HCB2012KF-500T40

R53 4.7K_04

GCLK _NB

-CPU_STOP

C122 0.1u/16V_04

C36 10p/50V_04

CPU

+VCC P

KBC_PCLK 20

+5VS 11,14,16,17,19,20,21,22,23,25,26

C110 10p/50V_04

R45 10K_04

SB_OSCCLK 14

+1.8VBFR

PCLK_PCM 24

GUICLK 7

CLK_CPU_BCLK# 2

USB_CLK

C235 0.1u/16V_04

C8

10u/10 V_08

100

+3VS

C227

10u/ 10V_08

C112 10p/50V_04

D2 1SS355

AC

R83 10K_04

U5

ICS952906FLF-T

48

24

10

17

34

6

11

18

23

28

37

43

47

4

5

32

31

30

2

21

22

29

26

25

7

8

42

27

40

3

3933

3846

41

9

12

13

14

15

16

19

20

1

45

44

36

35

VDDA

VDD48

VDDPCI1

VDDPCI2

VDD

GND

GND

GND

GND

GND

GND

GND

GND

X1

X2

SDATA

SCLK

RESET

REF1/FS0

48MHZ/ FS3

24_48MHZ /SE L24_48

3V66_0

3V66_1

3V66_2

PCI_F0/FS2

PCI_F1/FS4

CPUCLKT1

VDD3V66

VDDCPU

VDDREF

CPUCLKT0VTT_PWRGD/PD

CPUCLKC0IREF

CPUCLKC1

PCI_F 2

MODE/PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

PCICLK6

REF0/FS1

CPUCLKT_ITP/PCI_STOP

CPUCLKC_ITP/CPU_STOP

25Mhz_0

25Mhz_1

DK3+

HCLK-_

C59

10u/10 V_08

C206

0.01u/25V_04

OFF

SMB_SBDATA8,9,14,16

HCLK+_

CLOCK GENERATOR

H

+3VS 2 ,6,7, 8,11,1 2,13, 14,15, 16,17, 19,2 1,22,2 4,25,2 6,28, 29

Q3

2N7002

G

DS

C26 0.1u/16V_04

-CPU _STOP

R94

10K_04

CPU_BSEL12

SEL24_ 48

C236 0.1u/16V_04

R38 10K_04

U7

ICS9P936FLF-T

10

21

27

1

9

28

2

16

15

3

12

5

7

13

18

20

24

6

8

14

17

19

23

11

26

25

4

22

VDD2.5/1.8-0

VDD2.5/1.8-1

VDD2.5/1.8-2

AVDD2.5-0

GND

GND

AGND

SDATA

SCLK

BUF_INT

FB_OUTC

DDRT0

DDRT1

DDRT2

DDRT3

DDRT4

DDRT5

DDRC0

DDRC1

DDRC2

DDRC3

DDRC4

DDRC5

FB_OUTT

AVDD2.5-1

AGND

BUF_INC

GND

RN15 22_04_4P2R

1 4

2 3

RN14 22_04_4P2R

14

23

+3.3VCLK

C194

4.7u/10V_08

+3.3VCLK

+VCC_CCD

CLK_ RESET

R84 1K_04

DCLK3- 9

RESERVED

SMB_SBDATA8,9,14 ,16

DCLK0- 8

R91 1K_04

C7

0.1u/16V_04

R77 22_04

RESERVED

C38 10p/50V_04

C181

0.01u/ 25V_04

PCISTOP#14

FS2

OFF

+VCC_CCD 21

+3V 8,9,13,14,15,16,18,20,21,26,28

FS0

PCLK_LPC 19

GCLK_NB 6

X2

14.318 MHz

1 2

R88

10K_04

DCLK3+ 9

PCLK_LPC

H

3V66_1

ON

C116 10p/50V_04

C81

10u/10V_08

FS2

C230 0.1u/16V_04

+1.8V 5,6,8,9,27,29

FS4

Q2

NDS352AP-NL

G

DS

ON

DCLK1- 8

FROM H8 def HI

DCLK2+ 9

R75 22_04

C234

0.01u/25V_04

CCD_EN20

FS1

L

MCL KI T 5

RN7 0_04_4P2R

1 4

2 3

R79 1K_04

C39 10p/50V_04

C100

0.01u/25V_04

200

+3.3 VCL K 26

CCD

POWER

PCLK_PCM

R50 51_1%_06

Q12

2N7002

G

DS

33

PCISBCLK 15

CPUCLK-__

DK1+

C47

0.01u/25V_04

R55

475_1%_06

PCIS BCLK

C91

27p/50V_06

MODE

AUTOS1

RN10

22_04_4P2R