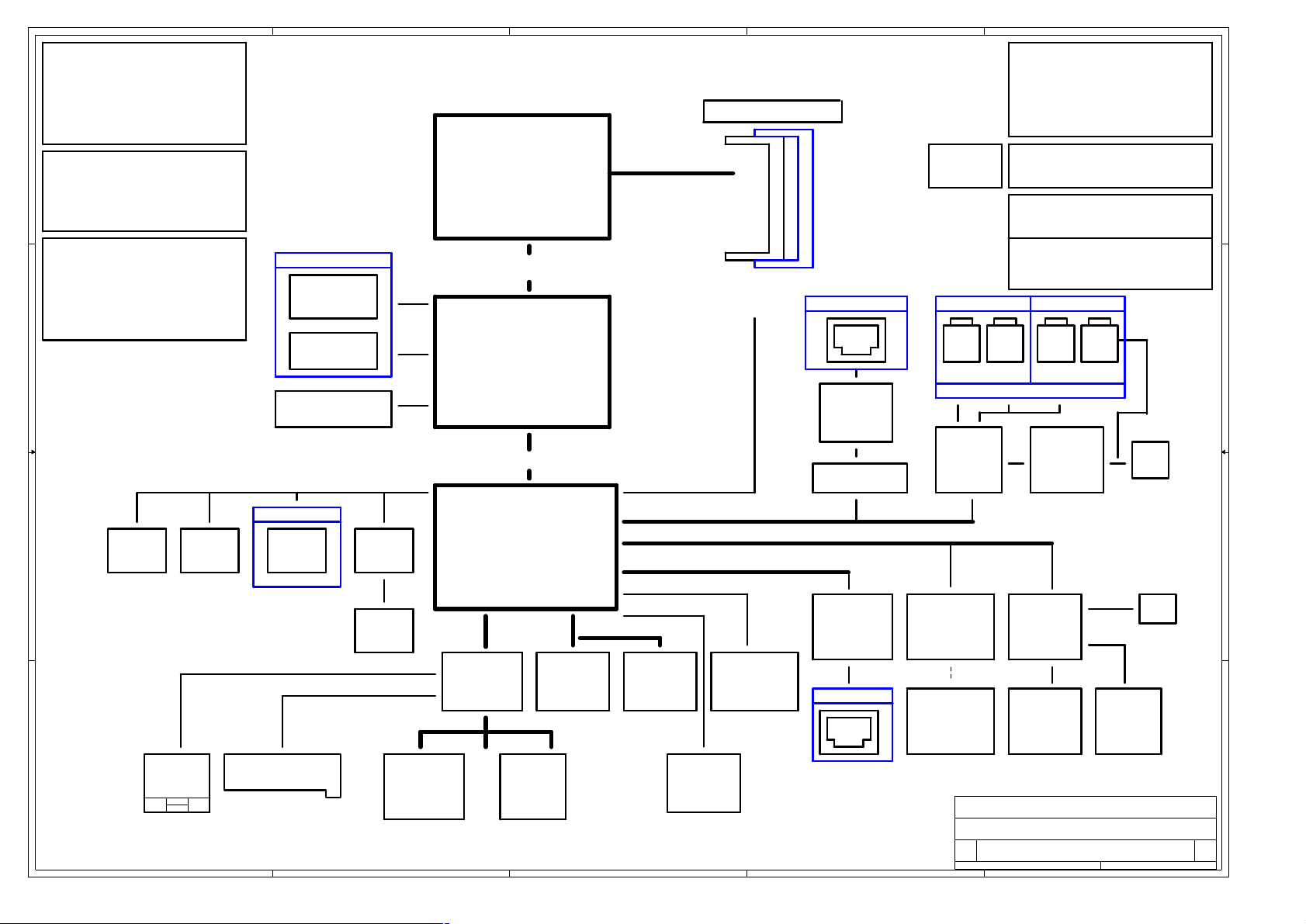

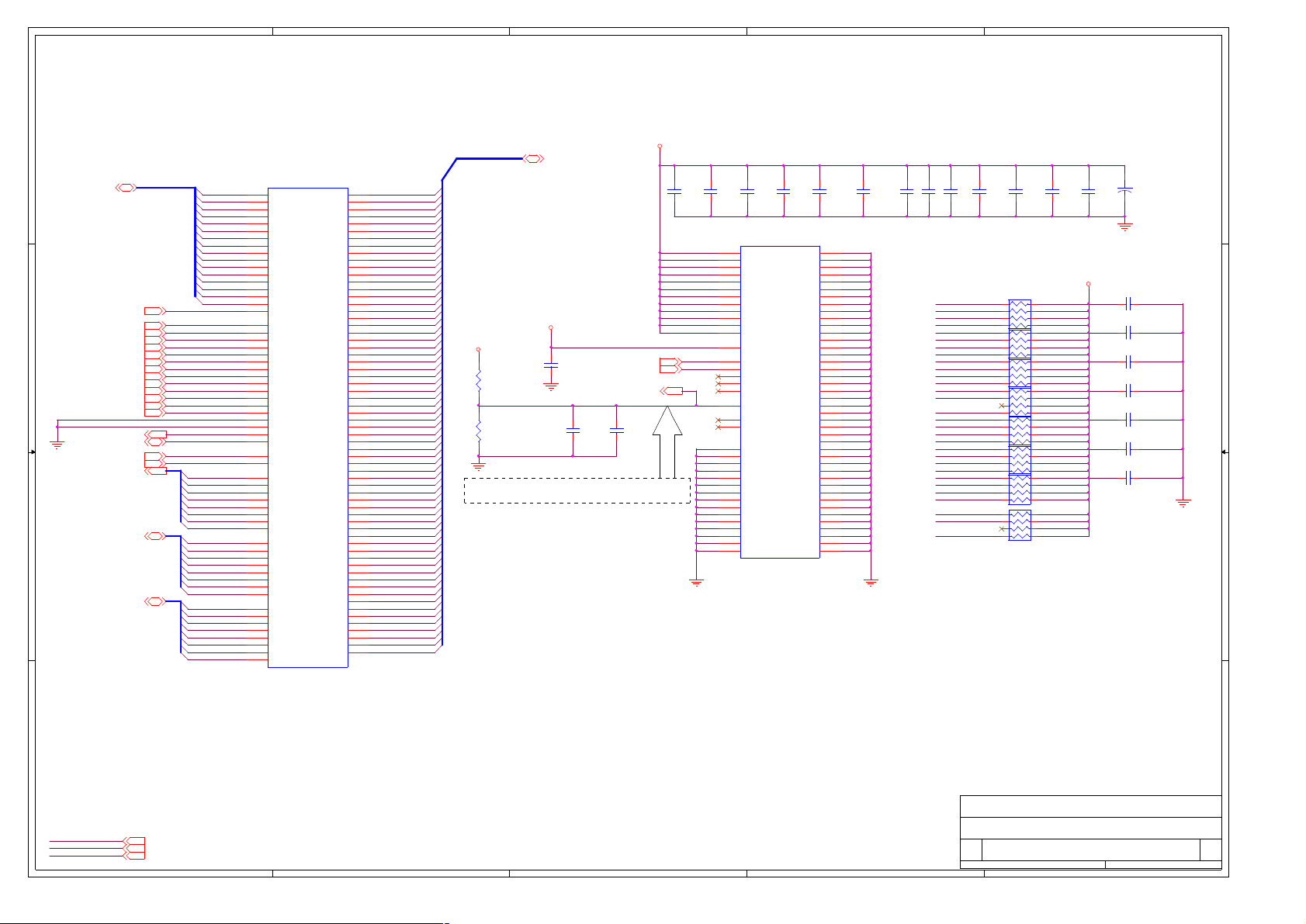

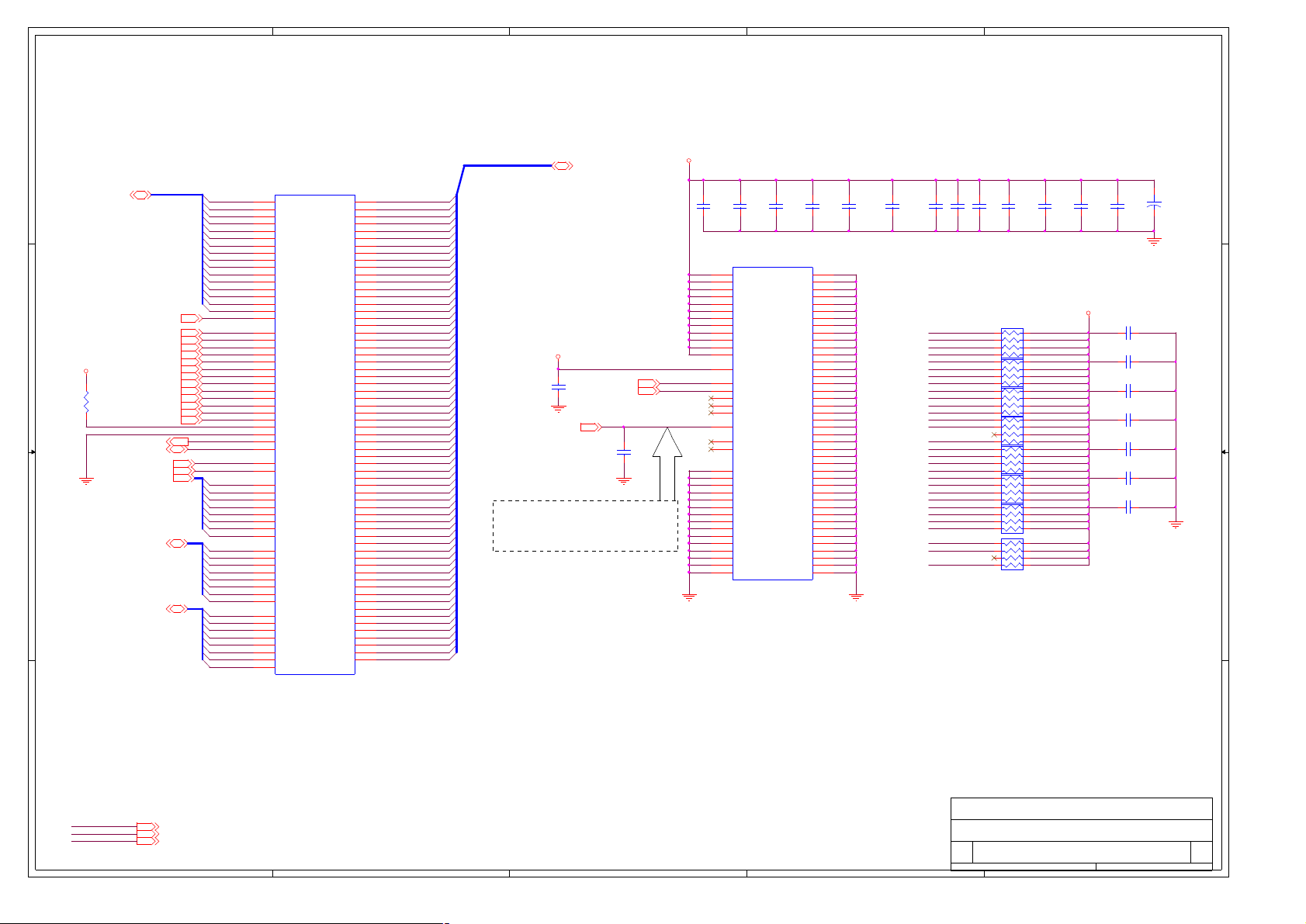

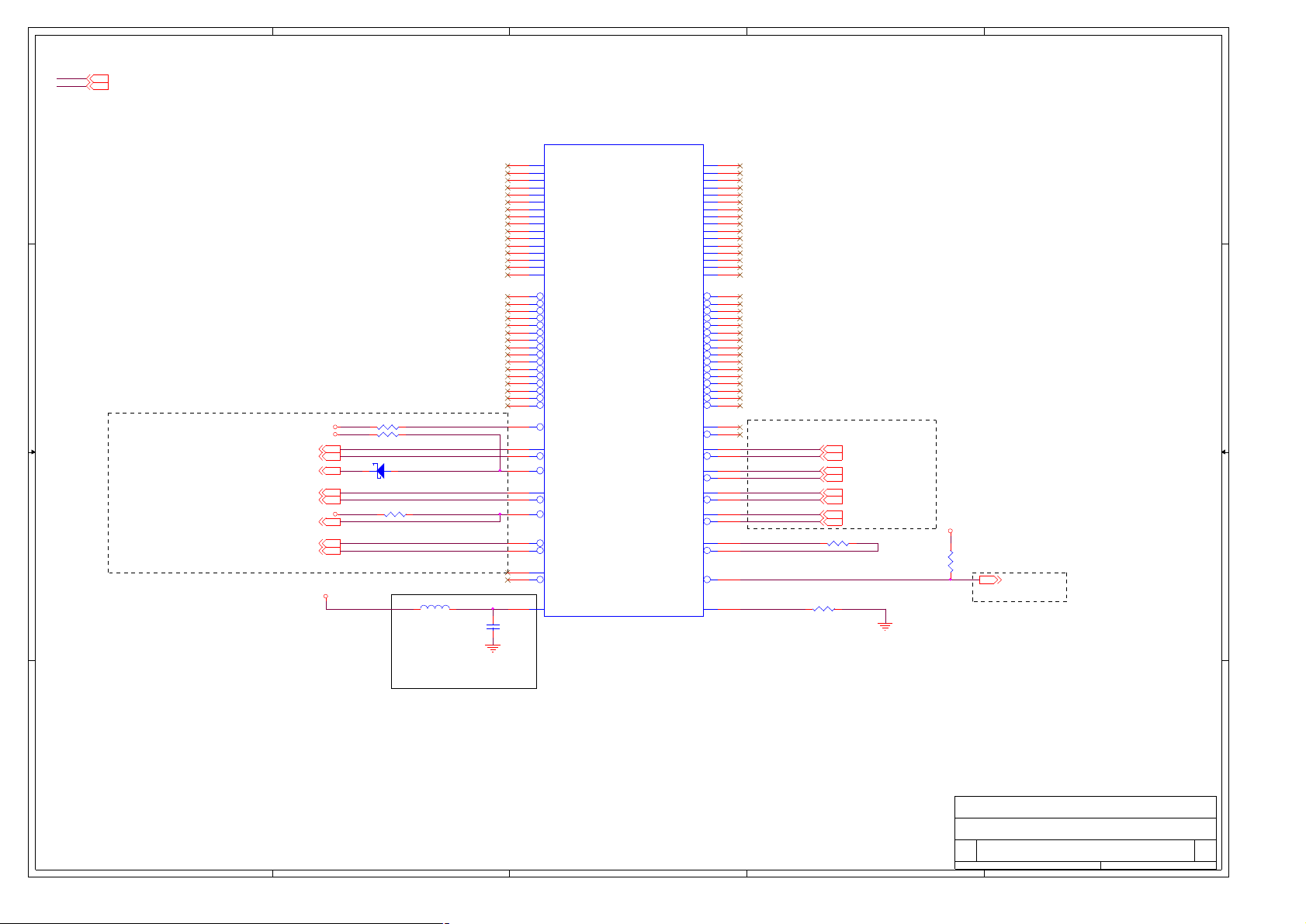

CLEVO M540JE,M550JE Schematics

5

D/D BOARD

1.CHARGER,DC JACK

CLEVO M540JE/M550JE System Block Diagram

2.CRT,COM1,RI-11

D D

SHEET 36,37,38

AUDIO BOARD

1.AUDIO PHONE JACK

2.USB CONNECTOR

3.RJ11 CONNECTOR

1.POWER BOTTON

2.INDICATOR LED

3.LID SWITCH

C C

SHEET 39

HOT KEY BOARD

SHEET 40

D/D BOARD

COM1

SHEET 36

CRT

SHEET 36

LCD CONN(LVDS)

SHEET 8

4

PROCESSOR

SOCKET

AMD S1

638 PIN

SHEET 2,3,4,5

Hyper Transport link

NORTH BRIDGE

C51M(V)

468 PBGA

SHEET 9,10,11,12,13

3

MEMORY TERMINATIONS

DDR2

533 /667MHz

SO-DIMM2

SHEET 6 SHEET 7

SHEET 6,7

2

DDR2 SDRAM

SOCKET

SO-DIMM1

AUDIO BOARD

RJ-11

AZALIA

MBC

1.+1.2V_HT,+1.5V,+1.5VS,+1.8VS

2.+3V,+5V,+12V,+3VS,+5VS,+12VS

3.+2.6VS,+3VS,+5VS,+2.5VCPU

4.+3VH8,+5VH8

5.+VDD3,+VDD5,+VDD12

SHEET 02,03,05,18,31,35

DDR VR

SHEET 32

1.+1.8V,+0.9V

1.+VCORE

1.+1.2VS

MAIN BOARDAUDIO BOARD

LINE

SPDIF

IN

OUT

SHEET 27

7.1 CHANNEL OUT

MIC

IN

SHEET 39

1

SHEET 32

SHEET 33

SHEET 34

HP

OUT

MODULE

AZALIA

Hyper Transport link

USB2.0

AUDIO BOARD

B B

CCD

SHEET 25

MBC

SHEET 22

USB2

SHEET 39

USB0

SHEET 20

USB1

SHEET 20

SOUTH BRIDGE

MCP51M

508 PBGA

SHEET 14,15,16,17,18,19

LPC

KBC

H8/2111

SHEET 24

LPC

BIOS

LPC

SHEET 23

SM BUS

AZALIA LINK

PCI-E BUS

PCI BUS

SATA 2

PATA-100

SIO

LPC

SHEET 21

33MHz

SATA CONN.

2.5" HDD

SHEET 21

H8 SM BUS

A A

TOUCH

PAD

SHEET 23

5

INT. K/B CONN.

SHEET 24

THERMAL

SENSOR

F75383M

SHEET 3

4

SMART

FAN

SHEET 8

IDE1

MASTER

CD-ROM

SHEET 21

CD-ROM/CD-RW/DVD-COMBO/

DVD-ROM/DVD+-RW

3

MBC CONN.

SHEET 26

LAN PHY

RTL8201CL/

LAN BOARD

RJ-45

2

CODEC

ALC883

SHEET 27

Mini CARD

SOCKET

SHEET 20

Mini CARD

Wireless LAN

802.11 a/b/g

Title

Size Document Number Rev

A3

3546

Date: Sheet of

AUDIO

AMP.

APA2020A

SHEET 28

NEW CARD

TI

PCI7402

SHEET 28SHEET 22

NEW CARD

SOCKET

SHEET 29

3 IN 1

SHEET 30

CLEVO CO. 藍天電腦

BLOCK DIAGRAM

6-71-M55E0-002 2.0

1

INT.

SPK

1 44Wednesday, May 24, 2006

IEEE

1394

5

4

3

2

1

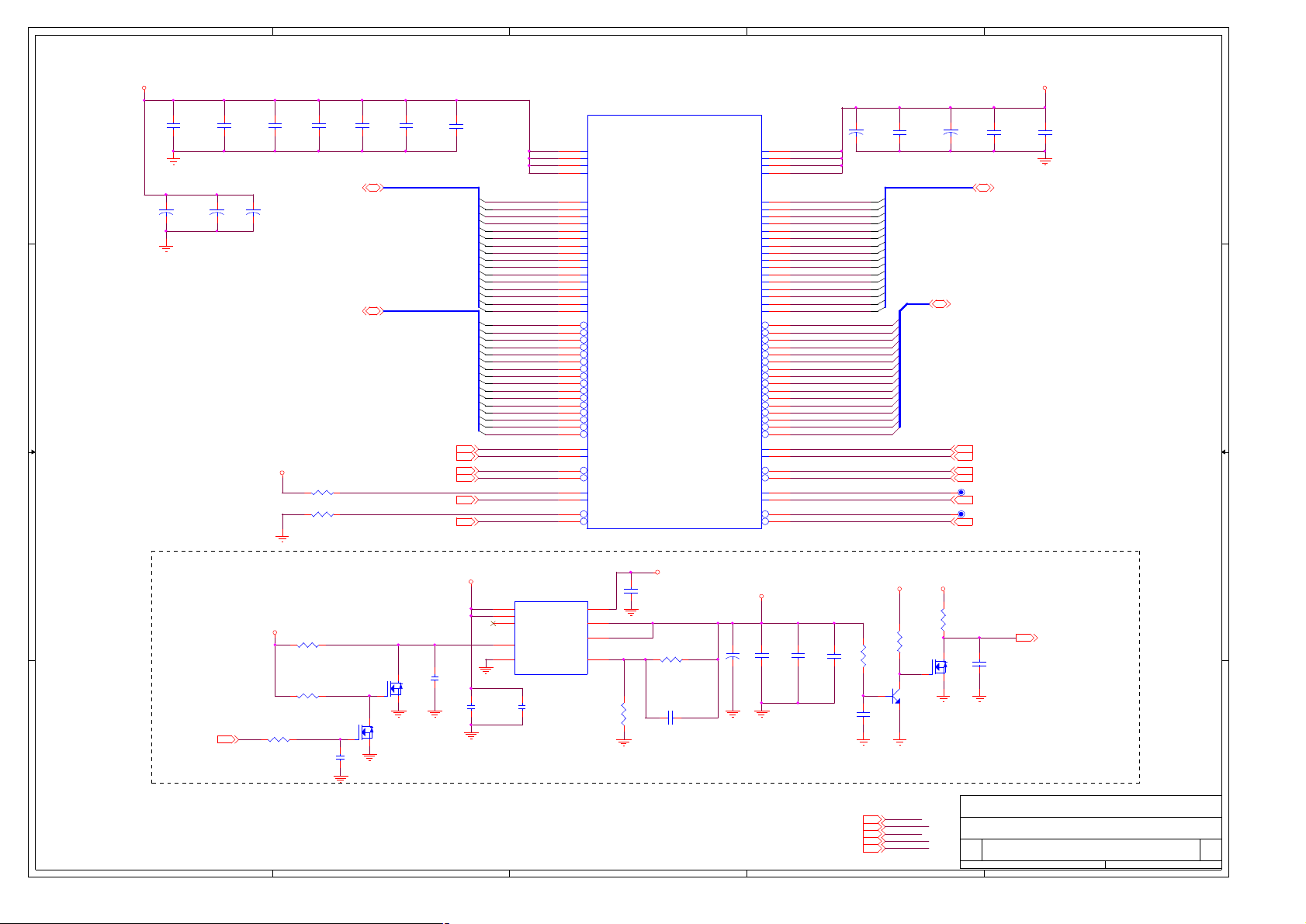

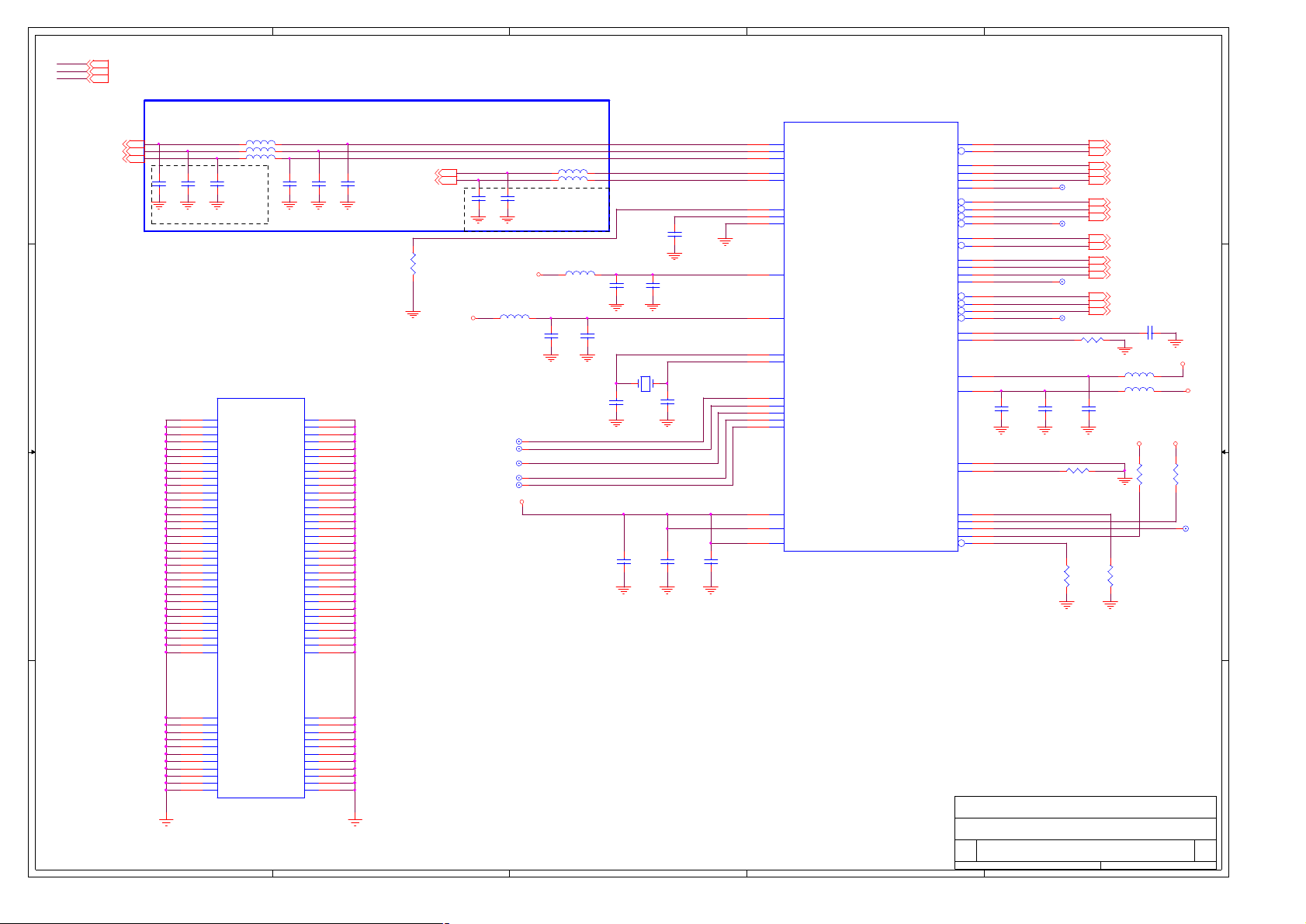

+1.2V_HT

0.1u_X7R_04

C435

0.1u_X7R_04

C455

+

4.7u_08

C459

+

4.7u_08

C431

0.22u_04

C434

D D

C429

+

*47u/6.3V_B

C C

+1.2V_HT

LAYOUT: PLACE CLOSE TO CPU

HT

ALONG HT POWER SHAPE

C436

0.22u_04

L0_CADIN_H[15..0]9

L0_CADIN_L[15..0]9

R296 49.9_1%

R297 49.9_1%

C433

0.22u_04

C451

180p_X7R_04

L0_CADIN_H[15..0]

L0_CADIN_L[15..0]

L0_CLKIN_H19

L0_CLKIN_H09

L0_CLKIN_L19

L0_CLKIN_L09

L0_CTLIN_H09

L0_CTLIN_L09

C432

1000p_04

L0_CADIN_H15

L0_CADIN_H14

L0_CADIN_H13

L0_CADIN_H12

L0_CADIN_H11

L0_CADIN_H10

L0_CADIN_H9

L0_CADIN_H8

L0_CADIN_H7

L0_CADIN_H6

L0_CADIN_H5

L0_CADIN_H4

L0_CADIN_H3

L0_CADIN_H2

L0_CADIN_H1

L0_CADIN_H0

L0_CADIN_L15

L0_CADIN_L14

L0_CADIN_L13

L0_CADIN_L12

L0_CADIN_L11

L0_CADIN_L10

L0_CADIN_L9

L0_CADIN_L8

L0_CADIN_L7

L0_CADIN_L6

L0_CADIN_L5

L0_CADIN_L4

L0_CADIN_L3

L0_CADIN_L2

L0_CADIN_L1

L0_CADIN_L0

L0_CLKIN_H1

L0_CLKIN_H0

L0_CLKIN_L1

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_H0

L0_CTLIN_L1

L0_CTLIN_L0

40MIL

D1

D2

D3

D4

N5

M3

L5

K3

H3

G5

F3

E5

N3

L1

L3

J1

G1

G3

E1

E3

P5

M4

M5

K4

H4

H5

F4

F5

N2

M1

L2

K1

H1

G2

F1

E2

J5

J3

K5

J2

P3

N1

P4

P1

U15A

V_HT0_A1

V_HT0_A2

V_HT0_A3

V_HT0_A4

HT_RXD<15>

HT_RXD<14>

HT_RXD<13>

HT_RXD<12>

HT_RXD<11>

HT_RXD<10>

HT_RXD<9>

HT_RXD<8>

HT_RXD<7>

HT_RXD<6>

HT_RXD<5>

HT_RXD<4>

HT_RXD<3>

HT_RXD<2>

HT_RXD<1>

HT_RXD<0>

HT_RXD<15>*

HT_RXD<14>*

HT_RXD<13>*

HT_RXD<12>*

HT_RXD<11>*

HT_RXD<10>*

HT_RXD<9>*

HT_RXD<8>*

HT_RXD<7>*

HT_RXD<6>*

HT_RXD<5>*

HT_RXD<4>*

HT_RXD<3>*

HT_RXD<2>*

HT_RXD<1>*

HT_RXD<0>*

HT_RXCLK<1>

HT_RXCLK<0>

HT_RXCLK<1>*

HT_RXCLK<0>*

HT_RXCTL<1>

HT_RXCTL<0>

HT_RXCTL<1>*

HT_RXCTL<0>*

SEC 1 OF 6

LDT

V_HT0_B1

V_HT0_B2

V_HT0_B3

V_HT0_B4

HT_TXD<15>

HT_TXD<14>

HT_TXD<13>

HT_TXD<12>

HT_TXD<11>

HT_TXD<10>

HT_TXD<9>

HT_TXD<8>

HT_TXD<7>

HT_TXD<6>

HT_TXD<5>

HT_TXD<4>

HT_TXD<3>

HT_TXD<2>

HT_TXD<1>

HT_TXD<0>

HT_TXD<15>*

HT_TXD<14>*

HT_TXD<13>*

HT_TXD<12>*

HT_TXD<11>*

HT_TXD<10>*

HT_TXD<9>*

HT_TXD<8>*

HT_TXD<7>*

HT_TXD<6>*

HT_TXD<5>*

HT_TXD<4>*

HT_TXD<3>*

HT_TXD<2>*

HT_TXD<1>*

HT_TXD<0>*

HT_TXCLK<1>

HT_TXCLK<0>

HT_TXCLK<1>*

HT_TXCLK<0>*

HT_TXCTL<1>

HT_TXCTL<0>

HT_TXCTL<1>*

HT_TXCTL<0>*

AE2

AE3

AE4

AE5

L0_CADOUT_H15

T4

L0_CADOUT_H14

V5

L0_CADOUT_H13

V4

L0_CADOUT_H12

Y5

L0_CADOUT_H11

AB5

L0_CADOUT_H10

AB4

L0_CADOUT_H9

AD5

L0_CADOUT_H8

AD4

L0_CADOUT_H7

T1

L0_CADOUT_H6

U2

L0_CADOUT_H5

V1

L0_CADOUT_H4

W2

L0_CADOUT_H3

AA2

L0_CADOUT_H2

AB1

L0_CADOUT_H1

AC2

L0_CADOUT_H0

AD1

L0_CADOUT_L15

T3

L0_CADOUT_L14

U5

L0_CADOUT_L13

V3

L0_CADOUT_L12

W5

L0_CADOUT_L11

AA5

L0_CADOUT_L10

AB3

L0_CADOUT_L9

AC5

L0_CADOUT_L8

AD3

L0_CADOUT_L7

R1

L0_CADOUT_L6

U3

L0_CADOUT_L5

U1

L0_CADOUT_L4

W3

L0_CADOUT_L3

AA3

L0_CADOUT_L2

AA1

L0_CADOUT_L1

AC3

L0_CADOUT_L0

AC1

L0_CLKOUT_H1

Y4

L0_CLKOUT_H0

Y1

L0_CLKOUT_L1

Y3

L0_CLKOUT_L0

W1

TP_HT_DWNCNTL1

T5

L0_CTLOUT_H0

R2

TP_HT_DWNCNTL1#

R5

L0_CTLOUT_L0

R3

C457

+

4.7u_08

L0_CADOUT_H[15..0]

C449

*22u_12

C458

C454

+

4.7u_08

0.1u_X7R_04

L0_CADOUT_H[15..0]9

L0_CADOUT_L[15..0]9

L0_CLKOUT_H19

L0_CLKOUT_H09

L0_CLKOUT_L19

L0_CLKOUT_L09

L0_CTLOUT_H09

L0_CTLOUT_L09

+1.2V_HT

C453

0.1u_X7R_04

B B

A A

5

0331

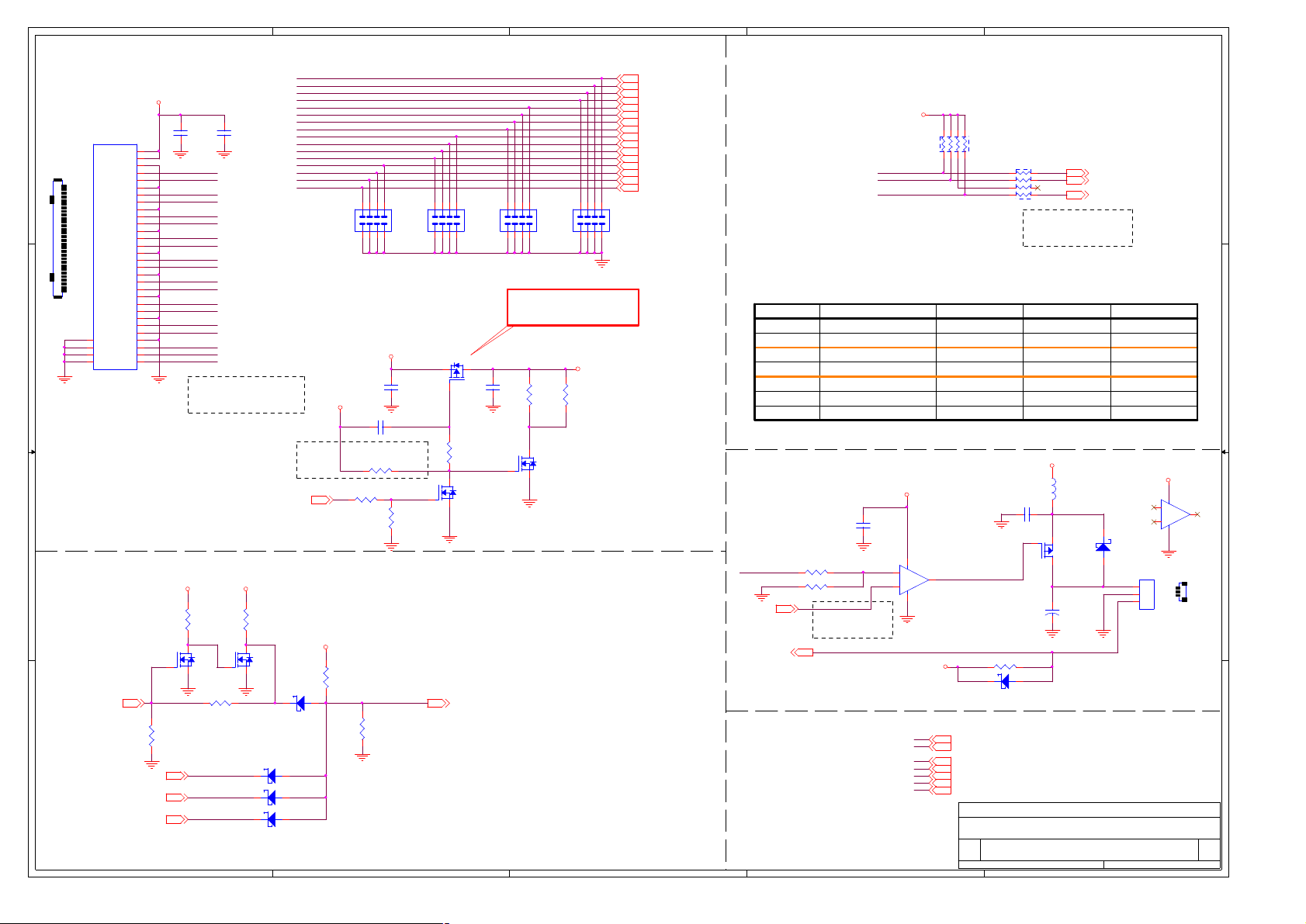

HTVDD_EN14

+5V

R5 100K_04

R2 100K_04

R13 0_04

Z0204

Z0203

G

C14

0.1u_04

DS

G

Q5

2N7002

+1.8V

U2

5

VIN

9

VIN

7

POK

Z0202

C5

DS

1000p_04

Q6

2N7002

4

C31

10u_08

8

EN

1

GND

APL5913

C21

0.1u_04 C43 56p_04

VCNTL

VOUT

VOUT

VFB

6

4

3

2

C4

1u

Z0205

R32

78.7K_1%

3

+5V

R33 39.2K_1%

+1.2V_HT

C428

+

+3VS+VDD5

C33

10u_08

C22

1u

1.5A

R20

47K_04

Z0207

60MIL

C32

10u_08

Z0206

*470u_2.5V_D2

+1.2V_HT3,9,13

+5V17,18,21,23,24,25,31,33

+VDD55,8,17,25,31,32,33,34,35

+3VS3,6,7,8,11,12,13,14,15,16,17,19,20,21,23,25,26,28,29,30,31

+1.8V3,4,5,6,7,18,32

C20

0.1u_04

2

B

E C

R6

47K_04

Q4

2N3904

R12

47K_04

DS

Q10

G

2N7002

Title

Size Document Number Rev

Wednesday, May 24, 2006

Date: Sheet of

HT_VLD14

C16

*0.1u_04

藍天電腦 CLEVO

02 AMD S1:HT

3546

6-71-M55E0-002

1

2 44

2.0

5

+2.6VS

R18

C65 0.1u_X7R_04

1K_04

PWRGD8,17,24,25

CPURST#9

D D

CPURST#

+2.6VS

R16

1K_04

CPU_PWRGD9

CPU_PWRGD

+2.6VS

R19

1K_04

LDTSTOP#9

+1.2V_HT

PLACE WITHIN 1"

5MIL TRACE

10MIL SPACE

C C

TO OTHER SIGNALS

PAIR 5/5/5,10 MILROUTE AS DIFF

CPUCLK_H9

LDTSTOP#

R299 44.2_1%_04

R298 44.2_1%_04

OR 10/10 IF SE

CPUCLK_H

VDDIOFB_H32

VDDIOFB_L32

LVC

147

1

2

LVC

147

4

5

LVC

147

9

10

VCORE+33

VCORE-33

C466 3900P_04

0412

U4A

74LVC08

3

U4B

74LVC08

6

U4C

74LVC08

8

P_PWRGD

LDTSTOP

L0_REF1

L0_REF0

VCORE+

VCORE-

VDDIOFB_H

VDDIOFB_L

CLKIN

R317

169_1%

CPUCLK_L9

ROUTE AS DIF 5/5/5/20

LAYOUT: PLACE 169 OHM NO MORE THAN

500 MILS FROM CPU

B B

+1.8V

C106

0.1u_04

CPUCLK_L

VCORE

C132

0.1u_X7R_04

+1.8V

R315

510_1%_04

R50

510_1%_04

C465 3900P_04

T3

T5

T7

T8

T9

R314

300_1%_04

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TRST#

CPU_TDI

S1_TEST25

S1_TEST25#

S1_TEST19

S1_TEST18

R49

300_1%_04

THERMDC

THERMDA

CLKIN#

12MIL

+1.8VS5,13

+5VS19,20,21,22,23,24,25,26,27,31

+VDD38,18,24,25,31,35

+VDD52,5,8,17,25,31,32,33,34,35

+3VS2,6,7,8,11,12,13,14,15,16,17,19,20,21,23,25,26,28,29,30,31

+3V15,17,18,19,20,21,22,25,27,29,31,32,33

+1.8V2,4,5,6,7,18,32

+1.2V_HT2,9,13

+2.6VS9,12,13,31

A A

VCORE5,33

+1.8VS

R66 *300_04

R67 *300_04

R68 *300_04

R69 *300_04

R70 300_1%_04

R71 *300_04

CPU_VID5 33

CPU_VID4 33

CPU_VID3 33

CPU_VID2 33

CPU_VID1 33

CPU_VID0 33

5

4

R38 *300_04

R15 *300_04

R17 *300_04

F8

F9

Z0301

B7

A7

F10

P6

R6

F6

E6

W9

Y9

A9

A8

G10

AA9

AC9

AD9

AF9

E9

E8

G9

H10

AA7

C2

TP_S1_TEST17

D7

TP_S1_TEST16

E7

TP_S1_TEST15

F7

TP_S1_TEST14

C7

TP_S1_TEST12

AC8

C3

AA6

W7

W8

Y6

AB6

B3

H19

H18

W18

D5

N20

P20

P19

N19

P22

R26

4

+1.8V

S1_VDDA

C460

0.22u_04

U15B

PZ638X3-284S-01

VDDA

VDDA

RESET*

PWROK

LDTSTOP*

HTREF1

HTREF0

VDD_FB

VDD_FB*

VDDIO_FB

VDDIO_FB*

CLKIN

CLKIN*

DBRDY

TMS

TCK

TRST*

TDI

TEST25

TEST25*

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST5

TEST4

TEST3

TEST2

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

I290

147

12

13

C456

3300p

SKT638

SEC 2 OF 6

MISC

LVC

11

C101

0.1u_X7R_04

CPU_PRESENT*

R39 0_04

R40 *0_04

U4D

74LVC08

THERMTRIP*

PROCHOT*

VID<5>

VID<4>

VID<3>

VID<2>

VID<1>

VID<0>

DBREQ*

TEST29

TEST29*

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28

TEST28*

TEST27

TEST26

TEST10

TEST8

3

+1.8V

+3V

0412

40MIL40MIL

C442

C462

C461

1u_04

AF6

AC7

AF5

AF4

A5

C6

A6

A4

C5

B5

A3

AC6

E10

AE9

LAYOUT: ROUTE TRACES 80 OHM DIFF IMPEDENCE

C9

C8

AE7

AD7

AE8

AB8

AF7

J7

H8

AF8

AE6

K8

C4

B18

R25

R23

H16

R22

R24

C1

H6

G6

AA8

NC

0.01u_04

Z0304

Z0307

R302 *300_04

Z0308

R303 300_1%_04

CPU_PSI#

CPUPRESENT

CPU_DBREQ

CPU_TDO

8/5/20 SPACING

FBCLKOUT

FBCLKOUT#

TP_S1_TEST24

TP_S1_TEST23

TP_S1_TEST22

TP_S1_TEST21

TP_S1_TEST20

+1.8V

R306 300_1%_04

Z0309

*22u_12

CPU_VID5 33

CPU_VID4 33

CPU_VID3 33

CPU_VID2 33

CPU_VID1 33

CPU_VID0 33

R53

300_1%_04

3

CPU_PSI#33

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

RSVD

L37FCI2012F-R33K

SID

SIC

PSI*

TDO

0323 Change

+2.5VCPU

C446

+

C452

*22u_12

100u/6.3V_B

PLEASE NEAR PULLUPS

T4

T6

R313

80.6_1%_04

THERMAL_ON#24

+1.8V

R51

1K_04

+VDD3

R324 100K_04

+1.8V

+1.8VS

R305

*300_04

R308 680

R307

300_1%_04

*BSS138

G

0331

PWRGD8,17,24,25

Q46

AO3409

G

Layout Note:

Route H_THERMDA and H_THERMDC

on the same layer.

10 mil trace on 10 mil spacing.

Q44

Z0312

G

DS

DS

Q47

2N7002

2

VCORE

R301

THERMTRIP

0329

Z0306

CPU_FETGATE

R26 10K_04

R326 0

Z0310

DS

THERMDA

THERMDC

2

0_04

R304 680

B

+3VS

R310

4.7K_04

R309 *680

C46

1u

Z0311

R320

100K_04

C464

2200p

Layout Note:

Near to ADM1032

ID

CPU00

VGA11

1

+VDD3

Z0303Z0302

E C

Q43

2N3904

B

C463

*0.1u_04

R316 4.7K_04

D22 1N4148

Q45

2N3904

E C

Low active to short

down system.

AC

0323 Change

AMD_PROCHOT#24

R312 *8.2K_1%_04

R311 *34.8K_1%_04

Z0313

1

3

2

U5

VIN

GNDSDADJ

G916T1U

VO

40MIL

5

4

Z0314

+VDD3

C467

1u_04

R322

4.7K_04

U14

1

2

3

5

VDD

D+

DGND

F75383M

4

THERM

6

ALERT

7

SDATA

8

SCLK

藍天電腦 CLEVO

Title

Size Document Number Rev

3546

Wednesday, May 24, 2006

Date: Sheet of

+2.5VCPU

+2.5VCPU+3V

35mA

R37

10K_04_1%

R36

10K_04_1%

R319

4.7K_04

6-71-M55E0-002

C48

0.22u_04

04060406

R318

10K_04

D23 SCS751V

H8_SDAT124

H8_SCLK124

K8 S1 : MISC

1

H8_THRMTRIP#24

TRMTRIP#35

C49

3300p

AC

PM_THRM#17

H8_THRM#24

3 44

2.0

5

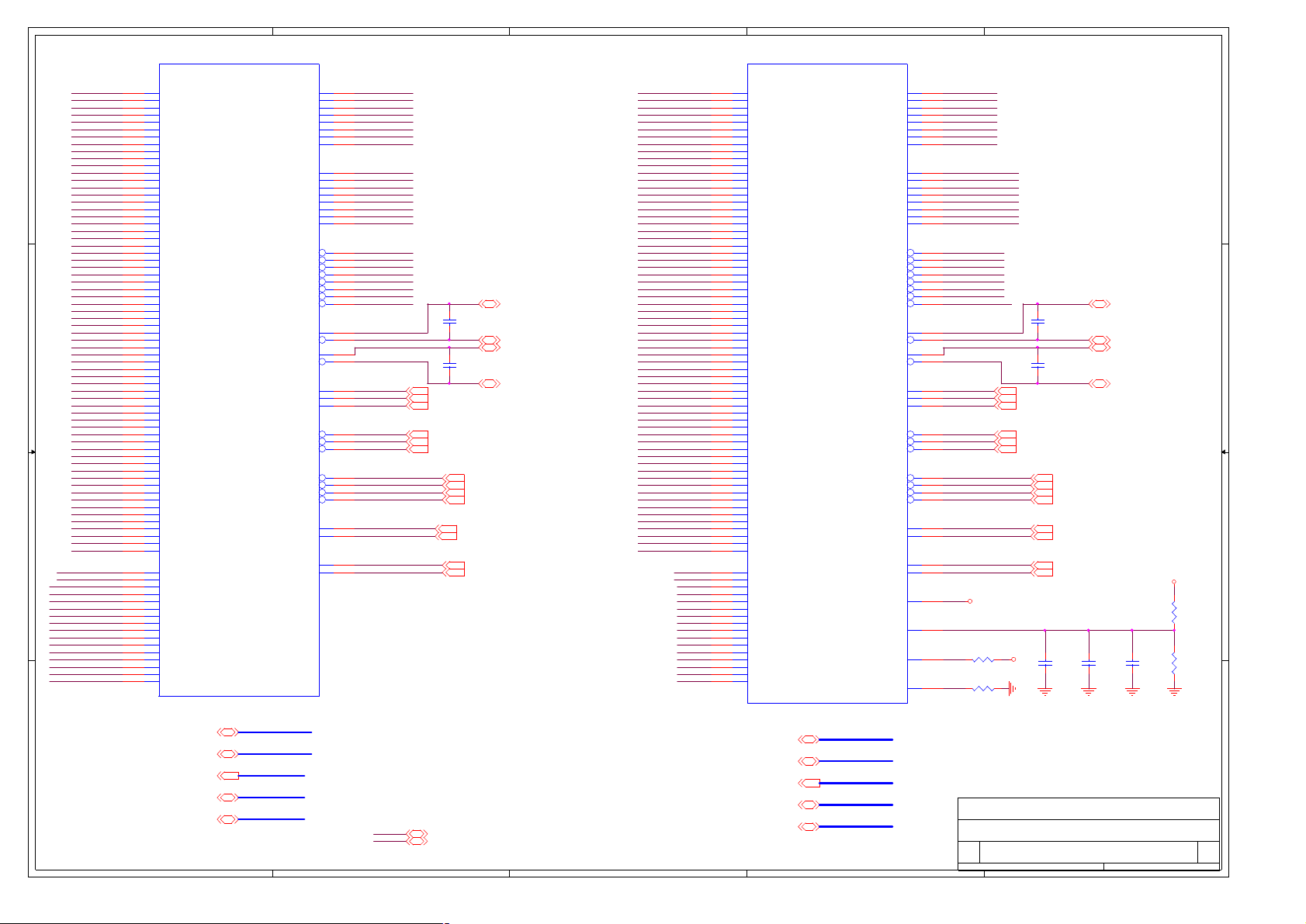

U15C

PZ638X3-284S-01

M_A_DATA63

AA12

AB12

AA14

AB14

W11

AD13

AB13

AD15

AB15

AB17

W14

W16

AD17

AD19

AD21

AB21

AB18

AA18

AA20

AA22

W21

W22

AA21

AB22

AB24

Y12

Y17

Y14

Y18

Y20

Y22

Y24

H22

H20

E22

E21

H24

F22

F20

C23

B22

F18

E18

E20

D22

C19

G18

G17

C17

F14

E14

H17

E17

E15

H15

E13

C13

H12

H11

G14

H14

F12

G12

K19

K20

V24

K24

R19

M19

M20

M24

M22

N22

N21

R21

MA_DATA<63>

MA_DATA<62>

MA_DATA<61>

MA_DATA<60>

MA_DATA<59>

MA_DATA<58>

MA_DATA<57>

MA_DATA<56>

MA_DATA<55>

MA_DATA<54>

MA_DATA<53>

MA_DATA<52>

MA_DATA<51>

MA_DATA<50>

MA_DATA<49>

MA_DATA<48>

MA_DATA<47>

MA_DATA<46>

MA_DATA<45>

MA_DATA<44>

MA_DATA<43>

MA_DATA<42>

MA_DATA<41>

MA_DATA<40>

MA_DATA<39>

MA_DATA<38>

MA_DATA<37>

MA_DATA<36>

MA_DATA<35>

MA_DATA<34>

MA_DATA<33>

MA_DATA<32>

MA_DATA<31>

MA_DATA<30>

MA_DATA<29>

MA_DATA<28>

J19

MA_DATA<27>

MA_DATA<26>

MA_DATA<25>

MA_DATA<24>

MA_DATA<23>

MA_DATA<22>

MA_DATA<21>

MA_DATA<20>

MA_DATA<19>

MA_DATA<18>

MA_DATA<17>

MA_DATA<16>

MA_DATA<15>

MA_DATA<14>

MA_DATA<13>

MA_DATA<12>

MA_DATA<11>

MA_DATA<10>

MA_DATA<9>

MA_DATA<8>

MA_DATA<7>

MA_DATA<6>

MA_DATA<5>

MA_DATA<4>

MA_DATA<3>

MA_DATA<2>

MA_DATA<1>

MA_DATA<0>

MA_ADD<15>

MA_ADD<14>

MA_ADD<13>

MA_ADD<12>

L20

MA_ADD<11>

MA_ADD<10>

L19

MA_ADD<9>

L22

MA_ADD<8>

L21

MA_ADD<7>

MA_ADD<6>

MA_ADD<5>

MA_ADD<4>

MA_ADD<3>

MA_ADD<2>

MA_ADD<1>

MA_ADD<0>

M_A_DATA62

M_A_DATA61

M_A_DATA60

M_A_DATA59

M_A_DATA58

M_A_DATA57

D D

C C

B B

M_A_DATA56

M_A_DATA55

M_A_DATA54

M_A_DATA53

M_A_DATA52

M_A_DATA51

M_A_DATA50

M_A_DATA49

M_A_DATA48

M_A_DATA47

M_A_DATA46

M_A_DATA45

M_A_DATA44

M_A_DATA43

M_A_DATA42

M_A_DATA41

M_A_DATA40

M_A_DATA39

M_A_DATA38

M_A_DATA37

M_A_DATA36

M_A_DATA35

M_A_DATA34

M_A_DATA33

M_A_DATA32

M_A_DATA31

M_A_DATA30

M_A_DATA29

M_A_DATA28

M_A_DATA27

M_A_DATA26

M_A_DATA25

M_A_DATA24

M_A_DATA23

M_A_DATA22

M_A_DATA21

M_A_DATA20

M_A_DATA19

M_A_DATA18

M_A_DATA17

M_A_DATA16

M_A_DATA15

M_A_DATA14

M_A_DATA13

M_A_DATA12

M_A_DATA11

M_A_DATA10

M_A_DATA9

M_A_DATA8

M_A_DATA7

M_A_DATA6

M_A_DATA5

M_A_DATA4

M_A_DATA3

M_A_DATA2

M_A_DATA1

M_A_DATA0

M_A_A15

M_A_A14 M_B_A14

M_A_A13

M_A_A12

M_A_A11

M_A_A10

M_A_A9

M_A_A8

M_A_A7

M_A_A6

M_A_A5

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

SKT638

SEC 3 OF 6

MEMORY_A

MA_DM<7>

MA_DM<6>

MA_DM<5>

MA_DM<4>

MA_DM<3>

MA_DM<2>

MA_DM<1>

MA_DM<0>

MA_DQS<7>

MA_DQS<6>

MA_DQS<5>

MA_DQS<4>

MA_DQS<3>

MA_DQS<2>

MA_DQS<1>

MA_DQS<0>

MA_DQS<7>*

MA_DQS<6>*

MA_DQS<5>*

MA_DQS<4>*

MA_DQS<3>*

MA_DQS<2>*

MA_DQS<1>*

MA_DQS<0>*

MA0_CLK<1>

MA0_CLK<1>*

MA0_CLK<2>

MA0_CLK<2>*

MA_BANK<2>

MA_BANK<1>

MA_BANK<0>

MA_RAS*

MA_CAS*

MA_WE*

MA0_CS<3>*

MA0_CS<2>*

MA0_CS<1>*

MA0_CS<0>*

MA_CKE<1>

MA_CKE<0>

MA0_ODT<1>

MA0_ODT<0>

Y13

AB16

Y19

AC24

F24

E19

C15

E12

W12

Y15

AB19

AD23

G22

C22

G16

G13

W13

W15

AB20

AC23

G21

C21

G15

H13

E16

F16

Y16

AA16

K22

R20

T22

T20

U20

U21

V19

J22

V22

T19

J20

J21

V20

U19

I462

M_A_DATA[0..63]6

M_A_A[15:0]6

A A

M_A_DM[0..7]6

M_A_DQS[0..7]6

M_A_DQS#[0..7]6

5

M_A_DATA[0..63]

M_A_A[15:0]

M_A_DM[0..7]

M_A_DQS[0..7]

M_A_DQS#[0..7]

4

M_A_DM7

M_A_DM6

M_A_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

M_A_DQS7

M_A_DQS6

M_A_DQS5

M_A_DQS4

M_A_DQS3

M_A_DQS2

M_A_DQS1

M_A_DQS0

M_A_DQS#7

M_A_DQS#6

M_A_DQS#5

M_A_DQS#4

M_A_DQS#3

M_A_DQS#2

M_A_DQS#1

M_A_DQS#0

M_CLK_DDR0

M_CLK_DDR#0

M_CLK_DDR1 M_CLK_DDR3

M_CLK_DDR#1

M_A_BS2

M_A_BS1

M_A_BS0 M_B_BS0

M_A_RAS#

M_A_CAS#

M_A_WE#

M_A_CS3#

M_A_CS2#

M_A_CS1#

M_A_CS0#

M_CKE1

M_CKE0

M_ODT1

M_ODT0

TRACE FROM CAP TO CPU MUST BE LESS THAN 1200 MILS

MAX NECKDOWN TO & FROM CAPS IS 500 MILS

M_A_CS3#6

M_A_CS2#6

M_A_CS1#6

M_A_CS0#6

M_CKE16

M_CKE06

M_ODT16

M_ODT06

M_CLK_DDR06

M_CLK_DDR#06

M_CLK_DDR16

M_CLK_DDR#16

C479

1.5PF_NPO_04

C144

1.5PF_NPO_04

M_A_BS26

M_A_BS16

M_A_BS06

M_A_RAS#6

M_A_CAS#6

M_A_WE#6

3

M_B_DATA63

M_B_DATA62

M_B_DATA61

M_B_DATA60

M_B_DATA59

M_B_DATA58

M_B_DATA57

M_B_DATA56

M_B_DATA55

M_B_DATA54

M_B_DATA53

M_B_DATA52

M_B_DATA51

M_B_DATA50

M_B_DATA49

M_B_DATA48

M_B_DATA47

M_B_DATA46

M_B_DATA45

M_B_DATA44

M_B_DATA43

M_B_DATA42

M_B_DATA41

M_B_DATA40

M_B_DATA39

M_B_DATA38

M_B_DATA37

M_B_DATA36

M_B_DATA35

M_B_DATA34

M_B_DATA33

M_B_DATA32

M_B_DATA31

M_B_DATA30

M_B_DATA29

M_B_DATA28

M_B_DATA27

M_B_DATA26

M_B_DATA25

M_B_DATA24

M_B_DATA23

M_B_DATA22

M_B_DATA21

M_B_DATA20

M_B_DATA19

M_B_DATA18

M_B_DATA17

M_B_DATA16

M_B_DATA15

M_B_DATA14

M_B_DATA13

M_B_DATA12

M_B_DATA11

M_B_DATA10

M_B_DATA9

M_B_DATA8

M_B_DATA7

M_B_DATA6

M_B_DATA5

M_B_DATA4

M_B_DATA3

M_B_DATA2

M_B_DATA1

M_B_DATA0

M_B_A15

M_B_A13

M_B_A12

M_B_A11

M_B_A10

M_B_A9

M_B_A8

M_B_A7

M_B_A6

M_B_A5

M_B_A4

M_B_A3

M_B_A2

M_B_A1

M_B_A0

AD11

AF11

AF14

AE14

AB11

AC12

AF13

AF15

AF16

AC18

AF19

AD14

AC14

AE18

AD18

AD20

AC20

AF23

AF24

AF20

AE20

AD22

AC22

AE25

AD26

AA25

AA26

AE24

AD24

AA23

AA24

W25

Y11

G24

G23

D26

C26

G26

G25

E24

E23

C24

B24

C20

B20

C25

D24

A21

D20

D18

C18

D14

C14

A20

A19

A16

A15

A13

D12

E11

G11

B14

A14

A11

C11

U25

M26

N23

N24

N25

N26

P24

P26

T24

J25

J26

L23

L25

L24

L26

U15D

PZ638X3-284S-01

MB_DATA<63>

MB_DATA<62>

MB_DATA<61>

MB_DATA<60>

MB_DATA<59>

MB_DATA<58>

MB_DATA<57>

MB_DATA<56>

MB_DATA<55>

MB_DATA<54>

MB_DATA<53>

MB_DATA<52>

MB_DATA<51>

MB_DATA<50>

MB_DATA<49>

MB_DATA<48>

MB_DATA<47>

MB_DATA<46>

MB_DATA<45>

MB_DATA<44>

MB_DATA<43>

MB_DATA<42>

MB_DATA<41>

MB_DATA<40>

MB_DATA<39>

MB_DATA<38>

MB_DATA<37>

MB_DATA<36>

MB_DATA<35>

MB_DATA<34>

MB_DATA<33>

MB_DATA<32>

MB_DATA<31>

MB_DATA<30>

MB_DATA<29>

MB_DATA<28>

MB_DATA<27>

MB_DATA<26>

MB_DATA<25>

MB_DATA<24>

MB_DATA<23>

MB_DATA<22>

MB_DATA<21>

MB_DATA<20>

MB_DATA<19>

MB_DATA<18>

MB_DATA<17>

MB_DATA<16>

MB_DATA<15>

MB_DATA<14>

MB_DATA<13>

MB_DATA<12>

MB_DATA<11>

MB_DATA<10>

MB_DATA<9>

MB_DATA<8>

MB_DATA<7>

MB_DATA<6>

MB_DATA<5>

MB_DATA<4>

MB_DATA<3>

MB_DATA<2>

MB_DATA<1>

MB_DATA<0>

MB_ADD<15>

MB_ADD<14>

MB_ADD<13>

MB_ADD<12>

MB_ADD<11>

MB_ADD<10>

MB_ADD<9>

MB_ADD<8>

MB_ADD<7>

MB_ADD<6>

MB_ADD<5>

MB_ADD<4>

MB_ADD<3>

MB_ADD<2>

MB_ADD<1>

MB_ADD<0>

SKT638

SEC 4 OF 6

MEMORY_B

2

MB_DM<7>

MB_DM<6>

MB_DM<5>

MB_DM<4>

MB_DM<3>

MB_DM<2>

MB_DM<1>

MB_DM<0>

MB_DQS<7>

MB_DQS<6>

MB_DQS<5>

MB_DQS<4>

MB_DQS<3>

MB_DQS<2>

MB_DQS<1>

MB_DQS<0>

MB_DQS<7>*

MB_DQS<6>*

MB_DQS<5>*

MB_DQS<4>*

MB_DQS<3>*

MB_DQS<2>*

MB_DQS<1>*

MB_DQS<0>*

MB0_CLK<1>

MB0_CLK<1>*

MB0_CLK<2>

MB0_CLK<2>*

MB_BANK<2>

MB_BANK<1>

MB_BANK<0>

MB_RAS*

MB_CAS*

MB_WE*

MB0_CS<3>*

MB0_CS<2>*

MB0_CS<1>*

MB0_CS<0>*

MB_CKE<1>

MB_CKE<0>

MB0_ODT<1>

MB0_ODT<0>

VTT_SENSE

M_VREF

M_ZN

M_B_DM7

AD12

M_B_DM6

AC16

M_B_DM5

AE22

M_B_DM4

AB26

M_B_DM3

E25

M_B_DM2

A22

M_B_DM1

B16

M_B_DM0

A12

M_B_DQS7

AF12

M_B_DQS6

AE16

M_B_DQS5

AF21

M_B_DQS4

AC25

M_B_DQS3

F26

M_B_DQS2

A24

M_B_DQS1

D16

M_B_DQS0

C12

M_B_DQS#7

AE12

M_B_DQS#6

AD16

M_B_DQS#5

AF22

M_B_DQS#4

AC26

M_B_DQS#3

E26

M_B_DQS#2

A23

M_B_DQS#1

C16

M_B_DQS#0

B12

M_CLK_DDR2

A17

M_CLK_DDR#2

A18

AF18

M_CLK_DDR#3

AF17

M_B_BS2

K26

M_B_BS1

T26

U26

M_B_RAS#

U24

M_B_CAS#

V26

M_B_WE#

U22

M_B_CS3#

Y26

M_B_CS2#

J24

M_B_CS1#

W24

M_B_CS0#

U23

M_CKE3

H26

M_CKE2

J23

M_ODT3

W23

M_ODT2

W26

Y10

+0.9V

W17

R55

39.2_1%_04

Z0401

AE10

R56

39.2_1%_04

Z0402

AF10

M_P

I2

M_B_DATA[0..63]

M_B_A[15:0]

M_B_DM[0..7]

M_B_DQS[0..7]

M_B_DQS#[0..7]

2

Title

Size Document Number Rev

Date: Sheet of

4

+1.8V2,3,5,6,7,18,32

+0.9V5,6,7,32

M_B_DATA[0..63]7

M_B_A[15:0]7

M_B_DM[0..7]7

M_B_DQS[0..7]7

M_B_DQS#[0..7]7

3

1

TRACE FROM CAP TO CPU MUST BE LESS THAN 1200 MILS

MAX NECKDOWN TO & FROM CAPS IS 500 MILS

C482

1.5PF_NPO_04

C146

1.5PF_NPO_04

M_B_BS27

M_B_BS17

M_B_BS07

M_B_RAS#7

M_B_CAS#7

M_B_WE#7

M_B_CS3#7

M_B_CS2#7

M_B_CS1#7

M_B_CS0#7

M_CKE37

M_CKE27

M_ODT37

M_ODT27

M_CLK_DDR27

M_CLK_DDR#27

M_CLK_DDR37

M_CLK_DDR#37

M_VREF

15 MIL TRACE

20 MIL SPACE SHORTERTHAN 6INCH

CPU_M_VREF

C145

C135

+1.8V

1000p_04

1000p_04

藍天電腦 CLEVO

04 AMD S1:MEMORY

3546

Wednesday, May 24, 2006

6-71-M55E0-002

1

C136

0.1u_04

4 44

+1.8V

R75

2K_1%_04

R74

2K_1%_04

2.0

SKT638

SEC 6 OF 6

GROUND

5

VCORE +1.8V

J6

VSS

J8

VSS

J10

VSS

J12

VSS

J14

VSS

J16

VSS

J18

VSS

K2

VSS

K7

VSS

K9

VSS

K11

VSS

K13

VSS

K15

VSS

K17

VSS

L6

VSS

L8

VSS

L10

VSS

L12

VSS

L14

VSS

L16

VSS

L18

VSS

M7

VSS

M9

VSS

M11

VSS

M17

VSS

N4

VSS

N6

VSS

N8

VSS

N10

VSS

N16

VSS

N18

VSS

P2

VSS

P7

VSS

P9

VSS

P11

VSS

P17

VSS

R8

VSS

R10

VSS

R16

VSS

R18

VSS

T7

VSS

T9

VSS

T11

VSS

T13

VSS

T15

VSS

T17

VSS

U4

VSS

U6

VSS

U8

VSS

U10

VSS

U12

VSS

U14

VSS

U16

VSS

U18

VSS

V2

VSS

V7

VSS

V9

VSS

V11

VSS

V13

VSS

V15

VSS

V17

VSS

W6

VSS

Y21

VSS

Y23

VSS

AC4

AD2

M10

M16

G4

H2

J9

J11

J13

J15

K6

K10

K12

K14

K16

L4

L7

L9

L11

L13

L15

M2

M6

M8

N7

N9

N11

P8

P10

P16

R4

R7

R9

R11

T2

T6

T8

T10

T12

T14

T16

U7

U9

U11

U13

U15

V6

V8

V10

V12

V14

V16

W4

Y2

U15E

PZ638X3-284S-01

SKT638

SEC 5 OF 6

POWER

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

I72

U15F

PZ638X3-284S-01

AA4

VSS

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AB2

VSS

AB7

VSS

AB9

D D

C C

B B

AB23

AB25

AC11

AC13

AC15

AC17

AC19

AC21

AD25

AE11

AE13

AE15

AE17

AE19

AE21

AE23

AD6

AD8

B11

B13

B15

B17

B19

B21

B23

B25

D11

D13

D15

D17

D19

D21

D23

D25

F11

F13

F15

F17

F19

F21

F23

F25

H21

H23

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

B4

VSS

B6

VSS

B8

VSS

B9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

D6

VSS

D8

VSS

D9

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

E4

VSS

F2

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H7

VSS

H9

VSS

VSS

VSS

J4

VSS

I73

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

VDDIO

4

H25

J17

K18

K21

K23

K25

L17

M18

M21

M23

M25

N17

P18

P21

P23

P25

R17

T18

T21

T23

T25

U17

V18

V21

V23

V25

Y25

+0.9V

A10

VTT

AA10

VTT

AB10

VTT

AC10

VTT

AD10

VTT

B10

VTT

C10

VTT

D10

VTT

W10

VTT

VCORE

C118

22u_08_X5R

C134

0.22u_04

MEMORY VTT

LAYOUT: PLACE CLOSE TO CPU

BETWEEN CPU AND MEMORY

C483

C116

1000p_04

0.22u_04

LAYOUT: PLACE CLOSE TO CPU

C493

4.7u_X5R

C497

4.7u_X5R

CPU VDD

LAYOUT: PLACE UNDER CPU ON BACK

C125

22u_08_X5R

C133

0.22u_04

C115

1000p_04

C495

4.7u_X5R

C129

180p_X7R_04

C117

1000p_04

C500

4.7u_X5R

C130

1u_04

C114

1000p_04

3

C164

22u_08_X5R

C131

0.01u_04

C486

0.22u_04

C113

*22u_08_X5R

C468

180p_X7R_04

C487

0.22u_04

C89

22u_08_X5R

C471

180p_X7R_04

C491

0.22u_04

C124

22u_08_X5R

C119

*22u_08_X5R

C469

180p_X7R_04

C95

*22u_08_X5R

0406

C473

180p_X7R_04

2

1

+1.8V

LAYOUT: PLACE UNDER CPU ON BACK

C192

22u_08_X5R

+1.8V

C202

22u_08_X5R

C142

0.22u_04

C522

0.22u_04

BETWEEN CPU AND MEMORY

C516

4.7u_X5R

C151

0.22u_04

C143

0.22u_04

C139

0.22u_04

C141

0.22u_04

C520

4.7u_X5R

0406

C518

4.7u_X5R

C521

4.7u_X5R

C138

0.01u_04

C523

0.01u_04

C517

180p_X7R_04

C515

180p_X7R_04

+1.8VS

+VDD5 +1.8V +1.8VS

+1.8VS+1.8V

R52

Q16 AO3400

D S

C140

C128

100K_04_1%

G

Z0501

DS

default:LOW

SUSB18,31,32,34

A A

+VDD52,8,17,25,31,32,33,34,35

+1.8VS3,13

+1.2V_HT2,3,9,13

+1.8V2,3,4,6,7,18,32

+0.9V4,6,7,32

VCORE3,33

+3VS2,3,6,7,8,11,12,13,14,15,16,17,19,20,21,23,25,26,28,29,30,31

5

4

Q15

2N7002

C109

G

0.1u_04

3

C122

0.1u_04

C123

0.1u_04

0.1u_X7R_04

PLACE NEAR PULLUPS

2

0.1u_04

藍天電腦 CLEVO

Title

Size Document Number Rev

Date: Sheet of

05 AMD S1 :POWER

3546

Wednesday, May 24, 2006

6-71-M55E0-002

5 44

1

2.0

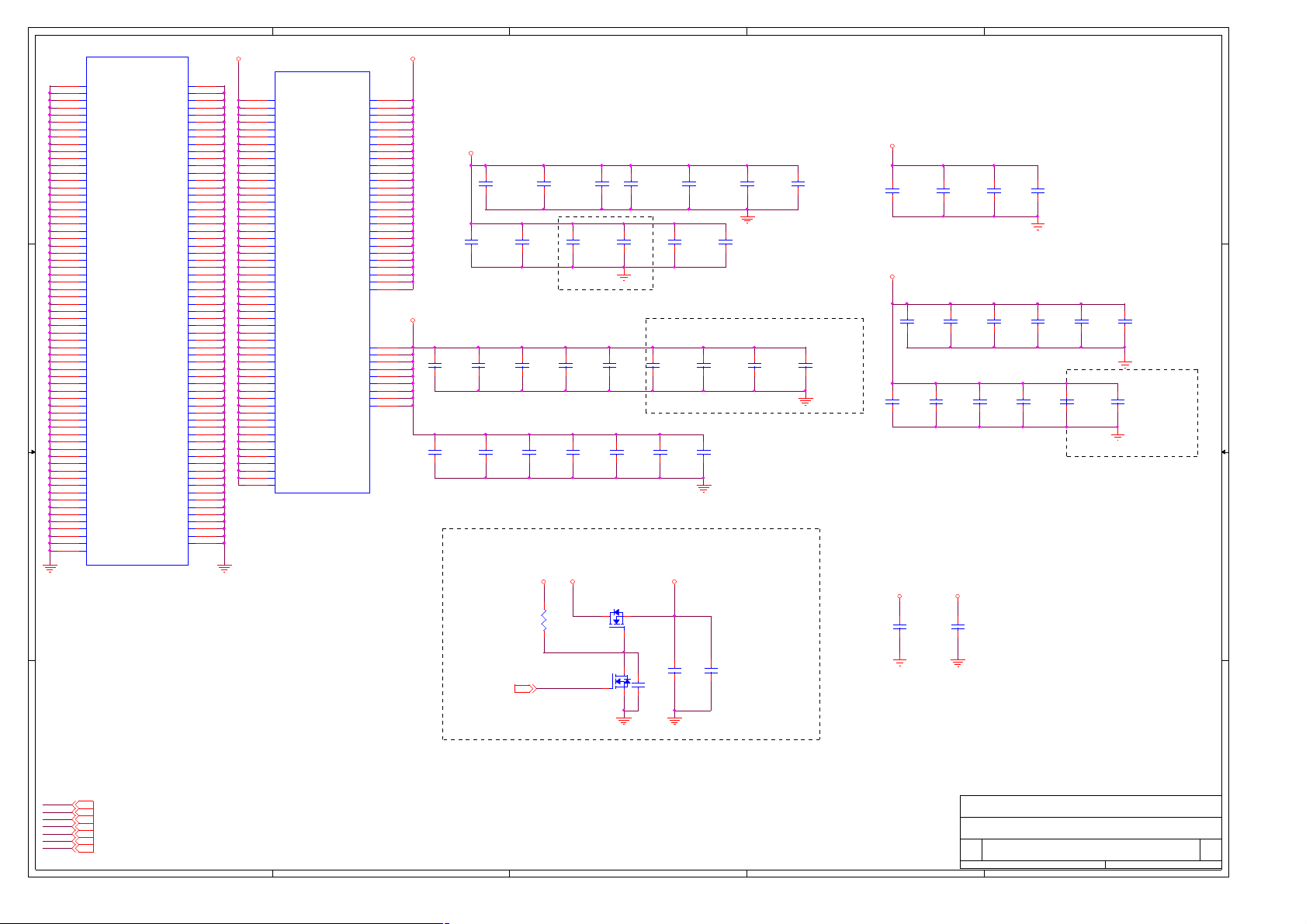

5

4

3

2

1

M_A_CS2#4

M_A_CS3#4

C310

SDREFC7

2.2u

+1.8V

C549

0.1u_04

M_A_CS2#

M_A_CS3#

C583

0.1u_04

112

111

117

96

95

118

81

82

87

103

88

104

199

83

120

50

69

163

201

202

47

133

183

77

12

48

184

78

71

72

121

122

196

193

1

8

C546

0.1u_04

JDIMM1B

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDDSPD

NC1

NC2

NC3

NC4

NCTEST

VREF

GND0

GND1

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

CA0115-200N02

C585

0.1u_04

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

C582

0.22u_04

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

C584

0.22u_04

C589

C5871uC588

1u

1u

M_CKE0

M_A_CS2#

M_A_BS2

M_A_A12

M_A_A9

M_A_A8

M_A_A5

M_A_A3

M_A_A1

M_A_A10

M_A_BS0

M_A_WE#

M_A_CAS#

M_A_CS1#

M_ODT1

M_CKE1

M_A_A15

M_A_A14

M_A_A11

M_A_A7

M_A_A6

M_A_A4

M_A_A2

M_A_A0

M_A_BS1

M_A_RAS#

M_A_CS0#

M_ODT0

M_A_A13

M_A_CS3#

C290

4.7u_08

C307

10u_08

81

72

6

5

81

72

6

5

81

72

6

5

81

72

6

5

3

4

3

4

3

4

3

4

C303

4.7u_08

RN1 8P4RX47_04

3

4

RN2 8P4RX47_04

3

4

RN3 8P4RX47_04

3

4

RN4 8P4RX47_04

3

4

RN5 8P4RX47_04

8 1

7 2

6

5

RN6 8P4RX47_04

8 1

7 2

6

5

RN7 8P4RX47_04

8 1

7 2

6

5

RN8 8P4RX47_04

8 1

7 2

6

5

C317

10u_08

+0.9V

C286 0.1u_04

C288 0.1u_04

C289 0.1u_04

C284 0.1u_04

C285 0.1u_04

C287 0.1u_04

C322 0.1u_04

12

C586

+

220u_4V_7343

D D

M_A_A[15:0]4

M_A_BS24

M_A_BS04

M_A_BS14

M_A_CS0#4

C C

B B

M_A_CS1#4

M_CLK_DDR04

M_CLK_DDR#04

M_CLK_DDR14

M_CLK_DDR#14

M_CKE04

M_CKE14

M_A_CAS#4

M_A_RAS#4

M_A_WE#4

MEM_SBCLK7,17

MEM_SBDATA7,17

M_ODT04

M_ODT14

M_A_DM[0..7]4

M_A_DQS[0..7]4

M_A_DQS#[0..7]4

M_A_A[15:0]

M_A_BS2

M_A_BS0

M_A_BS1

M_CKE0

M_CKE1

M_A_CAS#

M_A_RAS#

M_A_WE#

MEM_SBCLK

MEM_SBDATA

M_ODT0

M_ODT1

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

JDIMM1A

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

85

107

106

110

115

30

32

164

166

79

80

113

108

109

198

200

197

195

114

119

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

CA0115-200N02

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

A16_BA2

BA0

BA1

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

M_A_DATA1

7

M_A_DATA2

17

M_A_DATA3

19

M_A_DATA4

4

M_A_DATA5

6

M_A_DATA6

14

M_A_DATA7

16

M_A_DATA8

23

M_A_DATA9

25

M_A_DATA10

35

M_A_DATA11

37

M_A_DATA12

20

M_A_DATA13

22

M_A_DATA14

36

M_A_DATA15

38

M_A_DATA16

43

M_A_DATA17

45

M_A_DATA18

55

M_A_DATA19

57

M_A_DATA20

44

M_A_DATA21

46

M_A_DATA22

56

M_A_DATA23

58

M_A_DATA24

61

M_A_DATA25

63

M_A_DATA26

73

M_A_DATA27

75

M_A_DATA28

62

M_A_DATA29

64

M_A_DATA30

74

M_A_DATA31

76

M_A_DATA32

123

M_A_DATA33

125

M_A_DATA34

135

M_A_DATA35

137

M_A_DATA36

124

M_A_DATA37

126

M_A_DATA38

134

M_A_DATA39

136

M_A_DATA40

141

M_A_DATA41

143

M_A_DATA42

151

M_A_DATA43

153

M_A_DATA44

140

M_A_DATA45

142

M_A_DATA46

152

M_A_DATA47

154

M_A_DATA48

157

M_A_DATA49

159

M_A_DATA50

173

M_A_DATA51

175

M_A_DATA52

158

M_A_DATA53

160

M_A_DATA54

174

M_A_DATA55

176

M_A_DATA56

179

M_A_DATA57

181

M_A_DATA58

189

M_A_DATA59

191

M_A_DATA60

180

M_A_DATA61

182

M_A_DATA62

192

M_A_DATA63

194

M_A_DATA0

5

M_A_DATA[0..63]

+1.8V

R186

2K_1%_04

R194

2K_1%_04

M_A_DATA[0..63]4

+3VS

C315

0.1u_04

SDREFC

C304

2.2u

Layout Note:Place these Caps near So-Dimm0

DDRVREF GEN. & DECOUPLING

Trace Width 12 Mil

Space 20 Mil

A A

藍天電腦 CLEVO

+0.9V4,5,7,32

+1.8V2,3,4,5,7,18,32

+3VS2,3,7,8,11,12,13,14,15,16,17,19,20,21,23,25,26,28,29,30,31

5

Title

Size Document Number Rev

4

3

2

Date: Sheet of

06 DDR2-1

3546

Wednesday, May 24, 2006

6-71-M55E0-002

6 44

1

2.0

5

4

3

2

1

D D

M_B_DATA[0..63]

M_B_A[15:0]4

C C

+3VS

R201

1K_04

B B

M_B_A[15:0]

M_B_BS24

M_B_BS04

M_B_BS14

M_B_CS0#4

M_B_CS1#4

M_CLK_DDR24

M_CLK_DDR#24

M_CLK_DDR34

M_CLK_DDR#34

M_CKE24

M_CKE34

M_B_CAS#4

M_B_RAS#4

M_B_WE#4

MEM_SBCLK6,17

MEM_SBDATA6,17

M_ODT24

M_ODT34

M_B_DM[0..7]4

M_B_DQS[0..7]4

M_B_DQS#[0..7]4

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_BS2

M_B_BS0

M_B_BS1

M_B_CS0#

M_B_CS1#

M_B_CAS#

M_B_RAS#

M_B_WE#

Z0701

MEM_SBCLK

MEM_SBDATA

M_ODT2

M_ODT3

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

JDIMM2A

102

A0

101

A1

100

A2

99

A3

98

A4

97

A5

94

A6

92

A7

93

A8

91

A9

105

A10/AP

90

A11

89

A12

116

A13

86

A14

84

A15

85

A16_BA2

107

BA0

106

BA1

110

S0#

115

S1#

30

CK0

32

CK0#

164

CK1

166

CK1#

79

CKE0

80

CKE1

113

CAS#

108

RAS#

109

WE#

198

SA0

200

SA1

197

SCL

195

SDA

114

ODT0

119

ODT1

10

DM0

26

DM1

52

DM2

67

DM3

130

DM4

147

DM5

170

DM6

185

DM7

13

DQS0

31

DQS1

51

DQS2

70

DQS3

131

DQS4

148

DQS5

169

DQS6

188

DQS7

11

DQS0#

29

DQS1#

49

DQS2#

68

DQS3#

129

DQS4#

146

DQS5#

167

DQS6#

186

DQS7#

CA0145-200N02

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

M_B_DATA1

7

M_B_DATA2

17

M_B_DATA3

19

M_B_DATA4

4

M_B_DATA5

6

M_B_DATA6

14

M_B_DATA7

16

M_B_DATA8

23

M_B_DATA9

25

M_B_DATA10

35

M_B_DATA11

37

M_B_DATA12

20

M_B_DATA13

22

M_B_DATA14

36

M_B_DATA15

38

M_B_DATA16

43

M_B_DATA17

45

M_B_DATA18

55

M_B_DATA19

57

M_B_DATA20

44

M_B_DATA21

46

M_B_DATA22

56

M_B_DATA23

58

M_B_DATA24

61

M_B_DATA25

63

M_B_DATA26

73

M_B_DATA27

75

M_B_DATA28

62

M_B_DATA29

64

M_B_DATA30

74

M_B_DATA31

76

M_B_DATA32

123

M_B_DATA33

125

M_B_DATA34

135

M_B_DATA35

137

M_B_DATA36

124

M_B_DATA37

126

M_B_DATA38

134

M_B_DATA39

136

M_B_DATA40

141

M_B_DATA41

143

M_B_DATA42

151

M_B_DATA43

153

M_B_DATA44

140

M_B_DATA45

142

M_B_DATA46

152

M_B_DATA47

154

M_B_DATA48

157

M_B_DATA49

159

M_B_DATA50

173

M_B_DATA51

175

M_B_DATA52

158

M_B_DATA53

160

M_B_DATA54

174

M_B_DATA55

176

M_B_DATA56

179

M_B_DATA57

181

M_B_DATA58

189

M_B_DATA59

191

M_B_DATA60

180

M_B_DATA61

182

M_B_DATA62

192

M_B_DATA63

194

DDRVREF GEN. & DECOUPLING

Trace Width 12 Mil

Space 20 Mil

M_B_DATA0

5

SDREFC6

+3VS

C305

0.1u_04

M_B_DATA[0..63]4

M_B_CS2#4

M_B_CS3#4

SDREFC

C306

0.1u_04

+1.8V

M_B_CS2#

M_B_CS3#

C545

0.1u_04

112

111

117

96

95

118

81

82

87

103

88

104

199

83

120

50

69

163

201

202

47

133

183

77

12

48

184

78

71

72

121

122

196

193

1

8

C547

0.1u_04

JDIMM2B

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDDSPD

NC1

NC2

NC3

NC4

NCTEST

VREF

GND0

GND1

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

CA0145-200N02

C548

0.1u_04

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

C551

0.1u_04

18

24

41

53

42

54

59

65

60

66

127

139

128

145

165

171

172

177

187

178

190

9

21

33

155

34

132

144

156

168

2

3

15

27

39

149

161

28

40

138

150

162

C544

0.22u_04

C550

0.22u_04

C294

C318

C296

1u

1u

1u

RN9 8P4RX47_04

M_CKE2

M_B_CS2#

M_B_BS2

M_B_A12

RN10 8P4RX47_04

M_B_A9

M_B_A8

M_B_A5

M_B_A3

RN11 8P4RX47_04

M_B_A1

M_B_A10

M_B_WE#

M_B_BS0

RN12 8P4RX47_04

M_B_CAS#

M_B_CS1#

M_ODT3

RN13 8P4RX47_04

M_B_A14

M_B_A15

M_CKE3

M_B_A11

RN14 8P4RX47_04

M_B_A7

M_B_A6

M_B_A4

M_B_A2

RN15 8P4RX47_04

M_B_A0

M_B_BS1

M_B_RAS#

M_B_CS0#

RN16 8P4RX47_04

M_ODT2

M_B_A13

M_B_CS3#

C291

4.7u_08

3

4

3

4

3

4

3

4

8 1

7 2

6

5

8 1

7 2

6

5

8 1

7 2

6

5

8 1

7 2

6

5

12

C179

C316

10u_08

+

220u_4V_7343

C311

C292

10u_08

4.7u_08

+0.9V

81

72

6

5

81

72

6

5

81

72

6

5

81

72

6

5

3

4

3

4

3

4

3

4

C325 0.1u_04

C326 0.1u_04

C329 0.1u_04

C323 0.1u_04

C324 0.1u_04

C327 0.1u_04

C328 0.1u_04

A A

藍天電腦 CLEVO

+0.9V4,5,6,32

+1.8V2,3,4,5,6,18,32

+3VS2,3,6,8,11,12,13,14,15,16,17,19,20,21,23,25,26,28,29,30,31

5

4

3

2

Title

Size Document Number Rev

Date: Sheet of

07 DDR2-2

3546

Wednesday, May 24, 2006

6-71-M55E0-002

1

7 44

2.0

5

4

3

2

1

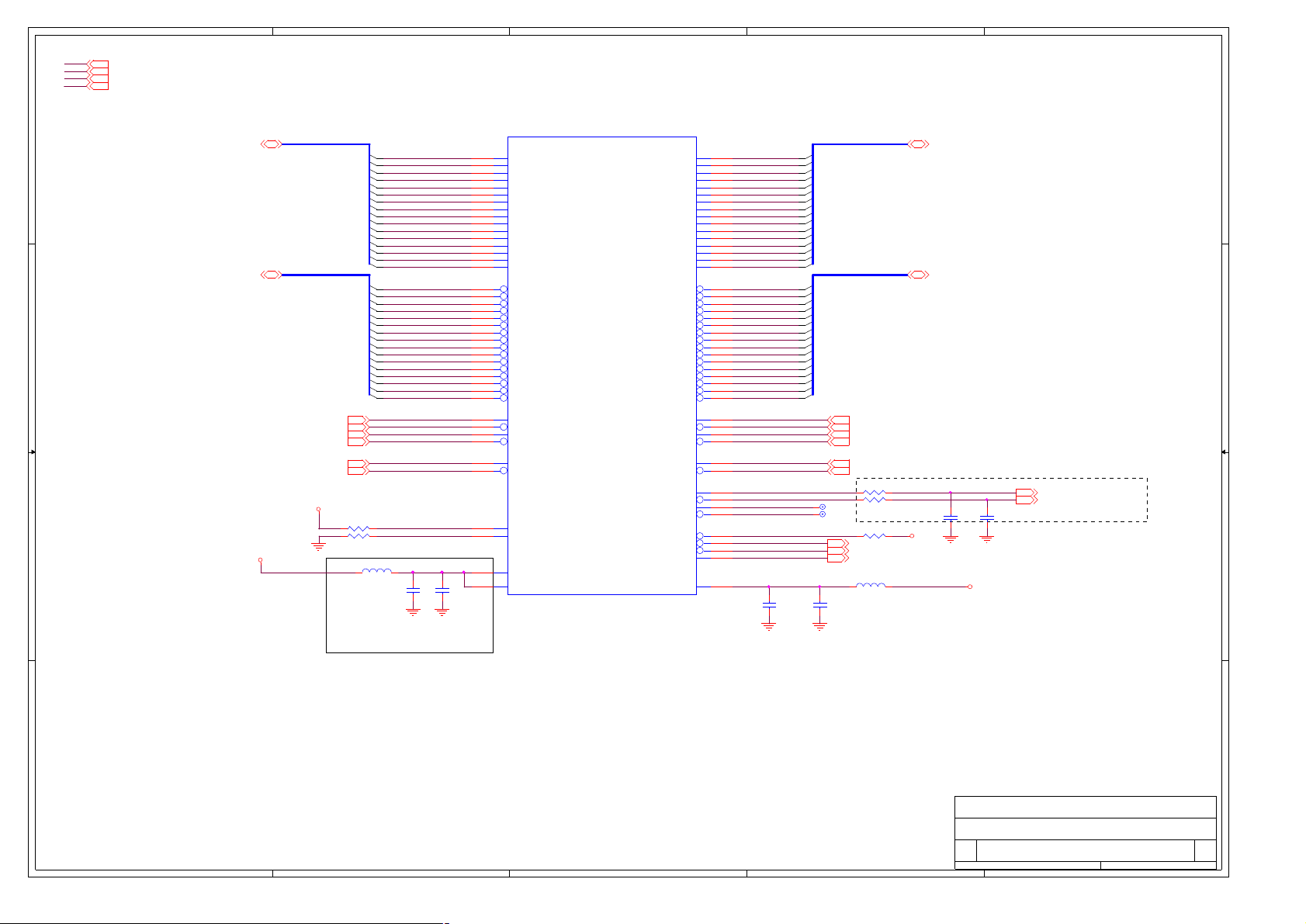

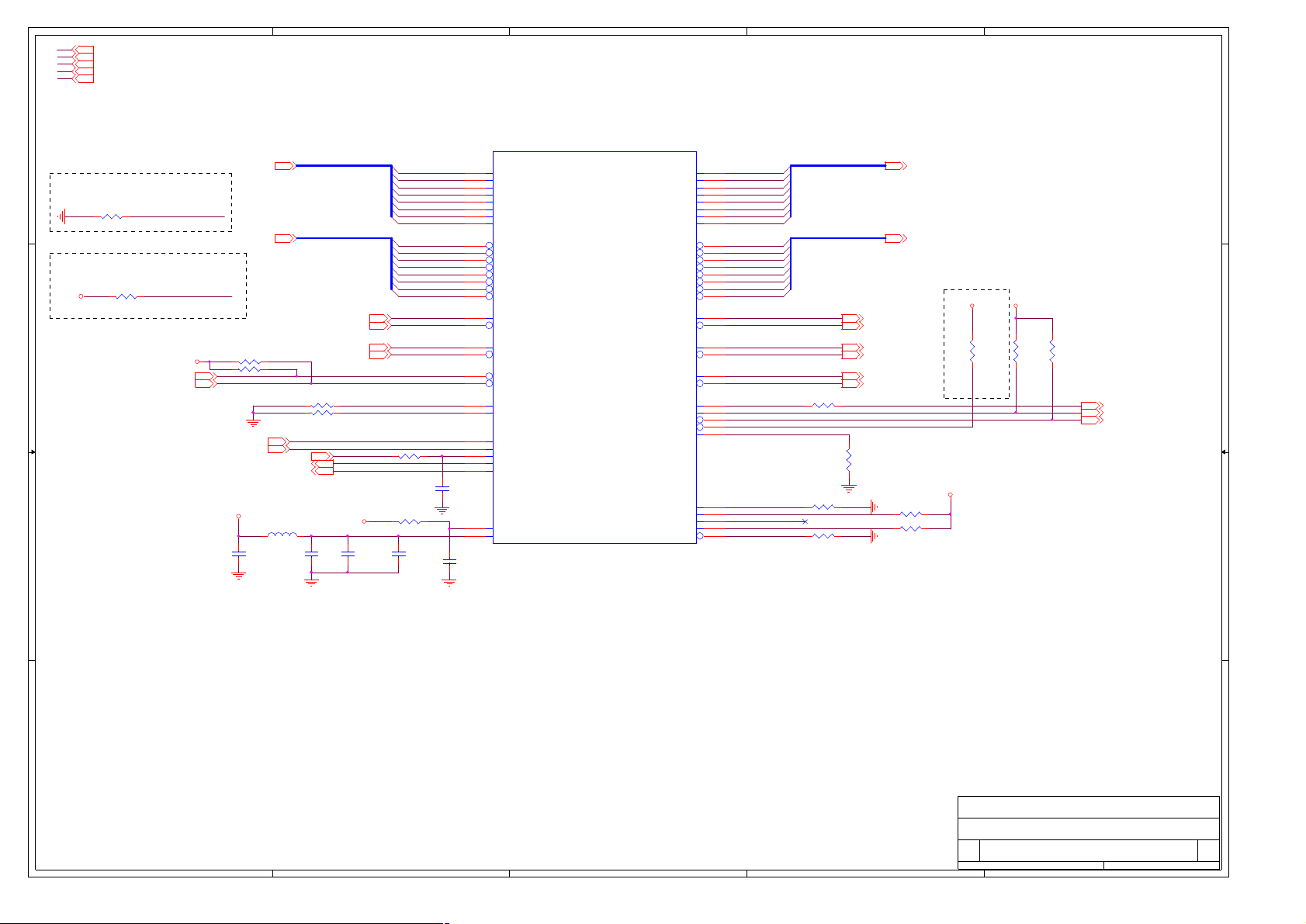

PANEL

LVDS-L0N

LVDS-L0P

ENAVDD17

AC

AC

AC

LVDS-L1N

LVDS-L1P

LVDS-L2N

LVDS-L2P

LVDS-LCLKN

LVDS-LCLKP

LVDS-U0N

LVDS-U0P

LVDS-U1N

LVDS-U1P

LVDS-U2N

LVDS-U2P

LVDS-UCLKN

LVDS-UCLKP

0329

D48

SCS751V

123

+VDD5

C489 0.47u

R334 330K_04_1%

R335

0_04

+3VS

R540

20K_1%

INV_BLON

AC

45

8P4CX10p

CP1

678

+3VS

2A 2A

C494

0.1u_04

Z0801

Z0802

G

R336

10K_04

R516

82K_1%

4

123

45

8P4CX10p

CP2

678

12-1001D-0B0

Q51

AO3415

DS

G

R337

56K_04

Z0811

DS

Q50

BSS138

INV_BLON25

123

45

678

Pin S & pin D trace

width min. 80 mils.

C477

0.1u_04

DS

G

8P4CX10p

CP3

R331

200_1%

Z0803

Q49

2N7002

123

PLVDD

R332

200_1%

PLVDD

1.5A

C481

C480

*10u_08

0.1u_04

LVDS-L0N

LVDS-L0P

LVDS-L1N

LVDS-L1P

LVDS-L2N

LVDS-L2P

LVDS-LCLKN

LVDS-LCLKP

LVDS-U0N

LVDS-U0P

LVDS-U1N

LVDS-U1P

LVDS-U2N

LVDS-U2P

LVDS-UCLKN

LVDS-UCLKP

CLCDID3

CLCDID2

CLCDID0

JLCD

30

1

GND1

GND2

GND3

GND4

JLCD1

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

Shield1

27

Shield2

28

Shield3

29

Shield4

30

LVC-C30SFYG

1

2

3

4

5

6

7

8

9

D D

C C

0323 Change

B B

INVERTER CONNECTOR

BLON17

A A

PWRGD3,17,24,25

+3VS +3VS

G

R547

10K_04

DS

Q87

2N7002

D39 SCS751V

D38 SCS751V

D46 SCS751V

R575

10K_04

Z0809 Z0810

DS

G

Q88

2N7002

R546 *0_04

R548

1K_04

H8BKLEN24

LID_SW#24

5

678

45

8P4CX10p

CP4

LVDS-L0N12

LVDS-L0P12

LVDS-L1N12

LVDS-L1P12

LVDS-L2N12

LVDS-L2P12

LVDS-LCLKN12

LVDS-LCLKP12

LVDS-U0N12

LVDS-U0P12

LVDS-U1N12

LVDS-U1P12

LVDS-U2N12

LVDS-U2P12

LVDS-UCLKN12

LVDS-UCLKP12

3

PANLE ID SELECTOR

+3VS

123

678

LCDID0 LCDID2 LCDID3

0 ( GND )

0 ( GND )

1 ( NC )

1 ( NC )

0 ( GND )

0 ( GND )

0 ( GND )

PANEL ID Select

TYPE

15" XGA

15" XGA

AU B150XG01

CPT CLAA150XH01

15" SXGA+AU B150PG03

15" SXGA+

14" WXGA

14" WXGA

14" WXGA

CPT CLAA150PB03

Hydis HT140WX1-100

AU B140EW01

SAMSUNG LTN140W1-L01

CLCDID3

CLCDID2

CLCDID0

PANEL MODEL JLCD-30(GPIO62)JLCD-29(GPIO61)JLCD-28(GPIO60)

FAN CONTROL

+VDD5

C424

FAN_ON24

FAN_SEN24

R281

4.99K_1%

R282 10K_04

v2.0 0517`06

0.1u_04

Z0805FAN_DC_VOL

2

U12A

84

LM358

3

+

1

2

-

+VDD3

+3V3,15,17,18,19,20,21,22,25,27,29,31,32,33

+3VS2,3,6,7,11,12,13,14,15,16,17,19,20,21,23,25,26,28,29,30,31

+5VH823,24,31

+5VS19,20,21,22,23,24,25,26,27,31

+VDD52,5,17,25,31,32,33,34,35

+VIN24,25,31,32,33,34,35

+VDD33,18,24,25,31,35

Title

Size Document Number Rev

Date: Sheet of

45

RN18

8P4RX10K_04

RN19 8P4RX1K

1

8

2

3

4 5

7

6

Z0804

Coaxial Cable

+VDD5

C420

10u_08

G

Z0808

R279 4.7K_04

AC

D19 SCS551V

CLEVO CO. 藍天電腦

3546

LCDID317

LCDID217

LCDID017

0323 Change

0 ( GND )

0 ( GND )

0 ( GND )

0 ( GND )

0 ( GND )

0 ( GND )

0 ( GND )

0 ( GND )

1 ( NC ) 0 ( GND )

1 ( NC ) 0 ( GND )

D20

SCS551V

A C

0 ( GND )

+VDD5

5

+

6

-

JFAN1

1

2

3

85205-0300

1 ( NC )

L30

HCB2012K-500T40

Z0807

Q42

NDS352

D S

FAN_DC_VOL

C421

+

100u/6.3V_B

6-71-M55E0-002

8 44Wednesday, May 24, 2006

1

U12B

LM358

7

JFAN

3

1

2.0A3

5

+1.2V_HT2,3,13

+3VS2,3,6,7,8,11,12,13,14,15,16,17,19,20,21,23,25,26,28,29,30,31

+2.6VS3,12,13,31

+1.2VPLL_PWR11,12,13

D D

L0_CADOUT_H[15..0]2

L0_CADOUT_L[15..0]2

C C

L0_CADOUT_H[15..0]

L0_CADOUT_L[15..0]

L0_CLKOUT_H02

L0_CLKOUT_L02

L0_CLKOUT_H12

L0_CLKOUT_L12

L0_CTLOUT_H02

L0_CTLOUT_L02

+1.2V_HT

R62 150_1%

R58 150_1%

B B

+1.2VPLL_PWR

L10

4

1 2

HCB1608K-121T25

L0_CADOUT_H0

L0_CADOUT_H1

L0_CADOUT_H2

L0_CADOUT_H3

L0_CADOUT_H4

L0_CADOUT_H5

L0_CADOUT_H6

L0_CADOUT_H7

L0_CADOUT_H8

L0_CADOUT_H9

L0_CADOUT_H10

L0_CADOUT_H11

L0_CADOUT_H12

L0_CADOUT_H13

L0_CADOUT_H14

L0_CADOUT_H15

L0_CADOUT_L0

L0_CADOUT_L1

L0_CADOUT_L2

L0_CADOUT_L3

L0_CADOUT_L4

L0_CADOUT_L5

L0_CADOUT_L6

L0_CADOUT_L7

L0_CADOUT_L8

L0_CADOUT_L9

L0_CADOUT_L10

L0_CADOUT_L11

L0_CADOUT_L12

L0_CADOUT_L13

L0_CADOUT_L14

L0_CADOUT_L15

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

HTCPUCAL_1P2V

HTCPUCAL_GND

1P2VPLL_FILT

C98

1u_04

C97

0.1u_X7R_04

W24

W21

M17

W23

W20

W22

M23

M22

W19

Y23

V24

U22

R24

P24

P22

N22

Y21

V21

T21

R18

P16

N20

Y22

V23

U21

R23

P23

P21

N21

Y20

U20

R19

P17

N19

N18

T23

T22

R21

R20

Y19

N16

T13

U13F

BGA

HT_CPU_RXD0_P

HT_CPU_RXD1_P

HT_CPU_RXD2_P

HT_CPU_RXD3_P

HT_CPU_RXD4_P

HT_CPU_RXD5_P

HT_CPU_RXD6_P

HT_CPU_RXD7_P

HT_CPU_RXD8_P

HT_CPU_RXD9_P

HT_CPU_RXD10_P

HT_CPU_RXD11_P

HT_CPU_RXD12_P

HT_CPU_RXD13_P

HT_CPU_RXD14_P

HT_CPU_RXD15_P

HT_CPU_RXD0_N

HT_CPU_RXD1_N

HT_CPU_RXD2_N

HT_CPU_RXD3_N

HT_CPU_RXD4_N

HT_CPU_RXD5_N

HT_CPU_RXD6_N

HT_CPU_RXD7_N

HT_CPU_RXD8_N

HT_CPU_RXD9_N

HT_CPU_RXD10_N

HT_CPU_RXD11_N

HT_CPU_RXD12_N

HT_CPU_RXD13_N

HT_CPU_RXD14_N

HT_CPU_RXD15_N

HT_CPU_RX_CLK0_P

HT_CPU_RX_CLK0_N

HT_CPU_RX_CLK1_P

HT_CPU_RX_CLK1_N

HT_CPU_RXCTL_P

HT_CPU_RXCTL_N

HT_CPU_CAL_1P2V

HT_CPU_CAL_GND

+1.2V_PLLHTCPU

+1.2V_PLLHTMCP

I105

C51

SEC 1 OF 6

3

HT_CPU_TXD0_P

HT_CPU_TXD1_P

HT_CPU_TXD2_P

HT_CPU_TXD3_P

HT_CPU_TXD4_P

HT_CPU_TXD5_P

HT_CPU_TXD6_P

HT_CPU_TXD7_P

HT_CPU_TXD8_P

HT_CPU_TXD9_P

HT_CPU_TXD10_P

HT_CPU_TXD11_P

HT_CPU_TXD12_P

HT_CPU_TXD13_P

HT_CPU_TXD14_P

HT_CPU_TXD15_P

HT_CPU_TXD0_N

HT_CPU_TXD1_N

HT_CPU_TXD2_N

HT_CPU_TXD3_N

HT_CPU_TXD4_N

HT_CPU_TXD5_N

HT_CPU_TXD6_N

HT_CPU_TXD7_N

HT_CPU_TXD8_N

HT_CPU_TXD9_N

HT_CPU_TXD10_N

HT_CPU_TXD11_N

HT_CPU_TXD12_N

HT_CPU_TXD13_N

HT_CPU_TXD14_N

HT_CPU_TXD15_N

HT_CPU_TX_CLK0_P

HT_CPU_TX_CLK0_N

HT_CPU_TX_CLK1_P

HT_CPU_TX_CLK1_N

HT_CPU_TXCTL_P

HT_CPU_TXCTL_N

CLKOUT_PRI_200MHZ_P

CLKOUT_PRI_200MHZ_N

CLKOUT_SEC_200MHZ_P

CLKOUT_SEC_200MHZ_N

HT_CPU_REQ*

HT_CPU_STOP*

HT_CPU_RESET*

HT_CPU_PWRGD

+2.5V_PLLHTCPU

C23

D23

E22

F23

H22

J21

K21

K23

D21

F19

F21

G20

J19

L17

L20

L18

C24

D24

E23

F24

H23

J22

K22

K24

D22

E20

E21

G19

J18

K17

K19

L19

G23

G24

G22

G21

L23

L24

B24

B23

A22

B21

F18

G18

D20

E19

L16

L0_CADIN_H0

L0_CADIN_H1

L0_CADIN_H2

L0_CADIN_H3

L0_CADIN_H4

L0_CADIN_H5

L0_CADIN_H6

L0_CADIN_H7

L0_CADIN_H8

L0_CADIN_H9

L0_CADIN_H10

L0_CADIN_H11

L0_CADIN_H12

L0_CADIN_H13

L0_CADIN_H14

L0_CADIN_H15

L0_CADIN_L0

L0_CADIN_L1

L0_CADIN_L2

L0_CADIN_L3

L0_CADIN_L4

L0_CADIN_L5

L0_CADIN_L6

L0_CADIN_L7

L0_CADIN_L8

L0_CADIN_L9

L0_CADIN_L10

L0_CADIN_L11

L0_CADIN_L12

L0_CADIN_L13

L0_CADIN_L14

L0_CADIN_L15

L0_CLKIN_H0

L0_CLKIN_L0

L0_CLKIN_H1

L0_CLKIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

CPUCLK_H#

CPUCLK_L#

TP_CLKOUT

TP_CLKOUT#

TP_HTCPU_REQ#

LDTSTOP#

CPURST#

CPU_PWRGD

2P5V_PLLHTCPU

C81

0.1u_X7R_04

2

L0_CADIN_H[15..0]

L0_CADIN_L[15..0]

L0_CLKIN_H02

L0_CLKIN_L02

L0_CLKIN_H12

L0_CLKIN_L12

L0_CTLIN_H02

L0_CTLIN_L02

R292 0_04

R291 0_04

T19

T20

R41 *20K_1%

LDTSTOP#3

CPURST#3

CPU_PWRGD3

L8 HCB1608K-121T25

1 2

+2.6VS

C88

4.7u_08

L0_CADIN_H[15..0] 2

L0_CADIN_L[15..0] 2

C450

*10p_04

+2.6VS

C447

*10p_04

CPUCLK_H3

CPUCLK_L3

1

Near the C51M

PLACE ON BACK SIDE

A A

藍天電腦 CLEVO

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

HT CPU

3546

Wednesday, May 24, 2006

6-71-M55E0-002

9

1

2.0

44

5

+1.2VS13,14,19,34

4

3

2

1

D D

HTMCP_UP[7..0]14

R60 *49.9_1%

RESISTOR FOR 4X4 LINK

OK TO FLOAT UNUSED

PINS

HTMCP_UP#[7..0]14 HTMCP_DWN#[7..0]14

RESISTOR FOR 4X4 LINK

OK TO FLOAT UNUSED

C C

B B

PINS

+1.2VS

R61 *49.9_1%

HTMCP_UP[7..0]

HTMCP_UP7

HTMCP_UP#[7..0]

HTMCP_UP#7

HTMCP_UPCLK014

HTMCP_UPCLK0#14

HTMCP_UPCNTL14

HTMCP_UPCNTL#14

HTMCP_REQ#14

HTMCP_STOP#14

HTMCP_RST#14

HTMCP_PWRGD14

MCPOUT_25MHZ14

MCPOUT_200MHZ14

MCPOUT_200MHZ#14

T21

T23

T25

T27

T29

T31

T33

T35

T37

T39

T41

T43

T45

T49

T51

T53

T55

HTMCP_UP0

HTMCP_UP1

HTMCP_UP2

HTMCP_UP3

HTMCP_UP4

HTMCP_UP5

HTMCP_UP6

HTMCP_UP7

TP_C51HTRXD9

TP_C51HTRXD10

TP_C51HTRXD11

TP_C51HTRXD12

TP_C51HTRXD13

TP_C51HTRXD14

TP_C51HTRXD15

HTMCP_UP#0

HTMCP_UP#1

HTMCP_UP#2

HTMCP_UP#3

HTMCP_UP#4

HTMCP_UP#5

HTMCP_UP#6

HTMCP_UP#7

TP_C51HTRXD9#

TP_C51HTRXD10#

TP_C51HTRXD11#

TP_C51HTRXD12#

TP_C51HTRXD13#

TP_C51HTRXD15#

HTMCP_UPCLK0

HTMCP_UPCLK0#

TP_HTMCP_UPCLK1

TP_HTMCP_UPCLK1#

HTMCP_UPCNTL

HTMCP_UPCNTL#

HTMCP_REQ#

HTMCP_STOP#

HTMCP_RST#

HTMCP_PWRGD

MCPOUT_25MHZ

MCPOUT_200MHZ

MCPOUT_200MHZ#

AD6

AC7

AA8

AA9

AD10

AD11

AC12

AC13

AA6

Y10

AA11

W12

AC6

AB7

AB8

AB9

AC10

AC11

AB12

AB13

AA7

W10

Y12

W11

AD9

AC9

U10

T10

AD14

AC14

AB5

AA5

AC5

AD5

AC4

W7

Y8

V9

V11

Y6

Y7

W9

V13

Y5

W5

U13A

BGA

HT_MCP_RXD0_P

HT_MCP_RXD1_P

HT_MCP_RXD2_P

HT_MCP_RXD3_P

HT_MCP_RXD4_P

HT_MCP_RXD5_P

HT_MCP_RXD6_P

HT_MCP_RXD7_P

HT_MCP_RXD8_P

HT_MCP_RXD9_P

HT_MCP_RXD10_P

HT_MCP_RXD11_P

HT_MCP_RXD12_P

HT_MCP_RXD13_P

HT_MCP_RXD14_P

HT_MCP_RXD15_P

HT_MCP_RXD0_N

HT_MCP_RXD1_N

HT_MCP_RXD2_N

HT_MCP_RXD3_N

HT_MCP_RXD4_N

HT_MCP_RXD5_N

HT_MCP_RXD6_N

HT_MCP_RXD7_N

HT_MCP_RXD8_N

HT_MCP_RXD9_N

HT_MCP_RXD10_N

HT_MCP_RXD11_N

HT_MCP_RXD12_N

HT_MCP_RXD13_N

HT_MCP_RXD14_N

HT_MCP_RXD15_N

HT_MCP_RX_CLK0_P

HT_MCP_RX_CLK0_N

HT_MCP_RX_CLK1_P

HT_MCP_RX_CLK1_N

HT_MCP_RXCTL_P

HT_MCP_RXCTL_N

HT_MCP_REQ*

HT_MCP_STOP*

HT_MCP_RESET*

HT_MCP_PWRGD

CLKIN_25MHZ

CLKIN_200MHZ_P

CLKIN_200MHZ_N

I164

C51

SEC 2 OF 6

SCLKIN_MCLKOUT_200MHZ_P

SCLKIN_MCLKOUT_200MHZ_N

HT_MCP_TXD0_P

HT_MCP_TXD1_P

HT_MCP_TXD2_P

HT_MCP_TXD3_P

HT_MCP_TXD4_P

HT_MCP_TXD5_P

HT_MCP_TXD6_P

HT_MCP_TXD7_P

HT_MCP_TXD8_P

HT_MCP_TXD9_P

HT_MCP_TXD10_P

HT_MCP_TXD11_P

HT_MCP_TXD12_P

HT_MCP_TXD13_P

HT_MCP_TXD14_P

HT_MCP_TXD15_P

HT_MCP_TXD0_N

HT_MCP_TXD1_N

HT_MCP_TXD2_N

HT_MCP_TXD3_N

HT_MCP_TXD4_N

HT_MCP_TXD5_N

HT_MCP_TXD6_N

HT_MCP_TXD7_N

HT_MCP_TXD8_N

HT_MCP_TXD9_N

HT_MCP_TXD10_N

HT_MCP_TXD11_N

HT_MCP_TXD12_N

HT_MCP_TXD13_N

HT_MCP_TXD14_N

HT_MCP_TXD15_N

HT_MCP_TX_CLK0_P

HT_MCP_TX_CLK0_N

HT_MCP_TX_CLK1_P

HT_MCP_TX_CLK1_N

HT_MCP_TXCTL_P

HT_MCP_TXCTL_N

CLKOUT_CTERM_GND

HT_MCP_CAL_1P2V

HT_MCP_CAL_GND

HTMCP_DWN0

AC24

HTMCP_DWN1

AD23

HTMCP_DWN2

AC22

HTMCP_DWN3

AC20

HTMCP_DWN4

AB18

HTMCP_DWN5

AA17

HTMCP_DWN6

AB16

HTMCP_DWN7

AC16

AB21

AB20

AB19

W18

W15

AA15

Y14

W13

HTMCP_DWN#0

AC23

HTMCP_DWN#1

AD22

HTMCP_DWN#2

AC21

HTMCP_DWN#3

AD20

HTMCP_DWN#4

AC18

HTMCP_DWN#5

AB17

HTMCP_DWN#6

AB15

HTMCP_DWN#7

AD16

AB22

AA20

AA19

V17

V15

Y15

W14

Y13

HTMCP_DWNCLK0

AC19

HTMCP_DWNCLK0#

AD19

TP_HTMCP_DWNCLK1

Y17

TP_HTMCP_DWNCLK1#

W17

HTMCP_DWNCNTL

AC15

HTMCP_DWNCNTL#

AD15

CLKOUT_CTERM

B22

TP_SLAVE_CLK

A20

TP_SLAVE_CLK#

B20

HTMCPCAL_1P2V

AB23

HTMCPCAL_GND

AB24

TP_C51HTTXD8TP_C51HTRXD8

TP_C51HTTXD9

TP_C51HTTXD10

TP_C51HTTXD11

TP_C51HTTXD12

TP_C51HTTXD13

TP_C51HTTXD14

TP_C51HTTXD15

TP_C51HTTXD8#TP_C51HTRXD8#

TP_C51HTTXD9#

TP_C51HTTXD10#

TP_C51HTTXD11#

TP_C51HTTXD12#

TP_C51HTTXD13#

TP_C51HTTXD14#TP_C51HTRXD14#

TP_C51HTTXD15#

HTMCP_DWN[7..0]

T22

T24

T26

T28

T30

T32

T34

T36

HTMCP_DWN#[7..0]

T38

T40

T42

T44

T46

T48T47

T50

T52

T54

T56

R286 2.37K_1%

T57

T58

R323 150_1%

R321 150_1%

HTMCP_DWN[7..0]14

HTMCP_DWNCLK014

HTMCP_DWNCLK0#14

HTMCP_DWNCNTL14

HTMCP_DWNCNTL#14

+1.2VS

A A

藍天電腦 CLEVO

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

C51M HT TO MCP & MUX

3546

Wednesday, May 24, 2006

6-71-M55E0-002

1

2.0

44

10

5

+3VS2,3,6,7,8,12,13,14,15,16,17,19,20,21,23,25,26,28,29,30,31

+1.2VPLL_PWR9,12,13

D D

C C

0329

Differential 20/5/5/5/20

+3VS

+3VS

PE1_RX_P20

PE1_RX_N20

WLAN_DET#20,24

Differential 20/5/5/5/20

B B

PE2_RX_P29

PE2_RX_N29

NEWCARD_DET#29

WLAN_CLKREQ#20

NEWCARD_CLKREQ#29

+3VS

+1.2VPLL_PWR

4

R294 10K_04

R295 10K_04

D21 SCS551V

AC

R209 10K_04

L13

1 2

HCB1608K-121T25

PE0_PRSNT#

PE1_RX_P

PE1_RX_N

PE1_PRSNT#

PE2_RX_P

PE2_RX_N

NEWCARD_DET#

WLAN_CLKREQ#

NEWCARD_CLKREQ#

1P2V_PLLPE

C104

AA3

AC3

AB3

T11

M9

N8

N6

R6

R8

U6

U7

M8

N7

N5

R5

R7

U5

U8

D1

G6

H6

D3

J8

J6

K9

L6

L7

P3

T8

V4

Y3

J7

J5

J9

L5

L8

P4

T9

V3

E2

J4

K3

E3

E4

U13B

BGA

PE0_RX0_P

PE0_RX1_P

PE0_RX2_P

PE0_RX3_P

PE0_RX4_P

PE0_RX5_P

PE0_RX6_P

PE0_RX7_P

PE0_RX8_P

PE0_RX9_P

PE0_RX10_P

PE0_RX11_P

PE0_RX12_P

PE0_RX13_P

PE0_RX14_P

PE0_RX15_P

PE0_RX0_N

PE0_RX1_N

PE0_RX2_N

PE0_RX3_N

PE0_RX4_N

PE0_RX5_N

PE0_RX6_N

PE0_RX7_N

PE0_RX8_N

PE0_RX9_N

PE0_RX10_N

PE0_RX11_N

PE0_RX12_N

PE0_RX13_N

PE0_RX14_N

PE0_RX15_N

PE0_PRSNT*

PE1_RX_P

PE1_RX_N

PE1_PRSNT*

PE2_RX_P

PE2_RX_N

PE2_PRSNT*

PE1_CLKREQ*/CLK

PE2_CLKREQ*/DATA

PE_REFCLKIN_P

PE_REFCLKIN_N

+1.2V_PLLPE

I103

C51

SEC 3 OF 6

3

PE0_TX0_P

PE0_TX1_P

PE0_TX2_P

PE0_TX3_P

PE0_TX4_P

PE0_TX5_P

PE0_TX6_P

PE0_TX7_P

PE0_TX8_P

PE0_TX9_P

PE0_TX10_P

PE0_TX11_P

PE0_TX12_P

PE0_TX13_P

PE0_TX14_P

PE0_TX15_P

PE0_TX0_N

PE0_TX1_N

PE0_TX2_N

PE0_TX3_N

PE0_TX4_N

PE0_TX5_N

PE0_TX6_N

PE0_TX7_N

PE0_TX8_N

PE0_TX9_N

PE0_TX10_N

PE0_TX11_N

PE0_TX12_N

PE0_TX13_N

PE0_TX14_N

PE0_TX15_N

PE0_REFCLK_P

PE0_REFCLK_N

PE1_TX_P

PE1_TX_N

PE1_REFCLK_P

PE1_REFCLK_N

PE2_TX_P

PE2_TX_N

PE2_REFCLK_P

PE2_REFCLK_N

PE_TSTCLK_P

PE_TSTCLK_N

PE_RESET*

PE_CTERM_GND

L1

L3

L4

M4

P1

R1

R3

R4

U4

V1

W1

W3

AA1

AB1

AC1

AD2

L2

M2

M3

N3

P2

R2

T2

T3

U3

V2

W2

Y2

AA2

AB2

AC2

AD3

K1

Differential 20/5/5/5/20

K2

PE1_TX_P

G4

PE1_TX_N

G5

CLK_PCIE_MINI

G2

CLK_PCIE_MINI#

G3

PE2_TX_P

H4

PE2_TX_N

J3

CLK_PCIE_NEW

H2

CLK_PCIE_NEW#

H3

F1

F2

PECLK_TEST

PECLK_TEST#

R300 *100_1%

G1

PE_COMP

D2

R293 2.37K_1%

2

PE1_TX_P20

PE1_TX_N20

CLK_PCIE_MINI 20

CLK_PCIE_MINI#20

PE2_TX_P29

PE2_TX_N29

CLK_PCIE_NEW29

CLK_PCIE_NEW#29

0329

+3VS

R42

*10K_04

PE_RST#20

0324

1

0.1u_X7R_04

PLACE ON BACK SIDE

A A

藍天電腦 CLEVO

Title

Size Document Number Rev

5

4

3

2

Date: Sheet of

PCI EXPRESS

3546

Wednesday, May 24, 2006

6-71-M55E0-002

11

1

2.0

44

5

+3VS2,3,6,7,8,11,13,14,15,16,17,19,20,21,23,25,26,28,29,30,31

+2.6VS3,9,13,31

+1.2VPLL_PWR9,11,13

Change from D03A to D04 for EMI

L32 HCB1608K-121T25

D D

C51_RED-C_MUX25

C51_GREEN-Y_MUX25

C51_RLUE-PB_MUX25

C42

56p_04

Change For M550J1_V10_0309

C C

C1

AA21

AA13

U14

H14

C11

AB4

AA4

J15

E12

AB10

Y18

E18

U18

E15

Y11

U19

N17

F16

D11

D19

H19

M19

J17

L13

B1

T17

T12

J16

L21

P19

T19

L14

B B

1 2

L33 HCB1608K-121T25

1 2

L34 HCB1608K-121T25

1 2

C41

C40

56p_04

56p_04

22P CHANGE TO 56P

U13D

BGA

C51

SEC 6 OF 6

C53

*22p_04

C54

*22p_04

V19

T14

C20

R17

AB14

U12

G13

Y16

H21

C22

AB6

F22

L22

R22

V22

AA22

A23

AA23

AA24

L11

M11

N11

P11

M12

N12

P12

M13

N13

P13

M14

N14

P14

L12

C55

*22p_04

4

L36 HCB1608K-121T25

DAC_HSYNC25

DAC_VSYNC25

C39

56p_04

1 2

L35 HCB1608K-121T25

1 2

C38