Page 1

Schematic Diagrams

Digitally signed by dd

DN: cn=dd, o=dd, ou=dd,

email=dddd@yahoo.com,

c=US

Date: 2009.12.21 20:31:16

+07'00'

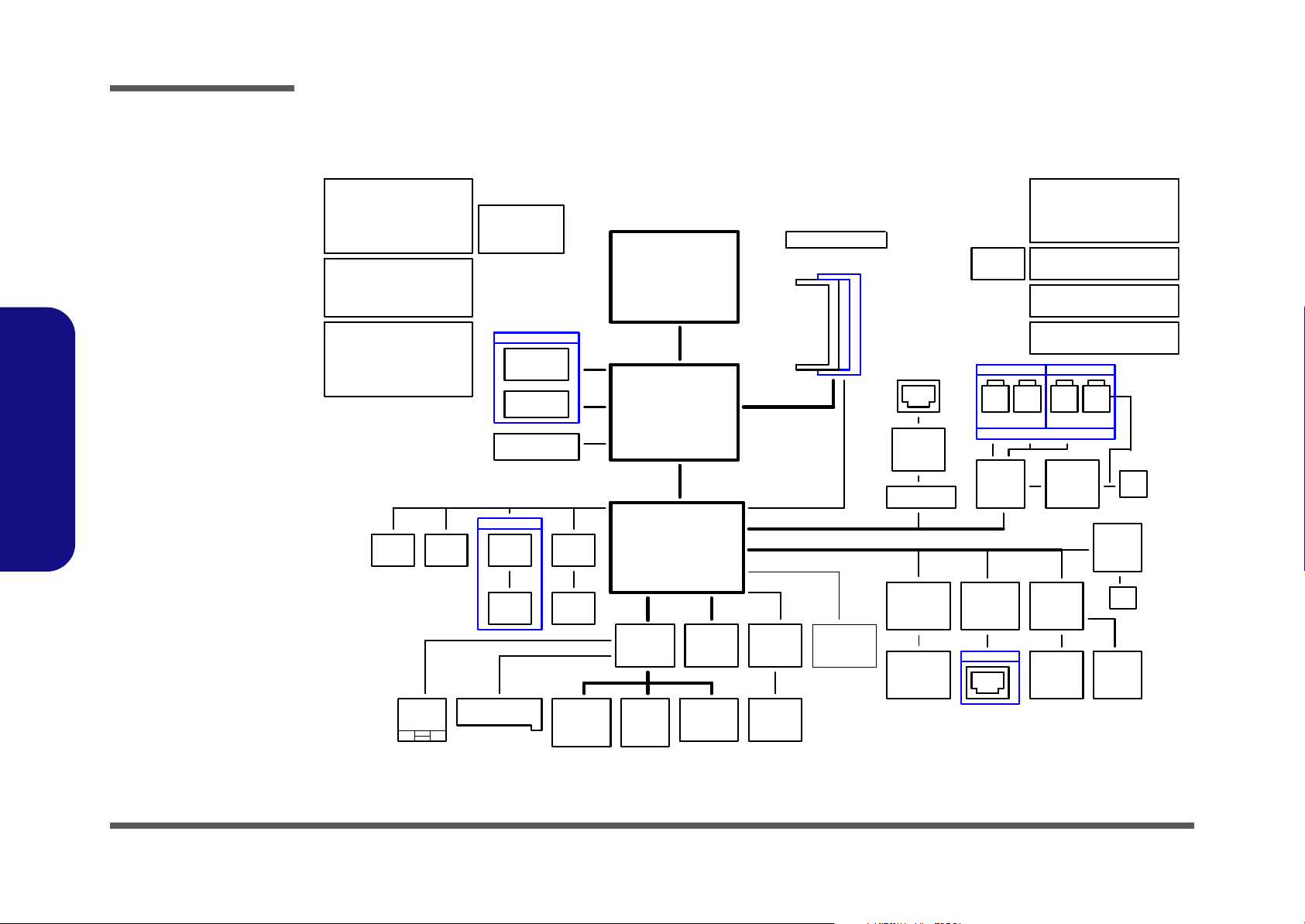

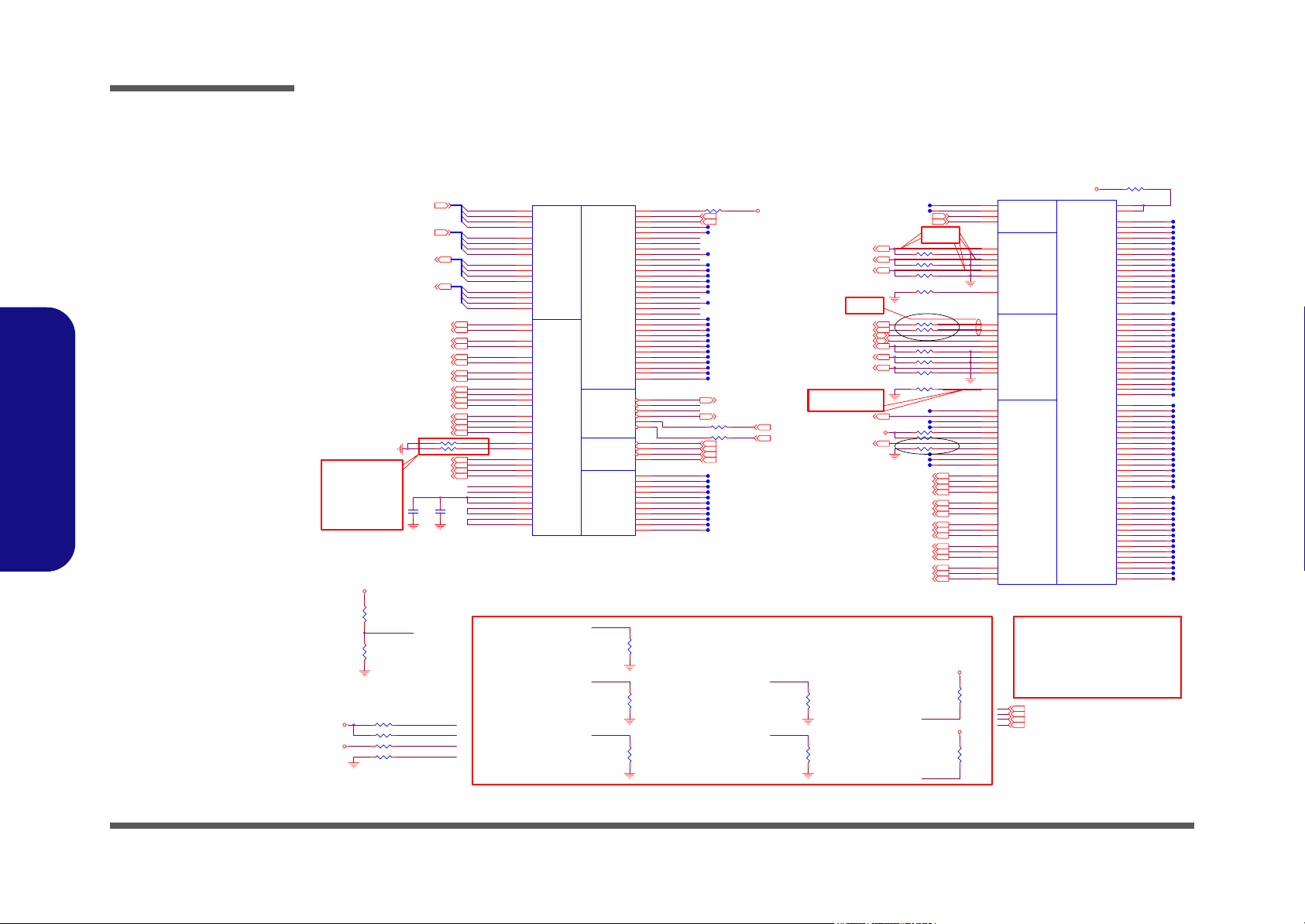

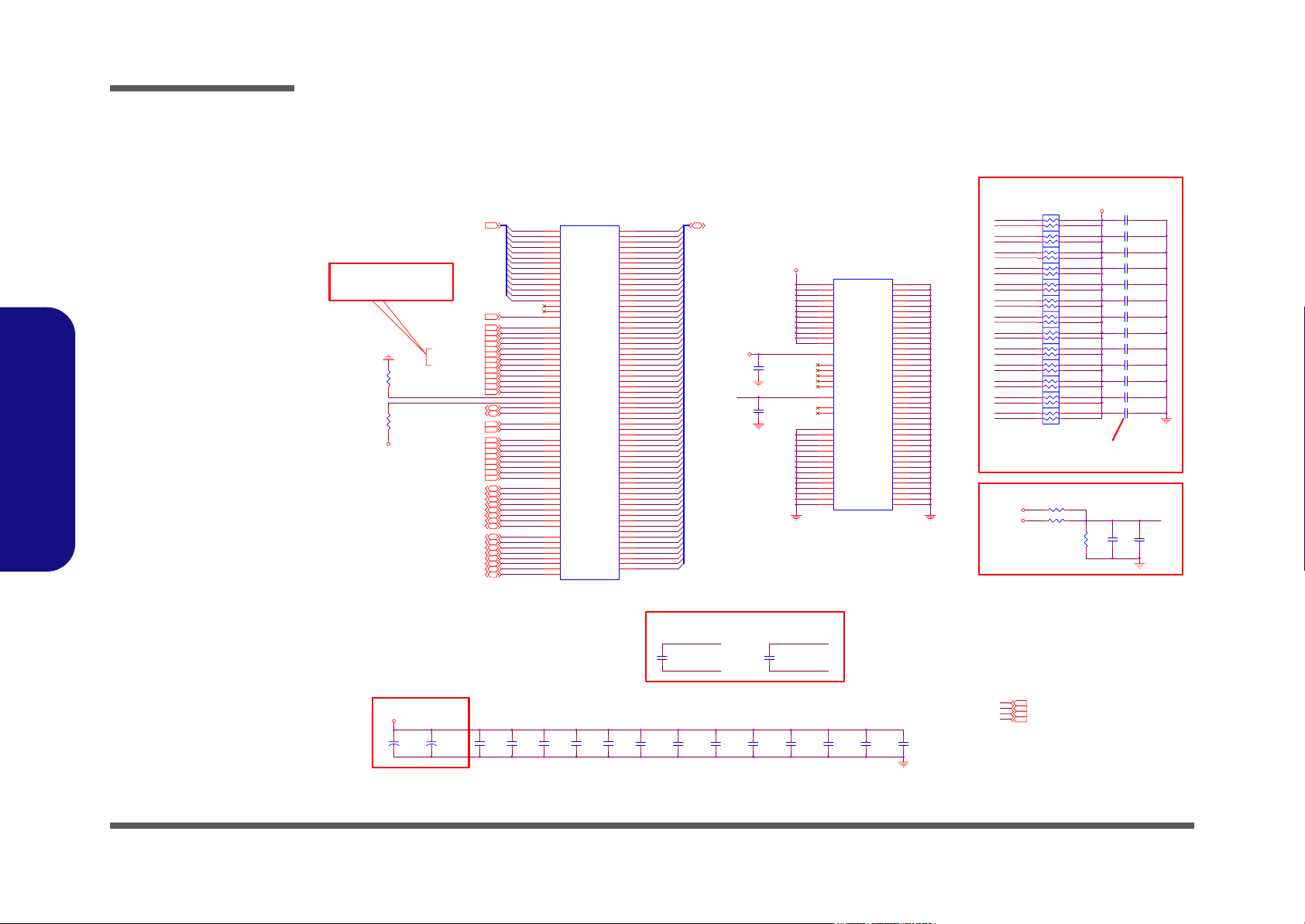

System Block Diagram

Sheet 1 of 40

System Block

Diagram

B.Schematic Diagrams

B - 2

D/D BOARD

1.CHARGER,DC JACK

2.CRT,S-VIDEO,RI-11

3.+VDD3,+VDD5,+VDD12

AUDIO BOARD

1.AUDIO PHONE JACK

2.USB CONNECTOR

HOT KEY BOARD

1.POWER BOTTON

2.INDICATOR LED

3.LID SWITCH

TOUCH

PAD

MBC

CCD

CLOCK GEN.

ICS954226

D/D BOARD

S-VIDEO

MINI DIN 7

LCD CONN(LVDS)

USB2.0

AUDIO BOARD

USB2

USB3

INT. K/B CONN.

CLEVO M540G/M550G System Block Diagram

MEMORY TERMINATIONS

PROCESSOR

DDR2 SDRAM SOCKET

SO-DIMM2

DDRII

400/533 MHz

SM BUS

AZALIA LINK

PCI BUS

SATA-150

PATA-100

MASTER

2.5" HDD

SLAVE

CD-ROM/CD-RW/DVD-COMBO/

DVD-ROM/DVD+-RW

SATA CONN.

2.5" HDD

SO-DIMM1

AZALIA

MBC

MODULE

MBC CONN.

33MHz

Mini PCI

SOCKET

MINI PCI

Wireless LAN

802.11 a/b/g

RJ-11

CRT

USB0

USB1

H8 SM BUS

THERMAL

SENSOR

F75383M

SOCKET

479 uFCPGA

FSB

NORTH BRIDGE

915GM

1257 PCBGA

DMI

SOUTH BRIDGE

ICH6-M

609 BGA

FWH

BIOS

FWH

SMART

BATTERY

KBC

H8/2111

SMART

FAN

LPC

DDR VR

MAIN BOARD

LINE

IN

AZALIA

CODEC

ALC880

LAN

RTL8100CL/

RTL8100SBL

LAN BOARD

RJ-45

1.+3V,+5V,+12V

2.+1.5VS,+3VS,+5VS,+12VS

3.+3VH8,+5VH8

1.+1.8V,+1.5V,+0.9V

1.+VCORE

1.+1.05VS,+2.5VS

AUDIO BOARD

SPDIF

MIC

IN

AUDIO

AMP.

APA2020A

ENE

CB714B

HP

OUT

OUT

7.1 CHANNEL OUT

PCMCIA

PCMCIA

SOCKET

1394

ENE

VT6307S

IEEE

1394

3 IN 1

CARD

READER

INT.

SPK

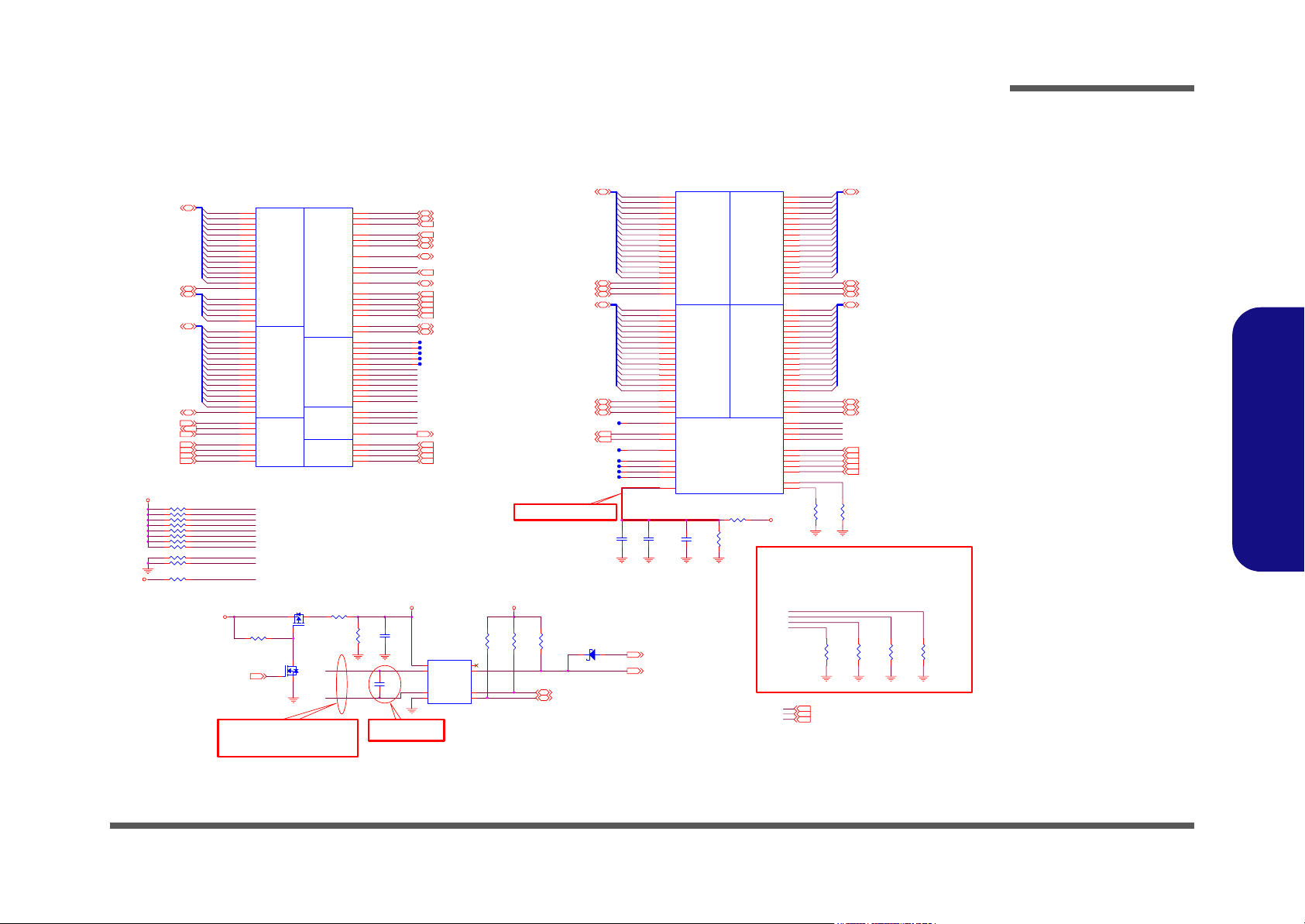

Page 2

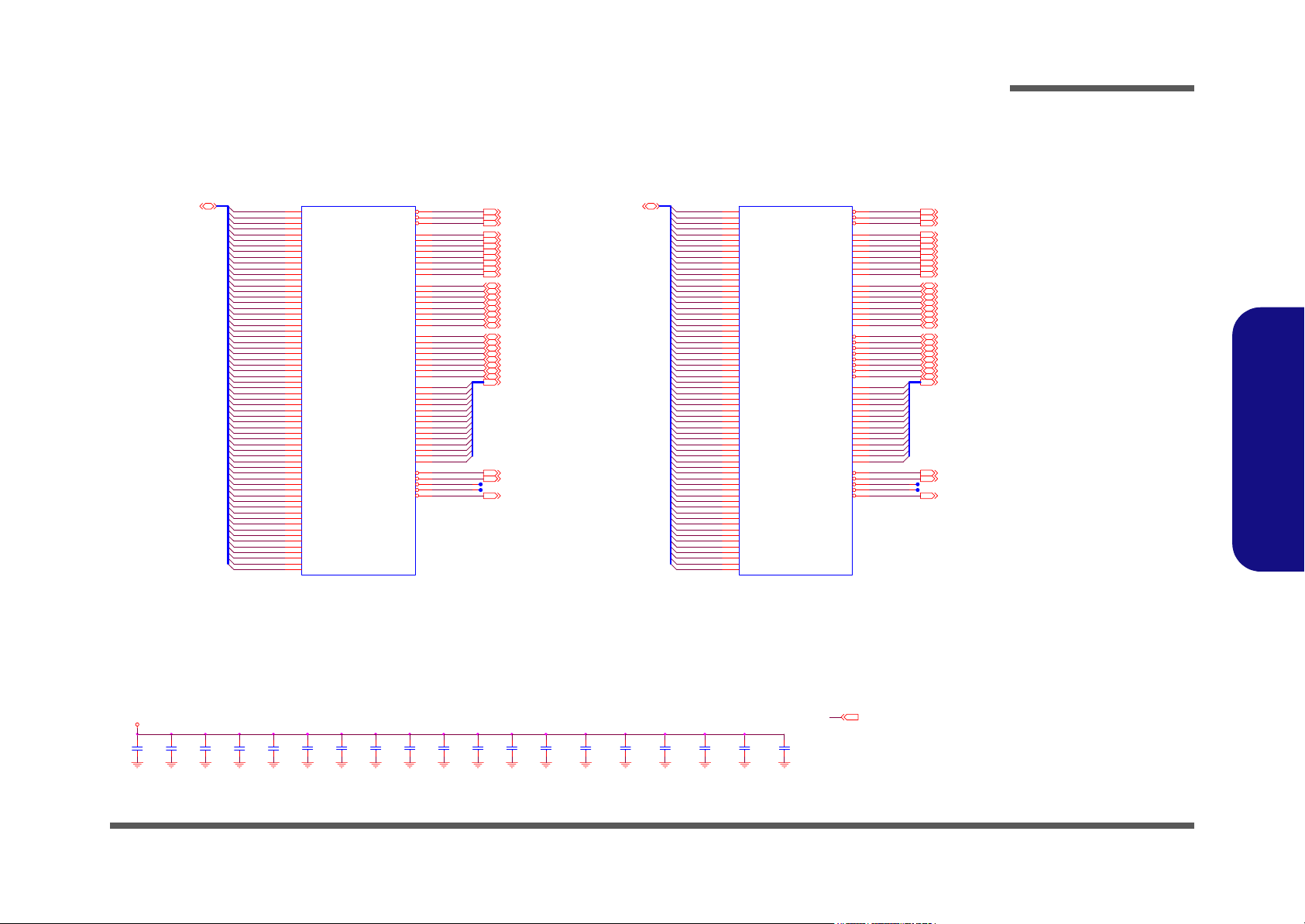

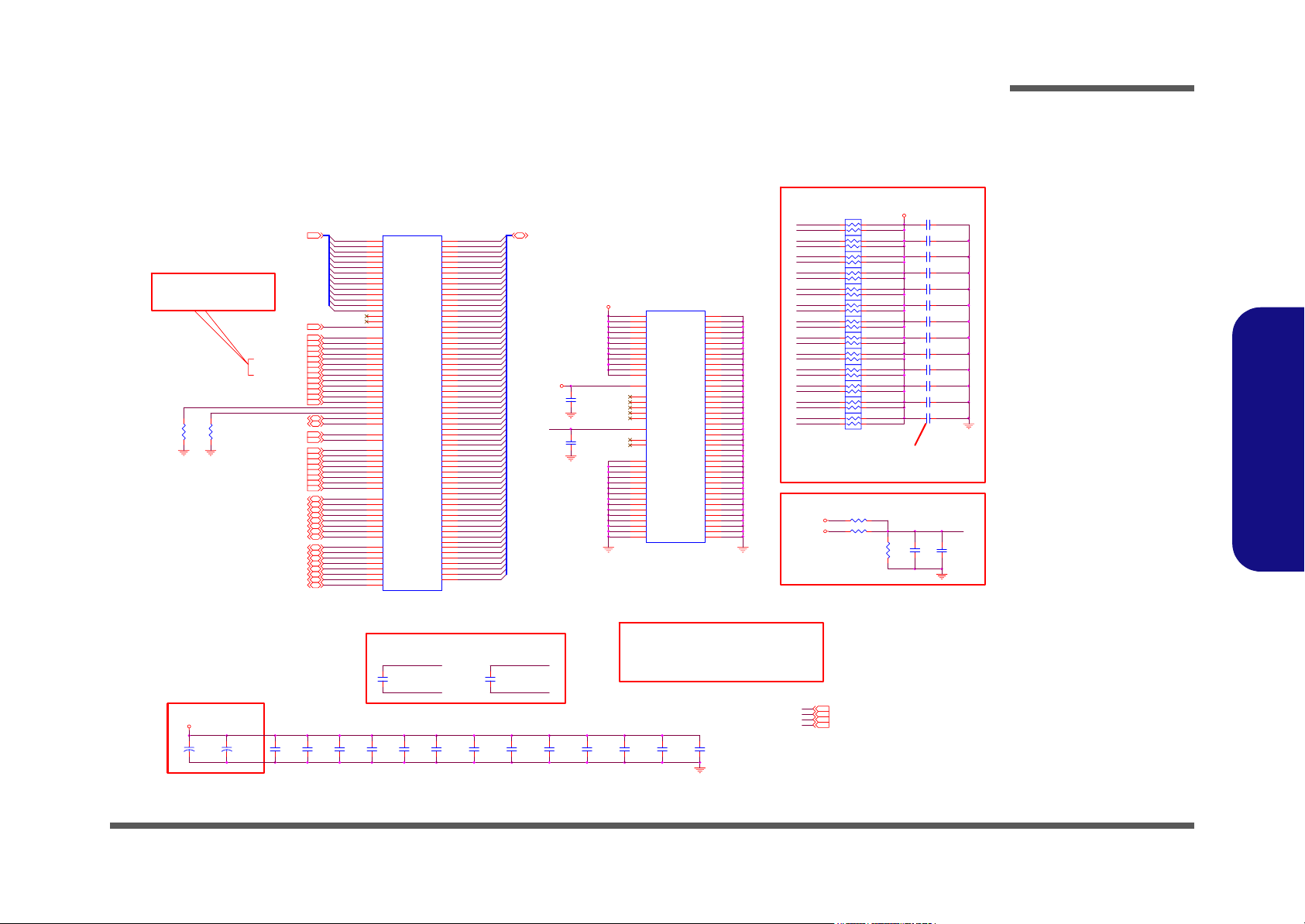

DOTHAN 1/2

Schematic Diagrams

H_REQ#[4:0][4]

+VCCP

+3VS

H_A#[31:3][4]

H_ADSTB#0[4]

H_A#[31:3][4]

H_ADSTB#1[4]

H_A20M#[13]

H_FERR#[13]

H_IGNNE#[13]

H_STPCLK#[13]

H_INTR[13]

H_NMI[13]

H_SMI#[13]

R211 56_04

R224 56_04

R219 54.9_1%

R208 200_1%

R218 39.2_1%

R222 150_1%

R221 54.9_1%

R220 27.4_1%

R223 680_1%

R214 150_1%

JSKT1A

H_A#3

P4

A3#

H_A#4

U4

A4#

H_A#5

V3

A5#

H_A#6

R3

A6#

H_A#7

V2

A7#

H_A#8

W1

A8#

H_A#9

T4

A9#

H_A#10

W2

A10#

H_A#11

Y4

A11#

H_A#12

Y1

A12#

H_A#13

U1

A13#

H_A#14

AA3

A14#

H_A#15

Y3

A15#

H_A#16

AA2

A16#

U3

ADSTB#0

H_REQ#0

R2

REQ0#

REQ1#

REQ2#

REQ3#

REQ4#

A17#

A18#

A19#

A20#

A21#

A22#

A23#

A24#

A25#

A26#

A27#

A28#

A29#

A30#

A31#

ADSTB#1

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

PZ47903-2741-13

Z0210

G

ADDR GROUP0ADDR GROUP1

Q65

AO3409

DS

G

DS

Q16

2N7002

H_REQ#1

P3

H_REQ#2

T2

H_REQ#3

P1

H_REQ#4

T1

H_A#17

AF4

H_A#18

AC4

H_A#19

AC7

H_A#20

AC3

H_A#21

AD3

H_A#22

AE4

H_A#23

AD2

H_A#24

AB4

H_A#25

AC6

H_A#26

AD5

H_A#27

AE2

H_A#28

AD6

H_A#29

AF3

H_A#30

AE1

H_A#31

AF1

AE5

C2

D3

A3

C6

D1

D4

B4

H_IERR#

H_PREQ#

H_PROCHOT#

H_CPURST#

H_PWRGD

H_TMS

H_TDI

H_TDO

H_TCK

H_TRST#

ITP_DBRST#

+3VH8

R243 100K_04

THERMAL_ON#[21]

Route H_THERMDA and H_THERMDC

on the same layer.

10 mil trace on 10 mil spacing.

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

RESET#

RS0#

RS1#

RS2#

TRDY#

HIT#

HITM#

BPM#0

BPM#1

BPM#2

BPM#3

PRDY#

PREQ#

TCK

TDI

TDO

TMS

XTP/ITP CONTROL

TRST#

DBR#

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

THERM

ITPCLK1

ITPCLK0

BCLK1

BCLK0

CLK

R236 200_1%

Z0209

H_THERMDA

H_THERMDC

N2

L1

J3

L4

H2

M2

N4

H_IERR#

A4

B5

J2

H_CPURST#

B11

H1

K1

L2

M3

K3

K4

H_BPM0#

C8

H_BPM1#

B8

H_BPM2#

A9

H_BPM3#

C9

H_PRDY#

A10

H_PREQ#

B10

H_TCK

A13

H_TDI

C12

H_TDO

A12

H_TMS

C11

H_TRST#

B13

ITP_DBRST#

A7

H_PROCHOT#

B17

H_THERMDA

B18

H_THERMDC

A18

PM_THRMTRIP#

C17

CLK_CPU_ITP#

A15

CLK_CPU_ITP

A16

CLK_CPU_FSB#

B14

CLK_CPU_FSB

B15

+VCC_THRM +3VH8

R235

C456

100K_04

1u

1

2

C448

3

2200p

5

Layout Note:Layout Note:

Near to ADM1032

H_ADS# [4]

H_BNR# [4]

H_BPRI# [4]

H_DEFER# [4]

H_DRDY# [4]

H_DBSY# [4]

H_BR0# [4]

H_INIT# [13]

H_LOCK# [4]

H_CPURST# [4]

H_RS#0 [4]

H_RS#1 [4]

H_RS#2 [4]

H_TRDY# [4]

H_HIT# [4]

H_HITM# [4]

PM_THRMTRIP# [5,13]

CLK_CPU_ITP# [11]

CLK_CPU_ITP [11]

CLK_CPU_FSB# [11]

CLK_CPU_FSB [11]

U19

VDD

THERM

D+

ALERT

D-

SDATA

GND

SCLK

F75383M

R242

4.7K_04

4

6

7

8

H_D#[63:0][4]

H_DSTBN#0[4]

H_DSTBP#0[4]

H_DINV#0[4]

H_D#[63:0][4]

H_DSTBN#1[4]

H_DSTBP#1[4]

CPU_BSEL0[3,4]

CPU_BSEL1[4]

Layout Note:

0.5" max, Zo= 55 Ohms

R241

R445

10K_04

H8_SDAT1 [21]

H8_SCLK1 [21]

D37 SCS551V

4.7K_04

JSKT1B

A19

H_D#0

D0#

A25

H_D#1

D1#

A22

H_D#2

D2#

B21

H_D#3

D3#

A24

H_D#4

D4#

B26

H_D#5

D5#

A21

H_D#6

D6#

B20

H_D#7

D7#

C20

H_D#8

D8#

B24

H_D#9

D9#

D24

H_D#10

D10#

E24

H_D#11

D11#

C26

H_D#12

D12#

B23

H_D#13

D13#

E23

H_D#14

D14#

C25

H_D#15

D15#

C23

DSTBN0#

C22

DSTBP0#

D25

DINV0#

H23

H_D#16

D16#

G25

H_D#17

D17#

L23

H_D#18

D18#

M26

H_D#19

D19#

H24

H_D#20

D20#

F25

H_D#21

D21#

G24

H_D#22

D22#

J23

H_D#23

D23#

M23

H_D#24

D24#

J25

H_D#25

D25#

L26

H_D#26

D26#

N24

H_D#27

D27#

M25

H_D#28

D28#

H26

H_D#29

D29#

N25

H_D#30

D30#

K25

H_D#31

D31#

K24

DSTBN1#

L24

DSTBP1#

J26

DINV1#

Z0201

E1

PSI#

C16

BSEL0

Z0202

B2

NC1

Z0203

C3

RSVD2

Z0204

AF7

RSVD3

Z0205

AC1

RSVD4

Z0206

E26

RSVD5

AD26

GTLREF0

PZ47903-2741-13

CPU_GTLREF

C451

C452

0.1u_X7R_04

1u_X7R

AC

PM_THRM# [14]

H8_THRM# [21]

C450

0.01u_04

MISC

DATA GROUP 0

DATA GROUP 1

R231 1K_1%R217 56_04

R232

2K_1%

Y26

H_D#32

D32#

AA24

H_D#33

D33#

T25

H_D#34

D34#

U23

H_D#35

D35#

V23

H_D#36

D36#

R24

H_D#37

D37#

R26

H_D#38

D38#

R23

H_D#39

D39#

AA23

H_D#40

D40#

U26

H_D#41

D41#

V24

H_D#42

D42#

U25

H_D#43

D43#

V26

H_D#44

D44#

Y23

H_D#45

D45#

AA26

H_D#46

D46#

Y25

H_D#47

D47#

W25

DSTBN2#

DATA GROUP 2DATA GROUP 3

W24

DSTBP2#

T24

DINV2#

H_D#48

AB25

D48#

H_D#49

AC23

D49#

H_D#50

AB24

D50#

H_D#51

AC20

D51#

H_D#52

AC22

D52#

H_D#53

AC25

D53#

H_D#54

AD23

D54#

H_D#55

AE22

D55#

H_D#56

AF23

D56#

H_D#57

AD24

D57#

H_D#58

AF20

D58#

H_D#59

AE21

D59#

H_D#60

AD21

D60#

H_D#61

AF25

D61#

H_D#62

AF22

D62#

H_D#63

AF26

D63#

AE24

DSTBN3#

AE25

DSTBP3#

AD20

DINV3#

COMP0

P25

COMP0

COMP1

P26

COMP1

COMP2

AB2

COMP2

COMP3

AB1C14

COMP3BSEL1

G1

DPRSTP#

B7

DPSLP#

C19

DPWR#

H_PWRGD

E4

PWRGOOD

A6

SLP#

Z0207

C5

TEST1

Z0208

F23

TEST2

+VCCP

Layout Note:

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms

COMP1, COMP3: 0.5" Max, Zo=55 Ohms

Best estimate is 18 mils wide trace for outer

layers and 14 mils wide trace if on internal

layers.

COMP0

COMP1

COMP2

COMP3

+3VS [7,9,10,11,12,13,14,15,16,17,18,19,20,22,23,25,26,27,29,30]

+3VH8 [12,21,22,27]

+VCCP [3,4,5,6,7,8,13,15,29,30]

R226

*1K_04

R207

54.9_1%

H_D#[63:0] [4]

H_DSTBN#2 [4]

H_DSTBP#2 [4]

H_DINV#2 [4]

H_D#[63:0] [4]

H_DSTBN#3 [4]

H_DSTBP#3 [4]

H_DINV#3 [4]H_DINV#1[4]

H_DPRSTP# [13]

H_DPSLP# [13]

H_DPWR# [4]

H_PWRGD [13]

H_CPUSLP# [4,13]

R212

*1K_04

R210

27.4_1%

R234

54.9_1%

R233

27.4_1%

Sheet 2 of 40

DOTHAN 1/2

B.Schematic Diagrams

DOTHAN 1/2 B - 3

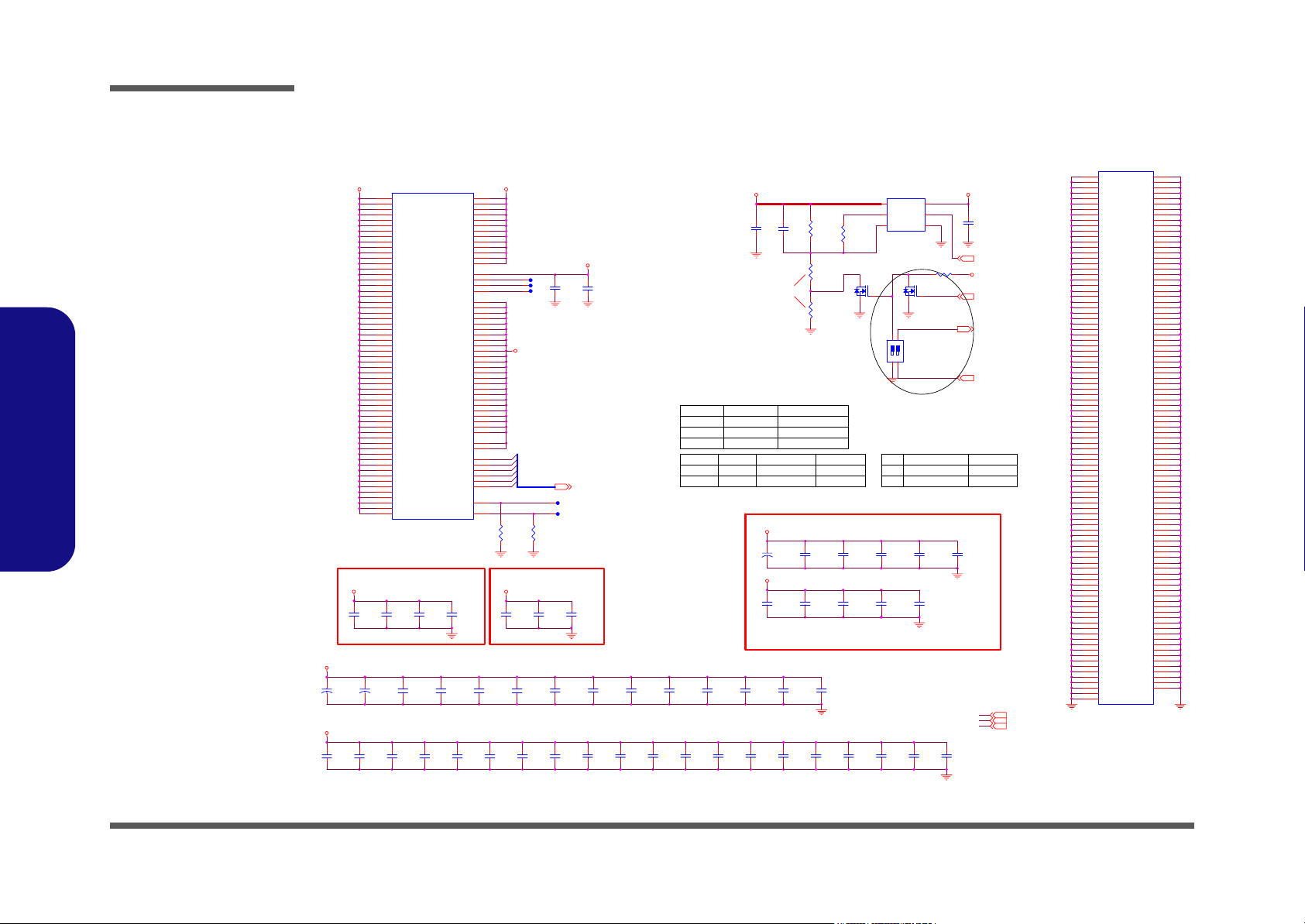

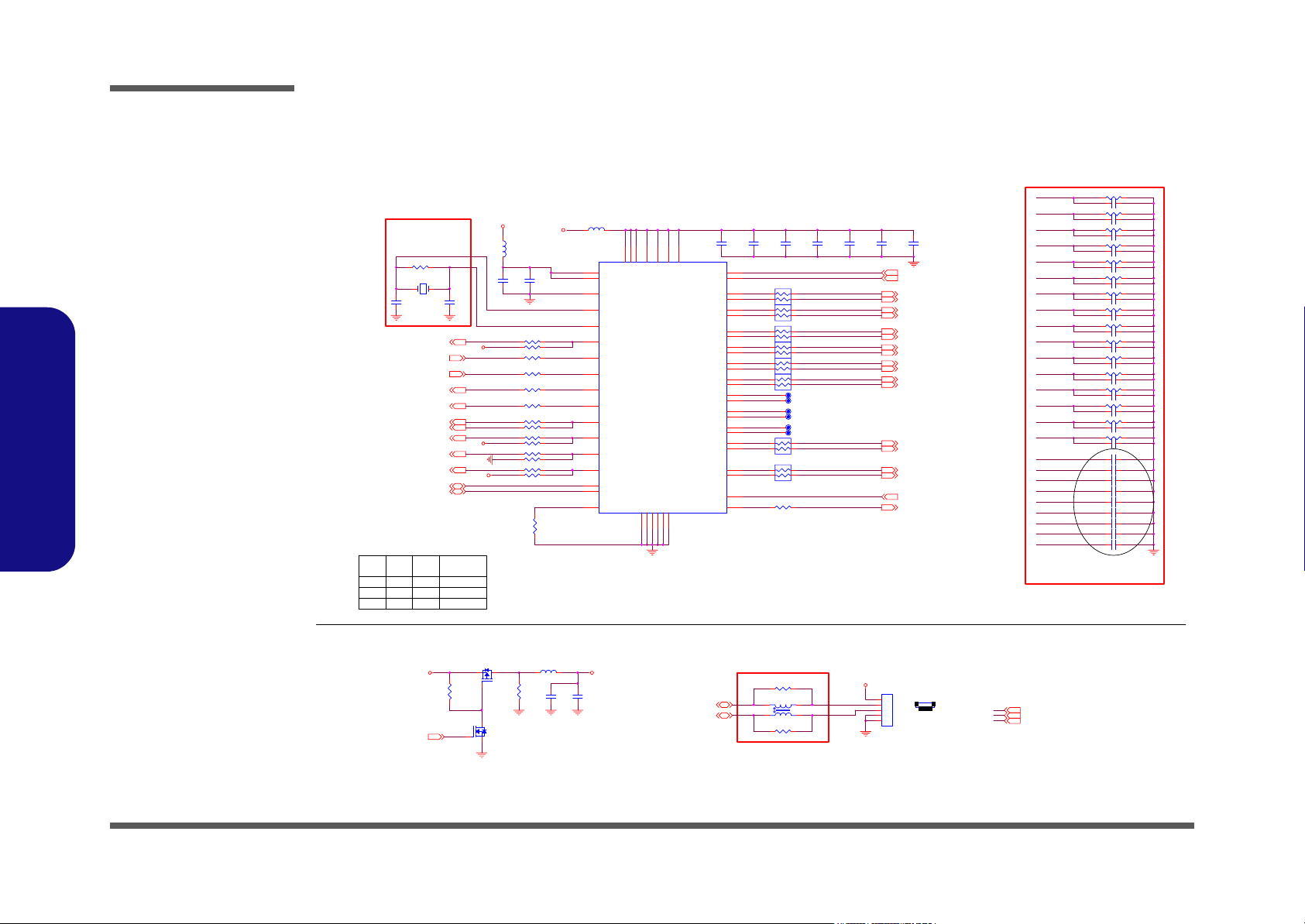

Page 3

Schematic Diagrams

Sheet 3 of 40

DOTHAN 2/2

B.Schematic Diagrams

DOTHAN 2/2

+VCORE

JSKT1C

AA11

VCC0

AA13

VCC1

AA15

VCC2

AA17

VCC3

AA19

VCC4

AA21

VCC5

AA5

VCC6

AA7

VCC7

AA9

VCC8

AB10

VCC9

AB12

VCC10

AB14

VCC11

AB16

VCC12

AB18

VCC13

AB20

VCC14

AB22

VCC15

AB6

VCC16

AB8

VCC17

AC11

VCC18

AC13

VCC19

AC15

VCC20

AC17

VCC21

AC19

VCC22

AC9

VCC23

AD10

VCC24

AD12

VCC25

AD14

VCC26

AD16

VCC27

AD18

VCC28

AD8

VCC29

AE11

VCC30

AE13

VCC31

AE15

VCC32

AE17

VCC33

AE19

VCC34

AE9

VCC35

AF10

VCC36

AF12

VCC37

AF14

VCC38

AF16

VCC39

AF18

VCC40

AF8

VCC41

D18

VCC42

D20

VCC43

D22

VCC44

D6

VCC45

D8

VCC46

E17

VCC47

E19

VCC48

E21

VCC49

E5

VCC52

E7

VCC51

E9

VCC52

F18

VCC53

F20

VCC54

F22

VCC55

F6

VCC56

F8

VCC57

G21

VCC58

PZ47903-2741-13

PUT SOCKET INSIDE PUT SOCKET BACKSIDE

+VCORE +VCORE

C413

C437

10u_08

10u_08

+VCORE

C55

C15

+

*100u/4V_B

C24

10u_08

C429

10u_08

C42

*10u_08

+VCORE

+

*100u/4V_B

C418

10u_08

POWER

C434

10u_08

C415

10u_08

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCCA0

VCCA1

VCCA2

VCCA3

VCCP0

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCP17

VCCP18

VCCP19

VCCP20

VCCP21

VCCP22

VCCP23

VCCP24

VCCQ0

VCCQ1

VCCSENSE

VSSSENSE

C409

10u_08

C44

*10u_08

VID0

VID1

VID2

VID3

VID4

VID5

C433

10u_08

JSKT1D

A2

VSS0

A5

+VCORE

G5

H22

H6

J21

J5

K22

U5

V22

V6

W21

W5

Y22

Y6

F26

Z0301

B1

Z0302

N1

Z0303

AC26

D10

D12

D14

D16

E11

E13

E15

F10

F12

F14

+VCCP

F16

K6

L21

L5

M22

M6

N21

N5

P22

P6

R21

R5

T22

T6

U21

P23

W4

E2

H_VID0

F2

H_VID1

F3

H_VID2

G3

H_VID3

G4

H_VID4

H_VID[5:0]

H4

H_VID5

AE7

TP_VCCSENSE

AF6

TP_VSSSENSE

R215

*54.9_1%

C52

10u_08

R213

*54.9_1%

C22

10u_08

+VCCA_CPU

C453

1u_X7R

H_VID[5:0] [29]

C16

10u_08

C449

0.01u_04

Vout = 1.215 * [ 1 + ( R1 / R2 ) ]

AME8804AEEY(Without RA)

V

+VCCA_CPU

R1

R2

Default

OFF

+1.8V ( Ra )

499_1%

1K_1% 1K_1% + 1K_1%

(+1.82V)

ON

OFF

200mA

C455

C454

1000p

1u_X7R

R2

+1.5V ( Ra + Rb )

V

CPU SELECTCPUSW-1 CPUSW-2

0.09u AUTOON

0.13u FSB400

+VCCP

C443

+

*330u/3V_D

+VCCP

C410

0.1u_X7R_04

R1

R238

499_1%

Ra

R237

1K_1%

Z0306

Rb

R489

1K_1%

499_1%

(+1.52V)

+VCCA_CPU

+1.5V

+1.8V

PLEASE NEAR CPU

C40

0.1u_X7R_04

C411

0.1u_X7R_04

Z0304

RA

R229

*0_04

Z0305

DS

C18

0.1u_X7R_04

C412

0.1u_X7R_04

Q92

2N7002

G

V

U18

6

VOUT

5

ADJ

AME8804AEEY

41

ON

12

FSB

100

133

C435

0.1u_X7R_04

C32

0.1u_X7R_04

VIN

ENPG

GND

Z0307

DS

3

CPUSW

FHDS-02F-T-T/R

53-4050C-040

2

1

34

2

R488 100K_04

Q93

*2N7002

G

5/30

VCCA_SW

LO

HI

C53

0.1u_X7R_04

C436

0.1u_X7R_04

+3V+VCCA_CPU

C466

0.1u_X7R_04

SUSB# [14,18,21,22,27,28,29]

+3V

VCCA_SW [14]

CLK_BSEL0 [4,11]

CPU_BSEL0 [2,4]

+VCCA_CPU

+1.8V

+1.5V

C428

0.1u_X7R_04

+VCCP = 1.05V (0.997V~1.102V)

C45

C21

*10u_08

C416

10u_08

*10u_08

C432

10u_08

C12

0.1u_X7R_04

C417

10u_08

C26

0.1u_X7R_04

C38

1u_X7R

C423

1u_X7R

C27

0.1u_X7R_04

C39

1u_X7R

C13

0.1u_X7R_04

C427

1u_X7R

C51

C11

0.1u_X7R_04

0.1u_X7R_04

PLEASE NEAR CPU

C43

C431

1u_X7R

1u_X7R

C48

0.1u_X7R_04

C419

1u_X7R

C49

0.1u_X7R_04

C29

1u_X7R

C37

1u_X7R

C424

1u_X7R

C420

1u_X7R

C31

1u_X7R

+3V [12,13,14,15,16,17,18,22,27,28,29,30]

+VCCP [2,4,5,6,7,8,13,15,29,30]

+VCORE [29]

A3

A8

A11

A14

A17

A20

A23

A26

AA1

AA4

AA6

AA8

AA10

AA12

AA14

AA16

AA18

AA20

AA22

AA25

AB3

AB5

AB7

AB9

AB11

AB13

AB15

AB17

AB19

AB21

AB23

AB26

AC2

AC5

AC8

AC10

AC12

AC14

AC16

AC18

AC21

AC24

AD1

AD4

AD7

AD9

AD11

AD13

AD15

AD17

AD19

AD22

AD25

AE3

AE6

AE8

AE10

AE12

AE14

AE16

AE18

AE20

AE23

AE26

AF2

AF5

AF9

AF11

AF13

AF15

AF17

AF19

AF21

AF24

B3

B6

B9

B12

B16

B19

B22

B25

C1

C4

C7

C10

C13

C15

C18

C21

C24

D2

D5

D7

D9

D11

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

PZ47903-2741-13

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

D13

D15

D17

D19

D21

D23

D26

E3

E6

E8

E10

E12

E14

E16

E18

E20

E22

E25

F1

F4

F5

F7

F9

F11

F13

F15

F17

F19

F21

F24

G2

G6

G22

G23

G26

H3

H5

H21

H25

J1

J4

J6

J22

J24

K2

K5

K21

K23

K26

L3

L6

L22

L25

M1

M4

M5

M21

M24

N3

N6

N22

N23

N26

P2

P5

P21

P24

R1

R4

R6

R22

R25

T3

T5

T21

T23

T26

U2

U6

U22

U24

V1

V4

V5

V21

V25

W3

W6

W22

W23

W26

Y2

Y5

Y21

Y24

B - 4 DOTHAN 2/2

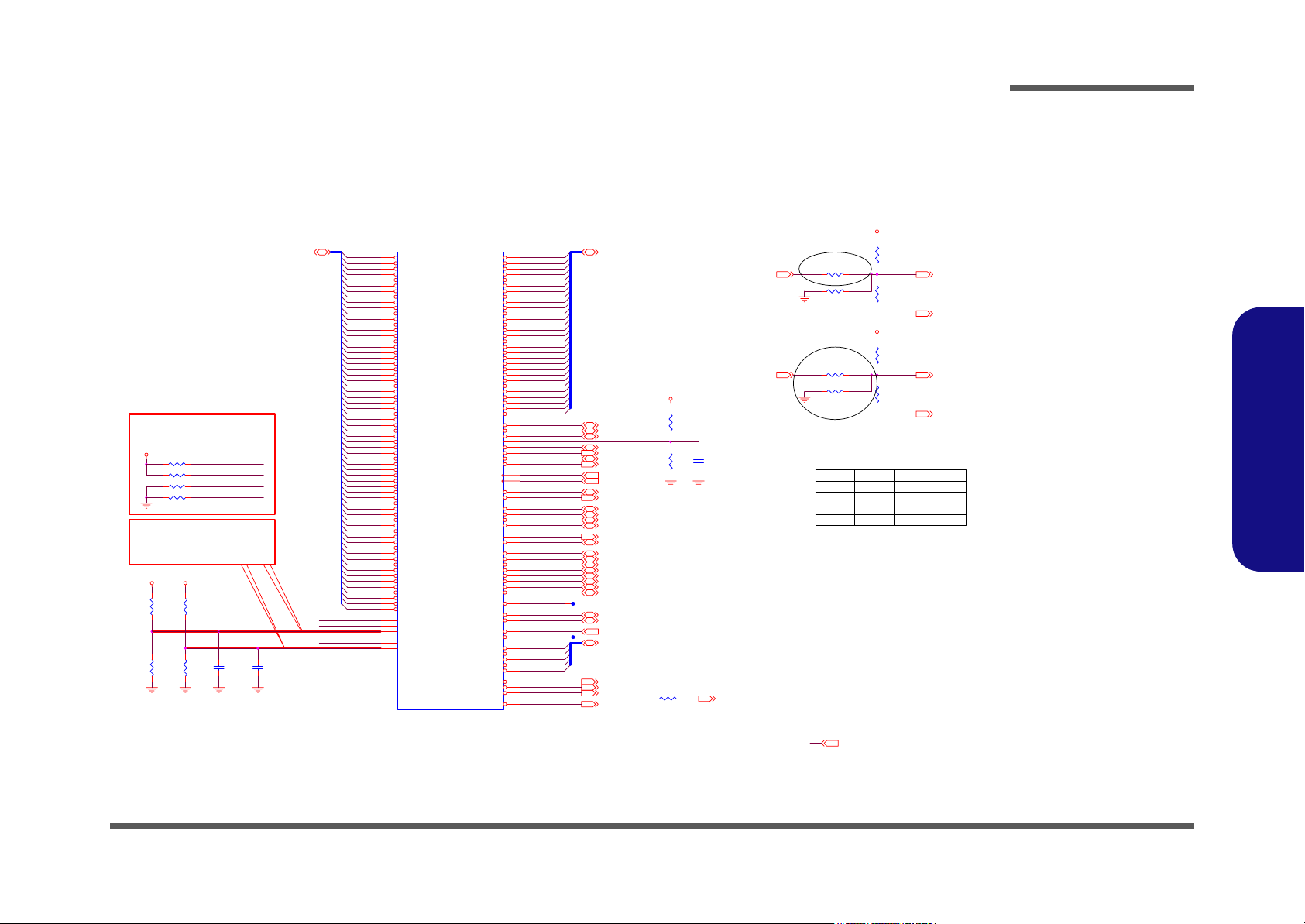

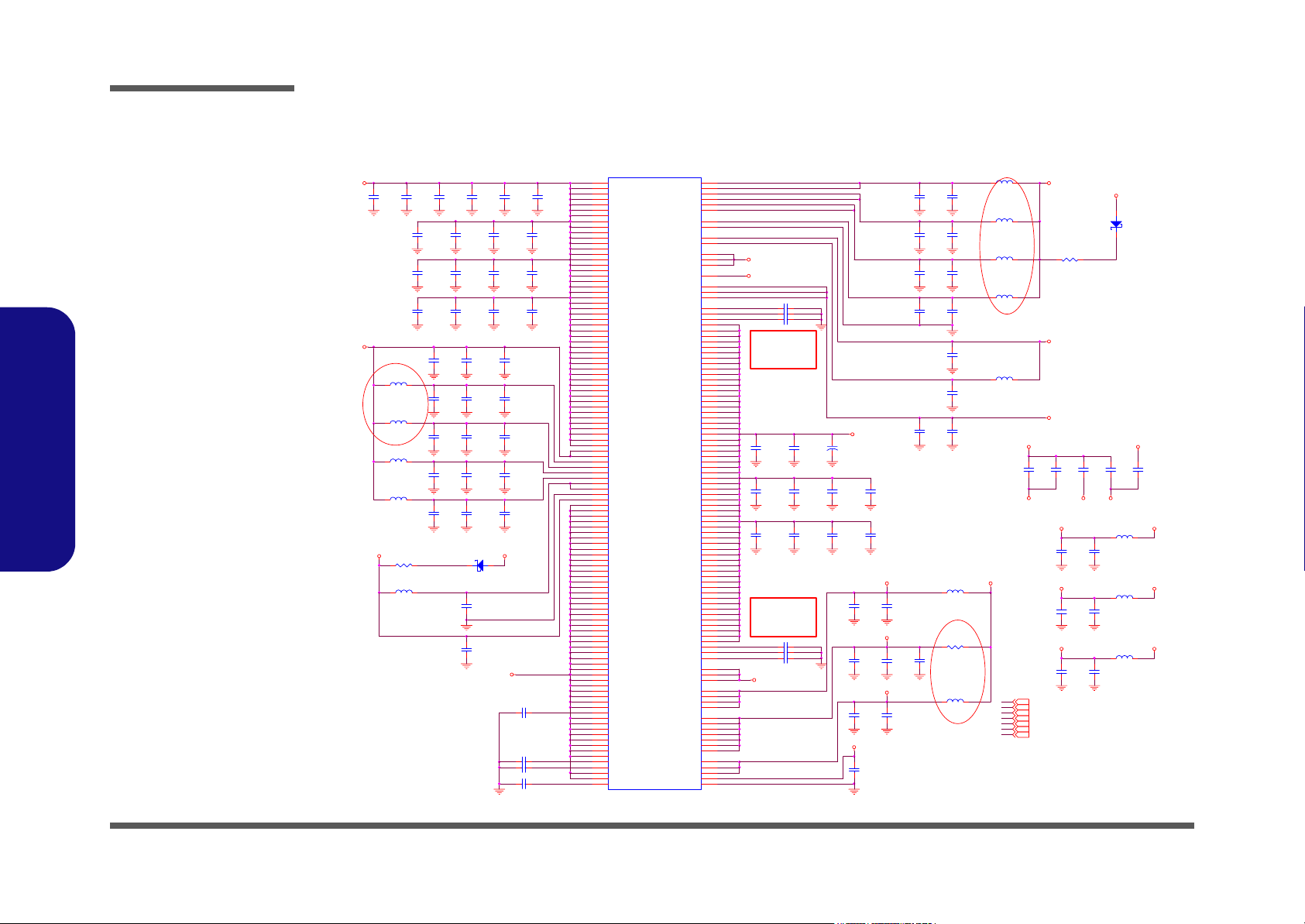

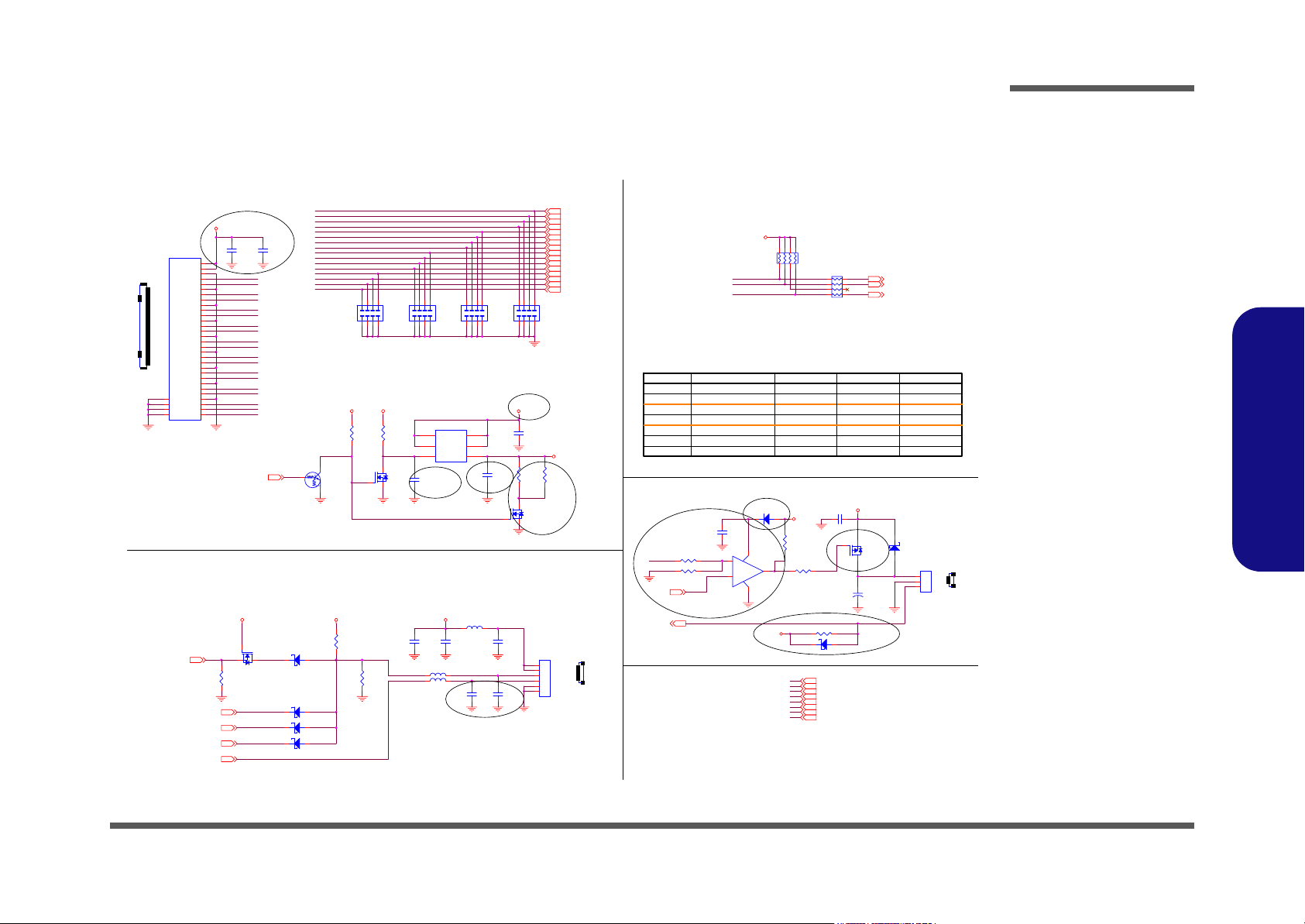

Page 4

915GM 1/5

Layout Notice:

10 mils wide, 20 mils spacing

+VCCP

R251 54.9_1%

R247 54.9_1%

R253 24.9_1%

R245 24.9_1%

Layout Notice:

MCH_HXSWING and MCH_HYSWING

should be 10 mils traces

and 20 mils spacing

+VCCP

R249

221_1%

R250

100_1%

+VCCP

R246

221_1%

R240

100_1%

MCH_HXSCOMP

MCH_HYSCOMP

MCH_HXRCOMP

MCH_HYRCOMP

C483

0.1u_X7R_04

C476

0.1u_X7R_04

Schematic Diagrams

+VCCP

H_D#[63:0][2]

MCH_HXRCOMP

MCH_HXSCOMP

MCH_HXSWING

MCH_HYRCOMP

MCH_HYSCOMP

MCH_HYSWING

U22A

H_D#0

E4

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22 H_A#25

H_D#23

H_D#24

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

HD0#

E1

HD1#

F4

HD2#

H7

HD3#

E2

HD4#

F1

HD5#

E3

HD6#

D3

HD7#

K7

HD8#

F2

HD9#

J7

HD10#

J8

HD11#

H6

HD12#

F3

HD13#

K8

HD14#

H5

HD15#

H1

HD16#

H2

HD17#

K5

HD18#

K6

HD19#

J4

HD20#

G3

HD21#

H3

HD22#

J1

HD23#

L5

HD24#

K4

HD25#

J5

HD26#

P7

HD27#

L7

HD28#

J3

HD29#

P5

HD30#

L3

HD31#

U7

HD32#

V6

HD33#

R6

HD34#

R5

HD35#

P3

HD36#

T8

HD37#

R7

HD38#

R8

HD39#

U8

HD40#

R4

HD41#

T4

HD42#

T5

HD43#

R1

HD44#

T3

HD45#

V8

HD46#

U6

HD47#

W6

HD48#

U3

HD49#

V5

HD50#

W8

HD51#

W7

HD52#

U2

HD53#

U1

HD54#

Y5

HD55#

Y2

HD56#

V4

HD57#

Y7

HD58#

W1

HD59#

W3

HD60#

Y3

HD61#

Y6

HD62#

W2

HD63#

C1

HXRCOMP

C2

HXSCOMP

D1

HXSWING

T1

HYRCOMP

L1

HYSCOMP

P1

HYSWING

915GM

HOST

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HADS#

HADSTB0#

HADSTB1#

HVREF

HBNR#

HBPRI#

HBREQ0#

HCPURST#

HCLKINN

HCLKINP

HDBSY#

HDEFER#

HDINV0#

HDINV1#

HDINV2#

HDINV3#

HDPWR#

HDRDY#

HDSTBN#0

HDSTBN#1

HDSTBN#2

HDSTBN#3

HDSTBP#0

HDSTBP#1

HDSTBP#2

HDSTBP#3

HEDRDY#

HHIT#

HHITM#

HLOCK#

HPCREQ#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HRS0#

HRS1#

HRS2#

HCPUSLP#

HTRDY#

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

G9

C9

E9

B7

A10

F9

D8

B10

E10

G10

D9

E11

F10

G11

G13

C10

C11

D11

C12

B13

A12

F12

G12

E12

C13

B11

D13

A13

F13

F8

B9

E13

J11

A5

D5

E7

H10

AB1

AB2

C6

E6

H8

K3

T7

U5

G6

F7

G4

K1

R3

V3

G5

K2

R2

W4

F6

D4

D6

B3

A11

A7

D7

B8

C7

A8

A4

C5

B4

G8

B5

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#26

H_A#27

H_A#28H_D#25

H_A#29

H_A#30

H_A#31

MCH_HLVREF

H_EDRDY#

H_PCREQ#

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_CPUSLP#_NB

H_A#[31:3] [2]

H_ADS# [2]

H_ADSTB#0 [2]

H_ADSTB#1 [2]

H_BNR# [2]

H_BPRI# [2]

H_BR0# [2]

H_CPURST# [2]

CLK_MCH_FSB# [11]

CLK_MCH_FSB [11]

H_DBSY# [2]

H_DEFER# [2]

H_DINV#0 [2]

H_DINV#1 [2]

H_DINV#2 [2]

H_DINV#3 [2]

H_DPWR# [2]

H_DRDY# [2]

H_DSTBN#0 [2]

H_DSTBN#1 [2]

H_DSTBN#2 [2]

H_DSTBN#3 [2]

H_DSTBP#0 [2]

H_DSTBP#1 [2]

H_DSTBP#2 [2]

H_DSTBP#3 [2]

H_HIT# [2]

H_HITM# [2]

H_LOCK# [2]

H_REQ#[4:0] [2]

H_RS#0 [2]

H_RS#1 [2]

H_RS#2 [2]

H_TRDY# [2]

+VCCP

R270

100_1%

R269

200_1%

R267 0_04

C495

0.1u_X7R_04

H_CPUSLP# [2,13]

5/30

CPU_BSEL0[2,3]

R263 *0_04

R261 *0_04

5/30

CPU_BSEL1[2]

R258 *0_04

R256 0_04

BSEL[0]

H(1)

L(0)

V

L(0)

H(1)

+VCCP

BSEL[1]

L(0)

L(0)

H(1)

H(1)

R260

1K_04

R262

1K_04

R255

1K_04

R257

1K_04

BCLK Frequency

CLK_BSEL0 [3,11]

MCH_BSEL0 [5]

CLK_BSEL1 [11]

MCH_BSEL1 [5]

100 MHz

133 MHz

RESERVED

RESERVED

B.Schematic Diagrams

Sheet 4 of 40

915GM 1/5

+VCCP [2,3,5,6,7,8,13,15,29,30]

915GM 1/5 B - 5

Page 5

Schematic Diagrams

Sheet 5 of 40

915GM 2/5

B.Schematic Diagrams

915GM 2/5

DMI_TXN[3:0][14]

DMI_TXP[3:0][14]

DMI_RXN[3:0][14]

DMI_RXP[3:0][14]

M_CLK_DDR0[10]

M_CLK_DDR1[10]

M_CLK_DDR3[9]

M_CLK_DDR4[9]

M_CLK_DDR0#[10]

M_CLK_DDR1#[10]

M_CLK_DDR3#[9]

M_CLK_DDR4#[9]

M_CKE0[10]

M_CKE1[10]

M_CKE2[9]

M_CKE3[9]

M_CS0#[10]

M_CS1#[10]

M_CS2#[9]

M_CS3#[9]

R284 40.2_1%

R279 40.2_1%

M_ODT0[10]

Note 1:

Route as short as

possible.

Note 2:

Installed for

Alviso C1 version

or later.

+1.8V

R293

1K_1%

M_VREF_MCH

R291

1K_1%

R81 10K_04

+2.5VS

R80 10K_04

R277 80.6_1%

+1.8V

R274 80.6_1%

M_ODT1[10]

M_ODT2[9]

M_ODT3[9]

C543

1u_X7R

PM_EXTTS0#

PM_EXTTS1#

M_RCOMPN

M_RCOMPP

C475

0.01u_04

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

M_RCOMPN

M_RCOMPP

M_VREF_MCH

SMXSLEW

SMYSLEW

(Default)

(Default)

U22B

AA31

DMIRXN0

AB35

DMIRXN1

AC31

DMIRXN2

AD35

DMIRXN3

Y31

DMIRXP0

AA35

DMIRXP1

AB31

DMIRXP2

AC35

DMIRXP3

AA33

AB37

AC33

AD37

Y33

AA37

AB33

AC37

AM33

AL1

AJ34

AF6

AN33

AK1

AJ33

AF5

AP21

AM21

AH21

AK21

AN16

AM14

AH15

AG16

Z0501

AF22

Z0502

AF16

AP14

AL15

AM11

AN10

AK10

AK11

AF37

AD1

AE27

AE28

AF9

AF10

DMI Select

Low = DMI x 2

High = DMI x 4

Low = DDR II Low = Lane Reverse Enable

High = DDR High = Normal operation

CPU Strap

Low = Reserved

High = Intel Pentium M High = Dynamic ODT Enabled

DMITXN0

DMITXN1

DMITXN2

DMITXN3

DMITXP0

DMITXP1

DMITXP2

DMITXP3

SM_CK0

SM_CK1

SM_CK3

SM_CK4

SM_CK0#

SM_CK1#

SM_CK3#

SM_CK4#

SM_CKE0

SM_CKE1

SM_CKE2

SM_CKE3

SM_CS0#

SM_CS1#

SM_CS2#

SM_CS3#

SM_OCDCOMP0

SM_OCDCOMP1

SM_ODT0

SM_ODT1

SM_ODT2

SM_ODT3

SMRCOMPN

SMRCOMPP

SMVREF0

SMVREF1

SMXSLEWIN

SMXSLEWOUT

SMYSLEWIN

SMYSLEWOUT

915GM

DMI

CFG/RSVDPMNC

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

RSVD26

RSVD27

RSVD28

RSVD29

RSVD30

RSVD31

BM_BUSY#

EXT_TS0#

EXT_TS1#

THRMTRIP#

PWROK

RSTIN#

DDR MUXING

DREF_CLKN

DREF_CLKP

DREF_SSCLKN

DREF_SSCLKP

SSC

CFG5

CFG6 CFG9

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

NC10

NC11

CFG0

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG18

CFG19

CFG20

NB_RSVD21

NB_RSVD22

NB_RSVD23

NB_RSVD24

NB_RSVD25

NB_RSVD26

NB_RSVD27

NB_RSVD28

NB_RSVD29

NB_RSVD30

NB_RSVD31

PM_EXTTS0#

PM_EXTTS1#

PWROK_NB

NB_RSTIN#

NB_NC1

NB_NC2

NB_NC3

NB_NC4

NB_NC5

NB_NC6

NB_NC7

NB_NC8

NB_NC9

NB_NC10

NB_NC11

(Default)

(Default)(Default)

R439 10K_04

G16

H13

G14

F16

F15

G15

E16

D17

J16

D15

E15

D14

E14

H12

C14

H15

J15

H14

G22

G23

D23

G25

G24

J17

A31

A30

D26

D25

AE11

AE10

AC10

AD10

J23

J21

H22

F5

AD30

AE29

A24

A23

C37

D37

AP37

NC1

AN37

NC2

AP36

NC3

AP2

NC4

AP1

NC5

AN1

NC6

B1

NC7

A2

NC8

B37

NC9

A36

A37

R271

*2.2K_04

R68

2.2K_04

R66

*2.2K_04

+VCCP

MCH_BSEL0 [4]

TV_DACA_OUT[22]

TV_DACB_OUT[22]

TV_DACC_OUT[22]

DAC_DDCACLK[22]

DAC_DDCADATA[22]

Minimize REFSET

DPG_VCORE [13,14]

PLT_RST# [14,17,19]

CFG16CFG7

routing length and

shield with VSS

R67

(Default)

*2.2K_04

R268

(Default)

*2.2K_04

PM_BMBUSY# [14]

PM_THRMTRIP# [2,13]

R96 0_04

R94 100_04

CLK_DREF# [11]

CLK_DREF [11]

CLK_DREFSS# [11]

CLK_DREFSS [11]

CFG[17:3] have internal pullup resistors

CFG[19:18] have internal pulldown resistors

PCIe Graphics LaneDDR/DDRII Select

FSB Dynamic ODT

Low = Dynamic ODT Disabled

DAC_VSYNC[22]

DAC_HSYNC[22]

DAC_GREEN[22]

MAX=0.5"

DAC_BLUE[22]

DAC_RED[22]

ENAVDD[12]

BLON[12]

+2.5VS

CLK_MCH_3GPLL#[11]MCH_BSEL1 [4]

CLK_MCH_3GPLL[11]

R60 150_1%

R61 150_1%

R64 150_1%

R74 4.99K_1%

R76 39.2_1%

R77 39.2_1%

R285 150_1%

R283 150_1%

R281 150_1%

R75 255_1%

R84 2.2K_04

R79 2.2K_04

R107 1.5K_04

LVDS-LCLKN[12]

LVDS-UCLKN[12]

LVDS-UCLKP[12]

VCC Select

Low = 1.05V

High = 1.5V

VTT Select

Low = 1.05V

High = 1.2V

MAX=0.5"

Minimize TV-REFSET

routing length and

shield with VSS

5/10

5/10

LVDS-LCLKP[12]

LVDS-L0N[12]

LVDS-L1N[12]

LVDS-L2N[12]

LVDS-L0P[12]

LVDS-L1P[12]

LVDS-L2P[12]

LVDS-U0N[12]

LVDS-U1N[12]

LVDS-U2N[12]

LVDS-U0P[12]

LVDS-U1P[12]

LVDS-U2P[12]

CFG18

CFG19

Z0503

Z0504

Z0505

+2.5VS

+2.5VS

Z0506

Z0507

Z0508

Z0509

Z0510

Z0511

Z0512

Z0513

L_IBG

Z0514

Z0515

Z0516

R83

*1K_04

R82

*1K_04

U22G

H24

SDVOCTRL_DATA

H25

SDVOCTRL_CLK

AB29

GCLKN

AC29

GCLKP

A15

TVDAC_A

B15

TV_IRTNA

C16

TVDAC_B

B16

TV_IRTNB

A17

TVDAC_C

B17

J18

H21

G21

E24

E23

E21

D21

C20

B20

A19

B19

J20

E25

F25

C23

C22

F23

F22

F26

C33

C31

F28

F27

B30

B29

C25

C24

B34

B33

B32

A34

A33

B31

C29

D28

C27

C28

D27

C26

TV_IRTNC

TV_REFSET

VSYNC

HSYNC

DDCCLK

DDCDATA

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

REFSET

LBKLT_CRTL

LBKLT_EN

LCTLA_CLK

LCTB_DATA

LDDC_CLK

LDDC_DATA

LVDD_EN

LIBG

LVBG

LVREFH

LVREFL

LACLKN

LACLKP

LBCLKN

LBCLKP

LADATAN0

LADATAN1

LADATAN2

LADATAP0

LADATAP1

LADATAP2

LBDATAN0

LBDATAN1

LBDATAN2

LBDATAP0

LBDATAP1

LBDATAP2

915GM

TV OUTCRTLVDS

PCI EXPRESS

CFG9:PCIe Graphics Lane

NOTE:Ohlone CRB is strapped for

PCI-E lane reversal for ease of

routing. If in integrated GFX mode,

need to use lane-reversal ADD2

add-in card since SDVO if does not

support lane reversal.

+1.5VS [7,14,15,27]

+1.8V [7,8,9,10,28]

+2.5VS [7,12,15,22,30]

+VCCP [2,3,4,6,7,8,13,15,29,30]

+1.5VS

EXP_COMPI

EXP_ICOMPO

EXP_RXN0

EXP_RXN1

EXP_RXN2

EXP_RXN3

EXP_RXN4

EXP_RXN5

EXP_RXN6

EXP_RXN7

EXP_RXN8

EXP_RXN9

EXP_RXN10

EXP_RXN11

EXP_RXN12

EXP_RXN13

EXP_RXN14

EXP_RXN15

EXP_RXP0

EXP_RXP1

EXP_RXP2

EXP_RXP3

EXP_RXP4

EXP_RXP5

EXP_RXP6

EXP_RXP7

EXP_RXP8

EXP_RXP9

EXP_RXP10

EXP_RXP11

EXP_RXP12

EXP_RXP13

EXP_RXP14

EXP_RXP15

EXP_TXN0

EXP_TXN1

EXP_TXN2

EXP_TXN3

EXP_TXN4

EXP_TXN5

EXP_TXN6

EXP_TXN7

EXP_TXN8

EXP_TXN9

EXP_TXN10

EXP_TXN11

EXP_TXN12

EXP_TXN13

EXP_TXN14

EXP_TXN15

EXP_TXP0

EXP_TXP1

EXP_TXP2

EXP_TXP3

EXP_TXP4

EXP_TXP5

EXP_TXP6

EXP_TXP7

EXP_TXP8

EXP_TXP9

EXP_TXP10

EXP_TXP11

EXP_TXP12

EXP_TXP13

EXP_TXP14

EXP_TXP15

R310 24.9_1%

PEG_COMP

D36

D34

Z0517

E30

Z0518

F34

Z0519

G30

Z0520

H34

Z0521

J30

Z0522

K34

Z0523

L30

Z0524

M34

Z0525

N30

Z0526

P34

Z0527

R30

Z0528

T34

Z0529

U30

Z0530

V34

Z0531

W30

Z0532

Y34

Z0533

D30

Z0534

E34

Z0535

F30

Z0536

G34

Z0537

H30

Z0538

J34

Z0539

K30

Z0540

L34

Z0541

M30

Z0542

N34

Z0543

P30

Z0544

R34

Z0545

T30

Z0546

U34

Z0547

V30

Z0548

W34

Z0549

E32

Z0550

F36

Z0551

G32

Z0552

H36

Z0553

J32

Z0554

K36

Z0555

L32

Z0556

M36

Z0557

N32

Z0558

P36

Z0559

R32

Z0560

T36

Z0561

U32

Z0562

V36

Z0563

W32

Z0564

Y36

Z0565

D32

Z0566

E36

Z0567

F32

Z0568

G36

Z0569

H32

Z0570

J36

Z0571

K32

Z0572

L36

Z0573

M32

Z0574

N36

Z0575

P32

Z0576

R36

Z0577

T32

Z0578

U36

Z0579

V32

Z0580

W36

B - 6 915GM 2/5

Page 6

915GM 3/5

Schematic Diagrams

M_A_DQ[63:0][10] M_B_DQ[63:0][9]

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

AG35

AH35

AL35

AL37

AH36

AJ35

AK37

AL34

AM36

AN35

AP32

AM31

AM34

AM35

AL32

AM32

AN31

AP31

AN28

AP28

AL30

AM30

AM28

AL28

AP27

AM27

AM23

AM22

AL23

AM24

AN22

AP22

AP11

AP10

U22C

SADQ0

SADQ1

SADQ2

SADQ3

SADQ4

SADQ5

SADQ6

SADQ7

SADQ8

SADQ9

SADQ10

SADQ11

SADQ12

SADQ13

SADQ14

SADQ15

SADQ16

SADQ17

SADQ18

SADQ19

SADQ20

SADQ21

SADQ22

SADQ23

SADQ24

SADQ25

SADQ26

SADQ27

SADQ28

SADQ29

SADQ30

SADQ31

AM9

SADQ32

AL9

SADQ33

AL6

SADQ34

AP7

SADQ35

SADQ36

SADQ37

AL7

SADQ38

AM7

SADQ39

AN5

SADQ40

AN6

SADQ41

AN3

SADQ42

AP3

SADQ43

AP6

SADQ44

AM6

SADQ45

AL4

SADQ46

AM3

SADQ47

AK2

SADQ48

AK3

SADQ49

AG2

SADQ50

AG1

SADQ51

AL3

SADQ52

AM2

SADQ53

AH3

SADQ54

AG3

SADQ55

AF3

SADQ56

AE3

SADQ57

AD6

SADQ58

AC4

SADQ59

AF2

SADQ60

AF1

SADQ61

AD4

SADQ62

AD5

SADQ63

915GM

DDR SYSTEM MEMORY A

SA_RCVENOUT#

SA_BS0#

SA_BS1#

SA_BS2#

SA_DM0

SA_DM1

SA_DM2

SA_DM3

SA_DM4

SA_DM5

SA_DM6

SA_DM7

SA_DQS0

SA_DQS1

SA_DQS2

SA_DQS3

SA_DQS4

SA_DQS5

SA_DQS6

SA_DQS7

SA_DQS0#

SA_DQS1#

SA_DQS2#

SA_DQS3#

SA_DQS4#

SA_DQS5#

SA_DQS6#

SA_DQS7#

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_CAS#

SA_RAS#

SA_RCVENIN#

SA_WE#

AK15

AK16

AL21

AJ37

AP35

AL29

AP24

AP9

AP4

AJ2

AD3

AK36

AP33

AN29

AP23

AM8

AM4

AJ1

AE5

AK35

AP34

AN30

AN23

AN8

AM5

AH1

AE4

AL17

AP17

AP18

AM17

AN18

AM18

AL19

AP20

AM19

AL20

AM16

AN20

AM20

AM15

AN15

AP16

AF29

AF28

AP15

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

Z0601

Z0602

M_A_BS0# [10]

M_A_BS1# [10]

M_A_BS2# [10] M_B_BS2# [9]

M_A_DM0 [10]

M_A_DM1 [10]

M_A_DM2 [10]

M_A_DM3 [10]

M_A_DM4 [10]

M_A_DM5 [10]

M_A_DM6 [10]

M_A_DM7 [10]

M_A_DQS0 [10]

M_A_DQS1 [10]

M_A_DQS2 [10]

M_A_DQS3 [10]

M_A_DQS4 [10]

M_A_DQS5 [10]

M_A_DQS6 [10]

M_A_DQS7 [10]

M_A_DQS0# [10]

M_A_DQS1# [10]

M_A_DQS2# [10]

M_A_DQS3# [10]

M_A_DQS4# [10]

M_A_DQS5# [10]

M_A_DQS6# [10]

M_A_DQS7# [10]

M_A_A[13:0] [10]

M_A_CAS# [10] M_B_CAS# [9]

M_A_RAS# [10]

M_A_WE# [10] M_B_WE# [9]

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AE31

AE32

AG32

AG36

AE34

AE33

AF31

AF30

AH33

AH32

AK31

AG30

AG34

AG33

AH31

AK30

AH29

AH28

AK29

AH30

AH27

AG28

AF24

AG23

AK22

AH24

AH23

AG22

AG10

AH11

AH10

U22D

SBDQ0

SBDQ1

SBDQ2

SBDQ3

SBDQ4

SBDQ5

SBDQ6

SBDQ7

SBDQ8

SBDQ9

SBDQ10

SBDQ11

SBDQ12

SBDQ13

SBDQ14

AJ31

SBDQ15

SBDQ16

AJ30

SBDQ17

SBDQ18

SBDQ19

SBDQ20

SBDQ21

SBDQ22

SBDQ23

SBDQ24

SBDQ25

AJ22

SBDQ26

SBDQ27

SBDQ28

SBDQ29

SBDQ30

AJ21

SBDQ31

SBDQ32

AG9

SBDQ33

AG8

SBDQ34

AH8

SBDQ35

SBDQ36

SBDQ37

AJ9

SBDQ38

AK9

SBDQ39

AJ7

SBDQ40

AK6

SBDQ41

AJ4

SBDQ42

AH5

SBDQ43

AK8

SBDQ44

AJ8

SBDQ45

AJ5

SBDQ46

AK4

SBDQ47

AG5

SBDQ48

AG4

SBDQ49

AD8

SBDQ50

AD9

SBDQ51

AH4

SBDQ52

AG6

SBDQ53

AE8

SBDQ54

AD7

SBDQ55

AC5

SBDQ56

AB8

SBDQ57

AB6

SBDQ58

AA8

SBDQ59

AC8

SBDQ60

AC7

SBDQ61

AA4

SBDQ62

AA5

SBDQ63

915GM

DDR SYSTEM MEMORY B

SB_RCVENOUT#

SB_BS0#

SB_BS1#

SB_BS2#

SB_DM0

SB_DM1

SB_DM2

SB_DM3

SB_DM4

SB_DM5

SB_DM6

SB_DM7

SB_DQS0

SB_DQS1

SB_DQS2

SB_DQS3

SB_DQS4

SB_DQS5

SB_DQS6

SB_DQS7

SB_DQS0#

SB_DQS1#

SB_DQS2#

SB_DQS3#

SB_DQS4#

SB_DQS5#

SB_DQS6#

SB_DQS7#

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_CAS#

SB_RAS#

SB_RCVENIN#

SB_WE#

AJ15

AG17

AG21

AF32

AK34

AK27

AK24

AJ10

AK5

AE7

AB7

AF34

AK32

AJ28

AK23

AM10

AH6

AF8

AB4

AF35

AK33

AK28

AJ23

AL10

AH7

AF7

AB5

AH17

AK17

AH18

AJ18

AK18

AJ19

AK19

AH19

AJ20

AH20

AJ16

AG18

AG20

AG15

AH14

AK14

AF15

AF14

AH16

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

Z0603

Z0604

M_B_BS0# [9]

M_B_BS1# [9]

M_B_DM0 [9]

M_B_DM1 [9]

M_B_DM2 [9]

M_B_DM3 [9]

M_B_DM4 [9]

M_B_DM5 [9]

M_B_DM6 [9]

M_B_DM7 [9]

M_B_DQS0 [9]

M_B_DQS1 [9]

M_B_DQS2 [9]

M_B_DQS3 [9]

M_B_DQS4 [9]

M_B_DQS5 [9]

M_B_DQS6 [9]

M_B_DQS7 [9]

M_B_DQS0# [9]

M_B_DQS1# [9]

M_B_DQS2# [9]

M_B_DQS3# [9]

M_B_DQS4# [9]

M_B_DQS5# [9]

M_B_DQS6# [9]

M_B_DQS7# [9]

M_B_A[13:0] [9]

M_B_RAS# [9]

B.Schematic Diagrams

Sheet 6 of 40

915GM 3/5

+VCCP

C124

10u_08

C117

10u_08

C125

10u_08

C132

10u_08

C133

10u_08

C96

1u_X7R

C102

1u_X7R

C129

1u_X7R

C109

1u_X7R

C127

1u_X7R

C130

1u_X7R

C470

1u_X7R

C112

0.1u_X7R_04

C110

0.1u_X7R_04

C121

0.1u_X7R_04

C111

0.1u_X7R_04

C118

0.1u_X7R_04

C115

0.1u_X7R_04

C119

0.1u_X7R_04

+VCCP [2,3,4,5,7,8,13,15,29,30]

915GM 3/5 B - 7

Page 7

Schematic Diagrams

915GM 4/5

Sheet 7 of 40

915GM 4/5

B.Schematic Diagrams

+VCORE_GMCH

+1.5VS

4A

C579

10u_08

TBD

HCB1608K-121T25

60mA

HCB1608K-121T25

60mA

HCB1608K-121T25

60mA

HCB1608K-121T25

+2.5VS

HCB1608K-121T25

2mA

U22E

T29

VCC0

R29

C570

C147

C174

C578

10u_08

C468

1u_X7R

C527

1u_X7R

C576

1u_X7R

C469

1u_X7R

C84

1u_X7R

10u_08

C197

0.1u_X7R_04

C187

0.1u_X7R_04

C165

0.1u_X7R_04

C471

0.1u_X7R_04

C530

0.1u_X7R_04

C573

0.1u_X7R_04

C472

0.1u_X7R_04

C85

0.1u_X7R_04

D27

SCS551V

C151

0.1u_X7R_04

C524

0.1u_X7R_04

+VCORE_GMCH

AC

+VCCP

10u_08

C189

0.1u_X7R_04

C198

0.1u_X7R_04

C154

0.1u_X7R_04

L39

L45

L34

L7

R299

10

VCCGFOLLOW

L15

+2.5VS_CRTDAC

10u_08

C149

0.1u_X7R_04

C148

0.1u_X7R_04

C157

0.1u_X7R_04

C479

0.1u_X7R_04

+1.5VS_DPLLA

C529

0.1u_X7R_04

+1.5VS_DPLLB

C222

0.1u_X7R_04

+1.5VS_HPLL

C480

0.1u_X7R_04

+1.5VS_MPLL

C86

0.1u_X7R_04

68mA

C490 0.47u

C486 0.47u

C473 0.22u

C482 0.22u

C572

10u_08

C200

0.1u_X7R_04

C199

0.1u_X7R_04

C150

0.1u_X7R_04

820mA

Z0701

Z0702

Z0703

Z0704

N29

M29

K29

J29

V28

U28

T28

R28

P28

N28

M28

L28

K28

J28

H28

G28

V27

U27

T27

R27

P27

N27

M27

L27

K27

J27

H27

K26

H26

K25

J25

K24

K23

K22

K21

W20

U20

T20

K20

V19

U19

K19

W18

V18

T18

K18

K17

AC2

AC1

B23

C35

AA1

AA2

F19

E19

G19

H20

K13

J13

K12

W11

V11

U11

T11

R11

P11

N11

M11

L11

K11

W10

V10

U10

T10

R10

P10

N10

M10

K10

J10

Y9

W9

U9

R9

P9

N9

M9

L9

J9

N8

M8

N7

M7

N6

M6

A6

N5

M5

N4

M4

N3

M3

N2

M2

B2

V1

N1

M1

G1

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCCH_MPLL1

VCCH_MPLL0

VCCA_DPLLA

VCCA_DPLLB

VCCA_HPLL

VCCA_MPLL

VCCA_CRTDAC0

VCCA_CRTDAC1

VSSA_CRTDAC

VCC_SYNC

VTT0

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT35

VTT36

VTT37

VTT38

VTT39

VTT40

VTT41

VTT42

VTT43

VTT44

VTT45

VTT46

VTT47

VTT48

VTT49

VTT50

VTT51

915GM

POWER

VCCA_TVDACA0

VCCA_TVDACA1

VCCA_TVDACB0

VCCA_TVDACB1

VCCA_TVDACC0

VCCA_TVDACC1

VCCA_TVBG

VSSA_TVBG

VCCD_TVDAC

VCCDQ_TVDAC

VCCD_LVDS0

VCCD_LVDS1

VCCD_LVDS2

VCCA_LVDS

VCCHV0

VCCHV1

VCCHV2

VCCSM0

VCCSM1

VCCSM2

VCCSM3

VCCSM4

VCCSM5

VCCSM6

VCCSM7

VCCSM8

VCCSM9

VCCSM10

VCCSM11

VCCSM12

VCCSM13

VCCSM14

VCCSM15

VCCSM16

VCCSM17

VCCSM18

VCCSM19

VCCSM20

VCCSM21

VCCSM22

VCCSM23

VCCSM24

VCCSM25

VCCSM26

VCCSM27

VCCSM28

VCCSM29

VCCSM30

VCCSM31

VCCSM32

VCCSM33

VCCSM34

VCCSM35

VCCSM36

VCCSM37

VCCSM38

VCCSM39

VCCSM40

VCCSM41

VCCSM42

VCCSM43

VCCSM44

VCCSM45

VCCSM46

VCCSM47

VCCSM48

VCCSM49

VCCSM50

VCCSM51

VCCSM52

VCCSM53

VCCSM54

VCCSM55

VCCSM56

VCCSM57

VCCSM58

VCCSM59

VCCSM60

VCCSM61

VCCSM62

VCCSM63

VCCSM64

VCCTX_LVDS0

VCCTX_LVDS1

VCCTX_LVDS2

VCCA_SM0

VCCA_SM1

VCCA_SM2

VCCA_SM3

VCC3G0

VCC3G1

VCC3G2

VCC3G3

VCC3G4

VCC3G5

VCC3G6

VCCA_3GPLL0

VCCA_3GPLL1

VCCA_3GPLL2

VCCA_3GBG

VSSA_3GBG

F17

E17

D18

C18

F18

E18

H18

G18

D19

H17

B26

B25

A25

A35

B22

B21

A21

AM37

AH37

AP29

AD28

AD27

AC27

AP26

AN26

AM26

AL26

AK26

AJ26

AH26

AG26

AF26

AE26

AP25

AN25

AM25

AL25

AK25

AJ25

AH25

AG25

AF25

AE25

AE24

AE23

AE22

AE21

AE20

AE19

AE18

AE17

AE16

AE15

AE14

AP13

AN13

AM13

AL13

AK13

AJ13

AH13

AG13

AF13

AE13

AP12

AN12

AM12

AL12

AK12

AJ12

AH12

AG12

AF12

AE12

AD11

AC11

AB11

AB10

AB9

AP8

AM1

AE1

B28

A28

A27

AF20

AP19

AF19

AF18

AE37

W37

U37

R37

N37

L37

J37

Y29

Y28

Y27

F37

G37

60mA

10mA

+1.8V_DDR_CAP1

+1.8V_DDR_CAP2

+1.8V_DDR_CAP5

+1.8V_DDR_CAP6

+1.8V_DDR_CAP4

+1.8V_DDR_CAP3

+1.5VS_DLVDS

+2.5VS_ALVDS

C224 0.1u_X7R_04

C217 0.1u_X7R_04

C542 0.1u_X7R_04

Note:

All VCCSM pins

shorted

internally.

2.7A

C531

10u_08

C182

0.1u_X7R_04

C131

0.1u_X7R_04

Note:

All VCCSM pins

shorted

internally.

C494 0.1u_X7R_04

C478 0.1u_X7R_04

C474 0.1u_X7R_04

60mA

+2.5VS_TXLVDS

0.150mA

C499

10u_08

C175

0.1u_X7R_04

C120

0.1u_X7R_04

+3VS_TVDACA

+3VS_TVDACB

+3VS_TVDACC Z0705

+3VS_ATVBG

+1.5VS_QTVDAC

+1.8V

C577

+

330u/3V_D

C176

C535

0.1u_X7R_04

0.1u_X7R_04

C498

C142

0.1u_X7R_04

0.1u_X7R_04

+1.5VS_DDRDLL

C516

1u_X7R

+1.5VS_PCIE

C575

1u_X7R

+1.5VS_3GPLL

C231

1u_X7R

+2.5VS

C525

0.1u_X7R_04

600mA

C511

0.1u_X7R_04

C571

10u_08

C229

0.1u_X7R_04

C136

1u_X7R

C144

1u_X7R

C508

1u_X7R

C514

1u_X7R

C526

1u_X7R

L37

HCB1608K-121T25

R311 0_08

C574

0.1u_X7R_04

1A

L18

HCB1608K-121T25

C137

0.1u_X7R_04

C143

0.1u_X7R_04

C507

0.1u_X7R_04

C513

0.1u_X7R_04

C155

0.1u_X7R_04

C123

0.1u_X7R_04

C522

0.1u_X7R_04

L11

HCB1608K-121T25

L14

HCB1608K-121T25

120mA

L36

HCB1608K-121T25

L38

HCB1608K-121T25

24mA

L10

HCB1608K-121T25

2mA

+VCORE_GMCH

+VDD3 +VCCP +1.8V

+1.5VS

+VDD3 [13,22,27]

+1.5VS [5,14,15,27]

+1.8V [5,8,9,10,28]

+2.5VS [5,12,15,22,30]

+3VS [2,9,10,11,12,13,14,15,16,17,18,19,20,22,23,25,26,27,29,30]

+VCCP [2,3,4,5,6,8,13,15,29,30]

+VCORE_GMCH [8,30]

+3VS

R278 10

+1.5VS

+2.5VS

C805

0.1u_04

+1.5VS_DLVDS +1.5VS

+2.5VS_ALVDS

+2.5VS_TXLVDS +2.5VS

C806

0.1u_04

C537

1u_X7R

C557

0.01u_04

C550

1u_X7R

C807

0.1u_04

C539

0.1u_X7R_04

C560

0.1u_X7R_04

C551

0.1u_X7R_04

+1.5VS

AC

D3

SCS551V

+VCCP

C808

0.1u_04

L40

HCB1608K-121T25

L42

HCB1608K-121T25

L41

HCB1608K-121T25

C809

0.1u_04

+2.5VS

B - 8 915GM 4/5

Page 8

915GM 5/5

AL27

AJ27

AG27

AF27

AB27

AA27

W27

G27

E27

B27

J26

G26

E26

A26

AN24

AL24

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

Schematic Diagrams

AG37

Y37

V37

T37

P37

M37

K37

H37

E37

AN36

AL36

AJ36

AF36

AE36

AD36

AC36

AB36

AA36

C36

AE35

Y35

W35

V35

U35

T35

R35

P35

N35

M35

L35

K35

J35

H35

G35

F35

E35

D35

B35

AN34

AH34

AD34

AC34

AB34

AA34

C34

AL33

AF33

AD33

W33

V33

U33

T33

R33

P33

N33

M33

L33

K33

J33

H33

G33

F33

E33

D33

AN32

AJ32

AD32

AC32

AB32

AA32

Y32

C32

A32

AL31

AG31

AD31

W31

V31

U31

T31

R31

P31

N31

M31

L31

K31

J31

H31

G31

F31

E31

D31

AP30

AE30

AC30

AB30

AA30

Y30

C30

AM29

AJ29

AG29

AD29

AA29

W29

V29

U29

P29

L29

H29

G29

F29

E29

D29

A29

AC28

AB28

AA28

W28

E28

AN27

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS6

VSS5

VSS4

VSS3

VSS2

VSS1

VSS0

U22F

915GM

VSS271

VSSALVDS

B36J2G2

AD12

AC12

AB12

VCCSM_NCTF30

VCCSM_NCTF31

VSS

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS270

VSS268

VSS269

AH2

AE2

AD2V2T2P2L2D2Y1

AD16

AC16

AD15

AC15

AD14

AC14

AD13

AC13

AB13

VCCSM_NCTF21

VCCSM_NCTF22

VCCSM_NCTF23

VCCSM_NCTF24

VCCSM_NCTF25

VCCSM_NCTF26

VCCSM_NCTF27

VCCSM_NCTF28

VCCSM_NCTF29

AJ3

AC3

AB3

AA3C3A3

AN2

AL2

AC22

AD21

AC21

AD20

AC20

AD19

AC19

AD18

AC18

AD17

AC17

VCCSM_NCTF10

VCCSM_NCTF11

VCCSM_NCTF12

VCCSM_NCTF13

VCCSM_NCTF14

VCCSM_NCTF15

VCCSM_NCTF16

VCCSM_NCTF17

VCCSM_NCTF18

VCCSM_NCTF19

VCCSM_NCTF20

AL5W5E5

AN4

AF4Y4U4P4L4H4C4

AD26

AC26

AD25

AC25

AD24

AC24

AD23

AC23

AD22

VCCSM_NCTF4

VCCSM_NCTF5

VCCSM_NCTF6

VCCSM_NCTF7

VCCSM_NCTF8

VCCSM_NCTF9

N17

M17

L17

VCC_NCTF76

VCC_NCTF77

VCC_NCTF78

VCCSM_NCTF0

VCCSM_NCTF1

VCCSM_NCTF2

VCCSM_NCTF3

AK7

AG7

AA7V7G7

AJ6

AE6

AC6

AA6T6P6L6J6B6AP5

P19

N19

M19

L19

Y18

R18

P18

N18

M18

L18

W17

V17

U17

T17

P17

VCC_NCTF61

VCC_NCTF62

VCC_NCTF63

VCC_NCTF64

VCC_NCTF65

VCC_NCTF66

VCC_NCTF67

VCC_NCTF68

VCC_NCTF69

VCC_NCTF70

VCC_NCTF71

VCC_NCTF72

VCC_NCTF73

VCC_NCTF74

VCC_NCTF75

AE9

AC9

AA9V9T9K9H9A9AL8Y8P8L8E8C8AN7

L21

Y20

R20

P20

N20

M20

L20

Y19

R19

VCC_NCTF53

VCC_NCTF54

VCC_NCTF55

VCC_NCTF56

VCC_NCTF57

VCC_NCTF58

VCC_NCTF59

VCC_NCTF60

H11

F11

AA10

Y10

L10

D10

AN9

AH9

L22

W21

V21

U21

T21

P21

N21

M21

VCC_NCTF45

VCC_NCTF46

VCC_NCTF47

VCC_NCTF48

VCC_NCTF49

VCC_NCTF50

VCC_NCTF51

VCC_NCTF52

B12

AN11

AL11

AJ11

AG11

AF11

AA11

Y11

W22

V22

U22

T22

R22

P22

N22

M22

VCC_NCTF37

VCC_NCTF38

VCC_NCTF39

VCC_NCTF40

VCC_NCTF41

VCC_NCTF42

VCC_NCTF43

VCC_NCTF44

AG14

K14

J14

F14

B14

A14

J12

D12

V23

U23

T23

R23

P23

N23

M23

L23

VCC_NCTF29

VCC_NCTF30

VCC_NCTF31

VCC_NCTF32

VCC_NCTF33

VCC_NCTF34

VCC_NCTF35

VCC_NCTF36

H16

D16

A16

K15

C15

AN14

AL14

AJ14

U24

T24

R24

P24

N24

M24

L24

W23

VCC_NCTF20

VCC_NCTF21

VCC_NCTF22

VCC_NCTF23

VCC_NCTF24

VCC_NCTF25

VCC_NCTF26

VCC_NCTF27

VCC_NCTF28

B18

A18

AN17

AJ17

AF17

G17

C17

AL16

K16

U25

T25

R25

P25

N25

M25

L25

W24

V24

VCC_NCTF12

VCC_NCTF13

VCC_NCTF14

VCC_NCTF15

VCC_NCTF16

VCC_NCTF17

VCC_NCTF18

VCC_NCTF19

AG19

W19

T19

J19

H19

C19

AL18

U18

+VCORE_GMCH+1.8V

T26

R26

P26

N26

M26

L26

W25

V25

VCC_NCTF3

VCC_NCTF4

VCC_NCTF5

VCC_NCTF6

VCC_NCTF7

VCC_NCTF8

VCC_NCTF9

VCC_NCTF10

VCC_NCTF11

C21

AK20

V20

G20

F20

E20

D20

A20

AN19

W26

V26

U26

U22H

915GM

VCC_NCTF0

VCC_NCTF1

VCC_NCTF2

AH22

J22

E22

D22

A22

AN21

AF21

F21

AJ24

AG24

J24

F24

D24

B24

AF23

H23

AL22

Sheet 8 of 40

915GM 5/5

B.Schematic Diagrams

NCTF

VSS_NCTF0

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS_NCTF9

VSS_NCTF10

VSS_NCTF11

VSS_NCTF12

VSS_NCTF13

VSS_NCTF14

VSS_NCTF15

VSS_NCTF16

VSS_NCTF17

VSS_NCTF18

VSS_NCTF19

VSS_NCTF20

VSS_NCTF21

VSS_NCTF22

VSS_NCTF23

VSS_NCTF24

VSS_NCTF25

VSS_NCTF26

VSS_NCTF27

VSS_NCTF28

VSS_NCTF29

VSS_NCTF30

VSS_NCTF31

VSS_NCTF32

VSS_NCTF33

VSS_NCTF34

VSS_NCTF35

VSS_NCTF36

VSS_NCTF37

VSS_NCTF38

VSS_NCTF39

VSS_NCTF40

VSS_NCTF41

VSS_NCTF42

VSS_NCTF43

VSS_NCTF44

VSS_NCTF45

VSS_NCTF46

VSS_NCTF47

VSS_NCTF48

VSS_NCTF49

VSS_NCTF50

VSS_NCTF51

VSS_NCTF52

VSS_NCTF53

VSS_NCTF54

VSS_NCTF55

VSS_NCTF56

VSS_NCTF57

VSS_NCTF58

VSS_NCTF59

VSS_NCTF60

VSS_NCTF61

VSS_NCTF62

VSS_NCTF63

VSS_NCTF64

VSS_NCTF65

VSS_NCTF66

VSS_NCTF67

VSS_NCTF68

Y13

AA12

Y12

U14

T14

R14

P14

N14

M14

L14

AA13

P15

N15

M15

L15

AB14

AA14

Y14

W14

V14

AB15

AA15

Y15

W15

V15

U15

T15

R15

V16

U16

T16

R16

P16

N16

M16

L16

AB17

AA17

Y17

R17

AB16

AA16

Y16

W16

Y21

R21

AB20

AA20

AB19

AA19

AB18

AA18

Y24

AB23

AA23

Y23

AB22

AA22

Y22

AB21

AA21

AB26

AA26

Y26

AB25

AA25

Y25

AB24

AA24

+1.8V [5,7,9,10,28]

+VCCP [2,3,4,5,6,7,13,15,29,30]

+VCORE_GMCH [7,30]

+VCCP

VTT_NCTF17

M12

L12

L13

W12

V12

U12

T12

R12

P12

N12

W13

V13

U13

T13

R13

P13

N13

M13

VTT_NCTF0

VTT_NCTF1

VTT_NCTF2

VTT_NCTF3

VTT_NCTF4

VTT_NCTF5

VTT_NCTF6

VTT_NCTF7

VTT_NCTF8

VTT_NCTF9

VTT_NCTF10

VTT_NCTF11

VTT_NCTF12

VTT_NCTF13

VTT_NCTF14

VTT_NCTF15

VTT_NCTF16

915GM 5/5 B - 9

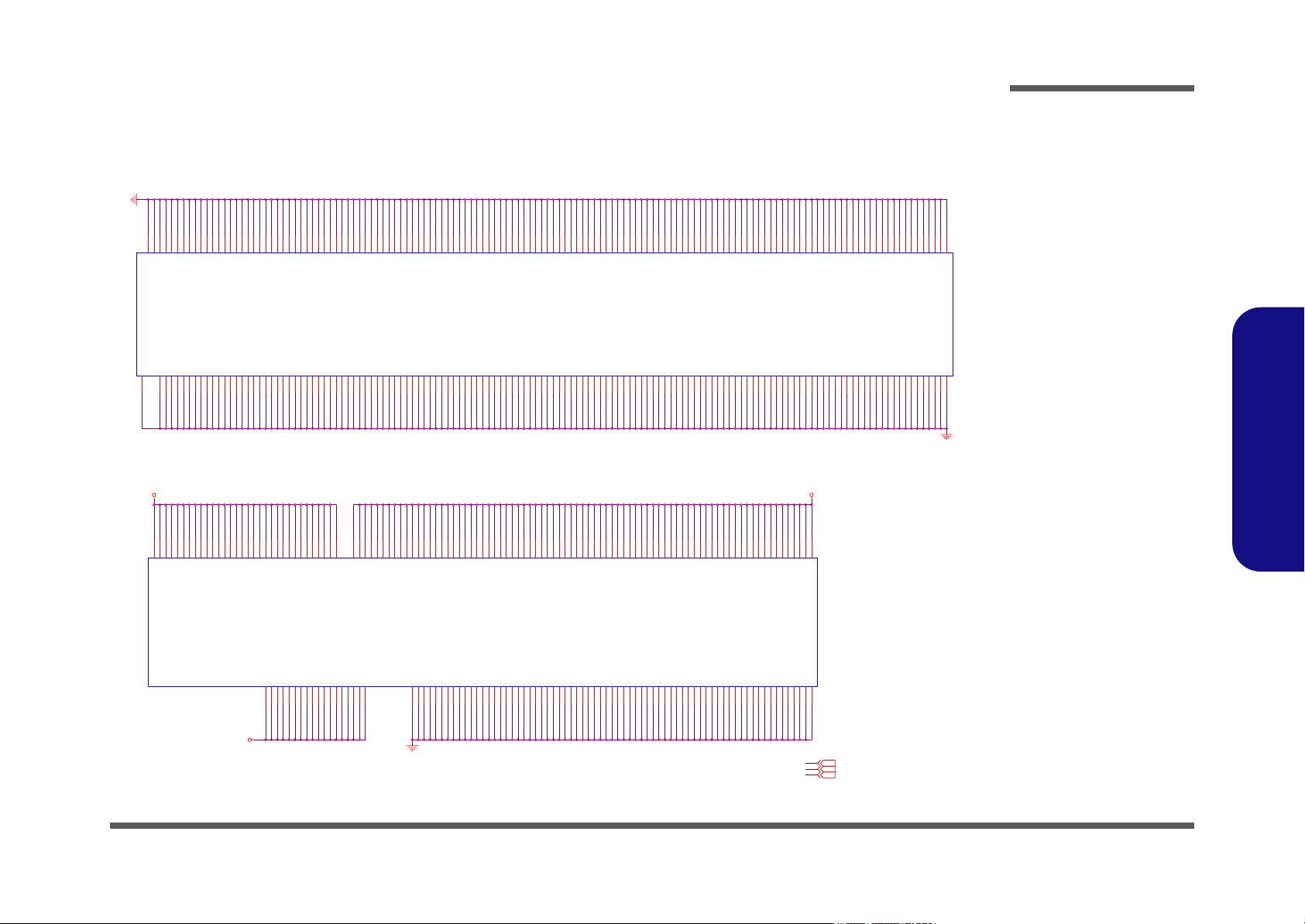

Page 9

Schematic Diagrams

DRII SO-DIMM 2

Sheet 9 of 40

DRII SO-DIMM 2

B.Schematic Diagrams

SO-DIMM 2

Layout Note:

Memory clock signal/space:

9 / 4 / 9 => 9 / 5 / 9

R43

10K_04

R44

10K_04

+3VS

+VTT_MEM RESISTORS

16-56034-45A

M_B_A0

M_B_A[13:0][6]

M_B_BS2#[6]

M_B_BS0#[6]

M_B_BS1#[6]

M_CLK_DDR3[5]

M_CLK_DDR3#[5]

M_CLK_DDR4[5]

M_CLK_DDR4#[5]

M_B_CAS#[6]

M_B_RAS#[6]

M_B_WE#[6]

ICH_SMBCLK[10,11,14,18]

ICH_SMBDAT[10,11,14,18]

M_B_DQS0[6]

M_B_DQS1[6]

M_B_DQS2[6]

M_B_DQS3[6]

M_B_DQS4[6]

M_B_DQS5[6]

M_B_DQS6[6]

M_B_DQS7[6]

M_B_DQS0#[6]

M_B_DQS1#[6]

M_B_DQS2#[6]

M_B_DQS3#[6]

M_B_DQS4#[6]

M_B_DQS5#[6]

M_B_DQS6#[6]

M_B_DQS7#[6]

M_B_BS2#

M_B_BS0#

M_B_BS1#

M_CS2#

M_CS2#[5]

M_CS3#

M_CS3#[5]

M_CLK_DDR3

M_CLK_DDR3#

M_CLK_DDR4

M_CLK_DDR4#

M_CKE2

M_CKE2[5]

M_CKE3

M_CKE3[5]

M_B_CAS#

M_B_RAS#

M_B_WE#

SA0_DIM2

SA1_DIM2

M_ODT2

M_ODT2[5]

M_ODT3

M_ODT3[5]

M_B_DM0[6]

M_B_DM1[6]

M_B_DM2[6]

M_B_DM3[6]

M_B_DM4[6]

M_B_DM5[6]

M_B_DM6[6]

M_B_DM7[6]

JDIMM-2A

M_B_A0 M_B_DQ0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

102

101

100

99

98

97

94

92

93

91

105

90

89

116

86

84

85

107

106

110

115

30

32

164

166

79

80

113

108

109

198

200

197

195

114

119

10

26

52

67

130

147

170

185

13

31

51

70

131

148

169

188

11

29

49

68

129

146

167

186

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12

A13

A14

A15

A16_BA2

BA0

BA1

S0#

S1#

CK0

CK0#

CK1

CK1#

CKE0

CKE1

CAS#

RAS#

WE#

SA0

SA1

SCL

SDA

ODT0

ODT1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS0#

DQS1#

DQS2#

DQS3#

DQS4#

DQS5#

DQS6#

DQS7#

CA0115-200N02

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

5

DQ0

7

M_B_DQ1

DQ1

17

M_B_DQ2

DQ2

19

M_B_DQ3

DQ3

M_B_DQ4

4

DQ4

6

M_B_DQ5

DQ5

M_B_DQ6

14

DQ6

16

M_B_DQ7

DQ7

M_B_DQ8

23

DQ8

25

M_B_DQ9

DQ9

35

M_B_DQ10

M_B_DQ11

37

20

M_B_DQ12

M_B_DQ13

22

M_B_DQ14

36

38

M_B_DQ15

43

M_B_DQ16

M_B_DQ17

45

M_B_DQ18

55

57

M_B_DQ19

M_B_DQ20

44

M_B_DQ21

46

M_B_DQ22

56

M_B_DQ23

58

M_B_DQ24

61

M_B_DQ25

63

73

M_B_DQ26

M_B_DQ27

75

M_B_DQ28

62

64

M_B_DQ29

M_B_DQ30

74

M_B_DQ31

76

M_B_DQ32

123

M_B_DQ33

125

M_B_DQ34

135

M_B_DQ35

137

M_B_DQ36

124

M_B_DQ37

126

M_B_DQ38

134

M_B_DQ39

136

M_B_DQ40

141

M_B_DQ41

143

M_B_DQ42

151

M_B_DQ43

153

M_B_DQ44

140

M_B_DQ45

142

M_B_DQ46

152

M_B_DQ47

154

M_B_DQ48

157

M_B_DQ49

159

M_B_DQ50

173

M_B_DQ51

175

M_B_DQ52

158

M_B_DQ53

160

M_B_DQ54

174

M_B_DQ55

176

M_B_DQ56

179

M_B_DQ57

181

M_B_DQ58

189

M_B_DQ59

191

M_B_DQ60

180

M_B_DQ61

182

M_B_DQ62

192

M_B_DQ63

194

M_B_DQ[63:0] [6]

+3VS

MVREF_DIM2

C467

0.1u_X7R_04

C250

0.1u_X7R_04

+1.8V

112

111

117

96

95

118

81

82

87

103

88

104

199

83

120

50

69

163

1

201

202

47

133

183

77

12

48

184

78

71

72

121

122

196

193

8

JDIMM-2B

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDDSPD

NC1

NC2

NC3

NC4

NCTEST

VREF

GND0

GND1

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6