Page 1

Schematic Diagrams

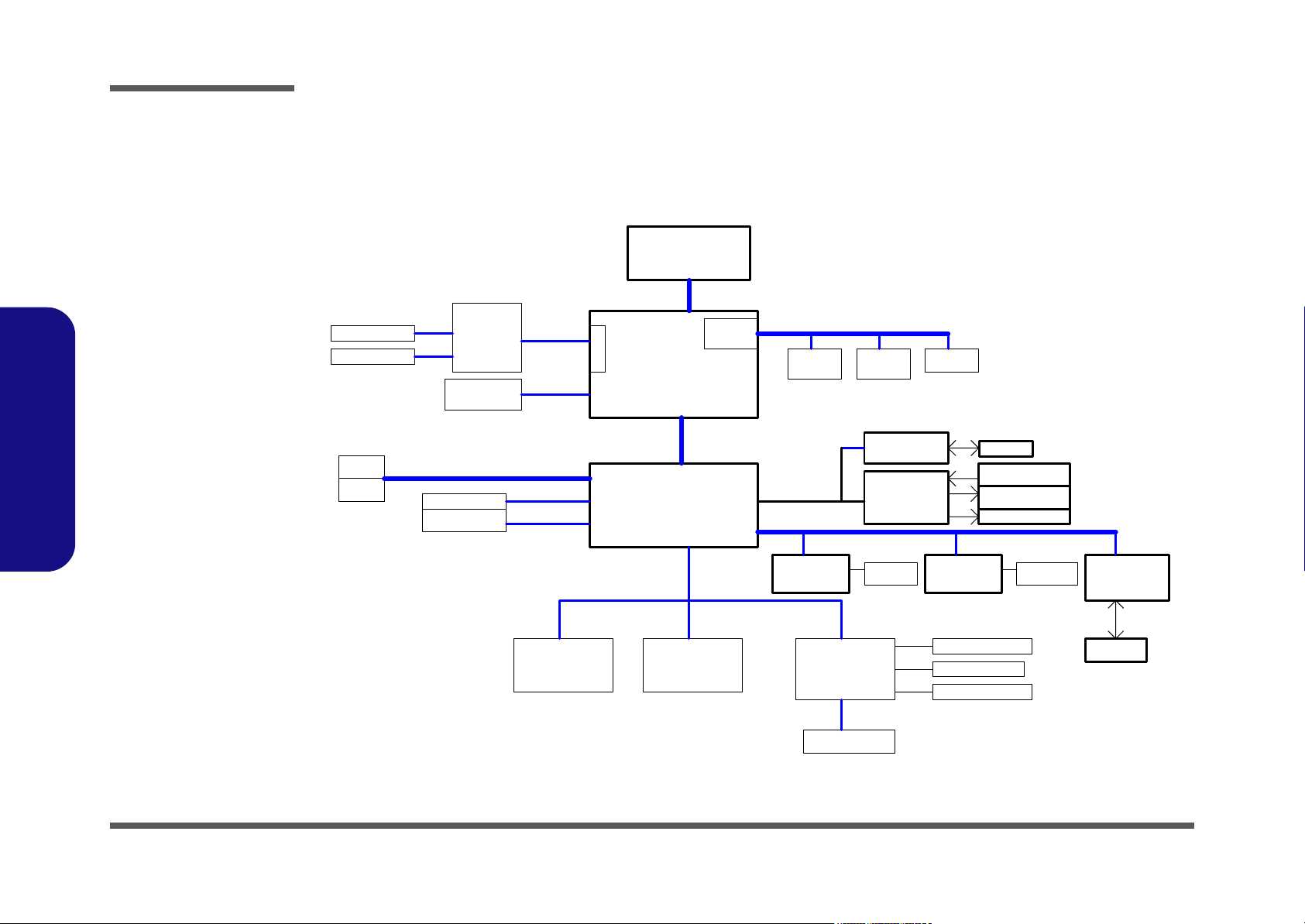

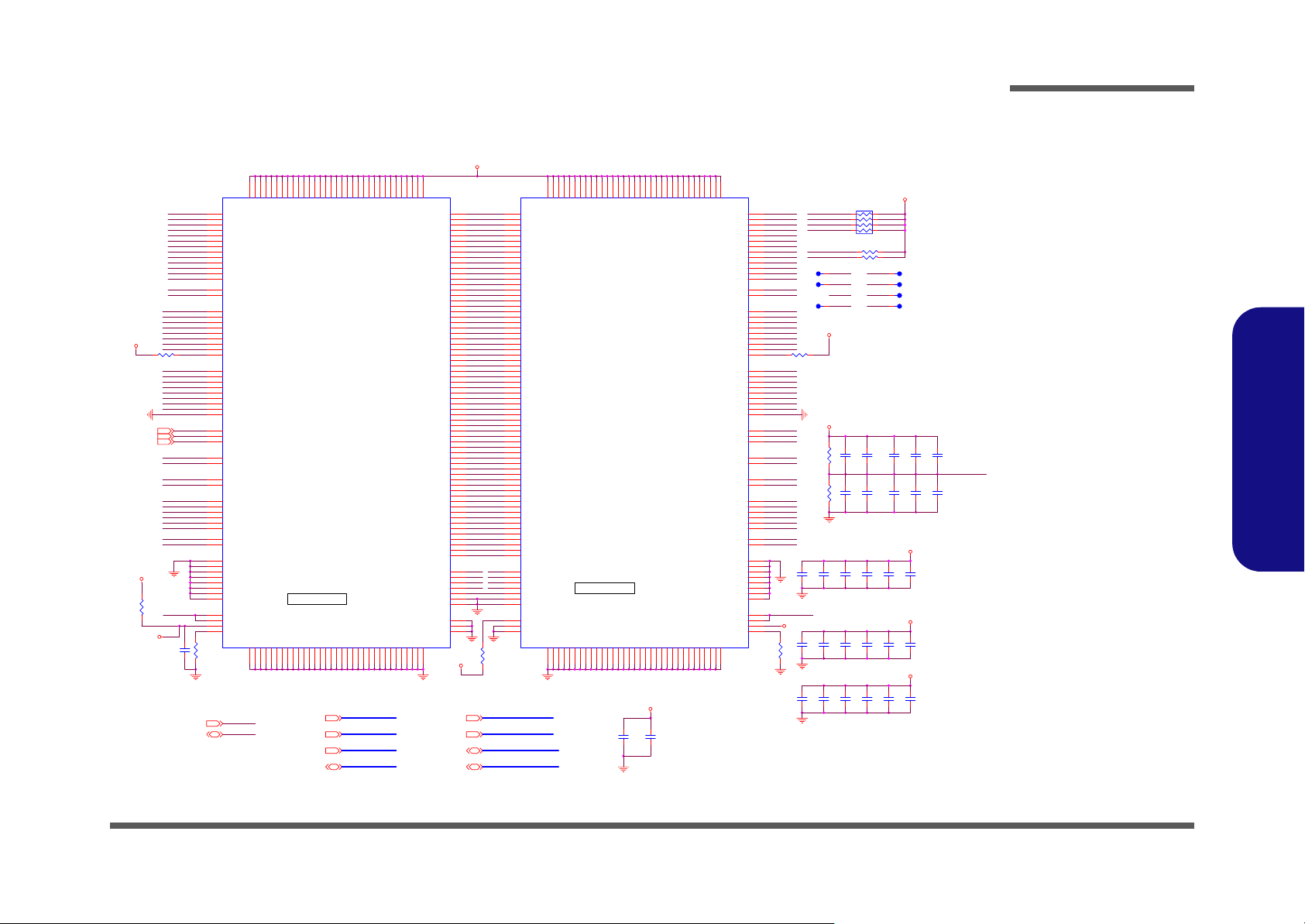

Appendix B:Schematic Diagrams

This appendix has circuit diagrams of the systems PCB’s.

Printed Circuit Board Part No. of the Latest Version

System Board 71-M2200-D06

Inverter Board 71-M220R-D03

The following table indicates where to find the appropriate schematic diagram.

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 LVDS Interface (SiS301/2LV) - Page B - 13 Audio Codec & AMP - Page B - 24

Table - Page B - 3 961A-1 (PCI/IDE/HyperZip) - 1 of 4 - Page B - 14 Fan & Modem Conn - Page B - 25

CPU (Socket 478) 1 of 2 - Page B - 4 961A-2 (Misc Signals) - 2 of 4 - Page B - 15 CPU VCORE - Page B - 26

CPU (Socket 478) 2 of 2 - Page B - 5 961A-3 (USB) - 3 of 4 - Page B - 16 System Power 1 SCH (+3V, +5V, +12V) - Page B - 27

Table 1

Schematic

Diagrams

Schematic Diagrams

Clock Generator - Page B - 6 961A-4 (Power & RTC) - 4 of 4 - Page B - 17 System Power 2 SCH (+2.5V, +1.25V) - Page B - 28

650-1 (Host/AGP) - 1 of 4 - Page B - 7 IDE, LVDS, Inverter Conn - Page B - 18 +1.8V, 3VH8, VCCID, PWRSW - Page B - 29

650-2 (Memory for DDR) - 2 of 4 - Page B - 8 PCI LAN RTL8100B - Page B - 19 Charger-PWM - Page B - 30

650-3 (HyperZip/VGA/Misc) - 3 of 4 - Page B - 9 PCMCIA PCI1410 - Page B - 20 Hole - Page B - 31

650-4 (Power) - 4 of 4 - Page B - 10 1394 TSB43AB21 - Page B - 21 Inverter Board - Page B - 32

DDR SDRAM DIMM 1 & DIMM2 - Page B - 11 LPC Super I/O NS393 - Page B - 22

DDR SSTL-2 Termination Resistors - Page B - 12 LPC H8 - Page B - 23

B-1

Page 2

Schematic Diagrams

Sheet 1 of 31

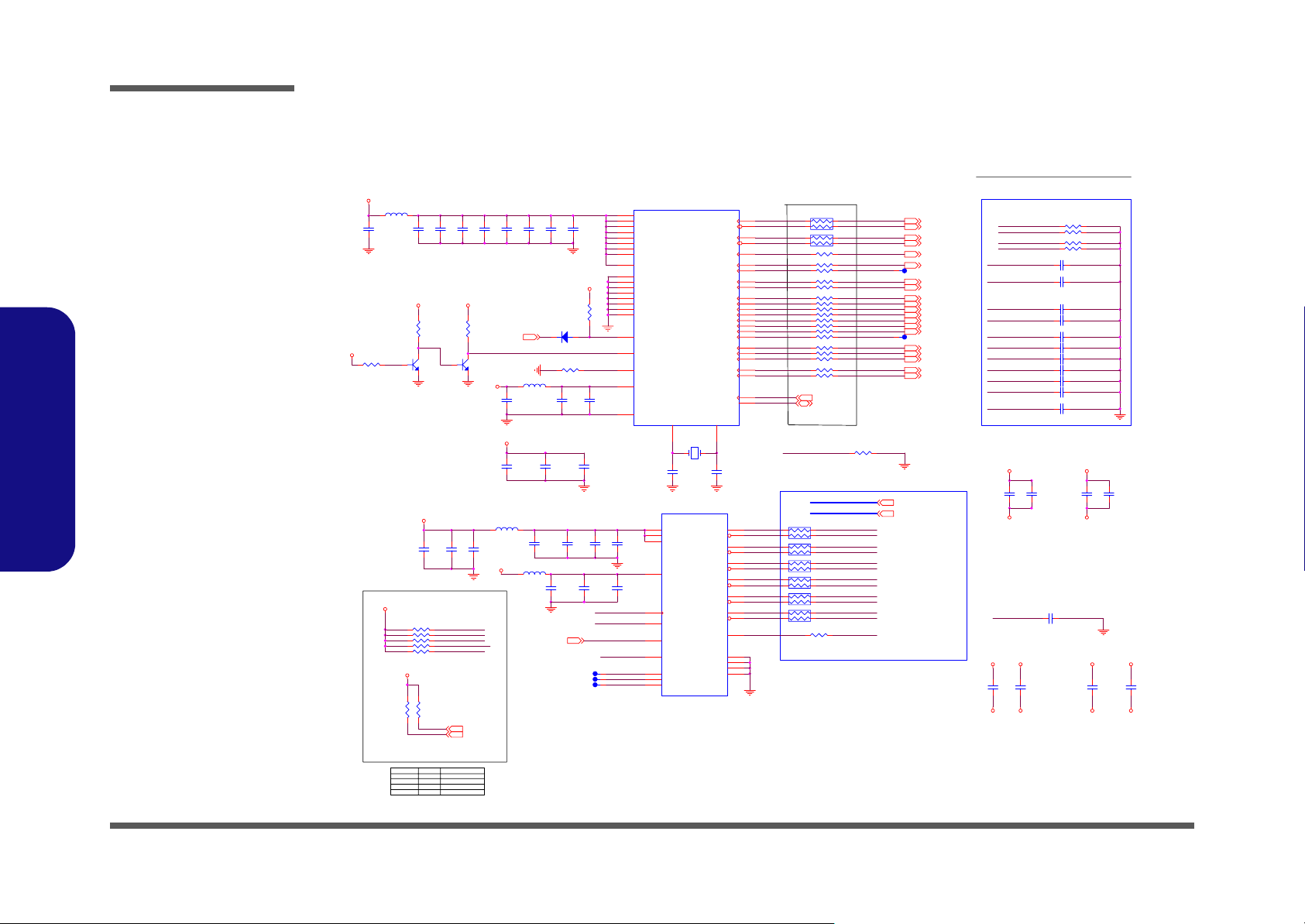

System Block

Diagram

System Block Diagram

M220 System Block Diagram

P4 CPU

SOCKET-478

Page 1 ; 2

Host Bus

GTL+ & AGTL

LCD PANNEL

TV OUT

LVDS

301/2 LV

SIS

128 PIN LQFP

Page 10

CRT PORT

VB-LINK

RGB

SiS

VGA

M650

1.8V CORE WITH MIXED 1.2V 1.5V 2.5V

3.3V I/0

702 PIN BGA

Page 4; 5; 6; 7

MEMORY

CONTROL

DDR SDRAM

DIMM 1 DIMM 2

Page 9 Page 9

SSTL-2 Termination

Rtt

Schematic Diagrams

B - 2 System Block Diagram (71-M2200-D06)

USB 0

USB 1

HDD

CDROM/DVDROM

PJ1: VDD5

PJ2: VDD3

PJ4: +2.5V

PJ5: +1.25VS

PJ6: +1.8VS

PR1: Vcore

Page 15

IDE 0 ULTRA 66/100

IDE 1

LPC Rom

MuTIOL

SiS 961(2L)

1.8V CORE WITH MIXED 1.2V 1.5V 2.5V

3.3V I/0

371 PIN BGA

Page 11 ; 12 ; 13 ; 14

LPC Bus

KBC

H8

2149

Page 20Page 19 Page 19

ACLINK

PCI BUS

CB

TI 1410

SIO

NS87393

Page 17

4MB ROM

MDC

AC'97

Audio Codec

REAL TEC ALC201

Audio Board

ONE SLOT

XBUS

Page 19

Page 22

IEE 1394

TI TPS43AB21

RJ 11 PORT

MIC IN PORT

Analog Out PORT

SPDIF OUT PORT

Page 18

PRINT PORT

Page 19

IR PORT

FLOPPY

Page 19

Page 19

ONE SLOT

LAN

REAL 8100BL

Page 16

RJ 45 PORT

Page 3

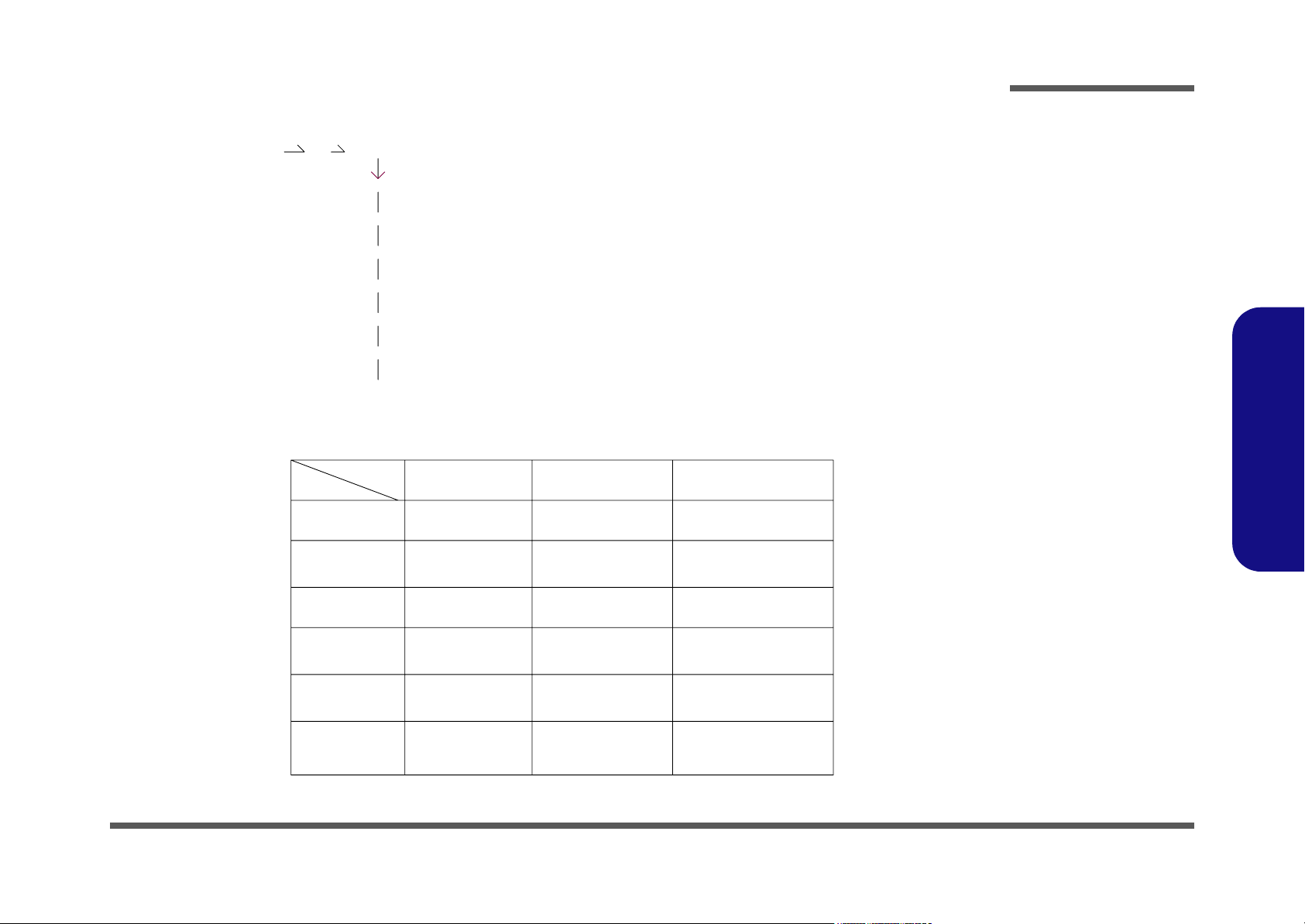

Table

Schematic Diagrams

VIN VINS AUX POWERS (SB5V,SB3.3V,SB2.5V,SB1.8V,+2.5VDIMM(or VCC3MEM)

(PWRTN)

(PSON#)

MAIN POWERS (VCC5,VCC3.3,VCC2.5V,VCC1.8V,VCCVID,DDR_VTT)

(CORE_ON)

VCC_CORE

(PWRGD TO CHIP)

(PCIRST#)

DEVICE

SIS650(VGA)

CHRONTEL CH0717

1394 TI TBA43AB22

CB TI 1410A

LAN REL8139C

MINI PCI

INTA#

INTA#

INTB#

*INTB#

INTC#

INTD#

INTC#

INTD#

REG1

GNT1

REG0

GNT0

REG2

GNT2

REG3

GNT3

Schematic Diagrams

Sheet 2 of 31

Table

AD22

AD23

AD21

AD24

AD25

Table (71-M2200-D06) B - 3

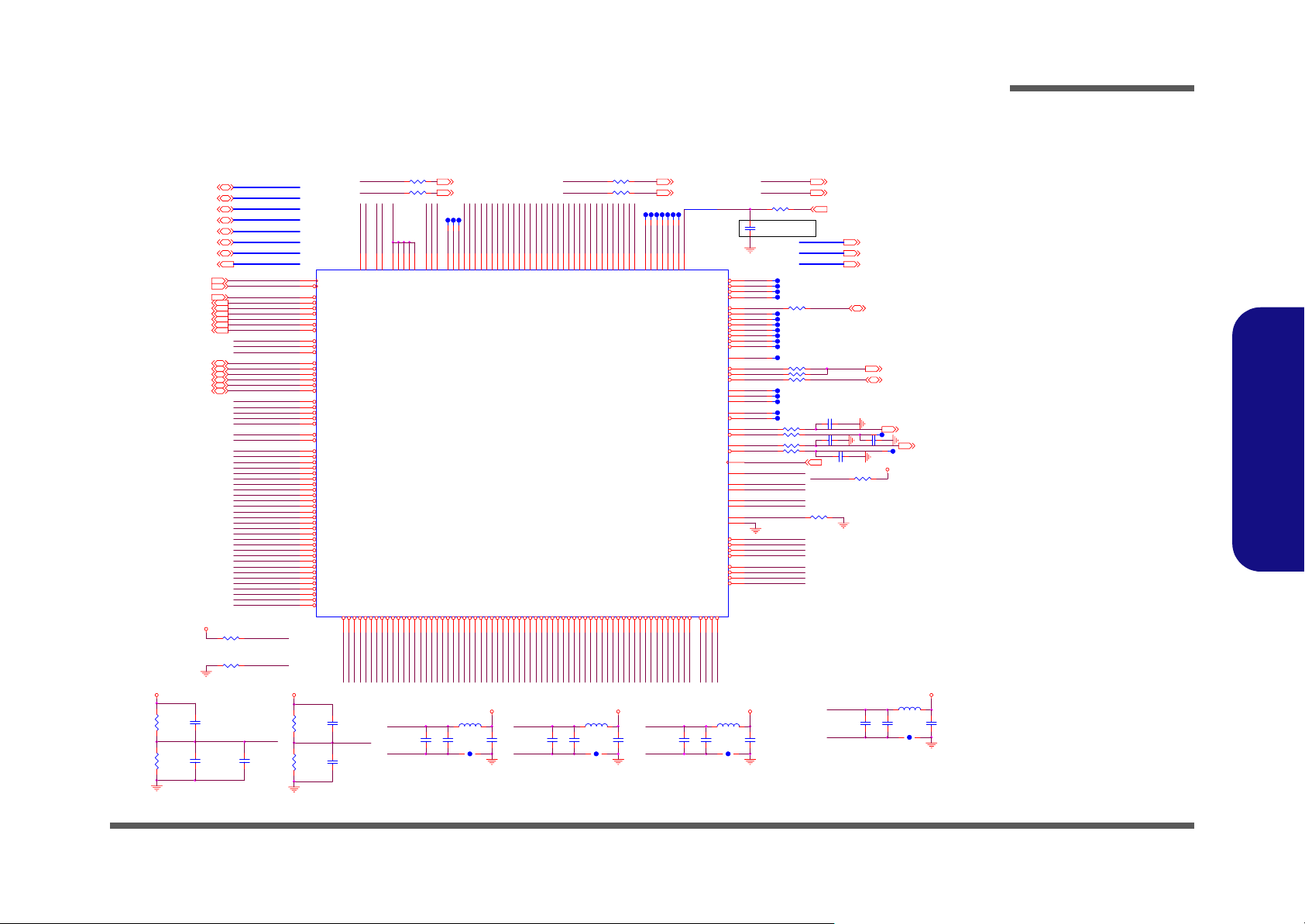

Page 4

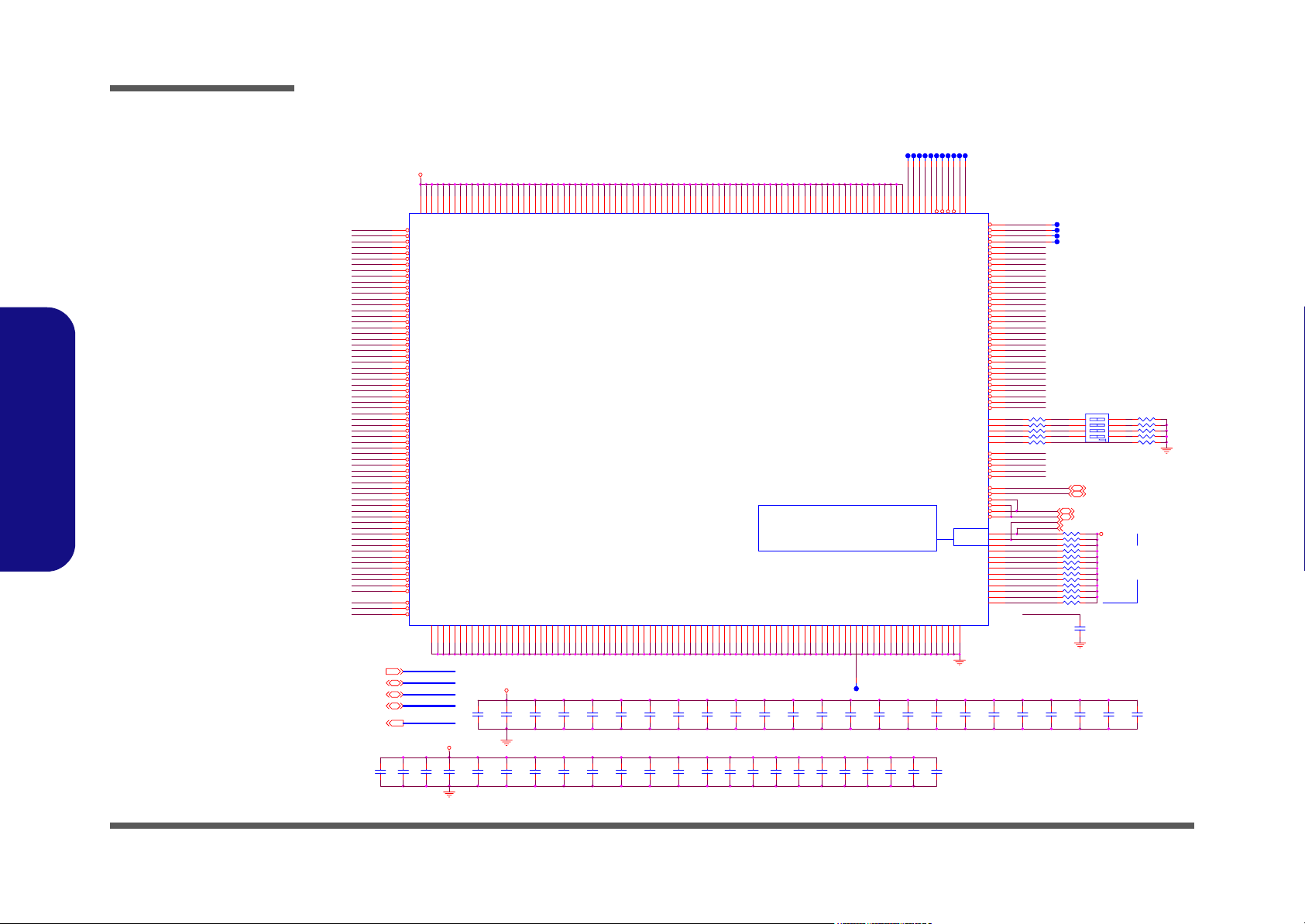

Schematic Diagrams

CPU (Socket 478) 1 of 2

Sheet 3 of 31

CPU 1 of 2

Schematic Diagrams

HD-0

HD-1

HD-2

HD-3

HD-4

HD-5

HD-6

HD-7

HD-8

HD-9

HD-10

HD-11

HD-12

HD-13

HD-14

HD-15

HD-17

HD-18

HD-19

HD-20

HD-21

HD-22

HD-23

HD-24

HD-25

HD-26

HD-27

HD-28

HD-29

HD-30

HD-31

HD-32

HD-33

HD-34

HD-35

HD-36

HD-37

HD-38

HD-39

HD-40

HD-41

HD-42

HD-43

HD-44

HD-45

HD-46

HD-47

HD-48

HD-49

HD-50

HD-51

HD-52

HD-53

HD-54

HD-55

HD-56

HD-57

HD-58

HD-59

HD-60

HD-61

HD-62

HD-63

RS-0

RS-1

RS-2

VCORE

VCC_CORE

JCPU1A

B21

D0

B22

D1

A23

D2

A25

D3

C21

D4

D22

D5

B24

D6

C23

D7

C24

D8

B25

D9

G22

D10

H21

D11

C26

D12

D23

D13

J21

D14

D25

D15

H22

D16

E24

D17

G23

D18

F23

D19

F24

D20

E25

D21

F26

D22

D26

D23

L21

D24

G26

D25

H24

D26

M21

D27

L22

D28

J24

D29

K23

D30

H25

D31

M23

D32

N22

D33

P21

D34

M24

D35

N23

D36

M26

D37

N26

D38

N25

D39

R21

D40

P24

D41

R25

D42

R24

D43

T26

D44

T25

D45

T22

D46

T23

D47

U26

D48

U24

D49

U23

D50

V25

D51

U21

D52

V22

D53

V24

D54

W26

D55

Y26

D56

W25

D57

Y23

D58

Y24

D59

Y21

D60

AA25

D61

AA22

D62

AA24

D63

F1

RS0

G5

RS1

F4

RS2

T160T157T128T51

T26T27T113T21T22T107T133

TZ0106

TZ0108

TZ0101

TZ0104

TZ0105

TZ0110

TZ0103

AD2

VSS

TZ0111

TZ0107

TZ0109

J26

K25

K26

L25

AD3

AE21

AF24

AF25

AB1

TZ0112

A35

Y1

A34

W2

A33

V3

A32

U4

A31

T5

A30

W1

A29

R6

A28

V2

A27

T4

A26

U3

A25

P6

A24

U1

A23

T2

A22

R3

A21

P4

A20

P3

A19

R2

A18

T1

A17

N5

A16

N4

A15

N2

A14

M1

A13

N1

A12

M4

A11

M3

A10

L2

A9

M6

A8

L3

A7

K1

A6

L6

A5

K4

A4

K2

A3

AE5

VID0

AE4

VID1

AE3

VID2

AE2

VID3

AE1

VID4

H3

REQ4

J3

REQ3

J4

REQ2

K5

REQ1

J1

REQ0

AB4

BPM5

AA5

BPM4

Y6

BPM3

AC4

BPM2

AB5

BPM1

AC6

BPM0

AD25

A6

Y3

W4

U6

AB22

AA20

AC23

AC24

AC20

AC21

AA2

AD24

NORTHWOOD478

TZ0113

TZ0114

TZ0115

HA-31

HA-30

HA-29

HA-28

HA-27

HA-26

HA-25

HA-24

HA-23

HA-22

HA-21

HA-20

HA-19

HA-18HD-16

HA-17

HA-16

HA-15

HA-14

HA-13

HA-12

HA-11

HA-10

HA-9

HA-8

HA-7

HA-6

HA-5

HA-4

HA-3

R563

R289

R566

R568

R570

HREQ-4

HREQ-3

HREQ-2

HREQ-1

HREQ-0

HBPRM5#

HBPRM4#

HBPM1#

HBPM0#

PM_CPUPERF#

H_DPSLP#

Z0101

Z0102

Z0103

Z0104

Z0105

Z0106

Z0107

Z0108

Z0109

Z0110

Z0111

Z0112

Z0113

H_DPSLP#

T162

T156

T159

T161

VID0

0

VID1

0

VID2

0

VID3

0

VID4

0(R)

PM_CPUPERF# [12]

H_DPSLP# [13,24]

R36

R257

R307

R310

R311

R232

R233

R231

R35

R255

R253

R306

R37

C718

0.0047UF

SW7 SW DIP-4

4

3

2

1

HBPRM5# [2]

HBPRM4# [2]

HBPM1# [2]

HBPM0# [2]

51

VCC_CORE

51

51

51

Design Guide

51

51

updates for

51

51

P4P/845

51

51

51

51

51

5

6

7

8

R564

R565

R567

R569

R571 51

51

51

51

51

DEP0

DEP1

DEP2

DEP3

TESTHI12

TESTHI11

TESTHI10

TESTHI9

TESTHI8

TESTHI7

TESTHI6

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

VSS

VSS

VSS

VSS

VSS

VSS

VSS

C11

C13

C15

C17

C19

C2

A10

A12

A14

A16

A18

A20A8AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

AE16

AE18

AE20

AE6

AE8

AF11

AF13

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

B11

B13

B15

B17

B19B7B9

C10

C12

C14

C16

C18

C20C8D11

D13

D15

D17

D19D7D9

E10

E12

E14

E16

E18

E20E8F11

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

F13

VCC

VCC

VCC

F15

F17

F19

F9

A7

NCNCNCNCNCNCNC

VCC

VCC

VCC

VCC

TZ0102

A22

INTEL P4 CPU SOCKET 478 PART 1

MOBIL CPU

AD25=DPSLP(H_DPSLP#)

A6=GHI#(PM_CPUPERF#)

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

SKTOCC#

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

H1H4H23

H26

A11

A13

A15

A17

A19

A21

A24

A26A3A9

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

AC19

AC2

AC22

AC25

AC5

AC7

AC9

AD1

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

AE9

AF1

AF10

AF12

AF14

AF16

AF18

AF20

AF26

AF6

AF8

VSS

B10

B12

B14

B16

B18

B20

B23

B26B4B8

C723

0.1UF

RS-[0..2]

HD-[0..63]

HA-[3..31]

HREQ-[0..4]

VID[0..4]

C724

0.1UF

VCC_CORE

C406

0.1UF

C721

10UF/6.3V

C102

0.1UF

VCC_CORE

C90

10UF/6.3V

C417

0.1UF

RS-[0..2][4]

HD-[0..63][4]

HA-[3..31][4]

HREQ-[0..4][4]

VID[0..4][12,24]

C722

0.1UF

B - 4 CPU (Socket 478) 1 of 2 (71-M2200-D06)

C109

10UF/6.3V

C440

0.1UF

C110

10UF/16V

C409

0.1UF

C87

10UF/6.3V

C439

0.1UF

C471

10UF/6.3V

C400

0.1UF

C430

10UF/16V

C378

0.1UF

C412

10UF/16V

C377

0.1UF

C401

10UF/16V

C376

0.1UF

C389

10UF/6.3V

C375

0.1UF

C82

0.1UF

C380

10UF/6.3V

C83

0.1UF

C442

10UF/16V

C84

0.1UF

C466

10UF/16V

C85

0.1UF

C469

10UF/6.3V

C97

0.1UF

C399

0.1UF

Z0114

T25

C467

10UF/6.3V

C116

0.1UF

C470

10UF/6.3V

C429

0.1UF

C468

10UF/6.3V

C117

0.1UF

10UF/6.3V(0805)

C383

C385

10UF/6.3V(0805)

10UF/6.3V(0805)

C386

C392

10UF/6.3V(0805)

10UF/6.3V(0805)

C407

10UF/6.3V(0805)

C431

10UF/6.3V(0805)

C434

Page 5

CPU (Socket 478) 2 of 2

HDSTBP-[0..3]

HDSTBN-[0..3]

DBI-[0..3]

HASTB-[0..1]

C25C5C7C9D10

D12

D14

D16

D18

D20

D21

JCPU1B

AE23

AD20

AD22

AC26

AD26

V21

P26

G25

E21

R5

L5

AE25

E5

D1

AF22

AF23

P1

L24

W23

P23

J23

F21

W22

R22

K22

E22

A5

A4

E11

E13

E15

E17

E19

E23

E26

E4

E7

E9

F10

F12

F14

F16

F18

F2

F22

F25

F5

F8

G21

G24

G3 R4

VSS

VSS

VCCIOPLL

VCCA

VSSA

ITP_CLK0

ITP_CLK1

DB#3

DB#2

DB#1

DB#0

ADSTB1

ADSTB0

DBRESET

LINT1

LINT0

BCLK0

BCLK1

COMP1

COMP0

STBP3

STBP2

STBP1

STBP0

STBN3

STBN2

STBN1

STBN0

VCC_SENSE

VSS_SENSE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

K24K3K6L1L23

J2

J22

J25J5K21

G6

D24D3D6

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

L26L4M2

M22

M25M5N21

VCC_CORE

27.4 1%

Final ITP Port Define Ready

2001-02-19 am 11:35

VCC_CORE

HCLK_ITP0#

HCLK_ITP0

4.7uH_SMD 30%

1 2

1 2

4.7uH_SMD 30%

4

RP35

4P2RX0(R)

HBPM0#

HBPM1#

HBPRM4#

HBPRM5#

HTCK

L20

Z0201

Z0202

L63

C362

47UF

HCLK-CPU#

1

HCLK-CPU

23

NMI[12]

INTR[12]

HCLK-CPU[3]

HCLK-CPU#[3]

R312

R236 51.1 1%

R268

Z0208 Z0206

T148

R269 0(R)

Z0209 Z0207

T149

ITP_STPWR

HBPM0#

[2]

HBPM1#

[2]

HBPRM4#

[2]

HBPRM5#

[2]

HTCK

[2]

HDSTBP-[0..3][4]

HDSTBN-[0..3][4]

HASTB-[0..1][4]

C62

47UF

HCLK_ITP0

HCLK_ITP0#

DBI-3

DBI-2

DBI-1

DBI-0

HASTB-1

HASTB-0

DBRESET

NMI

INTR

HCLK-CPU

HCLK-CPU#

51.1 1%

HDSTBP-3

HDSTBP-2

HDSTBP-1

HDSTBP-0

HDSTBN-3

HDSTBN-2

HDSTBN-1

HDSTBN-0

0(R)

R86 1.5K

R294 51

R292 51

R287 51

R283 51

R280

DBI-[0..3][4]

Z0204

Z0205

Z0203

Schematic Diagrams

20 mil

C367

C370

CB1

30 mil

HTDI

HTRST-

1UF

T152

T153

T155

T158

VCCVID

T151

T154

R235

100 1%

FERR- [12]

STPCLK- [12]

INIT- [12]

DBSY- [4]

DRDY- [4]

HTRDY- [4]

ADS- [4]

HLOCK- [4]

BREQ0- [4]

BNR- [4]

HIT- [4]

HITM- [4]

BPRI- [4]

DEFER- [4]

IGNNE- [12]

SMI- [12]

A20M- [12]

CPUSLP- [12]

CPUPWRGD [4]

CPURST- [4]

BSEL0 [3]

BSEL1 [3]

R291

R284 680

220PF

220PF

F6

F20

AA6

AA21

D8

E1

C22

VSS

VSS

VSS

VSS

VSS

VSS

MCERR

GTLREF3

GTLREF2

GTLREF1

GTLREF0

STPCLK

DRDY

DEFER

PROCHOT

IGNNE

PWRGOOD

RESET

THERMDA

THERMDC

THERMTRIP

BSEL0

BSEL1

VCCVID

VCCVIDPRG

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N24N3N6P2P22

R279

VSS

P25

P5

R1

R23

R26

Z0219CPURST-

0

AC3

IERR

V6

B6

FERR

Y4

AA3

BINIT

W5

INIT

AB2

RSP

H5

DBSY

H2

J6

TRDY

G1

ADS

G4

LOCK

H6

BR0

G2

BNR

F3

HIT

E3

HITM

D2

BPRI

E2

D4

TCK

C1

TDI

F7

TMS

E6

TRST

D5

TDO

C3

B2

B5

SMI

C6

A20M

AB26

SLP

AB23

AB25

B3

C4

A2

AD6

AD5

AC1

AP0

V5

AP1

AF4

AF3

Y5

VSS

Y25

VSS

Y22

VSS

Y2

VSS

W6

VSS

W3

VSS

W24

VSS

W21

VSS

V4

VSS

V26

VSS

V23

VSS

V1

VSS

U5

VSS

U25

VSS

U22

VSS

U2

VSS

T6

VSS

T3

VSS

T24

VSS

T21

VSS

NORTHWOOD478

IERR

TZ0206

FERRSTPCLK-

TZ0208

INIT-

TZ0207

DBSYDRDYHTRDYADSHLOCKBREQ0BNRHITHITMBPRIDEFERHTCK

HTDI

HTMS

HTRSTHTDO

PROCHOTIGNNESMIA20MCPUSLPCPUPWRGD

CPURST-

THERMDA

THERMDC

THERMTRIP-

TZ0201

TZ0202

TZ0203

ITP/TAP TERMINATION

CLOSE TO CPU

C443

C453

220PF

220PF

DBRESET

HTMS

H8_SMDATA

H8_SMCLK

THERMDA

THERMDC

R267 0

R256 200(0805)

+3VS +3VS

VCC_CORE

150

CPUGTLVREFA

CPUGTLVREFB

C461

1UF

C464

0.1UF

C419

0.1UF

CPURSTCPUSLP-

R301

R288

20 Mils

C413

0.1UF(0805)

R234

R305 82_1%

R304

100 1%

0.1UF

CPUPWRGD

C719

0.0047UF

R274 2.2K

R276 2.2K

C418

22P

T143

20 mil

Z717

82_1%

VCC_CORE

C465

C463

0.1UF

0.1UF

VCC_CORE

C432

C382

0.1UF

C720

0.0047UF

150

40.2 1%

U5

3

DXP

4

DXN

11

ALERT#

2

GND(VCC)

7

GND

8

GND

TC1066

Hardware Protect

=100

度

85

95

100

115

VCC_CORE

C462

0.1UF

C388

0.1UF

C725

0.0047UF

VCC_CORE

VCC_CORE

3VH8

CRIT1

0

0

X

1

CPU SIGNAL TERMINALION

FERR-

BREQ0-

PROCHOT-

CPUPWRGD

THERMTRIP-

A20M-

STPCLK-

CPUSLP-

SMI-

INIT-

IGNNE-

INTR

NMI

CPURST-

HTDO

IERR

ITP/TAP TERMINATION

15

STBY#

12

SMBDATA

14

SMBCLK

6

ADD1

10

ADD0

1

CRIT1/VCC

5

CRIT0

9

OS#

13

NC

16

NC

CRIT0

0

1

0

0

CLOSE TO CPU

R262 62 1%

R313

R316

R34

R318

R265 56 1%

R308 56 1%

R33 56 1%

R270

R309 56 1%

R317

R315

R264

R32

R314 75

R303

CLOSE TO ITP PORT

20 mil

H8_SMDATA

H8_SMCLK

R266 1K

Z210

R259 1K

Z241

Z240

T215

TP16

R273

4.7K(R)

Z717

R82 R

R83 10K(R)

R272

4.7K

R260 0

TZ0209

Z936

51 1%

62 1%

51 1%

62 1%

56 1%

56 1%

56 1%

56 1%

51 1%

10K

H8_SMDATA[20,28]

H8_SMCLK[20,28]

OS#

OS# [27]

VCC_CORE

Schematic Diagrams

Sheet 4 of 31

CPU 2 of 2

CPU (Socket 478) 2 of 2 (71-M2200-D06) B - 5

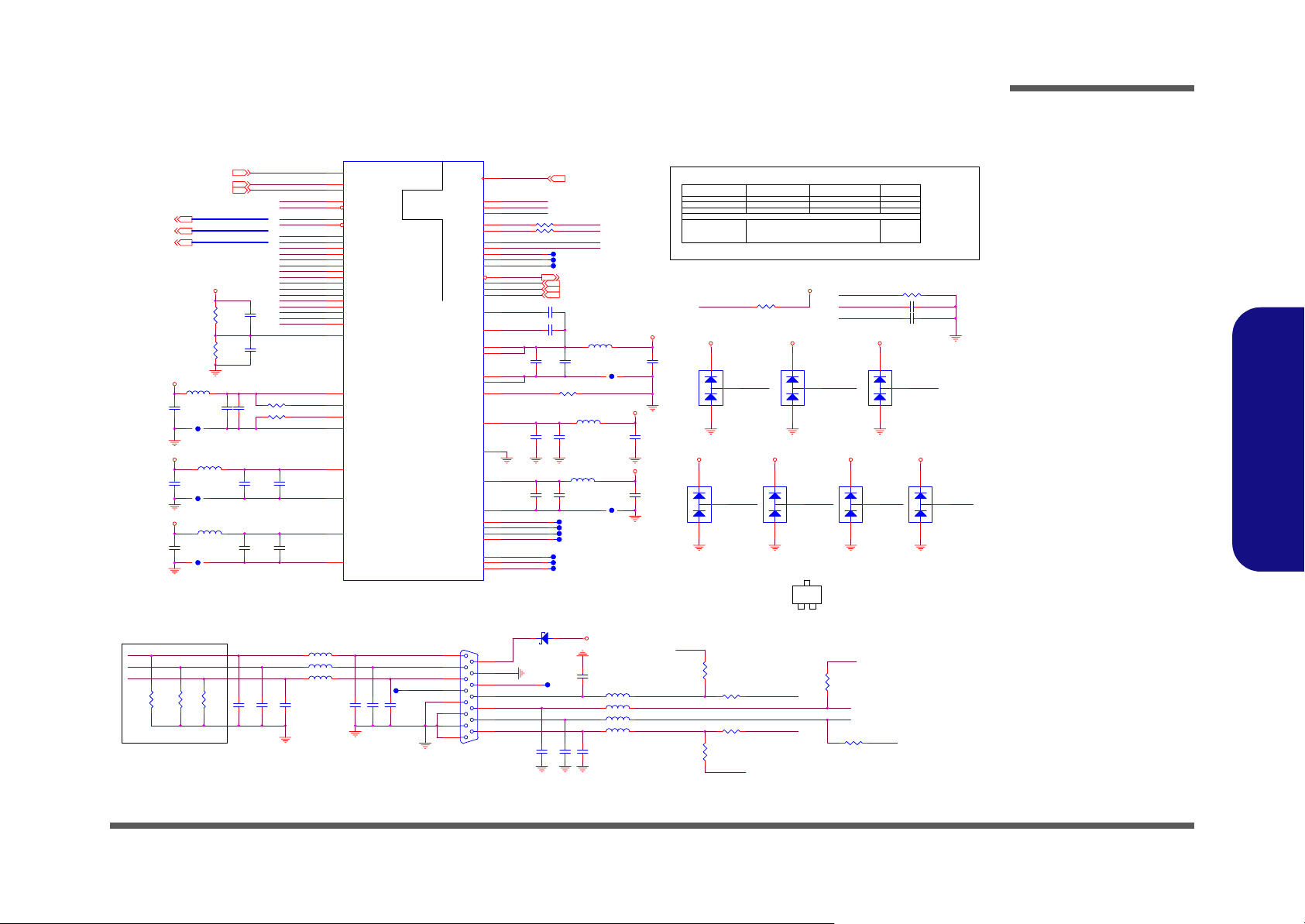

Page 6

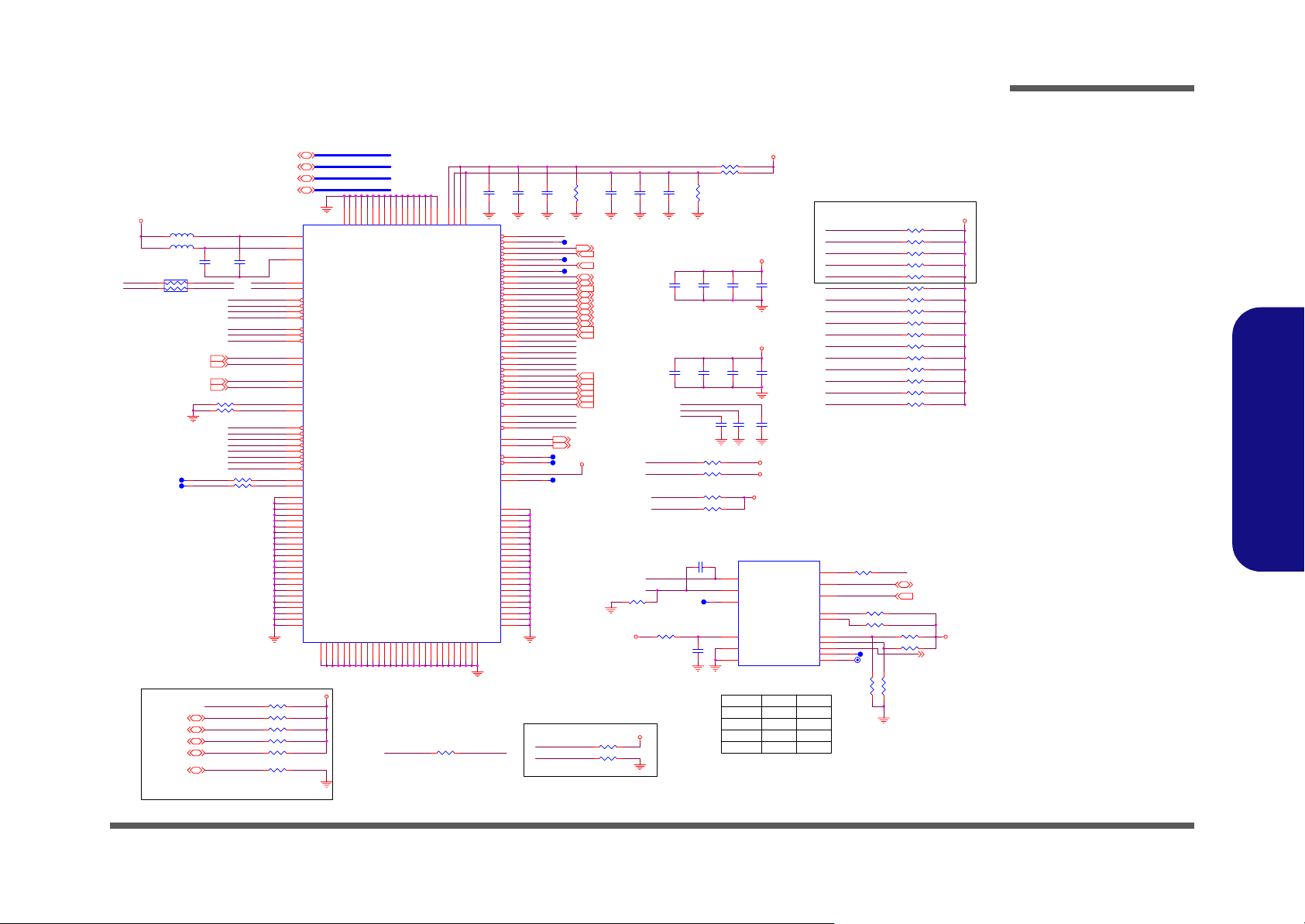

Schematic Diagrams

Clock Generator

Sheet 5 of 31

Clock Generator

Schematic Diagrams

+3VS

L72

BK2125HS121

1 2

C571

C572

0.1UF

10UF/16V

R387

10K

VCC_CORE

R397

10K

PLEASE PLACE IN COMP SIDE

AND NEAR TOGETHER

Z0503

C

Z0504

B

E

+2.5VS

10UF/16V

+3VS

Frequency

Selection

R338 4.7K

R339 4.7K

R340 4.7K(R)

R341

R342 4.7K(R)

+3VS

R281

4.7K

BSEL1 BSEL0 Function

L L

L H

H L

H H

C513

C501

0.1UF

CPUSTP-[12,13]

+3VS

1 2

+2.5VS

C525

0.1UF

0.1UF

L70

1 2

C533

0.1UF

C573

10UF/16V

BK2125HS121

C618

10UF/16V

L74

1 2

FWDSDCLKO[5]

FS4 FS3 FS2 FS1 FS0

0 0 0 1 1

C545

C519

0.1UF

0.1UF

+3VS+3VS

R381

10K

C

Q10

B

Q11

E

2N3904

C619

R277

4.7K

2N3904

+3VS

Clock Buffer (DDR)

L76

C621

C620

0.1UF

0.01UF

FS0

FS1

FS2

FS3

4.7K(R)

FS4

BSEL0 [2]

BSEL1 [2]

Damping Resistors

Main Clock Generator

U22

1

11

13

19

28

29

42

48

12

5

8

18

24

25

32

41

46

Z0538

45

33

Z0505

38

Z0506

36

C529

0.01UF

37

ICS 952001

CY 28342

C586

C591

0.1UF

0.1UF

Z0525

C605

0.1UF

SMBCLK

SMBDAT

FB_IN

TZ0509

TZ0510

TZ0511

CLOCK GEN (650)

VDDREF

VDDZ

VDDPCI

VDDPCI

VDD48

VDDAGP

VDDCPU

VDDSD

PCI_STOP#

VSSREF

VSSZ

VSSPCI

VSSPCI

VSS48

VSSAGP

VSSCPU

VSSSD

CPU_STOP#

PD#/VTT_PWRGD

IREF

VDDA

VSSA

PCICLK_F0/FS3

PCICLK_F1/FS4

24_48M/MULTISEL

XIN

6

Y6

Z0523

1 2

14.318MHz

C488

10PF

U28

CLOCK BUFFER (DDR48)

3

VDD

12

VDD

23

VDD

10

AVDD

7

SCLK

22

SDATA

8

20

9

18

21

FB_OUT

CLK_IN

FB_IN

NC

NC

NC

ICS 93722

CY28352

CPU SDRAM ZCLK AGP PCI

100M 133M 66M 66M 33M

CPUCLK0

CPUCLK#0

CPUCLK1

CPUCLK#1

SDCLK

AGPCLK0

AGPCLK1

ZCLK0

ZCLK1

PCICLK0

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

REF0/FS0

REF1/FS1

REF2/FS2

SDATA

XOUT

7

Z0524

CLK0

CLK#0

CLK1

CLK#1

CLK2

CLK#2

CLK3

CLK#3

CLK4

CLK#4

CLK5

CLK#5

GND

GND

GND

GND

SCLK

10PF

Z0507

40

Z0508

39

Z0509

44

Z0510

43

Z0511

47

Z0512

31

Z0513

30

Z0514

9

Z0515

10

14

15

Z0516

16

Z0517

17

Z0518

20

Z0519

21

Z0520

22

Z0521

23

2

3

4

Z0522

27

48M

MULTISEL

26

SMBCLK

35

SMBDAT

34

C489

Z0526

2

Z0527

1

Z0528

4

Z0529

5

Z0530

13

Z0531

14

Z0532

17

Z0533

16

Z0534

24

Z0535

25

Z0536

26

Z0537

27

19

FB_OUT

28

15

11

6

CLKVCC

C570

C544

0.1UF

0.1UF

+3VS

R352

10K

D20

AC

1N4148

Z0502

R361

475 1%

BK1608HS121

C528

0.1UF

C526

C520

0.01UF

0.1UF

BUFFERVCC

C608

0.1UF

BK1608HS121

C589

C602

10UF/16V

0.01UF

FWDSDCLKO

T185

T191

T184

0 0 0 0 1 100M 100M 66M 66M 33M

Place near to the

Clock Outputs

RP52

1

2 3

RP51

1

2 3

R351 22

R377

R380 22

R359 22

R363 22

R374

FS3

R373 33

FS4

R376 33

R379 33

R390 33

R395 33

R403 33

R409 33(R)

R350

FS0

R354 33

FS1

R355 33

FS2

R391

R396

SMBCLK [8,12,20]

SMBDAT [8,12,20]

MULTISEL

DDRCLK[0..5]

4

4

4

1

2 3

2 3

1

2 3

1

R431

DDRCLK-[0..5]

4P2RX0

23

1

1

23

1

23

4

4P2RX0

4

4P2RX0

4

RP69

RP73 4P2RX0

RP75 4P2RX0

RP76 4P2RX0

RP72

RP70

NEAR DDR SODIMM

4

4

R404

22

4P2RX33

4P2RX33

22

33

33

22

22

DDRCLK3

DDRCLK-3

DDRCLK2

DDRCLK-2

DDRCLK0

DDRCLK-0

DDRCLK1

DDRCLK-1

DDRCLK4

DDRCLK-4

DDRCLK5

DDRCLK-5

FB_IN

HCLK-CPU

HCLK-CPU#

HCLK-650

HCLK-650#

SDCLK

AGPCLK

GCLK_AGP

ZCLK0

ZCLK1

PCICLK961

PCICLK1394

PCICLKPCM

PCICLKLAN

PCICLKIO

PCICLKH8

PCICLKDEBUG

PCICLKMINI

REFCLK0

REFCLK1

CLKAPIC

UCLK48M

SIO48M

0(R)

HCLK-CPU [2]

HCLK-CPU# [2]

HCLK-650 [4]

HCLK-650# [4]

SDCLK [5]

AGPCLK [4]

T174

ZCLK0 [6]

ZCLK1 [11]

PCICLK961 [11]

PCICLK1394 [18]

PCICLKPCM [17]

PCICLKLAN [16]

PCICLKIO [19]

PCICLKH8 [20]

PCICLKDEBUG[15]

T178

14.381MHZ

REFCLK0 [6]

REFCLK1 [12]

CLKAPIC [12]

48 MHZ

UCLK48M [13]

SIO48M [19]

DDRCLK[0..5] [8]

DDRCLK-[0..5] [8]

By-Pass Capacitors

Place near to the Clock

Outputs

HCLK-CPU

R364

HCLK-CPU#

R370

HCLK-650

R356

HCLK-650#

R360

C502

SDCLK

C532

AGPCLK

C514 10PF(R)

ZCLK0

C518 10PF(R)

ZCLK1

C524

PCICLK961

C531 10PF(R)

PCICLK1394

C538 10PF(R)

PCICLKPCM

C543 10PF(R)

PCICLKLAN

C547 10PF(R)

PCICLKIO

C551

PCICLKH8

C548 10PF(R)

UCLK48M

CLKVCC

C508

C579

0.1UF

0.1UF

+5VS +5VS

By-Pass Capacitors

Place near to the Clock Buffer

C603 10PF(R)

FB_IN

+2.5V

BUFFERVCC CLKVCC

C712

C710

0.1UF

0.1UF

2.5V

2.5V

10PF(R)

10PF(R)

10PF(R)

10PF(R)

49.9 1%

49.9 1%

49.9 1%

49.9 1%

BUFFERVCC

C617

0.1UF

+2.5V

C578

0.1UF

C622

0.1UF

CLKVCC

2.5V

C708

0.1UF

B - 6 Clock Generator (71-M2200-D06)

Page 7

650-1 (Host/AGP) - 1 of 4

Schematic Diagrams

HDSTBP-[0..3][2]

HDSTBN-[0..3][2]

DBI-[0..3][2]

HD-[0..63][1]

HASTB-[0..1][2]

HA-[3..31][1]

HREQ-[0..4][1]

RS-[0..2][1]

HCLK-650[3]

HCLK-650#[3]

HLOCK-[2]

DEFER-[2]

HTRDY-[2]

CPURST-[2]

CPUPWRGD[2]

BPRI-[2]

BREQ0-[2]

ADS-[2]

HITM-[2]

HIT-[2]

DRDY-[2]

DBSY-[2]

BNR-[2]

VCC_CORE

VCC_CORE VCC_CORE

C35

R17

120_1%

0.01UF

C34

R16

150 1%

0.01UF

place this

capacitorunder 650 solder

side

HDSTBP-[0..3]

HDSTBN-[0..3]

DBI-[0..3]

HD-[0..63]

HASTB-[0..1]

HA-[3..31]

HREQ-[0..4]

RS-[0..2]

HCLK-650

HCLK-650#

HLOCKDEFERHTRDYCPURST-

CPUPWRGD

BPRI-

BREQ0-

RS-2

RS-1

RS-0

ADS-

HITM-

HITDRDYDBSY-

BNR-

HREQ-4

HREQ-3

HREQ-2

HREQ-1

HREQ-0

HASTB-1

HASTB-0

HA-31

HA-30

HA-29 AGPCLK

HA-28

HA-27 AGPRCOMP

HA-26

HA-25 A1XAVDD

HA-24 A1XAVSS

HA-23

HA-22 A4XAVDD

HA-21 A4XAVSS

HA-20

HA-19 AVREFGC

HA-18

HA-17

HA-16

HA-15 HDSTBN-3

HA-14 HDSTBN-2

HA-13 HDSTBN-1

HA-12 HDSTBN-0

HA-11

HA-10 HDSTBP-3

HA-9 HDSTBP-2

HA-8 HDSTBP-1

HA-7 HDSTBP-0

HA-6

HA-5

HA-4

HA-3

R28

20 1%

R29

113 1%

HPCVERF = 2/3 VCCP

HVREF

C36

0.1UF

HNCOMP

Rds-on(n) = 10 ohm

HNCVERF = 1/3 VCCP

HPCOMP

Rds-on(p) = 56 ohm

AJ26

AH26

U24

U26

V26

C20

D19

U25

U29

V28

U28

W26

V24

V27

W28

W29

W24

W25

Y27

AD24

AA24

AF26

AE25

AH28

AD26

AG29

AE26

AF28

AC24

AG28

AE29

AD28

AC25

AD27

AE28

AF27

AB24

AB26

AC28

AC26

AC29

AA26

AB28

AB27

AA25

AA29

AA28

Y26

Y24

Y28

R15

150 1%

R14

120_1%

T27

T24

T26

T28

CPUCLK

CPUCLK#

HLOCK#

DEFER#

HTRDY#

CPURST#

CPUPWRGD

BPRI#

BREQ0#

RS#2

RS#1

RS#0

ADS#

HITM#

HIT#

DRDY#

DBSY#

BNR#

HREQ#4

HREQ#3

HREQ#2

HREQ#1

HREQ#0

HASTB#1

HASTB#0

HA#31

HA#30

HA#29

HA#28

HA#27

HA#26

HA#25

HA#24

HA#23

HA#22

HA#21

HA#20

HA#19

HA#18

HA#17

HA#16

HA#15

HA#14

HA#13

HA#12

HA#11

HA#10

HA#9

HA#8

HA#7

HA#6

HA#5

HA#4

HA#3

C33

0.01UF

C32

0.01UF

HNCVREF

R251 22

AHSYNC

AVSYNC

C1XAVSS

C1XAVDD

AH25

AJ25

C1XAVSS

C4XAVSS

AH27

C4XAVSS

C1XAVDD

C4XAVDD

AJ27

C4XAVDD

22

R54

HNCVREF

HPCOMP

HNCOMP

HVREF

U21

T21

P21

N21

J17

B20

B19

A19A7F9B7M6M5M4L3L6L4K6L2K3J3K4J2J6J4J1H6F4F1G6E3F5E2E4E1D3D4C2F7C3E6B2D5D6A3D7C5A5C6D8

HVREF0

HVREF1

HVREF2

HVREF3

HVREF4

HPCOMP

HNCOMP

HOST

HD#63

HD#62

HD#61

HD#60

HD#59

HD#58

HD#57

HD#56

HD#55

HD#54

HD#53

HD#52

HD#51

HD#50

HD#49

HD#48

HD-55

HD#47

A23

D21

F22

D24

D23

C24

B24

E25

E23

HD-54

HD-53

HD-52

HD-51

HD-50

HD-49

HD-48

HD-47

BK1608HS121

9.06mA

C181

0.1UF

B21

F19

A21

E19

D22

D20

B22

C22

B23

HD-63

HD-62

HD-61

HD-60

HD-59

HD-58

HD-57

HD-56

C1XAVDD C4XAVDD

C1XAVSS C4XAVSS

VAHSYNC [10]

VAVSYNC [10]

T23T136T10

VBD7

VBD6

VBD5

VBD4

VBD3

VBD2

VBD1

VBD0

VAD6

VAD5

VAD4

VAD7

VAD8

VAD9

VAD10

VAD11

VADE

TZ0625

TZ0626

TZ0627

ST0

ST1

ST2

VBD7/AAD0

VBD6/AAD1

VBD5/AAD2

VBD4/AAD3

VBD3/AAD4

VBD2/AAD5

VAD6/AAD8

VAD5/AAD9

CBD1/AAD6

CBD0/AAD7

VAD4/AAD10

VAD7/AAD11

VAD8/AAD12

VAD9/AAD13

VADE/AAD16

VAD10/AAD14

HNCOMPVREF

VAD11/AAD15

650-1

HD#46

HD#45

HD#44

HD#43

HD#42

HD#41

HD#40

HD#39

HD#38

HD#37

HD#36

HD#35

HD#34

HD#33

HD#32

HD#31

HD#30

HD#29

HD#28

HD#27

HD#26

G24

HD-33

H24

HD-32

HD#25

G29

J26

G26

J25

H26

G28

H28

HD-31

HD-30

HD-29

HD-28

HD-27

HD-26

HD-25

C183

0.1UF

HD-46

D25

HD-45

A25

C26

B26

B27

HD-44

HD-43

HD-42

L36

1 2

C182

0.01UF

HD-41

D26

B28

E26

F28

G25

F27

F26

HD-40

HD-39

HD-38

HD-37

HD-36

HD-35

HD-34

+3VS

C203

10UF/16V

N12

R38 22

BHSYNC

R224 22

BVSYNC VBDE

AVSYNC

VBD11

VBD10

VBD8

VBD9

VAD1

VAD0

VAD2

VAD3

VBDE

VBCTL0

VBCTL1

VAD1/AAD23

VAD0/AAD24

VAD2/AAD25

VAD3/AAD26

BHSYNC

VBDE/AAD27

VBCTL0AAD28

VBCTL1/AAD29

VBHSYNC/AAD30

BVSYNC

AHSYNC

VBD8/AAD21

VBD9/AAD22

VBD11/AAD19

VBD10/AAD20

VAVSYNC/AAD17

VAHSYNC/AAD18

AGP

HD#24

HD#23

HD#22

HD#21

HD#20

HD#19

HD#18

HD#17

HD#16

HD#15

HD#14

HD#13

HD#12

J24

K28

J29

K27

J28

M24

HD-24

HD-23

HD-22

HD-21

HD-20

BK1608HS121

10mA 10mA

1 2

C184

0.01UF

HD#11

L26

K26

L25

L28

M26

P26

L29

N24

N26

HD-19

HD-18

HD-17

HD-16

HD-15

HD-14

HD-13

HD-12

HD-11

HD-10

+3VS +3VS

L37

C204

10UF/16V

N13

TZ0618

TZ0619

TZ0620

TZ0621

SBA7

SBA6

SBA5

SBA4

VBVSYNCAAD31

HD#10

HD#9

HD#8

HD#7

HD#6

HD#5

M27

N28

P27

N29

R24

HD-9

HD-8

HD-7

HD-6

HD-5

A1XAVDD

A1XAVSS

VBHSYNC [10]

VBVSYNC [10]

T103T96T94T99 T117

T100T109

BCLK

TZ0622

TZ0623

TZ0624

C7

SBA3

SBA2

SBA1

VBCLK/SBA0

VBCAD/AREQ#

VBHCLK/RBF#

VGPIO2/WBF#

VGPIO3/PIPE#

VAGCLK/AD_STB0

VAGCLKN/AD_STB#0

VBGCLK/AD_STB1

VBGCLKN/AD_STB#1

HD#4

HD#3

HD#2

HD#1

HD#0

R28

M28

P28

R26

R29

HD-4

HD-3

HD-2

HD-1

HD-0

C30

0.1UF

AC/BE#3

AC/BE#2

AC/BE#1

AC/BE#0

AGNT#

AFRAME#

AIRDY#

ATRDY#

ADEVSEL#

ASERR#

ASTOP#

APAR

SB_STB

SB_STB#

AGPCLK

AGPRCOMP

A1XAVDD

A1XAVSS

A4XAVDD

A4XAVSS

AGPVREF

AGPVSSREF

HDSTBN#3

HDSTBN#2

HDSTBN#1

HDSTBN#0

HDSTBP#3

HDSTBP#2

HDSTBP#1

HDSTBP#0

DBI#3

DBI#2

DBI#1

E21

A27

H27

DBI-3

DBI-2

DBI-1

BK1608HS121

1 2

C31

0.01UF

BCLK

U6A

TZ0601

F6

F3

TZ0602

H4

TZ0603

K5

TZ0604

C9

A6

TZ0605

G2

TZ0606

G1

TZ0607

G3

TZ0608

G4

TZ0609

H5

TZ0610

H1

TZ0611

H3

TZ0612

Z0602 VBHCLK

E8

Z0603

F8

Z0604

D9

D10

TZ0613

NC

B3

TZ0614

NC

C4

TZ0615

NC

B5

TZ0616

A4

TZ0617

AGCLK

K1

AGCLKN

L1

BGCLK

C1

BGCLKN

D1

B10

M1

B9

A9

B8

A8

M3

M2

F20

F23

K24

P24

F21

F24

L24

N25

DBI#0

SIS650

R25

DBI-0

C319

10UF/16V

N4

20MIL20MIL20MIL

VADE

R23 22

NEAR SIS650

C41

10PF(R)

VAD[0..11]

VBD[0..11]

VBCTL[0..1]

T123

T34

T137

T141

R24 0

T19

T122

T119

T127

T126

T138

T36

T134

R222 0

R223 0(R)

R221 0(R)

T20

T108

T12

PIN D1 CH7017 CONNECT TO VBGCLKN

SIS301LV NC BUT SIS301LV PULL GND

T18

T101

22

R64

R69 22(R)

22

R46

R47 22(R)

AGPRCOMP

R76

VADE [10]

VBDE [10]

VBCLK [10]

VBCADZ0601

VBCAD

C86 0603(R)

C352 0603(R)

C356 0603(R)

AGPCLK [3]

8.2K

A4XAVDD

A4XAVSS

VAD[0..11] [10]

VBD[0..11] [10]

VBCTL[0..1] [10]

VBCAD [10]

C394 0603(R)

+3VS

R261

60_1%

BK1608HS121

10mA

C29

0.1UF

VBHCLK [10]

VBCAD [10]

VAGCLK [10]

T44

T114

L13

1 2L14

C28

0.01UF

20MIL

VBGCLK [10]

+3VS

C320

10UF/16V

N3

Schematic Diagrams

Sheet 6 of 31

650-1 (Host/AGP)

1 of 4

650-1 (Host/AGP) - 1 of 4 (71-M2200-D06) B - 7

Page 8

Schematic Diagrams

650-2 (Memory for DDR) - 2 of 4

Sheet 7 of 31

650-2

(Memory for DDR)

2 of 4

Schematic Diagrams

Rs place close to DIMM1

MD4

RP45

MD5

DQM0

MD6

8P4RX10

MD7

MD12

MD13

DQM1

MD14

MD15

MD10

MD11

MD20

MD21

DQM2

MD22

MD23

MD28

MD29

MD19

8P4RX10

MD26

DQM3

MD30

MD31

MD36

MD37

DQM4

MD38

MD39

MD44

MD45

DQM5

MD46

MD47

MD52

MD53

DQM6

MD54

MD55

MD60

MD61

DQM7

MD62

MD63

MD1

MD0

DQS0

8P4RX10

MD3

MD8

8P4RX10

MD18

DQS2

RP10

MD17

MD16

8P4RX10

MD25

DQS3

MD24

MD27

MD34

DQS4

RP18

MD33

MD32

8P4RX10

MD41

DQS5

RP17

MD40

MD35

8P4RX10

MD49

MD48

RP16

MD43

MD42

8P4RX10

MD56

MD51

RP15

MD50

DQS6

8P4RX10

MD59

MD58

RP14

DQS7

MD57

8P4RX10

RP46

RP40

8P4RX10

RP47

8P4RX10

RP36

8P4RX10

RP37

RP41

8P4RX10

RP42

8P4RX10

RP48

8P4RX10

RP44

8P4RX10

RP43

8P4RX10

RP12

8P4RX10

RP11

RP13

8P4RX10

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

45

36

27

18

45

36

27

18

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

18

27

36

45

/RMD[0..63]

/RDQM[0..7]

/RDQS[0..7]

/RMA[0..14]

/RCS-[0..5]

CKE[0..5]

/RMD4

/RMD5 MD1

/RDQM0

/RMD7

/RMD12

/RMD13

/RDQM1

/RMD14

/RMD15

/RMD10

/RMD11

/RMD20

/RMD21

/RDQM2

/RMD22

/RMD23

/RMD28

/RMD29

/RMD19

/RMD26

/RDQM3

/RMD30

/RMD31

/RMD36

/RMD37

/RDQM4

/RMD38

/RMD39

/RMD44

/RMD45

/RDQM5

/RMD46

/RMD47

/RMD52

/RMD53

/RDQM6

/RMD54

/RMD55

/RMD60

/RMD61

/RDQM7

/RMD62

/RMD63

/RMD1

/RMD0

/RDQS0

/RMD2MD2

/RMD3

/RMD8

/RMD9MD9

/RDQS1DQS1

/RMD18

/RDQS2

/RMD17

/RMD16

/RMD25

/RDQS3

/RMD24

/RMD27

/RMD34

/RDQS4

/RMD33

/RMD32

/RMD41

/RDQS5

/RMD40

/RMD35

/RMD49

/RMD48

/RMD43

/RMD42

/RMD56

/RMD51

/RMD50

/RDQS6

/RMD59

/RMD58

/RDQS7 DQM7

/RMD57

MD0

MD2

MD3/RMD6

MD4

MD5

MD6

MD7

DQM0

DQS0 MA0

MD8 MA1

MD9 MA2

MD10 MA3

MD11 MA4

MD12 MA5

MD13 MA6

MD14 MA7

MD15 MA8

DQM1 MA9

DQS1 MA10

MD16 MA11

MD17 MA12

MD18 MA13

MD19 MA14

MD20

MD21 SRASMD22 SCASMD23 SWEDQM2

DQS2

MD24

MD25 CS-0

MD26

MD27 CS-2

MD28

MD29 CS-4 /RCS-4

MD30 CS-5 /RCS-5

MD31

DQM3

DQS3

MD32 Z0701 CKE0

MD33 Z0702 CKE1

MD34 CKE2

MD35 CKE3

MD36 CKE4

MD37 CKE5

MD38 Z0703

MD39

DQM4

DQS4

MD40 SDCLK

MD41

MD42 Z0704

MD43

MD44

MD45

MD46

MD47

DQM5 SDAVDD

DQS5

MD48 SDAVSS

MD49

MD50

MD51 DDRAVDD

MD52

MD53 DDRAVSS

MD54

MD55

DQM6

DQS6 DDRVREFA

MD56 DDRVREFB

MD57

MD58 Z0705

MD59

MD60

MD61

MD62

MD63

DQS7

AG22

AH21

AD23

AE23

AF22

AF21

AD22

AH22

AD21

AG20

AE19

AF19

AE21

AD20

AD19

AH19

AF20

AH20

AF18

AG18

AH17

AD16

AD18

AD17

AF17

AE17

AH18

AD14

AG14

AE13

AF14

AD13

AF13

AH13

AH14

AD10

AH10

AG10

AF10

AJ23

AJ21

AJ17

AJ13

AJ15

AE9

AD8

AH9

AF9

AD9

AJ9

AH5

AG4

AE5

AH3

AG6

AF6

AF5

AF4

AH4

AJ3

AE4

AD6

AE2

AC5

AG2

AG1

AF3

AC6

AD4

AF2

AB6

AD3

AA6

AB3

AC4

AE1

AD2

AC1

AB4

AC2

/RMD[0..63] [8,9]

/RDQM[0..7] [8,9]

/RDQS[0..7] [8,9]

/RMA[0..14] [8,9]

/RCS-[0..5] [8,9]

CKE[0..5] [8]

U6B

MD0

MD1

MD2

MD3

MD4

MD5

MD6

MD7

DQM0

DQS0/CSB#0

MD8

MD9

MD10

MD11

MD12

MD13

MD14

MD15

DQM1

DQS1/CSB#1

MD16

MD17

MD18

MD19

MD20

MD21

MD22

MD23

DQM2

DQS2/CSB#2

MD24

MD25

MD26

MD27

MD28

MD29

MD30

MD31

DQM3

DQS3/CSB#3

MD32

MD33

MD34

MD35

MD36

MD37

MD38

MD39

DQM4

DQS4/CSB#4

MD40

MD41

MD42

MD43

MD44

MD45

MD46

MD47

DQM5

DQS5/CSB#5

MD48

MD49

MD50

MD51

MD52

MD53

MD54

MD55

DQM6

DQS6/CSB#6

MD56

MD57

MD58

MD59

MD60

MD61

MD62

MD63

DQM7

DQS7/CSB#7

SIS650

650-2

SRAS#

SCAS#

S3AUXSW#

SDCLK

FWDSDCLKO

SDRCLKI

SDAVDD

SDAVSS

DDRAVDD

DDRAVSS

DDRVREFA

DDRVREFB

DRAM_SEL

MA10

MA11

MA12

MA13

MA14

SWE#

CS#0

CS#1

CS#2

CS#3

CS#4

CS#5

CKE0

CKE1

CKE2

CKE3

CKE4

CKE5

+2.5V

C179

Rs place close to DIMM1

3

4

RP39

8 1

7 2

653

8 1

7 2

653

8P4RX0

8 1

7 2

653

10K

+3V

8P4RX0

81

72

6

5

4

4

8P4RX0

4

/RSRAS- [8,9]

/RSCAS- [8,9]

/RSWE- [8,9]

SRAS-

SCAS-

SWE-

S3AUXSW- [27]

+3V

FWDSDCLKO [3]

TZ0702

MA13

MA8

MA6

/RMA4

/RMA2

/RMA0

/RMA12

/RMA1

/RMA9

/RMA7

/RMA14

/RMA10

/RMA11

/RMA3

/RMA5

C272 10PF(R)R192

C254 10PF(R)

C250 10PF(R)

T61T64

SDAVDD

SDAVSS

DDRAVDD

DDRVREFA

DDRVREFB

5.69mA

C132

0.1UF

8.76mA

C139

0.1UF

BK1608HS121

1 2

C131

0.01UF

BK1608HS121

1 2

C138

0.01UF

RP38

TZ0701

10PF(R)

/RMA13

/RMA8

/RMA6

MA4

MA2

MA0

MA12

MA1

MA9

MA7

MA14

MA10

MA11

MA3

MA5

0

0

S3AUXSW-

R99

SDCLK [3]

FWDSDCLKO

R282 4.7K

RP20 8P4RX0

RP19

/RSRAS/RSCAS/RSWE-

/RCS-0

/RCS-1CS-1

/RCS-2

/RCS-3CS-3

AH11

MA0

AF12

MA1

AH12

MA2

AG12

MA3

AD12

MA4

AH15

MA5

AF15

MA6

AH16

MA7

AE15

MA8

AD15

MA9

AF11

AG8

AJ11

AG16

AF16

AH8

AJ7

AH7

AE7

AF7

AH6

AJ5

AF8

AD7

AB2

AA4

AB1

Y6

AA5

Y5

Y4

AA3

AD11

AE11

Y1

Y2

AA1

AA2

AJ19

AH2

W3

R191

R173 0

R190 0

R189 0

R195 0

R194 0

R175 0

R174 0

R104 0

R286 0

R103 0

R118 22

C178

DDRAVSS

0.01UF

C180

0.01UF

C176

0.01UF

C177

0.01UF

L31

20MIL

L33

R120

150 1%

R119

150 1%

+2.5V

R117

150 1%

R116

150 1%

+3VS

C424

10UF/16V

N10

+3VS

C449

10UF/16V

N11

20MIL

B - 8 650-2 (Memory for DDR) - 2 of 4 (71-M2200-D06)

Page 9

650-3 (HyperZip/VGA/Misc) - 3 of 4

U6C

SIS650

ZAD[0..15][11]

ZSTB[0..1][11]

ZSTB-[0..1][11]

+1.8VS

L23

BK1608HS121

1 2

C374

10UF/16V

N5

+3VS

BK1608HS121

1 2

C450

10UF/16V

N6

+3VS

BK1608HS121

1 2

C425

10UF/16V

N7

ROUT

GOUT

BOUT

R25

R2675R27

75

NEAR SIS650

ZCLK0[3]

ZUREQ[11]

ZDREQ[11]

ZAD[0..15]

ZSTB[0..1]

ZSTB-[0..1]

+1.8VS

C92

0.1UF

20MIL

L27

10MIL

L26

10MIL

75

R72

150 1%

R68

150 1%

35.4mA

C89

0.01UF

6.49mA

C115

0.1UF

7.92mA

C128

0.1UF

C23

22PF

0.1UF

0.1UF

C103

C403

R258

R263

ZCLK0

ZUREQ

ZDREQ

ZVREF

20 mil

20 mil

20 mil

C22

22PF

56

56

C111

V3

ZCLK

U6

ZUREQ

U1

20 mil

20 mil

ZDREQ

T3

ZSTB0

T1

ZSTB#0

P1

ZSTB1

P3

ZSTB#1

T4

ZAD0

R3

ZAD1

T5

ZAD2

T6

ZAD3

R2

ZAD4

R6

ZAD5

R1

ZAD6

R4

ZAD7

P4

ZAD8

N3

ZAD9

P5

ZAD10

P6

ZAD11

N1

ZAD12

N6

ZAD13

N2

ZAD14

N4

ZAD15

U3

ZVREF

V5

VDDZCMP

U4

ZCMP_N

U2

ZCMP_P

V6

VSSZCMP

W1

Z1XAVDD

W2

Z1XAVSS

V2

Z4XAVDD

V1

Z4XAVSS

ZSTB0

ZSTB-0

ZSTB1

ZSTB-1

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

Z1XAVDD

C114

0.01UF

Z1XAVSS

Z4XAVDD

0.01UF

Z4XAVSS

L3 BK2125HS121

L2 BK2125HS121

L5 BK2125HS121

C24

22PF

VGA

HyperZip

650-3

FRED

FGRN

FBLU

TZ0801

T92

C295

C5

C294

22PF

22PF

22PF

VOSCI

ROUT

GOUT

BOUT

HSYNC

VSYNC

VGPIO0

VGPIO1

CSYNC

RSYNC

LSYNC

INT#A

PCIRST#

PWROK

AUXOK

VCOMP

VVBWN

DACAVDD1

DACAVDD2

DACAVSS1

DACAVSS2

VRSET

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

DLLEN#

TESTMODE0

TESTMODE1

TESTMODE2

TRAP0

TRAP1

ENTEST

CN4

CRT CON

1

2

3

4

5

6

7

8

REFCLK0

C15

A12

ROUT

GOUT

B13

BOUT

A13

R4

Z0801 HSYNC

F13

R5

Z0802 VSYNC

E13

D13

D12

CSYNC

E12

RSYNC

A11

LSYNC

F12

INTA#

B11

Y3

W4

W6

C1

VCOMP

E14

C2

VVBWN

F14

DACAVDD

B12

C13

DACAVSS

C12

C14

VRSET

D14

DCLKAVDD

B15

A15

ECLKAVDD

B14

ECLKAVSS

A14

DLLEN-

E11

TMODE0

C11

TMODE1

F11

TMODE2

A10

TRAP0

E10

TRAP1

D11

ENTEST

F10

D1 RB751V

Z0803

9

10

TZ0802

11

DDCDA

12

HS

13

VS

14

DDCDC

15

C305

220PF

20 mil

C13

0.1UF

20 mil

C9

0.01UF

20 mil

C11

0.01UF

C307

220PF

REFCLK0 [3]

33

33

DDC1CLK

DDC1DATA

T135

T5

T129

INTA# [10,11]

PCIRST#[10,11,15,16,17,18,19,20,21]

PWRGD[12,13]

AUXOK [12,20,26,27]

0.1UF

0.1UF

L11

84.8mA

1 2

BK1608HS121

C14

N1

R1

1 2

BK1608HS121

T125

T24

T118

T13

T132

T140

T11

AC

C308

T2

1000PF

1UF

1 2

BK1608HS121

C10

0.1UF

L10

C12

0.1UF

20MIL

130 1%

+3VS

L9

7.57mA

+3VS

18.07mA

N2

10MIL

+5VS

L4 BK2125HS121

L8 BK2125HS121

L6 BK2125HS121

L7 BK2125HS121

C306

1000PF

NOTE: This page is for universal PCB design( suitable for both 645 or 650)

NB Hardware Trap Table

0

enable PLL

SDR

normal

TV selection, NTSC/PAL(0/1)

enable VB

enable VGA interface

enable panel link

4.7K

R3

RSYNC PWRGD

D3

C

BAV99

ROUT

AC

A

D15

BAV99

AC

AS SIS AP NOTE

A650-0-003

R8 100

R10 100

Z0803

DDCDA

C

A

DDC1DATA

HSYNC

VSYNC

DDC1CLK

+1.8VS

C318

10UF/16V

C317

10UF/16V

DLLEN#

DRAM_SEL

TRAP0

TRAP1

CSYNC

RSYNC

LSYNC

C315

10UF/16V

+5VS +5VS

Z0803

R208

2.2K

Z0804

Z0805

R207

2.2K

C

A

+1.8VS +1.8VS+1.8VS

C

A

D5

BAV99

AC

BAV99

SOT-23

+3VS

D4

BAV99

AC

3

12

R11

4.7K(R)

1

disable PLL

DDR

NB debug mode

ENTEST

AUXOK

BOUT

+5VS +5VS

C

A

Z0803

R9

4.7K(R)

0

1(DDR)

0 yes

0

0

1

0

R22 4.7K

C153

C154 0.1UF

D2

C

BAV99

AC

A

D14

BAV99

HSDDCDC VS

AC

Z0803

embedded pull-low

(30~50K Ohm)Default

yes

yes

0.1UF

GOUT

D13

C

BAV99

AC

A

Schematic Diagrams

Schematic Diagrams

Sheet 8 of 31

650-3

(HyperZip/VGA/

Misc)

3 of 4

650-3 (HyperZip/VGA/Misc) - 3 of 4 (71-M2200-D06) B - 9

Page 10

Schematic Diagrams

Sheet 9 of 31

650-4 (Power)

4 of 4

Schematic Diagrams

650-4 (Power) - 4 of 4

VCC_CORE +1.8VS +3VS +3V

VCC_CORE

+2.5V

+3VS

+1.8VS

AE10

AE12

AE14

AE16

AE18

AE20

AE22

AA10

AA13

AA14

AA15

AA16

AA17

AB13

AB17

H21

H22

J16

J20

J21

J22

K16

K17

K18

K19

K20

K21

L20

M20

N20

P20

R20

R21

T20

U20

V20

W20

Y20

Y21

AA20

AA21

AA22

AB21

A16

VTT

A17

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

VTT

A18

VTT

B16

VTT

B17

VTT

B18

VTT

C16

VTT

C17

VTT

C18

VTT

D15

VTT

D16

VTT

D17

VTT

D18

VTT

E15

VTT

E16

VTT

E17

VTT

E18

VTT

F15

VTT

F16

VTT

F17

VTT

F18

VTT

AB5

VDDM

AD5

VDDM

AE6

VDDM

AE8

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

V10

VDDM

V11

VDDM

W18

VDDM

Y9

VDDM

Y10

VDDM

Y12

VDDM

Y14

VDDM

Y16

VDDM

Y18

VDDM

Y19

VDDM

AA8

VDDM

AA9

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

VDDM

AB8

VDDM

AB9

VDDM

VDDM

VDDM

E5

VDDQ

E7

VDDQ

E9

VDDQ

G5

VDDQ

J5

VDDQ

L5

VDDQ

H8

VDDQ

H9

VDDQ

J8

VDDQ

J9

VDDQ

J10

VDDQ

J13

VDDQ

K9

VDDQ

K11

VDDQ

K13

VDDQ

L10

VDDQ

N9

VDDQ

N10

VDDQ

N5

VDDZ

R5

VDDZ

U5

VDDZ

W5

VDDZ

P9

VDDZ

P10

VDDZ

R9

VDDZ

R10

VDDZ

T9

VDDZ

T10

VDDZ

T11

VDDZ

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

PVDDP

VSS

VSS

VSS

VSS

VSS

VSS

L17

L19

N19

R19

U19

W19

VSS

M12

M13

M14

M15

M16

M17

M18

N12

VTT

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

N13

N14

N15

N16

N17

N18

P12

P13

VTT

VTT

VTT

VSS

VSS

VSS

P14

P15

P16

P17

AB22

VTT

VTT

VTT

VTT

VTT

VTT

650-4

Power

VSS

VSS

VSS

VSS

VSS

VSS

P18

R12

R13

R14

R15

+3VS

C335

10UF/16V

C373

1UF

C398

0.1UF

C415

0.1UF

C197

10UF/16V(0805)

C200

10UF/16V(0805)

C201

10UF/16V(0805)

C202

10UF/16V

C717

C444

0.1UF

C436

0.1UF

C452

0.1UF

C459

0.1UF

C351

10UF/16V

C366

1UF

C369

0.1UF

C65

0.1UF

+1.8VS

C426

0.1UF

C410

10UF/16V

C390

0.1UF

C405

0.1UF

+1.8V

L12

L14

L15

L16

L18

M11

M19

N11

P19

R11

T19

U11

V19

W11

W13

W15

W17

P11

J14

J15

K15

K10

K12

K14

M10

W10

Y11

Y13

Y15

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

IVDD

PVDD

PVDD

PVDD

PVDD

OVDD

OVDD

OVDD

PVDDZ

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

R16

R17

R18

T12

T13

T14

T15

T16

T17

T18

U12

U13

U14

VSS

U15

U16

U17

U18

V12

V13

V14

V15

V16

PVDDM

PVDDM

PVDDM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

V17

V18

VSS

B25

C28

C29

D27

D28

E28

E29

AF23

Y17

PVDDM

PVDDM

VSS

VSS

AF24

U6D

U10

AUX1.8

AUX3.3

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF25

AG24

AG26

AH23

+1.8V

U9

+3V

A20

A22

A24

A26

C19

C21

C23

C25

C27

E20

E22

VCC_CORE

E24

F25

H25

K25

M25

P25

T25

V25

Y25

AB25

AD25

E27

G27

J27

L27

N27

R27

U27

W27

AA27

AC27

AE27

D29

F29

H29

K29

M29

P29

T29

V29

Y29

AB29

AD29

AF29

AE24

AG25

B4

B6

C8

C10

D2

F2

H2

K2

P2

T2

V4

AD1

AF1

AC3

AE3

AG3

AG5

AG7

AG9

AG11

AG13

AG15

AG17

AG19

AG21

AG23

AJ4

AJ6

AJ8

AJ10

AJ12

AJ14

AJ16

AJ18

AJ20

AJ22

AJ24

AG27

VSS

VSS

SIS650

AH24

C339

10UF/16V

C338

10UF/16V

C337

10UF/16V

C336

10UF/16V

+3VS

C42

0.1UF

C40

0.1UF

C48

0.1UF

C360

0.1UF

Place these capacitors under 650 solder

side

VCC_CORE

C387

0.1UF

C451

0.1UF

C404

0.1UF

C368

0.1UF

C428

10UF/16V

C411

1UF

C105

0.1UF

+1.8VS

C402

1UF

C43

1UF

C44

1UF

C45

1UF

C50

0.1UF

C39

0.1UF

C63

0.1UF

C371

0.1UF

C408

0.1UF

C433

0.1UF

C396

0.1UF

C391

0.1UF

+3V

C441

10UF/16V

C448

1UF

C454

0.1UF

+2.5V

+2.5V

10UF/6.3V(0805)

C354

0.1UF

C361

1UF

C357

0.1UF

C435

0.1UF

C194

1UF

C195

1UF

C455

0.1UF

C456

0.1UF

C80

0.1UF

+1.8VS

+3V

+3VS

+3VS

10UF/6.3V(0805)

C379 0.1UF

C393 0.1UF

C381 0.1UF

C437

0.1UF

C438

0.1UF

C99

0.1UF

C414

0.1UF

C340

10UF/16V

C78

1UF

C81

0.1UF

C427

0.1UF

C716

C196

1UF

C193

1UF

C458

0.1UF

C457

0.1UF

+1.8VS

B - 10 650-4 (Power) - 4 of 4 (71-M2200-D06)

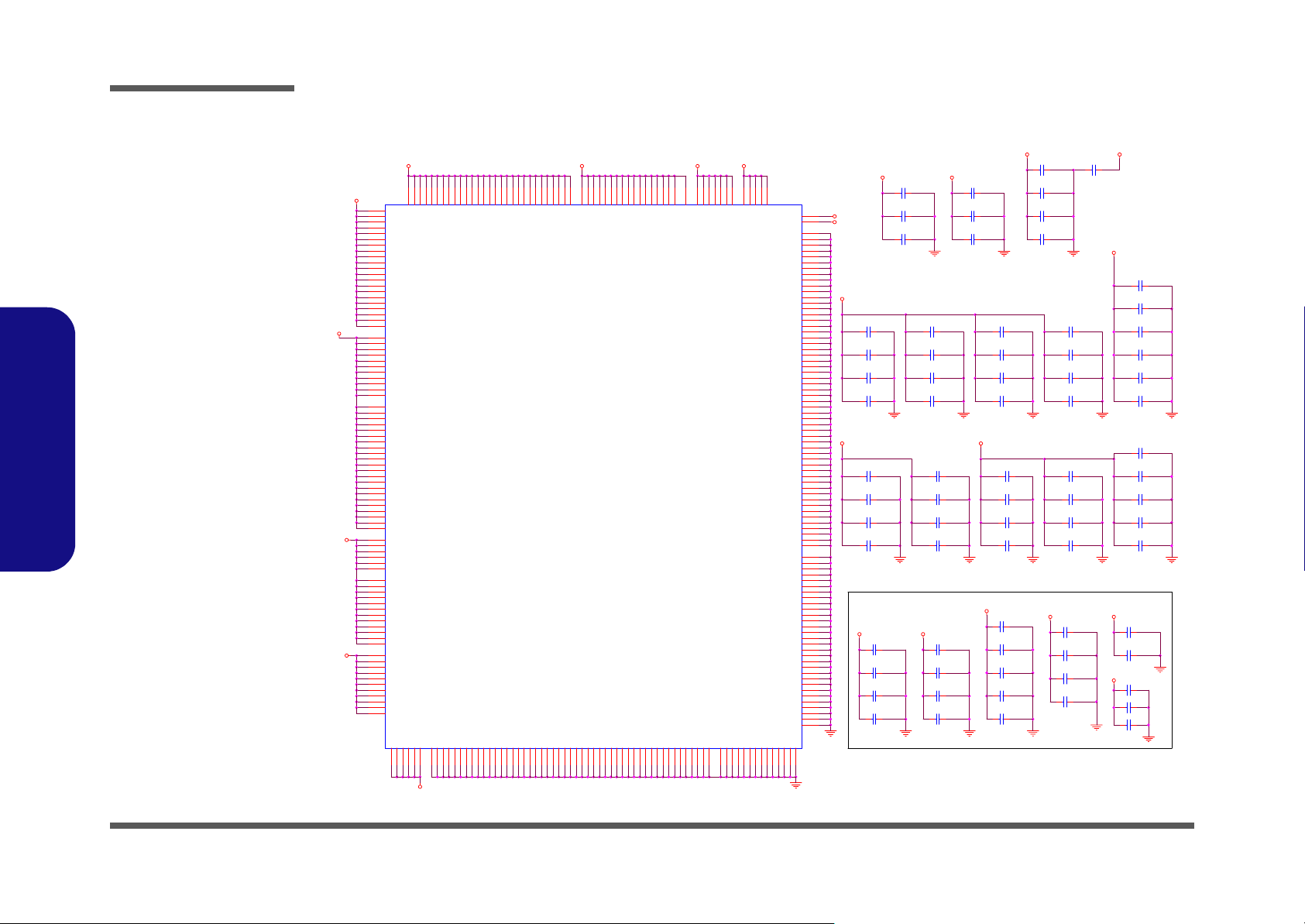

Page 11

DDR SDRAM DIMM 1 & DIMM2

+2.5V

+2.5V

/RSRAS-[5,9]

/RSWE-[5,9]

/RSCAS-[5,9]

+3VS

VDDSPD

91021223334364546575869708182929394113

U19

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

/RMA0

112

/RSRAS/RSWE/RSCAS-

Z1001

Z1002

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10/AP

100

A11

99

A12

117

BA0

116

BA1

12

DM0

26

DM1

48

DM2

62

DM3

134

DM4

148

DM5

170

DM6

184

DM7

78

DM8

11

DQS0

25

DQS1

47

DQS2

61

DQS3

133

DQS4

147

DQS5

169

DQS6

183

DQS7

77

DQS8

118

RAS#

119

WE#

120

CAS#

121

S0#

122

S1#

96

CKE0

95

CKE1

35

CK0

37

CK0#

160

CK1

158

CK1#

89

CK2

91

CK2#

193

SDA

195

SCL

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

1

VREF

2

VREF

197

VDDSPD

199

VDDID

R187

10K

VSS

3415162728383940515263647576878890103

SMBCLK

SMBDAT

/RMA1

/RMA2

/RMA3

/RMA4

/RMA5

/RMA6

/RMA7

/RMA8

/RMA9

/RMA10

/RMA13

/RMA14

/RMA11

/RMA12

/RDQM0

/RDQM1

/RDQM2

/RDQM3

/RDQM4

/RDQM5

/RDQM6

/RDQM7

R164

8.2K

/RDQS0

/RDQS1

/RDQS2

/RDQS3

/RDQS4

/RDQS5

/RDQS6

/RDQS7

/RCS-0

/RCS-1

CKE0

CKE1

DDRCLK0

DDRCLK-0

DDRCLK1

DDRCLK-1

DDRCLK2

DDRCLK-2

SMBDAT

SMBCLK

R188

DDRVREF

0

VDDSPD

C269

0.1UF

SMBCLK[3,12,20]

SMBDAT[3,12,20]

VDD

addr =1010000b

DDR SO-DIMM

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

/RMA[0..14][5,9]

/RDQM[0..7][5,9]

/RCS-[0..5][5,9]

/RDQS[0..7][5,9]

114

131

132

143

144

155

156

157

167

168

179

180

191

192

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

DU/RESET#

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

104

125

126

/RMA[0..14]

/RDQM[0..7]

/RCS-[0..5]

/RDQS[0..7]

137

138

149

VSS

150

159

161

162

173

174

185

186

DDRCLK[0..5][3]

DDRCLK-[0..5][3]

/RMD[0..63][5,9]

CKE[0..5][5]

/RMD0

5

DQ0

/RMD1 /RMA1

7

DQ1

/RMD2

13

DQ2

/RMD3

17

DQ3

/RMD4

6

DQ4

/RMD5

8

DQ5

/RMD6 /RMA6

14

DQ6

/RMD7

18

DQ7

/RMD8

19

DQ8

/RMD9

23

DQ9

/RMD10

29

DQ10

/RMD11

31

DQ11

/RMD12

20

DQ12

/RMD13

24

DQ13

/RMD14

30

DQ14

/RMD15

32

DQ15

/RMD16

41

DQ16

/RMD17

43

DQ17

/RMD18

49

DQ18

/RMD19

53

DQ19

/RMD20

42

DQ20

/RMD21

44

DQ21

/RMD22

50

DQ22

/RMD23

54

DQ23

/RMD24

55

DQ24

/RMD25

59

DQ25

/RMD26

65

DQ26

/RMD27

67

DQ27

/RMD28

56

DQ28

/RMD29

60

DQ29

/RMD30

66

DQ30

/RMD31

68

DQ31

/RMD32

127

DQ32

/RMD33

129

DQ33

/RMD34

135

DQ34

/RMD35

139

DQ35

/RMD36

128

DQ36

/RMD37

130

DQ37

/RMD38

136

DQ38

/RMD39

140

DQ39

/RMD40

141

DQ40

/RMD41

145

DQ41

/RMD42

151

DQ42

/RMD43

153

DQ43

/RMD44

142

DQ44

/RMD45

146

DQ45

/RMD46

152

DQ46

/RMD47

154

DQ47

/RMD48

163

DQ48

/RMD49

165

DQ49

/RMD50

171

DQ50

/RMD51

175

DQ51

/RMD52

164

DQ52

/RMD53

166

DQ53

/RMD54

172

DQ54

/RMD55

176

DQ55

/RMD56

177

DQ56

/RMD57

181

DQ57

/RMD58

187

DQ58

189

/RMD59

DQ59

/RMD60

178

DQ60

/RMD61

182

DQ61

/RMD62

188

DQ62

190

/RMD63

DU/A13

DU/BA2

DQ63

DU

DU

DU

DU

SA0

SA1

SA2

85

123

124

200

86

97

98

194

196

198

VDDSPD

TZ1002

TZ1003

TZ1004

DDRST

Z1003

TZ1005TZ1001

TZ1006

TZ1007

TZ1008

R362

1K

DDRCLK[0..5]

DDRCLK-[0..5]

/RMD[0..63]

CKE[0..5]

127

129

135

139

128

130

136

140

141

145

151

153

142

146

152

154

163

165

171

175

164

166

172

176

177

181

187

189

178

182

188

190

123

124

200

194

196

198

13

17

14

18

19

23

29

31

20

24

30

32

41

43

49

53

42

44

50

54

55

59

65

67

56

60

66

68

85

86

97

98

5

7

6

8

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DU

DU

DU

DU

DU/RESET#

DU/A13

DU/BA2

SA0

SA1

SA2

Schematic Diagrams

U23

114

131

132

143

144

155

156

157

167

168

179

180

191

192

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

addr =1010001b

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

162

173

174

185

186

104

125

126

137

138

149

150

159

161

+2.5V

C270

C271

10U/16V

10U/16V

91021223334364546575869708182929394113

DDR SO-DIMM_R

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

VSS

VSS

VSS

VSS

VSS

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10/AP

100

A11

99

A12

117

BA0

116

BA1

12

DM0

26

DM1

48

DM2

62

DM3

134

DM4

148

DM5

170

DM6

184

DM7

Z1004

78

DM8

11

DQS0

25

DQS1

47

DQS2

61

DQS3

133

DQS4

147

DQS5

169

DQS6

183

DQS7

77

DQS8

118

RAS#

119

WE#

120

CAS#

121

S0#

122

S1#

96

CKE0

95

CKE1

35

CK0

37

CK0#

160

CK1

158

CK1#

89

CK2

91

CK2#

193

SDA

195

SCL

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

1

VREF

2

VREF

197

VDDSPD

Z1005

199

VDDID

R366

VSS

VSS

VSS

VSS

10K

3415162728383940515263647576878890103

CKE3

/RMA0

CKE0

CKE1

/RMA2

CKE2

/RMA3

/RMA4

/RMA5

CKE4

/RMA7

/RMA8

CKE5

/RMA9

/RMA10

/RMA13

T169

/RMA14

T166

/RMA11

/RMA12

/RDQM0

/RDQM1

/RDQM2

/RDQM3

/RDQM4

/RDQM5

/RDQM6

/RDQM7

R193 8.2K

/RDQS0

/RDQS1

/RDQS2

/RDQS3

/RDQS4

/RDQS5

/RDQS6

/RDQS7

DDRVREF GEN. & DECOUPLING

/RSRAS/RSWE/RSCAS-

R434

75 1%