Page 1

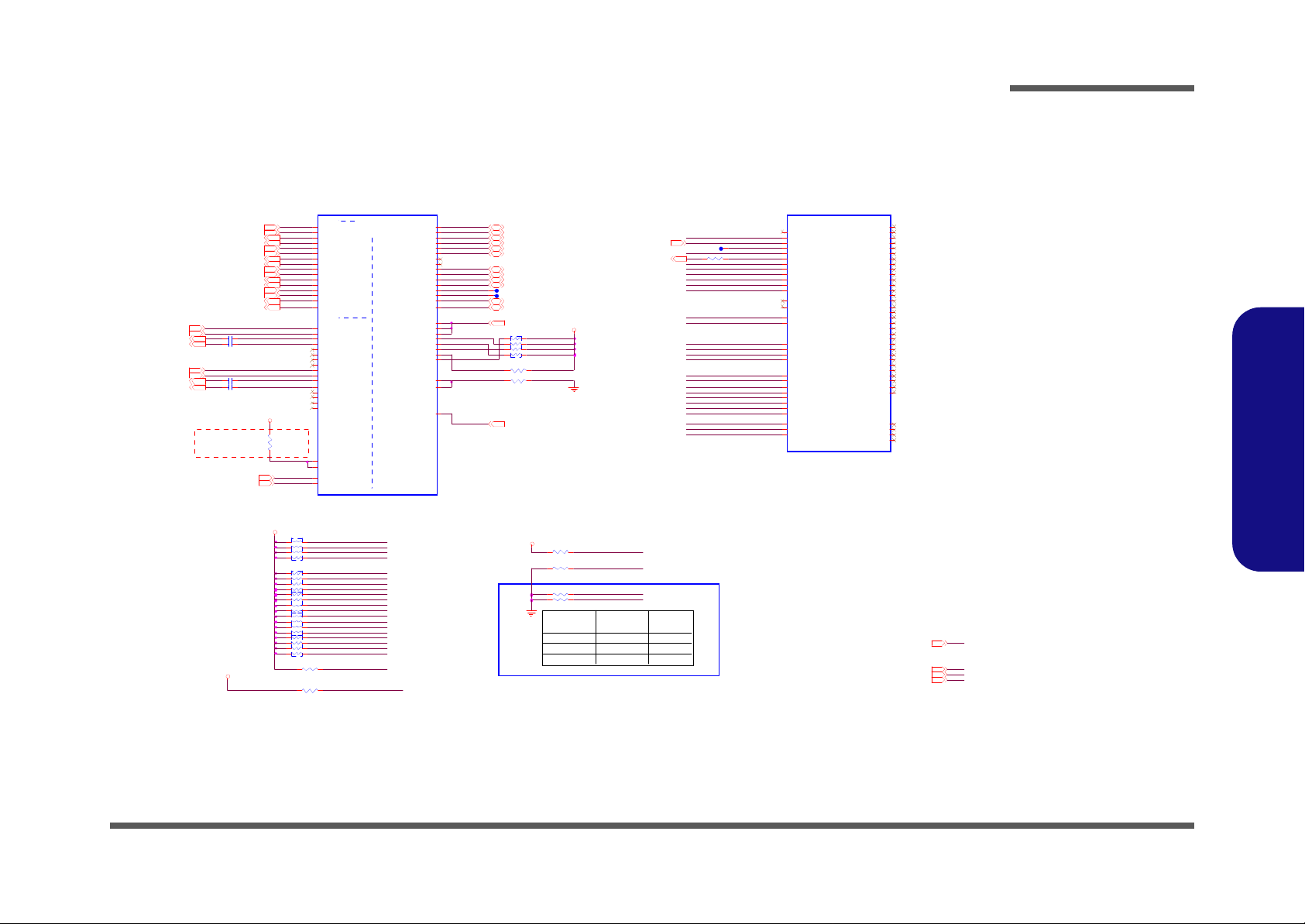

Appendix B: Schematic Diagrams

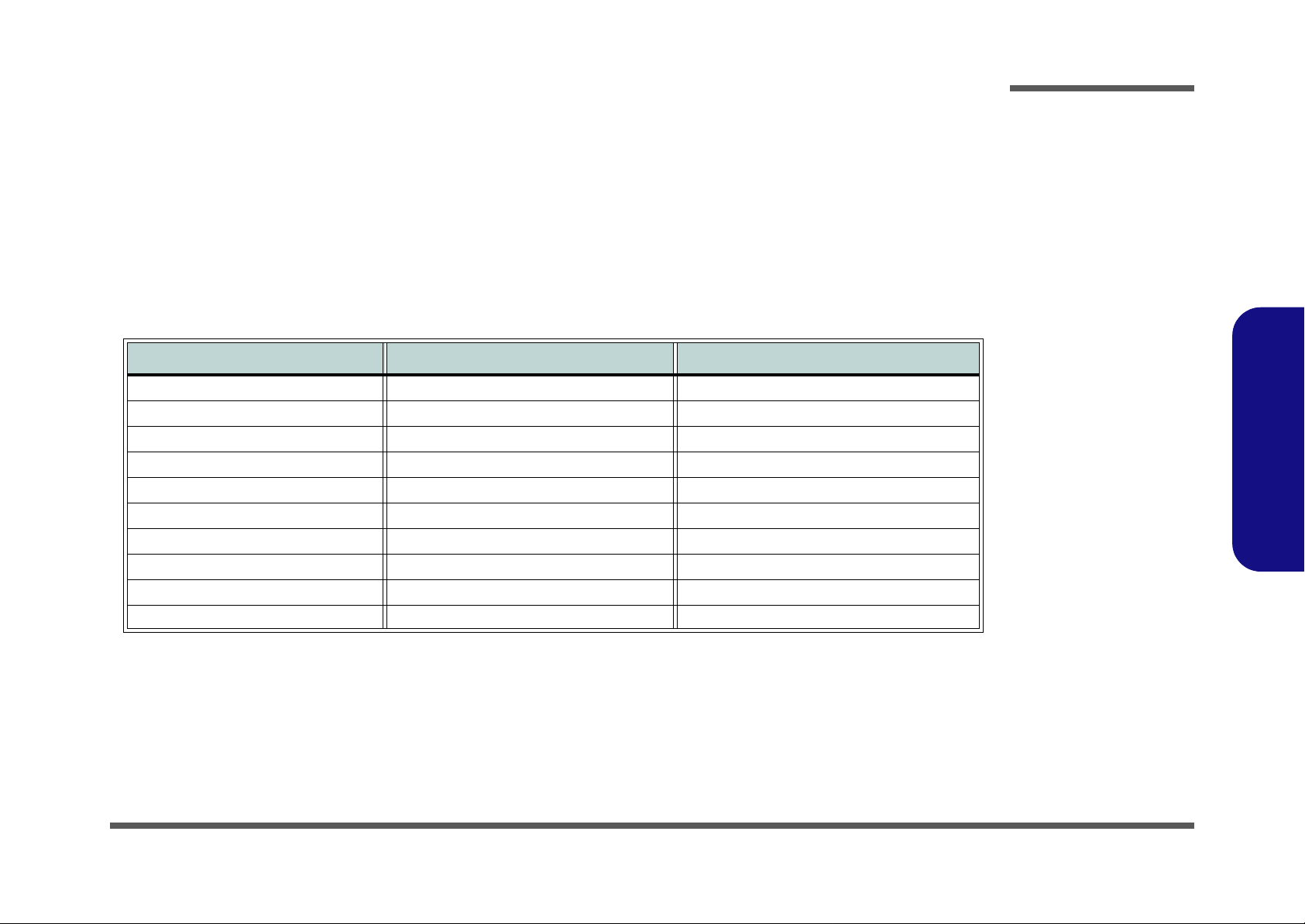

Table B - 1

SCHEMATIC

DIAGRAMS

This appendix has circuit diagrams of the 6-71-W2100-D04 notebook’s PCB’s. The following table indicates where to

find the appropriate schematic diagram.

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 Tigerpoint Part E-F - Page B - 12 PWR SW, 1.8VS, 3VS, 5VS, 1.5VS - Page B - 22

Cedarview CPU Part D - Page B - 3 Panel, HDD, LED - Page B - 13 PWR VCORE - Page B - 23

Cedarview CPU Part A-C-F - Page B - 4 BTB, 3G, WLAN, BT - Page B - 14 PWR VDD3, 3.3V, VDD5V, SYS15V - Page B - 24

Cedarview CPU Part B - Page B - 5 Audio Codec VT1812P - Page B - 15 CRT - Page B - 25

Cedarview CPU Part E - Page B - 6 KBC-ITE IT8502E-J, TP, LID - Page B - 16 Card Reader (w/ LAN) JMB261C - Page B - 26

DDRIII SO-DIMM_0 - Page B - 7 TPM & HDMI - Page B - 17 BTB, USB, CCD, PWR SW - Page B - 27

IDT CLOCK - Page B - 8 USB PORT & USB CHARGER - Page B - 18 Click Board - Page B - 28

Tigerpoint Part A-B - Page B - 9 PWR AC IN, CHARGE - Page B - 19 Power Button Board - Page B - 29

Tigerpoint Part C - Page B - 10 PWR 1.5V, 0.75V - Page B - 20 Power Button for M1115 - Page B - 30

Tigerpoint Part D - Page B - 11 PWR 1.05VS - Page B - 21

Schematic Diagrams

B.Schematic Diagrams

B-1

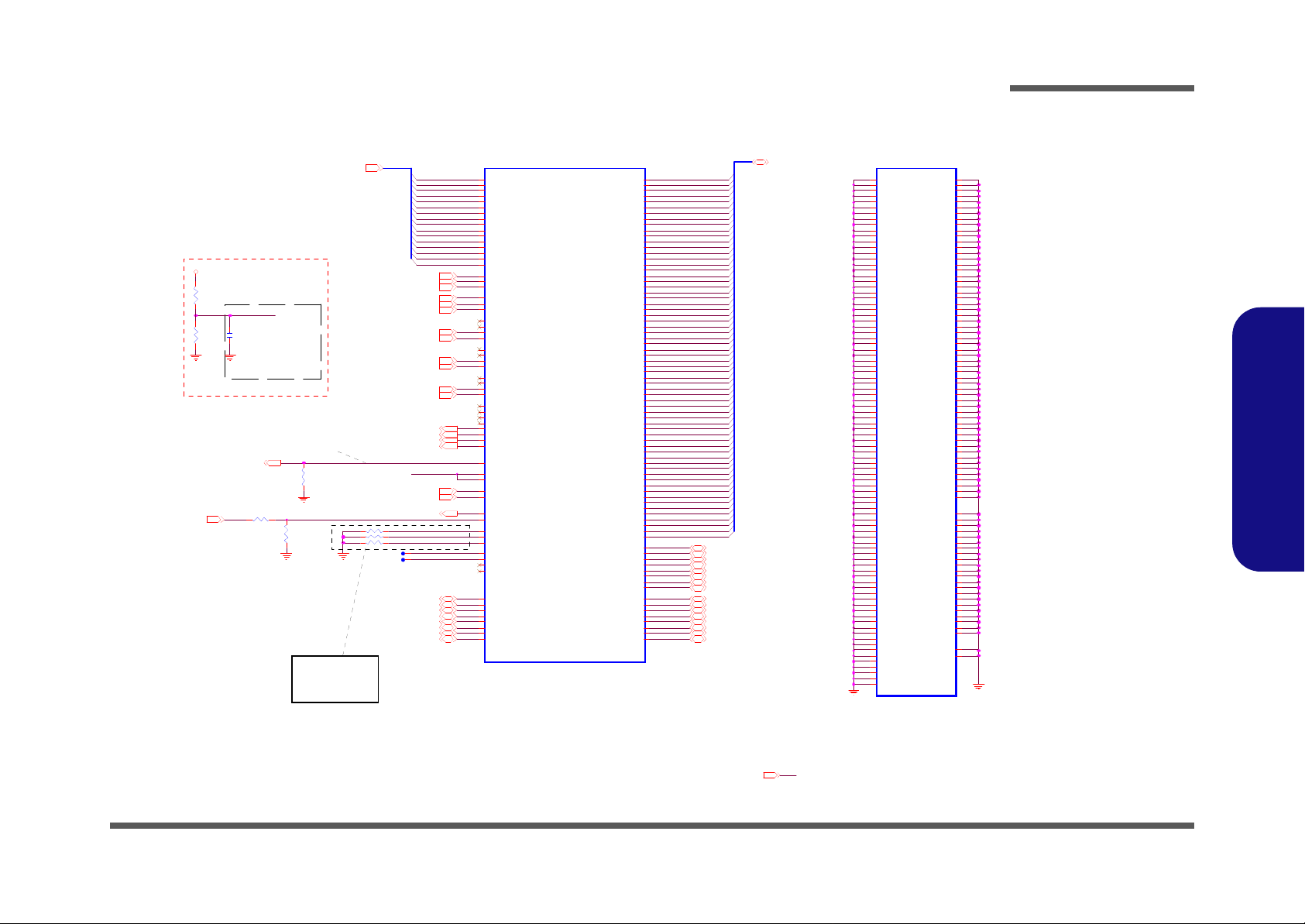

Page 2

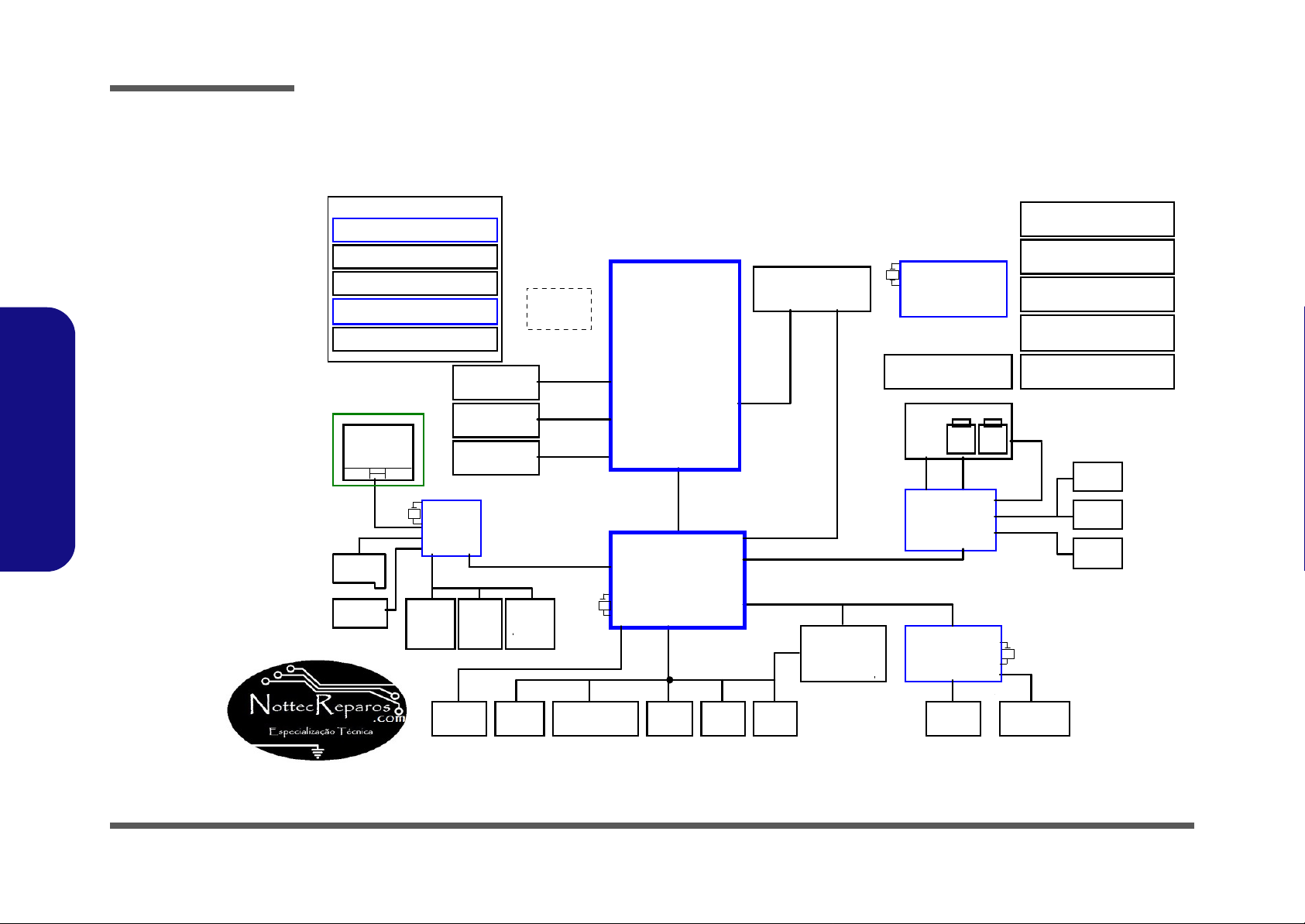

Schematic Diagrams

Sheet 1 of 29

System Block

Diagram

6-7P-W2105-001

MB:6-71-W 2100-D0 1

IO:6-71-W21 01-D01

PW R SW:6 -7 1-M1 15S -D 02(M 11 1 5)

Colck Generator

14 .31 8 MHz

17.1mm*8.1mm*1.2mm

TSSOP 64PIN

IDT 9VRS4338

AC-IN,CHARGER

PW R SW:6 -7 1-M1 10S -D 03(M 11 0 0M )

CLICK:6-71-M1102-D01A

G711ST9U

HP

OU T

THERMAL

SENSOR

SOUTH BRIDGE

Intel

Cedarview 32nm

TDP 3.5W

Mem ory Ter min ati on

480 Mbps

3 2.768 KH z

IN T SPK L

USB2.0

DDR3

VDD3,VDD5

1 7mm*17 mm*1.06 mm

PCIE

48 pin s QFN

VCORE+ GFX

DDR 3 One C han nel

360 MM AP

1 920x120 0

<=8"

SMART

BATTERY

24 MHz

1.5V,0.75VS(VTT_MEM)

LPC

D irect X 10.1

100 MHz

9*9*1.6m m

1GB & 2GB

0.1"~13

SATA I/II 3.0Gb/s

IN T MIC

10 G bits/s

0.5"~11"

2 2mm*22 mm*2.35 mm

F CBGA 559 pin

32 .7 68 KH z

C 0/C1/C 2/C3/C4

<7.5"

CLEVO Cedar Rock -NetX Sys tem Block Diagram

CRT OUT

1 280x800

X4/X 2-GEN1

INT. K/B

1"~16"

DMI

EC SMBUS

VT1802

800 /1067MT /s

PROCESSOR

33 MHz

<12"

Azalia Codec

IN T SPK R

AZALIA LINK

Tiger Point

S HEE T 15

1.05VS,1.5VS

SMART

FAN

<12"

MI C

IN

CL IC K B OA RD

TOUCH PAD

SYSTEM SMBUS

SO-DIMM0

LCD CONNECTOR

Socket

25

MHz

Card Reader

CARD READER

RJ-45

LAN

CCD

(USB7)

Bluetooth

(USB5)

Mini Card

WLAN

3.3V,5V,3VS,5VS,1.8VS

HSPI ROM

EC

14*14* 1.6mm

128pins LQFP

ITE 8518

Use EDP LCD

NB 1366x7 68

ELD 1920x 1080

1 .65Gb/s

NB 2X

ELD 4X

<8"

HDMI CONNECTOR

Port_1

(USB1)

Port_0

(USB0)

3G CARD (USB4)

Mini PCIE

JMC261C

Port_2

S HEE T 12

(USB2)

SATA HDD

System Block Diagram

B.Schematic Diagrams

B - 2 System Block Diagram

Page 3

Cedarview CPU Part D

R35

49.9_1%_04

R1 4 1K _0 4

C251

*0.1u_10V_X7R_04

R1 86 51_ 04

R34

2 . 2K _04

R9*1K_04

H_RSVD_K28

R30 *51_04

R6 51_ 04

C252

*0. 1u _10 V_ X7 R _04

R37

* 220 _04

R12 *1K_04

R7*1K_04

Q16

*G711ST9U

OUT1VC C

2

GND

3

R5 51_ 04

C226

*0 .1 u_ 16V_Y 5 V _ 04

R2 5 51 _04

R13 *1K_04

R28

2.2K_04

R36

49 .9_1%_04

R1 95 10 0_0 4

R196 *1K_04

R 1 0 51_ 04

R29

*2 20_ 04

R 198 75 _1 %_0 4

R8*1K_04

CPU

C E DARVIEW

ICH

4 OF 6

REV = 1.10

U12D

C D V _22 MM_R E V1 P1 0_5

CPUSLP#

B22

RSVD_N25

N25

RSVD_N24

N24

R SVD _W 26

W26

R SVD _W 25

W25 RSVD_R6

R6 RSVD_R5

R5

TR S T#

B24 TMS

D24 TD O

B25

TD I

C24

TC LK

C25

MV_ GPIO_RCOMP

K23

HV_GPIO_RCOMP

K24

RSVD_H30

H30

R SVD _J 31

J31 R SV D _K 29

K29 RSV D _L 30

L30

R SVD _L 29

L29

R SVD _K 30

K30 RSVD_H27

H27 R SV D _K 27

K27

R SVD _K 26

K26

R SVD _J 28

J28 R SV D _K 25

K25 ST R AP_ K 28

K28

ST R AP _L 27

L27

R SVD _L 26

L26

RSVD_L24

L24

RSVD_L22

L22

RSVD_K21

K21

SVID_DATA

C16

SVI D _C LK

D18

SVID_ALERT#

B16

RSVD_F19

F19

RSVD_E19

E19

HPLL_ REFCLK

K19

H P LL_ REF C LK _P

J19

PREQ#

G29

PRDY#

H29

DBR#

E30

RESET #

G30

PWRGOOD

D23PROCH OT #

A19

PB E #

C20

RSVD_L11

L11

THERMTRIP#

B20

INTR/LINT00

D20

INIT#

A23

DPLSLP#

B21DPRSTP#

C21

STPCLK#

D22RSVD_C18

C18

NMI/LINT10

C22

SMI#

B18

R 197 11 0_ 1%_ 04

R 1 1 51_ 04

R188 54 . 9_1 %_0 4

1. 05 VS

1. 05 VS

1. 0 5V S

1. 8V S1.8V S

1.05 VS

3. 3V

1. 8V S

H_DPRSTP # 10

H_INTR 9

H_A20M# 9

H_SMI# 9

H_PWRGD 1 0

H_STPCL K# 9

H_DPSLP# 10

H_INIT# 9

H_NMI 9

H_FERR# 9

H_THERMTRIP# 9

3.3 V8, 1 0, 11 , 1 2, 13 , 15, 17, 19 , 20,21,22

3.3 VS3,6,7,8,9,1 0,11 , 12,1 3, 14 ,15,16,21

1.0 5VS5,7 , 9, 10,11,20,22

H_CPU_ S VI D C LK 22

H_CPU_SVIDALRT# 22

H_CPU_SVIDDAT22

CLK_CPU_HPL# 7

PLTRST # 10

CLK_CPU_HPL 7

H_PROCHOT# 22

H_CPUSLP# 9

TH E R M_VOLT 15

1.8 VS5,15 ,21

LAYOUT NOTE:

H_CPUSL P#

Place termina tion near CPU

H_INIT#

H_PROCHOT#

H_INTR

H_NMI

H_SMI#

H_A20M#

H_STPCLK #

H_RSVD_H29

H_TCK

H_TRST#

H_TMS

H_TDI

Thermal IC

H_RSVD_G29

H_RSVD_L27

HV_GPIO_RCOMP

H_RSVD_H29

H_RSVD_K28

MV_GPIO _RC OMP

H_STPCLK#

CAD N ote: H_CP U_SVIDALR T#_R, H_CPU _SVI DDAT_ R

Place the PU r esistors close to C PU

H_CPU_SVIDDAT_R

C AD No te: H_CPU _SVIDCLK_ R

P lace the PU

r esist ors close to VR

H_CPU_SVIDCL K_R

H_CPU_SVIDALRT#_R

PROC HOT# m ust be term inated with a 56-O,

pu ll-u p re s is to r to VCCP e v e n if it is n o t us e d .

8/30

1:2 (4mils:8mils)

3

2

1

PTH3

10 K_ N TC _0 6

12

H_RSVD_G29

R 19 0 *10 mi l_s ho r t

D03

H_RSVD_L27

S VID Signa ls

H_CPU_SVIDA LRT#_R

H_CPU_SVIDDA T_R

H_CPU_SVIDCLK_R

3.3V

EM I

R201

1 0K _1% _04

H_CPUSLP#

H_TCK

H_TDO

H_TDI

H_TDO

R 18 7 *10 mi l_s ho r t

H_TRST#

H_TMS

R 18 9 *10 mi l_s ho r t

H_INIT#

H_PROCHOT#

H_A20M#

H_INTR

H_NMI

H_SMI#

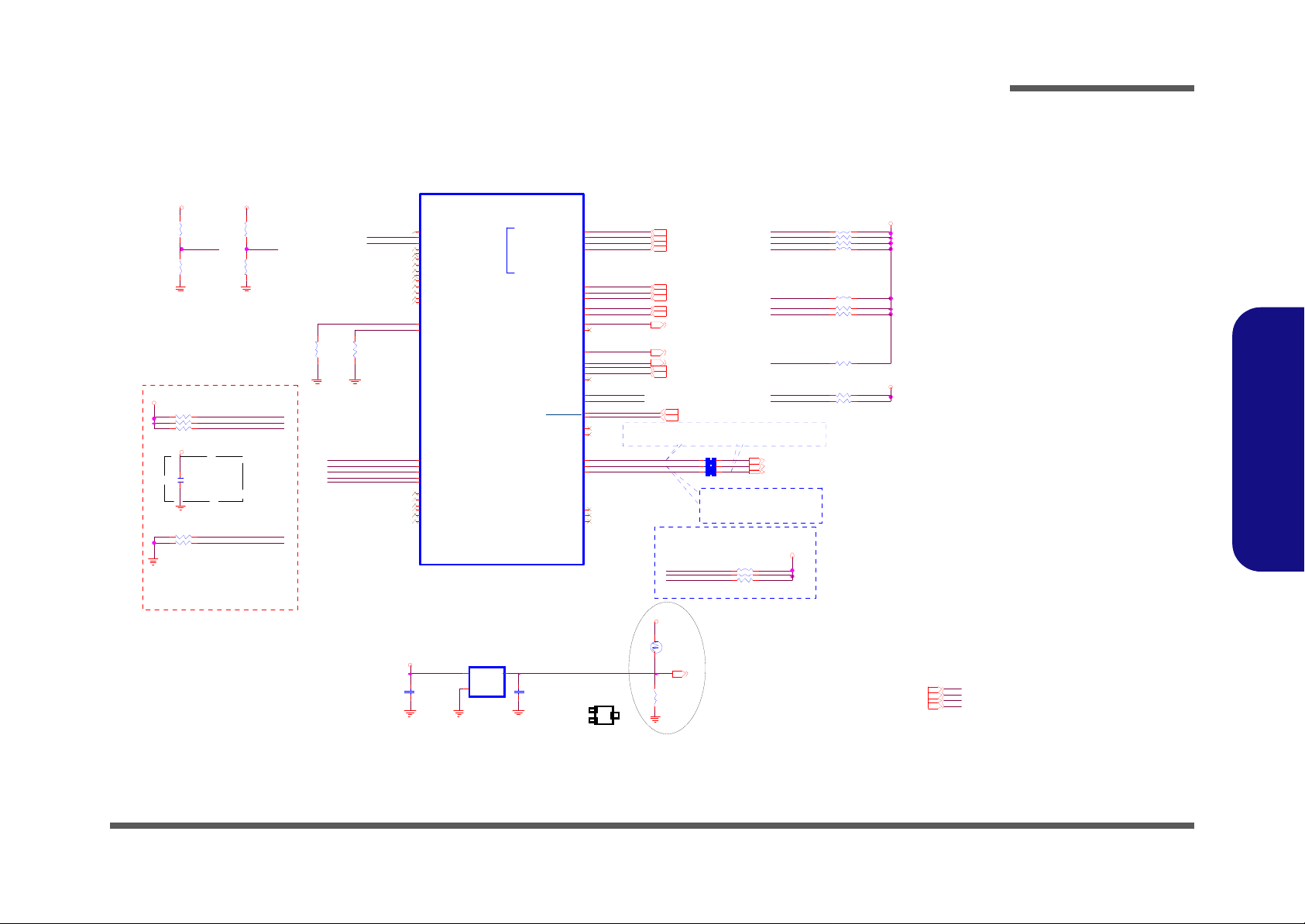

Sheet 2 of 29

Cedarview CPU

Part D

Schematic Diagrams

B.Schematic Diagrams

PLACE NEAR CPU

Cedarview CPU Part D B - 3

Page 4

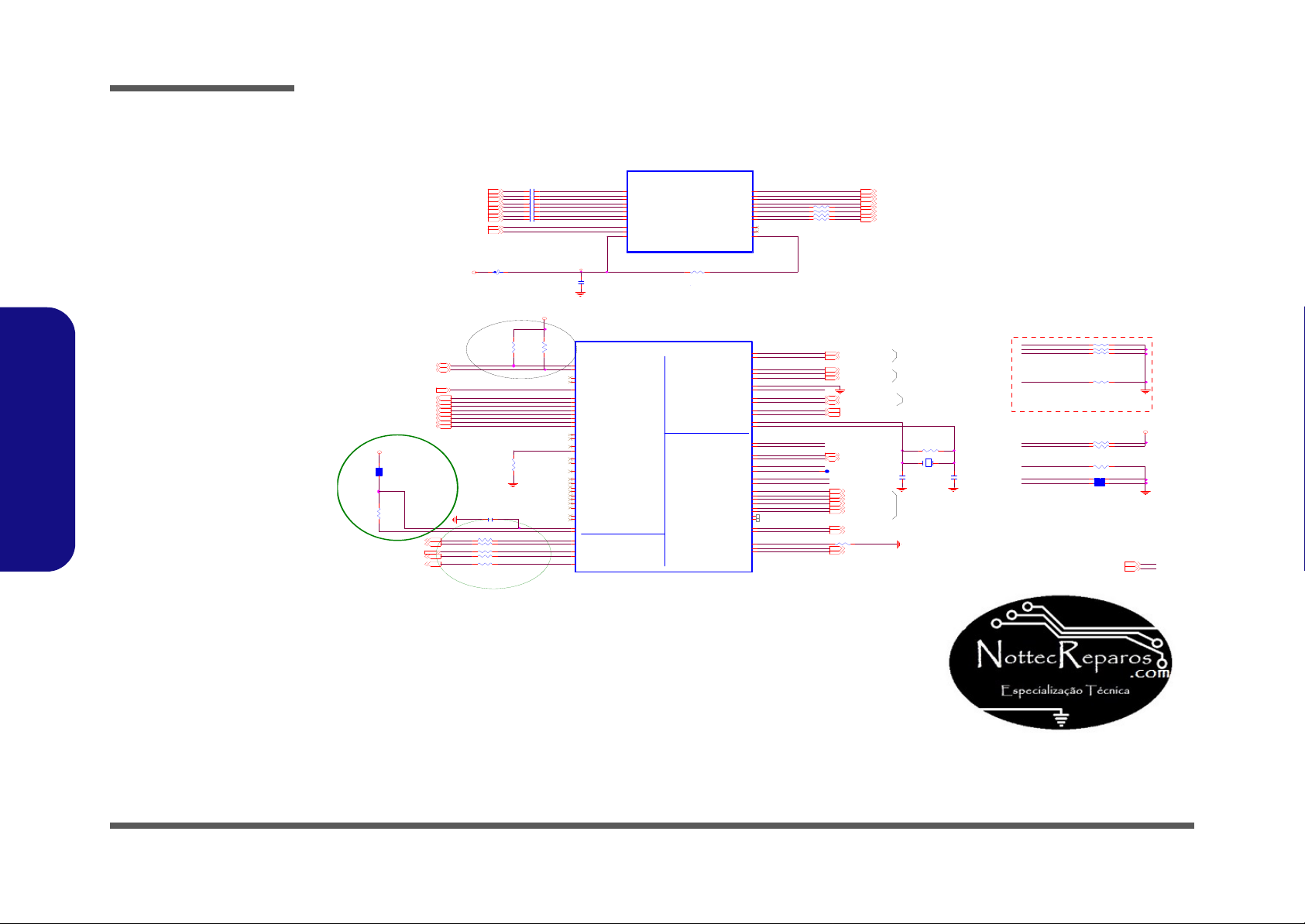

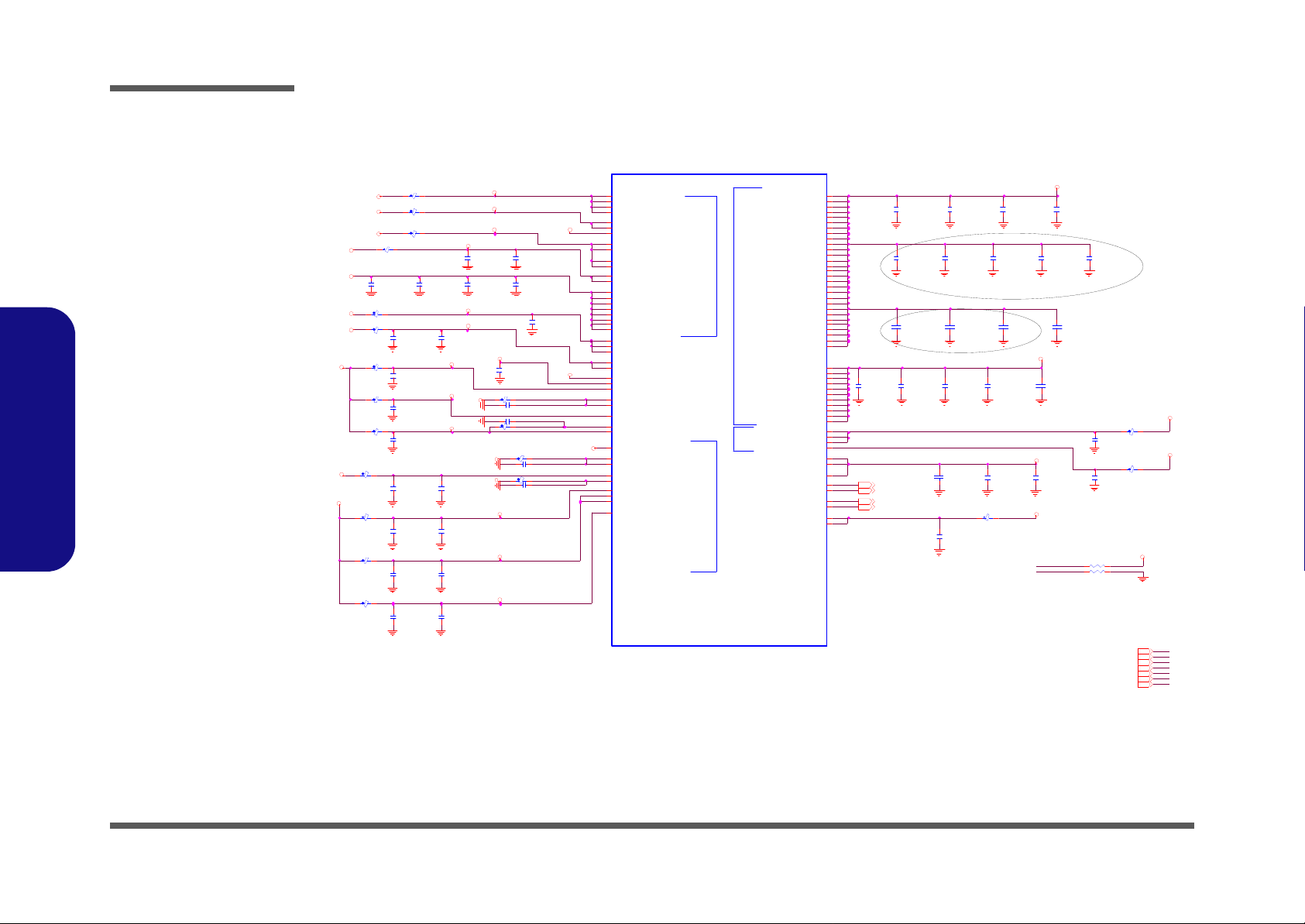

Schematic Diagrams

Sheet 3 of 29

Cedarview CPU

Part A-C-F

DMI_TXP_3

DM I_TXN _2

DMI_TXP_2

DM I_TXN _3

DMI_TXP_0

DM I_TXN _0

DM I_TXN _1

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

H_AZI L_SD O

BRE F_ REXT

DAC _ RED

DAC _ GR EE N

H_AZI L_SY NC

DAC _ BL UE

C14

22p_50V_NPO_04

C20 1U_6.3V_X5R _04

R38 *0_04

CEDARVIEW

DMI

1 OF 6

R EV = 1 .10

U12 A

CD V_2 2MM _REV1P1 0_ 5

DMI_REFCLKP

N9

DMI_REFCLKN

N8

DMI_REF1P5

T2

DMI_RXN3

P3

DMI_RXP3

P2 DMI_RXN2

N1

DMI_RXP2

N2

DMI_RXN1

M2 DMI_RXP1

M3

DMI_RXN0

L2

DMI_RXP0

L3

DM I_RC OMP

T1RS VD_TP_ R7

R7

RS VD_TP_ R8

R8

DMI_TXN3

N6

DMI_TXP3

N5DMI_TXN2

L8

DMI_TXP2

L9

DMI_TXN1

L6DMI_TXP1

L5

DMI_TXN0

K5

DMI_TXP0

K6C237 0.1u_10V_X7R _04

R209 7.5K_1%_04

R40 *0_04

C236 0.1u_10V_X7R _04

C256

1u_6.3V _X5R_04

R45 33_04

R21

7.5K_1%_04

R193 150_1%_04

C240 0.1u_10V_X7R _04

R17 2 .2 K_04

R192 150_1%_04

X5

FSX8L_27MH z

1 2

DMI_TXP_1

IHDA

DD I

CED A RVIEW

LVDS

VGA

3 OF 6

REV = 1.10

U12C

CD V_22MM_R EV1 P10 _5

DPL_REFCLKP

B9

DP L_R EF C LK N

A9

AZIL_R ST#

E21

AZIL_SD O

F21

AZIL_SD I

E22

AZIL_SY NC

F22

AZIL_BC LK

H21

BR EFR EXT

F15

BR EF1 P5V

E15

RS VD_TP_ H17

H17

RS VD_TP_ J1 7

J17

DD I1 _ T XN3

K13 DDI1 _ T XP3

J13

DD I1 _ T XN2

E13

DD I1 _ T XP2

F13 DD I1_TXN1

H11

DD I1 _ T XP1

J11 DD I1 _ TXN 0

F11

DD I1 _ T XP0

E11

DD I1 _ HP D

D26

DD I1 _ A UXN

C10

DD I1 _ A UXP

D10

DDI1_DDC_SDA

G27

DDI1_DDC_SCL

F25

RS VD_TP_ J1 5

J15

RS VD_TP_ H15

H15

DD I0 _ T XN3

A7

DD I0 _ T XP3

B7 DD I0_TXN2

C3

DD I0 _ T XP2

D4

DD I0 _ T XN1

F2

DD I0 _ T XP1

F3

DD I0 _ T XN0

G3 DD I0 _ T XP0

G2

DD I0 _ HP D

H22

DD I0 _ A UXN

B8 DD I0_AUXP

C8

DDI0_DDC_SDA

J22 DDI0_DDC_SCL

H25

PANE L_VDDE N

F29

PAN EL_ BKLTEN

E25P ANEL_ BKLTC TL

G22

LV DS _ C LK N

J4

LVDS_CLKP

H4

LVDS_TXN3

G6

LVD S_ TXP3

G5

LVDS_TXN2

H8

LVD S_ TXP2

H7LVDS_TXN1

E8

LVD S_ TXP1

F8

LVDS_TXN0

H10LVD S_TXP0

G10

LVDS_VREFL

H3

LVDS_VREF H

H2

LVDS_VBG

F10

LVDS_IBG

E10

LVDS_ D DC_D AT A

H24

LVDS_ D DC_ CL K

G24

LVDS_CTRL_DATA

E24

LVDS_CTRL_CLK

F28

DPL_REFSSCCLKN

E17

D PL_ REF SSCC L KP

F17

CR T_D DC _CLK

E27CRT_DDC_D ATA

E29

CR T_IR EF

A13

CR T_IR T N

D12

CR T _B LU E

C11

CR T_G RE E N

B11

CRT_RED

B12

CR T_VSYN C

C14

CRT_HSYNC

D14

R191 150_1%_04

C238 0.1u_10V_X7R _04

C243 *0.1u_10V_X7R_04

R48 90.9_1%_04

HDMIC_C1CN

HDMIC_C1CP

HDMIC_C2CP

HDMIC_CLKCP

HDMIC_CLKCN

HDMIC_C0CN

HDMIC_C0CP

HDMIC_C2CN

L47 *HCB1005K F-121T20_short

R26 *10K_ 0 4

R20

2.2K_04

R4

1M_04

C13

22p_50V_NPO_04

C242 *0.1u_10V_X7R_04

R39 *0_04

T1

R19

10K_04

R199 619_1%_04

R44 90.9_1%_04

R24 2.37K_1%_04

C248 *0.1u_10V_X7R_04

R18

10K_04

R47 90.9_1%_04

R16 2 .2 K_04

D0 3

R41 *0_04

C249 *0.1u_10V_X7R_04

R49 90.9_1%_04

3.3VS

1.5VS

3.3V S

1.5VS_DM IREF

1. 5 V S

C LK_DR EFSS# 7

DAC_GREEN 13

CLK_DREFSS 7

DAC_HSYNC 13

DAC_BLUE 13

DAC_VSYNC 13

DAC_DDCACLK 13

DAC_RED 13

DAC_DDCADATA 13

D MI_IC H_IT_MR 1 _DN8

D MI_IC H_IT_MR 0 _DP8

D MI_IC H_IT_MR 1 _DP8

D MI_IC H_IT_MR 0 _DN8 DMI_ICH_MT_IR0_DN 8

DMI_ICH_MT_IR0_DP 8

DMI_ICH_MT_IR1_DP 8

DMI_ICH_MT_IR1_DN 8

AZ_SDIN110

3.3VS6,7, 8,9,10,11,12,13,14,15,16,21

AZ_SY NC10,14

AZ_BITC L K10 , 1 4

AZ_SDOUT10,14

L_DDC_DATA 12

AZ_R ST#10 ,1 4

LVDS-L2P 12

LVDS-L2N 12

LVDS-L1N 12

MC H _ BL O N 12

LVDS-LCLKP 12

D DI1 D ISABLE: 2.2K TO GN D

LV DD _E N 1 2

LVDS-L1P 12

L_ DD C_ C LK 12

LVDS-LCLKN 12

LVDS-L0P 12

1.5VS5,7,8,11,21

LVDS-L0N 12

CLK_CPU_DMI#7

HDMI_CTRLCLK16

CLK_CPU_DMI7

HD MI_ C T RL DA TA16

HD MIC _ CL K C P16

PORT C_HP C16

R15

*HCB1005KF-121T20_short

HD MI C_ C1 C P16

HDMIC_CLKCN16

HDMIC_C1CN16

HDMIC_C2CN16

HD MI C_ C2 C P16

HD MI C_ C0 C P16

D MI_IC H_IT_MR 2 _DP8

HDMIC_C0CN16

D MI_IC H_IT_MR 2 _DN8

D MI_IC H_IT_MR 3 _DN8

D MI_IC H_IT_MR 3 _DP8 DMI_ICH_MT_IR3_DP 8

DMI_ICH_MT_IR2_DN 8

DMI_ICH_MT_IR2_DP 8

DMI_ICH_MT_IR3_DN 8

R23 *10mil_short

R22 *10mil_short

VGA RGB re sis to rs co ls e t o M CH ball

Zo = 37.5 Ohm ? 5%

signa l : 9 m ils

length < 800 mils

Two VGA RGB resistors between

Zo = 50 Oh m ? 5%

signa l : 5 m ils

lengt h < 14000 mil s

LVD_VREFL_OUT_R

LVD_V REFH_OUT_R

LVD_IBG

DPL_REFCLKP

DMI_RCOMP

OPTION

D03

Zd iff = 9 0 Ohm ? 0%

signal / space : 4 / 5 mils

le ngth < 785 0 mi ls

(1)

(2 )

L V DS Control Signal Group

LBKLT_CTL,LBKLT_EN,LVDD_EN

(1)

LVDS Cloc k & Data Signal Group

Zo = 50 O hm ? 0%

sign al : 5 mils

le ngth < 6000 mi ls

LVD_VREFH_OU T_R

TP_LVD_VBG

LVD_IBG

LVD_VREFL_OUT_R

LCTLA_CLK

LVD S_BKLTCTL

LCTLB_DATA

H_AZI L_SD I

DAC_BLUE

DAC_GREEN

DAC_RED

DMI_RCOMP

length < 500mils

DPL_REFCLKN

LCTLB_DATA

Zd iff = 80 Ohm ? 7.5%

l engt h =b reak ou t( <=50 0mils) +(< = 6000 m ils)

DMI Signal Group

BRE F_ 1P5V

DAC REF SET

LCTLA_CLK

DD I_ DD C_SD A

H_AZI L_BC L K

LA Y O UT NOT E:

Place VGA RGB resistors close to MCH

< 800 mils t o M CH ball

D0 3

H_AZI L_R ST #

DMI_RXN_3

DMI_RXP_2

DMI_RXN_2

DMI_RXP_3

(1)

(2)

3/7

(3)

(2)

CRT Sync Signal Group

D AC_HSYNC,DAC_VSYNC

Zo = 50 Ohm ?5%

signa l : 5 m ils

lengt h < 14500 mi ls

(1)

CR T DAC Signal Gro up

CR T_RED,CRT_GREEN,CRT_BLUE

(3)

CRT Control S igna l G r oup

C RT_DDC_CLK,CRT_DDC_DATA

Zo = 50 Oh m ? 5%

signal : 5 m ils

lengt h < 15100 mil s

D ACR EF SE T

LA Y O UT NOT E:

Pla ce DA C REF SET r e s i st or c l o se to M CH

< 500 mils t o M CH ball

PORTC_HPC

Cedarview CPU Part A-C-F

B.Schematic Diagrams

B - 4 Cedarview CPU Part A-C-F

Page 5

Cedarview CPU Part B

DDR3_DQPU

Maximum via 2

Width 5mil

Spacing 10 m il

< 2"in ch

M_A _DQ 58

M_A _DQ 27

M_A_A13

M_A _DQ 44

M_A _DQ 19

M_A _DQ 33

M_A _DQ 25

M_A _DQ 18

M_A _DQ 37

M_A _DQ 17

M_A_A4

M_A_A10

M_A _DQ 4

M_A _DQ 20

M_A _DQ 8

M_A _DQ 26

M_A _DQ 23

M_A _DQ 57

M_A _DQ 60

M_A _DQ 30

M_A _DQ 52

M_A _DQ 9

M_A_A8

M_A_A1

M_A _DQ 2

M_A _DQ 10

M_A _DQ 28

M_A _DQ 62

M_A _DQ 51

M_A _DQ 29

M_A _DQ 39

M_A _DQ 55

M_A _DQ 38

M_A _DQ 54

M_A _DQ 45

M_A _DQ 41

M_A _DQ 42

M_A _DQ 24

M_A _DQ 11

M_A _DQ 35

M_A _DQ 31

M_A _DQ 43

M_A_A2

M_A _DQ 22

M_A _DQ 40

M_A _DQ 49

M_A _DQ 63

M_A _DQ 53

M_A _DQ 36

M_A _DQ 3

M_A _DQ 50

M_A _DQ 34

M_A_A9

M_A _DQ 13

M_A _DQ 48

M_A_A11

M_A _DQ 46

M_A _DQ 59

M_A_A7

M_A _DQ 1

M_A _DQ 21

M_A_A5

M_A _DQ 32

M_A _DQ 0

M_A _DQ 5

M_A _DQ 7

M_A _DQ 14

M_A _DQ 16

M_A _DQ 56

M_A _DQ 6

M_A _DQ 47

M_A _DQ 15

M_A_A6

M_A_A3

M_A_A12

M_A _DQ 61

M_A _DQ 12

Widt h 8mi l

Spacing 8 mil

< 300mil

M_A_A15

DELAY _ALL_SYS_PWRGD10, 15

R204

1K_1% _04

R205 33.2 _1%_04

R200

10 K_1%_ 04

T2

R207 22.6 _1%_04

T3

C253

0.1u _16V _Y5 V_0 4

R206 274_1 %_0 4

R208

100K_04

MC H _V REF

Widt h 4mil

Spac ing 5 mil

GND

CEDARVIEW

6 O F 6

REV = 1.10

U12F

CDV _22 MM_REV1 P10_5

VSS

H13

VSS

G8

VSS

G3 1

VSS

G2 1

VSS

G1 9

VSS

G1 7

VSS

G1 5

VSS

G1 3

VSS

G1 1

VSS

G1

VSS

F4

VSS

F2 4

VSS

E7

VSS

E5

VSS

E2

VSS

D9

VSS

D8

VSS

D28

VSS

D19

VSS

C7

VSS

C30

VSS

C26

VSS

C12

VSS

B2 3

VSS

B1 9

VSS

B1 4

VSS

B1 0

VSS

AL 7

VSS

AL25

VSS

AL23

VSS

AL19

VSS

AL13

VSS

AK9

VSS

AK28 VSS

AK19

VSS

AK13 VSS

AJ 3

VSS

AJ 2

VSS

AH 9

VSS

AH 6

VSS

AH28

VSS

AH26

VSS

AG 5

VSS

AG22

VSS

AF7

VSS

AF28

VSS

AF24

VSS

AF21

VSS

AF13 VSS

AF11

VSS

AE31 VSS

AE3

VSS

AE19

VSS

AE17

VSS

AE15

VSS

AE11

VSS

AE10

VSS

AE1

VSS

AD 8

VSS

AD 5

VSS

AD26

VSS

AD24

VSS

AD21

VSS

AD19

VSS

AC 4

VSS

AC28 VSS

AC22

VSS

AC13

VSS

AC11

VSS

AC10

VSS

AC 1

VSS

AB29

VSS

AB23

VSS

AB17

VSS

AB15

VSS

AA9

VSS

AA7

VSS

AA29

VSS

AA27

VSS

AA26

VSS

AA23 VSS

AA21

VSS

AA19 VSS

AA13

VSS

AA10

VSS

AA1

VSS

A2 5

VSS

A2 1

VSS

A1 6

VSS

A1 1

VSSA _CRTDAC

D13

VSS_CDVDET

L14

VSS

E1

VSS

C31

VSS

C2

VSS

C1

VSS

B31

VSS

B3

VSS

B2

VSS

AL5

VSS

AL30

VSS

AL3

VSS

AL29

VSS

AL2

VSS

AK31

VSS

AK30

VSS

AK2

VSS

AK1

VSS

AJ31

VSS

AJ1

VSS

AH1

VSS

A3

VSS

A29

VSS

A27

VSS

Y4VSS

W6

VSS

W5VSS

W30

VSS

W27

VSS

W24

VSS

W23

VSS

W22

VSS

W21

VSS

W2

VSS

W19

VSS

W14

VSS

W10

VSS

V2

VSS

U9

VSS

U6VSS

U5

VSS

T3VSS

T18

VSS

T14

VSS

P4

VSS

P16

VSS

P14

VSS

N7

VSS

N4

VSS

N28

VSS

N27

VSS

N26

VSS

N23

VSS

N22

VSS

N21

VSS

N19

VSS

N14VSS

N10

VSS

M4

VSS

M29

VSS

L7

VSS

L31

VSS

L25

VSS

L23

VSS

L13

VSS

L10

VSS

L1

VSS

K9

VSS

K8

VSS

K7

VSS

K3

VSS

K15VSS

K11

VSS

J30VSS

J21

VSS

J2

VSS

J10

VSS

H6

VSS

H28

VSS

H26

VSS

H19

DDR3

CED ARVIEW

2 OF 6

REV = 1.10

U12B

CDV_22MM_REV1P10_5

DDR3_WE#

AH1 0

DDR3_VREF

AJ27

DDR3_VCCA_PWROK

W7

DDR3_REFP

AC1 9

DDR3_REFN

AB19

DDR3_RAS#

AJ11

DDR3_ODT PU

AJ26

DDR3_ODT 3

AJ 7

DDR3_ODT 2

AL 9

DDR3_ODT 1

AK7

DDR3_ODT 0

AK10

RSVD_TP_AF19

AF19

RSVD_TP_AG19

AG1 9

RSVD_TP_AB11

AB11

RSVD_TP_AB13

AB13

DDR3_M A9

AH2 0 DDR 3_MA8

AJ20

DDR3_M A7

AK20 DDR 3_MA6

AJ18

DDR3_M A5

AH1 8

DDR3_M A4

AK18

DDR3_M A3

AJ16

DDR3_M A2

AJ14

DDR 3_MA15

AJ22

DDR 3_MA14

AH2 2

DDR 3_MA13

AJ 8

DDR 3_MA12

AJ21

DDR 3_MA11

AK21

DDR 3_MA10

AJ12

DDR3_M A1

AK16

DDR3_M A0

AK14

DDR3_DRAMRST#

AK25

DDR3_DRAM_PWRO K

AA5

D DR3_D Q S#7

AA2

D DR3_D Q S#6

AB7

D DR3_D Q S#5

AF3

D DR3_D Q S#4

AF10

D DR3_D Q S#3

AF22

D DR3_D Q S#2

AF29

D DR3_D Q S#1

AB25

D DR3_D Q S#0

AA31

DDR3_DQS7

Y3

DDR3_DQS6

AB6

DDR3_DQS5

AF4

DDR3_DQS4

AG10

DDR3_DQS3

AE22

DDR3_DQS2

AF30

DDR3_DQS1

AB24

DDR3_DQS0

AA30

DDR3_DQPU

AK27

DD R3_DQ9

AA22DD R3_DQ8

AA24

DD R3_DQ7

AB30

DDR3_DQ63

W1

DDR3_DQ62

Y2

DDR3_DQ61

AB3

DDR3_DQ60

AC2

DD R3_DQ6

AB28

DDR3_DQ59

V3

DDR3_DQ58

W4

DDR3_DQ57

AB4

DDR3_DQ56

AB2DDR3 _DQ55

AA8

DDR3_DQ54

AB9DDR3 _DQ53

AE5

DDR3_DQ52

AE8

DDR3_DQ51

AB5

DDR3_DQ50

AA6

DD R3_DQ5

W28

DDR3_DQ49

AD6

DDR3_DQ48

AD7

DDR3_DQ47

AD4

DDR3_DQ46

AE2

DDR3_DQ45

AK3

DDR3_DQ44

AH4

DDR3_DQ43

AD3

DDR3_DQ42

AD2

DDR3_DQ41

AG3DDR3 _DQ40

AH2

DD R3_DQ4

W31

DDR3_DQ39

AF8DDR3_DQ38

AD10

DDR3_DQ37

AE13

DDR3_DQ36

AG13

DDR3_DQ35

AG7

DDR3_DQ34

AG8

DDR3_DQ33

AD11

DDR3_DQ32

AD13

DDR3_DQ31

AE21

DDR3_DQ30

AG21

DD R3_DQ3

AC31

DDR3_DQ29

AG25

DDR3_DQ28

AG27

DDR3_DQ27

AC21

DDR3_DQ26

AD22

DDR3_DQ25

AG24

DDR3_DQ24

AE24DDR3_DQ23

AJ29

DDR3_DQ22

AG30

DDR3_DQ21

AD30

DDR3_DQ20

AD28

DD R3_DQ2

AC30

DDR3_DQ19

AK29

DDR3_DQ18

AJ30

DDR3_DQ17

AE29

DDR3_DQ16

AD29

DDR3_DQ15

AD27

DDR3_DQ14

AD25

DDR3_DQ13

AA25

DDR3_DQ12

AB27

DDR3_DQ11

AE26

DDR3_DQ10

AE27

DD R3_DQ1

Y29

DD R3_DQ0

Y30

DDR3_DM 7

AA3

DDR3_DM 6

AB8

DDR3_DM 5

AG 2

DDR3_DM 4

AG1 1

DDR3_DM 3

AB21

DDR3_DM 2

AE30

DDR3_DM 1

AB26

DDR3_DM 0

Y28

DDR3_CS#3

AK8

DDR3_CS#2

AK11

DDR3_CS#1

AH 8

DDR3_CS#0

AH1 2

DDR3_CM DPU

AJ25

DDR3_CKE3

AH2 4

DDR3_CKE2

AK24

DDR3_CKE1

AJ24

DDR3_CKE0

AH2 3

DDR3_CK#3

AD1 5

DDR3_CK#2

AC1 7

DDR3_CK#1

AG1 7

DDR3_CK#0

AF15

DDR3_CK3

AC1 5

DDR3_CK2

AD1 7

DDR3_CK1

AF17

DDR3_CK0

AG1 5

DDR3_CAS#

AJ10

DDR3_BS2

AK22

DDR3_BS1

AH1 3

DDR3_BS0

AK12

DDR3_VREF_NCTF

AL28

R203

1K_1% _04

R19 4 12K _1%_04

1.5 V

M_A_RAS#6

M_ A_A [1 5:0 ]6

M_A_BS06

M_A_CAS#6

M_A _WE #6

M_A_BS26

M_A_DQS4# 6

M_A_BS16

M_A _DM76

M_A_DQS0 6

M_A _DM06

M_A_DQS3 6

M_A _DM16

M_A_DQS4 6

M_A_DQS6# 6

M_A_DQS7# 6

M_A_DQS0# 6

M_A_DQS1# 6

M_A _DM36

M_A _DM56

M_A _DM26

M_A_DQS5# 6

M_A_DQS7 6

M_A_DQS6 6

M_A _DM46

M_A_DQS2# 6

M_A _DQ [ 63: 0 ] 6

M_A_DQS5 6

M_A _DM66

M_A_A14

M_A_DQS2 6

M_A_DQS3# 6

M_A_DQS1 6

CPU_R SVD_T P_ 03

DDR3_DRAMRST#6

1.5V5, 6,1 9,21

CLK_DDR3REF_ CLK7

DDR3_DRAM_PWROK10

CLK_DDR3REF_CLK#7

M_ CS3 #6

M_ CKE 26

M_ CS2 #6

M_ CKE 36

M_ OD T36

M_ OD T26

M_CLK_ DDR26

M_CLK_ DDR36

M_CLK_ DDR2#6

CPU_R SVD_T P_ 04

M_CLK_ DDR3#6

Place r esistors and CA P

clos e to DDR _V REF p in

LA YOUT NO TE:

MCH_VREF

LA YOUT NO TE:

M_A_A0

DDR3_ODTPU

DDR3_CM DPU

Sheet 4 of 29

Cedarview CPU

Part B

Schematic Diagrams

B.Schematic Diagrams

Cedarview CPU Part B B - 5

Page 6

Schematic Diagrams

VCC SE NSE

VSSSE NSE

C37

1u_6.3V_X 5R_04

VCC AG PI O

VCC DMPL

C26

1u_6.3V_X 5R_04

D02

C44

1u_6. 3V_X5R_04

VCC AG L VD S

VCC SF R MPL

C46

1u _6.3V_X5R_04

L3 *HCB1005K F-121T20_sh ort

C39

*0.1u_16V_Y5V_04

C239

22 u_6.3V_X5R _08

L16 HCB1005KF -121T 20

L13 *HCB1005K F-121T2 0_short

C49

1u_6.3V_X5R_04

C12

1u_6.3V_X5R_04

L7 *HCB1005KF-121T20_short

DDR

PLL

CEDARVIEW

POWE R

DMI

CP U

5 OF 6

REV = 1 .1 0

U12E

CDV_22MM_ REV 1P10_5

V_S M_7

AL21

VCCAHPLL

B26

VCCPLLCPU1_2

B30

VCCPLLCPU1_1

C29

VCCPLLCPU0

B27

VCCDMPL

AA11

VCC SF RMP L

AA18

VCC AZ ILAON_2

A30

VCC AZ ILAON_1

B29

VCCDIO

L21

VCCDL VDS

J1

VCC AL V DS

H5

VCCADAC

B13

VCC AG PI O _2

D31

VCC AG PI O _1

D30

VCC AG PI O _D I O

N18

VCC AG PI O _R EF

L16

VCC AG PI O _L V

L19

VCCADP1_SFR

L18

VCCADP0_SFR

K17

VCCADP_3

D6

VCCADP_2

C6

VCCADP_1

B5

V_S M_8

AG31

V_S M_6

AL16

V_S M_5

AL11

V_S M_4

AK 5

V_S M_3

AK23

V_S M_2

AH1 9

V_S M_1

AH1 4

VCCCKDDR_2

AK 6

VCCCKDDR_1

AJ6

VCCADLLDDR_ 2

W13

VCCADLLDDR_ 1

W11

VCCACKDDR_2

W9

VCCACKDDR_1

W8

VCCRAMXX X_3

V4 VCCRAM XX X_2

N31

VCCRAMXX X_1

N30

VCCADDR_4

W18

VCCADDR_3

W16

VCCADDR_2

AA16

VCCADDR_1

AA14

VCCT HRM_2

K2

VCCT HRM_1

N16

VSS_G FXSE NSE

U7

VCC_GFX SE NSE

U8

VSS_CPUS ENSE

M30

VCC_CPUS ENSE

M28

VCC F HV_3

V14

VCC F HV_2

T16

VCC F HV_1

V16

VCCADMI_PLLSFR

K4VCCADM I_ 3

A4

VCCADM I_ 2

C5

VCCADM I_ 1

B4

VCC_GFX _ 1 1

V13

VCC_GFX _ 1 0

V11

VCC_GFX _ 0 9

U10

VCC_GFX _ 0 8

T13

VCC_GFX _ 0 7

T11VCC_G FX _ 0 6

R9VCC_GFX _ 0 5

R10

VCC_GFX _ 0 4

P13

VCC_GFX _ 0 3

P11

VCC_GFX _ 0 2

N13

VCC_GFX _ 0 1

N11

VCC_CPU_29

V30

VCC_CPU_28

V29VCC_CPU_27

V28

VCC_CPU_26

V21

VCC_CPU_25

V19

VCC_CPU_24

V18

VCC_CPU_23

U27

VCC_CPU_22

U26

VCC_CPU_21

U25

VCC_CPU_20

U24

VCC_CPU_19

U23VCC_CPU_18

U22VCC_CPU_17

T31

VCC_CPU_16

T30

VCC_CPU_15

T29

VCC_CPU_14

T21

VCC_CPU_13

T19

VCC_CPU_12

R27

VCC_CPU_11

R26

VCC_CPU_10

R25

VCC_CPU_09

R24VCC_CPU_08

R23VCC_CPU_07

R22

VCC_CPU_06

P30

VCC_CPU_05

P29

VCC_CPU_04

P28

VCC_CPU_03

P21

VCC_CPU_02

P19

VCC_CPU_01

P18

C19 2.2u_6.3V_X 5R_06

L15 *HCB1005K F-121T20_sh ort

C27

10u_6.3V_X5 R_ 0 6

C9

1u_6.3V_X5R_04

L44 *HCB1005K F-121T20_sh ort

C47

*1u_6.3V_X 5R_04

C40

*0.1u_16V_Y5V_04

R33 10_1%_04

C24 4.7u_6.3V_X 5R_06

L8

*HCB1005KF-121T20_short

L10 HCB1005KF -121T20

C25

1u_6.3V_X5R_04

C18

10u_6.3V_X5 R_ 0 6

C50

10u_6.3V_X5 R_ 0 6

C22

1u_6.3V_X5R_04

L9

*HCB1005KF-121T20_short

C245

*22u_6.3V_X 5R_08

C241

*1u_6.3V_X 5R_04

C235

*22u_6.3V_X 5R_08

R31 10_1%_04

L17 HCB1005 KF-121T 20

C54

1u_6.3V_X5R_04

C42

*0.1u_16V_Y5V_04

C11

10u_6.3V_X5 R_ 0 6

L4 *HCB1005K F-121T2 0_short

L11 *HCB1005K F-121T2 0_short

C53

1u_6.3V_X 5R_04

C255

0.1u_16V_Y5V_04

L12 *HCB1005K F-121T20_sho rt

C233

10u_6.3V_X5 R_ 0 6

C227

22u_6.3V _X5R _08

C254

22u_6.3V_X5R_08

C57

1u_6.3V_X 5R_04

C36

1u_ 6.3V_X5R _0 4

C17

1u_6 . 3V_ X5R_04

C228

1u_6.3V_X5R_04

L5

*HCB1005KF-121T20_short

L14 *HCB1005K F-121T20_sho rt

C43

*1u_6.3V_X 5R_04

L46 *HCB1608K F-121 T25_short

d03

C234

*1u_6.3V_X5R_04

C21

*1u_6.3V_X 5R_04

C229 2.2u_6.3V_X5R_06

C55

1u_6.3V_X 5R_04

L6 *HCB1005K F-121T2 0_short

C10

1u_6.3V_X5R_04

C16

10u_6.3V_X5 R_ 0 6

L1 *HCB1005K F-121T2 0_short

C51 2.2u_6.3V_X5R_06

L45 *HCB1005K F-121T20_ sh o rt

C28

1u_ 6.3V_X5R _0 4

C246

*22u_6.3V_X5R_08

C247

22u_6.3V_X 5R_08

C15

1u_6.3V_X5R_04

C23

1u_6.3V_X5R_04

C41

* 0. 1 u_ 16V_Y 5V_ 04

C29

0.1u_10V_X 7R_04

L2 *HCB1005K F-121T20_sh ort

1.8VS

VCO RE

1.8VS

VCORE

VGFX

1.05VS

1.05VS _RSEN SE

1.5VS

1.05VS

1. 05 VS_E AST

1.05VS

1.05VS_VCC ADP

1.05VS

1.5V

1.05VS _EAS T

1.5V

1.5V _VCCKDDR

1.05VS _VCCDDR

1.05VS_EA ST

1. 05VS_ RSEN S E

VCCADAC

1.5VS

1.05VS_ RS EN SE

1.5VS _V CCADP

VCC AG PIO_DI O

1.5VS

3.3VS_PRIME

3. 3V S_PRI ME

1.05VS_RSENSE

VCCLVDS

1. 05V S

1. 05VS_V CCPLLCP U0

1. 05VS_ VCC AH PL L

1. 05VS_V CCPLLCP U1

1.5VS

1.05VS_ RS EN SE

VSSSENSE 22

VGFX22

VCC SEN SE 22

1.5VS3,7,8, 11,21

VCORE22

3. 3VS_PR IME11,15,21

1.8VS2,15,21

1.05V S2,7,9,10,11 ,2 0 ,2 2

1.5V4,6,19,21

VCC GFXSENSE 22

VSS GF XSENSE 22

C33

1u_6.3V_X5R_04

Sheet 5 of 29

Cedarview CPU

Part E

Cedarview CPU Part E

B.Schematic Diagrams

B - 6 Cedarview CPU Part E

Page 7

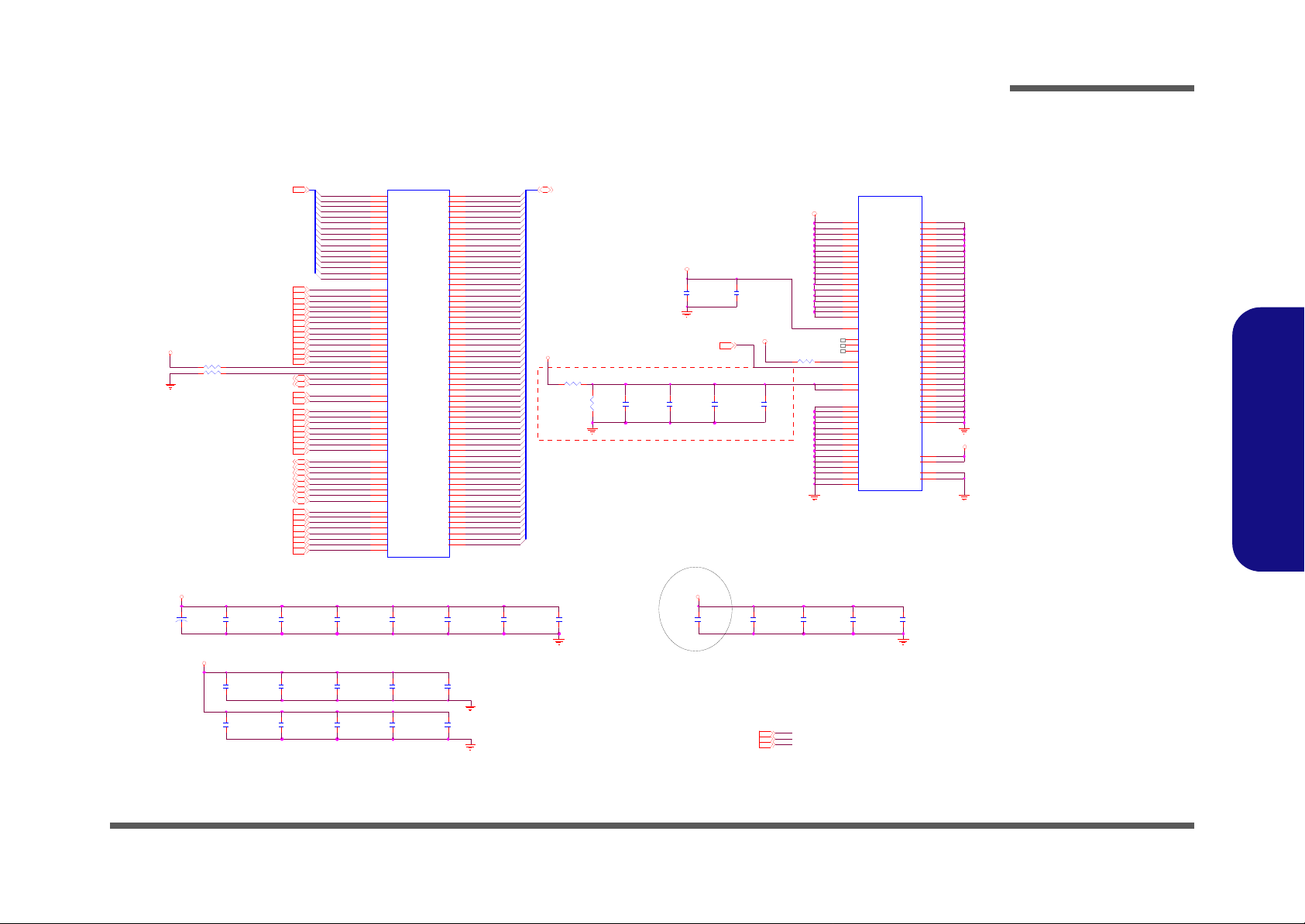

DDRIII SO-DIMM_0

+

C279

*2 20 U_ 4V _D

R114

1K_ 1%_ 04

C137

1U _6 .3V_ X5 R_ 04

R113 1K_1%_04

C275

*1 0u _6. 3 V_ X5R _ 08

C144

0. 1u _1 6V_ Y 5 V_04

C123

0.1u_16V_Y5V_04

R122 10K_04

C120

0.1u_16V_Y5V_04

C127

0. 1u _16 V_Y 5V_04

C140

*1U_6.3V_Y5V_04

C122

2. 2u _1 6V_ X5R _0 6

C129

*1U _6 . 3 V_Y 5V_04

C277

0. 1u _1 6V_Y 5V_04

C124

*0.1 u_16V_Y5V_04

C130

0 .1 u_ 16 V_Y 5V_04

C126

0. 1u _1 6V_ Y 5 V_04

C278

*10u_6.3V_X5R_08

C276

*10u_6.3V_X5R_08

J_DIMM1B

AS 0A 62 1- U4R N - 7F

VDD1

75

VDD2

76

VDD3

81

VDD4

82

VDD5

87

VDD6

88

VDD7

93

VDD8

94

VDD9

99

VDD10

100

VDD11

105

VDD12

106

VDDSPD

199

NC1

77

NC2

122

NCTEST

125

VREF_DQ

1

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VSS16

44

VSS17

48

VSS18

49

VSS19

54

VSS20

55

VSS21

60

VSS22

61

VSS23

65

VSS24

66

VSS25

71

VSS26

72

VSS27

127

VSS28

128

VSS29

133

VSS30

134

VSS31

138

VSS32

139

VSS33

144

VSS34

145

VSS35

150

VSS36

151

VSS37

155

VSS38

156

VSS39

161

VSS40

162

VSS41

167

VSS42

168

VSS43

172

VSS44

173

VSS45

178

VSS46

179

VSS47

184

VSS48

185

VSS49

189

VSS50

190

VSS51

195

VSS52

196

G2

GN D2

G1

GN D1

VTT2

204

VTT1

203

VREF_CA

126

RESET#

30

EVENT#

198

VDD13

111

VDD14

112

VDD16

118

VDD15

117

VDD17

123

VDD18

124

C150

0.1u_16V_Y5V_04

C155

1U _6 .3 V_X5 R_ 0 4

R123 10K_04

C133

0. 1u_ 16 V_Y 5V_04

C131

0. 1u _16 V_Y 5V_04

C125

*1 U_ 6. 3V_Y 5V_ 04

J_DIM M1A

AS 0A62 1- U4 RN -7F

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC#

83

A13

119

A14

80

A15

78

DQ0

5

DQ1

7

DQ2

15

DQ3

17

DQ4

4

DQ5

6

DQ6

16

DQ7

18

DQ8

21

DQ9

23

DQ10

33

DQ11

35

DQ12

22

DQ13

24

DQ14

34

DQ15

36

DQ16

39

DQ17

41

DQ18

51

DQ19

53

DQ20

40

DQ21

42

DQ22

50

DQ23

52

DQ24

57

DQ25

59

DQ26

67

DQ27

69

DQ28

56

DQ29

58

DQ30

68

DQ31

70

DQ32

129

DQ33

131

DQ34

141

DQ35

143

DQ36

130

DQ37

132

DQ38

140

DQ39

142

DQ40

147

DQ41

149

DQ42

157

DQ43

159

DQ44

146

DQ45

148

DQ46

158

DQ47

160

DQ48

163

DQ49

165

DQ50

175

DQ51

177

DQ52

164

DQ53

166

DQ54

174

DQ55

176

DQ56

181

DQ57

183

DQ58

191

DQ59

193

DQ60

180

DQ61

182

DQ62

192

DQ63

194

BA0

109

BA1

108

RAS#

110

WE#

113

CAS#

115

S0#

114

S1#

121

CKE0

73

CKE1

74

CK0

101

CK0#

103

CK1

102

CK1#

104

SDA

200

SCL

202

SA1

201

SA0

197

DM0

11

DM1

28

DM2

46

DM3

63

DM4

136

DM5

153

DM6

170

DM7

187

DQS0

12

DQS1

29

DQS2

47

DQS3

64

DQS4

137

DQS5

154

DQS6

171

DQS7

188

DQS0#

10

DQS1#

27

DQS2#

45

DQS3#

62

DQS4#

135

DQS5#

152

DQS6#

169

DQS7#

186

ODT0

116

ODT1

120

BA2

79

C152

0.1u_10V_X5R_04

C156

1U_6.3V_X5R _04

C128

0. 1u _1 6V_Y 5V_04

C157

1U_6.3V_X5R_04

R258 10K_04

C121

2. 2u _16 V_X 5R _0 6

C136

10u_6.3V_X5R_06

C132

*0.1u_16V_Y5V_04

C274

*1 U_ 6. 3V_Y 5 V_04

1.5V

VTT_MEM

3. 3VS

1.5V

1.5V

VTT_MEM

1.5V

3. 3VS

3.3VS3, 7,8 ,9 ,1 0, 11,1 2, 13, 14 , 1 5, 16 ,2 1

3. 3VS

VTT_MEM19

M_A_DQS4#4

1.5V4, 5,19 ,2 1

M_A_DQS6#4

M_A_DQS5#4

M_A_DQS7#4

M_C LK_ DD R34

M_A_DQS04

M_A_BS14

M_ODT34

M_A_RAS#4

SMBCLK07,10

DDR 3_D RAMR ST#4

M_C LK_ DD R3#4

M_A_WE#4

M_A_CAS#4

M_A_BS04

M_C LK_ DD R24

M_ODT24

M_A_BS24

M_CKE24

M_CKE34

M_CS3#4

M_A_DQ[63:0] 4

M_C LK_ DD R2#4

SMBDAT07, 10

M_CS2#4

M_A_DM14

M_A_A[15:0]4

M_A_DM34

M_A_DQS14

M_A_DM24

M_A_DQS0#4

M_A_DM54

M_A_DQS24

M_A_DM64

M_A_DM74

M_A_DM44

M_A_DQS44

M_A_DQS34

M_A_DQS54

M_A_DQS64

M_A_DM04

M_A_DQS1#4

M_A_DQS74

M_A_DQS2#4

M_A_DQS3#4

D03

SO -DI MM 0

M_A_DQ29

M_A_DQ4

M_A_DQ3

M_A_DQ2

M_A_DQ1

M_A_DQ34

M_A_DQ33

M_A_DQ32

M_A_DQ31

M_A_DQ30

M_A_DQ40

M_A_DQ39

M_A_DQ37

M_A_DQ36

M_A_DQ35

M_A_DQ46

M_A_DQ45

M_A_DQ44

M_A_DQ43

M_A_DQ42

M_A_DQ41

M_A_DQ28

M_A_DQ50

M_A_DQ49

M_A_DQ38

M_A_DQ47

M_A_DQ55

M_A_DQ54

M_A_DQ53

M_A_DQ52

M_A_DQ51

M_A_DQ58

M_A_DQ57

M_A_DQ56

M_A_DQ6

M_A_DQ5

M_A_DQ48

M_A_DQ59

M_A_DQ63

M_A_DQ62

M_A_DQ61

M_A_DQ60

M_A_DQ12

M_A_DQ11

M_A_DQ9

M_A_DQ8

M_A_DQ7

M_A_DQ16

M_A_DQ15

M_A_DQ14

M_A_DQ13

M_A_DQ10

M_A_DQ19

M_A_DQ18

M_A_DQ17

M_A_DQ21

M_A_DQ23

M_A_DQ0

M_A_DQ22

M_A_DQ27

M_A_DQ26

M_A_DQ25

M_A_DQ24

M_A_DQ20

CL OSE TO SO -DIM M_ 0

SA0_DIM0

M_A_DM6

M_A_DM7

SA1_DIM0

M_A_DM2

M_A_DM1

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM0

M_A_A9

M_A_A6

M_A_A5

M_A_A7

M_A_A8

M_A_A3

M_A_A4

M_A_A14

M_A_A0

M_A_A1

M_A_A2

M_A_A13

M_A_A10

M_A_A12

M_A_A11

M_A_DQS1

M_A_DQS0

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS1#

M_A_DQS0#

M_A_DQS7

M_A_DQS6

M_A_DQS4#

M_A_DQS3#

M_A_DQS2#

M_A_DQS7#

M_A_DQS6#

M_A_DQS5#

M_A_A15

Sheet 6 of 29

DDRIII SO-DIMM_0

Schematic Diagrams

B.Schematic Diagrams

DDRIII SO-DIMM_0 B - 7

Page 8

Schematic Diagrams

FSLB

167MHz

200MHz

01

11

10

PM_STPPCI#

CLK_ICH

1. 5 V S3 ,5, 8 , 11 ,21

FSLC

CLKICH 48

R68 10K_04

C69

0.1u_16V_Y5V_04

C72

0.1u_16V_Y5V_04

FSLC

C78

*1 0u _6 . 3V _ X 5R _ 0 6

FSLB

C85

*0.1u_16V_Y5V_04

C82

1u _1 0V _ Y 5V _ 06

R81

*1 0K_ 04

R78 33_04

L18

*HCB1608KF-121T25_short

C60

*10u_6.3V_X5R_06

R74 10K_04

L20

*HCB1608KF-121T25_short

R82 33_04

U6

9V R S4 33 8

X2

1

X1

2

VDDR EF

3

REF0_2X/FSLC

4

SD A TA

5

SC LK

6

VDDPCI_ 3 .3

7

ITP _ EN /PC ICLK_F0_2X

8

FSLB/PCILK1_2X

9

CLKREQA#/PCICLK2 _2X

10

GND PCI11GN D25

12

vS E L _P CI / 2 5M _ PC IC L K 3_ 2x

13

VDD 2514VDD 48

15

vSATA_SEL/U SB _48Mhz_2x

16

G ND48

17

CLKREQB#

18

DOT96 _ LRS/SRC4 _LRS

19

DOT96 #_L RS /SR C4#_LRS

20

VDD_CORE_ 1.5

21

L CD 1 00 _L R S

22

LCD 100#_LRS

23

GNDLCD24GNDSATA

25

SATA#_LRS

26

SATA_LRS

27

SR C3#_LRS

28

SRC3 _LRS

29

VDDSRC _LVIO

30

PC I _S T O P #_ 3. 3

31

SR C2#_LRS

32

SRC2 _LRS

33

GNDSRC

34

SR C1#_LRS

35

SRC1 _LRS

36

C P U _ST OP #_ 3. 3

37

CPU_ ITP# /SR C0#_LRS

38

CPU_ ITP/SRC0 _LRS

39

VDD_CORE_ 1.5

40

VDDC PU _L V IO

41

CPU1#_LRS

42

CPU1 _LRS

43

GNDC PU

44

CPU0#_LRS

45

CPU0 _LRS

46

CLKPW RGD/PD#_3.3

47

GNDR E F48THERM AL PAD

49

R87 33_04

R64 10K_04

C58

27 p_ 50 V _N PO _0 4

R95 10K_04

X1

F S X8 L_ 14 .31 81 8M Hz

1 2

C73

0.1u_16V_Y5V_04

C62

0.1u_16V_Y5V_04

R69

10 K_0 4

C59

27 p_ 50 V_N PO _0 4

R63 *0_04

R86 10K_04

C86

0.1u_16V_Y5V_04

R94 33_04

R70

*1 0K _0 4

R71 33_04

R77

10K_04

C68

*0 .1u_16V_Y5V_04

3. 3 V S_ C L K3.3VS

3. 3 VS3.3VS

1.05VS_CLK

1. 0 5V S

3. 3 VS

SM BD AT06, 1 0

CLK _IC H1410

SM BC LK06,1 0

CLK_ DREFSS 3

CLK _IC H488

CLK_ DREFSS# 3

CLK_C PU_H PL 2

CLK_C PU_H PL# 2

CLK_D DR3 REF _CLK# 4

CLK_S ATA# 9

CLK_D DR3 REF _CLK 4

PM _S T PC PU #10

CLK_S ATA 9

PM_STPPCI#10

CLK_ICH_ DMI# 8

ALL_SYS_PWRGD10,15

CLK_C PU_D MI 3

C LK _ P C I E_W LA N # 13

CLK_C PU_D MI# 3

CLK_P CIE_JMC261 1 3

CLK_ICH_ DMI 8

CLK_P CIE_WLAN 13

PC LK _ I C H8

CLK_P CIE_JMC261 # 13

1. 5 V S

PCLK_TPM16

1. 0 5V S2,5,9,10,11,20,22

KBC_PCLK15

3. 3 V S3, 6 ,8, 9 , 10 , 11 ,12 , 13 ,14 , 15 ,16 , 21

1. 5 V S _C L K

CLK_ICH

PMSTP CPU#

CLKREQB#

CLKREQA#

PM_STPP C I#

Fr e que nc y

Hos t C loc kFSLC

100MHz

0 0 133MH z

C83

0.1u_16V_Y5V_04

XT A L _ O U T

XT A L _ I N

C61

0 .1u _1 6V _ Y 5V _ 04

C87

*1 u_ 10 V _Y 5 V _0 6

C L KR EQ A#

L21

*HCB1608KF-121T25_short

10 m ils

PLAC E CRYS TAL WITHIN

500 MILS OF C K505

XT A L _ O U T

XT A L _ I N

PMSTPCPU#

D03

C L KR EQ B#

FSLB

Sheet 7 of 29

IDT Clock

IDT CLOCK

B.Schematic Diagrams

B - 8 IDT CLOCK

Page 9

Tigerpoint Part A-B

Z0810

PERR#

SERR#

STOP#

F R AME#

TRD Y#

PLO CK#

F LAS H_SE L 1

F LAS H_SE L 0

GPIO22

Zd if f = 9 0 Ohm ? 5%

sig nal / space : 5 / 6 m ils

USB Sig nal Gro up

INTB#

INTF#

INTA#

INTC#

REQ#1

IRDY#

TRD Y#

PLOCK#

PCI_ PME#

Zo = 50 Ohm ? 5%

signal : 5 mils

Le ng t h < 50 0 m il to r e s is tor

LAY OUT NOTE:

USB0 USB Port 0

USB1 USB Port 1

USB2 USB Port 2

USB3 Bul etoo th

USB4 3G (PCI E Mi ni Car d)

USB5 Co mb o

Bule too th +WLAN

USB6 N.C.

USB7 CCD

Zdiff = 100 O h m ? 0%

signal / space : 4 / 7 m ils

PCIE Signal Group

IRDY#

INTD#

RSVD0 2

PCIRST#

ST OP#

FLA SH_SE L0

FLA SH_SE L1

LAYOUT NOTE:

< 500 mils to TPT b all

T7

R240 *10K_ 04

1 O F 6

Tigerpoint

PCI

U13A

NM10 -EXP RES S

AD0

B22

AD1

D18

AD2

C17

AD3

C18

AD4

B17

AD5

C19

AD6

B18

AD7

B19

AD8

D16

AD9

D15

AD10

A13

AD11

E14

AD12

H14

AD13

L14

AD14

J14

AD15

E10

AD16

C11

AD17

E12

AD18

B9

AD19

B13

AD20

L12

AD21

B8

AD22

A3

AD23

B5

AD24

A6

AD25

G12

AD26

H12

AD27

C8

AD28

D9

AD29

C7

AD30

C1

AD31

B1

C/ BE0#

H16

C/ BE1#

M15

C/ BE2#

C13

C/ BE3#

L16

PAR

A5

PME#

C22

PLO CK#

A8

FRAME#

A16

S TR AP0#

D11

RSVD01

K9

REQ 1#

G16

RSVD02

M13

GPIO1

C9

PIRQ A#

B2

PIRQ B#

D7

PIRQ C#

B3

PIRQ D#

H10

PIRQ E#/GPIO2

E8

PIRQ F#/GPIO3

D6

PIRQ G#/ GPIO4

H8

PIRQ H#/ GPIO5

F8

REQ 2#

A20

GNT2#

E16

GNT1#

A18

TRD Y#

A10

SERR#

B11

IRDY#

B7

PCIRST#

A23

PCICLK

J12

DEVS EL#

B15

GPIO22

C15

GPIO17/ STRAP2#

A2

STOP#

F14

PERR#

D10

GPIO48/ STRAP1#

G14

T8

R236 *1K_0 4

INTE#

PCI-E

DMI

USB

Tigerp o int

2 O F 6

U13B

NM10-EX PRESS

DMI2 TX N

U23

DMI1 TX N

T24

DMI1 TX P

T25

DMI2 RXN

T19

OC0#

D4

OC2#

D3

OC3#

D2

OC1#

C5

OC4#

E5

OC5#/GPI O29

E6

OC6#/GPI O30

C2

DMI_ CL KP

W24

DMI_ CL KN

W23

DMI_IRCO MP

J22

DMI_ ZCOMP

H24

PETP4

N24

PETN4

N25

PERP4

P18

PERN4

P17

PETP3

M21

PETN3

L22

PERP3

L24

PERN3

L23 PE TP2

K25 PETN 2

K24 PER P2

M19

PERN2

M18

PETP1

J24

PETN1

J23

PERP1

K22

PERN1

K21

DMI3 TX P

V23

DMI3 TX N

V24

DMI3 RXP

V20

DMI2 TX P

U24

DMI2 RXP

T18

DMI1 RXP

T20

DMI1 RXN

T21

DMI0 TX P

P20

DMI0 TX N

P21

DMI0 RXP

R24

DMI0 RXN

R23

CLK48

F4

US BRBI AS#

G3

US BR BI AS

G2

OC7#/GPI O31

C3

USBP 7 P

N2

USBP7N

N1

USBP 6 P

M5

USBP6N

M6USBP 5 P

L3USBP5N

L2USBP4P

K2

USBP4N

K1

USBP 3 P

K5

USBP3N

K6

USBP 2 P

J3

USBP2N

J2

USBP 1 P

H2

USBP1N

H3

USBP 0 P

H6

USBP0N

H7

DMI3 RXN

V21

INTH#

INTG#

PERR#

RN11

8.2K_8P4R_04

1

2

3456

7

8

R233 10K_04

RN9

8.2K_8P4R_04

1

2

3456

7

8

REQ#2

R118 8.2K _04

R239 *1K_0 4

C107 0.1u_10V _X7R_04

SERR#

R109 8.2K _04

GPIO22

RN2

8.2K_8P4R_04

1

2

3456

7

8

DE VSEL#

FRAME#

RN12

8.2K_8P4R_04

1

2

3456

7

8

R235 1K_04

RN3

8.2K_8P4R_04

1

2

3456

7

8

C269 0.1u_10V _X7R_04

R111

24. 9_1%_04

R231 22.1_1%_04

C268 0.1u_10V _X7R_04

C103 0.1u_10V _X7R_04

RN 8

10K_8P4R_04

1

2

3456

7

8

T28

PCI _ P ME#

R244 *0_04

3.3VS

3.3V

3. 3V

1.5VS

PCL K_I CH7

PME#13, 15

3.3V2, 10,11,12, 13,15,17, 19, 20,21,22

3.3VS3,6, 7,9,10, 11,12,13, 14, 15,16,21

PCI E_TX P1_WLAN13

1.5VS3,5, 7, 11,21

USB_PN1 13

DMI_ICH_MT_ IR0 _DN3

CLK _ICH_DMI7

PCI E_TX N1_WLAN13

USB_PN4 13

CLK _ICH4 8 7

DMI_ICH_MT_ IR1 _DP3

USB_PP0 13

USB_PP5 13

PCIE_RXP1_WLAN13

USB_PP4 13

DMI_ICH_MT_ IR0 _DP3

DMI_ICH_MT_ IR1 _DN3

USB_PP7 13

PCI E _ R XN 1_ WLAN13

PCI E_TX N5_CARD13

USB_PN7 13

CLK _ICH_DMI#7

PCI E_TX P5_CARD13

PCIE_RXP5_CARD13

PCI E _ R XN 5_ C ARD13

USB_PN5 13

DMI_ICH_IT_M R0_ DN3

USB_PN0 13

DMI_ICH_IT_M R0_ DP3

DMI_ICH_IT_M R1_ DP3

DMI_ICH_IT_M R1_ DN3

RSVD01

USB_OC#0_1_2 17

USB_PP2 17

USB_PP1 13

USB_PN2 17

DMI_ICH_MT_ IR2 _DP3

DMI_ICH_MT_ IR2 _DN3

DMI_ICH_MT_ IR3 _DN3

DMI_ICH_IT_M R2_ DN3

DMI_ICH_MT_ IR3 _DP3

DMI_ICH_IT_M R3_ DN3

DMI_ICH_IT_M R2_ DP3

DMI_ICH_IT_M R3_ DP3

STR AP 0#

Z0803

Z0804

INTA#

INTC#

INTD#

GPIO1

INTE#

I N TF#

INTG#

INTH#

TOP BLOCK SWAP OVERRIDE

USB_RBIAS

STR AP0#

RSVD01

3. 3VS_PRIME_VCC3

RSVD02

1

GPIO1

INTB#

Z0806

3. 3VS_PRIME_VCC39, 10, 11

Z0808

Z0807

Z0809

1

0

SP I

FLASH_SEL1

LPC

FLASH_SEL 0

PC I

0

MODE

1

1

GPIO4 8/ST RAP 1 #GPI O 17/ S TRAP 2 #

DE VSEL#

REQ#1

REQ#2

USB_OC#7

USB_OC#3

USB_OC#4

USB_OC#5

USB_OC#2_6

Sheet 8 of 29

Tigerpoint Part A-B

Schematic Diagrams

B.Schematic Diagrams

Tigerpoint Part A-B B - 9

Page 10

Schematic Diagrams

Z0901

KB C_G A20 #

H_FERR#

H_FERR#

3.3VS_PRIME_VCC38, 1 0 , 1 1

3.3VS_PR I ME_ VC C 3

KBC_ R ST#

DBG STR P_ SE TUP

H_THERMTRIP#

THE SV_DETECT

KB C_R ST#

LPC_SIRQ

KBC_GA20#

3.3VS

R213 24.9_1%_04

R59 60.4_1%_04

R220

10K_04

R93 60.4_1%_04

3 OF 6

Tigerpoint

HOST

SATA

U13C

NM10-EXPRESS

SATA0RXN

AE 6

SATA0RXP

AD6

SATA0TXN

AC7

SATA0TXP

AD7

SATA1RXN

AE 8

SATA1RXP

AD8

SATA1TXN

AD9

SATA1TXP

AC9

SATA_CLKN

AD4

GPIO36

AD23

A20M#

Y20

CPUSLP#

Y21

IGNNE#

Y18

INIT3_3V#

AD2 1

INIT#

AC2 5

INTR

AB 24

FERR#

Y22

NMI

T17

RC I N #

AC2 1

SERI R Q

AA 16

SMI #

AA 21

STPCL K#

V18

TH E RM T R IP #

AA 20

RSVD 0 3

R12

RSVD 0 4

AE 20

RSVD 0 5

AD17

RSVD 0 6

AC15

RSVD 0 7

AD18

RSVD 0 8

Y12

RSVD 0 9

AA 10

RSVD 1 0

AA 12

RSVD 1 1

Y10

RSVD 1 2

AD15

RSVD 1 3

W10

RSVD 1 4

V12

RSVD 1 5

AE 21

RSVD 1 6

AE 18

RSVD 1 7

AD19

RSVD 1 8

U12

RSVD 1 9

AC17

RSVD 2 0

AB 13

RSVD 2 1

AC13

RSVD 2 2

AB 15

RSVD 2 3

Y14

RSVD 2 4

AB 16

RSVD 2 5

AE 24

RSVD 2 6

AE 23

RSVD 2 7

AA 14

RSVD 2 8

V14

RSVD 2 9

AD16

SA TA_CL KP

AC4

SATAR B IA S#

AD1 1

SATAR BI AS

AC1 1

SATALED#

AD2 5

RSVD 3 1

AB 10

A20GA TE

U16

RSVD 3 0

AB 11

R99 10K_04

RN 6

10K_8P4R_04

1

2

3456

7

8

1.05VS

3.3VS

KBC_GA20# 15

SA TA_LED # 1 2

H_INIT# 2

H_A20M# 2

H_FERR# 2

H_INTR 2

H_NMI 2

H_SMI# 2

LPC_SIRQ 15,16

H_ STPC L K# 2

1. 0 5V S2,5,7,10,11,20,22

3. 3 V S3,6,7,8,10,11,12,13,14,15,16,21

SA TA TXP0 1 2

CL K_ SATA 7

CL K_ SATA# 7

SA TA TXN 0 1 2

SA TARXP 0 12

SA TARXN 0 12

KB C_R ST# 15

H_THERMTRIP# 2

H_CP USLP# 2

SATA Signal Group

Zdif f = 92 Ohm ? 0%

s ignal / s p ace : 4 / 5.5 m i ls

LPC_SIRQ

H_THERMTRIP#

R 1 04 1K _0 4

H_IGNNE#

H_IGNNE#

LAYOUT NOTE:

Zo = 50 Ohm ? 5%

signal : 5 m ils

Len gth < 500 mil to r esis t or

Place resietor close to TPT

SA TA_LED #

SATA_LED #

Sheet 9 of 29

Tigerpoint Part C

B.Schematic Diagrams

Tigerpoint Part C

B - 10 Tigerpoint Part C

Page 11

Tigerpoint Part D

Q1

MTN7002ZHS3

G

DS

SU SBL19,20,21

G FX_PW RG D

D03

H SPI_SC LK15

HSPI_C E#15

HS PI_MSO15

H SPI_MS I15

PLTRST#

ICH _ RT CR ST

IC H_ SY NC #

BKLTSEL 1#

Z1007

Z1005

KBC _ SWI#

SMLALERT#

IC H_SPKR

LCD_PID0

DBG_STRAP_DET

KBC _ SMI#

IC H_ IN TV RMEN

KBC _ RSMRS T#

SMLINK1

IC H_SM BD AT0

PC IE_W AKE#

CONFIG_MODE#

IC H_ R TCX1IC H_ R TCX1

IC H_SM BC LK0

SU SCLK

GPIO8

BATLO W #

KBC_CLKR UN#

AZ_SYNC

PM _STPPCI#_ R

AZ_SDOUT

IC H_ R I

SMLINK0

H_DPRSTP#

BR DID 2

LAN_RST#LAN_RST#

H_DPSLP#

BR DID 1

SU SC#

N M10_GPIO11

IMVP6_PWRG D_R

IC H_ R TCR ST

FP_R ST#

KBC _SMI#

LCD_PID0

GPIO9

GPIO0

IC H_ R TCX2IC H_ R TCX2

GPIO13 KBC _ SCI#

IC H_ SM BCL K0

IC H_SM BDAT0

KBC_SWI #

KBC _SCI#

IC H_ PW RO K

AZ_SDOUT

AZ_SY NC

SM _ INT RU DE R#

ICH _ PW RO K

LD RQ0#

IC H_ SM BC LK 0

SMBCLK0

SMBDAT0

IC H_ SM BD AT0

BKLTS EL1#

ICH _P W RO K

H_D PRSTP#

CONFIG_MODE#

PLTR ST#

ICH _S P KR

KBC_R SMR ST#

ICH_S YNC#

LD R Q 0 #

KBC_ C LK RU N#

BRD ID1

GPIO 0

BRD ID2

SMLIN K0

SMLIN K1

BATLOW#

H_DPSLP#

SUSC LK

SUS C#

ALL_S YS_PW R GD

ICH_RI

PCIE_WA KE#

NM10_GP IO11

SMLALER T#

GPIO 9

FP_RST#

GPIO8

PLTRS T#

PM _DPR SL PVR

C 67 *0.1u_16V_Y 5V _04

R 120 2.2K_04

T4

R22 3 10K_ 0 4

X6 *MC-146_32.768K Hz

1 4

32

R227 10K_04

D3 *CDBU00340

AC

RN 1

10K_8P4R_04

1

2

3456

7

8

R98 *56_04

C26 1

22p_50V_NPO_04

R168

1K_04

U5C

74LVC08PW

9

10

8

147

R 229 *10K_04

R21 5 10K_ 0 4

R221 *1K_04

R 107 *1K_04

R 226 *10K_04

R 237 10K_04

R23 2 1K _04

R61 *100K_04

R 214 *0_04

R88 330K_0 4

PJ4

8mil

1 2

U5D

74LVC 08PW

12

13

11

147

R 121 2.2K_04

C 270 *10p_50V_NPO _04

R11 6 *1 K_ 0 4

R 115 *10mil_short

U5A

74LVC08PW

1

2

3

147

RN 10

10K_8P4R_04

1

2

3456

7

8

U5B

74LVC 08P W

4

5

6

147

R 225 *10K_04

S

D

G

Q5A

MTD N 70 02 Z H S6 R

2

61

R23 8 1K _04

R54 *10mil_short

R 108 10K_04

R 117 2.2K_04

C 63 *150P_50V_NPO_04

R 241 *10mil_short

C

A

A

D14

BAT54 CS3

1

2

3

R219 *1K_04

R102 1M_04

RN 7

10K_8P4R_04

1

2

3456

7

8

R 212 10M_04

R21 7 10K_ 0 4

R92 10K_ 0 4

C21 5

1u_10V_Y 5V_06

R103 20K_1%_04

X7 MC-306_32.768KHz

1 4

32

T27

S

D

G

Q5B

MTD N 700 2 Z H S6 R

5

34

R62 *56_04

R83 *10K_04

C259

22p_50V_N PO_04

R21 6 1K _04

EPROM

Tigerpoint

MISC

RTC

SMB

SPI

LPC

AUDIO

LAN

4 OF 6

U 13D

N M10-EXPR ESS

DPRSTP#

AB23

DPSLP#

AA18

R SVD 31

F20

GPIO8

K18

GPIO9

H19

GPIO 10

M1 7

GPIO 12

A24

GPIO 13

C23

GPIO 14

P5

GPIO 15

E24

DPRSLPVR

AB20

STP_PC I#

Y16

STP_CPU#

AB19

GPIO 24

R3

GPIO 25

C24

GPIO 26

D19

GPIO 27

D20

GPIO 28

F22

CLKR UN #

AC19

GPIO 33

U14

GPIO 34

AC1

GPIO 38

AC23

GPIO 39

AC24

CPUPWRGD/GPIO49

AB22

TH RM #

AB17

VR MP W RG D

V16

MC H_S Y NC #

AC18

PW RBTN#

E21

RI#

H23

SU S_ST AT#/LPC PD #

G22

SU SCLK

D22

SY S_ RES ET #

G18

PLTRST B

G23

WAKE#

C25

IN TR UD ER #

T8

PWR OK

U10

RS MR ST #

AC3

IN T VRM E N

AD3

SPKR

J1 6

SLP_S3 #

H20

SLP_S4 #

E25

SLP_S5 #

F21

BATLOW #

B25

LD RQ1#/GPIO23

AA5

LAD0/FWH0

V6

LAD1/FWH1

AA6

LAD2/FWH2

Y5

LAD3/FWH3

W8

LFRAME#

Y4

HDA_RST#

U2

H DA_SD I0

W2

H DA_SD IN1

V2

H DA_SD IN2

P8

H DA_SD OU T

AA1

H DA_SY NC

Y1

CLK14

AA3

EE _CS

U3

EE _DIN

AE2

EE _DOU T

T6

EE _SHCL K

V3

LAN_CLK

T4

LANR_STSY NC

P7

LAN_RST#

B23

LAN_RXD0

AA2

LAN_RXD1

AD1

LAN_RXD2

AC2

LAN_TXD0

W3

LAN_TXD1

T7

LAN_TXD2

U4

RTCX1

W4

RTCX2

V5

RTCRST#

T5

SM BALER T#/G PIO11

E20

SM BC LK

H18

SM BD ATA

E23

SMLALERT#

H21

SM LINK0

F25

SM LINK1

F24

SP I_MISO

R2

SP I_MOS I

T1

SP I_CS#

M8

SP I_CL K

P9

SP I_A RB

R4

GPIO6

W16

GPIO7

W14

BM_BU SY#/G PIO 0

T1 5

H DA_BIT_ CLK

P6

LD RQ0#

Y8

C96

1u_6.3V_X5R_04

R234 4.7K_04

R 119 2.2K_04

R91 *10mil_short

R60

10K_1%_04

R65

12K_1%_04

VC C_R TC

VD D3

3.3VS

3.3V 3.3V

3.3VS

3. 3V

3. 3 VS

3. 3V S

3.3VS_ PR IME_VC C3

1.05VS

3.3V

3.3VS

R TC-BAT

3.3V

3. 3V

3.3V

TH ER M_ALERT # 1 5

KBC_SM I# 15

H_DPRSTP# 2

AZ _SDIN014

LP C _ A D215,16

PCIE_WA KE# 13

KBC_SC I# 1 5

H_PW R GD 2

AZ_S Y NC3,14

PLTR ST# 2

ICH _S P KR 14

LP C _ A D015,16

AZ_S D OU T3,14

CLK _ IC H147

PM_STPC PU# 7

LP C _ A D315,16

PM_STPPC I# 7

LPC_FR AME #15, 1 6

KB C_RSM RS T# 15

LP C _ A D115,16

KBC_PW RBTN# 15

1.05VS2,5,7,9,11,20,22

AZ _BI TC LK3, 14

AZ _R ST#3, 14

KBC_C LK RUN# 15,16

H_DPSLP# 2

SM BDA T06,7

3.3VS3,6,7,8,9,11, 12,13,14,15,16,21

VCC _RTC11

VDD313,15,16,18,21,23

3.3V2,8, 11,12,13, 15,17,19,20,21,22

GFX _ PW R GD21,22

S U S C # 1 5, 19

KBC_SW I# 15

ALL_SY S_ PW R GD 7 ,15

SB_BLON 12

SM BCLK06,7

S U S B # 1 5, 21

DD R3 _ DR AM_PWR OK 4

1.5V _PW RGD19

ICH _P W RO K 12

ALL_SY S_PW R GD7,15

B U F _P LT _ R S T# 1 3 , 1 5, 16

PLTRS T#2

S4_STATE# 16

N M10_GPIO1113

PO K23

3.3VS _PRIM E_V CC 38,9,11

AZ _SDIN13

1.8VS_PW R GD15

3.3V S_P RIME5,11,15,21

DELAY _ALL_SY S_ PWR GD4,15

L PC S i gn al Gr ou p

Zo = 55 Ohm ? 5%

s ign al : 4 mi ls

Zo = 55 Ohm ? 5%

s ign al : 4 mi ls

HDA Signal Gro up

PC I E P O RT CON F B I T 0

PC I E P O RT CON F B I T 1

RTC Sig nal G ro up

RTCX1,RTCX 2,RTCRST#

Zo = 50 Ohm ? 5%

s ign al : 4 mi ls

Length < 100 0 mils

Clear CMOS

D03 7 /1

?LAYOUT

FOR??? ?WLAN

BOARD ID

DC COUPLING SELET ION

SP KR STUFF R For Safe Mode .

ICH_INTVRMEN

SM_INTRUDER#

D02

R273

1K_04

C 293 2200p_50V_X7R _04

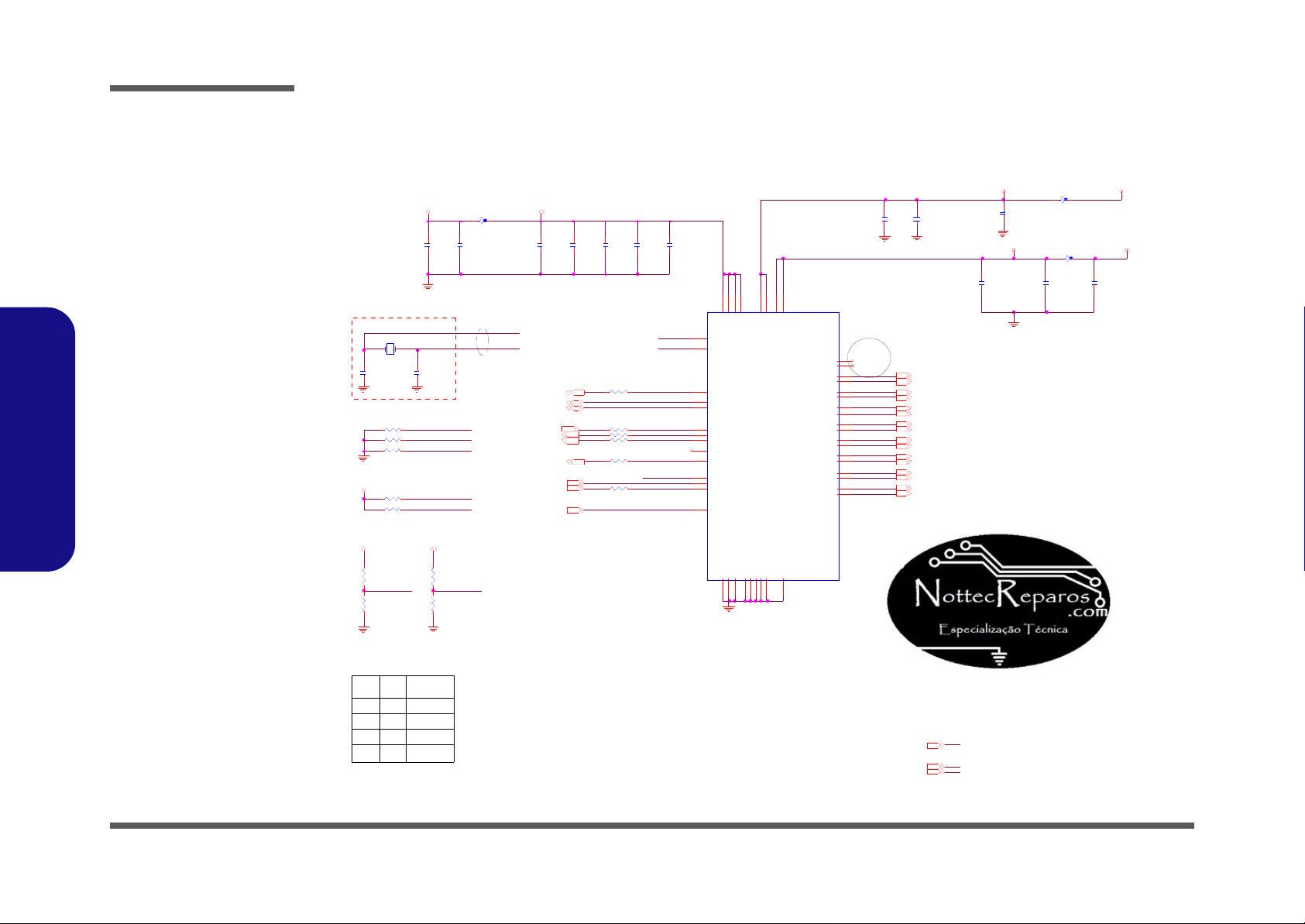

Sheet 10 of 29

Tigerpoint Part D

Schematic Diagrams

B.Schematic Diagrams

Tigerpoint Part D B - 11

Page 12

Schematic Diagrams

R110

10_1%_04

C102

1u_6.3V_X5R_04

L23

*HCB1005KF-121T20_s hort

C113

1u_10V_Y5V_06

C110

1u_6.3V_X5R_04

C97

0 .1u _1 6V_Y 5V _0 4

C114

0 .1u _1 0V_X 5R _ 04

C104

10u_6.3V_X5R_06

3. 3 V5V

3. 3 VS _ PR IME

1. 5 VS

1. 5 VS

1. 0 5V S

1. 5 VS

3.3V

5V S 3. 3 V S

VC C _ R T C

VCC_R TC10

1. 0 5V S2, 5 , 7,9, 1 0, 2 0,2 2

3. 3 V2,8,10,12,13,15 ,17,19,20,21,22

1. 5 V S3, 5, 7 , 8, 2 1

3. 3 V S3,6,7,8,9,10,12,13,14,15,16,21

5V17 ,19,20,21,22

3. 3 V S_ PR IM E5, 1 5, 2 1

5V S12 ,13 , 14,15,16,21

L24

*HC B1608KF-121T25_short

VCC1_05

2mA

L26

*HCB1005KF-121T20_s hort

3. 3 VS _ PR IME_VCC3

VCCSUS3_ 3

3.3 VS_PRIME_VCC38,9,10

VCCDMIPLL

VCC5REF

d03

d0 3

V5REF_SUS

0. 98A

1. 3A

0.1 3A

0.2 9A

6mA

14mA

10mA

10mA

50mA

50mA

VCCSATAPLL

C99

10u_6.3V_X5R_06

C71

1u_10V_Y5V_06

C93

1u_6.3V_X5R_04

C84

0.01u_16V_X7R_04

C112

*1 u_ 6.3 V _X5R _ 04

C111

0 .1u _1 6V_Y 5 V _0 4

POWER

Tig erp oi nt

5 OF 6

U13E

NM 10-EXPR ESS

V C C1 _5 _2

M9

V C C1 _5 _3

M2 0

V C C1 _5 _4

N22

VCC1_05_4

V10

V_CPU_IO

W18

V C C1 _5 _1

AA8

VC C SU S 3 _3 _4

F1

VC C SU S 3 _3 _3

K7

VC C SU S 3 _3 _2

N4

VC C SU S 3 _3 _1

F18

V C C3 _3 _6

T9

V C C3 _3 _5

R10

V C C3 _3 _4

G1 0

V C C3 _3 _3

F10

V C C3 _3 _2

AD13

V C C3 _3 _1

H25

VCC1_05_3

P15

VCC1_05_2

K17

VCC1_05_1

J10

VCCUSBP LL

F6

VCCDMIPLL

Y25

VCCRTC

AE3

VCCSATAPLL

Y6

VCC5 REF _SUS

F5

VC C 5R E F

F12

D8

RB751S-40C2

AC

C100

0 .1u _1 6V_Y 5 V _0 4

C139

*0.1u_10V_X5R_04

C80

*4.7u_6.3V_X5R_06

C138

1 u_ 6. 3 V_ X5 R _ 04

C116

1u_6.3V_X5R_04

C101

0 .1u _1 6V_Y 5V _0 4

C98

*1 u_ 6. 3 V _X 5R _ 04

C260

0 .1u _1 6V_Y 5 V _0 4

C262

0 .01 u_ 16 V_ X7 R _0 4

R124

100_1%_04

C105

0 .1u _1 6V_Y 5V _0 4

C77

*1u_ 10 V_Y5 V_06

VCC1_5

L27

*HC B1608KF-121T25_short

C92

0 .1u _1 6V_Y 5 V _0 4

L22

*HC B1005KF-121T20_short

C115

*1 u_ 6.3 V _X5R _ 04

C95

*1 0u _6. 3V_ X5R _0 6

C89

10u_6.3V_X5R_06

C7 5

*1u_10V_Y5 V_06

L19

*HCB1608KF-121T25_s hort

D20

RB751S-40C2

AC

Tigerpoint

GND

6 OF 6

U13F

N M10 -EXPRESS

VSS59

F2

VSS58

AE 1 3

VSS57

G24

VSS56

AE 2 5

VSS55

AE 1 0

VSS54

AE 1

VSS53

AD 2 4

VSS52

AD 2 0

VSS51

AD 1 0

VSS50

AD 2

VSS49

AC 8

VSS48

AB 8

VSS47

AB 7

VSS46

AB 6

VSS45

AB 4

VSS44

Y24

VSS43

Y2

VSS42

W2 2

VSS41

W1 2

VSS40

V2 5

VSS39

V2 2

VSS38

V1 9

VSS37

V8

VSS36

V7

VSS35

V1

VSS34

T2 2

VSS33

T2

VSS32

R22

VSS31

R14

VSS30

P1 9

VSS29

P1 3

VSS28

P1 1

VSS27

N23

VSS26

N14

VSS25

N13

VSS24

N12

VSS23

N3

VSS22

M11

VSS21

M7

VSS20

L4

VSS19

K2 0

VSS18

K1 9

VSS17

K1 1

VSS16

K8

VSS15

K4

VSS14

H5

VSS13

H4

VSS12

H1

VSS11

G8

VSS10

G4

VSS09

F1 6

VSS08

E1 8

VSS07

B2 4

VSS06

B2 0

VSS05

B1 6

VSS04

B1 0

VSS03

B6

VSS02

A2 5

VSS01

A1

RSVD32

AE 1 6

Sheet 11 of 29

Tigerpoint Part E-F

Tigerpoint Part E-F

B.Schematic Diagrams

B - 12 Tigerpoint Part E-F

Page 13

Panel, HDD, LED

Sheet 12 of 29

Panel, HDD, LED

Z1303

Z1304

R53

0.2_06

R51

0.2_06

LV DD_ EN#

Z1306

Z1305

R 184 0.2_06

INV_BLON

Z1307

C1

10u_6.3V_X5R_06

Q21

*D TC 114 EUA

CE

B

C8

*1u_10V_Y5V_06

R170

220_04

C22 5

0.01u_50V_X7R_04

Q13

*P2003 EVG46 2

5

7 3

1

8

U3

G5243A

VIN

4

VIN

5

EN

3

VOU T

1

GN D

2

U4B

74LVC08PW

4

5

6

147

S

D

G

Q14B

*MTDN7002ZHS6R

5

34

U4A

74 L V C 08 P W

1

2

3

147

U4D

74LVC08PW

12

13

11

147

S

D

G

Q1 4 A

*M TD N 70 0 2ZH S 6R

2

61

POWER LED

LE D 08

C31 0.01u_16V_X7R_04

R58 100K_04

Q12

*MTN7002ZHS3

G

DS

Q2 0

DTC1 14EUA

CE

B

2

C65

*0 .1u _ 16 V _Y 5V_ 04

3

4

R179 *1 00K_04

J _H DD1

323AH2 2 F RT0102CC

S1

S2

S3

S4

S5

S6

S7

P1

P2

P3

P4

P5

P6

P7

P8

P9

P10

P11

P12

P13

P14

P15

BAT LED

31

SG

Y

D15

KPB-30 25Y SGC

1

3

2

4

1

SG

Y

D17

KPB-3025YSGC

1

3

2

4

2

R269

220_04

C56

1u_10V_Y5V_06

3.3VS

C29 2

1u _6.3V_Y5V_0 4

L43

HCB1005KF-121T20

R162

220_04

R272

220_04

4

R66

10 0 K _0 4

C52

0.1u_16V_Y5V_04

C45 0.01u_16V_X7R_04

D16

KP-20 12SGC

AC

R180

*10K_04

R 56 100K_04

R178

*1M_04

C2

0.1u_16V_Y5V_04

R57 10K_04

LE D 06

HDD LED

J_LC D1

88242-3001

112

2

334

4

556

6

778

8

9910

10

111112

12

131314

14

151516

16

171718

18

191920

20

212122

22

232324

24

252526

26

272728

28

292930

30

W LAN / B T LE D

4

123

LED02

LED01

LED04

R177

220_04

LED03

C66

*100 p_ 5 0V_ N P O _04

R55 10K_04

C223

*0.22u_50V_06

R163

220_04

C22 4

*0.1u_50V_Y5V_06

R181

*220_04

C38 0.01u_16V_X7R_04

U4C

74LVC08PW

9

10

8

147

R16 4

220_04

SG

Y

D18

KPB-3025YSGC

1

3

2

4

C48

1u_10V_Y5V_06

C32 0.01u_16V_X7R_04

BACKLIGHT ON CONTROL

3.3V

3.3VS

3. 3 V

3.3V

3. 3 V

5V S

LED

PLVDD

Cl os e to the HDD

Connector.

VLED

3. 3 VS

PIN GND1~2=GND

SATA HDD

VIN

3. 3 V

VLED

PN: 6- 20 -43720-022

323AH22FRT0102C3

PN: 6- 20 -43730-022

194502-1

3.3VS 3.3VS

3. 3 VS

SATAR XN0 9

BKL_EN15

LI D _S W #15

SB_BL ON10

SATAT XP0 9

SATAR XP0 9

SATAT XN0 9

ICH_PW RO K10

VDD 31 0,1 3 , 15 , 1 6,1 8, 2 1 , 23

MCH_BLON3

5V11 ,17,1 9,20,21 ,22

VIN18 , 1 9,2 1,2 2 , 23

3.3VS3,6,7,8,9,10,11,13,14,15,16,21

5VS1 1 ,13,1 4,15,16 ,21

3.3V2,8,10,11,13,15,17 ,19,20,21,22

LVDS-LC LKN3

LVDS-LC LKP3

LCD_BRIGHTNESS15

LVDD_EN 3

LVDS-L1N3

LVDS-L1P3

L_DD C_CL K 3

LV D S - L2 P 3

LV D S - L0 N 3

LV D S - L2 N 3

LV D S - L0 P 3

L_DD C_DAT A 3

BT_EN 13,15

LV D D _EN 3

WL AN_LED# 1 3

WLAN_EN 13,15

SATA_ L ED# 9

LE D_ BA T_CH G 1 5

LED_BAT_FULL 15LED_PWR 15

LED_ACIN 15

D03

D03

R50

0.2_06

R182

0.2_06

R52

0.2_06

R18 3

0.2_06

1A

2A

1A

2A

Z1301

Z1302

3. 3 VS _ LC D

C289

*0.1u _50V_Y5V_0 6

C290

*0.1u _50V_Y5V_0 6

D02

PANEL

VIN

L_D DC_ CL K

L_D DC_ DA T A

INV_BLO N

D0 3

R18 5

0.2_06

LED07 LED10 LED09

5VS

L_ DDC _D A TA

L_ DDC _C LK

LVDD_EN

Schematic Diagrams

B.Schematic Diagrams

Panel, HDD, LED B - 13

Page 14

Schematic Diagrams

Sheet 13 of 29

BTB, 3G, WLAN, BT

D03

UIM_VPP

UIM_DATA

UIM_PWR

UIM_RST

UIM_CLK

3G CARDMINI-PCIE CARD AND Debug Port

UIM_VPP

PME#_ R

R154 *10mil_short

NM10_GPIO11_R

3. 3 V

P N : 6- 20- 84D 0 0-2 26

1-0 81- 40035 2-00 1

P N : 6- 21- 84D 9 0-2 26

8 891 0-5 204 M- 01

BT_ SBD#

Pin#24Pin#2 Pin# 52Pin# 39 , 41

L3 0

F C M10 05 M F- 6 00T 01

C6

*22p_50V_NPO_04

Q7

A O 34 15

G

DS

C201

0. 1u _1 6V_Y 5V _0 4

C151

1u_10V_Y5V_06

C205

*0 .1u_16V_Y5V_04

C5

*22p_50V_NPO_04

R 1 44 *1 0K _0 4

R 135

10_ 06

R1 4.7K_04

(TOP VIEW)

J_ S IM1

91 71 2- 0 090 P

UIM_DATA

7

UIM_VPP

4

UIM_GND

2

UIM_PWR

1

UIM_RST

3

UIM_CLK

5

GNG

GND1

UIM_I/O

6

UI M _ MCMD

8

DETECT_SW

9

GND

GND2

GND

GND3

GND

GND4

C148

1u_6.3V_X5R_04

R 1 38 *0 _0 4

D10

*V1 5AVLC0402

1 2

J_BTB1

QPOF Z34R2 BS02K

112

2

334

4

556

6

778

8

9910

10

111112

12

131314

14

151516

16

171718

18

191920

20

212122

22

232324

24

252526

26

272728

28

292930

30

313132

32

333334

34

L2 8

F C M10 05 M F- 6 00T 01

KE Y

J_3G1

1 -081 -40 03 52-0 01

COEX1

3

COEX2

5

CLKREQ#

7

GND0

9

REF CL K-

11

REF CL K+

13

WA K E #

1

GND1

15

PE T n 0

23

PE T p 0

25

GND2

21

GND3

27

PE R n 0

31

PE R p 0

33

GND4

29

Reserved0

17

Reserved1

19

W_DISABLE#

20

GND12

37

3. 3V AU X _ 3

39

3. 3V AU X _ 4

41

GND13

43

Reserved2

45

Reserved3

47

Reserved4

49

Reserved5

51 LED_WLAN#

44LED_WWAN#

42

GND6

18

UIM_ V PP

16UIM_RESET

14

3.3VAUX_0

2

UIM_ C LK

12UIM_DATA

10

UIM_PW R

8

1. 5V _ 0

6

GND5

4

PERSET#

22

3.3VAUX_1

24

GND7

26

1. 5V _ 1

28

SMB_ CLK

30

SMB_DATA

32

GND8

34

USB_D-

36

USB_ D +

38

GND9

40

LED_ WPAN#

46

1. 5V _ 2

48

GND10

50

3.3VAUX_2

52

GND11

35

R 2 *1 0 mil _s ho rt

C134

*0.1u_16V_Y5V_04

3G 0 1

R128

20 K_1% _0 4

+

C216

22 0U_ 4V _D 2 _D

C146 22p_50V_NPO_04

R157 *0 _04

C147 22p_50V_NPO_04

C154

0. 1u _1 6V_Y 5V _ 04

R 1 26 10 0K _0 4

KEY

J_MINI1

1-081-400352-001

COEX1

3

COEX2

5

CLKREQ#

7

GND0

9

REF CLK-

11

REF CLK+

13

WA K E#

1

GND1

15

PE Tn 0

23

PE Tp 0

25

GND2

21

GND3

27

PE R n0

31

PE R p0

33

GND4

29

Reserved0

17

Reserved1

19

W_DISABLE#

20

GND12

37

3. 3V AU X _ 3

39

3. 3V AU X _ 4

41

GND13

43

Reserved2

45

Reserved3

47

Reserved4

49

Reserved5

51

LE D _ WL AN#

44LED_WWAN#

42

GND6

18

UIM_VPP

16UIM_RESET

14

3.3VAUX_0

2

UIM_CLK

12UIM_ D A TA

10UIM_PW R

8

1.5V_0

6

GND5

4

PERSET#

22

3.3VAUX_1

24

GND7

26

1.5V_1

28

SM B _ CLK

30

SMB_ DATA

32

GND8

34

USB_ D-

36

USB_D+

38

GND9

40

LE D _W P A N#

46

1.5V_2

48

GND10

50

3.3VAUX_2

52

GND11

35

C4

*22p_50V_NPO_04

C160

0.1u_ 16V_ Y5V_0 4

C232 22p_50V_NPO_04

C117

*4.7u_6.3V_X5R_06

R129 10K_04

R 147 *0_ 04

C7

*22p_50V_NPO_04

C185

10u_10 V_Y5V_08

S

D

G

Q6A