Page 1

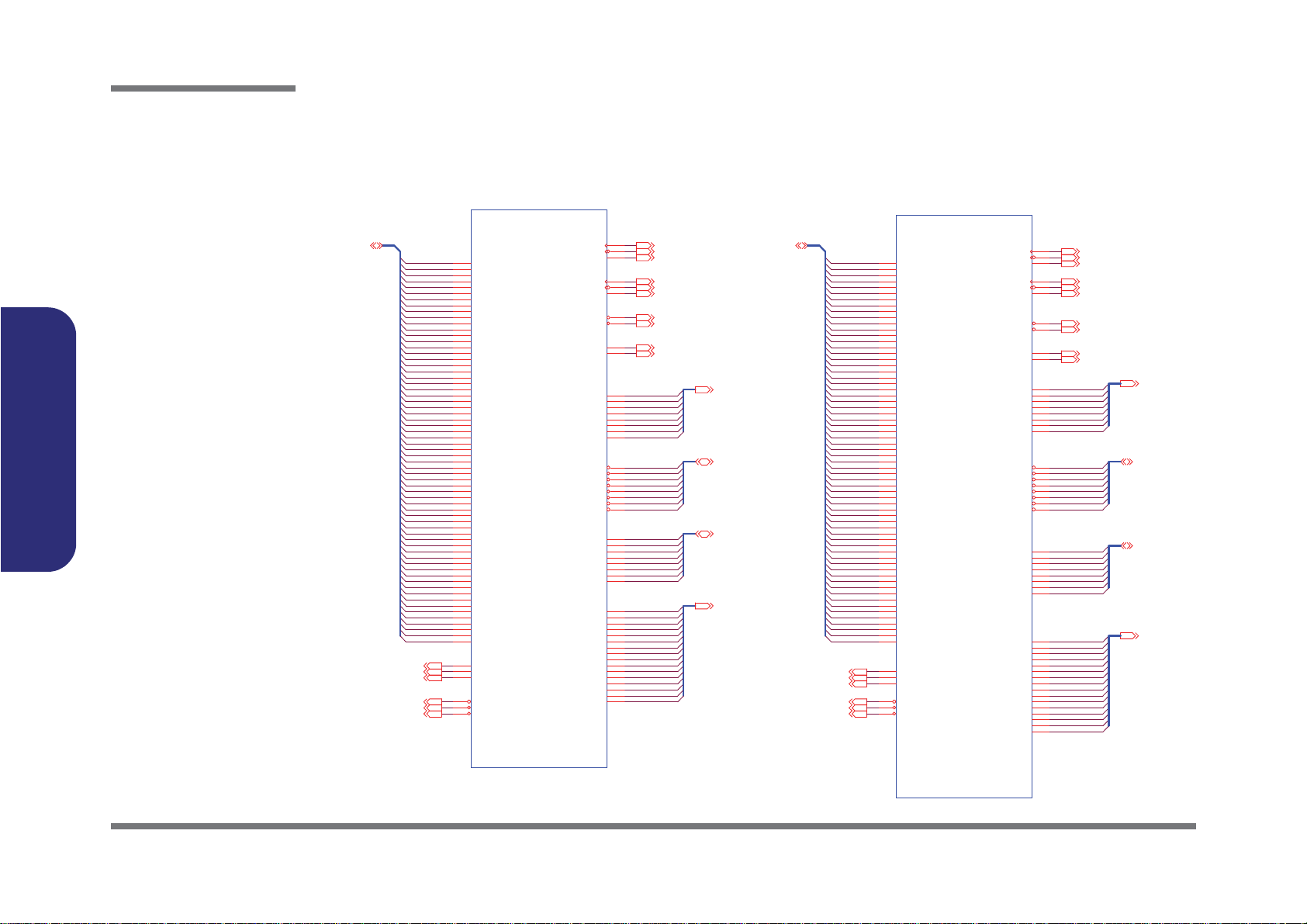

Schematic Diagrams

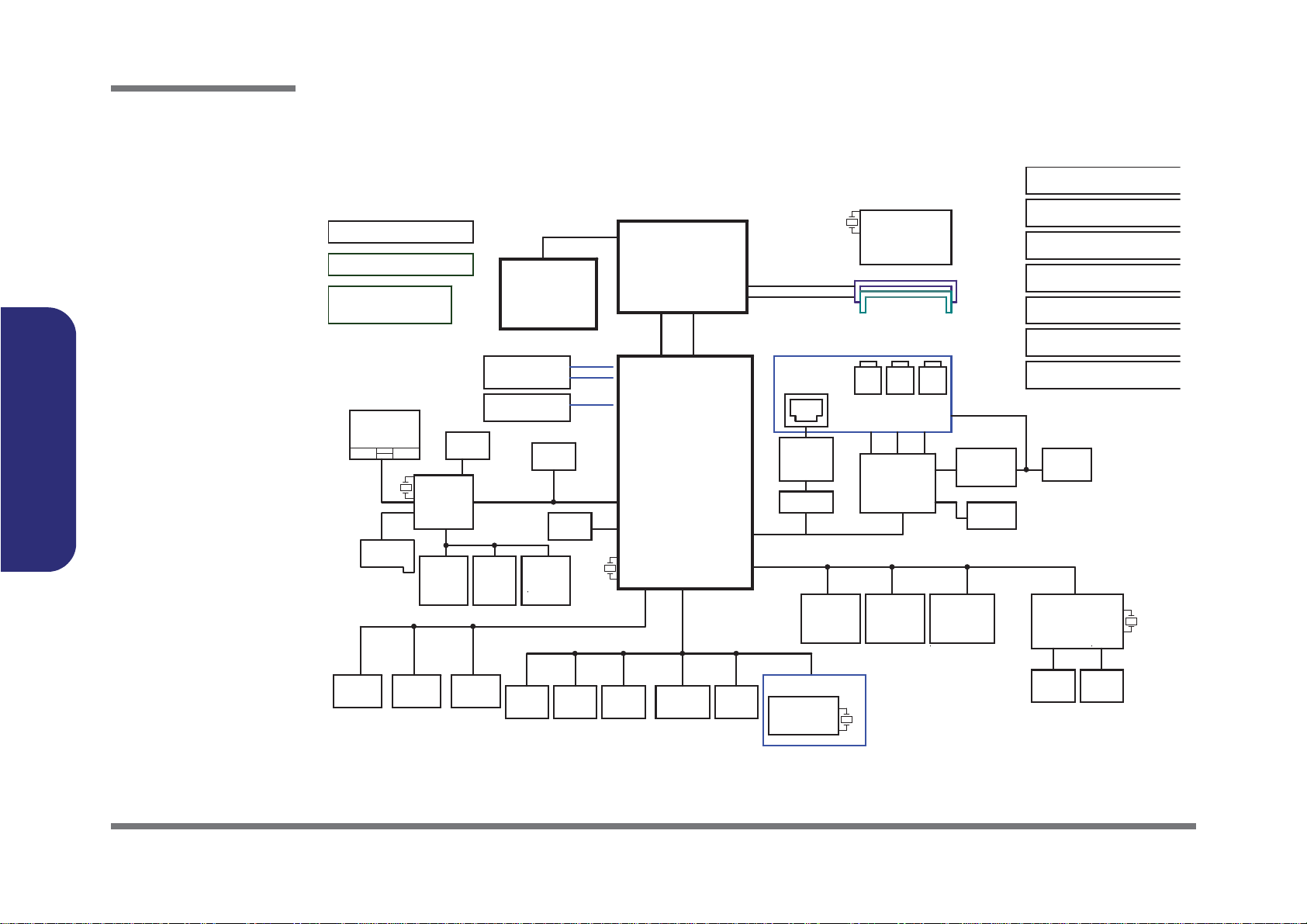

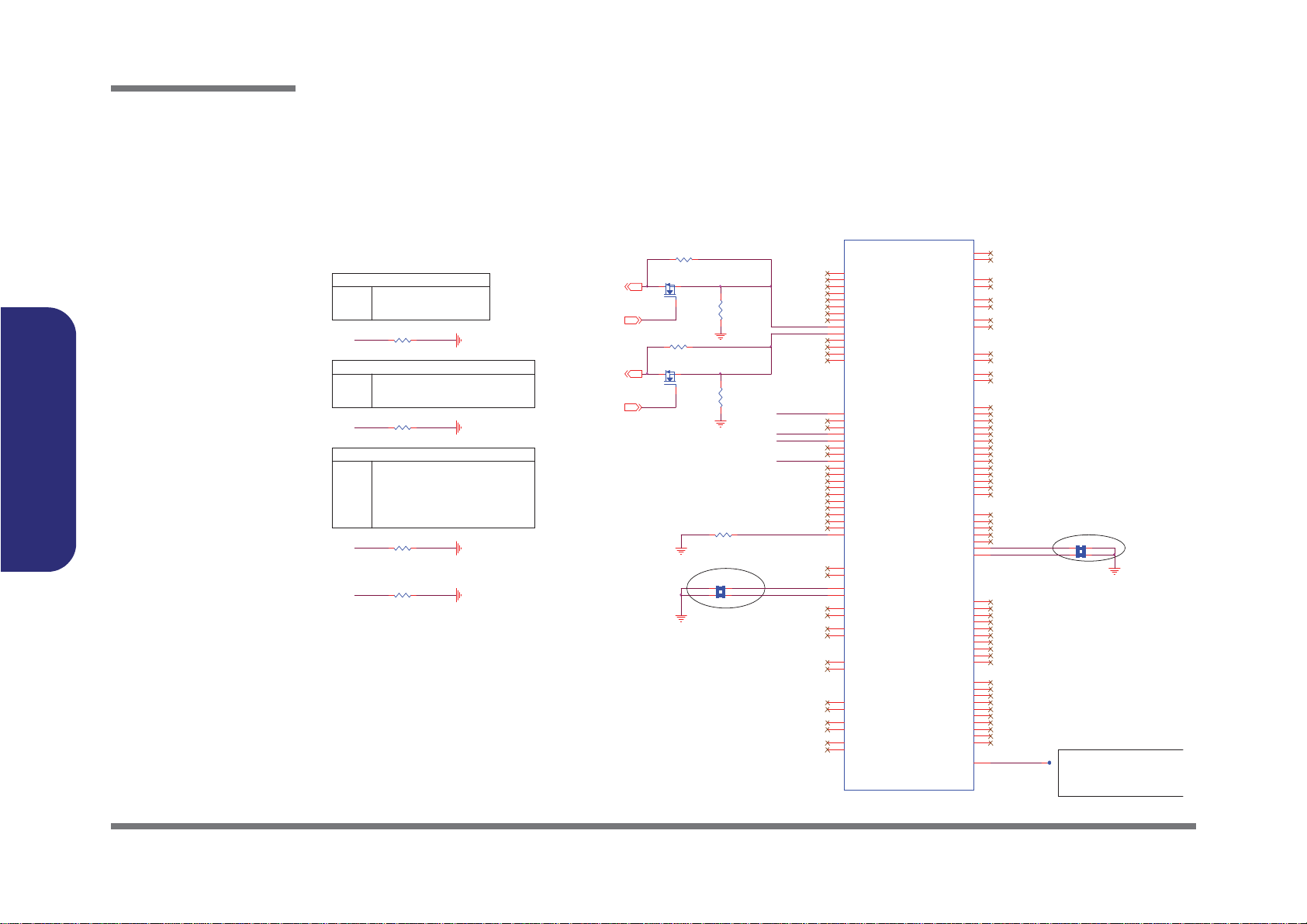

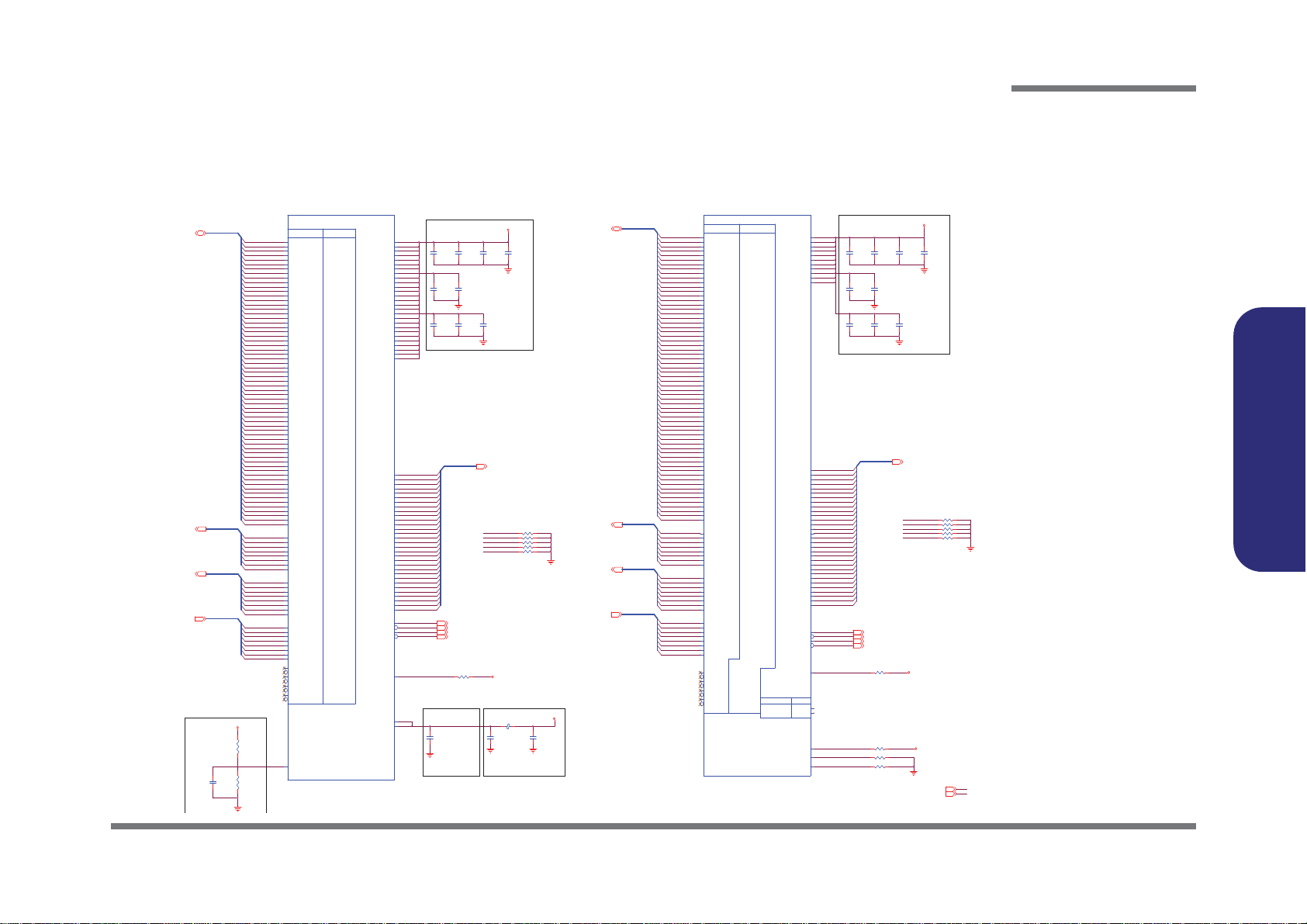

B4100M System Block Diagr am

FingerPrint

(USB2)

(USB4)

12 MHz

LCD CONNECTOR

<8"

TOUCH PAD

CRT CONNECTOR

LPC

CARD

READER

GPU NVDIDA N11x NVVDD

SMART

BATTERY

SO-DIMM1

HP

OUT

INT SPK R

CLICK BOARD

SOCKET

<=8"

PCIE

27x27mm

1071 Ball FCBGA

480 Mbps

DDRIII

SENTELIC

Mini PCIE

SPI

0.5"~5.5"

1"~16"

DDRIII

INT MIC

25

MHz

Arrandale

24 MHz

<12"

FDI

MIC

IN

B4100 (INT SPK L)

128pins LQFP

SO-DIMM2

32.768KHz

(USB11)

Bluetooth

VCORE, 1.1VS_VTT

EC SMBUS

USB PORT

AZALIA LINK

FINGER PRINTER BOARD

(USB10)(USB0)

USB PORT

(USB1)

USB PORT

0.1"~13

eSATA

SYSTEM SMBUS

SATA ODDSATA HDD

BIOS

SPI

LAN

ITE 8502E

<12"

Ibex Peak-M

Platform

Controller

Hub (PCH)

SPDIF

OUT

INT. K/B

Azalia Codec

EC

0.5"~11"

<15"

5V,3V,5VS,3VS,1.5VS,

1.8VS,+1.5S_CPU

1.5V,0.75VS(VTT_MEM)

USB2.0

969 Balls

Nvidia

Optimus N11x

VDD3,VDD5

DMI*4

rPGA989/988

W83L771AWG

32.768 KHz

JMICRO

1.8V, PEX_VDD

MDC CON

AZALIA

MDC

MODULE

RJ-11

SATA I/II 3.0Gb/s

800/1067/1333 MHz

DDR3 / 1.5V

(Optional)

CCD

(USB5)

B4100

(USB9)

NEW CARD

B4100-D03a

REALTEK

ALC272

33 MHz

THERMAL

SENSOR

100 MHz

14*14*1.6mm

PROCESSOR

6-49-C4102-010

SMART

FAN

SLG8SP585

14.318 MHz

Clock Generator

PCIE*8

JMC251

AUDIO BOARD

RJ-45 7IN1

SOCKET

B5100

B4100

(USB8)USB PORTHDMI Connector

TI TPA6017A2

AMP

3G CARD

(USB3)

(Optional)

FBVDDQ

PHONE JACK x3, USB x1,

INT SPK L, RJ-11

AUDIO BOARD

WLAN

VGFX_CORE

Optional

TPM 1.2

AC-IN

FINGER PRINTER BOARD

POWER SWITCH BOARD

http://hobi-elektronika.net

System Block Diagram

B.Schematic Diagrams

Sheet 1 of 49

System Block

Diagram

B - 2 System Block Diagram

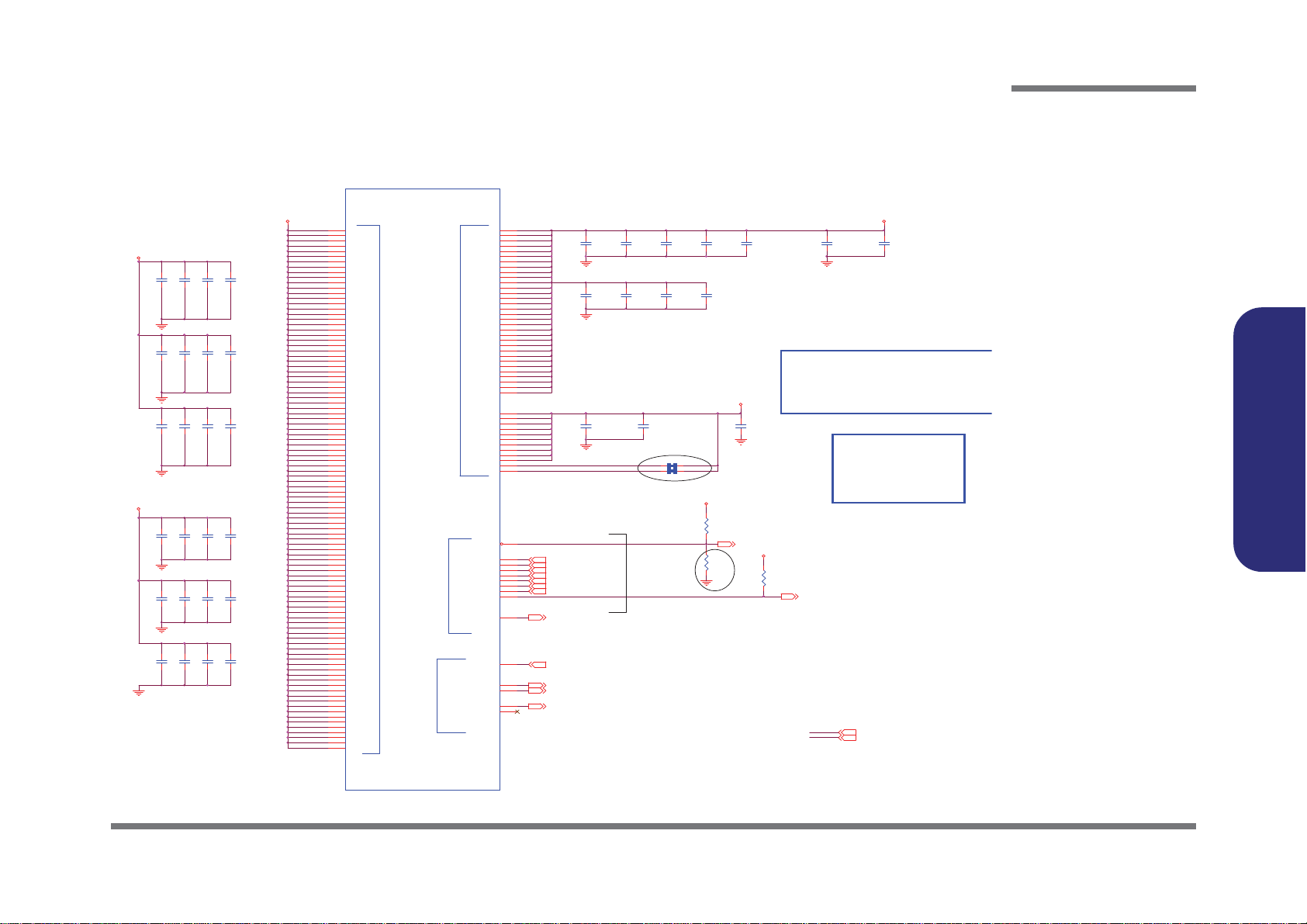

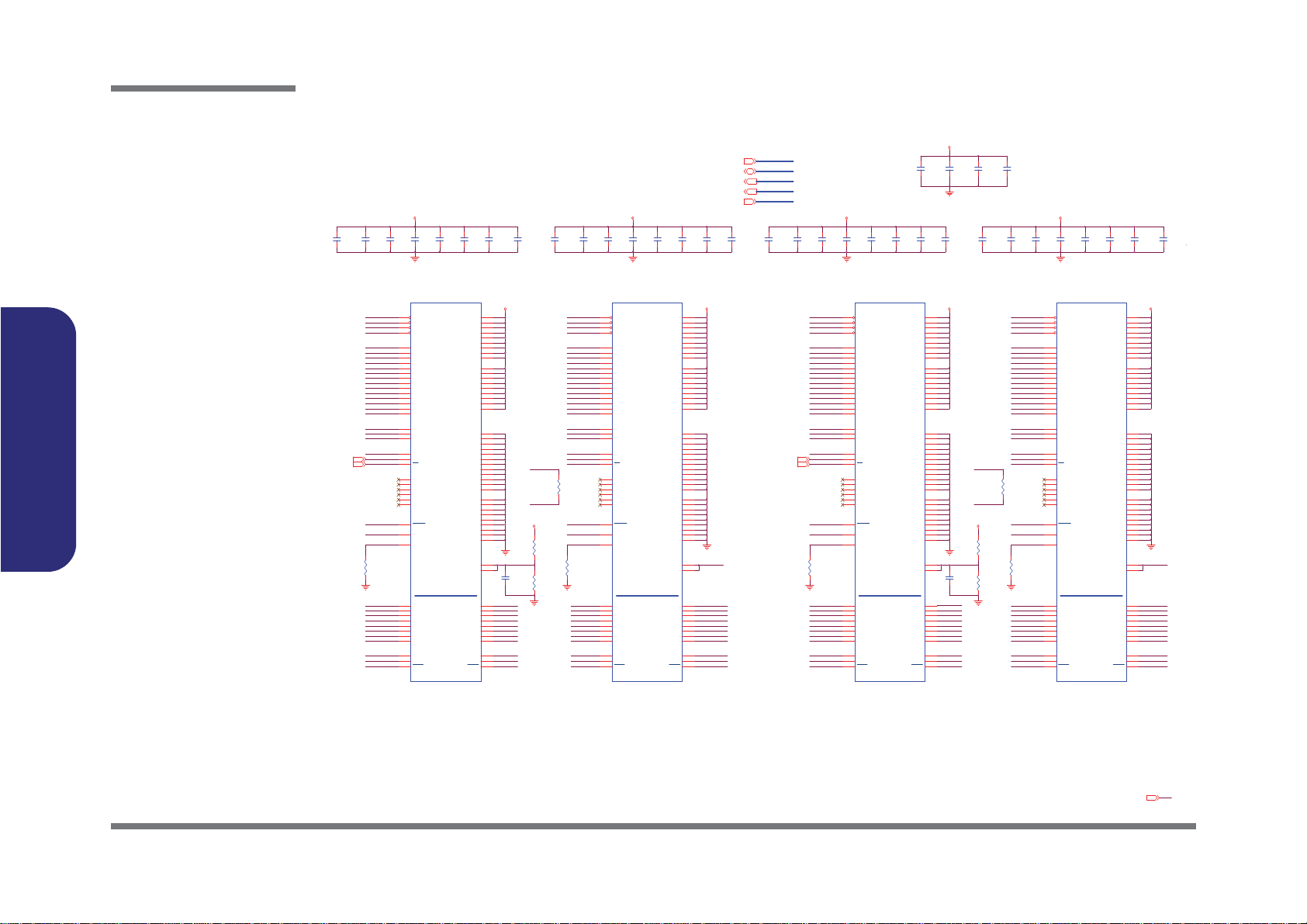

Page 2

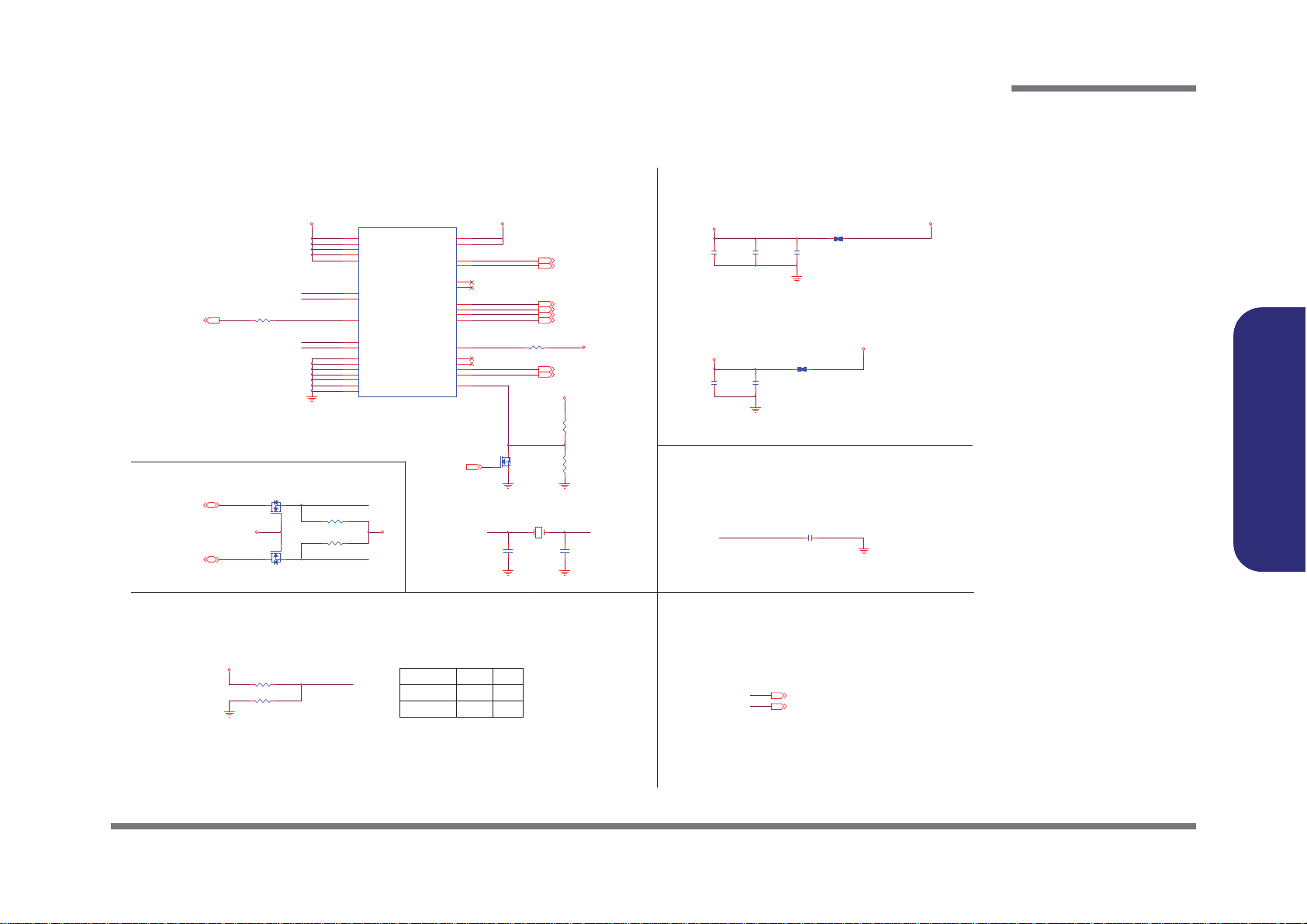

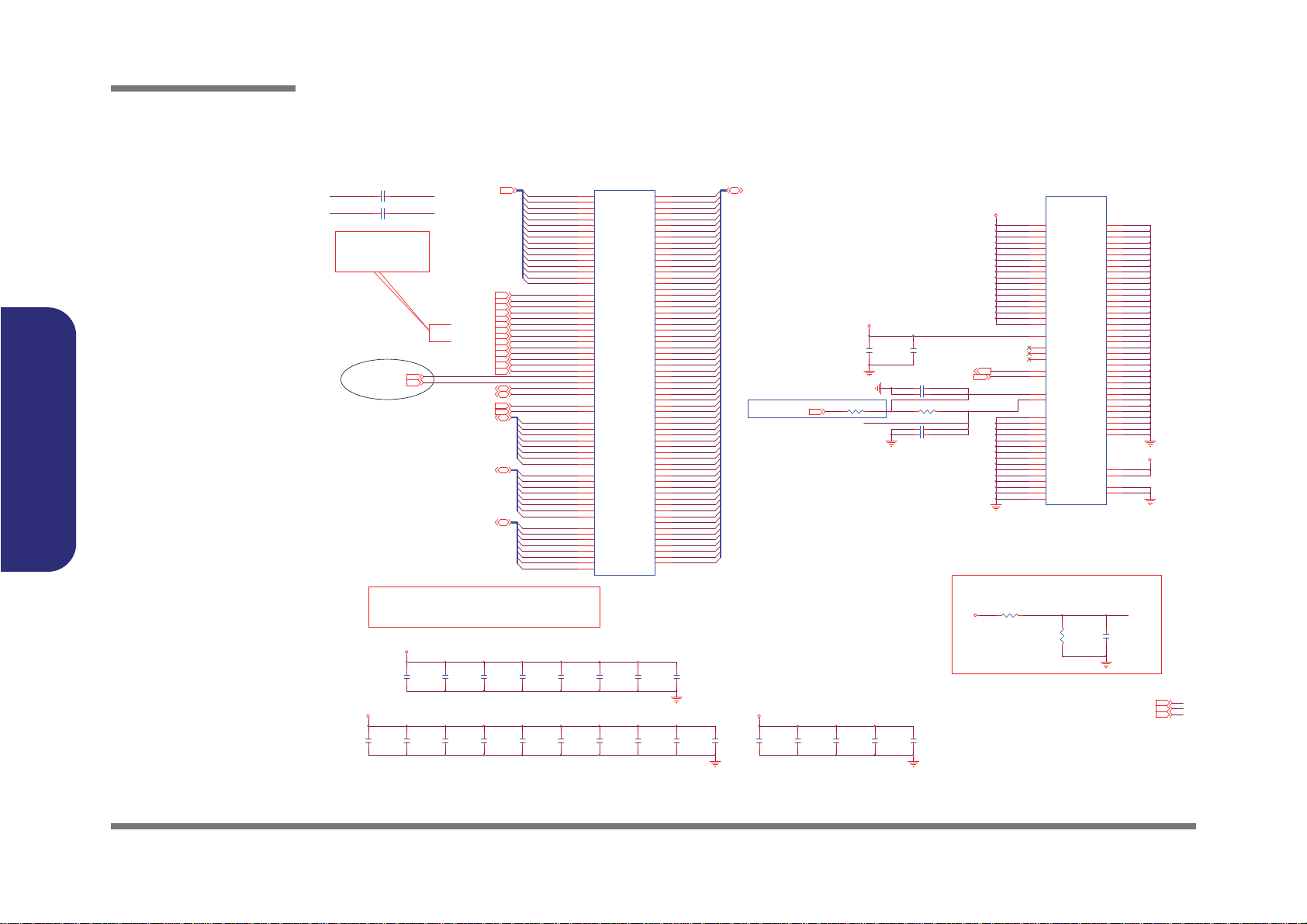

Clock Generator

CLK_SCLK

CLK_SDATA

CLK_SCLK

3.3VS

REF_0/CPU_SEL

CPU_STOP#

REF_0/CPU_SEL

CLK_SDATA

XOU T

REF_0/C PU_SEL

XIN

PR121 2.2K_04

CLK_PWRG D

C483

1U_10V_06

C482

.1U_16V_04

R328

10K_04

X4 F SX8L_14.31818M Hz

12

L33 *HCB1608KF-121T25_32mil_short

PR120 2.2K_04

C436

33p_50V_NPO_04

C435

33p_50V_NP O_04

R322

1M_04

C491

.1U_16V_04

Q37

MTN7002ZHS3

G

DS

L31

*HCB1608KF-121T25_32mil_short

PR117 33_04

PR118 *4.7k_04

PR122 2.2K_04

Q38

MTN7002ZHS3

G

D S

C467

1U_10V_06

C475

.1U_16V_04

U29

SLG8SP585

VDD_DOT

1

VDD_27

5

VDD_SRC

17

VDD_CPU

24

VDD_REF

29

VSS_DOT

2

XTAL_ OU T

27

XTAL_ IN

28

REF_0/CPU_SEL

30

SDA

31

SCL

32

VSS_27

8

VSS_SATA

9

VSS_SRC

12

VSS_CPU

21

VSS_REF

26

VDD_SRC_I/O

15

VDD_CPU_I/O

18

DOT_96

3

DOT_96#

4

27M

6

27M_SS

7

SRC_1/SATA

10

SRC_1#/SATA#

11

SRC_2

13

SRC_2#

14

CPU_STOP#

16

CPU_1

20

CPU_1#

19

CPU_0

23

CPU_0#

22

CKPWRGD/PD#

25

GND

33

PR119 10k_04

Q36

MTN7002ZHS3

G

D S

C437 *10P_50V_04

3.3VS

CLK_VCC1

CLK_VCC2CLK_VCC 1

XOU T

XIN

3.3VS

3.3VS3.3VS

1.1VS_VTT

CLK_VCC2

CLK_BUF_BCLK_N 20

CLK_BUF_BCLK_P 20

CLK_BUF_DOT96_N 20

CLK_BUF_REF1420

CLK_BUF_DOT96_P 20

3.3VS

CLKEN#42

1.1VS_VTT 4,6,7,19,20,21,24,25,26, 38,40,41,42

SMB_DATA10,11, 20

SMB_CLK10,11, 20

CLKGEN POWER

CLK_SATA# 20

CLK_SATA 20

CLK_PCIE_ICH# 20

CLK_PCIE_IC H 20

1(0.7V-1.5V)

0(default)

PIN_30 CPU_1CPU_0

EMI

EMI Capactior

VDD_I/O can be

ranging from

1.05V to 3.3V

0.1uF near the every power pin

0.1uF near the every power pin

??

9LRS3197

CLOCK GENERATOR

CPU_SEL_During CK_PEWGD Latch Pinl

SMBus

100MHz100MHz

133MHz133MHz

3.3VS 10,11,12,13,19,20, 21,22,23,24,25, 26,28,29,30,31,32, 34,35,36,41,42,45

Sheet 2 of 49

Clock Generator

http://hobi-elektronika.net

Schematic Diagrams

B.Schematic Diagrams

Clock Generator B - 3

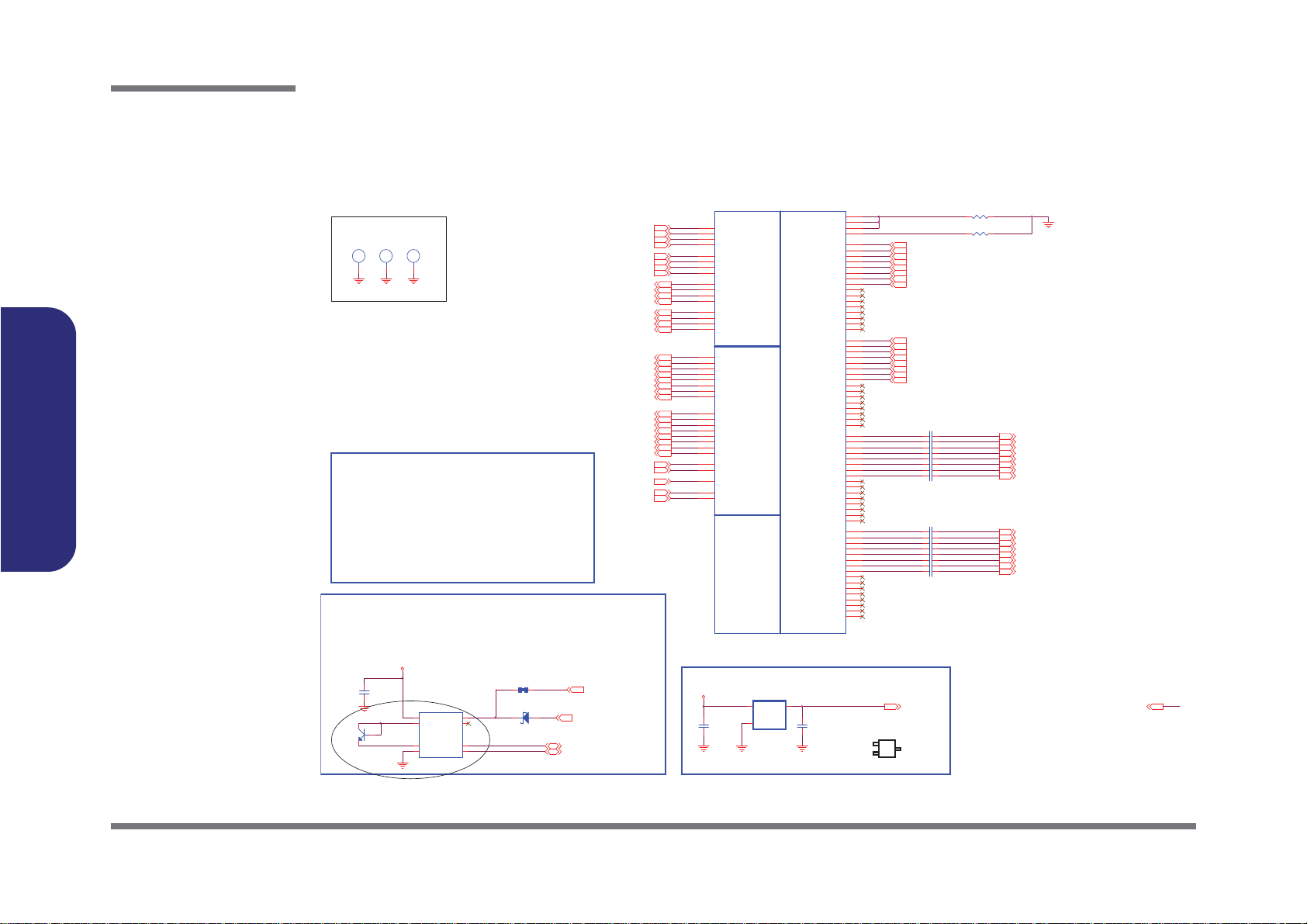

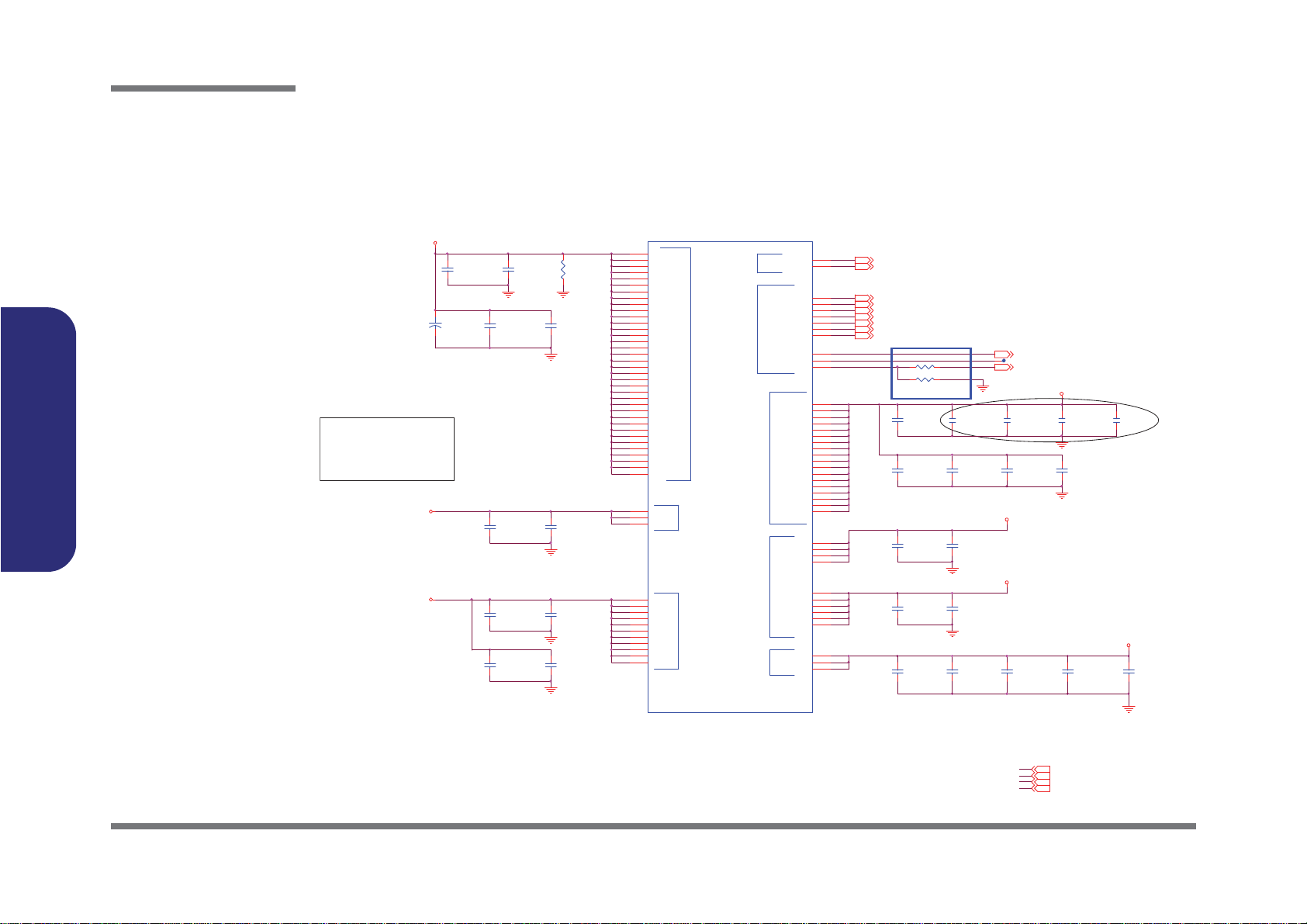

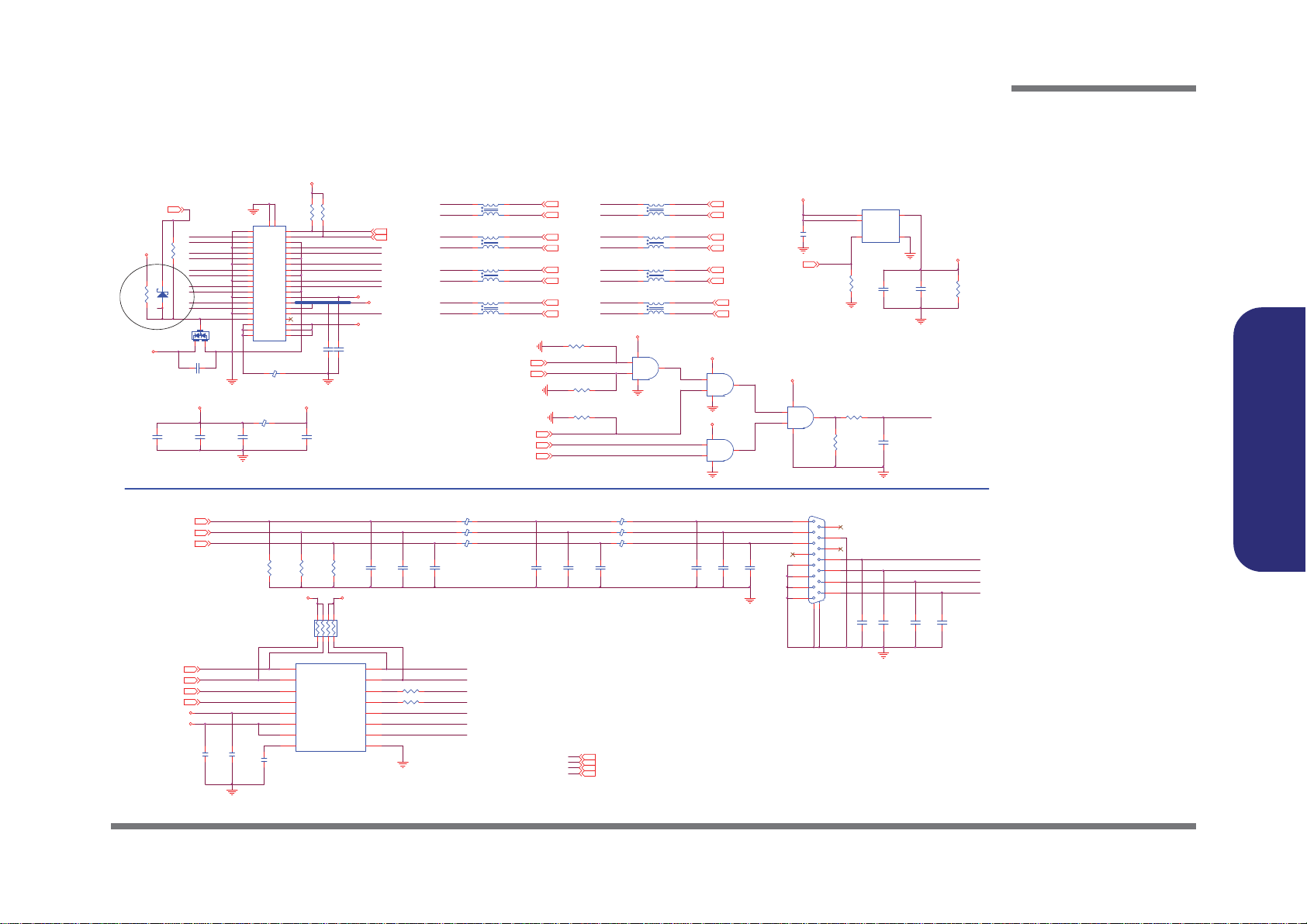

Page 3

Schematic Diagrams

Sheet 3 of 49

CPU 1/7

(DMI, PEG, FDI)

PLACE NEAR U29

H17

H8_0D4_4

H10

H8_0D4_4

H18

H8_0D4_4

Cost down

THERM_VOLT 35

3

2

1

3.3V

PEG_IRCOMP_R

EXP_RBIAS

R221 * 10mil_short

CRIT_TEMP_REP# 24

Analog Thermal Sensor

C538 .1U_10V_X7R_04

C550 .1U_10V_X7R_04

R429 750_1%_04

C548 .1U_10V_X7R_04

C547 .1U_10V_X7R_04

R427 49.9_1%_04

C546 .1U_10V_X7R_04

C542 .1U_10V_X7R_04

C543 .1U_10V_X7R_04

C541 .1U_10V_X7R_04

C540 .1U_10V_X7R_04

C549 .1U_10V_X7R_04

C536 .1U_10V_X7R_04

C537 .1U_10V_X7R_04

C539 .1U_10V_X7R_04

C545 .1U_10V_X7R_04

PCI EXPRESS -- GRAPHICS

DMI Intel(R) FDI

U40A

MOLEX 479890142

DMI_R X#[0]

A24

DMI_R X#[1]

C23

DMI_R X#[2]

B22

DMI_R X#[3]

A21

DMI_RX[0]

B24

DMI_RX[1]

D23

DMI_RX[2]

B23

DMI_RX[3]

A22

DMI_TX#[0]

D24

DMI_TX#[1]

G24

DMI_TX#[2]

F23

DMI_TX#[3]

H23

DMI_TX[0]

D25

DMI_TX[1]

F24

DMI_TX[3]

G23

DMI_TX[2]

E23

FDI_ TX#[ 0]

E22

FDI_ TX#[ 1]

D21

FDI_ TX#[ 2]

D19

FDI_ TX#[ 3]

D18

FDI_ TX#[ 4]

G21

FDI_ TX#[ 5]

E19

FDI_ TX#[ 6]

F21

FDI_ TX#[ 7]

G18

FDI_TX[0]

D22

FDI_TX[1]

C21

FDI_TX[2]

D20

FDI_TX[3]

C18

FDI_TX[4]

G22

FDI_TX[5]

E20

FDI_TX[6]

F20

FDI_TX[7]

G19

FDI_FSYNC[0]

F17

FDI_FSYNC[1]

E17

FDI_INT

C17

FDI_ LSY NC [ 0]

F18

FDI_ LSY NC [ 1]

D17

PEG_ICOMPI

B26

PEG_ICOMPO

A26

PEG_RBIAS

A25

PEG_RCOMPO

B27

PEG_RX#[0]

K35

PEG_RX#[1]

J34

PEG_RX#[2]

J33

PEG_RX#[3]

G35

PEG_RX#[4]

G32

PEG_RX#[5]

F34

PEG_RX#[6]

F31

PEG_RX#[7]

D35

PEG_RX#[8]

E33

PEG_RX#[9]

C33

PEG_RX#[10]

D32

PEG_RX#[11]

B32

PEG_RX#[12]

C31

PEG_RX#[13]

B28

PEG_RX#[14]

B30

PEG_RX#[15]

A31

PEG_RX[0]

J35

PEG_RX[1]

H34

PEG_RX[2]

H33

PEG_RX[3]

F35

PEG_RX[4]

G33

PEG_RX[5]

E34

PEG_RX[6]

F32

PEG_RX[7]

D34

PEG_RX[8]

F33

PEG_RX[9]

B33

PEG_RX[10]

D31

PEG_RX[11]

A32

PEG_RX[12]

C30

PEG_RX[13]

A28

PEG_RX[14]

B29

PEG_RX[15]

A30

PEG_TX#[0]

L33

PEG_TX#[1]

M35

PEG_TX#[2]

M33

PEG_TX#[3]

M30

PEG_TX#[4]

L31

PEG_TX#[5]

K32

PEG_TX#[6]

M29

PEG_TX#[7]

J31

PEG_TX#[8]

K29

PEG_TX#[9]

H30

PEG_TX#[10]

H29

PEG_TX#[11]

F29

PEG_TX#[12]

E28

PEG_TX#[13]

D29

PEG_TX#[14]

D27

PEG_TX#[15]

C26

PEG_TX[0]

L34

PEG_TX[1]

M34

PEG_TX[2]

M32

PEG_TX[3]

L30

PEG_TX[4]

M31

PEG_TX[5]

K31

PEG_TX[6]

M28

PEG_TX[7]

H31

PEG_TX[8]

K28

PEG_TX[9]

G30

PEG_TX[10]

G29

PEG_TX[11]

F28

PEG_TX[12]

E27

PEG_TX[13]

D28

PEG_TX[14]

C27

PEG_TX[15]

C25

Q28

*2N3904

B

E C

C552 .1U_10V_X7R_04

U19

*W83L771AWG

VDD

1

D+

2

D-

3

THER M

4

GND

5

ALERT

6

SDATA

7

SCLK

8

C551 .1U_10V_X7R_04

3.3V

DMI_TXP221

DMI_TXP121

DMI_TXP021

DMI_TXN221

DMI_TXN121

DMI_TXN021

DMI_TXP321

DMI_RXN221

DMI_RXN121

DMI_RXN021

DMI_TXN321

DMI_RXP221

DMI_RXP121

DMI_RXP021

DMI_RXN321

FDI_INT21

FDI_FSYNC121

FDI_FSYNC021

DMI_RXP321

PEG_RX#2 13

FDI_LSYNC121

FDI_LSYNC021

PEG_RX7 13

PEG_RX#4 13

PEG_RX5 13

PEG_RX#7 13

PEG_RX#1 13

PEG_RX4 13

PEG_RX#0 13

PEG_RX#3 13

PEG_RX2 13

PEG_RX#6 13

PEG_RX3 13

PEG_RX#5 13

PEG_RX6 13

PEG_RX0 13

PEG_TX3 13

PEG_TX6 13

PEG_RX1 13

PEG_TX#3 13

PEG_TX0 13

PEG_TX#2 13

PEG_TX#5 13

PEG_TX7 13

PEG_TX4 13

PEG_TX#7 13

PEG_TX1 13

PEG_TX#0 13

PEG_TX5 13

PEG_TX#1 13

PEG_TX2 13

PEG_TX#6 13

FDI_TXN121

FDI_TXN021

PEG_TX#4 13

FDI_TXN521

FDI_TXN421

FDI_TXN321

FDI_TXN221

FDI_TXP121

FDI_TXP021

FDI_TXN721

FDI_TXN621

FDI_TXP521

FDI_TXP421

FDI_TXP321

FDI_TXP221

3.3V4,12,13,17,19,20,21,23,24,26,28, 29, 31, 32,33, 36, 38,39, 40,43

FDI_TXP721

FDI_TXP621

20 mil

D11 *RB751V

AC

1:2 (4mils:8mils)

PM_EXTTS#_EC 4

On Board DDR3 Thermal Sensor

PROCESSOR 1/7 ( DMI,PEG,FDI )

It applies to Auburndale and Clarksfie ld discrete graphic designs.

If discrete graphic chip is used for Auburndale, VAXG (GFX core) rail can be connected

to GND if motherboard only supports disc rete graphics and also in a common

motherboard design if GFX VR is not stuffed. On the othe r hand, if the VR is stuffed,

VAXG can be left floating in a common mothe rboard design (Gfx VR keeps VAXG from

floating).

In addition, FDI_RXN_[7:0] and FDI _RXP_[7:0] can be left floating on the PCH.

FDI_TX[7:0] and FDI_TX#[7:0] can b e left floating on the Auburndale.

The GFX_IMON, FDI_FSYNC[0], FDI_F SYNC[1], FDI_LSYNC[0], FDI_LSYNC[1 ], and

FDI_INT signals should be tied to GND (thr ough 1K ? % resistors) in the co mmon

motherboard design case. Please no t that if these signals are left floating, there are n o

functional impacts but a small amount of power (~15 mW) maybe wasted. VAXG_SENSE

and VSSAXG_SENSE on Auburndale can be left as no connect.

DPLL_REF_SSCLK and DPLL_R EF_SSCLK# can be connected to G ND on Auburndale

directly if motherboard only suppo rts discrete graphics. In a common motherboar d

design, these pins are dr iven via PCH (even if Graphics is disabled by BIOS) thus no

external termination is required.

PULL HIGH? ? ? IBEX? PAGE21

C328

*.1U_1 6V_04

CPU

C321

.1U_16V_04

C303

.1U_16V_04

Q27

G711ST9U

OUT1VCC

2

GND

3

SMC_CPU_THER M 20,35

SMD_CPU_THER M 20,35

PEG_TX_2

PEG_TX_1

PEG_TX#_3

PEG_TX_4

PEG_TX#_2

PEG_TX#_5

PEG_TX#_7

PEG_TX_6

PEG_TX#_6

PEG_TX#_1

PEG_TX#_4

PEG_TX_7

PEG_TX#_0

PEG_TX_0

PEG_TX_5

PEG_TX_3

http://hobi-elektronika.net

CPU 1/7 (DMI, PEG, FDI)

B.Schematic Diagrams

B - 4 CPU 1/7 (DMI, PEG, FDI)

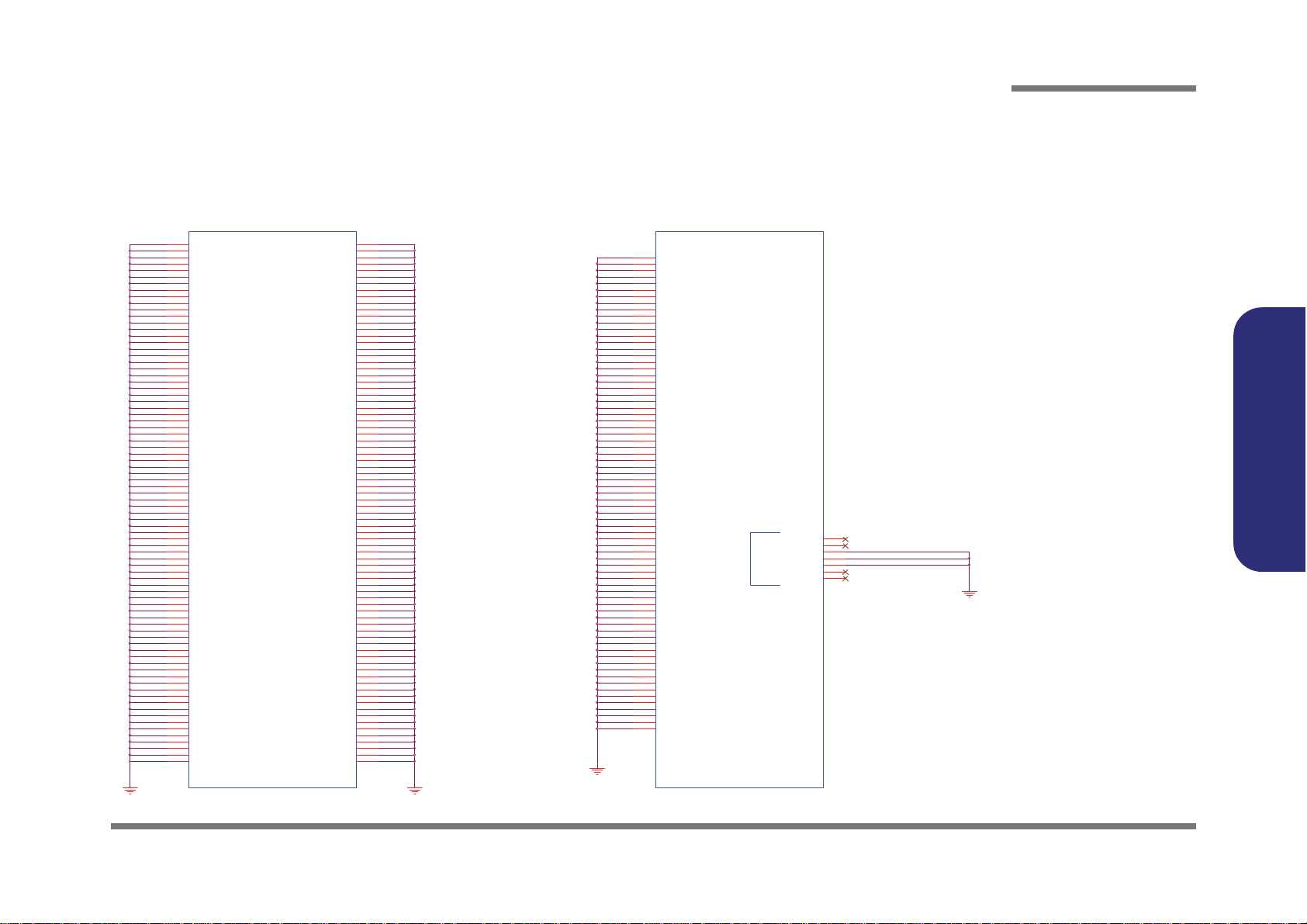

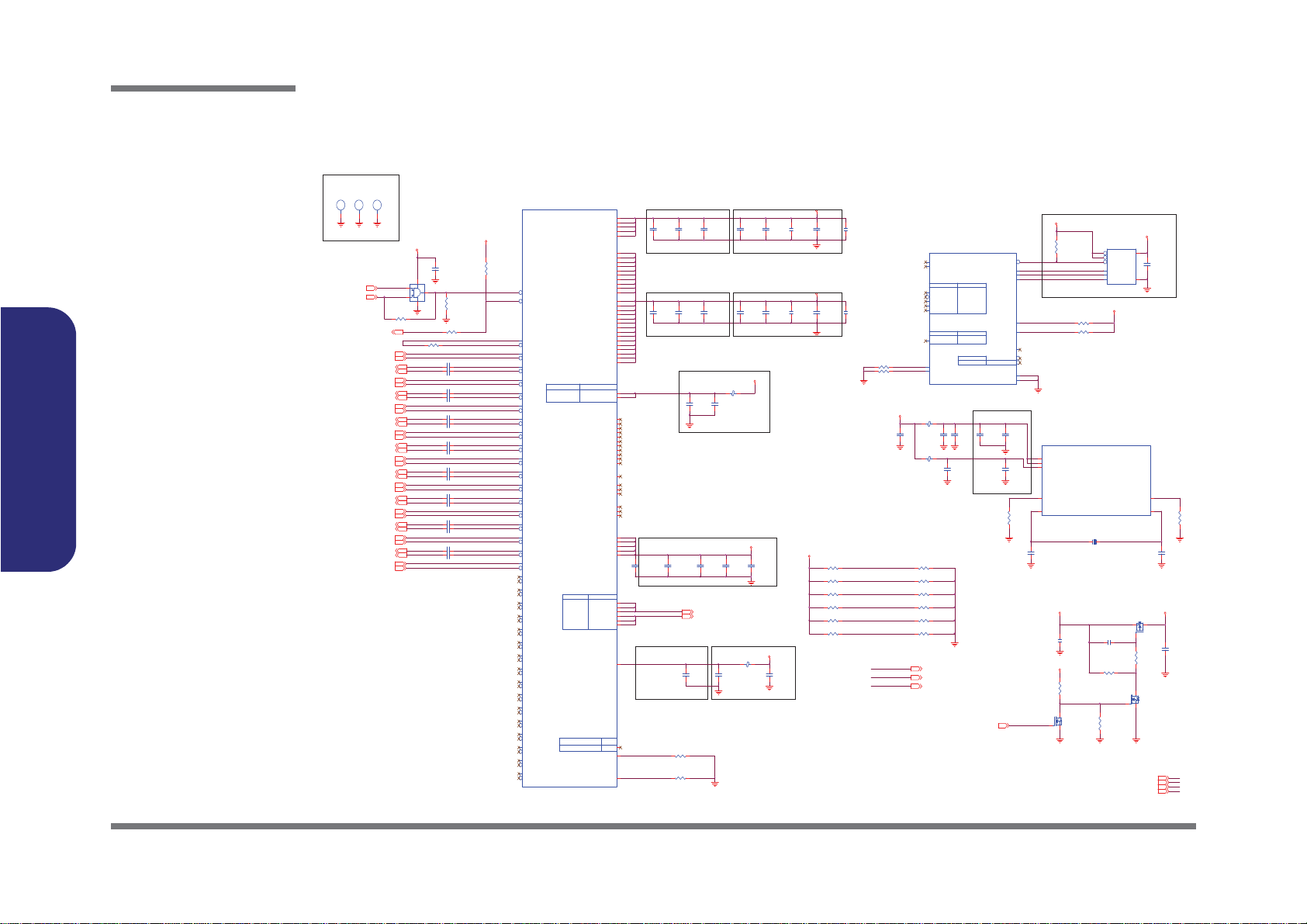

Page 4

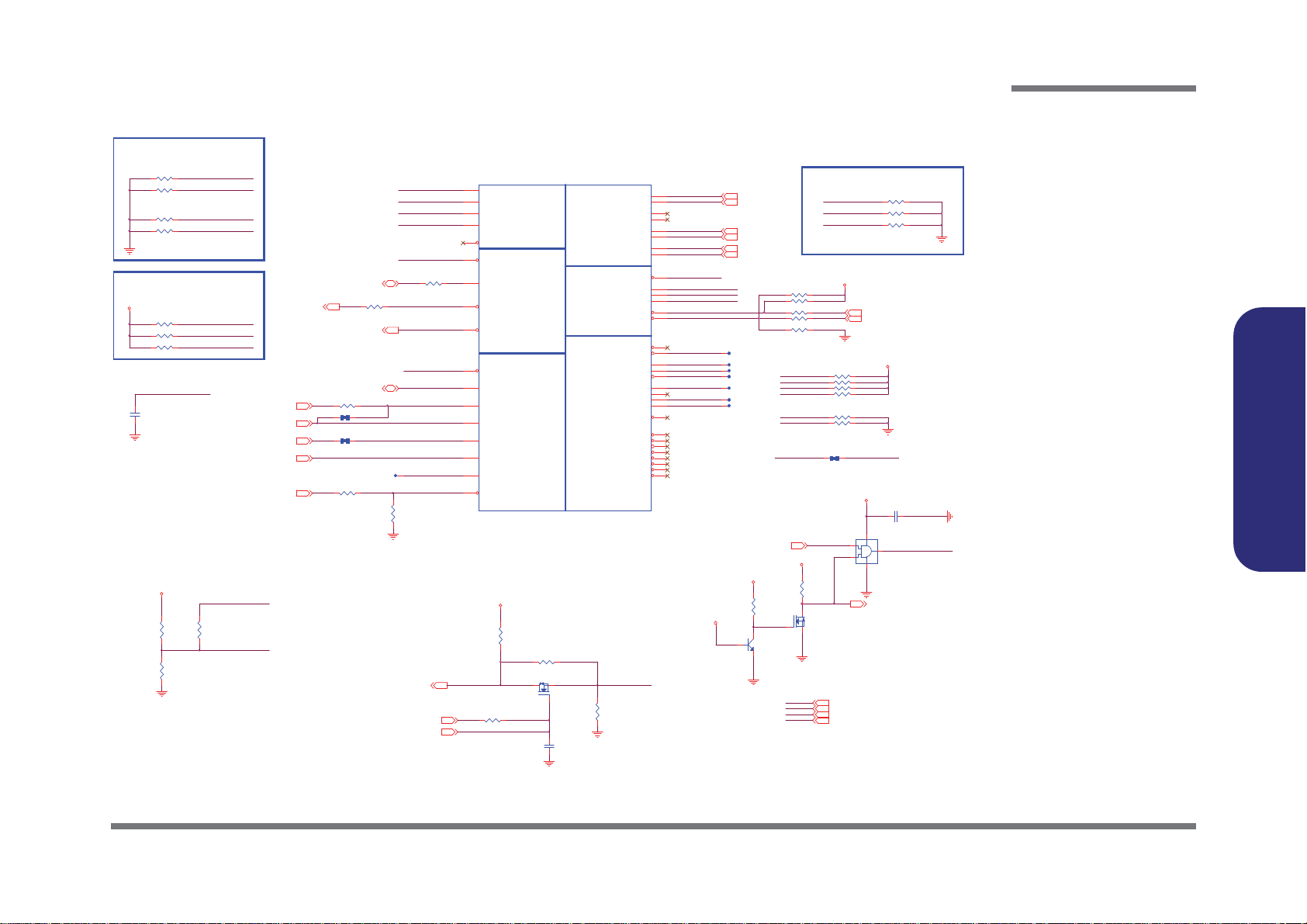

CPU 2/7 (CLK, MISC)

+1.5S_ CPU 7, 36

1.1VS_VTT_PWRGD21,40

Q13

*MTN7002ZHS3

G

DS

R162

*10K_04

3.3V

3.3V

+1.5S_CPU

U11

*74AHC1G08GW

1

2

5

4

3

DRAMPWRGD_CPU

Q12

*2N3904

B

E C

+1.5S_CPU_PWRGD 39

3.3V

C222 *.1u_10V_X7R_04

R163

*10K_04

SYS_AGENT_PWROK

H_CPURST#

DDR3 Compensation Signals

H_PROCHOT#_D

Processor Pullups

XDP _TDI _ M

XDP_TRST#

1.5V 10,11,36,39

H_PROCHOT#42

If PROCHOT# is not used, then it must be terminated

with a 50-O pull-up resistor to VTT_1.1 rail.

PROCESSOR 2/7 ( CLK,MISC,JTAG )

H_COMP2

H_COMP3

H_COMP1

H_COMP0

R107 *68_04

R128 *12.4K_1%_04

R67 *51_04

R69 *51_04

R130 10K_04

R159 1.5K_1%_04

R125 49.9_1%_04

R421 20_1%_04

R110 0_04

R153 *0_04

R440 24.9_1%_04

R419 49.9_1%_04

R418 51_04

R60 *51_04

R131 10K_04

CLOCKS

MISC THERMAL

PWR MANAGEMENT

DDR3

MISC

JTAG & BPM

U40B

MOLEX 479890142

SM_RCOMP[1]

AM1

SM_RCOMP[2]

AN1

SM_DRAMRST#

F6

SM_RCOMP[0]

AL1

BCLK#

B16

BCLK

A16

BCLK_ITP#

AT30

BCLK_ITP

AR30

PEG_CLK#

D16

PEG_CLK

E16

DPLL_REF_SSCLK#

A17

DPLL_REF_SSCLK

A18

CATERR#

AK14

COMP3

AT23

PECI

AT15

PROCHOT#

AN26

THERMTR IP#

AK15

RESET_OBS#

AP26

VCCPWRGOOD_1

AN14

VCCPWRGOOD_0

AN27

SM_DRAMPWR OK

AK13

VTTPWRGOOD

AM15

RSTIN#

AL14

PM_EXT_TS#[0]

AN15

PM_EXT_TS#[1]

AP15

PRDY#

AT28

PREQ#

AP27

TCK

AN28

TMS

AP28

TRST#

AT27

TDI

AT29

TDO

AR27

TDI_M

AR29

TDO_ M

AP29

DBR#

AN25

BPM#[0]

AJ22

BPM#[1]

AK22

BPM#[2]

AK24

BPM#[3]

AJ24

BPM#[4]

AJ25

BPM#[5]

AH22

BPM#[6]

AK23

BPM#[7]

AH23

COMP2

AT24

PM_SYNC

AL15

TAPPWRGOOD

AM26

COMP1

G16

COMP0

AT26

SKTOCC#

AH24

R109 68_04

R424 20_1%_04

R115 *0_04

R129 * 0_04

TRACE WIDTH 10MIL, LENGTH <500MILS

R441 100_1%_04

R155

750_1%_04

R433 49. 9_1%_04

R108 51_04

R68 *51_04

R439 130_1%_04

XDP _TM S

1.1VS_VTT

1.1VS_VTT

1.1VS_VTT

BCLK_CPU _P 24

CLK_DP_P 20

CLK_DP_N 20

H_CPUPWRGD24

BUF _PLT_ RST#23,28,31,35

PM_DRAM_PWR GD21

H_VTTPWRGD21

BCLK_CPU _N 24

H_THRMTRIP#24

CLK_EXP_N 20

CLK_EXP_P 20

1.1VS_VTT 2,6, 7,19,20,21, 24,25,26,38,40, 41,42

H_PECI24,35

PM_EXTTS#_EC 3

TS#_DIMM0_1 10,11

DELAY_PWRGD21,42

H_PM_SYNC21

R134

1.1K_1%_04

VDDPW RGOOD_R

R158

3K_1%_04

+1.5S_C PU

R157

*1.5K_1%_04

DRAMPWRGD_CPU

R114 *10mil_short

H_PROCHOT#_D

R156 *10mil_short

C1126

.1u_10V_X7R_04

R416 *10mil_short

XDP _TD O _M

H_CPURST#

Processor Compensation

Signals

H_PWRGD_XDP

PLT_RST#_R

XDP_PREQ#

XDP _TC L K

XDP_TRST#

XDP _TM S

Connect to the Processor (VTTPWRGOOD) VTT_1.1 VR power

good signal to processor. Signal voltage level is 1.1 V.

H_COMP3

SYS_AGENT_PWROK

H_COMP2

PM_EXTTS#[1]

H_COMP1

Signal from PCH to Processor

Connect to PCH (PLT_RST#)

(needs to be level translated

from 3.3 V to 1.1 V).

CPU_DRAMRST#

SM_RCOMP_0

XDP _TD O _M

3.3V 3,12,13,17,19, 20,21,23,24,26,28,29,31,32, 33,36,38,39, 40,43

XDP _TD I _R

SM_RCOMP_1

VDDPWRGOOD_R

SM_RCOMP_2

H_CATERR#

XDP _P RE Q#

XDP _TC L K

R246

*1K_04

Q32

*MTN7002ZHS3

G

D S

R241

*100K_04

R250 0_04

XDP _TD I _R

R234 *0_04

DDR3_DRAMRST#10,11

1.5V

DDR3_DRAMRST#

DRAMRST_CNTRL_PCH24

CPU_DRAMRST#

C360

*470p_50V_X7R_04

PM_EXTTS#[0]

DRAMRST_CNTRL9

H_COMP0

XDP _TD I _M

XDP _TD O_ M

R121 0_04

SM_RCOMP_2

SM_RCOMP_1

SM_RCOMP_0

H_CATERR#

Sheet 4 of 49

CPU 2/7

(CLK, MISC)

http://hobi-elektronika.net

Schematic Diagrams

CPU 2/7 (CLK, MISC) B - 5

B.Schematic Diagrams

Page 5

Schematic Diagrams

PROCESSOR 3/7 ( DDR3 )

M_A_D Q1

M_A_D Q2

M_A_D Q3

M_A_A6

M_A_A5

M_A_A7

M_A_A8

M_A_A9

M_A_D Q29

M_A_D Q4

M_A_A4

M_A_D Q32

M_A_D Q31

M_A_D Q30

M_A_D Q37

M_A_D Q36

M_A_D Q35

M_A_D Q34

M_A_D Q33

M_A_D Q42

M_A_D Q41

M_A_D Q40

M_A_D Q39

M_A_D Q47

M_A_D Q46

M_A_D Q45

M_A_D Q44

M_A_D Q43

M_A_D Q51

M_A_D Q28

M_A_D Q50

M_A_D Q49

M_A_D Q38

M_A_D Q48

M_A_D Q55

M_A_D Q54

M_A_D Q53

M_A_D Q52

M_A_A3

M_A_D Q5

M_A_A0

M_A_DQS7

M_A_A1

M_A_A2

M_A_A15

M_A_DQS6

M_A_D Q58

M_A_D Q57

M_A_D Q56

M_A_D Q6

M_A_D Q59

M_A_D Q63

M_A_D Q62

M_A_D Q61

M_A_D Q60

M_A_DQS4

M_A_DQS5

M_A_DQS0

M_A_DQS2

M_A_DQS1

M_A_DQS3

M_A_D Q7

M_A_A14

M_A_A13

M_A_D Q8

M_A_D Q9

M_A_D Q13

M_A_D Q12

M_A_D Q11

M_A_A11

M_A_D Q19

M_A_D Q18

M_A_D Q17

M_A_D Q16

M_A_D Q15

M_A_D Q14

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_D Q10

M_A_DQS#2

M_A_DQS#1

M_A_DQS#3

M_A_DQS#4

M_A_DQS#0

M_A_D Q22

M_A_D Q21

M_A_D Q26

M_A_D Q25

M_A_D Q24

M_A_D Q23

M_A_D Q0

M_A_A12

M_A_D Q20

M_A_D Q27

M_A_D M4

M_A_D M5

M_A_D M6

M_A_D M7

M_A_D M0

M_A_D M2

M_A_D M1

M_A_D M3

M_A_A10

DDR SYSTEM MEMORY A

U40C

MOLEX 479890142

SA_BS[0]

AC3

SA_BS[1]

AB2

SA_BS[2]

U7

SA_CAS#

AE1

SA_RAS#

AB3

SA_WE#

AE9

SA_CK[0]

AA6

SA_CK[1]

Y6

SA_CK#[0]

AA7

SA_CK#[1]

Y5

SA_CKE[0]

P7

SA_CKE[1]

P6

SA_CS#[0]

AE2

SA_CS#[1]

AE8

SA_ODT[0]

AD8

SA_ODT[1]

AF9

SA_DM[0]

B9

SA_DM[1]

D7

SA_DM[2]

H7

SA_DM[3]

M7

SA_DM[4]

AG6

SA_DM[5]

AM7

SA_DM[6]

AN10

SA_DM[7]

AN13

SA_DQS[0]

C8

SA_DQS#[0]

C9

SA_DQS[1]

F9

SA_DQS#[1]

F8

SA_DQS[2]

H9

SA_DQS#[2]

J9

SA_DQS[3]

M9

SA_DQS#[3]

N9

SA_DQS[4]

AH8

SA_DQS#[4]

AH7

SA_DQS[5]

AK10

SA_DQS#[5]

AK9

SA_DQS[6]

AN11

SA_DQS#[6]

AP11

SA_DQS[7]

AR13

SA_DQS#[7]

AT13

SA_MA[0]

Y3

SA_MA[1]

W1

SA_MA[2]

AA8

SA_MA[3]

AA3

SA_MA[4]

V1

SA_MA[5]

AA9

SA_MA[6]

V8

SA_MA[7]

T1

SA_MA[8]

Y9

SA_MA[9]

U6

SA_MA[10]

AD4

SA_MA[11]

T2

SA_MA[12]

U3

SA_MA[13]

AG8

SA_MA[14]

T3

SA_MA[15]

V9

SA_DQ[0]

A10

SA_DQ[1]

C10

SA_DQ[2]

C7

SA_DQ[3]

A7

SA_DQ[4]

B10

SA_DQ[5]

D10

SA_DQ[6]

E10

SA_DQ[7]

A8

SA_DQ[8]

D8

SA_DQ[9]

F10

SA_DQ[10]

E6

SA_DQ[11]

F7

SA_DQ[12]

E9

SA_DQ[13]

B7

SA_DQ[14]

E7

SA_DQ[15]

C6

SA_DQ[16]

H10

SA_DQ[17]

G8

SA_DQ[18]

K7

SA_DQ[19]

J8

SA_DQ[20]

G7

SA_DQ[21]

G10

SA_DQ[22]

J7

SA_DQ[23]

J10

SA_DQ[24]

L7

SA_DQ[25]

M6

SA_DQ[26]

M8

SA_DQ[27]

L9

SA_DQ[28]

L6

SA_DQ[29]

K8

SA_DQ[30]

N8

SA_DQ[31]

P9

SA_DQ[32]

AH5

SA_DQ[33]

AF5

SA_DQ[34]

AK6

SA_DQ[35]

AK7

SA_DQ[36]

AF6

SA_DQ[37]

AG5

SA_DQ[38]

AJ7

SA_DQ[39]

AJ6

SA_DQ[40]

AJ10

SA_DQ[41]

AJ9

SA_DQ[42]

AL10

SA_DQ[43]

AK12

SA_DQ[44]

AK8

SA_DQ[45]

AL7

SA_DQ[46]

AK11

SA_DQ[47]

AL8

SA_DQ[48]

AN8

SA_DQ[49]

AM10

SA_DQ[50]

AR11

SA_DQ[51]

AL11

SA_DQ[52]

AM9

SA_DQ[53]

AN9

SA_DQ[54]

AT11

SA_DQ[55]

AP12

SA_DQ[56]

AM12

SA_DQ[57]

AN12

SA_DQ[58]

AM13

SA_DQ[59]

AT14

SA_DQ[60]

AT12

SA_DQ[61]

AL13

SA_DQ[62]

AR14

SA_DQ[63]

AP14

DDR SYSTEM MEMORY - B

U40D

MOLEX 479890142

SB_BS[0]

AB1

SB_BS[1]

W5

SB_BS[2]

R7

SB_CAS#

AC5

SB_RAS#

Y7

SB_WE#

AC6

SB_CK[0]

W8

SB_CK[1]

V7

SB_CK#[0]

W9

SB_CK#[1]

V6

SB_CKE[0]

M3

SB_CKE[1]

M2

SB_CS#[0]

AB8

SB_CS#[1]

AD6

SB_ODT[0]

AC7

SB_ODT[1]

AD1

SB_DM[0]

D4

SB_DM[1]

E1

SB_DM[2]

H3

SB_DM[3]

K1

SB_DM[4]

AH1

SB_DM[5]

AL2

SB_DM[6]

AR4

SB_DM[7]

AT8

SB_DQS[4]

AG2

SB_DQS#[4]

AH2

SB_DQS[5]

AL5

SB_DQS#[5]

AL4

SB_DQS[6]

AP5

SB_DQS#[6]

AR5

SB_DQS[7]

AR7

SB_DQS#[7]

AR8

SB_DQS[0]

C5

SB_DQS#[0]

D5

SB_DQS[1]

E3

SB_DQS#[1]

F4

SB_DQS[2]

H4

SB_DQS#[2]

J4

SB_DQS[3]

M5

SB_DQS#[3]

L4

SB_MA[0]

U5

SB_MA[1]

V2

SB_MA[2]

T5

SB_MA[3]

V3

SB_MA[4]

R1

SB_MA[5]

T8

SB_MA[6]

R2

SB_MA[7]

R6

SB_MA[8]

R4

SB_MA[9]

R5

SB_MA[10]

AB5

SB_MA[11]

P3

SB_MA[12]

R3

SB_MA[13]

AF7

SB_MA[14]

P5

SB_MA[15]

N1

SB_DQ[0]

B5

SB_DQ[1]

A5

SB_DQ[2]

C3

SB_DQ[3]

B3

SB_DQ[4]

E4

SB_DQ[5]

A6

SB_DQ[6]

A4

SB_DQ[7]

C4

SB_DQ[8]

D1

SB_DQ[9]

D2

SB_DQ[10]

F2

SB_DQ[11]

F1

SB_DQ[12]

C2

SB_DQ[13]

F5

SB_DQ[14]

F3

SB_DQ[15]

G4

SB_DQ[16]

H6

SB_DQ[17]

G2

SB_DQ[18]

J6

SB_DQ[19]

J3

SB_DQ[20]

G1

SB_DQ[21]

G5

SB_DQ[22]

J2

SB_DQ[23]

J1

SB_DQ[24]

J5

SB_DQ[25]

K2

SB_DQ[26]

L3

SB_DQ[27]

M1

SB_DQ[28]

K5

SB_DQ[29]

K4

SB_DQ[30]

M4

SB_DQ[31]

N5

SB_DQ[32]

AF3

SB_DQ[33]

AG1

SB_DQ[34]

AJ3

SB_DQ[35]

AK1

SB_DQ[36]

AG4

SB_DQ[37]

AG3

SB_DQ[38]

AJ4

SB_DQ[39]

AH4

SB_DQ[40]

AK3

SB_DQ[41]

AK4

SB_DQ[42]

AM6

SB_DQ[43]

AN2

SB_DQ[44]

AK5

SB_DQ[45]

AK2

SB_DQ[46]

AM4

SB_DQ[47]

AM3

SB_DQ[48]

AP3

SB_DQ[49]

AN5

SB_DQ[50]

AT4

SB_DQ[51]

AN6

SB_DQ[52]

AN4

SB_DQ[53]

AN3

SB_DQ[54]

AT5

SB_DQ[55]

AT6

SB_DQ[56]

AN7

SB_DQ[57]

AP6

SB_DQ[58]

AP8

SB_DQ[59]

AT9

SB_DQ[60]

AT7

SB_DQ[61]

AP9

SB_DQ[62]

AR10

SB_DQ[63]

AT10

M_CKE0 10

M_CLK_DDR#1 10

M_CLK_DDR1 10

M_CKE1 10

M_A_BS110

M_ODT1 10

M_CS#1 10

M_CS#0 10

M_A_BS210

M_A_DM[7:0] 10

M_A_CAS#10

M_ODT0 10

M_CLK_DDR0 10

M_A_WE#10

M_A_A[15:0] 10

M_A_RAS#10

M_A_D Q[6 3:0]10

M_B_BS011

M_CLK_DDR#0 10

M_A_BS010

M_B_BS211

M_B_W E#11

M_B_RAS#11

M_B_BS111

M_B_ DQ [6 3: 0]11

M_CKE3 11

M_CKE2 11

M_B_CAS#11

M_CS#3 11

M_CS#2 11

M_CLK_DDR#3 11

M_CLK_DDR3 11

M_CLK_DDR#2 11

M_CLK_DDR2 11

M_ODT2 11

M_ODT3 11

M_B_DQS[7:0] 11

M_B_DQS#[7:0] 11

M_B_A[15:0] 11

M_B_DM[7:0] 11

M_A_DQS[7:0] 10

M_A_DQS#[7:0] 10

M_B_D Q48

M_B_D Q47

M_B_D Q54

M_B_D Q53

M_B_D Q52

M_B_D Q51

M_B_D Q50

M_B_D Q49

M_B_DQS5

M_B_D Q58

M_B_D Q57

M_B_D Q56

M_B_D Q55 M_B_DQS7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS6

M_B_D Q61

M_B_D Q60

M_B_D Q59

M_B_DQS#4

M_B_DQS#6

M_B_DQS#5

M_B_D Q11

M_B_D Q63

M_B_D Q62

M_B_D M6

M_B_D M5

M_B_D Q12

M_B_DQS#7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_D M7

M_B_D M0

M_B_D M1

M_B_D M2

M_B_D M3

M_B_D M4

M_B_D Q3

M_B_D Q2

M_B_D Q1

M_B_D Q4

M_B_D Q6

M_B_D Q5

M_B_D Q9

M_B_D Q8

M_B_D Q7

M_B_D Q0

M_B_D Q10

M_B_D Q13

M_B_A2

M_B_A3

M_B_A4

M_B_A6

M_B_A5

M_B_A0

M_B_A1

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A13

M_B_A12

M_B_D Q14

M_B_D Q18

M_B_D Q17

M_B_D Q16

M_B_A14

M_B_A15

M_B_D Q15

M_B_A7

M_B_D Q23

M_B_D Q22

M_B_D Q21

M_B_D Q20

M_B_D Q19

M_B_D Q28

M_B_D Q27

M_B_D Q26

M_B_D Q25

M_B_D Q24

M_B_D Q34

M_B_D Q33

M_B_D Q32

M_B_D Q31

M_B_D Q30

M_B_D Q29

M_B_D Q39

M_B_D Q38

M_B_D Q37

M_B_D Q36

M_B_D Q35

M_B_D Q44

M_B_D Q43

M_B_D Q42

M_B_D Q41

M_B_D Q40

M_B_D Q46

M_B_D Q45

Sheet 5 of 49

CPU 3/7

(DDR3)

http://hobi-elektronika.net

CPU 3/7 (DDR3)

B.Schematic Diagrams

B - 6 CPU 3/7 (DDR3)

Page 6

CPU 4/7 (Power)

VCORE

R105

1K_04

C563

10U_6.3V_06

C559

10U_6.3V_06

1K PU to VTT and 1K PD to GND

for POC

C150

22U_6.3V_X5R_08

1.1VS_VTT

R70

1K_04

1.1VS_VTT

ICCMAX_VTT Max Current

for VTT Rail

SV 18

XE 21

PSI# 42

PSI#

C157

22U_6.3V_X5R_08

C165

22U_6.3V_X5R_08

VCORE

C145

22U_6.3V_X5R_08

C171

22U_6.3V_X5R_08

C163

22U_6.3V_X5R_08

C183

22U_6.3V_X5R_08

C156

22U_6.3V_X5R_08

The decoupling capacitors, filt er

recommendations and sense resistors on the

CPU/PCH Rails are specific to t he CRB

Implementation. Customers need to follow the

recommendations in the Calpella Platform

Design Guide

C144

22U_6.3V_X5R_08

C584

22U_6.3V_X5R_08

C149

22U_6.3V_X5R_08

Please note that the

VTT Rail Values are

Auburndale VTT=1.05V

Clarksfield VTT=1.1V

C560

10U_6.3V_06

VCORE

C173

22U_6.3V_X5R_08

R434 *10mil_short

Cost down

PROCESSOR 4/7 ( POWER )

C573

10U_6.3V_06

R104

*1K_04

C170

10U_6.3 V_06

C586

22U_6.3V_X5R_08

C187

22U_6.3V_X5R_08

C179

10U_6.3V_06

C569

10U_6.3V_06

+VTT_44

C585

22U_6.3V_X5R_08

POWER

CPU CORE SUPP LY

1.1V RAIL POWER

SENSE LINES

CPU VIDS

U40F

MOLEX 479890142

ISENSE

AN35

VTT_SENSE

B15

PSI#

AN33

VID[0]

AK35

VID[1]

AK33

VID[2]

AK34

VID[3]

AL35

VID[4]

AL33

VID[5]

AM33

VID[6]

AM35

PROC_D PRSLPVR

AM34

VTT_SELECT

G15

VCC_SENSE

AJ34

VSS_SENSE_VTT

A15

VCC1

AG35

VCC2

AG34

VCC3

AG33

VCC4

AG32

VCC5

AG31

VCC6

AG30

VCC7

AG29

VCC8

AG28

VCC9

AG27

VCC10

AG26

VCC11

AF35

VCC12

AF34

VCC13

AF33

VCC14

AF32

VCC15

AF31

VCC16

AF30

VCC17

AF29

VCC18

AF28

VCC19

AF27

VCC20

AF26

VCC21

AD35

VCC22

AD34

VCC23

AD33

VCC24

AD32

VCC25

AD31

VCC26

AD30

VCC27

AD29

VCC28

AD28

VCC29

AD27

VCC30

AD26

VCC31

AC35

VCC32

AC34

VCC33

AC33

VCC34

AC32

VCC35

AC31

VCC36

AC30

VCC37

AC29

VCC38

AC28

VCC39

AC27

VCC40

AC26

VCC41

AA35

VCC42

AA34

VCC43

AA33

VCC44

AA32

VCC45

AA31

VCC46

AA30

VCC47

AA29

VCC48

AA28

VCC49

AA27

VCC50

AA26

VCC51

Y35

VCC52

Y34

VCC53

Y33

VCC54

Y32

VCC55

Y31

VCC56

Y30

VCC57

Y29

VCC58

Y28

VCC59

Y27

VCC60

Y26

VCC61

V35

VCC62

V34

VCC63

V33

VCC64

V32

VCC65

V31

VCC66

V30

VCC67

V29

VCC68

V28

VCC69

V27

VCC70

V26

VCC71

U35

VCC72

U34

VCC73

U33

VCC74

U32

VCC75

U31

VCC76

U30

VCC77

U29

VCC78

U28

VCC79

U27

VCC80

U26

VCC81

R35

VCC82

R34

VCC83

R33

VCC84

R32

VCC85

R31

VCC86

R30

VCC87

R29

VCC88

R28

VCC89

R27

VCC90

R26

VCC91

P35

VCC92

P34

VCC93

P33

VCC94

P32

VCC95

P31

VCC96

P30

VCC97

P29

VCC98

P28

VCC99

P27

VCC100

P26

VTT0_33

AF10

VTT0_34

AE10

VTT0_35

AC10

VTT0_36

AB10

VTT0_37

Y10

VTT0_38

W10

VTT0_39

U10

VTT0_40

T10

VTT0_41

J12

VTT0_42

J11

VTT0_1

AH14

VTT0_2

AH12

VTT0_3

AH11

VTT0_4

AH10

VTT0_5

J14

VTT0_6

J13

VTT0_7

H14

VTT0_8

H12

VTT0_9

G14

VTT0_10

G13

VTT0_11

G12

VTT0_12

G11

VTT0_13

F14

VTT0_14

F13

VTT0_15

F12

VTT0_16

F11

VTT0_17

E14

VTT0_18

E12

VTT0_19

D14

VTT0_20

D13

VTT0_21

D12

VTT0_22

D11

VTT0_23

C14

VTT0_24

C13

VTT0_25

C12

VTT0_26

C11

VTT0_27

B14

VTT0_28

B12

VTT0_29

A14

VTT0_30

A13

VTT0_31

A12

VTT0_32

A11

VSS_SENSE

AJ35

VTT0_43

J16

VTT0_44

J15

C174

10U_6.3 V_06

C190

*10U_6.3V_06

C204

*10U_6.3V_06

C175

22U_6.3V_X5R_08

C626

10U_6.3V_06

C186

10U_6.3V_06

C188

22U_6.3 V_X5R_08

C177

10U_6.3V_06

C180

10U_6.3V_06

1.1VS_VTTVCORE

1.1VS_VTT

1.1VS_VTT

IMON 42

VSS_SENSE 42

VCC_SENSE 42

1.1VS_VTT 2,4,7, 19,20,21,24,25,26, 38,40,41,42

VCORE 42

PM_DPRSLPVR 42

H_VTTV ID1 40

H_VID1 42

H_VID2 42

H_VID5 42

H_VID4 42

H_VID0 42

H_VID6 42

H_VID3 42

VTT_SENSE 40,41

C565

10U_6.3V_06

TO VCORE POWER CONTROL

PROCESSOR UNCORE POWER

C564

10U_6.3V_06

PROCESSOR CORE POWER

+VTT_43

C570

10U_6.3V_06

C574

10U_6.3V_06

C580

10U_6.3V_06

C566

10U_6.3V_06

R435 *10mil_short

ICCMAX Maximum Processor SV 52

Core ICC XE 65

C579

10U_6.3V_06

VTT TOTAL 21A

52A

Sheet 6 of 49

CPU 4/7

(Power)

http://hobi-elektronika.net

Schematic Diagrams

B.Schematic Diagrams

CPU 4/7 (Power) B - 7

Page 7

Schematic Diagrams

VCCPLL 0.6A

TP_GFX_I MON

C146

22U_6.3V_X5R_08

C158

22U_6.3V_X5R_08

R120

*0_04

Please note that the

VTT Rail Values are

Auburndale VTT=1.05V

Clarksfield VTT=1.1V

R112 *1K_04

C266

10U_6.3V_06

C267

10U_6.3V_06

C268

10U_6.3V _06

C1133

10U_6.3V_06

+1.5S_CPU

R113 100_04

+1.5S_CPU 4,36

PROCESSOR 5/7 ( GRAPHICS POWER )

FOR DISABLE

GPUVSSSENSE 41

GPUVCCSENSE 41

VDDQ 6A

GFX_IMON 41

C193

1U_6.3V_X5R_04

C561

2.2u_6.3V_X5R_04

+

C567

330u_2.5V_V_A

C152

10U_6.3V_06

C588

22U_6.3V_X5R_08

C196

1U_6.3V_X5R_04

C555

10U_6.3V_06

C135

1U_6.3V_X5R_04

C264

1U_6.3V_X5R_04

C160

22U_6.3V_X5R_08

C143

22U_6.3V_X5R_08

C189

22U_6.3V_X5R_08

C142

4.7U_6.3V_X5R_06

C265

1U_6.3V_X5R_04

C587

22U_6.3V_X5R_08

C153

10U_6.3V_06

C161

22U_6.3V_X5R_08

C197

1U_6.3V_X5R_04

C562

1U_6.3V_X5R_04

C600

22U_6.3V_X5R_08

C601

22U_6.3V_X5R_08

C147

22U_6.3V_X5R_08

C210

10U_6.3V_06

POWER

GRAPHICS VIDs

GRAPHICS

DDR3 - 1.5V RAILS

FDI PEG & DMI

SENSE

LINES

1.1V1.8V

U40G

MOLEX 479890142

GFX_VID[ 0]

AM22

GFX_VID[ 1]

AP22

GFX_VID[ 2]

AN22

GFX_VID[ 3]

AP23

GFX_VID[ 4]

AM23

GFX_VID[ 5]

AP24

GFX_VID[ 6]

AN24

GFX_VR_EN

AR25

GFX_DPRSLPVR

AT25

GFX_IMON

AM24

VAXG_SENSE

AR22

VSSAXG_SENSE

AT22

VAXG1

AT21

VAXG2

AT19

VAXG3

AT18

VAXG4

AT16

VAXG5

AR21

VAXG6

AR19

VAXG7

AR18

VAXG8

AR16

VAXG9

AP21

VAXG10

AP19

VAXG11

AP18

VAXG12

AP16

VAXG13

AN21

VAXG14

AN19

VAXG15

AN18

VAXG16

AN16

VAXG17

AM21

VAXG18

AM19

VAXG19

AM18

VAXG20

AM16

VAXG21

AL21

VAXG22

AL19

VAXG23

AL18

VAXG24

AL16

VAXG25

AK21

VAXG26

AK19

VAXG27

AK18

VAXG28

AK16

VAXG29

AJ21

VAXG30

AJ19

VAXG31

AJ18

VAXG32

AJ16

VAXG33

AH21

VAXG34

AH19

VAXG35

AH18

VAXG36

AH16

VTT1_45

J24

VTT1_46

J23

VTT1_47

H25

VTT1_48

K26

VTT1_49

J27

VTT1_50

J26

VTT1_51

J25

VTT1_52

H27

VTT1_53

G28

VTT1_54

G27

VTT1_55

G26

VTT1_56

F26

VTT1_57

E26

VTT1_58

E25

VDDQ1

AJ1

VDDQ2

AF1

VDDQ3

AE7

VDDQ4

AE4

VDDQ5

AC1

VDDQ6

AB7

VDDQ7

AB4

VDDQ8

Y1

VDDQ9

W7

VDDQ10

W4

VDDQ11

U1

VDDQ12

T7

VDDQ13

T4

VDDQ14

P1

VDDQ15

N7

VDDQ16

N4

VDDQ17

L1

VDDQ18

H1

VTT0_59

P10

VTT0_60

N10

VTT0_61

L10

VTT0_62

K10

VCCPLL1

L26

VCCPLL2

L27

VCCPLL3

M26

VTT1_63

J22

VTT1_64

J20

VTT1_65

J18

VTT1_66

H21

VTT1_67

H20

VTT1_68

H19

VGFX_CORE

1.1VS_VTT

1.1VS_VTT

1.8VS

1.1VS_VTT

1.1VS_VTT

DFGT_VID_0 41

DFGT_VR_EN 41

DFGT_VID_4 41

DFGT_VID_3 41

DFGT_VID_2 41

DFGT_VID_1 41

1.1VS_VTT 2,4,6,19,20,21,24,25,26,38,40,41,42

VGFX_CORE 41

1.8VS 25,36,38

DFGT_VID_6 41

DFGT_VID_5 41

Sheet 7 of 49

CPU 5/7

(VGFX Power)

http://hobi-elektronika.net

CPU 5/7 (VGFX Power)

B.Schematic Diagrams

B - 8 CPU 5/7 (VGFX Power)

Page 8

PROCESSOR 6/7 ( GND )

VSS

U40H

MOLEX 479890142

VSS1

AT20

VSS2

AT17

VSS3

AR31

VSS4

AR28

VSS5

AR26

VSS6

AR24

VSS7

AR23

VSS8

AR20

VSS9

AR17

VSS10

AR15

VSS11

AR12

VSS12

AR9

VSS13

AR6

VSS14

AR3

VSS15

AP20

VSS16

AP17

VSS17

AP13

VSS18

AP10

VSS19

AP7

VSS20

AP4

VSS21

AP2

VSS22

AN34

VSS23

AN31

VSS24

AN23

VSS25

AN20

VSS26

AN17

VSS27

AM29

VSS28

AM27

VSS29

AM25

VSS30

AM20

VSS31

AM17

VSS32

AM14

VSS33

AM11

VSS34

AM8

VSS35

AM5

VSS36

AM2

VSS37

AL34

VSS38

AL31

VSS39

AL23

VSS40

AL20

VSS41

AL17

VSS42

AL12

VSS43

AL9

VSS44

AL6

VSS45

AL3

VSS46

AK29

VSS47

AK27

VSS48

AK25

VSS49

AK20

VSS50

AK17

VSS51

AJ31

VSS52

AJ23

VSS53

AJ20

VSS54

AJ17

VSS55

AJ14

VSS56

AJ11

VSS57

AJ8

VSS58

AJ5

VSS59

AJ2

VSS60

AH35

VSS61

AH34

VSS62

AH33

VSS63

AH32

VSS64

AH31

VSS65

AH30

VSS66

AH29

VSS67

AH28

VSS68

AH27

VSS69

AH26

VSS70

AH20

VSS71

AH17

VSS72

AH13

VSS73

AH9

VSS74

AH6

VSS75

AH3

VSS76

AG10

VSS77

AF8

VSS78

AF4

VSS79

AF2

VSS80

AE35

VSS81

AE34

VSS82

AE33

VSS83

AE32

VSS84

AE31

VSS85

AE30

VSS86

AE29

VSS87

AE28

VSS88

AE27

VSS89

AE26

VSS90

AE6

VSS91

AD10

VSS92

AC8

VSS93

AC4

VSS94

AC2

VSS95

AB35

VSS96

AB34

VSS97

AB33

VSS98

AB32

VSS99

AB31

VSS100

AB30

VSS101

AB29

VSS102

AB28

VSS103

AB27

VSS104

AB26

VSS105

AB6

VSS106

AA10

VSS107

Y8

VSS108

Y4

VSS109

Y2

VSS110

W35

VSS111

W34

VSS112

W33

VSS113

W32

VSS114

W31

VSS115

W30

VSS116

W29

VSS117

W28

VSS118

W27

VSS119

W26

VSS120

W6

VSS121

V10

VSS122

U8

VSS123

U4

VSS124

U2

VSS125

T35

VSS126

T34

VSS127

T33

VSS128

T32

VSS129

T31

VSS130

T30

VSS131

T29

VSS132

T28

VSS133

T27

VSS134

T26

VSS135

T6

VSS136

R10

VSS137

P8

VSS138

P4

VSS139

P2

VSS140

N35

VSS141

N34

VSS142

N33

VSS143

N32

VSS144

N31

VSS145

N30

VSS146

N29

VSS147

N28

VSS148

N27

VSS149

N26

VSS150

N6

VSS151

M10

VSS152

L35

VSS153

L32

VSS154

L29

VSS155

L8

VSS156

L5

VSS157

L2

VSS158

K34

VSS159

K33

VSS160

K30

VSS

NCTF

U40I

MOLEX 479890142

VSS161

K27

VSS162

K9

VSS163

K6

VSS164

K3

VSS165

J32

VSS166

J30

VSS167

J21

VSS168

J19

VSS169

H35

VSS170

H32

VSS171

H28

VSS172

H26

VSS173

H24

VSS174

H22

VSS175

H18

VSS176

H15

VSS177

H13

VSS178

H11

VSS179

H8

VSS180

H5

VSS181

H2

VSS182

G34

VSS183

G31

VSS184

G20

VSS185

G9

VSS186

G6

VSS187

G3

VSS188

F30

VSS189

F27

VSS190

F25

VSS191

F22

VSS192

F19

VSS193

F16

VSS194

E35

VSS195

E32

VSS196

E29

VSS197

E24

VSS198

E21

VSS199

E18

VSS200

E13

VSS201

E11

VSS202

E8

VSS203

E5

VSS204

E2

VSS205

D33

VSS206

D30

VSS207

D26

VSS208

D9

VSS209

D6

VSS210

D3

VSS211

C34

VSS212

C32

VSS213

C29

VSS214

C28

VSS215

C24

VSS216

C22

VSS217

C20

VSS218

C19

VSS219

C16

VSS220

B31

VSS221

B25

VSS222

B21

VSS223

B18

VSS224

B17

VSS225

B13

VSS226

B11

VSS227

B8

VSS228

B6

VSS229

B4

VSS230

A29

VSS_NCTF1

AT35

VSS_NCTF2

AT1

VSS_NCTF3

AR34

VSS_NCTF4

B34

VSS_NCTF5

B2

VSS_NCTF6

B1

VSS_NCTF7

A35

VSS231

A27

VSS232

A23

VSS233

A9

http://hobi-elektronika.net

Schematic Diagrams

CPU 6/7 (GND)

B.Schematic Diagrams

Sheet 8 of 49

CPU 6/7 (GND)

CPU 6/7 (GND) B - 9

Page 9

Schematic Diagrams

RESERVED

U40E

MOLEX 479890142

CFG[0]

AM30

CFG[1]

AM28

CFG[2]

AP31

CFG[3]

AL32

CFG[4]

AL30

CFG[5]

AM31

CFG[6]

AN29

CFG[7]

AM32

CFG[8]

AK32

CFG[9]

AK31

CFG[10]

AK28

CFG[11]

AJ28

CFG[12]

AN30

CFG[13]

AN32

CFG[14]

AJ32

CFG[15]

AJ29

CFG[16]

AJ30

CFG[17]

AK30

RSVD34

AH25

RSVD35

AK26

RSVD38

AJ26

RSVD_NCTF_42

AT3

RSVD39

AJ27

RSVD_NCTF_40

AP1

RSVD_NCTF_41

AT2

RSVD_NCTF_43

AR1

RSVD_TP_86

H16

RSVD45

AL28

RSVD46

AL29

RSVD47

AP30

RSVD48

AP32

RSVD49

AL27

RSVD50

AT31

RSVD51

AT32

RSVD52

AP33

RSVD53

AR33

RSVD_NCTF_54

AT33

RSVD_NCTF_55

AT34

RSVD_NCTF_56

AP35

RSVD_NCTF_57

AR35

RSVD58

AR32

RSVD_NCTF_30

C35

RSVD_NCTF_31

B35

RSVD_NCTF_28

A34

RSVD_NCTF_29

A33

RSVD27

J28

RSVD26

J29

RSVD16

A19

RSVD15

B19

RSVD17

A20

RSVD18

B20

RSVD20

T9

RSVD19

U9

RSVD22

AB9

RSVD21

AC9

RSVD_NCTF_23

C1

RSVD_NCTF_24

A3

RSVD_TP_66

AA5

RSVD_TP_67

AA4

RSVD_TP_68

R8

RSVD_TP_71

AA2

RSVD_TP_72

AA1

RSVD_TP_73

R9

RSVD_TP_69

AD3

RSVD_TP_74

AG7

RSVD_TP_70

AD2

RSVD_TP_75

AE3

RSVD_TP_76

V4

RSVD_TP_77

V5

RSVD_TP_78

N2

RSVD_TP_81

W3

RSVD_TP_82

W2

RSVD_TP_83

N3

RSVD_TP_79

AD5

RSVD_TP_84

AE5

RSVD_TP_80

AD7

RSVD_TP_85

AD9

RSVD36

AL26

RSVD_NCTF_37

AR2

RSVD1

AP25

RSVD2

AL25

RSVD3

AL24

RSVD4

AL22

RSVD5

AJ33

RSVD6

AG9

RSVD7

M27

RSVD8

L28

RSVD9

J17

RSVD10

H17

RSVD11

G25

RSVD12

G17

RSVD13

E31

RSVD14

E30

RSVD32

AJ13

RSVD33

AJ12

RSVD_TP_59

E15

RSVD_TP_60

F15

KEY

A2

RSVD62

D15

RSVD63

C15

RSVD64

AJ15

RSVD65

AH15

VSS

AP34

R432 *0_04

R102 *3.01k_04

TP_RSV D8 6

????, ????

CFG7

DRAMRST_CNTRL4

DRAMRST_CNTRL4

R238 0_04

Q31

*AO3402L

G

D S

Q30

*AO3402L

G

D S

MVREF_DQ_DIM111

MVREF_DQ_DIM010

R233

*100K_04

VREF_CH_B_DIMMVREF_C H _B_DIMM

R242

*100K_04

R249 0_04

VREF_CH_A_DIMM

R431 *10mil_short

CFG3

CFG4

Cost down

R154 *10mil_short

Cost down

VSS (AP34) can be left NC i

CRB implementation ; EDS/DG

recommendation to GND

CFG4

CFG3

CFG0

CFG7

Clarksfield (only for early samples

pre-ES1) - Connect to GND with 3.01 K Ohm/5%

resistor

PROCESSOR 7/7 ( RESERVED )

H_RSVD17_R

H_RSVD18_R

RSVD86

Connect to GND

RSVD64_R

RSVD65_R

R62 *3.01k_04

CFG7

R122 *10mil_short

RSVD86

R430 *10mil_short

CFG0

1 : Single PEG

0 : Bifurcation enable

CFG0

CFG3

PCI-Express Configuration Select

CFG4

CFG3 - PCI-Express Static Lane Reversal

1 : Normal Operation

0 : Lane Numbers Reversed

15 -> 0, 14 -> 1, ...

CFG4 - Display Port Presence

1 : Disablled; No physical Display Port

attached to Embedd ed Displ ay Port

0 : Enabled; An ext ernal Di splay Po rt

device is connected to the Embedded

isplay Port

R106 *3.01k_04

R61 *3.01k_04

http://hobi-elektronika.net

CPU 7/7 (RESERVED)

Sheet 9 of 49

B.Schematic Diagrams

CPU 7/7

(RESERVED)

B - 10 CPU 7/7 (RESERVED)

Page 10

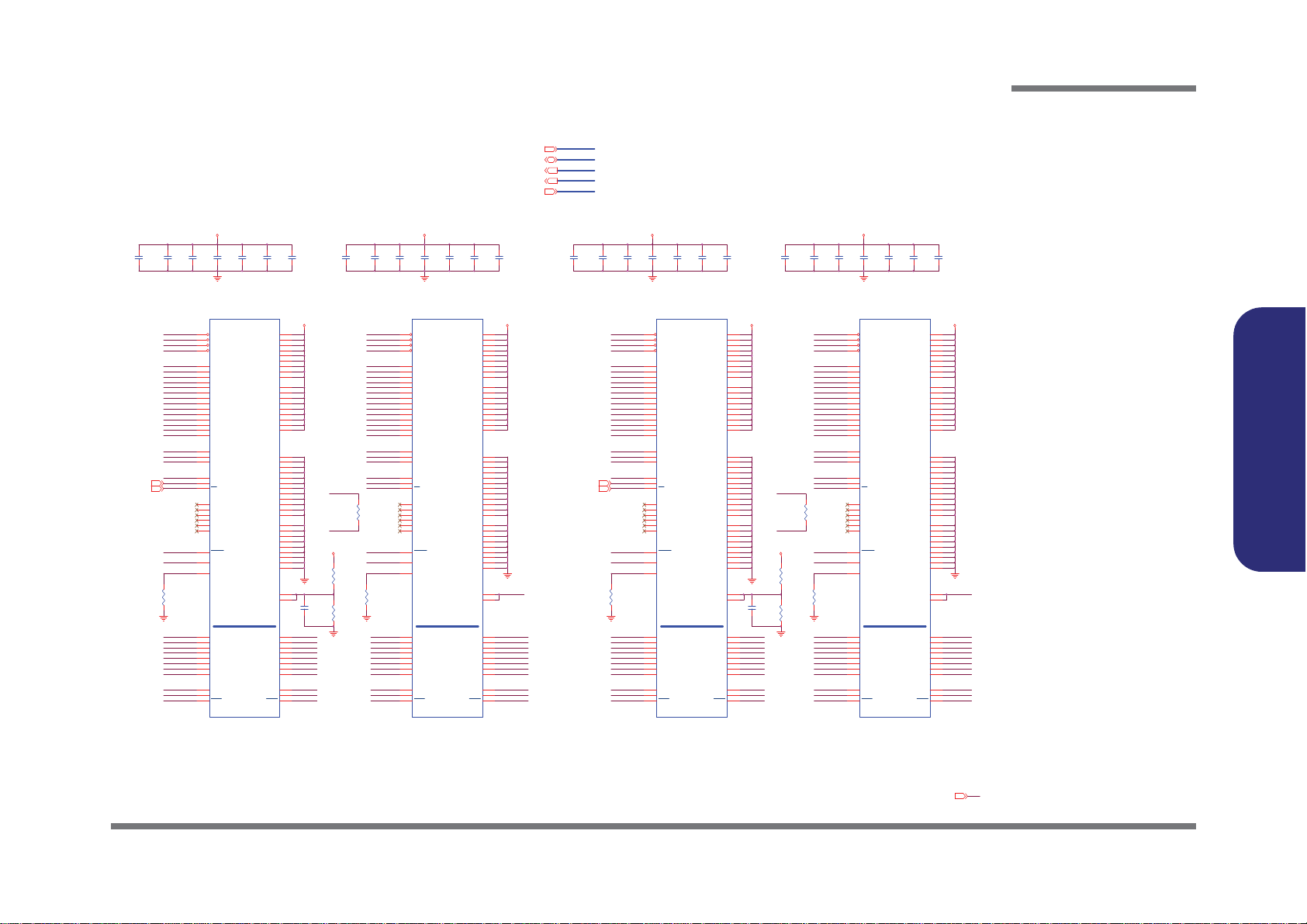

DDR3 SO-DIMM_0

C285

.1U_16V_04

C287

.1U_16V_04

+

C334

*220u_4V_V_A

C284

1U_6.3V_04

C323

.1U_16V_04

C337 . 1U_16V_04

C365 1U _6.3V_04

C313

10U_6.3V_08

C342

1U_6.3V_04

C336 1U _6.3V_04

C301

.1U_16V_04

C319

1U_6.3V_04

RN14

8P4RX10K_04

1

2

3456

7

8

C282

.1U_16V_04

C343

1U_6.3V_04

C316

.1U_16V_04

C318

1U_6.3V_04

C283

.1U_16V_04

C312

.1U_16V_04

C288

10U_6.3V_06

C290

1U_6.3V_04

R232 0_04

R220 10K_04

C279

10U_6.3V_06

SO-DIMM A

JD IMM1A

AS0A621-U2SN-7F

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC #

83

A13

119

A14

80

A15

78

DQ0

5

DQ1

7

DQ2

15

DQ3

17

DQ4

4

DQ5

6

DQ6

16

DQ7

18

DQ8

21

DQ9

23

DQ10

33

DQ11

35

DQ12

22

DQ13

24

DQ14

34

DQ15

36

DQ16

39

DQ17

41

DQ18

51

DQ19

53

DQ20

40

DQ21

42

DQ22

50

DQ23

52

DQ24

57

DQ25

59

DQ26

67

DQ27

69

DQ28

56

DQ29

58

DQ30

68

DQ31

70

DQ32

129

DQ33

131

DQ34

141

DQ35

143

DQ36

130

DQ37

132

DQ38

140

DQ39

142

DQ40

147

DQ41

149

DQ42

157

DQ43

159

DQ44

146

DQ45

148

DQ46

158

DQ47

160

DQ48

163

DQ49

165

DQ50

175

DQ51

177

DQ52

164

DQ53

166

DQ54

174

DQ55

176

DQ56

181

DQ57

183

DQ58

191

DQ59

193

DQ60

180

DQ61

182

DQ62

192

DQ63

194

BA0

109

BA1

108

RAS#

110

WE#

113

CAS#

115

S0#

114

S1#

121

CKE0

73

CKE1

74

CK0

101

CK0#

103

CK1

102

CK1#

104

SDA

200

SCL

202

SA1

201

SA0

197

DM0

11

DM1

28

DM2

46

DM3

63

DM4

136

DM5

153

DM6

170

DM7

187

DQS0

12

DQS1

29

DQS2

47

DQS3

64

DQS4

137

DQS5

154

DQS6

171

DQS7

188

DQS0#

10

DQS1#

27

DQS2#

45

DQS3#

62

DQS4#

135

DQS5#

152

DQS6#

169

DQS7#

186

ODT0

116

ODT1

120

BA2

79

R229 *0_04

C315

1U_6.3V_04

C289

1U_6.3V_04

C607 . 1U_16V_04

C311

1U_6.3V_04

C298 *10p_50V_NPO_04

C363

.1U_10V_X7R_04

R237

1K_1%_04

C310 *10p_50V_NPO_04

+

C346

220u_4V_V_A

C280

10U_6.3V_06

C286

.1U_16V_04

R247 1K_1%_04

C322

.1U_16V_04

M_A_D Q1

M_A_D Q2

M_A_D Q3

M_A_D Q4

M_A_D Q29

M_A_D Q30

M_A_D Q31

M_A_D Q32

M_A_D Q33

M_A_D Q34

M_A_D Q35

M_A_D Q36

M_A_D Q37

M_A_D Q39

M_A_D Q40

M_A_D Q41

M_A_D Q42

M_A_D Q43

M_A_D Q44

M_A_D Q45

M_A_D Q46

M_A_D Q47

M_A_D Q38

M_A_D Q49

JD IMM1B

AS0A621-U2SN-7F

VDD1

75

VDD2

76

VDD3

81

VDD4

82

VDD5

87

VDD6

88

VDD7

93

VDD8

94

VDD9

99

VDD10

100

VDD11

105

VDD12

106

VDDSPD

199

NC1

77

NC2

122

NCTEST

125

VREF_D Q

1

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VSS16

44

VSS17

48

VSS18

49

VSS19

54

VSS20

55

VSS21

60

VSS22

61

VSS23

65

VSS24

66

VSS25

71

VSS26

72

VSS27

127

VSS28

128

VSS29

133

VSS30

134

VSS31

138

VSS32

139

VSS33

144

VSS34

145

VSS35

150

VSS36

151

VSS37

155

VSS38

156

VSS39

161

VSS40

162

VSS41

167

VSS42

168

VSS43

172

VSS44

173

VSS45

178

VSS46

179

VSS47

184

VSS48

185

VSS49

189

VSS50

190

VSS51

195

VSS52

196

G2

GND2

G1

GND1

VTT2

204

VTT1

203

VREF_C A

126

RESET#

30

EVENT#

198

VDD13

111

VDD14

112

VDD16

118

VDD15

117

VDD17

123

VDD18

124

M_A_D Q50

M_A_D Q28

M_A_D Q51

M_A_D Q52

M_A_D Q53

M_A_D Q54

1.5V

C325

1U_6.3V_04

C299

.1U_16V_04

M_A_D Q55

M_A_D Q48

M_A_D Q5

M_A_D Q6

M_A_D Q56

3.3VS

3.3VS

M_A_D Q57

M_A_D Q58

M_A_D Q60

M_A_D Q61

M_A_D Q62

VTT_MEM

VTT_MEM

M_A_D Q63

M_A_D Q59

M_A_D Q7

M_A_D Q8

M_A_D Q9

M_A_D Q11

1.5V

1.5V

1.5V

M_A_D Q12

M_A_D Q13

M_A_D Q14

M_A_D Q15

M_A_D Q16

3.3VS

M_CLK_DDR15

M_A_BS15

M_A_D Q17

M_A_D Q18

M_A_D Q19

M_A_D Q10

M_A_D Q21

M_A_R AS#5

M_ODT15

DDR3_DRAMRST#4,11

SMB_CLK2,11,20

M_A_D Q22

M_A_D Q0

M_A_D Q23

M_A_D Q24

M_A_D Q25

M_A_D Q26

M_CLK_DDR#15

M_A_C AS#5

M_A_W E#5

M_A_D Q27

M_A_D Q20

M_A_BS05

M_ODT05

VTT_MEM11,39

1.5V4,11,36,39

M_CLK_DDR05

M_CKE05

M_A_BS25

M_CKE15

M_A_D Q[63:0 ] 5

M_CS#15

M_CLK_DDR#05

M_CS#05

TS#_DIMM0_14, 11

SMB_DATA2,11,20

M_A_DQS[7:0]5

M_A_D QS#[ 7: 0]5

M_A_D M[7: 0]5

M_A_A[ 15 :0 ]5

MVREF _DQ_DI M09

3.3VS2,11,12,13, 19,20,21,22,23,24,25,26,28, 29,30,31,32,34, 35,36,41,42,45

SA0_DIM1 11

SA1_DIM1 11

CHANGE TO STANDARD

CLOSE TO SO-DIMM_0

MVREF _DIM0

20mils

signal/space/signal:

Layout Note:

8 / 4 / 8

20mils

MVREF_DIM0

SA0_DIM0

SA1_DIM0

M_CLK_DDR0

M_CLK_DDR#1M_CLK_DDR1

M_A_D M7

M_A_D M6

M_A_D M5

M_CLK_DDR#0

M_A_D M4

M_A_D M3

M_A_D M1

M_A_D M2

M_A_D M0

ME issue

Cost down

M_A_A9

M_A_A8

M_A_A7

M_A_A5

M_A_A6

M_A_A4

M_A_A3

M_A_A2

M_A_A1

M_A_A0

M_A_A15

M_A_A14

M_A_A13

M_A_A11

M_A_A12

M_A_A10

M_A_D QS0

M_A_D QS1

M_A_D QS2

ME issue

M_A_D QS3

M_A_D QS4

M_A_D QS5

M_A_D QS6

M_A_D QS7

M_A_D QS#0

M_A_D QS#1

M_A_D QS#2

M_A_D QS#3

M_A_D QS#4

M_A_D QS#5

M_A_D QS#6

M_A_D QS#7

Sheet 10 of 49

DDR3 SO-DIMM_0

http://hobi-elektronika.net

Schematic Diagrams

B.Schematic Diagrams

DDR3 SO-DIMM_0 B - 11

Page 11

Schematic Diagrams

MVREF_DIM1

SO-DIMM B

CHANGE TO STANDARD

C338

1U_6.3V_04

R244 *0_04

C320

1U_6.3V_04

C332

1U_6.3V_04

C356

.1U_16V_04

JDIMM2B

AS0A621-UASN -7F

VDD1

75

VDD2

76

VDD3

81

VDD4

82

VDD5

87

VDD6

88

VDD7

93

VDD8

94

VDD9

99

VDD10

100

VDD11

105

VDD12

106

VDDSPD

199

NC1

77

NC2

122

NCTEST

125

VREF_DQ

1

VSS1

2

VSS2

3

VSS3

8

VSS4

9

VSS5

13

VSS6

14

VSS7

19

VSS8

20

VSS9

25

VSS10

26

VSS11

31

VSS12

32

VSS13

37

VSS14

38

VSS15

43

VSS16

44

VSS17

48

VSS18

49

VSS19

54

VSS20

55

VSS21

60

VSS22

61

VSS23

65

VSS24

66

VSS25

71

VSS26

72

VSS27

127

VSS28

128

VSS29

133

VSS30

134

VSS31

138

VSS32

139

VSS33

144

VSS34

145

VSS35

150

VSS36

151

VSS37

155

VSS38

156

VSS39

161

VSS40

162

VSS41

167

VSS42

168

VSS43

172

VSS44

173

VSS45

178

VSS46

179

VSS47

184

VSS48

185

VSS49

189

VSS50

190

VSS51

195

VSS52

196

G2

GND2

G1

GND1

VTT2

204

VTT1

203

VREF_CA

126

RESET#

30

EVENT#

198

VDD13

111

VDD14

112

VDD16

118

VDD15

117

VDD17

123

VDD18

124

Layout Note:

M_B_D Q31

M_B_D Q46

M_B_D Q13

M_B_D Q24

M_B_D Q56

M_B_D Q28

M_B_D Q11

M_B_D Q23

M_B_D Q61

M_B_D Q62

M_B_D Q58

M_B_D Q50

M_B_D Q1

M_B_D Q16

M_B_D Q60

M_B_D Q2

M_B_D Q40

M_B_D Q54

M_B_D Q41

M_B_D Q57

M_B_D Q37

M_B_D Q25

M_B_D Q30

M_B_D Q27

M_B_D Q44

JDIMM2A

AS0A621-UASN-7F

A0

98

A1

97

A2

96

A3

95

A4

92

A5

91

A6

90

A7

86

A8

89

A9

85

A10/AP

107

A11

84

A12/BC#

83

A13

119

A14

80

A15

78

DQ0

5

DQ1

7

DQ2

15

DQ3

17

DQ4

4

DQ5

6

DQ6

16

DQ7

18

DQ8

21

DQ9

23

DQ10

33

DQ11

35

DQ12

22

DQ13

24

DQ14

34

DQ15

36

DQ16

39

DQ17

41

DQ18

51

DQ19

53

DQ20

40

DQ21

42

DQ22

50

DQ23

52

DQ24

57

DQ25

59

DQ26

67

DQ27

69

DQ28

56

DQ29

58

DQ30

68

DQ31

70

DQ32

129

DQ33

131

DQ34

141

DQ35

143

DQ36

130

DQ37

132

DQ38

140

DQ39

142

DQ40

147

DQ41

149

DQ42

157

DQ43

159

DQ44

146

DQ45

148

DQ46

158

DQ47

160

DQ48

163

DQ49

165

DQ50

175

DQ51

177

DQ52

164

DQ53

166

DQ54

174

DQ55

176

DQ56

181

DQ57

183

DQ58

191

DQ59

193

DQ60

180

DQ61

182

DQ62

192

DQ63

194

BA0

109

BA1

108

RAS#

110

WE#

113

CAS#

115

S0#

114

S1#

121

CKE0

73

CKE1

74

CK0

101

CK0#

103

CK1

102

CK1#

104

SDA

200

SCL

202

SA1

201

SA0

197

DM0

11

DM1

28

DM2

46

DM3

63

DM4

136

DM5

153

DM6

170

DM7

187

DQS0

12

DQS1

29

DQS2

47

DQS3

64

DQS4

137

DQS5

154

DQS6

171

DQS7

188

DQS0#

10

DQS1#

27

DQS2#

45

DQS3#

62

DQS4#

135

DQS5#

152

DQS6#

169

DQS7#

186

ODT0

116

ODT1

120

BA2

79

M_B_D Q3

M_B_D Q7

M_B_D Q9

M_B_D Q34

M_B_D Q5

C367

.1U_16V_04

C354 1U _6.3V_04

M_B_D Q47

M_B_D Q43

M_B_D Q38

M_B_D Q17

C324

10U_6.3V_08

R235

1K_1%_04

M_B_D Q42

M_B_D Q8

M_B_D Q59

M_B_D Q35

M_B_D Q36

C349

10U_6.3V_08

C371

.1U_16V_04

8 / 4 / 8

M_B_D Q4

M_B_D Q26

M_B_D Q63

M_B_D Q33

C369

.1U_16V_04

C373

.1U_16V_04

M_B_D Q45

M_B_D Q48

M_B_D Q55

M_B_D Q29

M_B_D Q15

C341

.1U_16V_04

C359

1U_6.3V_04

M_B_D Q10

M_B_D Q52

M_B_D Q53

R243 0_04

C358

.1U_10V_X7R_04

M_B_D Q6

M_B_D Q19

M_B_D Q18

M_B_D Q0

M_B_D Q12

C339

.1U_16V_04

R248 1 K_1%_04

M_B_D Q20

M_B_D Q39

M_B_D Q49

M_B_D Q51

M_B_D Q21

C355 *10p_50V_NPO_04

C372

.1U_16V_04

M_B_D Q32

M_B_D Q14

M_B_D Q22

C353

.1U_16V_04

C374

1U_6.3V_04

C361 *10p_50V_NPO_04

C357

.1U_16V_04

C368

1U_6.3V_04

C376 1U _6.3V_04

C330

1U_6.3V_04

C317

1U_6.3V_04

C335

1U_6.3V_04

C362 . 1U_16V_04

C377 . 1U_16V_04

C348

10U_6.3V_08

C340

1U_6.3V_04

C370

.1U_16V_04

C366

10U_6.3V_08

1.5V

VTT_M EM

3.3VS

1.5V

1.5V

1.5V

DDR3_DRAMRST#4,10

1.5V4,10,36,39

VTT_M EM

SMB_CLK2,10, 20

SMB_DATA2,10,20

VTT_MEM10,39

M_B_A[1 5:0 ]5 M_B_D Q[6 3:0] 5

TS#_D IMM0_14,10

M_B_R AS#5

M_B_ BS15

M_CLK_DDR35

M_B_W E#5

M_B_C AS#5

M_CLK_DDR#35

M_B_ BS25

M_C KE25

M_CLK_DDR25

M_B_ BS05

M_CLK_DDR#25

M_C S#35

M_C KE35

M_OD T25

M_OD T35

M_C S#25

M_B_DQS#[7:0]5

M_B_DQS[7:0]5

M_B_D M[7: 0]5

SA0_DI M110

3.3VS2,10,12,13,19,20,21,22,23,24,25,26,28,29,30,31,32,34,35,36,41,42,45

MVR EF _DQ _D IM19

SA1_DI M110

SO-DIMM_1 is placed farther from the GMCH than SO-DIMM_0

M_B_A4

M_B_A6

M_B_A5

M_B_A1 3

M_B_A1 2

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A7

M_B_A8

M_B_A9

M_B_A1 0

M_B_A1 1

M_B_A1 4

20mils

Layout Note:

Cost down

SA1_DIM1

signal/space/signal:

CLOSE TO SO-DIMM _1

M_B_A1 5

M_B_D M5

M_B_D M6

M_B_D M7

M_B_D M0

M_B_D M2

M_B_D M1

M_B_D M3

M_B_D M4

M_B_D QS0

M_B_D QS6

M_B_D QS5

M_B_D QS4

M_B_D QS3

M_B_D QS2

M_B_D QS1

M_B_D QS#3

M_B_D QS#2

M_B_D QS#1

M_B_D QS#0

M_B_D QS7

M_B_D QS#7

M_B_D QS#6

M_B_D QS#5

M_B_D QS#4

M_CLK_DDR2 M_CLK_DDR#2

M_CLK_DDR3 M_CLK_DDR#3

CU? ?

MVREF_DIM1

SA0_DIM1

Sheet 11 of 49

DDR3 SO-DIMM_1

http://hobi-elektronika.net

DDR3 SO-DIMM_1

B.Schematic Diagrams

B - 12 DDR3 SO-DIMM_1

Page 12

Panel, Inverter, CRT

Sheet 12 of 49

Panel, Inverter,

CRT

NB_ENAVDD

J_CRT1

108AH15F ST04N1C3

8

7

6

5

4

3

2

1

9

10

11

12

13

14

15

GND2

GND1

DDCDATA

24 mil

FGRN

FBLUE

VSYNC

DDCLK

HSYNC

FRED

C3

220P_50V_X7R_04

C5

1000P_50 V_X7R_04

C1

1000P_50V_X7R_04

C2

220P_50V_X7R_04

R387

*10K_04

CRT

L52

*WCM3216F2S-161T03

1

4

2

3

D24

BAV99 RECTI FIER

A

C

AC

BRIGHTNESS35

.

L48 FC M1005MF-600T0 1_04

.

L50 FC M1005MF-600T0 1_04

.

L49 FC M1005MF-600T0 1_04

L54

*WCM3216F2S-161T03

1

4

2

3

L56

*WCM3216F2S-161T03

1

4

2

3

L58

*WCM3216F2S-161T03

1

4

2

3

.

L36 FCM1005MF-600T01_04

.

L37 FCM1005MF-600T01_04

LVDS-U2P

.

L38 FCM1005MF-600T01_04

C504

22P_50V_04

C506

22P_50V_04

C508

22P_50V_04

LVDS-U2N

C17

.1U_16V_04

NB_ENAVD D22, 35

PANEL

RLVDS-LC LKP

RLVDS-U CLKN

RLVDS-U 1N

RLVDS-U 1P

RLVDS-L1P

RLVDS-L1N

RLVDS-LC LKN

RLVDS-U 2N

RLVDS-L0N

RLVDS-L0P

RLVDS-U 2P

RLVDS-U 0N

RLVDS-U CLKP

RLVDS-L2N

RLVDS-L2P

RLVDS-U 0P

INV_BLON

2A

C502

0.22u_10V_Y5V_04

C6

0.22u_10V_Y5V_04

R1 33_04

DDCLK

HSYNC

R388

0_04

DDCDATA

RN1

2.2K_8P4R_0 4

8 1

7 265

3

4

R7 33_04

C4

0.22u_10V_Y5V_04

DAC_DDCADATA22

DAC_HSYNC22

DAC_VSYNC22

DAC_DDCACLK22

3.3VS

FGRN

FRED

FBLUE

U30

IP4772CZ16

VCC_SYNC

1

VCC_VIDEO

2

VIDEO_1

3

VIDEO_2

4

VIDEO_3

5

GND

6

VCC_DDC

7

BYP

8

DDC_OUT1

9

DDC_IN1

10

DDC_IN211DDC_OUT2

12

SYNC_IN113SYNC _OUT1

14

SYNC_IN215SYNC _OUT2

16

5VS

VSYNC

5VS

DAC_GREEN

DAC_RED

C514

22P_50V_04

C532

22P_50V_04

DAC_BLUE

C503

22P_50V_04

C665

22P_50V_04

R372

150_1%_04

R370

150_1%_04

R371

150_1%_04

C505

22P_50V_04

C507

22P_50V_04

DAC_BLUE22

DAC_GREEN22

DAC_RED22

LVDS-U1P 22

LVDS-U1N

LVDS-U1P

LVDS-U1N 22

C510

*1U_10V_06

NEAR PIN4,5

LVDS-U0P 22

LVDS-U0P

LVDS-U0N

LVDS-U0N 22

U32

G5243A

VIN

4

VIN

5

EN

3

VOUT

1

GND

2

C511

.1U_16V_ 04

C512

10U_10V_08

R376

*100K_04

R377

100K_04

LVDS-UC LKN 22

LVDS-UCLKP 22

PLVDD

3.3VS

LVDS-UCLKN

LVDS-UCLKP

2A

RLVDS-U 1N

RLVDS-U2N

RLVDS-U 0P

RLVDS-U CLKP

RLVDS-U CLKN

RLVDS-U 1P

RLVDS-U 0N

RLVDS-U2P

L53

*WCM3216F2S-161T03

1

4

2

3

BKL_EN

L57

*WCM3216F2S-161T03

1

4

2

3

BLON

L55

*WCM3216F2S-161T03

1

4

2

3

L51

*WCM3216F2S-161T03

1

4

2

3

3.3VS

P_DDC_CLK

P_DDC_DATA

LVDS-L2N

LVDS-L2P

.

L2

HCB1608KF-121T25

C513

.1U_50V_06

R411 100K_04

C15

.1U_50V_06

C16

.1U_50V_06

U35B

74LVC08PW

4

5

6

147

U35D

74LVC08PW

12

13

11

147

C509

.1U_16V_04

R401

*1M_04

PLEASE CLOSE TO CONNECTOR

R358

2.2K_04

U35A

74LVC08PW

1

2

3

147

.

L1

HCB1608KF-121T25

R353

2.2K_04

C529

1U_6.3V_X5R_04

R409 *100K_04

C14

10u_25V_NPO_12

R400

4.7K_04

C11

10u_25V_NPO_12

U35C

74LVC08PW

9

10

8

147

J_LCD1

87216-4006

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

Gnd 1G1Gnd 2

G2

R410 *100K_04

3.3V

3.3V

LVDS-L1N 2 2

3.3V

3.3V

LVDS-L1N

LVDS-L0N 2 2

LVDS-L1P 22

3.3VS

LVDS-L1P

LVDS-L0P 22

PLVDD

VIN

PLVDD

3.3VS

LVDS-L0N

LVDS-LCLKN 22

LEDPL_VIN

LVDS-L0P

LVDS-LCLKP 22

LVDS-LCLKN

LVDS-LCLKP

VIN 36,37,39,4 0,41,42, 43,44

LEDPL_VIN

5VS 19, 22,25,26, 30,32,34 ,36,41, 42,45

ALL_SYS_PWRGD21,35

BKL_EN35

3.3V 3, 4,13,17,19,20,21,23, 24,26,28,29,31, 32,33,36,38,39,40,43

SB_BLON24

LID_SW#30,35

LVDS-U2N 22

3.3VS 2,10, 11,13,19 ,20,21, 22,23,24, 25,26, 28,29,30, 31,32,34 ,35,36,41, 42,45

LVDS-L2P 22

LVDS-L2N 2 2

LVDS-U2P 22

RLVDS-LCLKP

RLVDS-LCLKN

RLVDS-L2N

RLVDS-L0N

RLVDS-L1P

RLVDS-L2P

BLON22

RLVDS-L0P

RLVDS-L1N

P_DDC_CLK 22

P_DDC_DATA 22

D33

*RB751V

A C

INVERTER CONNECTOR

INV_BLON

3.3V

For 71

hannstar

LCD issue

http://hobi-elektronika.net

Schematic Diagrams

B.Schematic Diagrams

Panel, Inverter, CRT B - 13

Page 13

3V3_RUN

PLACE NEAR BALL S

3V3_RUN

PEX_VDD_SVDD

PEX_PLLVDD

1

R32

10K_04

C37

4.7U_6. 3V_06

PEG_CLKREQ#

PERSTB#

3V3_RUN

3V3_RUN17,43

PLACE NEAR BALLS

2200 mA

C51

10U_6.3V_06

PLACE NEAR BGAPLACE NEAR BALL S

VGA_ROM_SI

C52

1U_6.3V_04

PEX_RX2#

PEX_RX4

PEG_RX#0

PEG_RX2

PEG_RX3

PEG_RX#5

PEX_RX6#

PEX_RX5#

PEX_RX1#

PEX_RX4#

PEG_RX#2

PEX_RX6

PEX_RX3

PEX_RX7

PEG_RX0

PEX_RX0#

PEG_RX4

PEX_RX7#

VGA_ROM_SO

PEG_RX1

PEG_RX#1

PEX_RX3#PEG_RX#3

PEG_RX5

PEX_RX1

PEX_RX5

PEG_RX#4

PEX_RX2

PEX_RX0

VGA_ROM_SCLK

VGA_STRAP0

VGA_STRAP1

VGA_STRAP2

VGA_PEXCLK

VGA_PEXCLK#

PEG_TX0

PEG_TX#0

PEG_TX1

PEG_TX#1

PEG_TX2

PEG_TX#2

PEG_TX3

PEG_TX#3

PEG_TX4

PEG_TX#4

B4100

PEG_TX5

PEG_TX#5

PEG_TX6

PEX_TERM P

PEG_TX#6

PEG_TX7

PEG_TX#7

GPU_TESTMODE

B5100

PS1_GND_SEN SE

3.3VS2,10,11, 12,19,20, 21,22,23, 24,25,26, 28,29,30, 31,32,34, 35,36,41, 42,45

C26

10U_6.3V_06

0

PLACE NEAR BALLS

C34

4.7U_6. 3V_06

PLACE NEAR BGA

R375

10K_04

R19 *20K_1%_04

R380 *34.8K_1 %_04

C97 .1U_10V_X7R_04

C101

.1U_16V_04

C515

20P_50V_04

C57

1U_6.3V_04

C77 .1U_10V_X7R_04

C72 .1U_10V_X7R_04

C107

.1U_16V_04

C42

.1U_16V_04

R66 2.49K_1%_04

R43 *10K_1%_04

Q2

AO3409

G

DS

C67 .1U_10V_X7R_04

R34 2.2K_04

R16 34.8K_1%_04

.

L5

HCB1005KF -121T20

C84

1U_6.3V_04

C33

22n_10V_Y 5V_04

C73 .1U_10V_X7R_04

R40 15K_1%_04

R42 34.8K_1%_04

6-03-00011-0FA N11M-OP1--B-B1 B 4100 512M

C66 .1U_10V_X7R_04

C70

.1U_16V_04

R390

10K_04

R50

10K_04

R52 *0_04

C43

.1U_16V_04

14/16 XTAL_PLL

U36D

U_GPU_GB1_128_1

D2

XTAL SSI N

AF9

SP_PLLVDD

AD9

VID_PLLVD D

AE9

PLLVDD

B2

XTALOU T

D1

XTAL OU TBU FF

B1

XTAL IN

U33

SST25VF512A

1

CS

2

SO

3

WP

4

GND

5

SI

6

SCK

7

HOLD8VCC

C109

1U_6.3V_04

C35

.01U_16V_04

C64

1U_6.3V_04

HDA_SYNC

HDA_SDO

DACB_CSYNC

G96

GT216

GT216

G96

G96

HDA_SDI

HDA_RST

PGOOD_OUT*

13/16 MISC2

HDA_BCLK

U36K

U_GPU_GB1_128_1

M9

MULTI_STRAP_REF 1_GND

N9

MULTI_STRAP_REF 0_GND

AB5

CEC

A7

RFU

B7

RFU

C7

RFU

D6

RFU

D7

RFU

J25

RFU

J26

RFU

K9

GND

AK14

GND

C5

RFU

A4

BUFRST

A5

SPDIF

G6

I2CH_SDA

F6

I2CH_SCL

D4

ROM_SCLK

C4

ROM_SO

D3

ROM_SI

C3

ROM_CS

R33 100K_04

H13

H8_0D4_4

R26 * 4.99K_1%_04

U4

74AHC1G08GW

1

2

5

4

3

H11

H8_0D4_4

H15

H8_0D4_4

C61

4.7U_6. 3V_06

C32

.1U_16V_04

GPU

R373 10K_1%_04

C63 .1U_10V_X7R_04

C122

4.7U_6. 3V_06

R41 *10K_1%_04

C103

.1U_16V_ 04

.

L4

HCB1005KF -121T20

R379 20K_1%_0 4

C95

.1U_16V_04

R18

22K_1%_04

R56 40.2K_1%_04

.

L3 HCB1005KF-121T20

C75

.1U_16V_ 04

R57

100K_04

C85 .1U_10V_X7R_04

R39 0_04

12mil

16mil

16mil

16mil

GT21x

G9x

GND_SENSE

VDD_SENSE

NC

NC

NC

NC

NC

G9x

GT21xG9x

GT21x

PEX_CAL_PD_VDDQ

1/16 PCI_EXPRESS

PEX_CAL_PU_GN D

U36A

U_GPU_GB1_128_1

AP34

PEX_RX15

AR34

PEX_RX15

AP32

PEX_TX15

AN32

PEX_TX15

AR32

PEX_RX14

AR31

PEX_RX14

AM32

PEX_TX14

AM31

PEX_TX14

AP31

PEX_RX13

AN31

PEX_RX13

AM30

PEX_TX13

AM29

PEX_TX13

AN29