Page 1

Model 5100S/5500S

Service Manual

Mainboard

D/D board

Inverter board

Hard transfer board

Specifications are subject to change without notice. October, 2000

Page 2

Contents

System specifications........................................................................................... 1

Chipsets ................................................................................................................ 3

SiS630S .................................................................................................................3

PC Card Chipset.....................................................................................................8

CPU and Memory .................................................................................................. 9

CPU ........................................................................................................................ 9

Adding or replacing the processor. ........................................................................10

A: Remove the heat sink ................................................................................................10

B: Remove the processor ..............................................................................................11

C: Insert a new processor..............................................................................................12

D: Reinstall the heat sink................................................................................................13

E: Changing the SW1 DIP Switch settings ....................................................................13

Memory .................................................................................................................15

Expansion Memory Socket .................................................................................... 16

Installing a Memory Module ............................................................................................17

Changing the S3 DIP Switch settings ............................................................................18

Removing a Memory Module..........................................................................................19

Drive information and Pin assignments ............................................................. 20

Storage Devices....................................................................................................20

HDD (BUIL T-IN).................................................................................................................20

HDD PIN ASSIGNMENT.................................................................................................20

Removing the HDD from the notebook ..........................................................................21

Removing the HDD from its tray ....................................................................................21

Inserting the HDD...........................................................................................................21

FDD ..................................................................................................................................22

FDD PIN ASSIGNMENT .................................................................................................22

Removing the Floppy Disk Drive ....................................................................................22

Inserting the Floppy Disk Drive.......................................................................................23

DVD-ROM.........................................................................................................................24

DVD-ROM PIN ASSIGNMENT .......................................................................................24

Removing the DVD-ROM Module...................................................................................25

Inserting the DVD-ROM module.....................................................................................25

CD-ROM (OPTIONAL)......................................................................................................26

CD-ROM PIN ASSIGNMENT..........................................................................................26

Interface Pin Assignments .....................................................................................27

RS-232 Serial Interface ..................................................................................................27

Parallel Interface.............................................................................................................27

USB Interface .................................................................................................................27

Internal trackpad Interface ..............................................................................................28

External Monitor Interface...............................................................................................28

External Keyboard/PS2 Mouse Interface........................................................................28

PCMCIA CardBus Interface............................................................................................29

Internal PCI Interface ......................................................................................................30

LCD Interface .................................................................................................................31

Power.................................................................................................................. 32

Application: ...........................................................................................................32

Charge board ........................................................................................................35

Inverter board ........................................................................................................38

Adaptor .................................................................................................................39

Page 3

Battery Pack..........................................................................................................41

Battery diagram.....................................................................................................44

Component diagrams and part numbers ........................................................... 45

Schematic Drawings ........................................................................................... 51

Page 4

System specifications

The 5100S/5500S uses the SiS630S core logic and InSyde BIOS code. This product also

features three bays for user-installed modules (a HDD, a CD-ROM or DVD-ROM or a FDD),

and has an optional Fax/Modem MDC module.

The main unit of the Model 5100S/5500S Notebook PC has the following components:

– Intel Mobile Pentium III with AGP technology-based mainboard, using the SiS630S

chipset solution supporting SDRAM with 0 MB on-board DRAM, expandable to

32MB, 64MB, 96MB, 128MB, 192MB, 256MB, or 512MB using one or two expansion

S.O. DIMMs

– user-installed modules: CD-ROM, DVD-ROM and an FDD

– main storage (HDD) bay: principal HDD, 2.5” up to 12GB(Ultra DMA33/66)

– User interfaces:

· one internal keyboard, 84 keys (depending on the language)

· one built-in trackpad

· one 800x600 SVGA TFT 12.1” LCD display panel with CCFT backlight

– Power Solutions

· power bay: battery pack

· AC/DC adapter

CPU ( µPGA2)

Intel Celeron-450 (1.6V)

Intel Celeron-500 (1.6V)

Intel Celeron-550 (1.6V)

Intel Celeron-700 (1.6V)

Intel Pentium III-600 * (1.6V)

Intel Pentium III-650 * (1.6V)

Intel Pentium III-700 * (1.6V)

Intel Pentium III-750 * (1.6V)

Intel Pentium III-850 * (1.6V)

* with Intel SpeedStep Technology

CD-ROM (MKE CR175) 24X removable module

CD type 12.8cm

Height 12.7mm

Data transfer rate 3600KB/s (max)

Random access time <100ms

Compliance Multimedia PC-2 Spec.

Transport drawer type load/eject

Interface PCI local bus master IDE

FDD

removable 3.5" 1.44MB

Memory

L2 Cache (on die)

Celeron(.18) series 128KB

Pentium III series 256KB

On board RAM 0MB

Upgradable to 512MB (MAX.)

BIOS

InSyde 256KB

HDD

Removable module up to 12GB

Drive size 2.5"

Height maximum 12.7mm

Average access time <13ms

Interface: PCI local bus master

IDE with Ultra DMA33/66 I/F

1

Page 5

Keyboard

Keys 84

Fn key support YES

Integrated numeric keypad YES

Inverted "T" layout cursor keys YES

TouchPad

built-in x 1

Interface PS/2

Power Supply

AC adapter

AC-in 100-240V 47-63Hz

Capacity 65W

Battery pack Li-Ion

Physical

Dimension 316mm(W)

256mm(D)

38.5mm(H)

Weight 3KG (with Lithium-lon

battery)

Packaging

(standard)

AC/DC adaptor & power cord x 1

User™s manual (printed format) x 1

Power Saving Management

Doze mode YES

Sleep mode YES

Suspend/Resume mode YES

Suspend to HDD mode YES

Hot key control suspend YES

APM ver 1.2 support YES

ACPI Ver 1.0 support YES

LCD TFT/DSTN

Backlite CCFT

Size 12.1"

Resolution 800x600

Color (CRT) 16,77M

Monitor 1280x1024

Support non-interlaced

Display

LCD/CRT (simultaneous) YES

VGA/EGA/CGA/Hercules compatible

YES

AGP 3D graphics accelerator YES

Adjustable brightness (TFT) YES

(Optional)

Car adapter x 1

Smart Li-Ion battery pack x 1

S.O. DIMM 32MB/64MB/128MB/256MB

Fax/modem module(56K, MDC) x 1

DVD-ROM (X8) x 1

CD-RW x1

Audio

3D, Sound Blaster compatible YES

Built-in speakers 2

Built-in microphone 1

External Audio Jacks

Speaker-out Jack YES

Microphone-in Jack YES

Ports

Serial port x 1

IrDA/SIR/ASK/FIR x 1

Parallel port x 1

15 pin external video port x 1

External 101/102 keyboard port/ PS/2 mouse

x 1

PC Card Standard Type I x 1

Modem (RJ-11) port for MDC x 1

USB connector x 1

speaker-out jack x 1

microphone-in jack x 1

LAN (RJ-45) port x 1

2

Page 6

Chipsets

SiS630S

– provides a high performance/low cost Desktop solution for the Intel mobile CPU

based system

– integrates a high performance North Bridge

– has an advanced hardware 2D/3D GUI engine, Super-South bridge or an external

AGP4X Slot

The SiS630S is a system-on-chip solution that complies with

– Easy PC Initiative which supports Instantly Available/OnNow PC technology

– USB

– Legacy Removal

– Slotless Design and FlexATX form factor

The SiS630S:

– integrates UltraAGPTM technology and advanced 128-bit graphic display interface.

– delivers AGP 4x performance and memory bandwidth up to 1 GB/s.

– supports an extra AGP Slot that supports 4X and Fast Write transactions.

– provides powerful hardware decoding DVD accelerator to improve the DVD

playback performance.

– Provides the standard interface for CRT monitors

– provides the Digital Flat Panel Port (DFP) for a standard interface between a

personal computer and a digital flat panel monitor.

– adopts Share System Memory Architecture which can flexibly utilize the frame

buffer size up to 64MB.

Key Features:

“Super-South Bridge” in SiS630S

- integrates all peripheral controllers/accelerators /interfaces.

- provides a total communication solution including 10/100Mb Fast Ethernet for

Office requirement and 1Mb HomePNA for Home Networking.

- offers AC’97 compliant interface that comprises digital audio engine with 3D-

hardware accelerator, on-chip sample rate converter, and professional wavetable

along with separate modem DMA controller.

- provides interface to Low Pin Count (LPC) operating at 33 MHz clock which is the

same as PCI clock on the host, and dual USB host controllers with six USB ports

that deliver better connectivity and 2 x 12Mb bandwidth.

- The built-in fast PCI IDE controller supports the ATA PIO/DMA, and the Ultra

DMA33/66 function that supports the data transfer rate up to 100 MB/s. It provides

the separate data path for two IDE channels that can eminently improve the

performance under the multi-tasking environment.

3

Page 7

Host Interface Controller

- Supports Intel mobile Pentium II/!!! CPUs

- Synchronous Host/DRAM Clock Scheme

- Asynchronous Host/DRAM Clock Scheme

Integrated DRAM Controller

- 3-DIMM/6-Bank of 3.3V SDRAM

- Supports Memory Bus up to 133 MHz

- System Memory Size up to 3 GB

- Up to 512MB per Row

- Supports 16Mb, 64Mb, 128Mb, 256Mb, 512Mb SDRAM Technology

- Suspend-to-RAM (STR)

- Relocatable System Management Memory Region

- Programmable Buffer Strength for CS#, DQM[7:0], WE#, RAS#, CAS#, CKE,

MA[14:0] and MD[63:0]

- Shadow RAM Size from 640KB to 1MB in 16KB increments

- Two Programmable PCI Hole Areas

Integrated A.G.P . Compliant T arget/66Mhz Host-to-PCI Bridge

- AGP v2.0 Compliant

- Supports Graphic Window Size from 4MBytes to 256MBytes

- Supports Pipelined Process in CPU-to-Integrated 3D A.G.P. VGA Access

- Supports 8 Way, 16 Entries Page Table Cache for GART to Enhance Integrated

A.G.P. VGA Controller

- Read/Write Performance

- Supports PCI-to-PCI Bridge Function for Memory Write from 33Mhz PCI Bus to

Integrated A.G.P. VGA

- Supports Additional AGP slot with 4X and Fast Write Transaction

Meet PC99 Requirements

PCI 2.2 Specification Compliant

High Performance PCI Arbiter

- Supports up to 4 PCI Masters

- Rotating Priority Arbitration Scheme

- Advanced Arbitration Scheme Minimizing Arbitration Overhead.

- Guaranteed Minimum Access Time for CPU And PCI Masters

Integrated Host-T o-PCI Bridge

- Zero Wait State Burst Cycles

- CPU-to-PCI Pipeline Access

- 256B to 4KB PCI Burst Length for PCI Masters

- PCI Master Initiated Graphical Texture Write Cycles Re-mapping

- Reassembles PCI Burst Data Size into Optimized Block Size

4

Page 8

Fast PCI IDE Master/Slave Controller

- Supports PCI Bus Mastering

- Native Mode and Compatibility Mode

- PIO Mode 0, 1, 2 , 3, 4

- Multiword DMA Mode 0, 1, 2

- Ultra DMA 33/66/100

- Two Independent IDE Channels Each with 16 DW FIFO

Virtual PCI-to-PCI Bridge

Integrated Ultra AGP VGA for Hardware 2D/3D Video/Graphics Accelerators

- Supports Tightly Coupled 64 Bits Host Interface to VGA to Speed Up GUI

Performance and Video Playback Frame Rate

- AGP v. 2.0 Compliant

- Zero-Wait-State 128x4 Post-Write Buffer with Write Combine Capability

- Zero-Wait-State 128x4 2-Way Read Ahead Cache Capability

- Re-locatable Memory-Mapped and I/O Address Decoding

- Flexible Design Shared Frame Buffer Architecture for Display Memory

- Shared System Memory Area up to 64MB

- Built-in 8K Bytes Texture Cache

- Supports High Quality Dithering

- Supports Bump Mapping

- Supports 8/16/24/32 BPP RGB/ARGB Texture Format

- Supports Video YUV Texture in All Supported Texture Formats

- 128-Bit 2D Engine with a Full Instruction Set

- Maximum 64 MB Frame Buffer with Linear Addressing

- Supports Hardware DVD Accelerator

- Supports Single Frame Buffer Architecture

- Supports Two Independent Video Windows with Overlay Function and Scaling

Factors

- Supports YUV-To-RGB Color Space Conversion

- Supports Graphic and Video Overlay Function

- Supports CD/DVD to TV Playback Mode

- Simultaneous Graphic and TV Video Playback Overlay

- Supports RGB555, RGB565, YUV422 and YUV420 Video Playback Format

- Supports Filtered Horizontal Up and Down Scaling Playback

- Supports DVD Sub-Picture Playback Overlay

- Supports DVD Playback Auto-Flipping

- Built-in Two Video Playback Line Buffers

- Built-in Programmable 24-bit True-Color RAMDAC up to 270 MHz Pixel Clock

RAMDAC Snoop Function

- Built-in Dual-Clock Generator

- Supports Multiple Adapters and Multiple Monitors

- Built-in PCI Multimedia Interface

- Supports Digital Flat Panel Port for Digital Monitor (LCD Panel)

5

Page 9

- Built-in VESA Plug and Display for CH7003, PanelLinkTM and LVDS Digital

Interface

- Built-in Secondary CRT Controller for Independent Secondary CRT, LCD or TV

digital output

- Supports VESA Standard Super High Resolution Graphic Modes

640x480 16/256/32K/64K/16M colors 120 Hz NI

800x600 16/256/32K/64K/16M colors 120 Hz NI

1024x768 256/32K/64K/16M colors 120 Hz NI

1280x1024 256/32K/64K/16M colors 85 Hz NI

1600x1200 256/32K/64K/16M colors 85 Hz NI

1920x1440 8bbp/16bbp 60NI

- Low Resolution Modes

- Supports Virtual Screen up to 4096x4096

- Fully Directx 7.0 Compliant

- Efficient and Flexible Power Management with ACPI Compliance

Low Pin Count Interface

- Forwards PCI I/O and Memory Cycles into LPC Bus

- Translates 8-/16-bit DMA Cycles into PCI Bus Cycles

Advanced PCI H/W Audio & Modem

Advanced Power Management

- Meets ACPI 1.0b Requirements

- Meets APM 1.2 Requirements

- ACPI Sleep States Include S1, S4, S5

- CPU Power States Include C0, C1, C2 C3

- Power Button with Override

- RTC Day-of-Month, Month-of-Year Alarm

- 24-bit Power Management Timer

- LED Blinking in S1 State

- System Power-Up Events Include: Power Button, Hot-Key, Keyboard Password/

Hot-

- Key, RTC Alarm, Modem Ring-In, LAN, PME#, AC’97 Wake-Up and USB

- Wake-Up

- Software Watchdog Timer

- Power Supply’98 Support

- PCI Bus Power Management Interface Spec. 1.0

Integrated DMA Controller

- Two 8237A Compatible DMA Controllers

- 8/16- bit DMA Data Transfer

- Distributed DMA Support

Integrated Interrupt Controller

- Two 8237A Compatible DMA Controllers

- Two 8259A Compatible Interrupt Controllers

- Level- or Edge-Triggered Programmable

6

Page 10

- Serial IRQ

- Interrupt Sources Re-routable to Any IRQ Channel

Three 8254 Compatible Programmable 16-bit Counters

- System Timer Interrupt

- Generate Refresh Request

- Speaker Tone Output

Integrated Keyboard Controller

- Hardwired Logic Provides Instant Response

- Supports PS/2 Mouse Interface

- Password Security and Password Power-Up

- System Sleep and Power-Up by Hot-Key

- KBC and PS2 Mouse Can Be Individually Disabled

Integrated Real Time Clock (RTC) with 256B CMOS SRAM

- Supports ACPI Day-of-Month and Month-of-Year Alarm

- 256 Bytes of CMOS SRAM

- Provides RTC H/W Year 2000 Solution

Universal Serial Bus Host Controller

- OpenHCI Host Controller with Root Hub

- Two USB Host Controllers

- Six USB Ports

- Supports Legacy Devices

- Over Current Detection

I2C Bus/SMBUS Series Interface

Integrated Fast Ethernet Controller and MAC Interface

- Plug and Play Compatible

- High-Performance 32-Bit PCI Bus Master Architecture with Integrated Direct

Memory

- Supports Big Endian and Little Endian Byte Alignments

- Implements Optional PCI 3.3v Auxiliary Power Source 3.3Vaux Pin And Optional

PCI

- Supports Software, Enhanced Software, and Automatic Polling Schemes to Internal

- PHY Status Monitor and Interrupt

- Supports 10base-T, 100base-Tx

NAND Tree for Ball Connectivity T esting

672-Balls BGA Package

1.8V Core with Mixed 3.3V and 5V I/O CMOS T echnology

7

Page 11

PC Card Chipset

The PCI1410 supports the following features:

- Ability to wake from D3 hot and D3 cold

- Fully compatible with the IntelE 430TX (Mobile Triton II) chipset

- A 144-Pin Low-Profile QFP (PGE), 144-ball MicroStar Ball Grid Array (GGU)

package, or 209-ball MicroStar Ball Grid Array (GHK) package

- 3.3-V core logic with universal PCI interfaces compatible with 3.3-V and 5-V PCI

signaling environments

- Mix-and-match 5-V/3.3-V 16-bit PC Cards and 3.3-V CardBus Cards

- Single PC Card or CardBus slot with hot insertion and removal

- Burst transfers to maximize data throughput on the PCI bus and the CardBus bus

- Parallel PCI interrupts, parallel ISA IRQ and parallel PCI interrupts, serial ISA

IRQ with parallel PCI interrupts, and serial ISA IRQ and PCI interrupts

- Serial EEPROM interface for loading subsystem ID and subsystem vendor ID

- Pipelined architecture allows greater than 130M bps sustained throughput from

CardBus-to-PCI and from PCI-to-CardBus

- Interface to parallel single-slot PC Card power interface switches like the TI

TPS2211

- Up to five general-purpose I/Os

- Programmable output select for CLKRUN

- Five PCI memory windows and two I/O windows available to the 16-bit PC Card

socket

- Two I/O windows and two memory windows available to the CardBus socket

- Exchangeable Card Architecture (ExCA) compatible registers are mapped in

memory and I/O space

- Intel 82365SL-DF and 82365SL register compatible

- Distributed DMA (DDMA) and PC/PCI DMA

- 16-Bit DMA on the PC Card socket

- Ring indicate, SUSPEND, PCI CLKRUN, and CardBus CCLKRUN

- Socket activity LED pins

- PCI Bus Lock (LOCK)

- Advanced Submicron, Low-Power CMOS Technology

- Internal Ring Oscillator

8

Page 12

CPU and Memory

CPU

The 5100S/5500S Notebook PC uses the Intel Mobile Pentium III/Celeron (.18) processor in a

µPGA2 package.

The Intel Mobile Pentium III/Celeron (.18) processor features an integrated L2 cache(256KB

for Pentium III and 128KB for Celeron (.18)) and a 64-bit high performance system bus.

The Mobile Pentium III/Celeron (.18) processor’s 64-bit wide Low Power Gunning Transceiver Logic system bus is compatible with the SIS630S AGPSet and provides a glue-less,

point-to-point interface for an I/O bridge/memory controller.

The Intel Mobile Pentium III and Celerons (.18) processors are fully compatible with all

software written for the Pentium processor with MMX technology, Pentium processor,

Intel486 microprocessor, and Intel386 microprocessor. In addition, they provide improved

multimedia & communications performance.

They feature:

Performance improved over existing mobile processors

- Supports the Intel Architecture with Dynamic Execution

- Supports the Intel Architecture MMX technology

Integrated primary (L1) instructions and data caches

- 4-way set associative, 32-byte line size, 1 line per sector

- 16-Kbyte instruction cache and 16-Kbyte writeback data cache

- Cacheable range programmable by processor programmable registers

Integrated second level (L2) cache

- 4-way set associative, 32-byte line size, 1 line per sector

- Operated at full core speed

- 128/256-Kbyte, ECC protected cache data array

Low Power GTL+ system bus interface

- 64-bit data bus, 100-MHz operation

- Uniprocessor, two loads only (processor and I/O bridge/memory controller)

- Short trace length and low capacitance allows for single ended termination

Voltage reduction technology

Pentium III processor clock control

- Quick Start for low power, low exit latency clock ‘throttling’

- Deep Sleep mode for extremely low power dissipation

Thermal diode for measuring processor temperature

9

Page 13

Adding or replacing the processor .

Note: If you plan on removing the heat sink, which is necessary to add or replace the

processor, you will need to have a replacement heat sink pad available. Before proceeding, please contact your dealer to get a replacement pad which you will need when you

reinstall the heat sink.

In order to add or replace the processor you must:

A: Remove the heat sink

B: Remove the processor

C: Insert a new processor

D: Reinstall the heat sink

E: Changing the SW DIP Switch settings

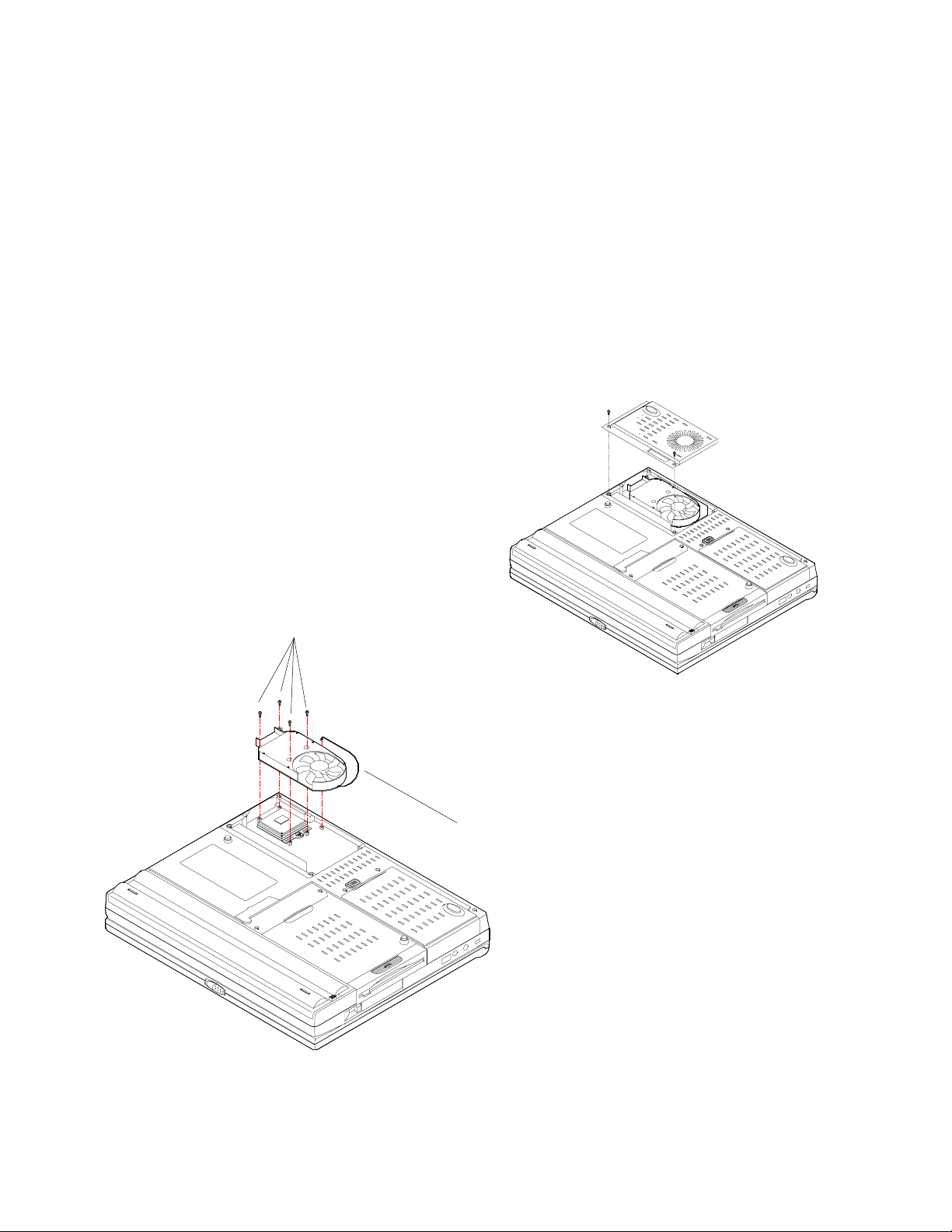

A: Remove the heat sink

1) Turn off the computer

2) Turn over the computer

3) Remove the Heat Sink and CPU Cover

Heat sink

heat sink screws

O

L

Figure 4-3

heat sink cable

4) Remove the 4 screws which hold the

heat sink in place.

5) Gently remove the heat sink cable.

6) Lift the heat sink out of the computer

10

Page 14

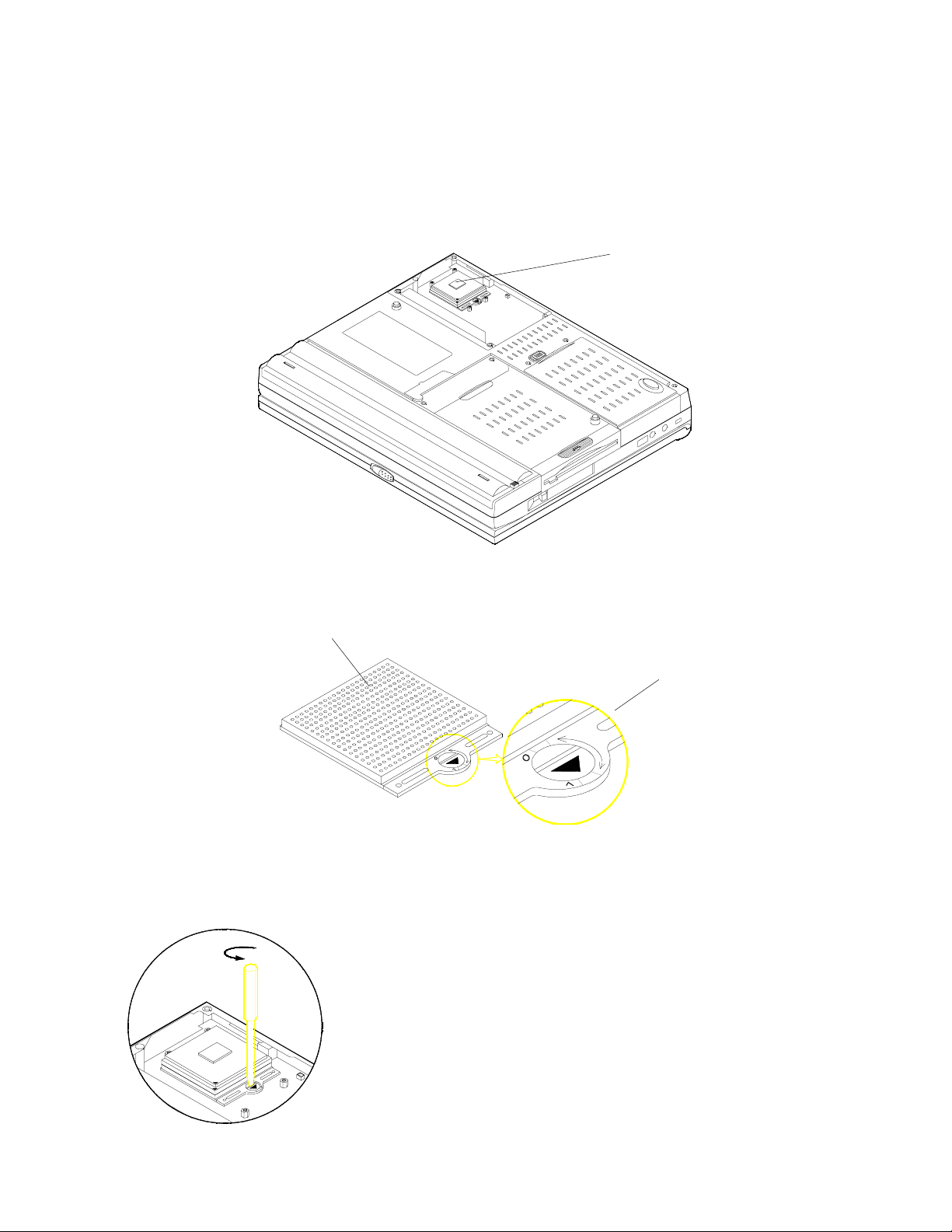

B: Remove the processor

The processor is secured on the mainboard with a lock which is easily opened using a small

regular screwdriver.

With the heat sink already removed you will need to set the lock to the open position before

removing the processor:

processor mounted on the socket

O

L

OPEN

Processor socket

Lock

1) Turn the screw on the

processor lock to the

open position. (O)

O

L

11

Page 15

2) Lift the processor

O

L

from the socket.

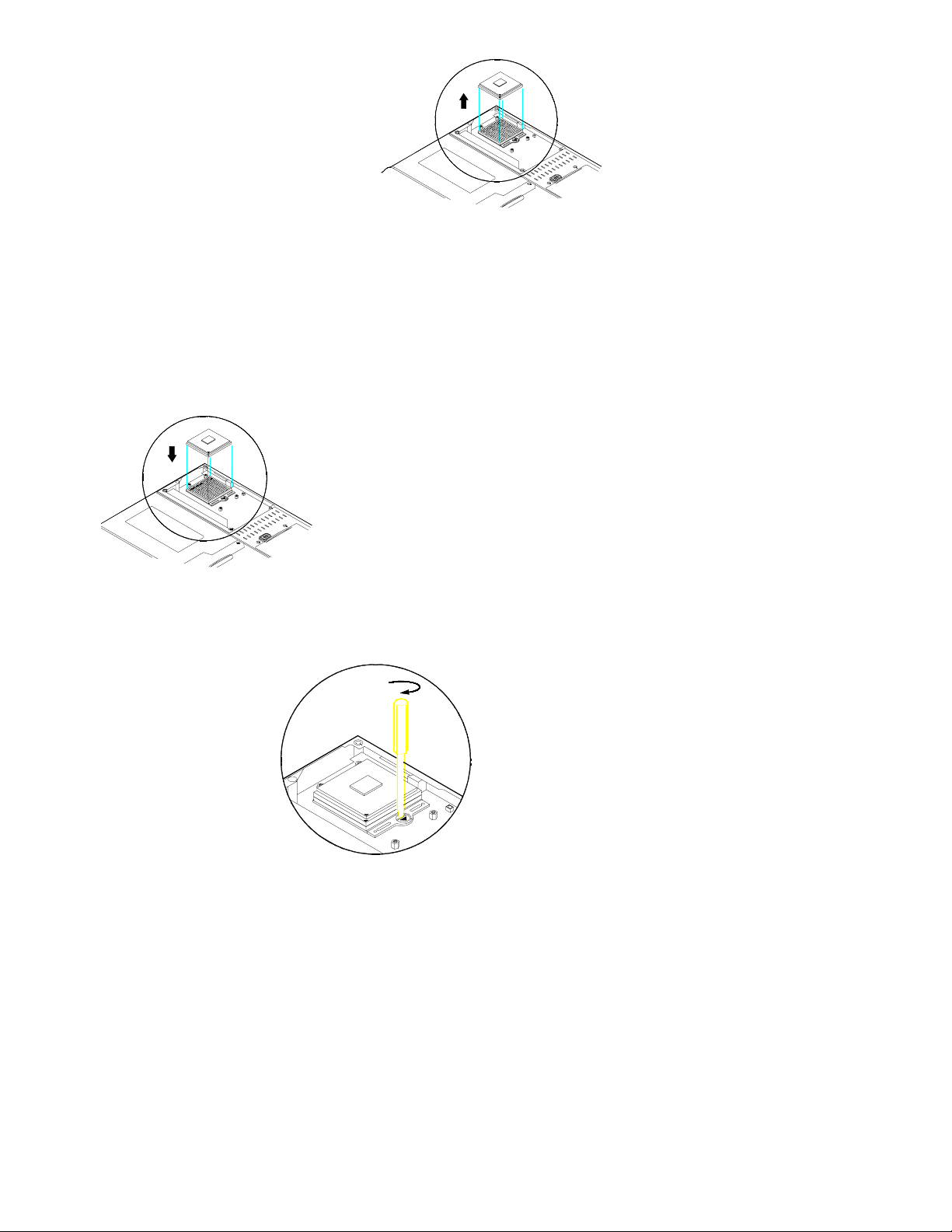

C: Insert a new processor

1) With the processor lock in the open position, align the pins of the processor with the

holes in the socket.

2) Press the processor into

O

L

the socket.

LOCK

3) Turn the screw to the locked

position (L)

O

L

12

Page 16

D: Reinstall the heat sink

Note: When reinstalling the heat sink, you will also have to replace the heat sink pad. A

heat sink pad can be obtained from your dealer.

1) Peel off the old heat sink pad and stick on a new one.

2) Insert the heat sink cable in the slot. (Figure 4-3)

3) Align the 4 screw holes on the heat sink with those on the mainboard and screw them

in about half way. Once all the screws are in about half way and the heat sink is

seated probably tighten the screws.

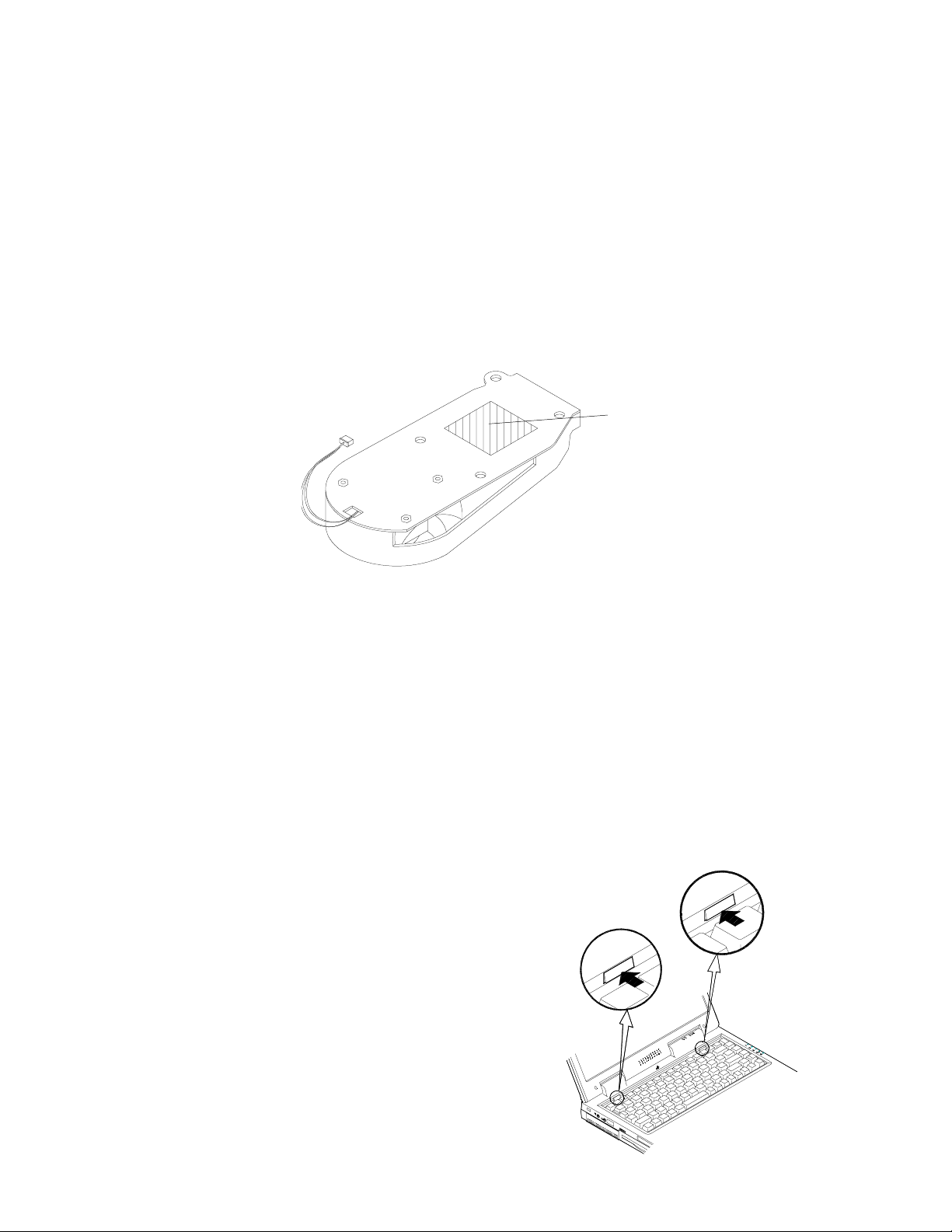

Heat sink pad

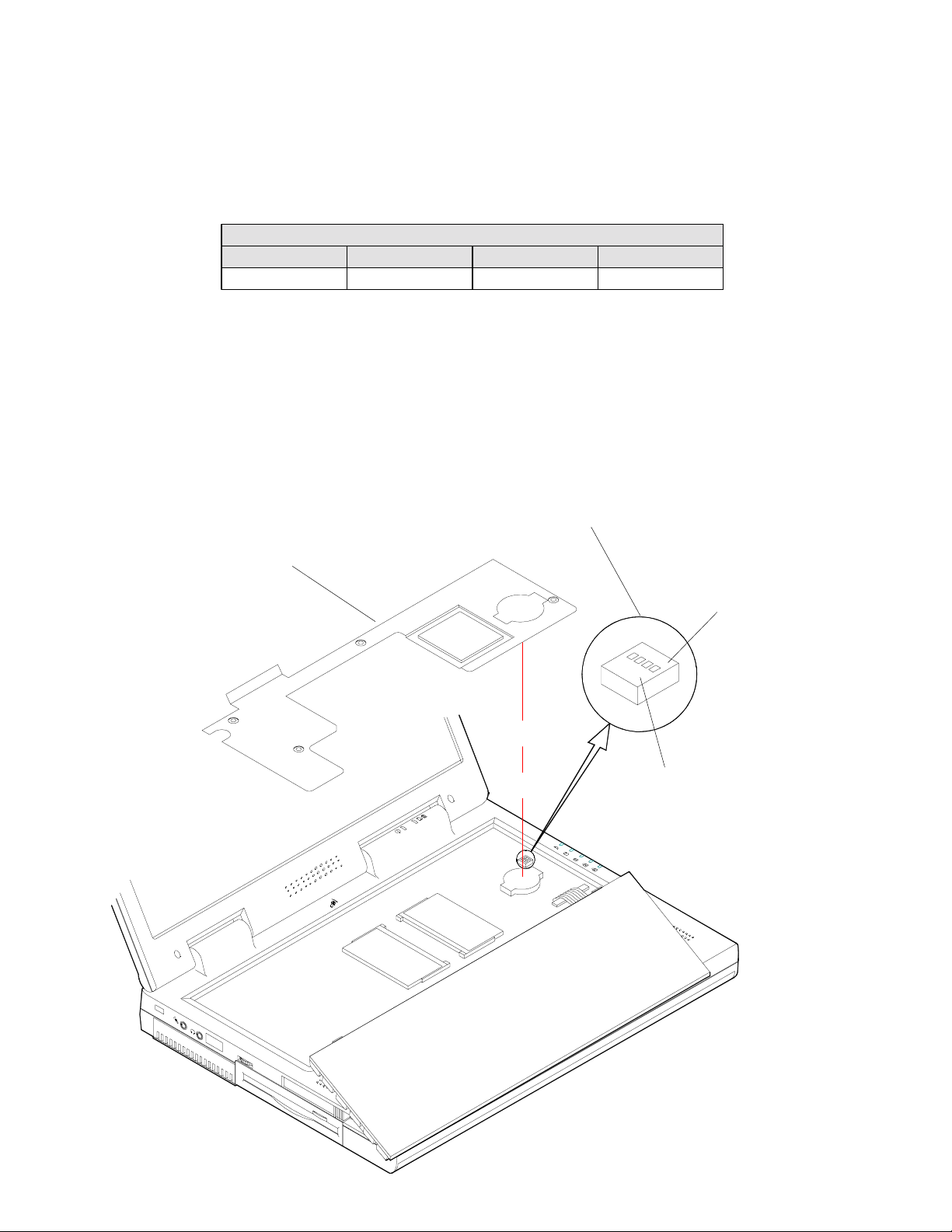

E: Changing the SW1 DIP Switch settings

If you have installed the processor with Intel Speedstep you will have to change the

SW1 DIP Switch settings. Follow these steps to get to change the SW1 DIP Switch

setings:

1) Turn off the computer.

2) Press the two keyboard latches to elevate the keyboard from its normal position.

3) Carefully lift the keyboard assembly out to expose the

mainboard.

13

Page 17

4) Remove the metal protective shield

5) Locate the SW DIP Switch on the right side.

6) Change the settings to the following:

SW settings for Intel Speedstep processor

SW1-1 SW1-2 SW1-3 SW1-4

ON ON ON OFF

7) Put the metal shield back into place

8) Put the keyboard back into place.

Metal shield

SW1 DIP Switch

OFF position

ON position

14

Page 18

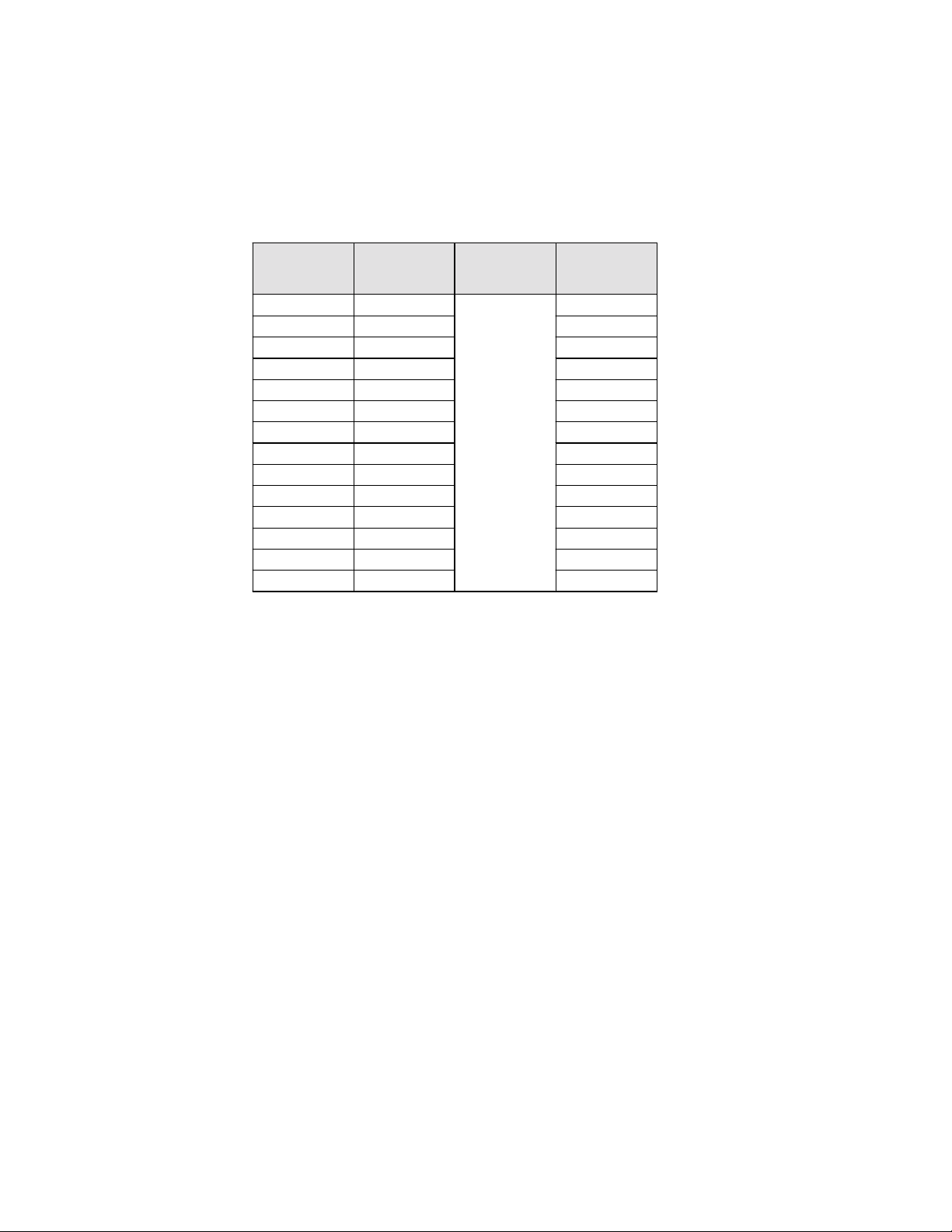

Memory

The computer has two memory sockets for PC-100/PC-133 compliant, 144 pin SODIMM

(Small Outline Dual In-line Memory Module) modules. The memory can be expanded to 512

MB with the following combinations:

Bank 0

(64-bit)

32 MB Emp t y 32 MB

32 MB 32 MB 64 MB

64 MB Emp t y 64 MB

64 MB 32 MB 96 MB

64 MB 64 MB 128 MB

128 MB Empty 128 MB

128 MB 32 MB 160 MB

128 MB 64 MB 192 MB

128 MB 128 MB 256 MB

256 MB Empty 256 MB

256 MB 32 MB 288 MB

256 MB 64 MB 320 MB

256 MB 128 MB 384 MB

256 MB 256 MB

Bank 1

(64-bit)

Power Total

Size

3.3V

512 MB

Once a new module is installed the memory size is automatically

detected by the POST routines when you turn on your computer.

15

Page 19

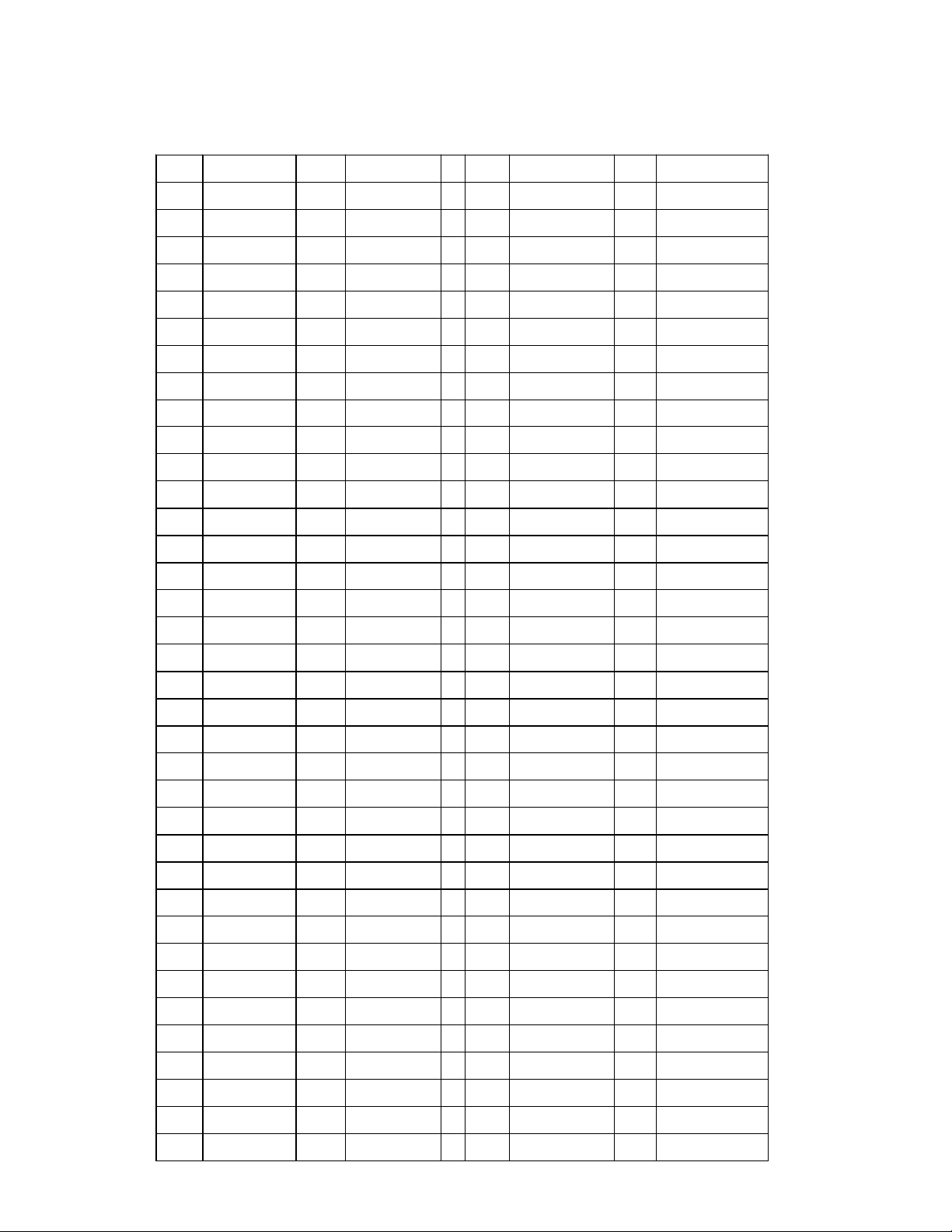

Expansion Memory Socket

The Model 5100S/5500S Notebook PC has two 144-pin SODIMM type memory sockets with the

following configuration:

Pin SDRAM Pin SDRAM Pin SDRAM Pin SDRAM

1 Vss 2 Vss 73 Reserved 74 CLK1

3 DQ0 4 DQ32 75 Vss 76 Vss

5 DQ1 6 DQ33 77 Reserved 78 Reserved

7 DQ2 8 DQ34 79 Reserved 80 Reserved

9 DQ3 10 DQ35 81 Vdd 82 Vdd

11 Vdd 12 Vdd 83 DQ16 84 DQ48

13 DQ4 14 DQ36 85 DQ17 86 DQ49

15 DQ5 16 DQ37 87 DQ18 88 DQ50

17 DQ6 18 DQ38 89 DQ19 90 DQ51

19 DQ7 20 DQ39 91 Vss 92 Vss

21 Vss 22 Vss 93 DQ20 94 DQ52

23 DQMB0 24 DQMB4 95 DQ21 96 DQ53

25 DQMB1 26 DQMB5 97 DQ22 98 DQ54

27 Vdd 28 Vdd 99 DQ23 100 DQ55

29 A0 30 A3 101 Vdd 102 Vdd

31 A1 32 A4 103 A6 104 A7

33 A2 34 A5 105 A8 106 BA0

35 Vss 36 Vss 107 Vss 108 Vss

37 DQ8 38 DQ40 109 A9 110 BA1

39 DQ9 40 DQ41 111 A10 112 A11

41 DQ10 42 DQ42 113 Vdd 114 Vdd

43 DQ11 44 DQ43 115 DQMB2 116 CAS6#

45 Vdd 46 Vdd 117 DQMB3 118 DQMB7

47 DQ12 48 DQ44 119 Vss 120 Vss

49 DQ13 50 DQ45 121 DQ24 122 DQ56

51 DQ14 52 DQ46 123 DQ25 124 DQ57

53 DQ15 54 DQ47 125 DQ26 126 DQ58

55 Vss 56 Vss 127 DQ27 128 DQ59

57 Reserved 58 Reserved 129 Vdd 130 Vdd

59 Reserved 60 Reserved 131 DQ28 132 DQ60

61 CLK0 62 CKE0 133 DQ29 134 DQ61

63 Vdd 64 Vdd 135 DQ30 136 DQ62

65 RAS# 66 CAS# 137 DQ31 138 DQ63

67 WE# 68 CKE1# 139 Vss 140 Vss

69 S0# 70 A12 141 SDA 142 SCL

71 S1# 72 A13 143 Vdd 144 Vdd

16

Page 20

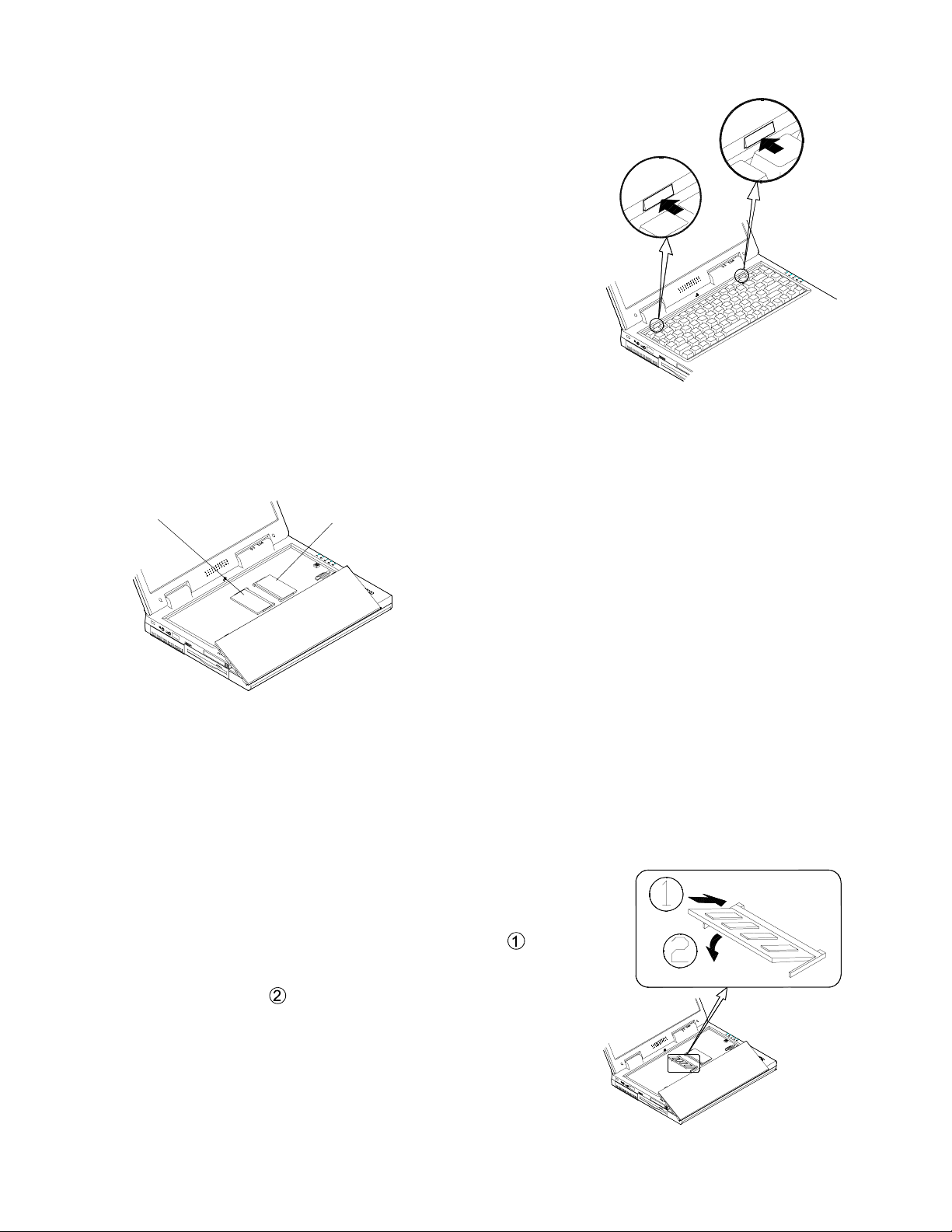

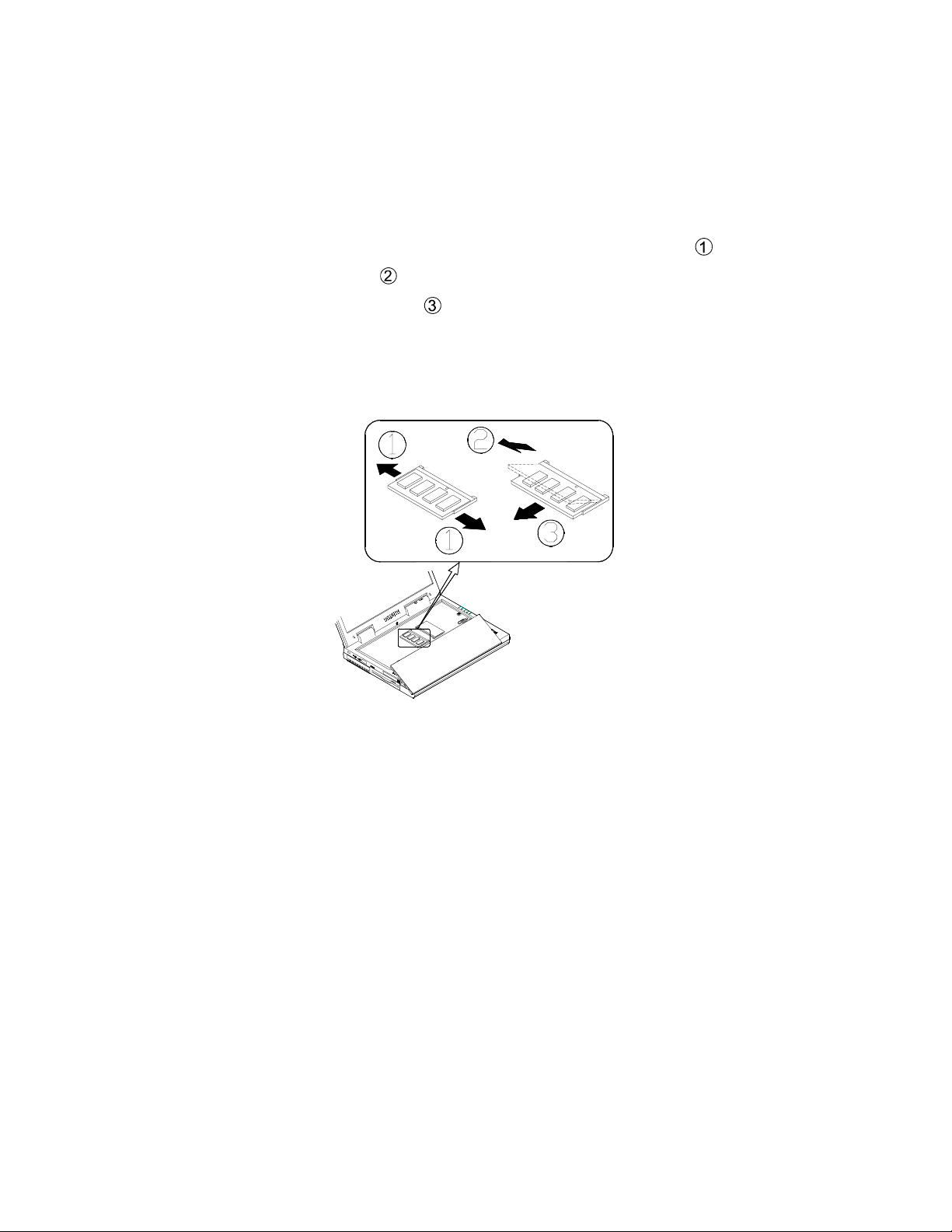

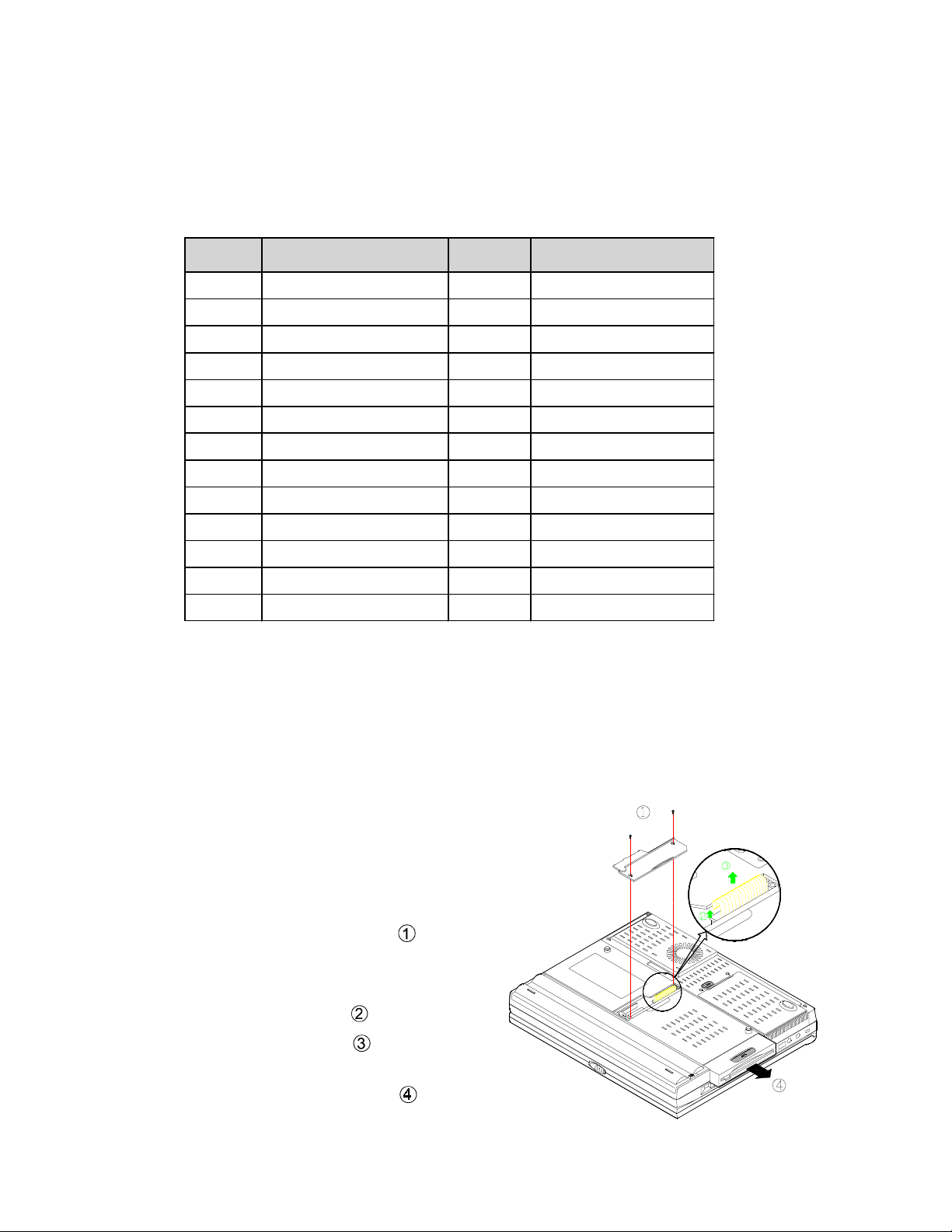

Installing a Memory Module

1) Turn off the computer.

2) Press the two keyboard latches at the top of the

keyboard to elevate the keyboard from its normal

position.

3) Carefully lift the keyboard assembly out to expose

the mainboard.

Figure 4-1

Bank 1 Bank 0

4) Locate the memory banks, Bank 0 is on the

right and Bank 1 is on the left.

Figure 4-2

Note: Only use Bank 0 if you have one memory module. If you are using two memory modules always use the larger module in Bank 0.

5) Insert the memory module at an angle (about 45°)

and fit its connectors firmly into the bank

.

6) Press down the edge of the memory module and lock

it into place

.

7) Put the keyboard back into place.

17

Page 21

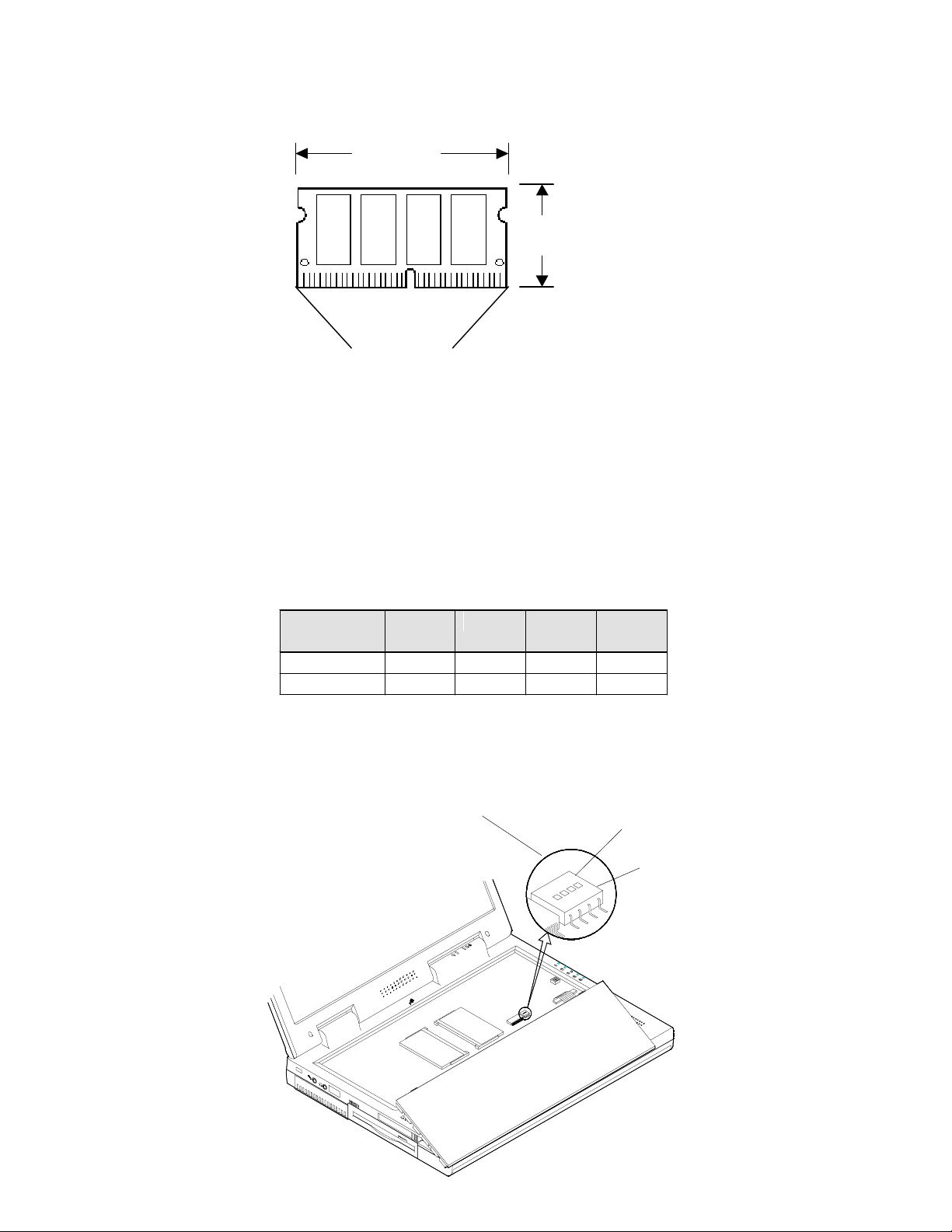

Note: Make sure the connectors go into the bank. You must use a RAM module that complies with Intel unbuffered SODIMM (67.6 mm x 29.0 mm). Please consult your dealer for

the details.

67.6 mm

29.0 mm

connectors

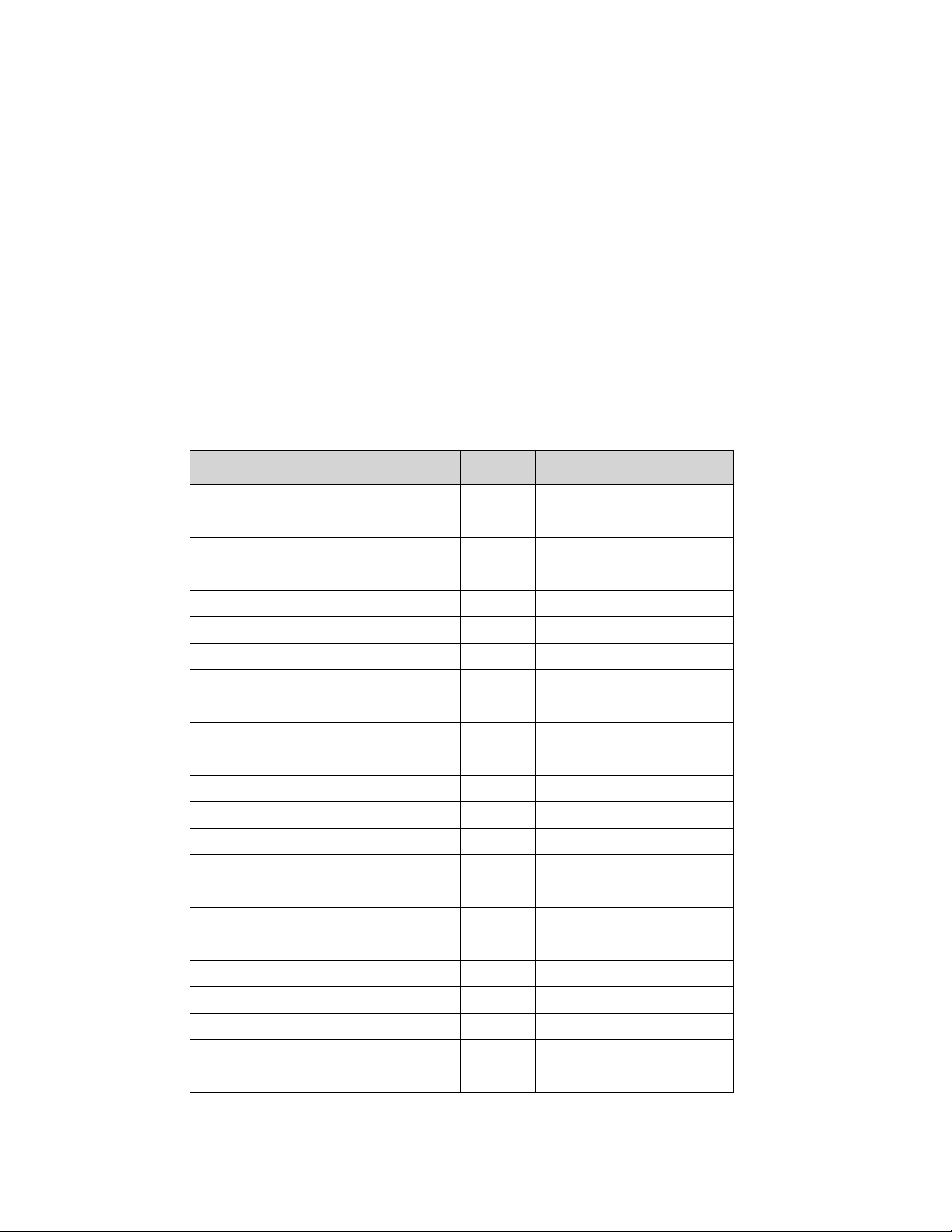

Changing the S3 DIP Switch settings

Once you have installed the new memory you will have to change the DIP Switch settings depending on the type of memory you have installed. Please refer to the chart

below for the correct settings for the S3 DIP Switches

SDRAM

TYPE

PC100 ON OFF OFF OFF

PC133 ON OFF ON OFF

S3-1 S3-2 S3-3 S3-4

S3 DIP Switch

ON position

OFF position

18

Page 22

Removing a Memory Module

1) Turn off the computer.

2) Press the two keyboard latches to elevate the keyboard from its normal position

(refer to Figure 4-1)

3) Carefully lift the keyboard assembly out to expose the mainboard.

4) Locate the memory sockets. Bank 0 is on the left and Bank 1 is on the right. (refer

to Figure 4-2)

5) Gently pull the two latches outward on both ends of the module

6) The module will pop up

7) Remove the memory module

8) Install a new memory module if desired (refer to Installing a Memory Module).

9) Put the keyboard back into place.

.

.

.

19

Page 23

Drive information and Pin assignments

Storage Devices

HDD (BUIL T-IN)

- 2.5", 12.7mm max. height and removable HDD

- Average access time: below 13ms

- PCI local bus IDE interface

- Supports: 12GB or higher HDD (Ultra DMA 33/66/100)

- MTBF 300,000 hours

- ULTRA DMA/SMART

HDD PIN ASSIGNMENT

Pin Description Pin Description

A-D DRIVE ID SELECT E, F KEY

1 RESET- 2 GROUND

3+DD74+DD8

5+DD66+DD9

7+DD58+DD10

9 +DD4 10 +DD11

11 +DD3 12 +DD12

13 +DD2 14 +DD13

15 +DD1 16 +DD14

17 +DD0 18 +DD15

19 GROUND 20 KEY

21 DMARQ 22 GROUND

23 DIOW- 24 GROUND

25 DIOR- 26 GROUND

27 IORDY 28 CSEL

29 DMACK- 30 GROUND

31 INTRQ 32 IOCS1633 DA1 34 PDIAG35 DA0 36 DA2

37 CS0- 38 CS139 DASP- 40 GROUND

41 +5 VOLTS SUPPLY 42 +5 VOLTS SUPPLY

43 GROUND 44 RESERVED

20

Page 24

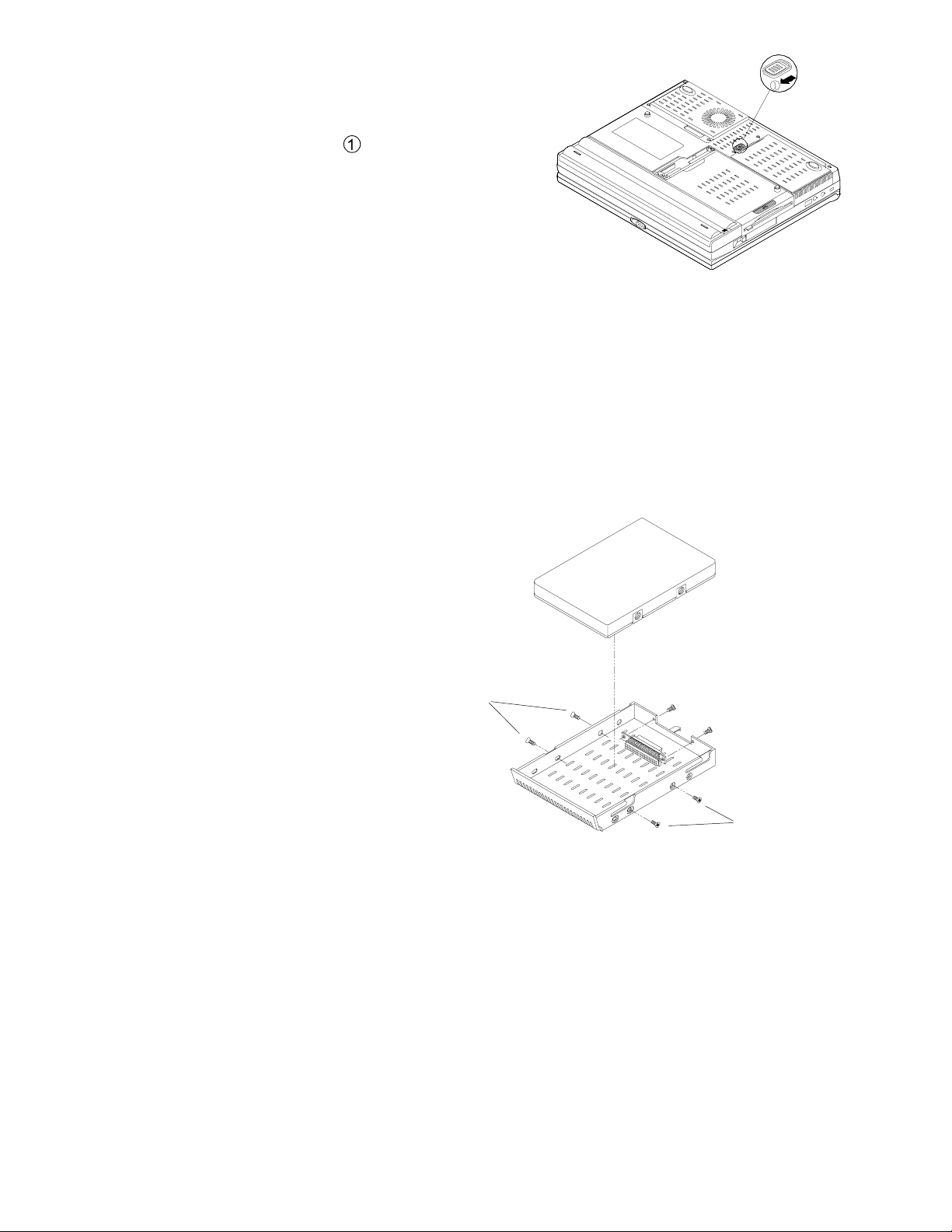

Removing the HDD from the notebook

1) Turn the computer off.

2) Turn the computer over.

3) Locate the HDD latch

4) Slide and hold the latch forward then slide

the HDD out of the computer.

5) Lift the hard disk drive out of the

computer.

.

Removing the HDD from its tray

1) Remove the HDD case from the computer (refer to Removing the HDD in Chapter

2 for details).

2) Remove the two sets of screws on the side of the case.

3) Slowly remove the HDD from the case until you see the connecting cable.

4) Gently disconnect the cable from the HDD being careful not to bend any pins or

crimp the cable.

5) Connect a new HDD

to the cable being

careful not to bend

any pins or crimp the

cable.

6) Slowly place the HDD

back into the case.

7) Hold the HDD firmly

in place with two

screws on each side.

8) Insert the HDD into

the computer (refer to

Inserting the HDD

in Chapter 2 for

details)

fastening screws

fastening screws

Inserting the HDD

1) Turn off the computer.

2) Turn the computer over.

3) Place the HDD case into the computer.

4) Slide the HDD in until you hear a click.

21

Page 25

FDD

- 3.5", 1.44MB floppy disk drive

- 3-Mode support for Japanese market

FDD PIN ASSIGNMENT

Pin Description Pin Description

1+5 V2INDEX

3 +5 V 4 DRIVE SELECT0

5+5 V6DISK CHANGE

7N.C.8Ready

9 HD(High : HD) 10 MOTOR ON

11 N.C. 12 DIRECTION

13 Mode Select 14 STEP

15 GND 16 WRITE DATA

17 GND 18 WRITE GATE

19 GND 20 TRACK 00

21 GND 22 WRITE PROTECT

23 GND 24 READ DATA

25 GND 26 Side One Select

Removing the FDD

Removing the Floppy Disk Drive

1) Turn off the computer.

2) Turn the computer over.

3) Locate the DVD / FDD cover

4) Unscrew and remove the cover .

5) Lift the white plastic piece which holds

.

the FDD cable in place

6) Pull out the FDD cable

7) Grasp the FDD tab and gently PULL

the FDD out of the computer

.

.

.

22

Page 26

8) Remove the two screws on each side of the FDD tray.

9) Remove the FDD from its tray. (see picture)

fastening screws

fastening screws

The FDD floppy disk drive out of its bay

Inserting the Floppy Disk Drive

Follow the instructions for removing the FDD in reverse order.

23

Page 27

DVD-ROM

- Model Matsushita SR8173

- Dimensions 128mm(W)x12.7mm(H)x127mm(D)

- Random access time 130ms-CD / 170ms-DVD

- Data transfer rate 4X speed (5400KB/s)-DVD

- Mechanism tray-loading

- Interface ATAPI

- MTBF 60,000POH

DVD-ROM PIN ASSIGNMENT

Signal Name I/O

AUDIO L-CH O 1 2 O AUDIO R-CH

AUDIO GROUND

/RESET I 5 6 I/O DD8

DD7 I/O 7 8 I/O DD9

DD6 I/O 9 10 I/O DD10

DD5 I/O 11 12 I/O DD11

DD4 I/O 13 14 I/O DD12

DD3 I/O 15 16 I/O DD13

DD2 I/O 17 18 I/O DD14

DD1 I/O 19 20 I/O DD15

DD0 I/O 21 22 O DMARQ

GROUND 23 24 I /DIOR

/DIOW I 25 26 GROUND

IORDY O 27 28 I /DMACK

INTRQ O 29 30 O /IOCS16

DA1 I 31 32 I/O /PDIAG

DA0 I 33 34 I DA2

/CS1FX I 35 36 I /CS3FX

/DASP I/O 37 38 I +5 V

+5 V I 39 40 I +5 V

+5 V I 41 42 I +5 V

GROUND 43 44 GROUND

GROUND 45 46 GROUND

CSEL I 47 48 GROUND

RESERVED 49 50 RESERVED

Connector

Contact

3 4 N.C.

I/O Signal Name

24

Page 28

Removing the DVD-ROM Module

Removing the DVD-ROM Module

1) Turn off the computer.

2) Turn the computer over.

3) Locate the DVD/FDD cover

4) Unscrew and remove the cover.

5) Remove the single screw which holds the DVD-ROM in the computer

6) Locate the cable tab and gently pull the cable tab upward to disconnect the DVD-ROM

from the computer mainboard

7) Grasp the DVD-ROM tab and gently PULL the DVD-ROM out of the computer

.

.

.

.

Inserting the DVD-ROM module

Refer to removing the DVD-ROM and follow the instructions in reverse order.

25

Page 29

CD-ROM (OPTIONAL)

- Model Matsushita CR175

- Dimensions 128mm(W)x12.7mm(H)x127mm(D)

- Random access time 120ms

- Data transfer rate 24X speed (3600KB/s)

- Mechanism tray-loading

- Interface ATAPI

- MTBF 60,000POH

CD-ROM PIN ASSIGNMENT

Signal Name I/O

AUDIO L-CH O 1 2 O AUDIO R-CH

AUDIO

GROUND

/RESET I 5 6 I/O DD8

DD7 I/O 7 8 I/O DD9

DD6 I/O 9 10 I/O DD10

DD5 I/O 11 12 I/O DD11

DD4 I/O 13 14 I/O DD12

DD3 I/O 15 16 I/O DD13

DD2 I/O 17 18 I/O DD14

DD1 I/O 19 20 I/O DD15

DD0 I/O 21 22 O DMARQ

GROUND 23 24 I /DIOR

/DIOW I 25 26 GROUND

IORDY O 27 28 I /DMACK

INTRQ O 29 30 O /IOCS16

DA1 I 31 32 I/O /PDIAG

DA0 I 33 34 I DA2

/CS1FX I 35 36 I /CS3FX

/DASP I/O 37 38 I +5 V

+5 V I 39 40 I +5 V

+5 V I 41 42 I +5 V

GROUND 43 44 GROUND

GROUND 45 46 GROUND

CONFIG(*1) I 47 48 GROUND

RESERVED 49 50 RESERVED

Connector

Contact

3 4 GROUND

I/O Signal Name

26

Page 30

Interface Pin Assignments

RS-232 Serial Interface

The RS-232C Serial Interface uses a 9 pin D-sub male connector with the following configuration:

Parallel Interface

The Parallel interface uses a 25-pin D-sub female connector with the following configuration:

Pin Description

1 DCD (DATA Carrier Detect)

2 RXD (Received Data)

3 TXD (Transmitted Data)

4 DTR (Data Terminal Ready)

5 GND (Signal Ground)

6 DSR (Data Set Ready)

7 RTS (Request To Send)

8 CTS (Clear To Send)

9 RI (Ring Indicator)

Pin Description Pin Description

1 Strobe# 2 Data 0

3 Data 1 4 Data 2

5 Data 3 6 Data 4

7 Data 5 8 Data 6

9 Data 7 10 ACK#

11 Busy 12 Paper Empty

13 Select 14 Auto Feed#

15 Error# 16 Initialize#

17 Select In 18 Ground

19 Ground 20 Ground

21 Ground 22 Ground

23 Ground 24 Ground

25 Ground

USB Interface

The external USB (Universal Serial Bus) has the following configuration:

Pin Description

1 USB_VCCA

2 USBP03 USBP0+

4 GND

27

Page 31

Internal trackpad Interface

The internal trackpad interface connector has the following configuration:

Pin Description

1 EKDA

2 EMDA

3 GND

4 VCC

5 EKCLK

6 EMCLK

7 GND

8 GND

9 GND

External Monitor Interface

The external monitor interface uses a 15-pin D-sub female connector with the following

configuration:

Pin Description Pin Description Pin Description

1 RED 6 GND 11 NC

2 GREEN 7 GND 12 DDCDA

3 BLUE 8 GND 13 HSYNC

4 NC 9 NC 14 VSYNC

5 GND 10 GND 15 DDCLK

RGB Out:

- Output Impedance : 75 Ohms

- RGB peak voltage: 0.7Vpp

External Keyboard/PS2 Mouse Interface

The external keyboard/PS2 mouse interface connector has the following configuration:

Pin Description

1 EKDA

2 EMDK

3 GND

4 VCC

5 EKCLK

6 EMCLK

7 GND

8 GND

9 GND

28

Page 32

PCMCIA CardBus Interface

Description DescriptionPin

CardBus 16Bit Card

A1 GND GND A40 A_VPP2 A_VPP2

A2 GND GND A41 A_CCLK A_A16

A3 A_CAD0 A_D3 A42 GND GND

A4 A_CCD1# A_CD1# A43 A_CTRDY# A_A22

A5 A_CAD14 A_D4 A44 A_CIRDY# A_A15

A6 A_CAD2 A_D11 A45 A_CFRAME# A_A23

A7 A_CAD3 A_D5 A46 A_CC/BE2# A_A12

A8 A_CAD4 A_D12 A47 A_CAD17 A_A24

A9 GND GND A48 A_CAD18 A_A7

A10 A_CAD5 A_D6 A49 GND GND

A11 A_CAD6 A_D13 A50 A_CAD19 A_A25

A12 A_CAD7 A_D7 A51 A_CAD20 A_A6

A13 RFU A_D14 A52 A_CVS2 A_VS2#

A14 A_CC/BE0# A_CE1# A53 A_CAD21 A_A5

A15 A_CAD9 A_D15 A54 A_CRST A_RESET

A16 A_CAD10 GND A55 A_CAD22 A_A4

A17 A_CAD9 A_A10 A56 A_CSERR# A_WAIT#

A18 A_CAD10 A_CE2# A57 GND GND

A19 A_CAD11 A_OE# A58 A_CAD23 A_A3

A20 A_CVS1 A_VS1# A59 A_CREQ# A_INPACK

A21 A_CAD12 A_A11 A60 A_CAD24 A_A2

A22 GND GND A61 A_CC/BE3# A_REG#

A23 A_CAD13 A_IORD# A62 A_CAD25 A_A1

A24 A_CAD14 A_A9 A63 A_CAUDIO# A_BVD2

A25 A_CAD15 A_IOWR# A64 A_CAD26 A_A0

A26 A_CC/BE1# A_A8 A65 GND GND

A27 A_CAD16 A_CAD16 A66 A_CSTSCHG A_BVD1

A28 GND GND A67 A_CAD27 A_D0

A29 A_CPAR A_A13 A68 A_CAD28 A_D8

A30 RFU A_A18 A69 A_CAD29 A_D1

A31 A_CPERR# A_A14 A70 A_CAD30 A_D9

A32 A_CBLOCK# A_A19 A71 RFU A_D2

A33 A_CGNT# A_WE# A72 A_CAD31 A_D10

A35 A_CINT# A_CINT# A73 GND GND

A36 A_CDEVSEK# A_CDEVSEL# A74 A_CCLKRUN# A_WP

A37 A_VCC A_VCC A75 A_CCD2# A_CD2#

A38 A_VCC A_VCC A76 GND GND

A39 A_VPP1 A_VPP1 A77 GND GND

Pin

CardBus 16Bit Card

29

Page 33

Internal PCI Interface

(For optional modem or LAN card)

Pin Description Pin Description

1 GND 2 GND

3 GND 4 GND

5 GND 6 GND

7 AUXBR 8 MIC_MODM

9 AD8 10 AD6

11 AD9 12 AD5

13 AD10 14 AD7

15 AD11 16 CBE#0

17 AD12 18 AD0

19 AD13 20 AD1

21 AD14 22 AD2

23 AD15 24 AD3

25 CBE#1 26 AD4

27 PAR 28 MODEMRI

29 VCC 30 VCC

31 SERR# 32 IDSEL

33 PERR# 34 CBE#3

35 STOP# 36 PME#

37 DEVSEL# 38 INTA#

39 TRDY# 40 RESET#

41 IRDY# 42 PCLKMODM

43 FRAME# 44 GNT#4

45 CBE#2 46 REQ#4

47 GND 48 GND

49 VCC3 50 VCC3

51 VCC3 52 VCC3

53 VCC3 54 VCC3

55 GND 56 GND

57 GND 58 GND

59 VCC 60 VCC

61 VCC 62 VCC

63 VCC 64 VCC

65 AD16 66 AD31

67 AD17 68 AD30

69 AD18 70 AD29

71 AD19 72 AD28

73 AD20 74 AD27

75 AD21 76 AD26

77 AD22 78 AD25

79 AD23 80 AD24

30

Page 34

LCD Interface

( For XGA TFT)

Pin Description Pin Description

1 INVVCC 2 INVVCC

3 ENABL 4 BRIGADJ

5 GND 6 LP

7 FLM 8 DISPOFF#

9 GND 10 CL2

11 CONTADJ 12 LDE

13 PANELID0 14 PANELID1

15 GND 16 LCDVDD

17 LCDVDD 18 GND

19 TXOUTV0- 20 TXOUTV0+

21 GND 22 TXOUTV123 TXOUTV1+ 24 GND

25 TXOUTV2- 26 TXOUTV2+

27 GND 28 TXCLKV29 TXCLKV+ 30 GND

31

Page 35

Power

Application:

This specification shall apply to the power module to be operated in the Notebook 5100S/

5500S system. The power board provides the following voltages for Intel P!!! CPUs:

1.35V &1.6V for CPU VCC_CORE

Input Power:

a. Adapter: +20.0V Constant Voltage Mode (65W ).

b. Battery: LI-ION Smart Battery ( 47.36W ).

c. Input Rating

ITEM MIN TYP MAX UNIT REMARK

Input Voltage 12 20 21 V --

Output Power:

DC OUTPUT

VOLTAGE REGULATION

Vcc / 5V ±5% 150mV 4.0A 6.0A

Vcc3 / 3.3V ±5% 150mV 4.0A 6.0A

12V / 12V ±5% 200mV 0.22A 0.35A

Vcc_Core / 1.6V ±5% 150mV 15A 17A

VccT / 1.5V ±5% 150mV 1.5A 2.0A

Vcc1.8 / 1.8V ±5% 100mV 2.0A 3.0A

Vdd1.8 / 1.8V ±5% 100mV 70mA 80mA

VC / 5V ±5% 100mV 70mA 80mA

Note:

The surge currents of all outputs can keep 10 seconds maximum .

The output ripple/noise requirements should be met throughout the load range and under

the input voltage from 12Vdc to 20Vdc. Measurements should be made with an

oscilloscope with the 20Mhz bandwidth output bypassed with a connector with a

0.1uF ceramic capacitor and a 10 uF electrolytic capacitor to simulate loading.

The system is full run under auto test.

RIPPLE &

NOISE

CURRENT

Max Surge

32

Page 36

Output Protection Requirements:

a. Over current protection:

Vcc OCP —7A max

Vcc3 OCP — 7A max

Vcc_Core OCP — 20A max

VccT OCP — 3.5A max

Vcc1.8 OCP — 3.5A max

b. Output Short Protection : Vcc,Vcc3,12V,Vcc_Core,VccT,Vcc1.8

The power supply shall not be damaged by short form the output to return .

Battery Protection:

The discharge circuits should be SHUTDOWN when the voltage for the Li-ion battery

voltage is down to 12V(+/-0.2V)

Vcc_Core VID setting :

No VID4 VID3 VID2 VID1 VID0 COREVCC

1 0 0 0 0 0 2.0V

2 0 0 0 0 1 1.95V

3 0 0 0 1 0 1.90V

4 0 0 0 1 1 1.85V

5 0 0 1 0 0 1.80V

6 0 0 1 0 1 1.75V

7 0 0 1 1 0 1.70V

8 0 0 1 1 1 1.65V

9 0 1 0 0 0 1.60V

10 0 1 0 0 1 1.55V

11 0 1 0 1 0 1.50V

12 0 1 0 1 1 1.45V

13 0 1 1 0 0 1.40V

14 0 1 1 0 1 1.35V

15 0 1 1 1 0 1.30V

16 0 1 1 1 1 1.25V

33

Page 37

Interface Specifications

JP1. Battery Connector (Off The Mother Board)

PIN SIGNAL

1~8 B+

9 BAT-DATA

10 TEMP

11 BAT-CLK

12 CELL

13~20 GND

CNA1. DC/DC Connector (Off The Power Board)

PIN SIGNAL

1~6 B+

7 VR_ON

8~13 GND

14 ~ 21 VCC3

22~27 GND

28~33 VCC

34~39 GND

40~42 12V

CN4. Battery Connector(Off The Mother Board)

PIN SIGNAL

1,2 GND

3 CELL

4 TEMP

5 BAT_CLK

6 BAT_DATA

7,8 BAT+

34

Page 38

Charge board

Battery parameters

The BIOS will download all battery parameters to the smart charger before POST. The

battery parameters are as follows:

LI-ION CHG V (0x39) : Li-ion CV = (0x39) /3 *4

LI-ION DESINH V (0x3A) : ERROR = (0X3A) * 1.27 +2.3V

LI-ION EDVI (0x3B) : EDVI = (0x3B) /3 *4

LI-ION EDVF (0x3C) : EDVI = (0x3C) /3 *4

Default EDVI and EDVF and Constant Voltage:

Battery Item Voltage

LI-ION Constant Voltage 16.8V ± 0.2V

EDVI 11.4V ± 0.2V

LI-ION

EDVF 10.8V ± 0.2V

Charge current and Charge Time:

ITEM MIN TYPE MAX UNIT REMARK

Input Voltage 19 20 21 V From AC Adapter

0.6 0. 8 1.0 A When System is on

Charge Current

1.3 1. 5 1.7 A When System is off

LI-Ion

Charge Time

Total Power Current ( IRQ ) :

Total Power Current

3A ±0.2A

- - 450 min When System is on

- - 230 min When System is off

*Total Power = System Power + Charge Power

35

Page 39

Hardware ShutDown:

Battery Type Max Voltage

LI-ION 12V ± 0.2V

Max Voltage Protection :

Battery Type Max Voltage

LI-ION 17.1V ± 0.2V

O.P.T ( Protect for environment temperature ) :

For a LI-ION battery charger start, if the temperature exceeds

50°C or falls below 5°C, the charger shall not charge and the charge indicator will

show no charger current.

If the environment temperature is below 50°C the charger shall auto re Charge. The thermistor of the battery pack will detect the environment temperature.

O.P.T

5 ~ 50°C

The trickle charge:

If the LI-ION battery voltage is below 3V/cell,the charge controller will enter the trickle

charge mode. The trickle charge current is about 200~300 mA (trickle charge time is 60

minutes max).

Charger full :

When the battery is fully charged, the charge controller will send a full signal and the gas

guage indicator will display capacity greater than 90%.

For the smart battery, the charge controller full signal and the gas gauge are different.

It’s normal for the gas gauge indicator to show a 90% charge even if the battery has just

been fully charged and is actually above a 90% capacity.

Battery empty shutdown :

When the battery is empty, the charge controller will send a shut down signal within 3

seconds. The shut down signal is 3.3V.

36

Page 40

Alert :

The charge controller will send an alert signal, when the adapter is plugged in or out, when

the battery is inserted or removed, or when the battery is low.

During the alert signal, the charge controller will send the low signal pulse three times

within a 10 second period.

Battery low alarm :

When the battery is low, the charge controller will send out the battery low alert. If KBC or

the OS doesn’t respond, the battery will go to the low signal in 2 seconds.

The battery low alarm is decided by the “alarm time”, the battery voltage is for reference

only. Therefore the battery low alarm defines the alarm time not the voltage.

Alarm time :

- Alarm time is defined from the time the battery low beep starts until the computer

shuts down.

- The alarm time of a dumb battery must be less than 15 minutes and greater than 3

minutes for ZD Mark3.0.

- The alarm time of a smart battery is defined by either the remaining capacitor

alarm or the remaining time alarm.

The battery is not normal if the green LED blinks while the battery is charging.

You must shutdown the computer, unplug the adapter and remove the battery. After the

battery cools down, reinstall the battery and plug in the adapter to recharge the battery.

Smart battery :

The charge current of the smart battery depends on BQ2040 data.

The full charge of a smart battery depends on the remaining capacitor alarm or remaining

time alarm .

The smart charger always reads the temperature of the smart battery to detect Max. T and

OPT.

BIOS issue

After re-flashing the Bios, don’t use the Ctrl+Alt+Del key to restart your computer. Instead you should press the power button to shutdown the computer and then turn on the

computer, this will reload the default BIOS.

While using Ctrl+Alt+Del keys (warm start), KBC doesn’t send out battery setup parameters to charge controller IC.

37

Page 41

Inverter board

APPLICA TION :

This specification refers to an inverter which operates a cold cathode fluorescent lamp for a

liquid-crystal display module.

This inverter is designed for the 12.1” TFT LCD-modules.

ELECTRICAL CHARACTERISTICS:

ITEM MIN TYPE MAX UNIT REMARKS

Input Voltage 4.5 5 5.5 V/DC

Input Current - 900 - mA/DC at Vin=5V

Inrush Current - - 4 A/AC Less than 1ms

Lamp Current

Output Voltage - 560 - V/AC

Frequencey - 60 - KHz

Starting Voltage 1000 - - V/AC

BKLO 0 - 3.3 V/DC ON = 3.3V

BRIGADJ 0 - 2.5 V/DC

5.5 6.0 6.5 mA/AC BRIG:2.5V

2.5 3.0 3.5 mA/AC BRIG:0V

Interface Specification:

J1 ( Connector 6 Pin ) Inverter To M/B Connector

PIN SIGNAL

1 B+

2 B+

3 GND

4 GND

5 BRIGADJ

6 BKLO

38

Page 42

Adapter

Configuration :

3-wire input AC line (line, neutral, FG)

Input characteristics:

Input Voltage: 100 ~ 240

Input Frequency: 47 ~ 63 Hz

Input Current : 1.6A max @115VAC,at full load.

0.8A max @230VAC,at full load.

Efficiency: 80 % (min) .at full load .

Output characteristics:

Output power: 65W (max)

Output Current:

ITEM TOLERANCE OUTPUT CURRENT

+10%vac,Full range

Output voltage (Accuracy) Min Max

+20Vdc (main) +/- 5% 0 3.25A

Regulation:

VOLTAGE TOLERANCE REGULATION

+20Vdc (main) +/- 5 % 19 ~ 21 V

Ripple & Noise :

The power supply shall not exceed 250mVrms on the indicated voltage for 60Hz or 50Hz

ripple, switching frequency ripple and noise dynamic load variations measured with a

20MHz bandwidth. Ripple & noise are measured at the end of output cables to which are

added a 0.1uf ceramic capacitor and a 10uF electrolytic capacitor.

Leakage Current:

0.75mA

Over Voltage Protection :

27V max.(do not test with external DC source).

Shutdown voltage protection:

10V max.

39

Page 43

Over Current Protection :

The power supply will not be damaged by an over current from the output (measure at 110

Vac input).

OUTPUT VOLTAGE LOWER UPPER

+20 to 10.0 Vdc 3.3A 3.8A

Short circuit protection:

A short circuit place at any output will cause no damage.

ESD requirements :

The adapter shall withstand IEC PUB. 801-5 (surge ) level 4 requirements.

EMI / EMC :

The radiated and conducted emissions of this AC adapter complies with the requirements

of the FCC PART 15, CLASS B & EN55022.

SAFETY :

This AC adapter is designed to meet the following standards:

# UL 1950 LISTED

# CUL LEVEL 3

# TUV EN60950

40

Page 44

Battery Pack

Recharging by AC Power

The battery pack automatically recharges when it is installed into a computer that is connected to an AC power supply. You can still use the computer when it is recharging. To

fully recharge the battery will take several hours and may be slightly longer if the computer is being used while the battery is recharging.

Proper Handling of the Battery Pack

DO NOT disassemble the battery pack under any circumstances.

DO NOT expose the battery to fire or high temperatures, it may explode.

DO NOT connect the metal terminals (+, -) together.

Battery Information

Proper care will improve the performance and extend the life and cycle life of the battery.

Follow these guidelines to get the best use out of the battery.

Power loss

When not in use, a battery will gradually lose its power, this is normal. The rate of power

loss depends on the battery type and is approximately:

0.2% / Day for a Li-Ion Battery

Battery storage

Outside the computer

If you are going to store a battery outside the computer for an extended period you must:

· Charge the battery to at least 40% capacity prior to storage.

· Follow steps 1 through 3 approximately every 30 days:

1. Completely recharge the battery.

2. Use the battery until it is fully discharged

3. Recharge the battery to at least 40% capacity.

Inside the computer

If a fully charged battery is stored inside the computer and the battery is not used for more

than 30 days, you must follow these steps:

41

Page 45

1. Completely recharge the battery.

2. Use the battery until it is fully discharged

3. Recharge the battery to 100% capacity.

(In this case it doesn’t matter whether or not the computer is being used)

Note: An empty battery will become damaged if stored too long and by following

these steps the battery cycle life and the battery life will increase.

Battery T esting

Testing a battery while its temperature remains high could possibly cause inaccurate measurements, therefore we strongly recommend:

· Waiting 30 minutes before testing a battery that has just been fully charged.

· Waiting at least 30 minutes before recharging a fully discharged battery.

Note: All battery testing should be done on a fully charged or fully discharged battery.

Battery alarm

The battery alarm is activated by a program and will sound when the battery power is low.

Note: If a fully discharged battery has been charged for less than 3 minutes, this program

will not be activated.

This happens when these 3 steps occur:

1. The computer is being used and the low battery alarm sounds.

2. The AC adapter is connected to charge the battery while the computer continues to be

used.

3. The adapter is unplugged within the first 3 minutes of charging.

After this sequence of steps, the computer will eventually shutdown without the low

battery alarm sounding and you will lose any work you have entered and not saved.

Therefore you should make sure that the AC adapter is firmly plugged into the computer

when charging the battery.

42

Page 46

Removing the battery pack

1) Turn the computer over.

2) Slide the latch in the direction indicated .

3) Gently grasp the battery pack on the edge

below the latches and lift it out of the bay

.

Inserting the battery pack

1) Turn the computer over.

2) Place the battery in its bay inserting the side without the latch in first.

3) Push down on the side with the latch until it clicks into place.

43

Page 47

Battery diagram

44

Page 48

Component diagrams and part numbers

10

18

15

14

4

16

6

8

1

2

13

4

11

4

5

3

7

9

21

22

19

20

31

12

22

23

17

22

22

25

26

33

7

22

24

35

36

22

7

32

22

14

28

34

29

30

31

45

Page 49

46

Page 50

4

6

3

5

13

11

7

ITEM

1

DISPLAY FRON T PA N EL

LCD 12.1" TFT SANYO T M 121SV- 02L07

2

DISPLAY BAC K PAN EL

3

HOOK KNOW

4

5

HOOK

SPRING FO R HOOK EXTEN

6

7

INV ERTER

LCD BRACKET (L)

8

LCD BRACKET (R)

9

10

CABLE 1H /2H 28AW G 35P 203m m

11

DISPLAY RU BBER PAD

12

DISPLAY RU BBER PAD

13

SCREW

SCREW

14

15

SCREW

16

SCREW

PART NAM E

14

16

9

15

2

8

15

10

PART NO.

39- 51011- 01E

50- F1255- S01

39- 51S01- 02A

1

FO R 12.1"

12.1" SV

FOR 12.1 SANYO

15

12

REM ARK

••••

42- 51081- 010

42- 510A 1- 010

38- 10R35- 021

0.35

43- 5 1S0R- 010

33- 51001- 050

33- 51001- 040

43- 51 S01-010

47- 51021- 010

47- 51021- 020

35- 01120- 4RO

35- 41120- 3RA

35- 84130- 6RA

35- B6130- 4R A

FOR LG (S2 ) 12. 1

FOR LG (S2 ) 12. 1

SANYO

UP

BOTTO M

M2*4L,P,NI,ICT

M2*0,4P*3L , B,NI,ICT,NY

M3*6L,K,BK/0,ICT,NY

M3*4,K1,BZ,ICT.NY

47

Page 51

48

Page 52

4

7

2

3

12

10

2

13

9

14

15

16

1

5

22

6

2

7

3

21

9

8

10

2

11

8

5

15

16

17

19

17

18

20

2

49

Page 53

50

Page 54

51

VCC_CORE

R191 0

VCC_SENSE

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

Z2

Z3

Z4

Z5

Z6

Z7

Z8

Z9

Z10

Z11

Z12

Z13

BR EQ0#

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

AD S#

Z14

Z15

Z16

Z17

Z18

Z19

Z20

BN R #

Z21

Z22

DBSY#

DRDY#

HIT#

HITM #

Z23

HLOCK#

TPRDY#

IER R #

CPU_FERR#

UPICD0

UPICD1

TC K

TDI

TDO

TM S

TRST#

TH ER M D P

THER MD N

VC C 3

C677

.1 U ( R )

PW R O KK

VCC_SENSE24

HA#[3..31]

T

T

T

T

T

T

T

T

T

T

T

T

BR EQ0# 3

HREQ#03

HREQ#13

HREQ#23

HREQ#33

HREQ#43

AD S# 3

T

T

T

T

T

T

T

BN R # 3

T

T

DBSY# 3

DRDY#3

HIT# 3

HITM #3

T

HLOCK#3

TPRDY#

IER R #

CPU_FERR#

UPICD0

UPICD1

TC K

TDI

TDO

TM S

TRST#

TH ER M D P2

THER MD N2

R720 10K(R)

U51

5

VC C

4

OUT

TC7S08F(R)

R728 0

HA#[3..31]3

IN 1

IN 2

GND

VC C T

1

2

3

R 193 1K

R 194 1.5K

DBRESET#

PW RO K

PW RG OO D12

TPRDY#

TPREQ#

CPURST#3

PW RO K12

Z629

TDI

TDO

TC K

TM S

TRST#

HD#[0..63]

HD#[0..63]3

CPURST#3

R244 110_1%

CPUPWR GD

CPU_STP#

PICCLK

R257 0

STP C L K#12,20

G C L _ L O /H I#12

HCLKCPU11

R205 0

CPU_STP#11 ,1 2,20

PIC C L K11

BPR I#3

RS#03

RS#13

RS#23

HTRDY#3

DEFER#3

A20M #12

IG N N E#12

IN IT#12

IN T R12

NMI12

TPREQ#

BSEL0

BSEL111

SM I#12

FLUSH#

BPR I#

CPURST#

RS#0

RS#1

RS#2

Z1

T

HTRDY#

DEFER#

ED G E C T R L P

A20M #

IG N N E#

IN IT#

IN T R

NMI

TPREQ#

CPUPWR GD

BSEL0

BSEL1

SLP#

SM I#

FLUSH#

STP C L K#

G C L _ L O /H I#

HCLKCPU

UPICCLK

R242

1K(R )

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

D10

D11

C10

B11

C12

B13

A14

B12

E12

B16

A13

D13

D15

D12

B14

E14

C13

A19

B17

A18

C17

D17

C18

B19

D18

B20

A20

B21

D19

C21

E18

C20

D20

D21

H18

E20

H19

E21

H21

G20

P18

G21

K18

K21

M18

R19

K19

T20

M19

U18

R18

AA2

AA16

AD 10

AC 13

AA10

AB18

AC 19

AB20

AA12

AB15

AB12

AB10

AC 9

AC 11

AA18

F19

F18

J18

F21

J20

L18

L21

J21

L20

W1

M3

C7

C8

B9

A9

U4

A6

U1

Y1

U2

U3

V5

R2

H8

H10

D0#

D1#

D2#

D3#

CPUVCC

D4#

D5#

D6#

D7#

D8#

D9#

D10#

D11#

D12#

D13#

D14#

D15#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

BPR I#

RESET#

RS0#

RS1#

RS2#

RSP#

TRD Y#

DEFER#

ED G E C T R L P

A20M #

IG N N E#

IN IT#

LINT0/INTR

LINT1/NM I

PR EQ#

PW RG OO D

BSEL0

BSEL1

SLP#

SM I#

FLUSH#

STP C L K#

GHI#

BC LK

PIC C L K

A2A7A8

H12

H14

H16J7J9

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

LOW POWER GTL+ DATA BUS

GTL+ I nput

1.5V CM OS I nput

<-- 2 .5 CM OS Input

GND

GND

GND

GND

GND

GND

A12

A21B1B5B6B7B8B10

J11

J13

J15K8K10

K12

K14

K16L7L9

L11

L13

L15M8M10

M12

M14

M16N7N9

N11

N13

N15P8P10

P12

P14

P16R7R9

R11

R13

R15T8T10

T12

T14

T16U7U9

U11

U13

U15

U40A

L3

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

GTL+ Ou tput

1.5V O pen Drai n Outp ut

1.5V Op en D rain I/O

JTAG I NTER FACE

THERMAL INT ERFA CE

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

B15

B18C9C11

C15

C16

C19D2D6D7D9E3E7E8E9

E10

E11

E13

E19F3F6F7F8F9F10

GND

F11

F12

F13

F14

F15

F16

F20G3G19H2H7H9H11

A3#

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

CPUVCC

K3

A4#

J2

A5#

L4

A6#

L1

A7#

K5

A8#

K1

A9#

J1

A10#

J3

A11#

K4

A12#

G1

A13#

H1

A14#

E4

A15#

F1

A16#

F4

A17#

F2

A18#

E1

A19#

C4

A20#

D3

A21#

D1

A22#

E2

A23#

D5

A24#

D4

A25#

C3

A26#

C1

A27#

B3

A28#

A3

A29#

B2

A30#

C2

A31#

A4

A32#

A5

A33#

B4

A34#

C5

A35#

V20

DEP0#

T21

DEP1#

U21

DEP2#

R21

DEP3#

V18

DEP4#

P21

DEP5#

P20

DEP6#

U19

DEP7#

C6

BR EQ0#

T2

REQ0#

V4

REQ1#

V2

REQ2#

W3

REQ3#

W5

REQ4#

TH ER M D A

THER MD C

GND

GND

GND

AD S#

AP0#

AP1#

BP2#

BP3#

BPM 0#

BPM 1#

BIN IT#

BN R #

BERR#

AERR#

DBSY#

DRDY#

HIT#

HITM #

RP#

LOCK#

PR DY#

IER R #

FERR#

PIC D 0

PIC D 1

TC K

TDI

TDO

TM S

TRST#

GND

GND

H13

Copperm ine

PW R O KK12

AB2

AB1

Y2

AA21

Y21

W21

W19

V21

T4

E6

AA1

AA3

T1

V1

Y4

W2

R1

W20

AD 9

AC 12

AB21

Y20

AA11

AD 13

AC 15

AD 14

AA14

AA15

AB16

LOW POWER GTL+ INTERFACE

GND

GND

GND

STP C L K#

STP C L K#12,20

SM I#

SM I#12

SLP#

SLP#

IN IT#

IN IT#12

IN T R

IN T R12

NMI

NMI12

IG N N E#

IG N N E#12

A20M #

A20M #12

IER R #

IER R #

CPURST#

CPURST#3

FLUSH#

TPREQ#

TTC K

TTM S

TDI

TDO

BSEL0

BSEL111

TRST#

TC K

UPICD0

UPICD1

GCL_LO/HI#12

B

Q45

E C

2N3904

R183 0(R)

PWRGOOD

PW R O KK

TDI

TDO

TC K

TM S

TRST#

TPRDY#

TPREQ#

CPURST#

Title

Size Docum ent Num ber Rev

Custom

Date: Sheet

Mo nday, S eptem ber 18, 2 000

C?

.1 U

FLUSH#

TPREQ#

TTC K

TTM S

TDI

TDO

BSEL0

BSEL1

TRST#

TC K

UPICD0

UPICD1

G C L _ L O /H I#

VC C 3

R182

4.7K

FERR#

CPU_FERR#

R134 0(R)

D48

AC

F01 J 2 E

C676 .1U(R)

R 721 47

R 722 47

´ ¯ ⁄ „q ‚ £ C L E V O CO .

CLEVO CO.

uPG A 2 P III-1

71-51S00-D02

R163 680

R158 270

R 258 1.5K

R 160 1K

R 226 1.5K

R 225 1.5K

R 166 1.5K

R 157 1.5K

R 156 1.5K

R 292 56 .2 _1%

R 159 1.5K

R 227 1.5K

R 224 1K

R 180 1K

R179 150

R181 150

R164 10K

R189 R

R188 0

R 238 1K

R 236 1K(R )

R 241 1K

R 243 1K

R 327 1.5K

R682 R

FERR#12

CPU_FERR#

CPUPWR GD

R 326 1.5K

VC C T

1

2

3

4

TTC K

5

TTM S

6

7

8

9

10

11

12

VC C T

VC C T

CPUPWR GDPW R O KK12

V2 .5

CN29

VC C T

TDI

TDO

TC K

TM S

TRST#

PR DY#

PR EQ#

CPURST#

GND

DBRESET#

GND

Conn. 12P(R)

of

1

A

29

Schematic Drawings

Page 55

52

5

#

VCCT

R736

R

Z73 0

R737

0

VCC_CORE

G1 0

G1 1

G1 2

G1 3

G1 4

G1 5

G1 6

G1 7

H1 7

K17

L17

M1 7

N1 7

P17

R1 7

T17

U1 7

V10

V11

V12

V13

V14

V15

V16

V17

W10

W11

W12

W13

W14

W15

W16

W17

AA6

AA7

AA8

AB6

AB7

AB8

AC6

AC7

AC8

AD6

AD7

AD8

R1 0

R1 2

R1 4

R1 6

R2 0

T11

T13

T15

T18

T19

U1 0

U1 2

U1 4

U1 6

G6

G7

G8

G9

H6

J17

K6

L6

M6

N6

P1

P6

R6

T6

U6

V6

V7

V8

V9

W6

W7

W8

W9

Y6

Y7

Y8

R8

T3

T5

T7

T9

U8

J6

A15

A16

A17

C1 4D8D1 4

D1 6

E15G2G5

VCCT

NCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNCNC

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT/CPUVCC

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

H1 5

H2 0J4J8

G1 8H3H5J5M4M5P3P4AA5

GND

GND

GND

GND

GND

GND

GND

GND

GND

J10

GND

J12

J14

J16

J19K2K7K9K11

K13

FREQUENCY SELECT TABLE

AA19

AC3

AC17

AC20

AD15

NC

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

K15

K20L5L8

L10

L12

L14

L16

L19M7M9

M1 1

M1 3

M1 5

M2 0N2N3N4N8

GND

N1 0

N1 2

N1 4

N1 6

N1 8

N1 9

N2 0P5P7P9P11

U40B

E5

VRE F

E16

VRE F

E17

VRE F

F5

VRE F

F1 7

VRE F

U5

VRE F

Y17

VRE F

Y18

VRE F

L2

PLL1

M2

PLL2

AD17

TESTHI

Y5

TESTLO1

N5

TESTLO2

AD20

TES TP

H4

TES TP

AA17

TES TP

G4

TES TP

AD2

VID0

AD3

VID1

AD4

VID2

AC4

VID3

AB4

VID4

AD19

RTTIMPEDP

AA9

CMOS R E F

AD18

CMOS R E F

P2

CL K R E F

AB19

RSVD

U2 0

GND

V3

GND

V19

GND

W4

GND

W18

GND

Y3

GND

Y9

GND

Y10

GND

Y11

GND

Y12

GND

Y13

GND

Y14

GND

Y15

GND

Y16

GND

Y19

GND

AA4

GND

AA13

GND

AA20

GND

AB3

GND

AB5

GND

AB9

GND

AB11

GND

AB13

GND

AB14

GND

AB17

GND

AC1

GND

AC2

GND

AC5

GND

AC10

GND

AC14

GND

AC16

GND

AC18

GND

AC21

GND

AD1

GND

AD5

GND

AD16

GND

AD21

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

P13

P15

P19R3R4

R5

Copp erm in e

C178

C180

C232

C240

.1U

.1U

R146 1

Z29 0

R19 0 10K

R148 1K

R328 1K

R240 R

R135 R

R204 R

R329 R

VID0 15,24

VID1 15,24

VID2 15,24

VID3 15,24

VID4 15,24

R23 9 56.2_1%

R20 3 1K_1%(08 05)

R18 7 2K_1%(08 05)

R14 4 2K_1%(08 05)

R14 5 2K_1%(08 05)

C168

.1U

VS S_S E N SE

C246

.1U

PLL1

PLL2

Z3 1

.1U

C179

22U/10V_1210

TESTHI

TESTLO1

TESTLO2

TESTP1

TESTP2

TESTP3

TESTP4

VID0

VID1

VID2

VID3

VID4

RTTIMPEDP

CMOS R E F

CL K R E F

C261

T

.1U

R192 0

.1U

L51

4.7UH(08 05)

CP U VRM S ELE C T TABL E FO R u PGA 2 P 3

VCC_ Core

VID[4:0]

NO CPU

11111

0.925 V

11110

0.950 V

11101

0.975 V

11100

1.000 V

11011

1.025 V

11010

1.050 V

11001

1.075 V

11000

1.100 V

10111

1.125 V

10110

1.150 V

10101

1.175 V

10100

1.200 V

10011

1.225 V

10011

1.250 V

10001

1.275 V

10000

C239

C167

.1U

4.7U

VCCT

VCCT

VS S_S E N SE 2 4

VID[4:0]

01111

01110

01101

01100

01011

01010

01001

01000

00111

00110