CLARE MXED102 Datasheet

1

www.clare.com

MXED102

DS-MXED102-R2

The MXED102 is Clare’s second-generation OLED column driver offering, which supports up to 240-monochromatic or 80-color OLED pixels. The MXED102's

exceptionally tight current-matching of adjacent and

cascaded outputs, precharge options, and OLED monitoring capability, ensures uniform luminance and highquality greyscaling in both monochromatic and RGB

mode. This is the first ASSP production driver for OLED

module OEM's building a new standard in flat-panel displays.

• CMOS High Voltage Process: 9V-30V Display Panel

Supply Compatible

• 240 Output Channels, Cascadable

• Token-Based Bidirectional Data Transfer: Direct User

Control of Scan Rate

• Current Source Magnitude User Control: 4 µA to 1 mA

• 6-Bit Monochromatic/Color Gray-Scale User Control

• Current matching accuracy: ± 2% ± 1.5 µA intra-die

± 1% inter-die

• Monochromatic/Color Voltage Precharge Options

• Built-In A-to-D Converter Monitoring of Display Panel

Characteristics

• 3.3 V to 5 V logic supply

• Up to 35 MHz clock frequency

• Gold-Bumped Die @ 60 micron Output Pitch

• TCP packaging

• Companion to Clare Micronix MXED202

128-Channel OLED Row Driver

Features

Description

240-Channel OLED Column Driver

For All Passive-Matrix Organic-Light-EmittingDiode Displays

• Monochrome and Color

• Small-Molecule and Polymer

• Current-Sourcing Anode Drivers

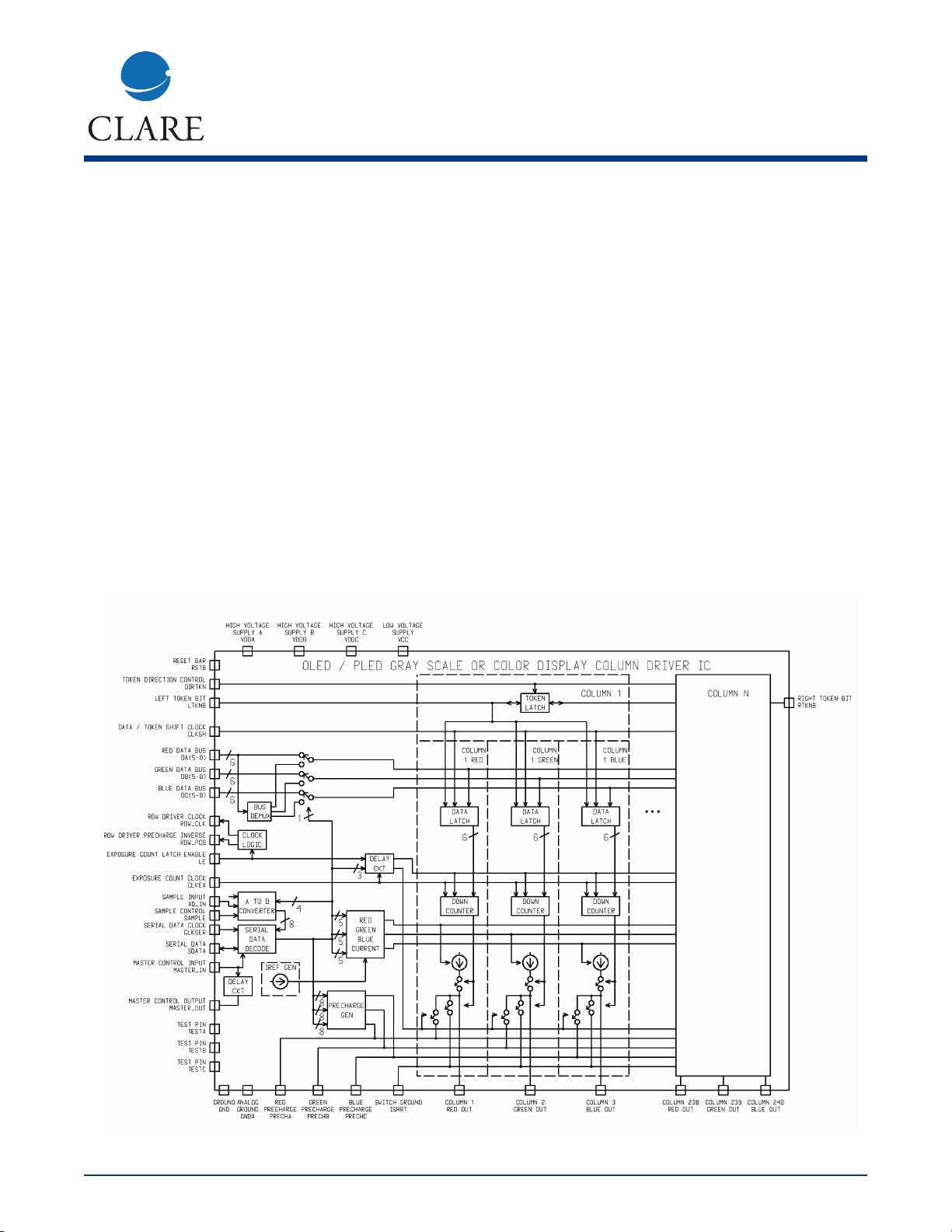

Column Driver Block Diagram

Preliminary

www.clare.com

2

MXED102

Rev. 2

Preliminary

PRELIMINARY ELECTRICAL DATA SHEET

This document is a specification for a digital data driver for Passive Matrix Organic Light Emitting Diode (OLED) and

Polymer Light Emitting displays (PLED, PolyLED, LEP, . . . ,etc) with anodes connected to the columns. The output

stage of each channel has a resistive switch to an on chip generated voltage used during precharge and a current

source used during data output to minimize non-uniformity caused by spatial and temporal variations of the LED

characteristics and by line resistances. The data driver chip is manufactured in a high voltage (30 V) CMOS process

and provided in bumped die and TCP (Tape Carrier Package) form.

Description of Operation:

Overview

: The MXED102 is configured via a serial port, and pixel data is updated on a per-row basis via a parallel

data bus.

Dynamic Pixel Control: Gray-Scale Control data is loaded into the 6-bit Column Exposure Counters each row scan

time, while the previously loaded data is being output to the OLED Display Panel. The control data sets the exposure time from 0 to 63 Exposure Clock times. Successive counters are accessed upon coincidence with the token

bit, which is shifted the length of the MXED102 by the Token Shift Clock. In 6-bit Data Mode, Databus C {DC(5-0)}

is used to enter per-pixel data, and the Token traverses length of the Chip in 240 Token Shift Clocks. In 18-bit Data

Mode, Databusses A, B, and C are used to load three successive pixels in parallel, and the Token traverses length

of the Chip in 80 Token Shift Clocks.

Chip Configuration: A display controller may use the serial bus to set the characteristics of all column driver ICs by

writing to all column driver ICs in parallel. During write, the controller writes the entire data packet. The controller

can also interrogate a single column driver IC, whose MASTER pin is pulled high. Only one column driver IC on a

given bus can be designated as master. During read, the controller writes the preamble, start of frame delimiter, register address, and turn around bits. It then tri-states for the bus tri-state and data bits and reads the data.

Color/Monochrome: The MXED102 supports three-each interleaved column Current Magnitude settings and three

Precharge Voltages, A,B and C, which may be mapped to R,G,B. Monochrome mode is selected by setting the

Color control bit to zero, in which case the Current Magnitude and Precharge Voltage is common.

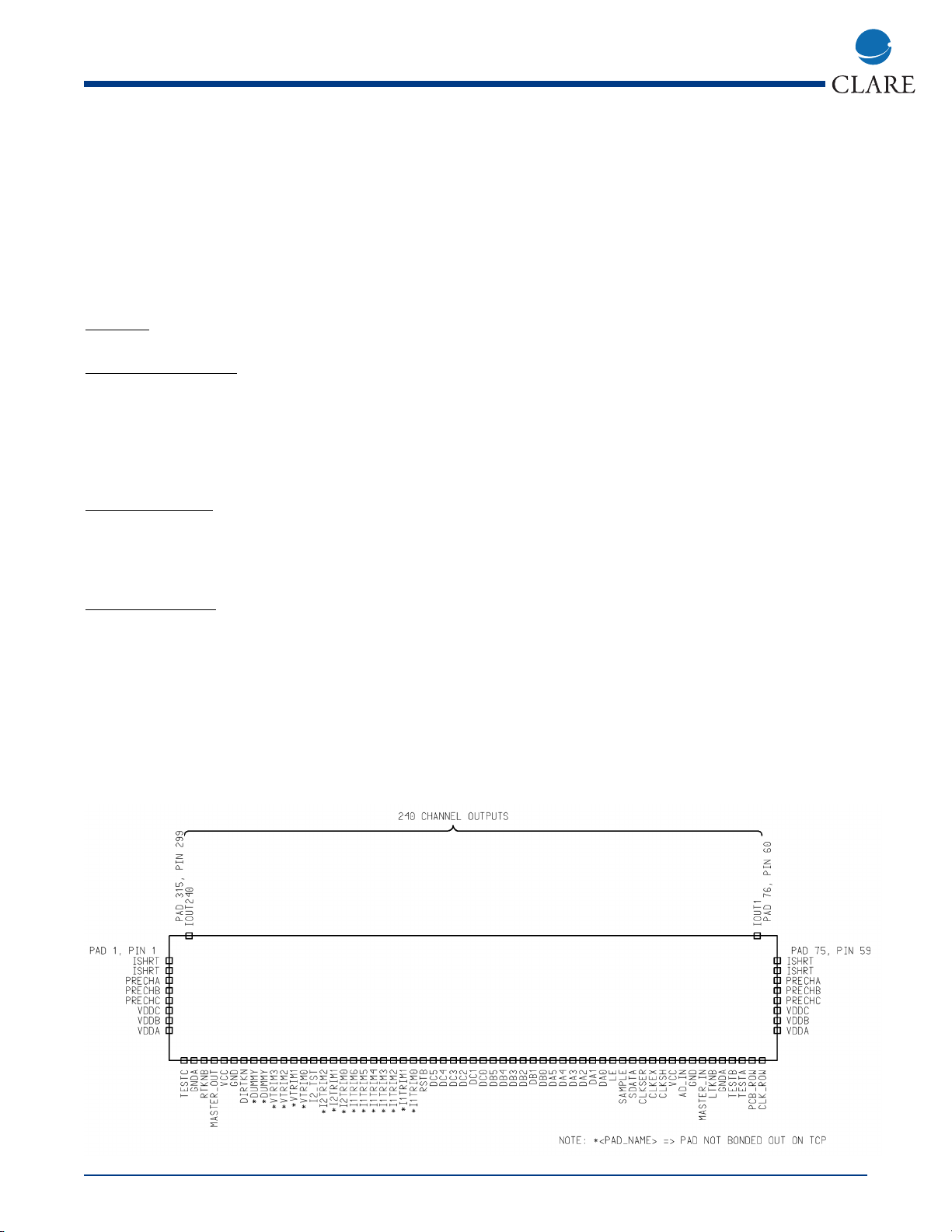

Package and Pin Out

Below is a diagram of the chip pinout:

MXED102 OLED/PLED Column Driver IC Pad Order

(NOT TO SCALE)

(DIE NOT FLIPPED)

MXED102

www.clare.com

3

Rev. 2

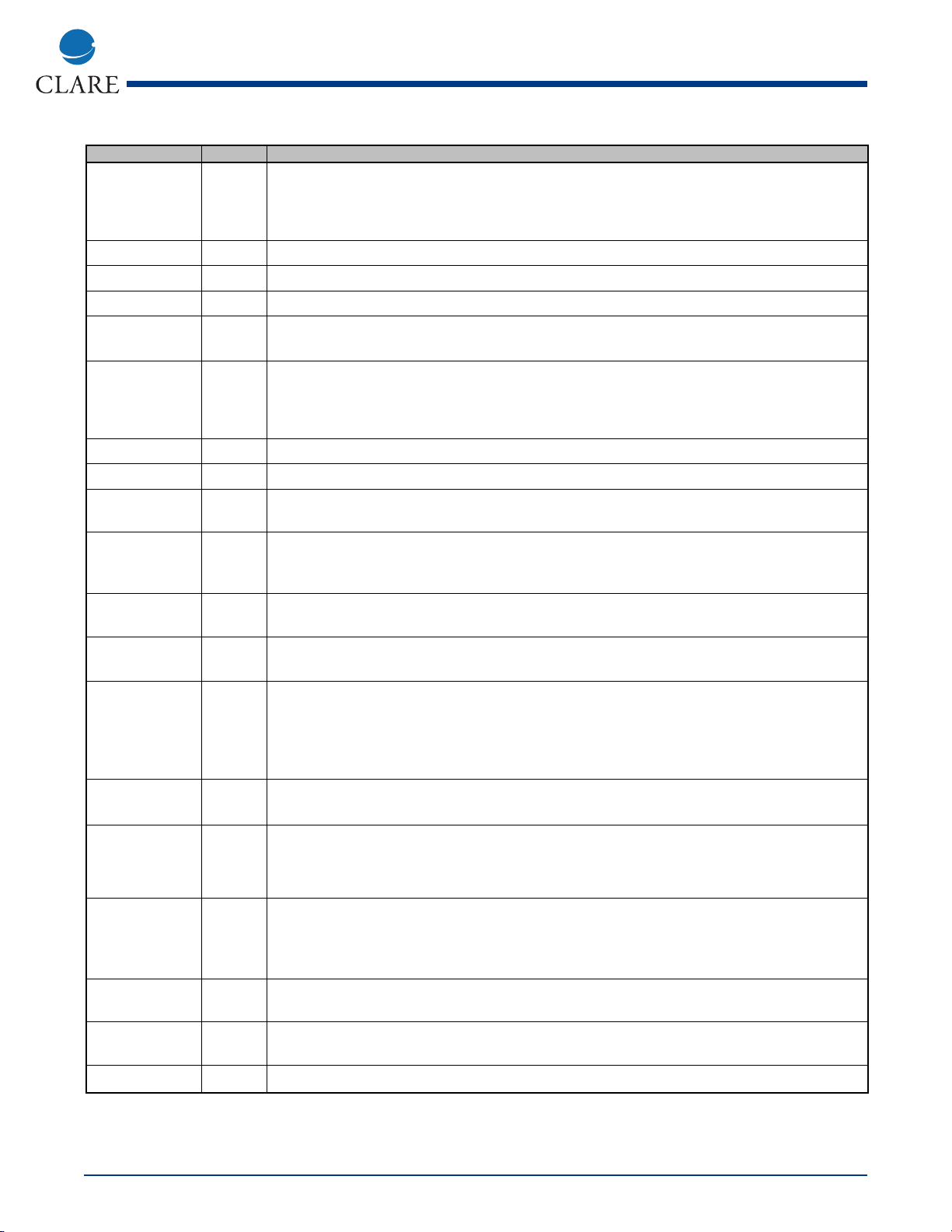

Pin List

Name I/O/A Description

VDDA, High voltage supply A/B/C:

VDDB, -

VDDC

VCC - Logic supply:

GND - Ground:

GNDA - Analog ground:

ISHRT - Ground used to short output channels: There can be high currents on this line. It

should be separated from the circuit ground pads (GND) to prevent ground bounce.

PRECHA, O/A

PRECHB,

PRECHC

MASTER_IN I Master In: High input implies chip is master. This input is pulled low internally.

MASTER_OUT O Master Out: MASTER_IN delayed by 1 LE clock cycle, sampled on rising edge of LE.

RSTB I Reset Bar: Input signal used to reset digital logic for test purposes. This input is

pulled high internally.

CLKSH I Token Shift Clock: Input signal used to shift tokens down the length of the driver IC

and latch data into the corresponding columns. The direction of token shift is deter

mined by DIRTKN pin.

LTKNB I/O Left Token Bit: Input for shift right, output for shift left. Signal is used to pass the

tokens into and out of the driver IC. High state represents the presence of token.

RTKNB I/O Right Token Bit: Input for shift left, output for shift right. Signal is used to pass the

tokens into and out of the driver IC. High state represents the presence of token.

DIRTKN I Token Direction Input: Input signal which, when high, causes the token to shift left to

right in the driver IC. A low signal causes the token to shift right to left. In the paral

lel data mode the token passes through the chip in 80 CLKSH clocks, in the serial

data mode the token passes through the chip in 240 CLKSH clocks. This input is

pulled high internally.

LE I Latch Enable: Input signal used to begin data output. When data output begins, new

data input for the following row can begin.

DA(5-0), I Data A/B/C: Signal buses used to input the exposure data.

DB(5-0),

DC(5-0)

CLKEX I Exposure Clock: Input signal used to clock the driver IC's exposure counter from 0 to

63 for a row exposure. The signal must be cycled at least 64 times between LE

pulses to completely cycle the counter. Cycles of CLKEX beyond 64 will have no

effect.

CLKSER I Serial Clock: Clock to write serial data into all column drivers or read serial data from

the master column driver.

SDATA I/O Serial Data: Serial data written to all column drivers or read from the master column

driver.

SAMPLE I Initiate A/D sample. This input is pulled low internally.

Precharge A/B/C: Column precharge voltage outputs. PRECHA/B/C should be tied

to PRECHA/B/C of all other column drivers to ensure a uniform display precharge

and should be bypassed to ground with a capacitor at least 50 times the display

capacitance.

Preliminary

www.clare.com

4

MXED102

Rev. 2

AD_IN A A to D Input: The part can do an A to D conversion on the voltage on this input.

TESTA, A Test Outputs: The A, B, and C driver bank outputs are muxed to the TESTA, TESTB,

TESTB, and TESTC pads respectively when these pads are pulled low. During normal

TESTC operation they are left open or tied to VDD.

I1TRIM A Current Source 1 Trim: These pins must be left open.

(6:0)

I2TRIM A Current Source 2 Trim: These pins must be left open.

(3:0)

VTRIM A Voltage Source Trim: These pins must be left open.

(3:0)

I2_TST A Current Source 2 Monitor: This pin must be left open.

IOUT(240-1) A Channel Outputs: The outputs of the driver IC that directly drives the display panel

CLK_ROW O Row Clock: Signal intended to drive the row driver IC shift data clock

PCB_ROW O Row Precharge: Signal intended to drive the row driver IC precharge input

Note: A => analog, I => digital input, O => digital output

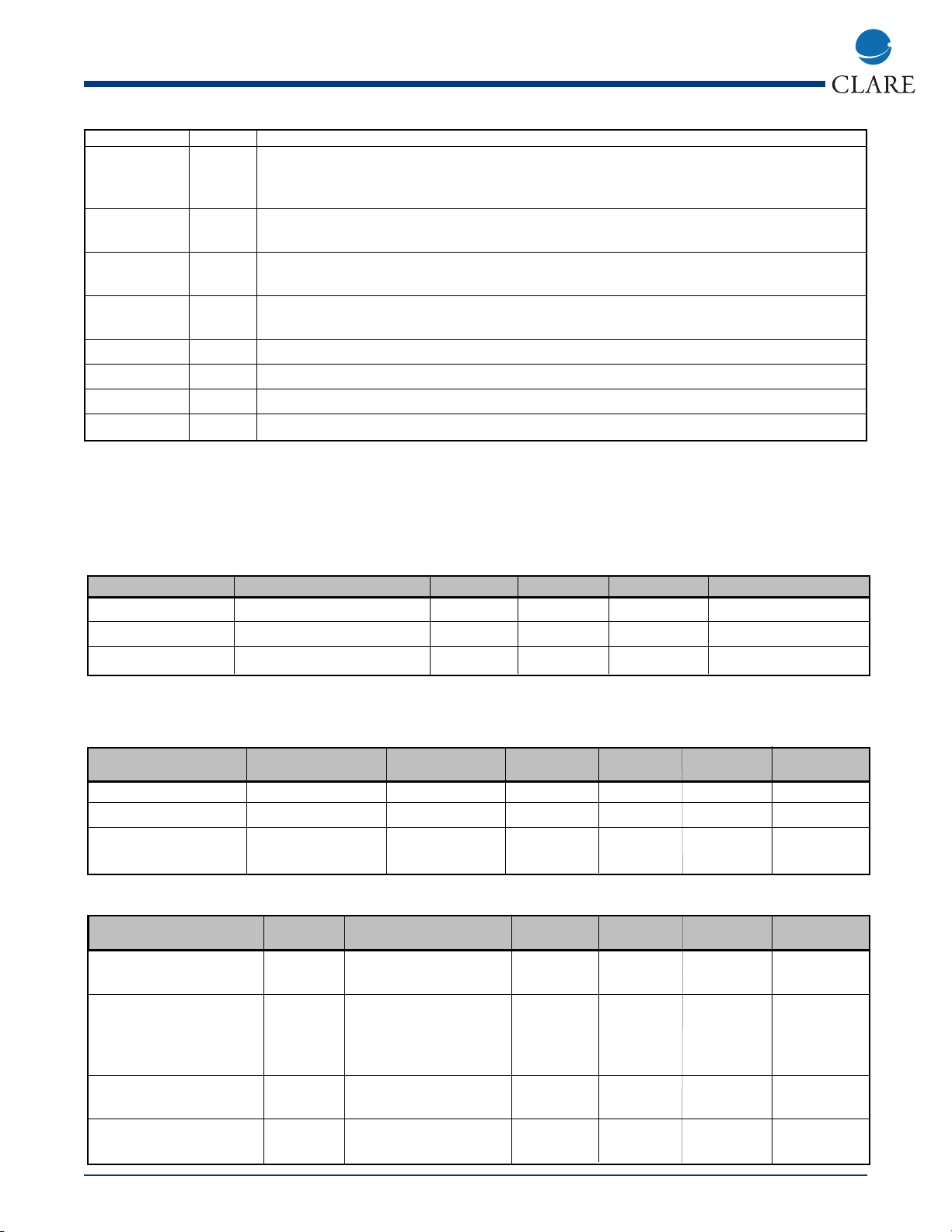

ELECTRICAL SPECIFICATIONS

Positive currents flow into the part, negative currents flow out of the part, largest currents are currents with the greatest absolute magnitude.

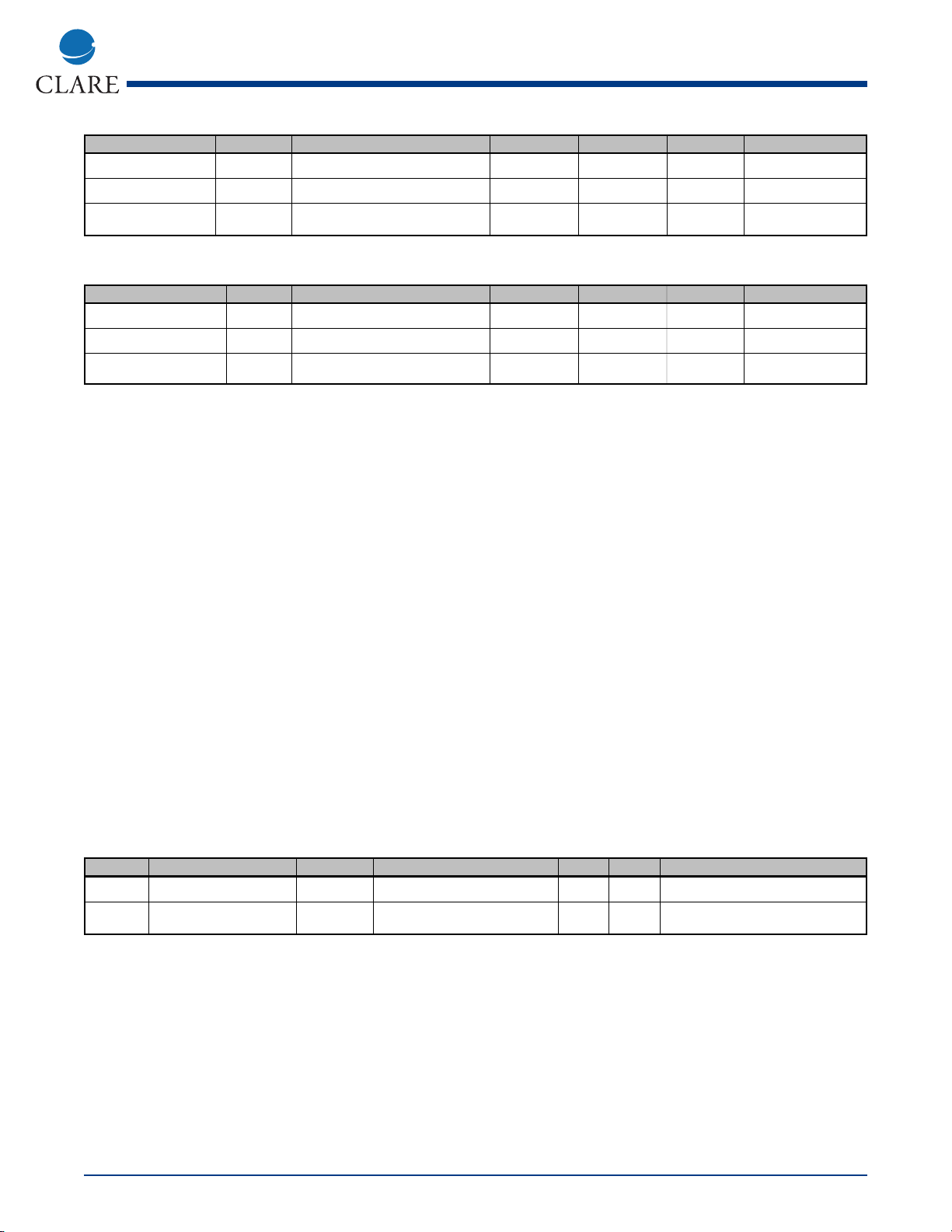

Absolute Maximum Ratings:

Parameter Operating Condition Min Typ Max Units

Ambient temp - -65 - 155

o

C

Low voltage supply - -0.3 - 7.0 V

High voltage supply - -0.3 - 35.0 V

Operating Conditions:

Unless otherwise stated, all parameters are specified for the following operating conditions.

Parameter Sym Operating Min Typ Max Units

Condition

Ambient temp TA - 0 - 70

o

C

Low voltage supply VCC - 3.0 - 5.5 V

High voltage supplies VDDA, - 9.0 - 30 V

VDDB, VDDC

Supply Currents:

Parameter Sym Operating Min Typ Max Units

Condition

High voltage supply IDD - - - TBD uA

current during standby (stby)

Internal high voltage IDD Current from VDD not 14 mA+ mA

supply current during (int) flowing out outputs or - - 12xIout

operation into precharge circuit

Iout = per channel

Low voltage supply ICC - - - TBD uA

current during standby (stby)

Low voltage supply ICC - - - 10 mA

current during operation

Preliminary

Pin List (continued)

MXED102

www.clare.com

5

Rev. 2

Digital Inputs:

Parameter Sym Operating Condition Min Typ Max Units

Input low voltage VIL - - - 0.5 V

Input high voltage VIH - VCC-0.5 - - V

Input current II - -10 - 10 uA

Digital Outputs:

Parameter Sym Operating Condition Min Typ Max Units

Output low voltage VOL Iout = 100 uA - - 0.4 V

Output high voltage VOH Iout = -100 uA VCC-0.4 - - V

Output rise/fall time TRF 10 to 90 %, Cload=5 pF - - 2.0 nS

Serial Configuration Bus:

Bus Operation:

The controller uses the serial bus to set the characteristics of all column driver ICs by writing to all column

driver ICs in parallel. During write, the controller writes the entire data packet. The controller can also inter

rogate a single column driver IC, who's MASTER pin is pulled high. Only 1 column driver IC on a given bus

can be designated as master. During read, the controller writes the preamble, start of frame delimiter, reg

ister address, and turn around bits. It then tri-states for the bus tri-state and data bits and reads the data.

Data Packet:

The data packet consists of:

- 14 bit preamble of all 1's

- 2 bit start of frame delimiter (SFD)

- 6 bit register address - MSB first

- 1 turn around bit (TA)

- 1 bus tristate (BT)

- 8 bit data packet - MSB first

Write => write data to all column driver ICs

Read => read data from master column driver IC

Data order => Preamble first, data last; MSB first, LSB last

R/W Preamble SFD Reg Address TA BT Data

write 1111 1111 1111 11 00 AAAA AA 0 0 DDDD DDDD

read 1111 1111 1111 11 01 AAAA AA 0 Z DDDD DDDD

Preliminary

www.clare.com

6

MXED102

Rev. 2

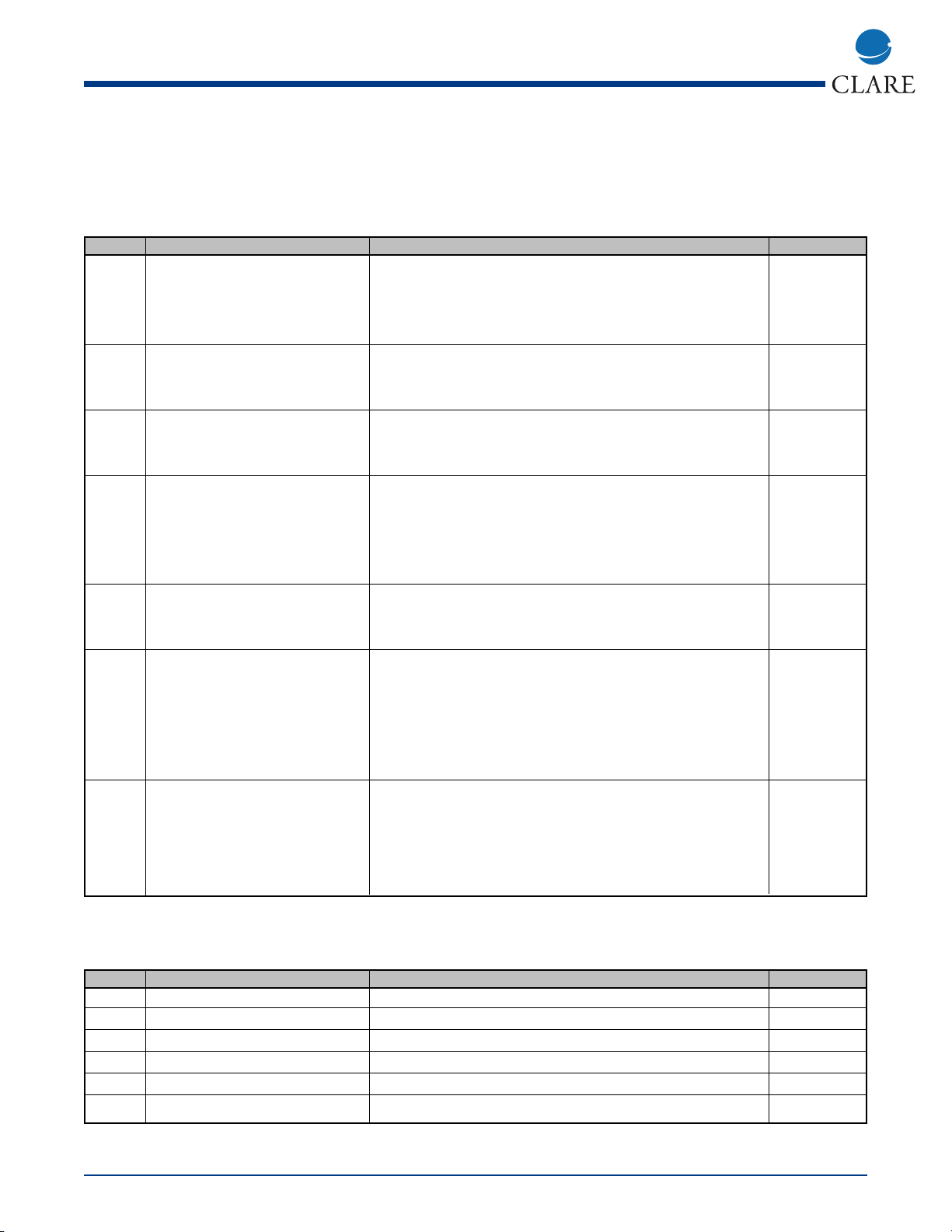

Input Registers

Register Address 0 - Test Register

Eight bits of data can be written to and read from this register in order to test the serial port. This register

has no effect on the column driver.

Register Address 1 - Control Register 1

Bit(s) Name Description Default

7 Freeze Master Modes:

1 => MASTER_OUT pin is not changed 0

0 => Normal, MASTER_OUT is updated to

MASTER_IN on rising edge of LE

6 Disable Precharge Driver Modes:

1 => Precharge circuit is disabled 0

0 => Normal

5 Standby Modes:

1 => Part is operating normally 0

0 => Part is in low power standby mode

4 Short Channels Modes:

1 => Channels are all shorted to ground after the 0

CLKEX count reaches 64

0 => Each channel is individually shorted to ground

after its current source is tristated

3 Color Mode Modes:

0 => Monochrome mode 0

1 => Color mode

2 Data Mux Modes:

0 => DA(5-0), DB(5-0), DC(5-0) data words are read 0

serially from the DC(5-0) pins. The DA(5-0) and

DB(5-0) pins are unused.

1 => DA(5-0), DB(5-0), DC(5-0) pins used to read

their respective data words.

1-0 Test Mode(1:0) Modes:

00 => Normal operation 00

01 => Test mode 1

10 => Test mode 2

11 => Test mode 3

Register Address 2 - Control Register 2

Bit(s) Name Description Default

7-2 Undefined - -

1 Fast Conversion Modes: -

- - 0 => Normal operation 0

-- 1 => -

0 High A/D Gain Modes: -

- - 0 => Normal operation 0

Preliminary

Loading...

Loading...