CLARE MXED101 Datasheet

1

www.clare.com

MXED101

DS-MXED101-R9

The MXED101 is a 6-bit, 192-output column driver IC

designed to drive passive matrix full-color (RGB) and monochrome Organic Light Emitting Diode (OLED) displays. Each

of the 192 current outputs is designed to act as a precision

high impedance current source. The MXED101 current source

output supply range is from 15 to 30V. The outputs are

arranged in a row on one side of the die with a pitch of 92

microns, which facilitates easy interface with the display.

The MXED101 consists of an Input Register, Transfer Latch,

Comparator, Bi-directional Shift Register, Counter, and 192

Programmable Current Outputs. The device has three 6-bit

input data buses, DA(5-0), DB(5-0), and DC(5-0), to accept

RGB or monochrome data. This data can be clocked through

the device at a maximum speed of 55 MHz with a 5V logic supply (40 MHz with a 3.3V logic supply).

The outputs of the MXED101 are arranged in three programmable interdigitized banks (A, B, and C) of 64 outputs each, a

bank for each color of the RGB data (programming the output

current is described in the Functional Description section). Bank

A controls outputs 1, 4, 7, …, 190; Bank B controls outputs 2, 5,

8, …, 191; and Bank C controls outputs 3, 6, 9, …, 192.

The MXED101 employs three methods to adjust display brightness: a global gain voltage, a 3-bit digital control for each color,

and an external 10.8 KW resistor. In addition to these methods,

the relative brightness of each output can be controlled by onchip pulse width modulation. A standby signal (STBY) is provided to place the display in low power standby mode whenever it

is necessary.

• CMOS technology

• 192 Precision outputs

• Programmable output current control

• Optimized adjacent channel and chip-to-chip output

matching

• 3.3V or 5V logic supply voltage

• 55 MHz clock frequency

• Cascadable

• 30V output driver supply voltage

• Bi-directional data transfer

• Supports Grayscale, Binary, and Standby modes

• Low power consumption

• Package type: TCP (MXED101TP) and Die

(MXED101DI)

Features:

General Description

30V, 192-Channel OLED Display Driver

Ordering Information

Part # Description

MXED101 30V, 192-Channel OLED

Display Driver

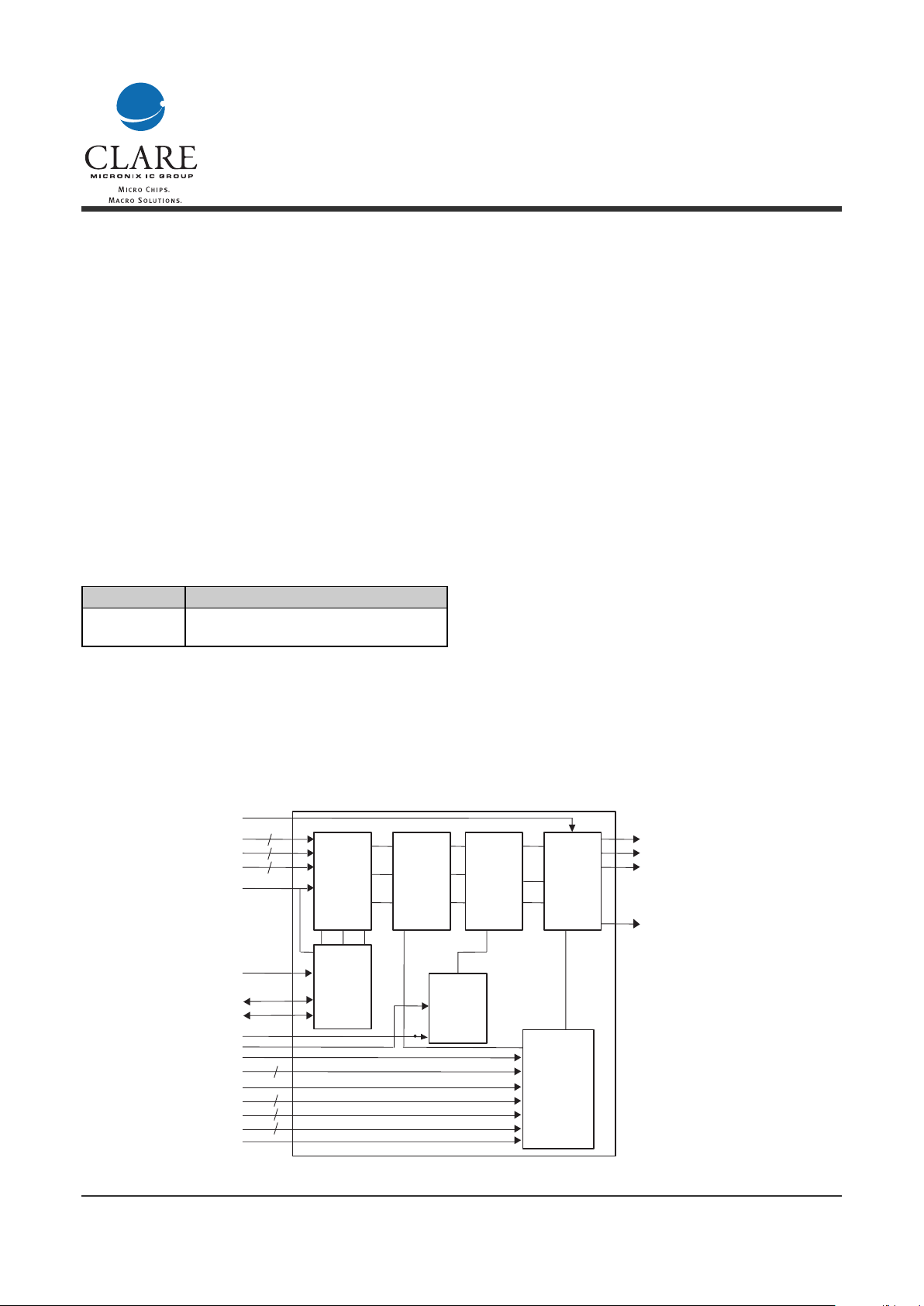

Block Diagram

Q1

Q2

Q3

.

.

.

Q192

.

.

.

.

192 X 6

Input

Register

192 x 6

Transfer

Latch

192 x 6

Comparator

Program-

mable

192-

channel

Output

Terminal

64 x 1

Bi-

Direction

Shift

Register

6-Bit

Up

Counter

Output

Mapping/

Current

Programmin

g

SWC

DA(5-0)

DB(5-0)

DC(5-0)

CLKSH

DIRTKN

RTKNB

LTKNB

LE

CLKEX

STBY

SDM(1-0)

GG

GA(2-0)

GB(2-0)

GC(2-0)

RG

Q1

Q2

Q3

Q192

www.clare.com

MXED101

Rev. 9

Electrical Characteristics

Absolute Maximum Ratings are stress ratings. Stresses

in excess of these ratings can cause permanent damage to the device. Functional operation of the device at

these or any other conditions beyond those indicated in

the operational sections of this data sheet is not implied.

Exposure of the device to the absolute maximum ratings for an extended period may degrade the device

and effect its reliability.

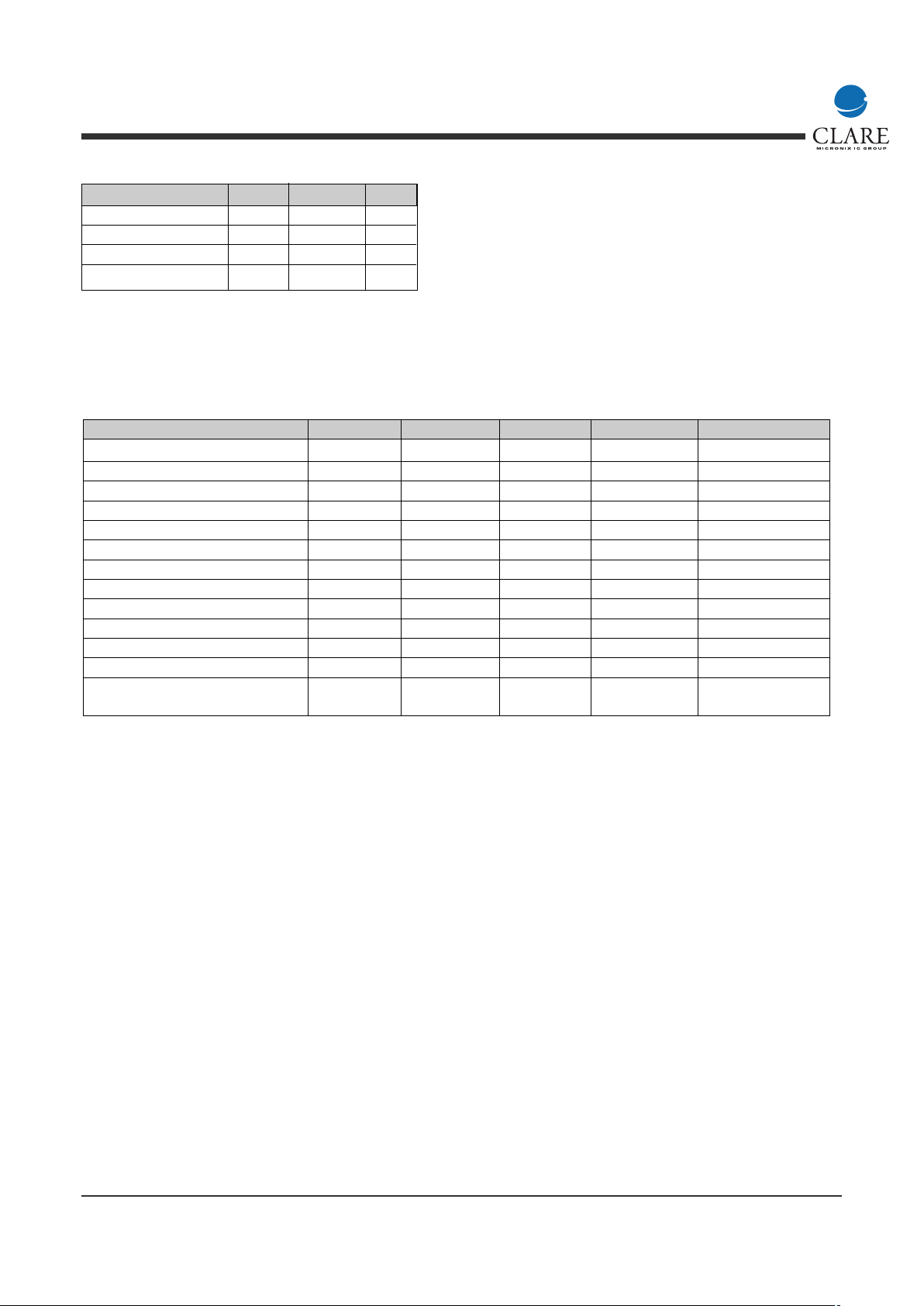

Absolute Maximum Ratings (Vss=OV)

2

Parameter Symbol Rating Unit

Logic Supply Voltage V

CC

-0.3 to 7.0 Vdc

Analog Supply Voltage V

DD

-.3 to 35.0 Vdc

Logic Input Voltage V

LIN

-.3 to VCC+.3 Vdc

Storage Temperature T

STG

-55 to 125 ˚C

Parameter Symbol Test Conditions Min Max Units

Logic Supply Voltage V

CC

3.0 5.5 Vdc

Analog Supply Voltage V

DD

15 30 Vdc

GG Voltage V

GG

VDD≥ 15V 0 12 Vdc

External RGPin Resistor R

RG

-0.1% +0.1% 10.8KΩ

High Logic Input Level V

IH

Vcc - 0.6 Vcc + 0.2 Vdc

Low Logic Input Level V

IL

-0.2 .6 Vdc

High Logic Level Input Current I

IH

-10 10 µA

Low Logic Level Input Current I

IL

-10 10 µA

High Logic Output Level V

OH

IOH>-10µA Vcc-0.2 V

Low Logic Output Level V

OL

IOL<10µA 0.2 V

Logic Supply Current I

cc

7mA

Analog Supply Current** I

DD

6.0 + Iout mA

Operating Temperature T

J

20 100 ˚C

(Junction)

**Analog supply current is highly dependable on the output current of the 192 output channels (Iout), which is determined by the application.

Note: V

dout

, I

bank

, and I

die

are transferred to the output parameters channels table.

MXED101

www.clare.com

Rev. 9

3

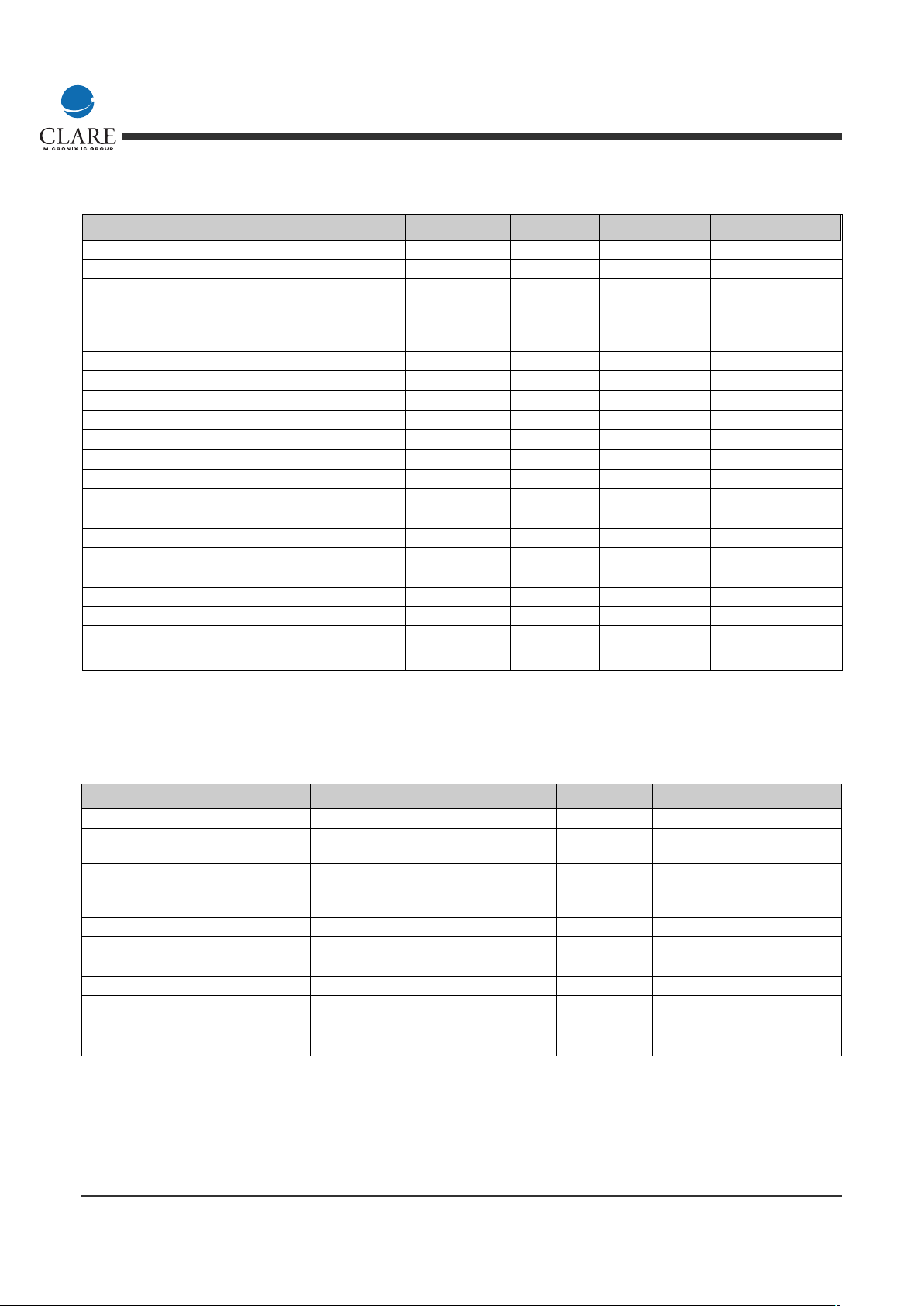

Digital Timing for Vcc in Range of 4.5 to 5.5 VDC

Parameter Symbol Min Typ Max Units

Shift Clock Frequency (VCC=4.5 + 5.5V) f

CLK

55 MHz

Shift Clock Frequency (VCC=3.0 to 4.4V) 40 MHz

Shift Clock Frequency Pulse Width t

SPW

722 nS

(VCC=4.5 + 5.5V)

Shift Clock Frequency Pulse Width t

SPW

9.6 30 nS

(VCC=3.0 to 4.4V)

Shift Clock Frequency Duty Cycle DC

SCK

40 50 60 %

Shift Clock to Latch Delay t

DSKL

3 (clock Cycles) nS

Exposure Clock Frequency f

EKF

10 MHz

Exposure Clock Pulse Width t

EPW

40 500 nS

Exposure Duty Cycle DC

EX

40 50 60 %

Data Setup Time t

DSU

5— — nS

Data Hold Time t

DHD

5— — nS

Token Setup Time t

TSU

5— — nS

Token Hold Time t

tHD

5— — nS

Token Bit Output Delay t

STD

—— 13 nS

Token Bit Pulse Width t

TPW

15 — — nS

Latch Pulse Width t

LAPW

50 — — nS

Last data to Latch Enable Time t

DLD

200 — — nS

Latch Disable to Exposure Clock Time t

LED

50 — — nS

Exposure Clock to Latch Enable Time t

DLE

50 — — nS

Standby to Ready Time t

STBY

10 mS

Output Channel Parameters

Parameter Symbol Typ Min Max Units

Driver Output Voltage Compliance V

Qn

VDD-3 Vdc

Per bank max to min channel output O<V

Qn<VDD

- 3,

current ratio I

BANK

V

Qn

match to 2V 1.0 1.04 A/A

High output die to low output die O<V

Qn<VDD

- 3,

average output current ratio I

DIE

V

Qn

match to 2V 1.0 1.02 A/A

R

RG

match to 0.1%

Output Current Rise Time t

IOR

_ _ 200 nS

Output Current Fall Time t

IOF

_ _ 200 nS

Output Current Settling Time t

IOS

_ _ 350 nS

Exposure Clock to Output High Delay t

OHD

_ _ 220 nS

Exposure Clock to Output Low Delay t

OLD

_ _ 220 nS

Channel output current rise/fall time t

IORF

10% to 90% 250 nS

Shorting Switch Resistance V(Qn) = IV 800 Ω

www.clare.com

4

MXED101

Rev. 9

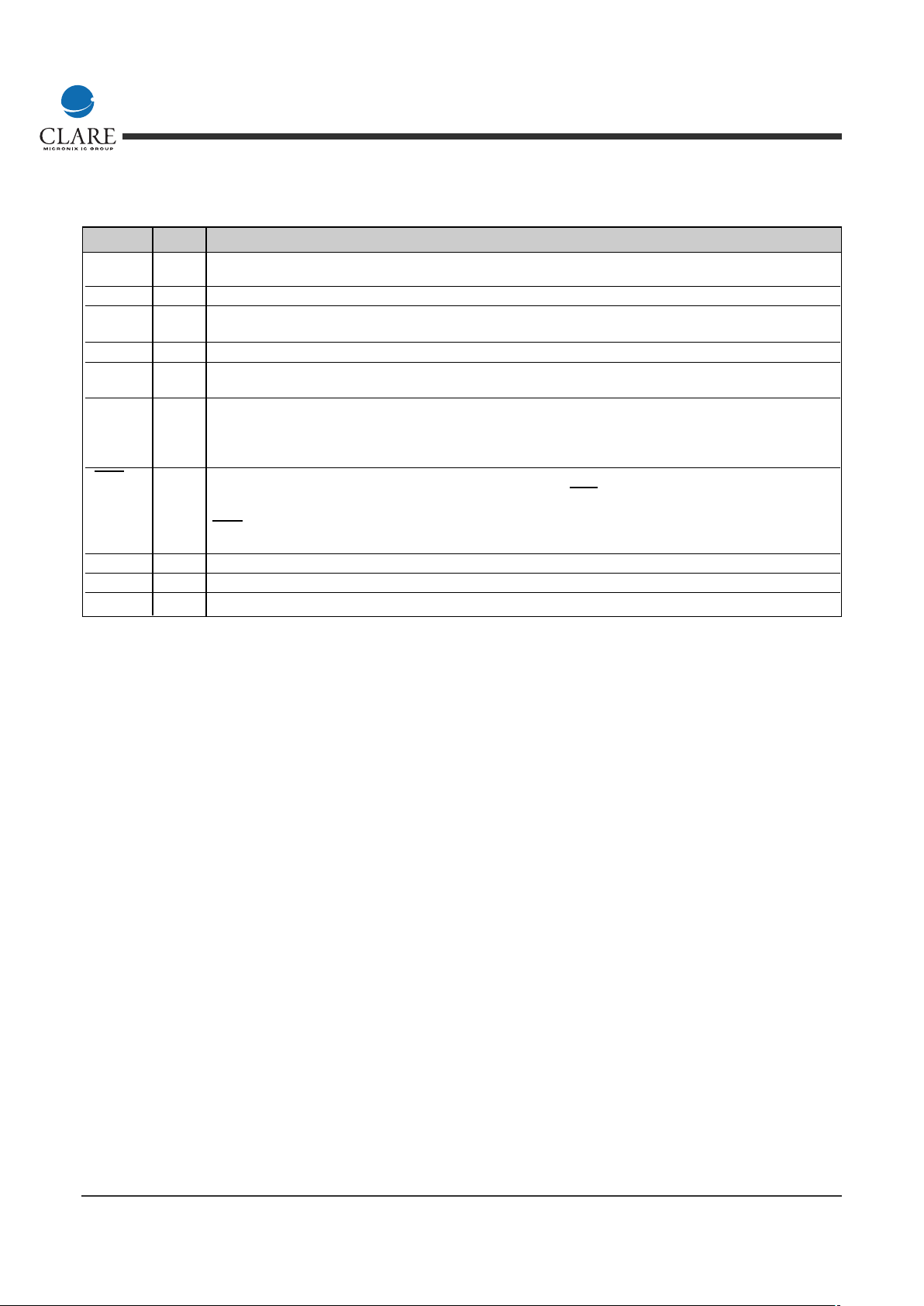

Signal Definition

Name I/0/A Description

V

DD

Power supply for the 192 current driver output channels - 6 pads

V

CC

Low voltage logic power supply - 2 pads

GND Ground - 4 pads

ISHRT Ground used to short the 192 current driver output channels - 4 pads. Note: There can be high currents on this line.

It should be seperated from the circuit ground pads (GND) to prevent ground bounce.

RSTB I Reset: Active low signal used to reset digital logic for test purposes. This input is pulled high internally.

CLKSH I Token Shift Clock: Used to shift tokens down the length of the driver IC. The direction of token shift is

determined by DIRTKN pin. It is possible to load only a portion of the 192 output channels prior to latching in

applications not requiring the full 192 channels. The speed of the clock is from DC to 55 MHz at 5V logic power

supply (40 MHz at 3.3V).

LTKNB I/O Left Token Bit: Used to pass the tokens into and out of the driver IC. The pin is used as input for shift right and as

output for shift left. High state represents the presence of token. The shifting is performed from DC to 55 MHz

(40 MHz at 3.3V).

RTKNB I/O Right Token Bit: Used to pass the tokens into and out of the driver IC. The pin is used as input for shift left and as

output for shift right. High state represents the presence of token. The shifting is performed from DC to 55 MHz

(40 MHz at 3.3V).

DIRTKN I Token Direction: Used to determine the shift direction of the token. When the signal is high, causes the token to shift

left to right (1–>64) and when the signal is low causes the token to shift to left (64–>1). This input is pulled high

internally. The token shifts 3 cells at a time to account for the 3 parallel data inputs.

LE I Latch Enable: Active high signal used to latch RGB data from the driver outputs into a set of transfer latches. Once a

line of data is latched into the transfer latch, OLED exposure can begin. At the same time, a new line of exposure data

can be loaded into the input register of the driver IC. On the rising edge of the of LE, all token registers are cleared, the

exposure counter is asynchronously preset to a low state and exposure data is allowed to pass from the input register

to the transfer latch. On the falling edge of LE, the exposure counter and output drivers are enabled within t

LED

(50 ns).

DA(5-0) I 6-bit Data input A. Signal bus used for the exposure data input word for outputs 1,4,7,…,190. The driver performs

at clock speed from DC to 55 MHz (40 MHz at 3.3V).

DB(5-0) I 6-bit Data input B. Signal bus used for the exposure data input word for outputs 2,5,8,…,191. The driver performs

at clock speed from DC to 55 MHz (40 MHz at 3.3V).

DC(5-0) I 6-bit Data input C. Signal bus used for the exposure data input word for channels 3,6,9,…,192. The driver performs

at clock speed from DC to 55 MHz (40 MHz at 3.3V).

CLKEX I Exposure Clock: Signal (DC to 10 MHz signal) used to clock the input of the driver ICs exposure counter (6-bits).

The signal is used to cycle the driver IC internal counter from 0 up to 63. The signal must be cycled at least 64 times

between LE pulses to completely cycle the counter. The first rising edge of CLKEX will enable all non zero outputs with-

out changing the counter. Additional rising edges of CLKEX will increment the counter. When the counter and data of

values for an output match, the output is disabled until LE re-enables the exposure counter. Cycles of CLKEX beyond 64

will have no effect until the next cycle of LE re-enables the counter.

TGR I Binary/Grayscale: Signal used to determine if the driver IC is either 6 bit grayscale or binary. Low –> grayscale.

High –> Binary. This input is internally pulled to a logic low.

GG A Global Gain: Used to set the global current gain. The voltage range on this pin is 0V to 12V when V

DD

is ≥ 15V. The

base current level is GG/RG, with a peak base current level of 1.455mA. This input is internally pulled to a logic low.

MXED101

www.clare.com

5

Rev. 9

Signal Definition (continued)

Name I/0/A Description

RG A Resistor Gain: Used to set the global current gain. A precision resistor shall be connected from this node to

analog ground which, in conjunction with the GG input voltage, sets up the base current level of the chip.

GA(2-0) I A Gain: Used to set the current on driver output channels 1,4,7,…,190. This input is internally pulled to a logic low.

GB(2-0) I B Gain: Used to set the current on driver output channels 2,5,8,…,191. This input is internally pulled to a

logic low.

GC(2-0) I C Gain: Used to set the current on driver output channels 3,6,9,…,192. This input is internally pulled to a logic low.

STBY I Standby Reset: Active high signal used to place the IC in a low power standby mode. When in the high state the IC

is non-functional and power dissipation is minimized. This input is internally pulled to a logic low.

SDM(1-O) I Stripe/Diagonal/Mosaic: These input signals are used to modify the output channel current levels depending on

which row of the display is active. The falling edge of LE is used to modify the A, B, C channels. When the STBY is

set to a logic high, the A, B, C channel outputs are reset to their initial mapping. These inputs are internally pulled to

a logic high. (See the SDM function below).

SWC I Switch Channels: This input signal is used to control when the individual output channels are in the tri-state condition

(current is not sourced and the switch to ground is off). When the SWC input is in the high state, each output

channel turns the switch to ground on as soon as the data count is matched and current source disabled. When

SWC is in the low state, each channel remains in the tri-state condition from when the current source is disabled

until the counter equals 63. This input is internally pulled to a logic low.

TST(9-0) I These pins should be left open circuited.

TEST(2-0) A These pins should be left open circuited.

Q1-Q192 A OLED current source driver outputs.

Note: A= > analog, I= > digital input, O= > digital output

Loading...

Loading...