CLARE M-986-2R2PL, M-986-2R2P, M-986-1R2P, M-986-1R2PL Datasheet

Part # Description

M-986-1R2P 40-pin plastic DIP, Single Channel

M-986-1R2PL 44-pin PLCC, Single Channel

M-986-2R2P 40-pin plastic DIP, Dual Channel

M-986-2R2PL 44-pin PLCC, Dual Channel

www.clare.com

DS-M976-2R2-R3

M-986-2R2

MFC Transceivers

1

Block Diagram

Pin Assignments

Ordering Information

Features

• Direct A-Law PCM digital input

• 2.048 Mb/s clocking

• Programmable forward/backward mode

• Programmable compelled/direct control

• Operates with standard codecs for analog

interfacing

• Microprocessor read/write interface

• Binary or 2-of-6 data formats

• Single- or dual-channel versions

• 5 volt power

Applications

• Test equipment

• Trunk adapters

• Paging terminals

• Traffic recorders

• PBXs

Description

The M-986-1R2 and -2R2 MFC Transceivers contain

all the logic necessary to transmit and receive CCITT

R2F (forward) and R2B (backward) multifrequency

signals on one 40-pin integrated circuit (IC). M-9861R2 is a single-channel version; M-986-2R2 provides

two channels. R1 single and dual multifrequency

transceivers are also available as M-986-1R1 and 2R1.

Operating with a 20.48 MHz crystal, the M-986 is

capable of providing a direct digital interface to an Alaw-encoded PCM digital input. Each channel can be

connected to an analog source using a coder-decoder

(codec) as shown in the Block Diagram below.

The M-986 can be configured by the customer to

operate with the transmitter and receiver either coupled together or independently, allowing it to handle a

compelled cycle automatically or via command from

the host processor. For the R2 versions of the M-986,

A-law is used for coding/decoding. The M-986 is configured and controlled through an integral coprocessor

port.

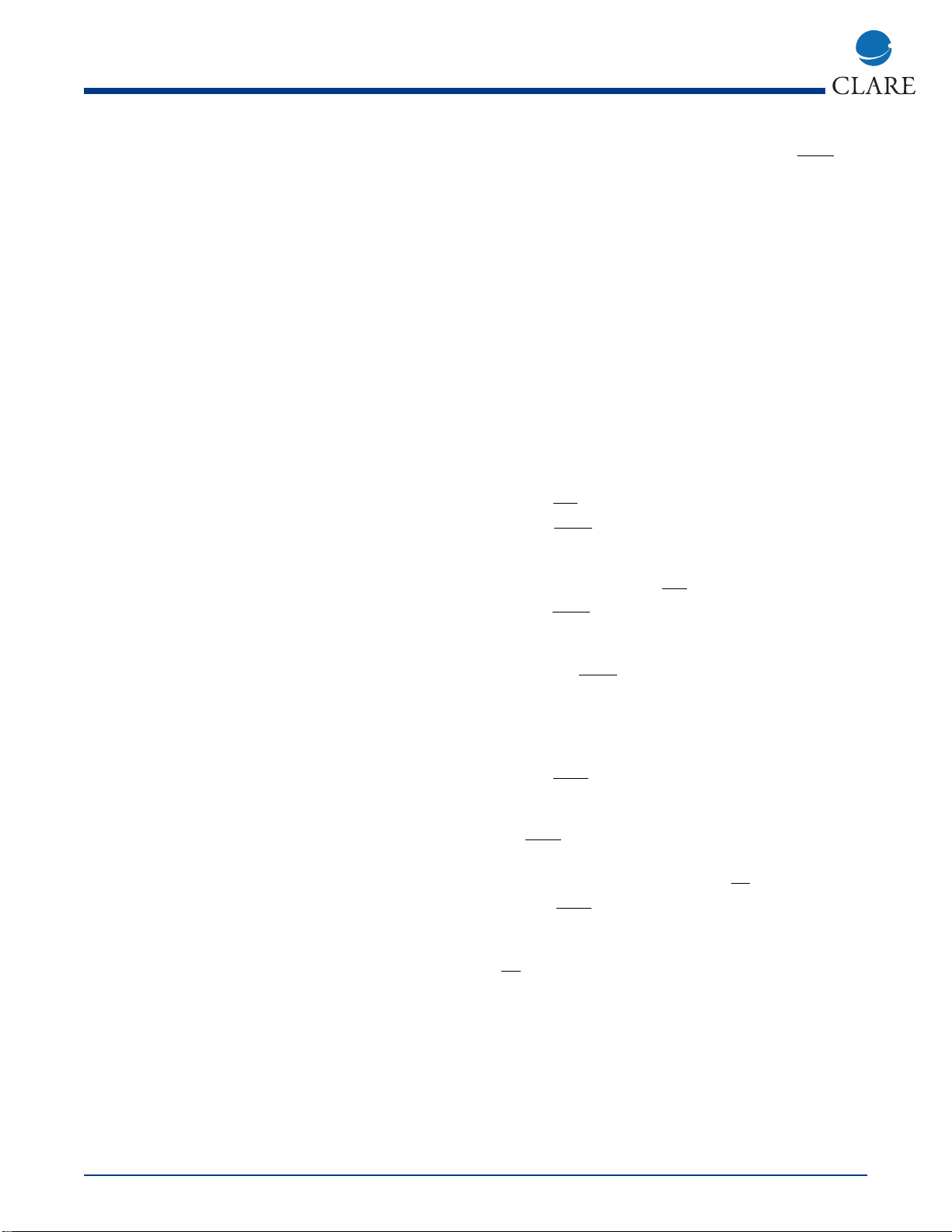

Configuration Bytes

Configuration Byte 1

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

0 0 ECLK IOM ENC1 EOD1 CMP1 FB1

ECLK Channels 1 & 2 1 = External codec clock; 0 = Internal codec clock

IOM Channels 1 & 2 1 = Binary input/output; 0 = 2-of-6 input/output

ENC1 Channel 1 1 = Enable channel; 0 = Disable channel

EOD1 Channel 1 1 = Indicate end of digit; 0 = No end of digit indication

CMP1 Channel 1 1 = Automatic Compelled mode; 0 = Manual mode

FB1 Channel 1 1 = Forward mode (Tx forward frequencies and Rx backward frequencies)

0 = Backward mode (Tx backward frequencies and Rx forward frequencies)

Configuration Byte 2

Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

0 1 0 0 ENC2 EOD2 CMP2 FB2

ENC2 Channel 2 1 = Enable channel; 0 = Disable channel

EOD2 Channel 2 1 = Indicate end of digit; 0 = No end of digit indication

CMP2 Channel 2 1 = Automatic Compelled mode; 0 = Manual mode

FB2 Channel 2 1 = Forward mode (Tx forward frequencies and Rx backward frequencies)

0 = Backward mode(Tx backward frequencies and Rx forward frequencies)

www.clare.com

2

M-986-2R2

Rev. 3

Function Description

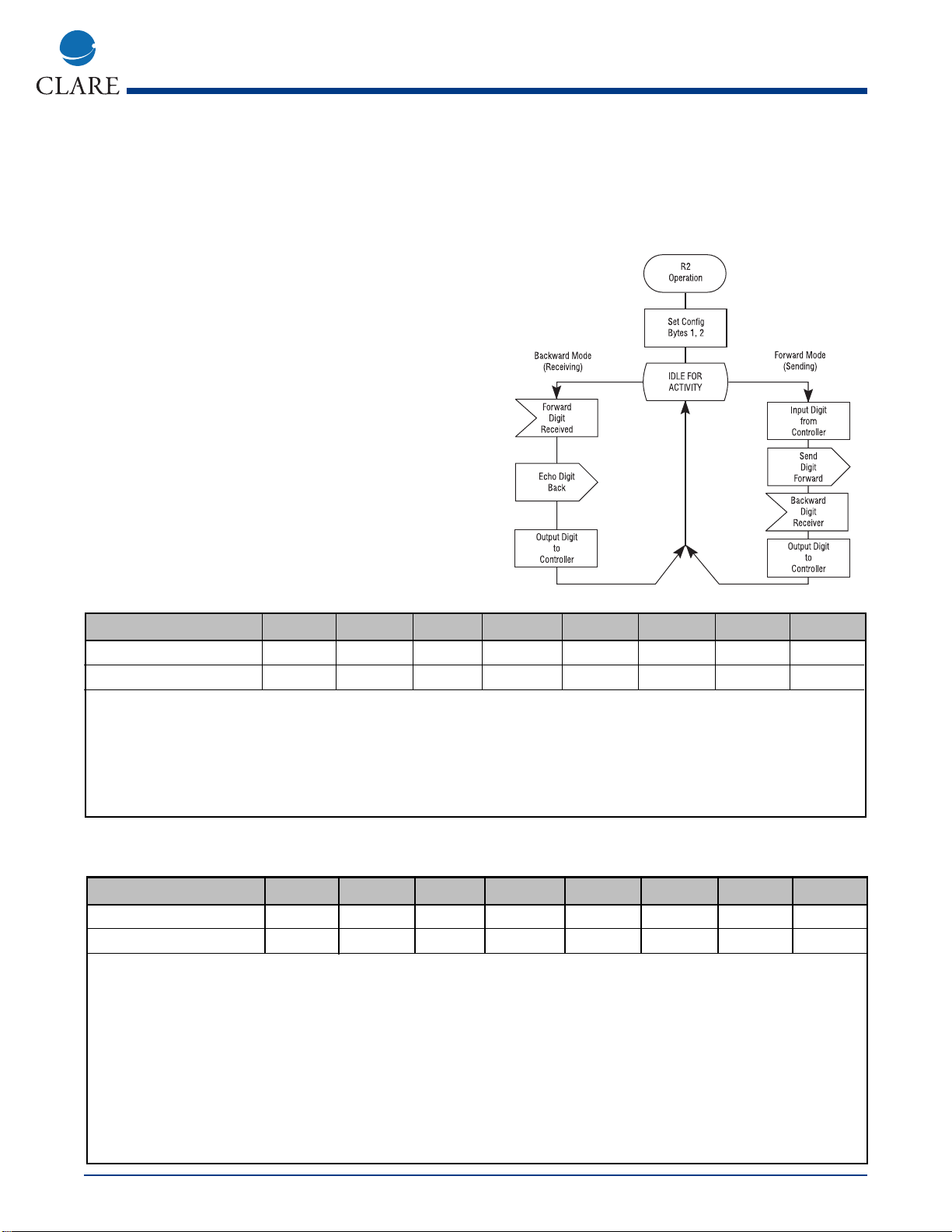

The M-986 can be set up for various operating modes

by writing two configuration bytes to the coprocessor

port.

Configuration Options

External/Internal Codec Clock (ECLK): If external

codec clocking is selected, an external clocking source

provides an 8kHz transmit framing clock and an 8kHz

receive framing clock. It also provides a serial bit clock

with a frequency that is a multiple of 8 kHz between

2.496 MHz and 216 kHz for exchange of data via the

serial ports. When internal codec clocking is selected,

the M-986 provides an 8kHz framing clock and a 2.048

MHz serial bit clock.

Binary/2 of 6 Input/Output (IOM): When the 2-of-6

input/output is selected, the M-986 encodes the

received R2 MF tone pair into in a 6-bit format, where

each bit represents one of the six possible frequencies.

A logic high level indicates the presence of a frequency. The digital input to the M-986 that selects the transmitted R2 MF tone pair must also be coded in the

2-of-6 format.

When binary input/output is selected, the M-986

encodes the received R2 MF tone pair into a 4 bit binary format. The digital input to the M-986 that selects the

transmitted R2 MF tone pair must also be coded in a 4

bit binary format.

Enable/Disable Channel (ENC): When a channel is

disabled, the receiver does not process its codec input

for R2 MF tones, and the transmitter does not respond

to transmit commands. If a transmit command is given

while the channel is enabled, the “tone off” command

must be given before the channel is disabled.

Disabling the channel does not automatically shut off

the transmitter. When a channel is enabled, the receiver and transmitter for that channel function normally.

End-of-Digit Indication (EOD): The end-of-digit indication option configures the M-986 to inform the host

processor when the far end terminates transmission of

the R2 MF tone it is sending. If this option is disabled,

the host processor will not be notified when tone

transmission terminates.

Automatic Compelled/Manual Sequence Signaling

(CMP): When manual mode is selected, R2 MF tone

transmission is turned on and off only via command

from the host processor.

If the automatic mode is selected, the transmitter and

receiver perform the compelled signaling handshake

automatically. The specifics of operation are different

for the forward and backward configurations.

In forward mode, the transceiver can exist in two

states, STATE 1 and STATE 2:

• STATE 1: No backward signal detected.

Transmitter under control of the host.

• STATE 2: Backward signal detected.

Transmitter off unconditionally.

M-986-2R2

www.clare.com

3

Rev. 3

A Transmit Tone Command written while the transceiver is in STATE 1 will be acted upon immediately. The

transmitter is unconditionally disabled upon entry into

STATE 2. If a transmit command is written to the transceiver while in STATE 2, that command will become

pending. Upon entry into STATE 1, a pending transmit

command is acted upon.

In backward mode, the transceiver can exist in two

states, STATE 1 and STATE 2:

STATE 1: No forward signal detected.

Transmitter off unconditionally.

STATE 2: Forward signal detected.

Transmitter transmits backward signal.

A transmit tone command written while the transceiver

is in STATE 2 will be acted upon immediately. The

transmitter is unconditionally disabled upon entry into

STATE 1. If a transmit command is written to the transceiver while in STATE 1, that command will become

pending. Upon entry into STATE 2, a pending transmit

command is acted upon.

EXAMPLE: Assume that the transceivers at both ends

of a link are configured in automatic compelled mode.

Both transceivers are in STATE 1. A compelled signaling sequence begins with the R2F host writing a transmit command byte to its transceiver via the

coprocessor bus. The transceiver immediately begins

transmitting the signal.

Automatic Compelled Mode Operation

Binary Coding Format

Byte Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Transmit tone command 1 CHN 0 0 A B C D

Receive tone return 0 CHN 0 0 A B C D

CHN: 1 = channel 2; 0 = channel 1

R2 MF Frequencies:

ABCD Forward (Hz) Backward (Hz) ABCD Forward (Hz) Backward (Hz)

0 0 0 0 Tone off Tone off 1 0 0 0 1500 & 1860 1020 & 660

0 0 0 1 1380 & 1500 1140 & 1020 1 0 0 1 1620 & 1860 900 & 660

0 0 1 0 1380 & 1620 1140 & 900 1 0 1 0 1740 & 1860 780 & 660

0 0 1 1 1500 & 1620 1020 & 900 1 0 1 1 1380 & 1980 1140 & 540

0 1 0 0 1380 & 1740 1140 & 780 1 1 0 0 1500 & 1980 1020 & 540

0 1 0 1 1500 & 1740 1020 & 780 1 1 0 1 1620 & 1980 900 & 540

0 1 1 0 1620 & 1740 900 & 780 1 1 1 0 1740 & 1980 780 & 540

0 1 1 1 1380 & 1860 1140 & 660 1 1 1 1 1860 & 1980 660 & 540

2 of 6 Coding Format

Byte Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Transmit tone command 1 CHN F6 F5 F4 F3 F2 F1

Receive tone return 0 CHN F6 F5 F4 F3 F2 F1

CHN: 1 = channel 2; 0 = channel 1

R2 MF Frequencies:

Bit name Forward (Hz) Backward (Hz) Bit name Forward (Hz) Backward (Hz)

F6 1980 540 F3 1620 900

F5 1860 660 F2 1500 1020

F4 1740 780 F1 1380 1140

www.clare.com

4

M-986-2R2

Rev. 3

The R2B transceiver detects the signal, enters STATE

2, and outputs the received tone code to its host via the

coprocessor port. If the R2B host had determined the

next tone to transmit and written a transmit command

to the transceiver prior to entry into STATE 2, the state

transition will cause this tone to be transmitted.

Otherwise, the R2B transmitter waits for a transmit

tone command from the host, and starts transmitting a

tone once the transmit tone command is received.

The R2F transceiver detects the backward signal,

enters STATE 2, and outputs the received tone code to

its host. Entry into STATE 2 unconditionally disables

the transmitter.

The R2B transceiver detects the absence of signal,

enters STATE 1, and informs the host with the end-oftone code if configured to do so. Entry into STATE 1

unconditionally disables the transmitter.

The R2F transceiver detects the absence of signal,

enters STATE 1, and informs the host with the end-oftone code if configured to do so. If the R2F host had

determined the next signal to transmit and written a

transmit command to the transceiver prior to entry into

STATE 1, the state transition will cause this signal to be

transmitted. Otherwise, the transmitter remains silent

until the next transmit command by its host.

Forward/Backward Frequencies (FB): When forward

mode is selected, the R2F (forward) frequencies are

transmitted and R2B (backward) frequencies are

received. When backward mode is selected, R2B frequencies are transmitted and R2F frequencies are

received. The R2F frequencies are 1380, 1500, 1620,

1740, 1860, and 1980 Hertz. The R2B frequencies are

540, 660, 780, 900, 1020, and 1140 Hz.

Initial Configuration: The configuration of the M-986

immediately after a reset will be as follows:

· End-of-digit indication ON

· Forward mode ON

· Channel disabled

· 2-of-6 input/output

· External serial and serial frame clocks.

Also, the M-986 will place 00 hex on the coprocessor

port to indicate to the host processor that it is working.

Transmit Tone Command

The transmit tone command allows the host processor

to transmit any two of the 6 possible frequencies in the

transmission mode the channel has been configured

for (forward or backward). The format of the command

depends on whether the M-986 is configured for binary format or 2-of-6 format.

Recieved Tone Detection

When a tone is detected by the M-986, the TBLF output goes low, indicating reception of the tone to the

host processor. The host processor can determine

which tone was detected and which channel the tone

was detected on by reading data from the M-986

coprocessor port. The M-986 will return a single byte

indicating the tone received and the channel that the

tone was received on.The format of the returned byte

depends on whether the M-986 is configured for binary or 2-of-6 coding.

Coprocessor Port

Commands are written to the M-986 via the coprocessor port, and data indicating the received R2 MF tone

is read from the coprocessor port.

Writing to the Coprocessor Port: The following

sequence describes writing a command to the M-986.

(1) The WR signal is driven low by the host processor.

(2) The RBLE (receive buffer latch empty) signal transitions to a logic high level.

(3) Data is written from LD7-LD0 to the receive buffer

latch (D7-D0) when the WR signal goes high.

(4) The RBLE signal transitions to a logic low level after

the M-986 reads the data. This signals the host

processor that the receive buffer is empty.

Note: The RBLE should be low before writing to the

coprocessor.

Reading the Coprocessor Port: The following

sequence describes reading received tone information

from the coprocessor port.

(1) The TBLF (transmit buffer latch full) port pin on the

M-986 goes low indicating the reception of a tone.

(2) The host processor detects the low logic level on

the TBLF pin either by polling a connected port pin or

by an interrupt.

(3) The host processor drives the RD signal low.

(4) The TBLF (transmit buffer latch full) signal transitions to a logic high level.

(5) Data is driven onto LD7-LD0 by the M-986 until the

RD signal is driven high by the host processor.

Clock Characeristics and Timing

Internal Clock Option: The internal oscillator is enabled

by connecting a crystal across X1 and X2/CLKIN. The

crystal must be 20.48 MHz, fundamental mode, and

parallel resonant, with an effective series resistance of

30 ohms, a power dissipation of 1 mW, and bespecified at a load capacitance of 20 pf.

Loading...

Loading...