CS8421

32-bit, 192 kHz Asynchronous Sample Rate Converter

Features

! 175 dB Dynamic Range

! –140 dB THD+N

! No Programming Required

! No External Master Clock Required

! Supports Sample Rates up to 211 kHz

! Input/Output Sample Rate Ratios from 7.5:1 to

1:8

! Master Clock Support for 128 x Fs, 256 x Fs,

384 x Fs, and 512 x Fs (Master Mode)

! 16, 20, 24, or 32-bit Data I/O

! 32-bit Internal Signal Processing

! Dither Automatically Applied and Scaled to

Output Resolution

! Flexible 3-Wire Serial Digital Audio Input and

Output Ports

RST

! Master and Slave Modes for Both Input and

Output

! Bypass Mode

! Time Division Multiplexing (TDM) Mode

! Attenuates Clock Jitter

! Multiple Part Outputs are Phase Matched

! Linear Phase FIR Filter

! Automatic Soft Mute/Unmute

! +2.5 V Digital Supply (VD)

! +3.3 V or 5.0 V Digital Interface (VL)

! Space-Saving 20-Pin TSSOP and QFN

Packages

See page 2 for Ordering Information.

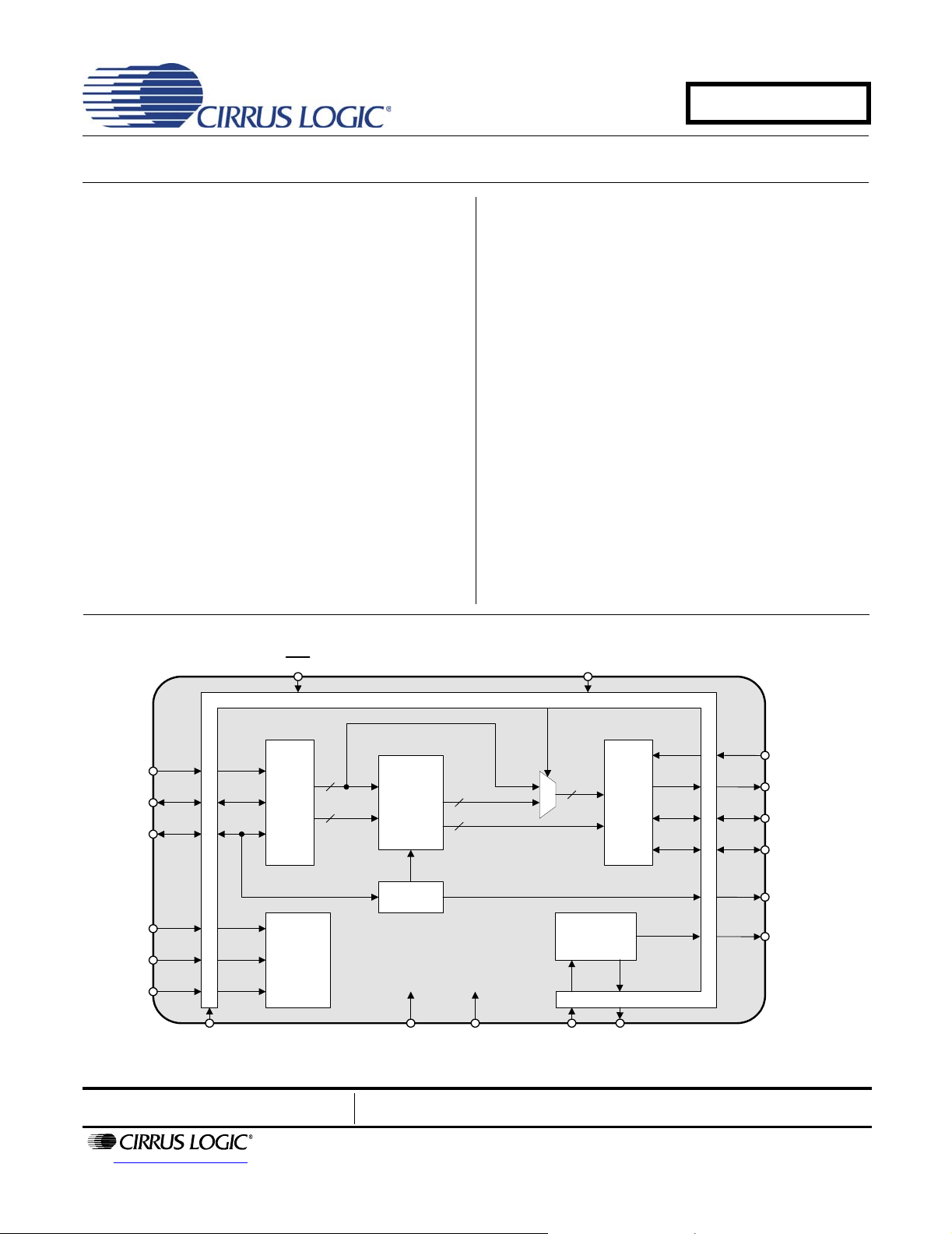

BYPASS

SDIN

Serial

ISCLK

ILRCK

Level Translators

MS_SEL

SAIF

SAOF

3.3 V or 5.0 V (VL)

Audio

Input

Sync Info

Serial

Port

Mode

Decoder

Preliminary Product Information

http://www.cirrus.com

Level Translators

Time

Data

Varying

Digital

Filters

Digital

PLL

2.5 V (VD) GND

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

Copyright © Cirrus Logic, Inc. 2005

Data

Sync Info

XTI XTO

(All Rights Reserved)

Serial

Audio

Data

Output

Clock

Generator

Level Translators

TDM_IN

SDOUT

OSCLK

OLRCK

SRC_UNLOCK

MCLK_OUT

JULY '05

DS641PP2

CS8421

General Description

The CS8421 is a 32-bit, high performance, monolithic CMOS stereo asynchronous sample ra te converter.

Digital audio inputs and outputs can be 32, 24, 20, or 16-bits. Input and output data can be completely asynchro-

nous, synchronous to an external data clock, or the part can operate without any external clock by using an

integrated oscillator.

Audio data is input and output through configur able 3-wire input/output ports. The CS8421 does no t require any software control via a control port.

Target applications include digital recording systems (DVD-R/RW, CD-R/RW, PVR, DAT, MD, and VTR), digital mixing consoles, high quality D/A, effects processors, computer audio systems, and automotive audio systems.

The CS8421 is also suitable for use as an asynchronous decimation or interpolation filter. See Cirrus Logic applications note AN270, “Audio A/D Conversion with an Asynchronous Decimation Filter”, available at www.cirrus.com for

more details.

The part is available in space saving 20-pin TSSOP and QF N pa ckag es and suppor ts sample rate s up to 211 kHz.

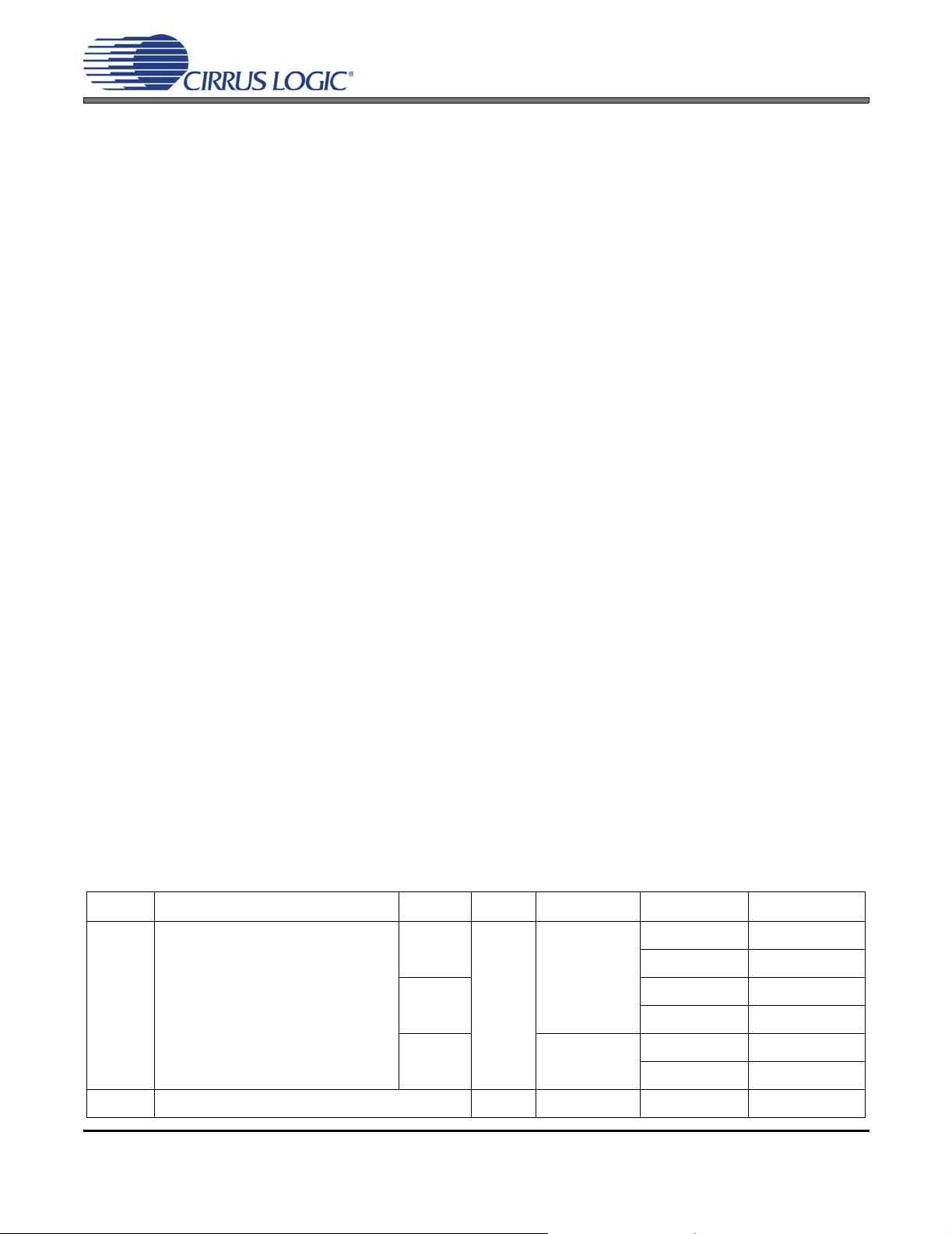

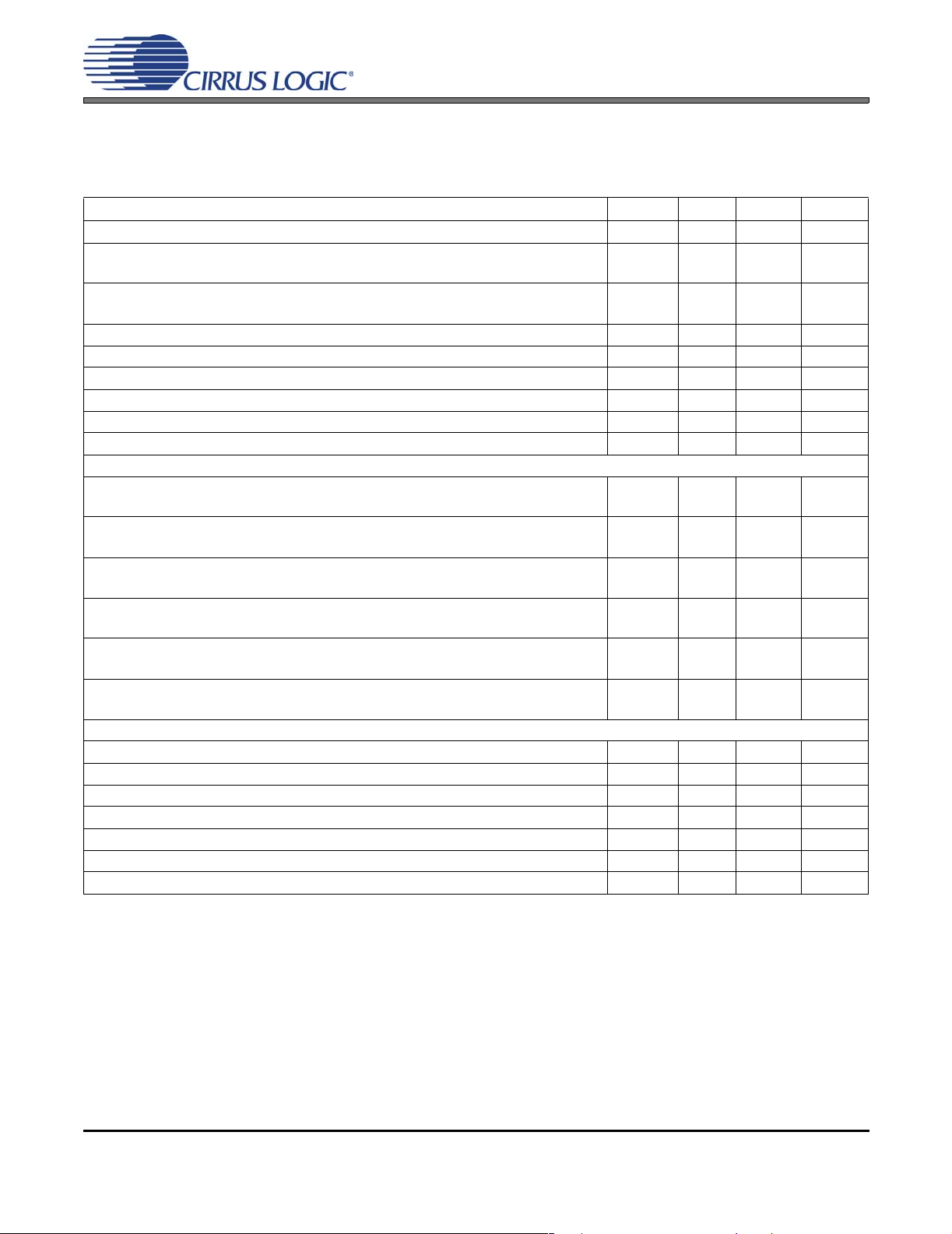

ORDERING INFORMATION

Product Description Package

TSSOP

CS8421

CDB8421

2 DS641PP2

32-bit Asynchronous Sample Rate

Converter

Evaluation Board for CS8421 - - - CDB8421

QFN

TSSOP -40° to +85°C

Pb-Free

YES

Temp Range Container

Rail CS8421-CZZ

Tape and Reel CS8421-CZZR

-10° to +70°C

Rail CS8421-CNZ

Tape and Reel CS8421-CNZR

Rail CS8421-DZZ

Tape and Reel CS8421-DZZR

Order#

TABLE OF CONTENTS

1. PIN DESCRIPTIONS ............................................................................................................................ 6

1.1 TSSOP Pin Descriptions ................................................. .... ... ... ... .................................................. 6

1.2 QFN Pin Descriptions ............................................................. ... ... ... .... ... ... ..................................... 8

2. CHARACTERISTICS AND SPECIFICATIONS ................................................................................... 10

SPECIFIED OPERATING CONDITIONS............................................................................................ 10

ABSOLUTE MAXIMUM RATINGS...................................................................................................... 10

PERFORMANCE SPECIFICATIONS......................................... ......................................................... 11

DIGITAL FILTER CHARACTERISTICS .............................................................................................. 12

DC ELECTRICAL CHARACTERISTICS .......... ... ... ... .... .......................................... ... ... ... ... .... ... ... ... ... 12

DIGITAL INPUT CHARACTERISTICS................................................................................................ 13

DIGITAL INTERFACE SPECIFICATIONS .......................................................................................... 13

SWITCHING SPECIFICATIONS ......................................................................................................... 13

3. TYPICAL CONNECTION DIAGRAMS ................................................................................................15

4. GENERAL DESCRIPTION .................................................................................................................. 17

5. THREE-WIRE SERIAL INPUT/OUTPUT AUDIO PORT ..................................................................... 17

6. MODE SELECTION ............................................................................................................................. 19

7. SAMPLE RATE CONVERTER (SRC) ................................................................................................. 20

7.1 Data Resolution and Dither ... .... ... ... ... ... .......................................... .... ... ... ... .... ... ... ... ................... 20

7.2 SRC Locking and Varispeed ........ ... ... ... .... ... ... ... .... ... ... ... .... ... ... ... ................................................ 20

7.3 Bypass Mode ................ ... ... ... .... ... ... ... ... .......................................... ............................................. 20

7.4 Muting .................... .......................................... ... .......................................... ................................ 21

7.5 Group Delay and Phase Matching Between Multiple CS8421 Parts ............................................ 21

7.6 Master Clock ....... .......................................... ... .......................................... ................................... 21

7.6.1 Clocking .... ... .... ... ............................................................................. .... ... ... ... ... .... ............ 22

8. TIME DIVISION MULTIPLEXING (TDM) MODE ................................................................................. 23

9. PERFORMANCE PLOTS ............................................................................................................ 25

10. APPLICATIONS ...................... .......................................... ... .... ... ...................................................... 34

10.1 Reset, Power Down, and Start-Up ............................................................................................. 34

10.2 Power Supply, Grounding, and PCB Layout .............................................................................. 34

11. PACKAGE DIMENSIONS ................................................................................................................ 35

THERMAL CHARACTERISTICS.........................................................................................................35

THERMAL CHARACTERISTICS.........................................................................................................36

12. REVISION HISTORY ........................................................................................................................ 37

CS8421

DS641PP2 3

LIST OF FIGURES

Figure 1. Non-TDM Slave Mode Timing..................................................................................................... 14

Figure 2. TDM Slave Mode Timing ............................................................................................................ 14

Figure 3. Non-TDM Master Mode Timing................................................................................................... 14

Figure 4. TDM Master Mode Timing .......................................................................................................... 14

Figure 5. Typical Connection Diagram, No External Master Clock............................................................ 15

Figure 6. Typical Connection Diagram, Master and Slave Modes............................................................. 16

Figure 7. Serial Audio Interface Format - I²S ............................................................................................. 18

Figure 8. Serial Audio Interface Format - Left-Justified.............................................................................. 18

Figure 9. Serial Audio Interface Format - Right-Justified ........................................................................... 18

Figure 10. Typical Connection Diagram for Crystal Circuit ........................................................................22

Figure 11. TDM Slave Mode Timing Diagram............................... .... ... ... ... ... .... ... ... ... .... ... ... ... ... .... ... ... ...... 23

Figure 12. TDM Master Mode Timing Diagram.......................................................................................... 23

Figure 13. TDM Mode Configuration (All CS8421 Outputs are Slave)....................................................... 24

Figure 14. TDM Mode Configuration (First CS8421 Output is Master, All Others are Slave).................... 24

Figure 15. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 48 kHz:48 kHz..................................... 25

Figure 16. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 44.1 kHz:192 kHz................................ 25

Figure 17. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 44.1 kHz:48 kHz.................................. 25

Figure 18. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 48 kHz:44.1 kHz.. .... ... ... ... ... .... ... ... ... ... 25

Figure 19. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 48 kHz:96 kHz..................................... 25

Figure 20. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 96 kHz:48 kHz..................................... 25

Figure 21. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone, 192 kHz:48 kHz................................... 26

Figure 22. Wideband FFT Plot (16k Points) -60 dBFS 1 kHz Tone, 48 kHz:96 kHz............................... ... 26

Figure 23. Wideband FFT Plot (16k Points) -60 dBFS 1 kHz Tone, 48 kHz:48 kHz............................... ... 26

Figure 24. Wideband FFT Plot (16k Points) -60 dBFS 1 kHz Tone, 44.1 kHz:192 kHz.......................... ... 26

Figure 25. Wideband FFT Plot (16k Points) -60 dBFS 1 kHz Tone, 44.1 kHz:48 kHz......................... ... ... 26

Figure 26. Wideband FFT Plot (16k Points) -60 dBFS 1 kHz Tone, 48 kHz:44.1 kHz............................... 26

Figure 27. Wideband FFT Plot (16k Points) -60 dBFS 1 kHz Tone, 96 kHz:48 kHz............................... ... 27

Figure 28. IMD, 10 kHz and 11 kHz -7 dBFS, 96 kHz:48 kHz ................................................................... 27

Figure 29. Wideband FFT Plot (16k Points) -60 dBFS 1 kHz Tone, 192 kHz:48 kHz................................ 27

Figure 30. IMD, 10 kHz and 11 kHz -7 dBFS, 48 kHz:44.1 kHz ................................................................ 27

Figure 31. IMD, 10 kHz and 11 kHz -7 dBFS, 44.1 kHz:48 kHz ................................................................ 27

Figure 32. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz Tone, 44.1 kHz:48 kHz................................ 27

Figure 33. Wideband FFT Plot (16k Points) 0 dBFS 80 kHz Tone, 192 kHz:192 kHz............................... 28

Figure 34. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz Tone, 48 kHz:96 kHz................................... 28

Figure 35. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz Tone, 48 kHz:48 kHz................................... 28

Figure 36. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz Tone, 96 kHz:48 kHz................................... 28

Figure 37. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz Tone, 48 kHz:44.1 kHz................................ 28

Figure 38. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz Tone, Fsi = 192 kHz..................................... 28

Figure 39. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz Tone, Fsi = 48 kHz....................................... 29

Figure 40. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz Tone, Fsi = 96 kHz....................................... 29

Figure 41. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz Tone, Fsi = 44.1 kHz.................................... 29

Figure 42. Dynamic Range vs. Output Sample Rate, -60 dBFS 1 kHz Tone, Fsi = 192 kHz .................... 29

Figure 43. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz Tone, Fsi = 32 kHz....................................... 29

Figure 44. Dynamic Range vs. Output Sample Rate, -60 dBFS 1 kHz Tone, Fsi = 32 kHz ...................... 29

Figure 45. Dynamic Range vs. Output Sample Rate, -60 dBFS 1 kHz Tone, Fsi = 96 kHz ...................... 30

Figure 46. Dynamic Range vs. Output Sample Rate, -60 dBFS 1 kHz Tone, Fsi = 44.1 kHz ................... 30

Figure 47. Frequency Response with 0 dBFS Input ..................................................................................30

Figure 48. Passband Ripple, 192 kH z: 48 kHz ..................................................... ... ... ................................ 30

Figure 49. Dynamic Range vs. Output Sample Rate, -60 dBFS 1 kHz Tone, Fsi = 48 kHz ...................... 30

Figure 50. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 48 kHz:48 kHz ....................................... 30

Figure 51. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 48 kHz:44.1 kHz.................................... 31

Figure 52. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 48 kHz:96 kHz ....................................... 31

CS8421

4 DS641PP2

Figure 53. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 96 kHz:48 kHz.................... ... .... ... ... ... ... 31

Figure 54. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 44.1 kHz:192 kHz.................. .... ... ... ... ... 31

Figure 55. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 44.1 kHz:48 kHz................. ... .... ... ... ... ... 31

Figure 56. Linearity Error, 0 to -140 dBFS Input, 200 Hz Tone, 192 kHz:44.1 kHz...................... ... ... ... ... 31

Figure 57. THD+N vs. Input Amplitude, 1 kHz Tone, 48 kHz:44.1 kHz ..................................................... 32

Figure 58. THD+N vs. Input Amplitude, 1 kHz Tone, 48 kHz:96 kHz ........................................................ 32

Figure 59. THD+N vs. Input Amplitude, 1 kHz Tone, 96 kHz:48 kHz ........................................................ 32

Figure 60. THD+N vs. Input Amplitude, 1 kHz Tone, 44.1 kHz:192 kHz ................................... .... ... ... ... ... 32

Figure 61. THD+N vs. Input Amplitude, 1 kHz Tone, 44.1 kHz:48 kHz ..................................................... 32

Figure 62. THD+N vs. Input Amplitude, 1 kHz Tone, 192 kHz:48 kHz ...................................................... 32

Figure 63. THD+N vs. Frequency Input, 0 dBFS, 48 kHz:44.1 kHz........................................................... 33

Figure 64. THD+N vs. Frequency Input, 0 dBFS, 48 kHz:96 kHz.............................................................. 33

Figure 65. THD+N vs. Frequency Input, 0 dBFS, 44.1 kHz:48 kHz..................... ... ... .... ... ... ... ... .... ... ... ...... 33

Figure 66. THD+N vs. Frequency Input, 0 dBFS, 96 kHz:48 kHz.............................................................. 33

LIST OF TABLES

Table 1. TSSOP Pin Descriptions................................................................................................................ 7

Table 2. QFN Pin Descriptions..................................................................................................................... 9

Table 3. Serial Audio Port Master/Slave and Clock Ratio Select Start-Up Options (MS_SEL) ................. 19

Table 4. Serial Audio Input Port Start-Up Options (SAIF)................................................. ......................... 19

Table 5. Serial Audio Output Port Start-Up Options (SAOF) ..................................................................... 19

CS8421

DS641PP2 5

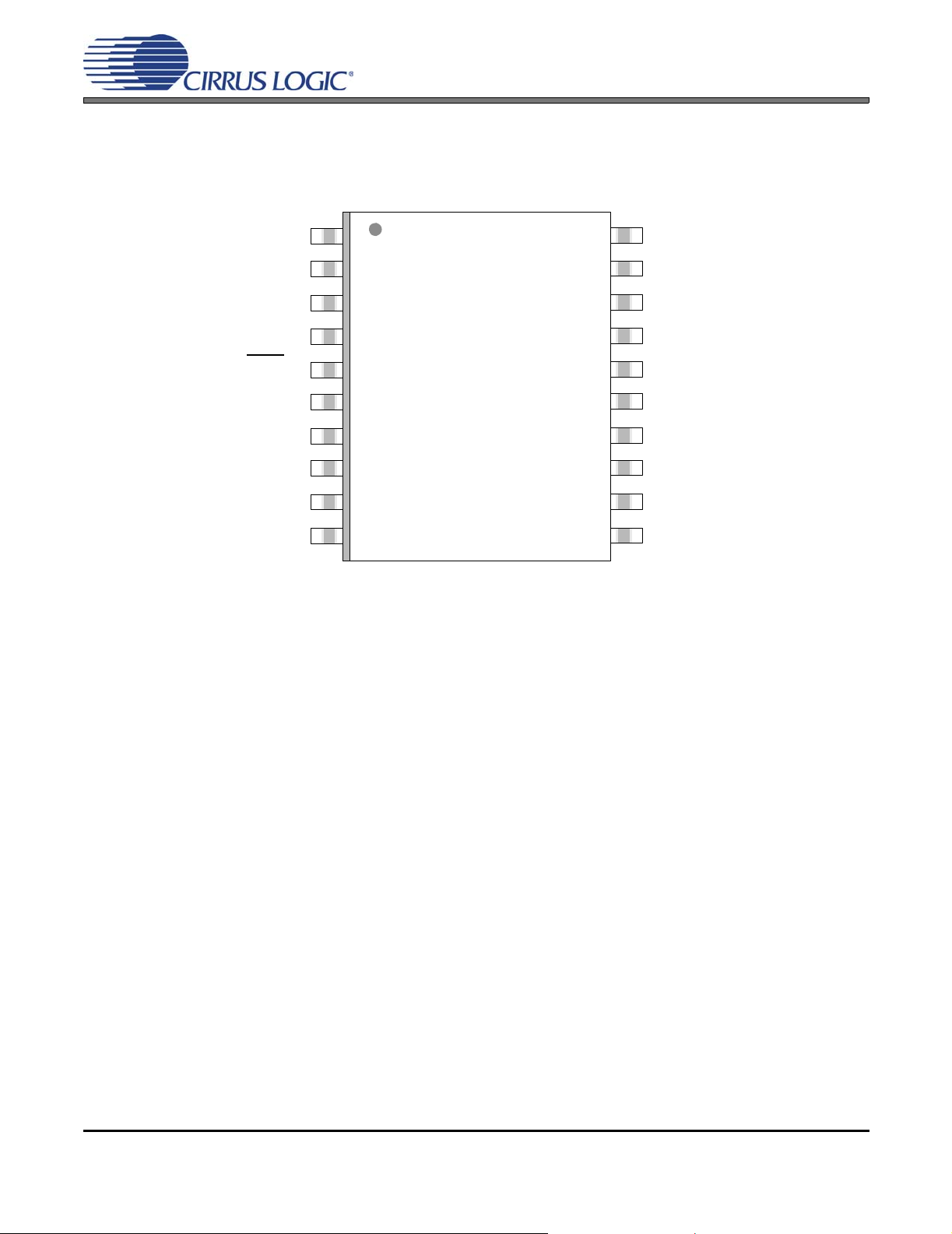

1. PIN DESCRIPTIONS

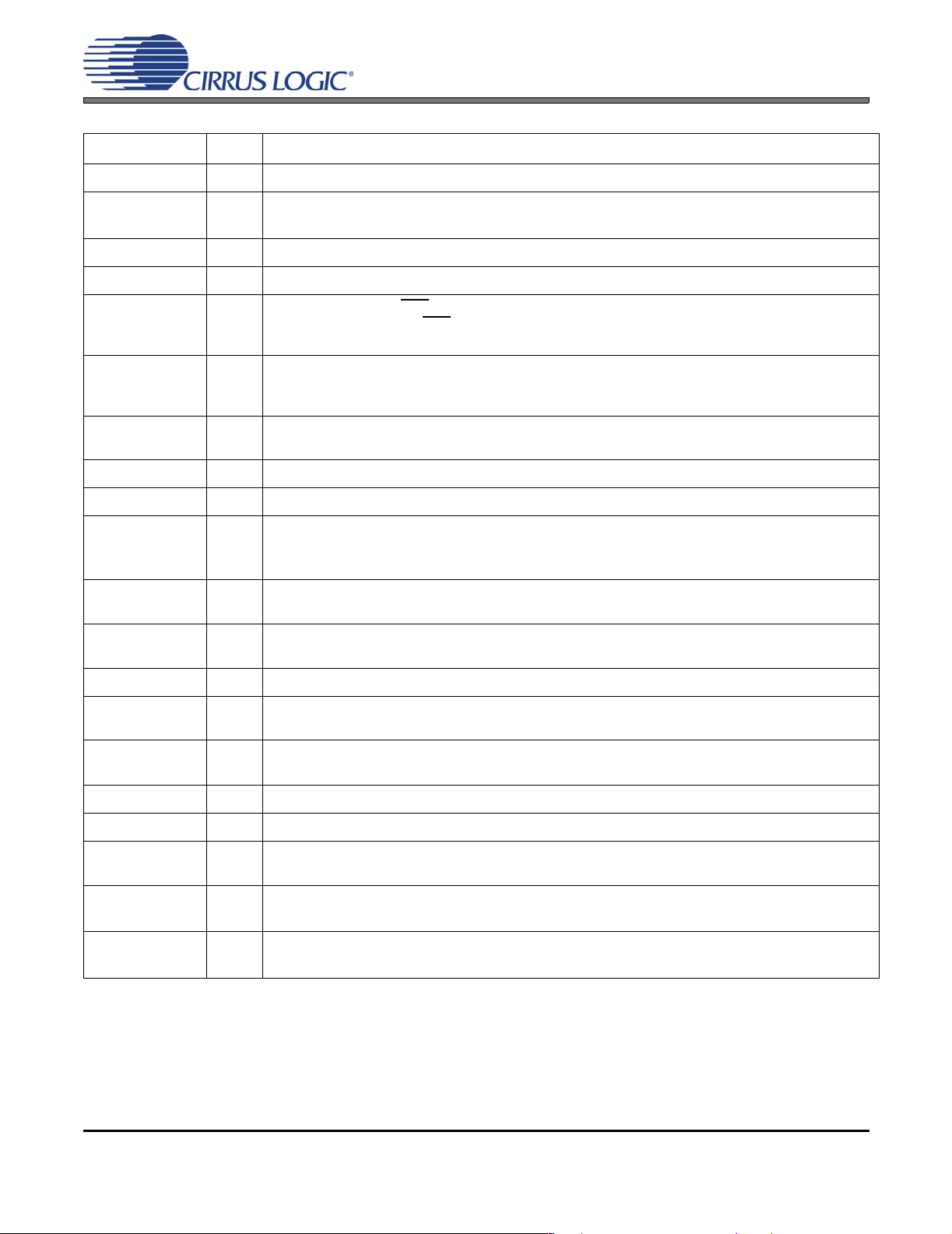

1.1 TSSOP PIN DESCRIPTIONS

CS8421

XTO SRC_UNLOCK

XTI SAIF

VD SAOF

GND VL

RST GND

BYPASS MS_SEL

ILRCK OLRCK

ISCLK OSCLK

SDIN SDOUT

MCLK_OUT TDM_IN

1

2

3

4

5

6

7

20

19

18

17

16

15

14

813

Top-Down View

9

20-pin TSSOP Package

12

10 11

6 DS641PP2

Pin Name # Pin Description

CS8421

XTO 1

XTI 2

VD 3

GND 4

RST 5

BYPASS 6

ILRCK 7

ISCLK 8

SDIN 9

MCLK_OUT 10

TDM_IN 11

Crystal Out (Output) - Crystal output for Master clock. See “Master Clock” on page 21.

Crystal/Oscillator In (Input) - Crystal or digital clock input for Master clock. See “Master Clock”

on page 21.

Digital Power (Input) - Digital core power supply. Typically +2.5 V.

Ground (Input) - Ground for I/O and core logic.

Reset (Input) - When RST is low the CS8421 enters a low power mode and all internal states are

reset. On initial power up RST must be held low until the power supply is stable and all input clocks

are stable in frequency and phase.

Sample Rate Converter Bypass (Input) - When BYP ASS is high, the sample rate converter will be

bypassed and any data input through the serial audio input port will be directly output on the serial

audio output port. When Bypass is low the sample rate converter will operate normally.

Serial Audio Input Left/Right Cl oc k (Input/Output) - Word rate clock for the audio dat a on th e

SDIN pin.

Serial Audio Bit Clock (Input/Output) - Serial bit clock for audio data on the SDIN pin.

Serial Audio Input Data Port (Input) - Audio data serial input pin.

Master Clock Output (Output) - Buffered and level shifted output for Master clock. If MCLK_OUT

is not required, this pin should be pulled high through a 47 kΩ resistor to turn the output off. See

“Master Clock” on page 21.

Serial Audio TDM Input (Input) - Time Division Multiplexing serial audio data input. Grounded

when not used. See

“Time Division Multiplexing (TDM) Mode” on page 23

SDOUT 12

OSCLK 13

OLRCK 14

MS_SEL 15

GND 16

VL 17

SAOF 18

SAIF 19

SRC_UNLOCK 20

Serial Audio Output Data Port (Output) - Audio data serial output pin. Optionally this pin may be

pulled low through a 47 kΩ resistor, but should not be pulled high.

Serial Audio Bit Clock (Input/Output) - Serial bit clock for audio data on the SDOUT pin.

Serial Audio Input Left/Right Cl oc k (Input/Output) - Word rate clock for the audio dat a on th e

SDOUT pin.

Master/Slave Select (Input) - Used to select Master or Slave for the input and output serial audio

ports at startup and reset. See

Ground (Input) - Ground for I/O and core logic.

Logic Power (Input) - Input/Output power supply. Typically +3.3 V or +5.0 V.

Serial Audio Output Format Select (Input) - Used to select the serial audio output format at star-

tup and reset. See Table 5 on page 19 for format settings.

Serial Audio Input Format Select (Input) - Used to select the serial audio input format at startup

and reset. See Table 4 on page 19 for format settings.

SRC Unlock Indicator (Output) - Indicates when the SRC is unlocked. See “SRC Locking and

Table 3 on page 19 for settings.

Varispeed” on page 20.

Table 1. TSSOP Pin Descriptions

DS641PP2 7

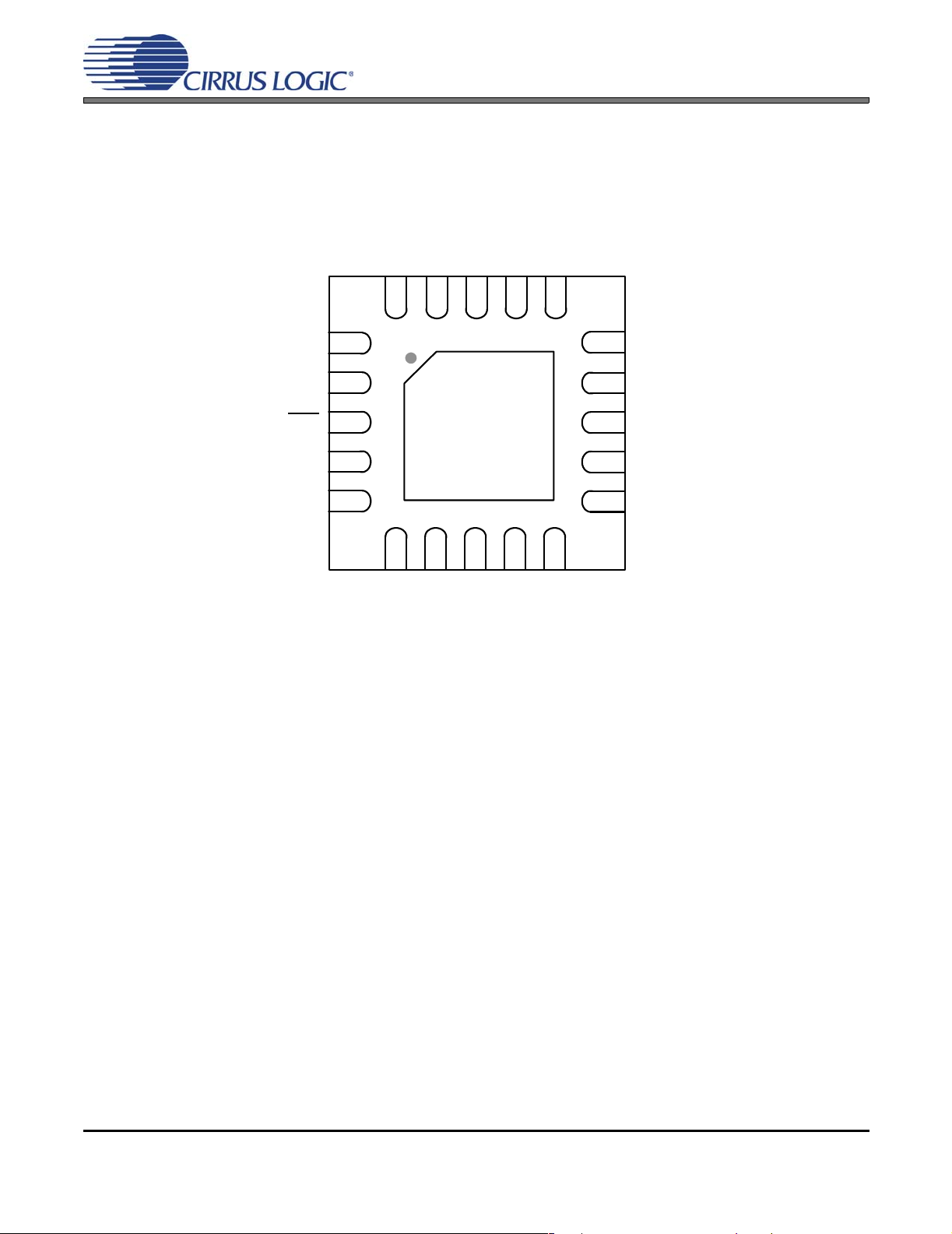

1.2 QFN PIN DESCRIPTIONS

CS8421

VD

GND

RST

BYPASS

ILRCK

XTI

XTO

181920

1

2

3

4

5

Thermal Pad

Top-Down View

20-pin QFN Package

SRC_UNLOCK

17

SAIF

SAOF

16

15

14

13

12

11

VL

GND

MS_SEL

OLRCK

OSCLK

76

8

SDIN

ISCLK

MCLK_OUT

10

9

SDOUT

TDM_IN

8 DS641PP2

Pin Name # Pin Description

CS8421

VD 1

GND 2

RST 3

BYPASS 4

ILRCK 5

ISCLK 6

SDIN 7

MCLK_OUT 8

TDM_IN 9

SDOUT 10

OSCLK 11

Digital Power (Input) - Digital core power supply. Typically +2.5 V.

Ground (Input) - Ground for I/O and core logic.

Reset (Input) - When RST is low the CS8421 enters a low power mode and all internal states are

reset. On initial power up RST must be held low until the power supply is stable and all input clocks

are stable in frequency and phase.

Sample Rate Converter Bypass (Input) - When BYPASS is high, the sample rate converter will be

bypassed and any data input through the serial audio input port will be directly output on the serial

audio output port. When Bypass is low the sample rate converter will operate normally.

Serial Audio Input Left/Right Clock (Input/Output) - Word rate clock for the audio data on the

SDIN pin.

Serial Audio Bit Clock (Input/Output) - Serial bit clock for audio data on the SDIN pin.

Serial Audio Input Data Port (Input) - Audio data serial input pin.

Master Clock Output (Output) - Buffered and level shifted output for Master clock. If MCLK_OUT

is not required, this pin should be pulled high through a 47 kΩ resistor to turn the output off. See

“Master Clock” on page 21.

Serial Audio TDM Input (Input) - Time Division Multiplexing serial audio data input. Grounded

when not used. See

Serial Audio Output Data Port (Output) - Audio data serial output pin. Optionally this pin may be

pulled low through a 47 kΩ resistor, but should not be pulled high.

Serial Audio Bit Clock (Input/Output) - Serial bit clock for audio data on the SDOUT pin.

“Time Division Multiplexing (TDM) Mode” on page 23

OLRCK 12

MS_SEL 13

GND 14

VL 15

SAOF 16

SAIF 17

SRC_UNLOCK 18

XTO 19

XTI 20

THERMAL PAD -

Serial Audio Input Left/Right Clock (Input/Output) - Word rate clock for the audio data on the

SDOUT pin.

Master/Slave Select (Input) - Used to select Master or Slave for the input and output serial audio

ports at startup and reset. See

Ground (Input) - Ground for I/O and core logic.

Logic Power (Input) - Input/Output power supply. Typically +3.3 V or +5.0 V.

Serial Audio Output Format Select (Input) - Used to select the serial audio output format at star-

tup and reset. See

Serial Audio Input Format Select (Input) - Used to select the serial audio input format at startup

and reset. See Table 4 on page 19 for format settings.

SRC Unlock Indicator (Output) - Indicates when the SRC is unlocked. See “SRC Locking and

Table 5 on page 19 for format settings.

Table 3 on page 19 for settings.

Varispeed” on page 20.

Crystal Out (Output) - Crystal output for Master clock. See “Master Clock” on page 21.

Crystal/Oscillator In (Input) - Crystal or digital clock input for Master clock. See “Master Clock”

on page 21.

Thermal Pad - Thermal relief pad for optimized heat dissipation.

Table 2. QFN Pin Descriptions

DS641PP2 9

CS8421

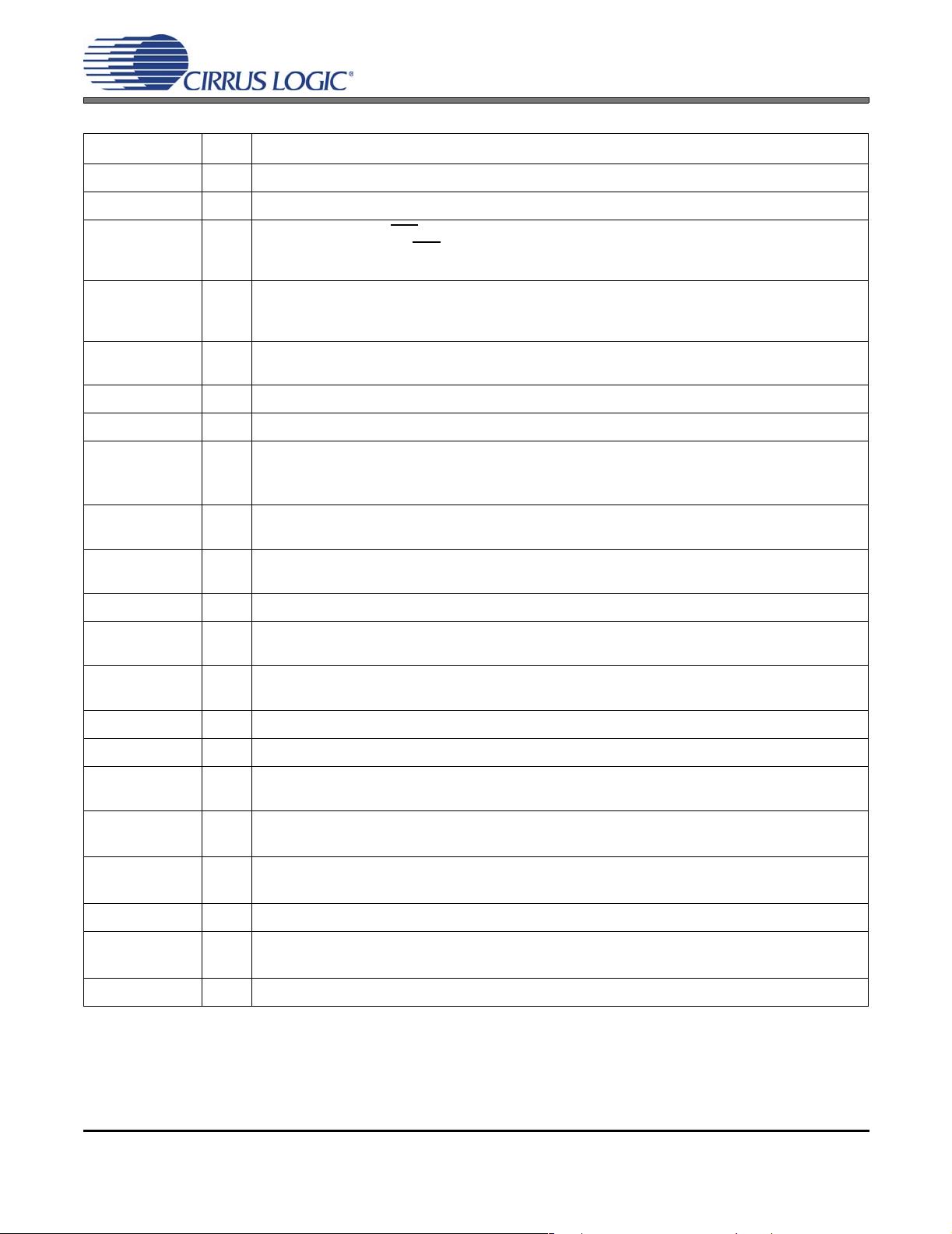

2. CHARACTERISTICS AND SPECIFICATIONS

(All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical

performance characteristics and spe cif icat ion s ar e de riv e d from measurements taken at nominal supply voltages

and T

= 25°C.)

A

SPECIFIED OPERATING CONDITIONS

(GND = 0 V, all voltages with respect to 0 V)

Parameter Symbol Min Nominal Max Units

Power Supply Voltage

Ambient Operating Temperature: ‘-CZ’

‘-CNZ’

‘-DZ’

VD

VL

T

2.38

3.14

A

-10

-10

-40

2.5

3.3 or 5.0

-

-

-

2.62

5.25

+70

+70

+85

V

V

°C

°C

°C

ABSOLUTE MAXIMUM RATINGS

(GND = 0 V; all voltages with respect to 0 V. Operation beyond these limits may result in permanent damage to the

device. Normal operation is not guaran te e d at th es e extremes.)

Parameter Symbol Min Max Units

Power Supply Voltage

Input Current, Any Pin Except Supplies (Note 1)

Input Voltage

Ambient Operating Temperature (power applied)

Storage Temperature

VD

VL

I

V

T

T

in

stg

-0.3

-0.3

3.5

6.0

V

V

-±10mA

in

A

-0.3 VL+0.4 V

-55 +125 °C

-65 +150 °C

Notes:

1. Transient currents of up to 100 mA will not cause SCR latch-up.

2. Numbers separated by a colon indicate input and ou tput sample rates. For example, 48 kHz:96 kHz indicates that Fsi = 48 khz and Fso = 96 kHz.

10 DS641PP2

CS8421

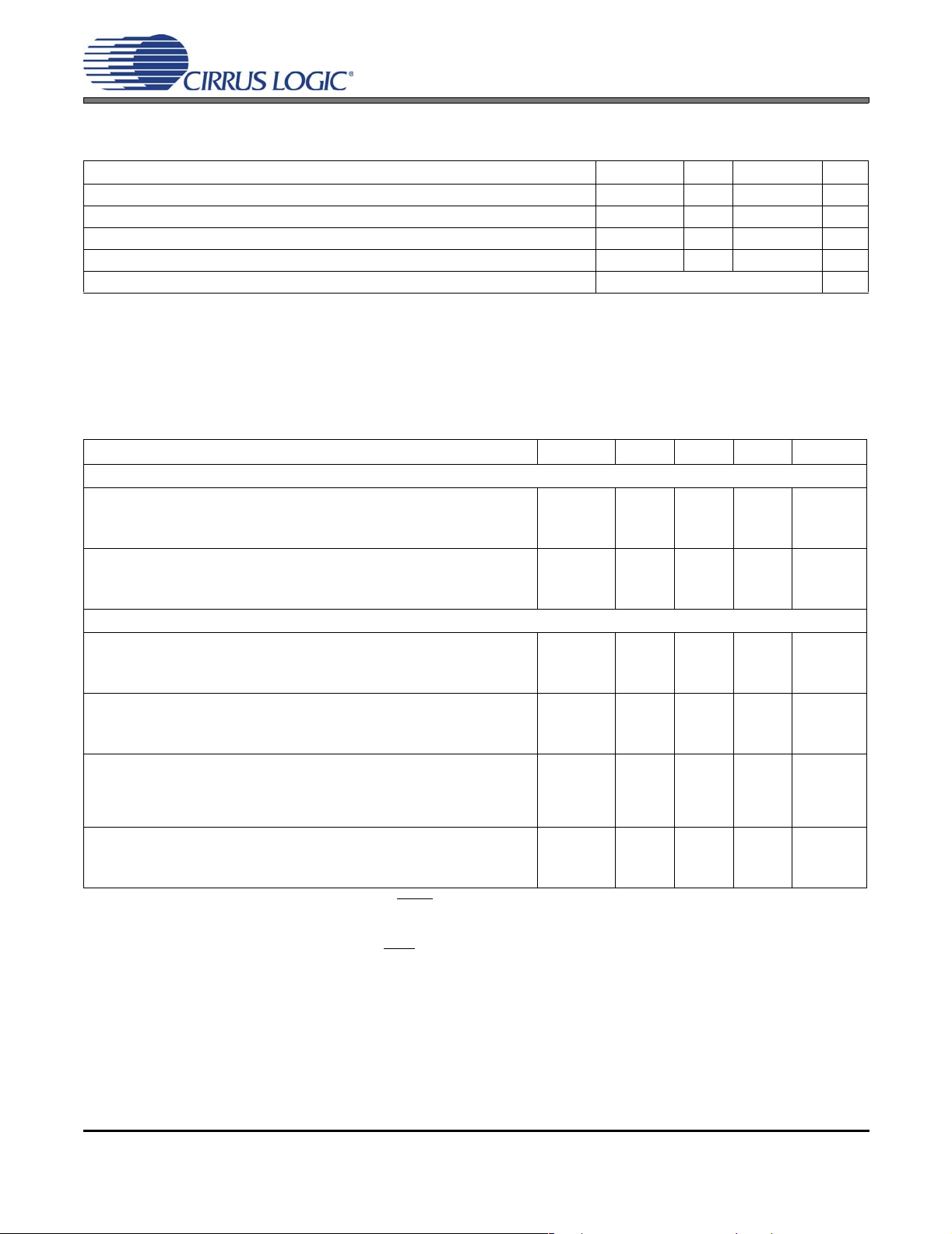

PERFORMANCE SPECIFICATIONS

(XTI/XTO = 27 MHz; Input signal = 1.000 kHz, 0 dBFS, Measurement Bandwidth = 20 to Fso/2 Hz, and Word

Width = 32-Bits, unless otherwise stated.)

Parameter Min Typ Max Units

Resolution

Sample Rate with XTI = 27.000 MHz Slave

Master

Sample Rate with other XTI clocks Slave

Master

Sample Rate with ring oscillator (XTI to GND or VL, XTO floating)

Sample Rate Ratio - Upsampling

Sample Rate Ratio - Downsampling

Interchannel Gain Mismatch

Interchannel Phase Deviation

Peak Idle Channel Noise Component (32-bit operation)

Dynamic Range (20 Hz to Fso/2, 1 kHz, -60 dBFS Input)

44.1 kHz:48 kHz A-Weighted

Unweighted

44.1 kHz:192 kHz A-Weighted

Unweighted

48 kHz:44.1 kHz A-Weighted

Unweighted

48 kHz:96 kHz A-Weighted

Unweighted

96 kHz:48 kHz A-Weighted

Unweighted

192kHz:32kHz A-Weighted

Unweighted

Total Harmonic Distortion + Noise (20 Hz to Fso/2, 1 kHz, 0 dBFS Input)

32 kHz:48 kHz

44.1 kHz:48 kHz

44.1 kHz:192 kHz

48 kHz:44.1 kHz

48 kHz:96 kHz

96 kHz:48 kHz

192kHz:32kHz

16 - 32 bits

7.2

53

XTI/3750

XTI/512

-

-

-

-

207

211

XTI/130

XTI/128

kHz

kHz

kHz

kHz

12 - 96 kHz

--1:8

- - 7.5:1

-0.0-dB

- 0.0 - Degrees

- - -192 dBFS

-

-

-

-

-

-

-

-

-

-

-

-

180

177

175

172

180

177

179

176

176

173

175

172

-

-

-

-

-

-

-

-

-

-

-

-

- -161 - dB

- -171 - dB

- -130 - dB

- -160 - dB

- -148 - dB

- -168 - dB

- -173 - dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

DS641PP2 11

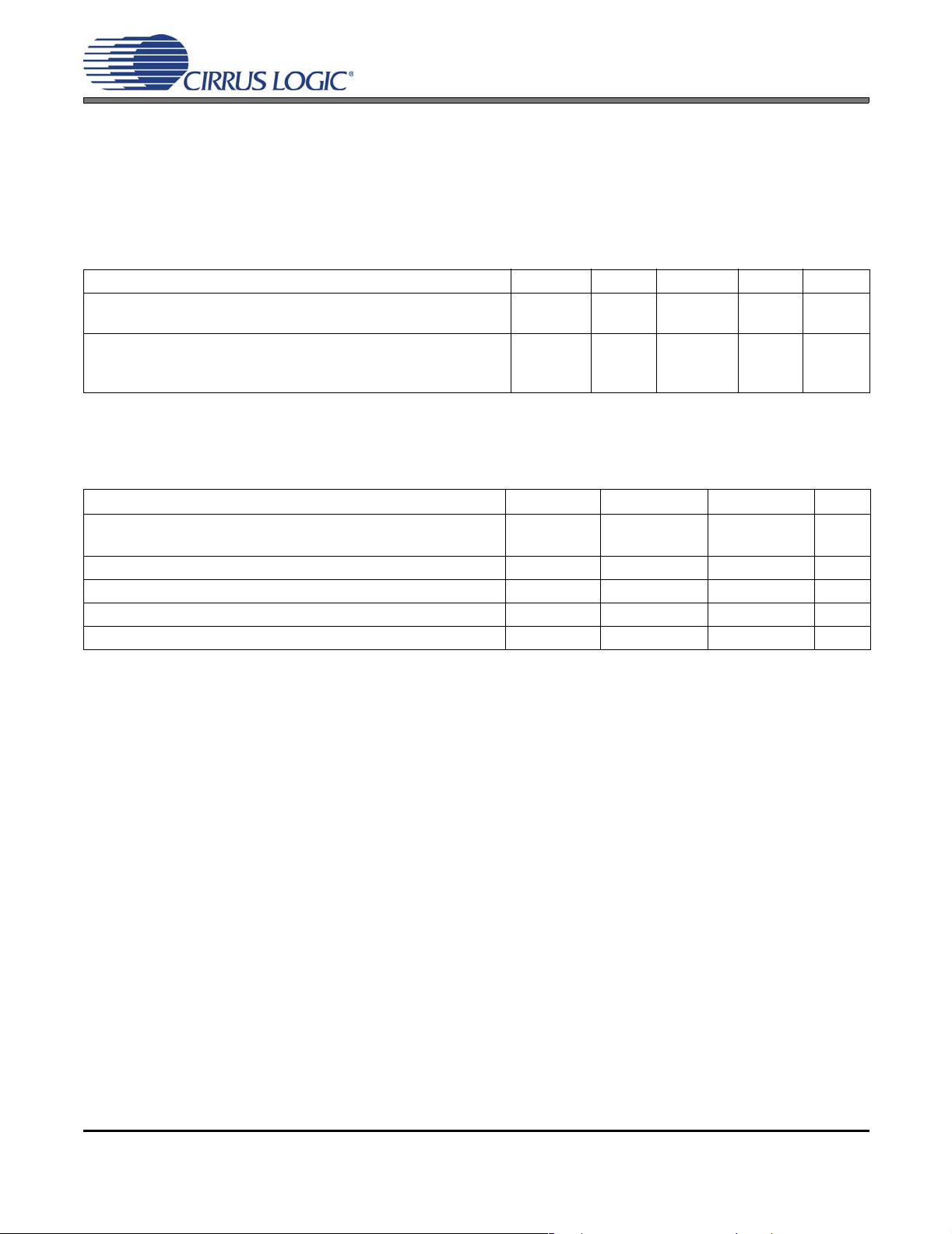

DIGITAL FILTER CHARACTERISTICS

Parameter Min Typ Max Units

Passband (Upsampling or Downsampling)

Passband Ripple

Stopband

Stopband Attenuation

Group Delay

3. The equation for the group delay through the sample rate converter is (56.581 / Fsi) + (55.658 / Fso).

For example, if the input sample rate is 192 kHz and the outp ut samp le rate is 96 kHz, the g roup dela y

through the sample rate converter is (56.581/192,000) + (55.658/96,000) =.875 milliseconds.

DC ELECTRICAL CHARACTERISTICS

(GND = 0 V; all voltages with respect to 0 V.)

Parameters Symbol Min Typ Max Units

Power-down Mode (Note 4)

Supply Current in power down VD

(Oscillator attached to XTI-XTO) VL = 3.3 V

VL = 5.0 V

Supply Current in power down VD

(Crystal attached to XTI-XTO) VL = 3.3 V

VL = 5.0 V

Normal Operation (Note 5)

Supply Current at 48 kHz Fsi and Fso VD

(Oscillator attached to XTI-XTO) VL = 3.3 V

VL = 5.0 V

Supply Current at 192 kHz Fsi and Fso VD

(Oscillator attached to XTI-XTO) VL = 3.3 V

VL = 5.0 V

Supply Current at 48 kHz Fsi and Fso VD

(Crystal attached to XTI-XTO) VL = 3.3 V

VL = 5.0 V

Supply Current at 192 kHz Fsi and Fso VD

(Crystal attached to XTI-XTO) VL = 3.3 V

VL = 5.0 V

CS8421

- - 0.4535*Fso Hz

- - ±0.007 dB

0.5465*Fso - - Hz

125 - - dB

(Note 3) ms

50

100

200

100

1.5

4

24

2.5

4

80

8

13

24

3

7

80

4

6.5

µA

µA

µA

µA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

4. Power Down Mode is defined as RST

= LOW with all clocks and data lines held static, except when a

crystal is attached across XTI-XTO, in which case the crystal will begin oscillating.

5. Normal operation is defined as RST

= HI.

12 DS641PP2

DIGITAL INPUT CHARACTERISTICS

Parameters Symbol Min Typ Max Units

Input Leakage Current

Input Capacitance

Input Hysteresis

DIGITAL INTERFACE SPECIFICATIONS

(GND = 0 V; all voltages with respect to 0 V.)

Parameters Symbol Min Max Units

High-Level Output Voltage, except MCLK_OUT and SDOUT (IOH=-4 mA)

Low-Level Output Voltage, except MCLK_OUT and SDOUT (IOL=4 mA)

High-Level Output Voltage, MCLK_OUT (IOH=-6 mA)

Low-Level Output Voltage, MCLK_OUT (IOL=6 mA)

High-Level Output Voltage, SDOUT (IOH=-8 mA)

Low-Level Output Voltage, SDOUT (IOL=8 mA)

High-Level Input Voltage

Low-Level Input Voltage

CS8421

I

in

I

in

V

OH

V

OL

V

OH

V

OL

V

OH

V

OL

V

IH

V

IL

--±10µA

-8- pF

- 250 - mV

0.77xVL - V

-.6V

0.77xVL - V

-.6V

0.77xVL - V

-.6V

0.58xVL VL+0.3 V

-0.3 0.8 V

SWITCHING SPECIFICATIONS

(Inputs: Logic 0 = 0 V, Logic 1 = VL; CL = 20 pF)

Parameters Symbol Min Max Units

RST pin Low Pulse Width

XTI Frequency (Note 7)

XTI Pulse Width High/Low

MCLK_OUT Duty Cycle

Slave Mode

I/OSCLK Frequency

OLRCK High Time

I/OSCLK High Time

I/OSCLK Low Time

I/OLRCK Edge to I/OSCLK Rising

OLRCK Rising Edge to OSCLK Rising Edge (TDM)

I/OSCLK Rising Edge to I/OLRCK Edge

OSCLK Rising Edge to OLRCK Falling Edge (TDM)

OSCLK Falling Edge/OLRCK Edge to SDOUT Output Valid

SDIN/TDM_IN Setup Time Before I/OSCLK Rising Edge

SDIN/TDM_IN Hold Time After I/OSCLK Rising Edge

(Note 6)

Crystal

Digital Clock Source

(Note 8)

t

lrckh

t

sckh

t

sckl

t

lcks

t

fss

t

lckd

t

fsh

t

dpd

t

t

ds

dh

1-ms

16.384

1.024

27.000

27.000

MHz

MHz

14.8 - ns

45 55 %

- 24.576 MHz

326 - ns

9-ns

9-ns

6-ns

5-ns

5-ns

5-ns

-18ns

3-ns

5-ns

DS641PP2 13

Parameters Symbol Min Max Units

Master Mode (Note 9)

I/OSCLK Frequency (non-TDM)

OSCLK Frequency (TDM)

I/OLRCK Duty Cycle

I/OSCLK Duty Cycle

I/OSCLK Falling Edge to I/OLRCK Edge

OSCLK Falling Edge to OLRCK Edge (TDM)

OSCLK Falling Edge to SDOUT Output Valid

SDIN/TDM_IN Setup Time Before I/OSCLK Rising Edge

SDIN/TDM_IN Hold Time After I/OSCLK Rising Edge

I/OLRCK

(input)

I/OSCLK

(input)

SDIN

(input)

SDOUT

(output)

t

lckd

t

lcks

t

dpd

t

sckh

t

t

ds

dh

MSB

MSB

t

sckl

MSB-1

MSB-1

OLRCK

(input)

OSCLK

(input)

TDM_IN

(input)

SDOUT

(output)

CS8421

64*Fsi/o MHz

256*Fso MHz

45 55 %

45 55 %

t

lcks

t

fss

t

dpd

t

ds

t

dh

t

lrckh

t

fss

t

fsh

-5ns

-5ns

-7ns

3-ns

5-ns

t

sckh

t

t

ds

dh

MSB

t

dpd

MSB

t

sckl

MSB-1

MSB-1

I/OLRCK

(output)

I/OSCLK

(output)

SDIN

(input)

SDOUT

(output)

Figure 1. Non-TDM Slave Mode Timing Figure 2. TDM Slave Mode Timing

6. After powering up the CS8421, RST should be held low until the power supplies and clocks are se ttled.

7. The maximum possible sample rate is XTI/128.

8. OLRCK must remain high for at least 8 OSCLK periods in TDM mode.

9. Only the input or the output serial port can be set as master at a given time.

t

lcks

t

t

ds

dh

MSB

t

dpd

MSB

MSB-1

MSB-1

Figure 3. Non-TDM Master Mode Timing Figure 4. TDM Master Mode Timing

OLRCK

(output)

OSCLK

(output)

TDM_IN

(input)

SDOUT

(output)

t

fss

t

t

ds

dh

MSB

t

dpd

MSB

MSB-1

MSB-1

14 DS641PP2

3. TYPICAL CONNECTION DIAGRAMS

+2.5 V +3.3 V or +5.0 V

0.1 µF0.1 µF

VD VL

CS8421

1 kΩ

*

Hardware Control

Settings

Serial

Audio

Source

**

ILRCK

ISCLK

SDIN

TDM_IN

MS_SEL

SAIF

SAOF

SRC_UNLOCK

BYPASS

RST

CS8421

GND

GND

OLRCK

OSCLK

SDOUT

XTI

Serial

Audio

Input

Device

Figure 5. Typical Connection Diagram, No External Master Clock

* When no external master clock is supplied to the part, both input and output must be set to slave mode for the part to operate

properly. This is done by connecting the MS_SEL pin to ground through a resistance of 0 Ω to 1 kΩ + 1% as stated in

Table 3, “Serial Audio Port Master/Slave and Clock Ratio Select Start-Up Options (MS_SEL),” on page 19.

** The connection (VL or GND) and value of these two resistors determines the mode of operation for the input and output

serial ports as described in

DS641PP2 15

Table 4 and Table 5 on page 19.

+2.5 V +3.3 V or +5.0 V

0.1 µF0.1 µF

VD VL

CS8421

Serial

Audio

Source

* **

Hardware Control

Settings

ILRCK

ISCLK

SDIN

TDM_IN

MS_SEL

SAIF

SAOF

SRC_UNLOCK

BYPASS

RST

CS8421

GND

MCLK_OUT

GND

OLRCK

OSCLK

SDOUT

XTI

XTO

47 kΩ

Serial

Audio

Input

Device

Crystal /Clock

Source

To external

hardware

Figure 6. Typical Connection Diagram, Master and Slave Modes

* The connection (VL or GND) and value of these three resistors determines the mode of operation for the input and output serial

ports as described in

Table 3 Serial Audio Port Master/Slave and Clock Ratio Select Start-Up Options (MS_SEL),

Table 4 Serial Audio Input Port Start-Up Options (SAIF), and Table 5 Serial Audio Output Port Start-Up Options

(SAOF)

** MCLK_OUT pin should be pulled high through a 47 kΩ resistor if an MCLK output is not needed.

, all on page 19.

16 DS641PP2

CS8421

4. GENERAL DESCRIPTION

The CS8421 is a 32-bit, high performance, monolithic CMOS stereo asynchronous sample rate converter.

The digital audio data is input and output through configurable 3-wire serial ports. The digital audio input/output ports

offer Left Justified, Right Justified, and I²S serial a udio f orm ats. The CS 8421 also supp orts a T DM m ode which al lows multiple channels of digital audio data on on e se rial line . A b ypass mo de allows the data to be p asse d dire ctly

to the output port without sample rate conversion.

The CS8421 does not require a control port interface, helping to speed design time by not requiring the user to develop software to configure the part. Pins that are sensed after reset allow the part to be configured. See “Reset,

Power Down, and Start-Up” on page 34.

Target applications include digital recording systems (DVD-R/RW, CD-R/RW, PVR, DAT, MD, and VTR), digital mixing consoles, high quality D/A, effects processors and computer audio systems.

Figure 5 and 6 show the supply and external connections to the CS8421.

5. THREE-WIRE SERIAL INPUT/OUTPUT AUDIO PORT

A 3-wire serial audio input/output port is provided. The interface format should be chosen to suit the attached device

through the MS_SEL, SAIF, and SAOF pins. Tables 3, 4, and 5 show the pin functions and their correspon ding settings. The following parameters are adjustable:

• Master or slave.

• Master clock (MCLK) frequencies of 128*Fsi/o, 256*Fsi/o, 384*Fsi/o, and 512*Fsi/o (Master mode).

• Audio data resolution of 16, 20, 24, or 32-bits.

• Left or right justification of the data relative to left/right clock (LRCK) as well as I²S.

Figures 7, 8, and 9 show the input/output formats available.

In master mode, the left/right clock and the serial bit clock are outputs, derived from the XTI input pin master clock.

In slave mode, the left/right clock and the serial bit clock are inputs and may be asynchronous to the XTI master

clock. The left/right clock should be continuous, but the duty cycle can be less than 50% if enough serial clocks are

present in each phase to clock all of the data bits.

ISCLK is always set to 64*Fsi when the input is set to master. In normal operation, OSCLK is set to 64*Fso. In TDM

slave mode, OSCLK must operate at N*64*Fso, where N is the number of CS8421’s connected together. In TDM

master mode, OSCLK is set to 256*Fso

For more information about serial audio formats, refer to the Cirrus Logic applications note AN282, “The 2-Channel

Serial Audio Interface: A Tutorial”, available at www.cirrus.com

.

DS641PP2 17

CS8421

I/OLRCK

I/OSCLK

SDIN

SDOUT

I/OLRCK

I/OSCLK

SDIN

SDOUT

I/OLRCK

I/OSCLK

SDIN

SDOUT

Channel A

MSB LSB

Figure 7. Serial Audio Interface Format - I²S

Channel A Channel B

MSB LSB

MSB

Figure 8. Serial Audio Interface Format - Left-Justified

Channel A

MSB

MSB Extended MSB Extended

MSB

LSB

LSB

Figure 9. Serial Audio Interface Format - Right-Justified

MSB

Channel B

LSB

LSB

Channel B

MSB

MSB LSB

MSB

MSB

LSB

18 DS641PP2

CS8421

6. MODE SELECTION

The CS8421 uses the resistors attached to the MS_SEL, SAIF, and SAOF pins to determine the mod es of operation.

After reset, the resistor value and condition (VL or GND) are sensed. This operation will take approximately 4 µs to

complete. The SRC_UNLOCK pin will remain high and the SDOUT pin will be muted until the mode detection sequence has completed. After this, if all clocks are stable, SRC_UNLOCK will be brought low when audio output is

valid and normal operation will occur. Tables3, 4, and 5 show the pin functions and their corresponding settings. If

the 1.0 kΩ option is selected for MS_SEL, SAIF, or SAOF, the resistor connected to that pin may be replaced by a

direct connection to VL or GND as appropriate.

The resistor attached to each mode selection pin should be placed physically close to the CS8421. The end of the

resistor not connected to the mode selection pins should be connected as close as possible to VL and GND to minimize noise. Tables 3, 4, and 5 show the pin functions and their corresponding settings.

MS_SEL pin Input M/S Output M/S

1.0 kΩ ± 1% to GND Slave Slave

1.96 kΩ ± 1% to GND Slave

4.02 kΩ ± 1% to GND Slave

8.06 kΩ ± 1% to GND Slave

16.2 kΩ ± 1% to GND Slave

1.0 kΩ ±1% to VL

1.96 kΩ ± 1% to VL

4.02 kΩ ± 1% to VL

8.06 kΩ ± 1% to VL

Table 3. Serial Audio Port Master/Slave and Clock Ratio Select Start-Up Options (MS_SEL)

Master (

Master (256 x Fsi)

Master (

Master (

128 x Fsi)

384 x Fsi)

512 x Fsi)

Master (

Master (

Master (384 x Fso)

Master (

128 x Fso)

256 x Fso)

512 x Fso)

Slave

Slave

Slave

Slave

SAIF pin Input Port Configuration

1.0 kΩ ± 1% to GND I²S up to 32-bit data

1.96 kΩ ± 1% to GND Left Justified up to 32-bit data

4.02 kΩ ± 1% to GND Right Justified 16-bit data

1.0 kΩ ± 1% to VL Right Justified 20-bit data

1.96 kΩ ± 1% to VL Right Justified 24-bit data

4.02 kΩ ± 1% to VL Right Justified 32-bit data

Table 4. Serial Audio Input Port Start-Up Options (SAIF)

SAOF pin Output Port Configuration

1.0 kΩ ± 1% to GND I²S 16-bit data

1.96 kΩ ± 1% to GND I²S 20-bit data

4.02 kΩ ± 1% to GND I²S 24-bit data

8.06 kΩ ± 1% to GND I²S 32-bit data

16.2 kΩ ± 1% to GND Left Justified 16-bit data

32.4 kΩ ± 1% to GND Left Justified 20-bit data

63.4 kΩ ± 1% to GND Left Justified 24-bit data

127.0 kΩ ± 1% to GND Left Justified 32-bit data

1.0 kΩ ± 1% to VL Right Justified 16-bit data

1.96 kΩ ± 1% to VL Right Justified 20-bit data

4.02 kΩ ± 1% to VL Right Justified 24-bit data

8.06 kΩ ± 1% to VL Right Justified 32-bit data

16.2 kΩ ± 1% to VL TDM Mode 16-bit data

32.4 kΩ ± 1% to VL TDM Mode 20-bit data

63.4 kΩ ± 1% to VL TDM Mode 24-bit data

127.0 kΩ ± 1% to VL TDM Mode 32-bit data

Ta bl e 5 . Seria l Au di o Output Port Start-Up Options (SAOF)

DS641PP2 19

CS8421

7. SAMPLE RATE CONVERTER (SRC)

Multirate digital signal processing techniques are used to conceptually upsample the incoming data to a very high

rate and then downsample to the outgo ing rate. The internal data path is 32-bits wide even if a lower bit depth is

selected at the output. The filtering is designed so that a full input audio bandwidth of 20 kHz is preserved if the input

sample and output sample rates are greater than or equal to 44.1 kHz. When the output sample rate becomes less

than the input sample rate, the input is automatically band limited to avoid aliasing products in the output. Careful

design ensures minimum ripple and distortion products are added to the incoming signal. The SRC also determines

the ratio between the incoming and outgoing sa mple rates, and sets the filter corn er frequenci es appropriately. An y

jitter in the incoming signal has little impact on the dynamic performance of the rate converter and has no influence

on the output clock.

7.1 Data Resolution and Dither

When using the serial audio input port in left justified and I²S modes all input data is treated as 32-bits wide.

Any truncation that has been done prior to the CS8421 to less than 32-bits should have been done using

an appropriate dithering process. If the serial audio input port is in right justified mode, the input data will be

truncated to the bit depth set by SAIF pin setting. If the SAIF bit depth is set to 16, 20, or 24-bits, and the

input data is 32-bits wide, then truncation distortion will occur. Similarly, in any serial audio input port mode,

if an inadequate number of bit clocks are entered (i.e. 16 clocks instead of 20 clocks), then the input wo rds

will be truncated, causing truncation distortion at low levels. In summary, there is no dithering mechanism

on the input side of the CS8421, and care must be taken to ensure that no truncation occurs.

Dithering is used internally where appropriate inside the SRC block.

The output side of the SRC can be set to 16, 20, 24, or 32-bits. Dithering is applied and is automatically

scaled to the selected output word length. This dither is not correlated betw ee n lef t and ri gh t ch an ne ls.

7.2 SRC Locking and Varispeed

The SRC calculates the ratio between the input sample rate and the output sample rate, and uses this information to set up various parameters inside the SRC block. The SRC takes some time to make this calculation, approximately 4200/Fso (8.75 ms at Fso of 48 kHz).

If Fsi is changing, as in a varispeed application, the SRC will track the incoming sample rate. During this

tracking mode, the SRC will still rate convert the audio data, but at increased distortion levels. Once the incoming sample rate is stable the SRC will return to normal levels of audio quality. The data buffer in the SRC

can overflow if the input sample rate changes at greater than 10%/sec.

The SRC_UNLOCK pin is used to indicate when the SRC is not locked. When RST

is a change in Fsi or Fso, SRC_UNLOCK will be set high. The SRC_UNLOCK pin will continue to be high

until the SRC has reacquired lock and settled, at which point it will transition low. When the SRC_UNLOCK

pin is set low, SDOUT is outputting valid audio data. This can be used to signal a DAC to unmute its output.

7.3 Bypass Mode

When the BYPASS pin is set high, the input data bypasses the sample rate converter and is sent directly to

the serial audio output port. No dithering is performed on the output data. This mode is ideal for passing

non-audio data through without a sample rate conversion. ILRCK and OLRCK should be the same sample

rate and synchronous in this mode.

is asserted, or if there

20 DS641PP2

7.4 Muting

The SDOUT pin is set to all zero output (full mute) immediately after the RST pin is set high. When the output

from the SRC becomes valid, though the SRC may not have reached full performance, SDOUT is unmuted

over a period of approximately 4096 OLRCK cycles (soft unmuted). When the outp ut becomes invalid, depending on the condition, SDOUT is either immediately set to all zero output (hard muted) or SDOUT is muted over a period of approximately 4096 OLRCK cycles until it reaches full mute (soft muted). The SRC will

soft mute SDOUT if there is an illegal ratio between ILRCK and the XTI master clock. Conditions that will

cause the SRC to hard mute SDOUT include removing OLRCK, the RST

between OLRCK and the XTI master clock. After all invalid states have been cleared, the SRC will soft unmute SDOUT.

pin being set low, or illegal ratios

7.5 Group Delay and Phase Matching Between Multiple CS8421 Parts

The equation for the group delay through the sample rate converter is shown in “Digital Filter Characteris-

tics” on page 12. This phase delay is equal across multiple parts. Therefore, when multiple parts operate at

the same Fsi and Fso and use a common XTI/XTO clock, their output data is phase matched.

7.6 Master Clock

The CS8421 uses the clock signal supplied through XTI as its master clock (MCLK). MCLK can be supplied

from a digital clock source, a crystal oscillator, or a fundamental mode crystal. Figure 10 shows the typical

connection diagram for using a fundamental mode crystal. Please refer to the crystal manufacturer’s specifications for the external capacitor recommendations. If XTO is not used, such as with a digital clock source

or crystal oscillator, XTO should be left unconnected or pulled low through a 47 kΩ resistor to GND.

CS8421

If either serial audio port is set as master, MCLK will be used to supply the sub-clocks to the master SCLK

and LRCK. In this case MCLK will be synchronous to the master serial audio port. If both serial audio ports

are set as slave, MCLK can be asynchronous to either or both ports. If the user needs to change the clock

source to XTI while the CS8421 is still powered on and running, a RESET must be issued once the XTI clock

source is present and valid to ensure proper operation.

When both serial ports are configured as slave and operating at sample rates less than 96 kHz, the CS8421

has the ability to operate without a master clock input through XT I. This benefits the design by not requiring

extra external clock components (lowering production cost) and not requiring a master clock to be routed to

the CS8421, resulting in lowered noise contribution in the system. In this mode, an inte rnal oscillator provides the clock to run all of the internal logic. To enable the internal oscillator simply tie XTI to GND or VL.

In this mode, XTO should be left unconnected.

The CS8421 can also provide a buffered MCLK output through the MCLK_OUT pin. This pin can be used

to supply MCLK to other system components that operate synchronously to MCLK. If MCLK_OUT is not

needed, the output of the pin can be disabled by pulling the pin high through a 47 kΩ resistor to VL.

MCLK_OUT is also disabled when using the internal oscillator mode. The MCLK_OUT pin will be set low

when disabled by using the internal oscillator mode.

DS641PP2 21

7.6.1 Clocking

In order to ensure proper operation of the CS8421, the clock or crystal attached to XTI must simultaneously

satisfy the requirements of LRCK for both the input and output as follows:

• If the input is set to master, Fsi ≤ XTI/128 and Fso ≤ XTI/130.

• If the output is set to master, Fso ≤ XTI/128 and Fsi ≤ XTI/130.

• If both input and output are set to slave, XTI ≥ 130*[maximum(Fsi,Fso)], XTI/Fsi < 3750, and XTI/Fso <

3750.

CS8421

XTI XTO

R

CC

Figure 10. Typical Connection Diagram for Crystal Circuit

22 DS641PP2

CS8421

8. TIME DIVISION MULTIPLEXING (TDM) MODE

TDM mode allows several CS8421 to be serially connected together allowing their corresponding SDOUT data to

be multiplexed onto one line for input into a DSP or other TDM capable multichann el device.

The CS8421 can operate in two TDM modes. The first mode consists of all of the CS8421’s output ports se t to slave

as shown in Figure 13. The second mode consists of one CS8421 output port set to master and the remaining

CS8421’s output ports set to slave as shown in Figure 14.

The TDM_IN pin is used to input the data while the SDOUT pin is used to output the data. The first CS 8421 in t he

chain should have its TDM_IN set to GND. Data is transmitted from SDOUT most significant bit first on the first

OSCLK falling edge after an OLRCK transition and is valid on the rising edge of OSCLK.

In TDM slave mode, the number of channels that can by multiplexed to one serial data line depends on the output

sampling rate. For slave mode, OSCLK must operate at N*64*Fso, where N is the number of CS8421’s connected

together. The maximum allowable OSCLK frequency is 24.576 MHz, so for Fso = 48 kH z, N = 8 (16 channels of

serial audio data).

In TDM master mode, OSCLK operates at 256*Fso, which is equivalent to N = 4, so a maximum of 8 channels of

digital audio can be multiplexed together. Note that fo r TDM master mode, MCLK must be at least 256*Fso, where

Fso ≤ 96 kHz. OLRCK identifies the start of a new frame. Each time slot is 32-bits wide, with the valid data sample

left justified within the time slot. Valid data lengths are 16, 20, 24 or 32-bits. Figures 11 and 12 show the interface

format for master and slave TDM modes with a 32-bit word-length.

OLRCK

OSCLK

SDOUT/

TDM_IN

OLRCK

OSCLK

SDOUT/

TDM_IN

LSBMSB LSBMSB LSBMSB LSBMSB LSBMSB LSBMSB

SDOUT 3 (Left) SDOUT 3 (Right)

32 clks 32 clks 32 clks 32 clks 32 clks 32 clks

SDOUT 2 (Left)

SDOUT 2 (Right) SDOUT 1 (Left) SDOUT 1 (Right) SDOUT 0 (Left) SDOUT 0 (Right)

Figure 11. TDM Slave Mode Timing Diagram

256 OSCLKs

LSBMSB LSBMSB LSBMSB LSBMSB LSBMSB LSBMSB

SDOUT 3 (Left) SDOUT 3 (Right)

32 clks 32 clks 32 clks 32 clks 32 cl ks 32 clks

SDOUT 2 (Left)

SDOUT 2 (Right) SDOUT 1 (Left) SDOUT 1 (Right) SDOUT 0 (Left) SDOUT 0 (Right)

Figure 12. TDM Master Mode Timing Diagram

LSBMSB LSBMSB

32 clks 32 clks

LSBMSB LSBMSB

32 clks 32 clks

DS641PP2 23

CS8421

Output

Clock

Source

OLRCK OSCLK SDOUT

LRCK

SCLK

PCM Source 0

CS8421

ILRCK

ISCLK

SDIN

Phase

Master/

Slave

0

OLRCK

OSCLK

SDOUTTDM_IN

OLRCK OSCLK SDOUT

PCM Source 1

CS8421

ILRCK

ISCLK

SDIN

1

OLRCK

OSCLK

SDOUTTDM_IN

Slave

OLRCK OSCLK SDOUT

PCM Source n

CS8421

ILRCK

ISCLK

SDIN

Slave

Figure 13. TDM Mode Configuration (All CS8421 Outputs are Slave)

N

OLRCK

OSCLK

SDOUTTDM_IN

DSP

LRCK

SCLK

SDIN

Slave

OLRCK OSCLK SDOUT

PCM Source 0

Figure 14. TDM Mode Configuration (First CS8421 Output is Master, All Others are Slave)

CS8421

ILRCK

ISCLK

SDIN

Clock

and

Phase

Master

0

OLRCK

OSCLK

SDOUTTDM_IN

OLRCK OSCLK SDOUT

PCM Source 1

CS8421

ILRCK

ISCLK

SDIN

Slave

1

OLRCK

OSCLK

SDOUTTDM_IN

OLRCK OSCLK SDOUT

PCM Source n

CS8421

ILRCK

ISCLK

SDIN

Slave

N

OLRCK

OSCLK

SDOUTTDM_IN

DSP

LRCK

SCLK

SDIN

Slave

24 DS641PP2

9. PERFORMANCE PLOTS

CS8421

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

5k 20k10k 15k

Hz

Figure 15. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz

Tone, 48 kHz:48 kHz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

5k 20k10k 15k

Hz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

20k 80k40k 60k

Hz

Figure 16. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz

Tone, 44.1 kHz:192 kHz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

2.5k 20k5k 7.5k 10k 12.5k 15k 17.5k

Hz

Figure 17. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz

Tone, 44.1 kHz:48 kHz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

10k 40k20k 30k

Hz

Figure 19. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz

Tone, 48 kHz:96 kHz

Figure 18. Wideband FFT Plot (16k Po ints) 0 dBFS 1 kHz

Tone, 48 kHz:44.1 kHz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

5k 20k10k 15k

Hz

Figure 20. Wideband FFT Plot (16k Po ints) 0 dBFS 1 kHz

Tone, 96 kHz:48 kHz

DS641PP2 25

CS8421

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

5k 20k10k 15k

Hz

Figure 21. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz

Tone, 192 kHz:48 kHz

-60

-80

-100

d

-120

B

F

S

-140

-60

-80

-100

d

-120

B

F

S

-140

-160

-180

-200

10k 40k20k 30k

Hz

Figure 22. Wideband FFT Plot (16k Points) -60 dBFS

1 kHz Tone, 48 kHz:96 kHz

-60

-80

-100

d

-120

B

F

S

-140

-160

-180

-200

5k 20k10k 15k

Hz

Figure 23. Wideband FFT Plot (16k Points) -60 dBFS

1 kHz Tone, 48 kHz:48 kHz

-60

-80

-100

d

-120

B

F

S

-140

-160

-180

-200

5k 20k10k 15k

Hz

Figure 25. Wideband FFT Plot (16k Points) -60 dBFS

1 kHz Tone, 44.1 kHz:48 kHz

-160

-180

-200

20k 80k40k 60k

Hz

Figure 24. Wideband FFT Plot (16k Points) -60 dBFS

1 kHz Tone, 44.1 kHz:192 kHz

-60

-80

-100

d

-120

B

F

S

-140

-160

-180

-200

2.5k 20k5k 7.5k 10k 12.5k 15k 17.5k

Hz

Figure 26. Wideband FFT Plot (16k Points) -60 dBFS

1 kHz Tone, 48 kHz:44.1 kHz

26 DS641PP2

CS8421

-60

-80

-100

d

-120

B

F

S

-140

-160

-180

-200

5k 20k10k 15k

Hz

Figure 27. Wideband FFT Plot (16k Points) -60 dBFS

1 kHz Tone, 96 kHz:48 kHz

-60

-80

-100

d

-120

B

F

S

-140

-160

-180

-200

5k 20k10k 15k

Hz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

5k 20k10k 15k

Hz

Figure 28. IMD, 10 kHz and 11 kHz -7 dBFS,

96 kHz:48 kHz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

2.5k 20k5k 7.5k 10k 12.5k 15k 17.5k

Hz

Figure 29. Wideband FFT Plot (16k Points) -60 dBFS

1 kHz Tone, 192 kHz:48 kHz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

5k 20k10k 15k

Hz

Figure 31. IMD, 10 kHz and 11 kHz -7 dBFS,

44.1 kHz:48 kHz

Figure 30. IMD, 10 kHz and 11 kHz -7 dBFS,

48 kHz:44.1 kHz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

5k 20k10k 15k

Hz

Figure 32. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz

Tone, 44.1 kHz:48 kHz

DS641PP2 27

CS8421

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

20k 80k40k 60k

Hz

Figure 33. Wideband FFT Plot (16 k Points) 0 dBFS 80 kHz

Tone, 192 kHz:192 kHz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

5k 20k10k 15k

Hz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

10k 40k20k 30k

Hz

Figure 34. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz

Tone, 48 kHz:96 kHz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

5k 20k10k 15k

Hz

Figure 35. Wideband FFT Plot (16 k Points) 0 dBFS 20 kHz

Tone, 48 kHz:48 kHz

+0

-20

-40

-60

-80

d

B

-100

F

S

-120

-140

-160

-180

-200

2.5k 20k5k 7.5k 10k 12.5k 15k 17.5k

Hz

Figure 37. Wideband FFT Plot (16 k Points) 0 dBFS 20 kHz

Tone, 48 kHz:44.1 kHz

Figure 36. Wideband FFT Plot (16k Points) 0 dBFS 20 kHz

Tone, 96 kHz:48 kHz

-120

-122.5

-125

-127.5

-130

-132.5

d

B

-135

F

S

-137.5

-140

-142.5

-145

-147.5

-150

50k 175k75k 100k 125k 150k

Hz

Figure 38. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz

Tone, Fsi = 192 kHz

28 DS641PP2

d

B

F

S

-120

-122.5

-125

-127.5

-130

-132.5

-135

-137.5

-140

-142.5

-145

-147.5

-150

50k 175k75k 100k 125k 150k

Hz

CS8421

-120

-122.5

-125

-127.5

-130

-132.5

d

B

-135

F

S

-137.5

-140

-142.5

-145

-147.5

-150

50k 175k75k 100k 125k 150k

Hz

Figure 39. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz

Tone, Fsi = 48 kHz

-120

-122.5

-125

-127.5

-130

-132.5

d

B

-135

F

S

-137.5

-140

-142.5

-145

-147.5

-150

50k 175k75k 100k 125k 150k

Hz

Figure 41. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz

Tone, Fsi = 44.1 kHz

-120

-122.5

-125

-127.5

-130

-132.5

d

B

-135

F

S

-137.5

-140

-142.5

-145

-147.5

-150

50k 175k75k 100k 125k 150k

Hz

Figure 40. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz

Tone, Fsi = 96 kHz

-135

-136

-137

-138

-139

d

B

-140

F

S

-141

-142

-143

-144

-145

50k 175k75k 100k 125k 150k

Hz

Figure 42. Dynamic Range vs. Output Sample Rate, -

60 dBFS 1 kHz Tone, Fsi = 192 kHz

-120

-122.5

-125

-127.5

-130

-132.5

d

B

-135

F

S

-137.5

-140

-142.5

-145

-147.5

-150

50k 175k75k 100k 125k 150k

Hz

Figure 43. THD+N vs. Output Sample Rate, 0 dBFS 1 kHz

Tone, Fsi = 32 kHz

Figure 44. Dynamic Range vs. Output Sample Rate, -

60 dBFS 1 kHz Tone, Fsi = 32 kHz

DS641PP2 29

CS8421

-120

-122.5

-125

-127.5

-130

-132.5

d

B

-135

F

S

-137.5

-140

-142.5

-145

-147.5

-150

50k 175k75k 100k 125k 150k

Hz

-120

-122.5

-125

-127.5

-130

-132.5

d

B

-135

F

S

-137.5

-140

-142.5

-145

-147.5

-150

50k 175k75k 100k 125k 150k

Hz

Figure 45. Dynamic Range vs. Output Sample Rate, -

60 dBFS 1 kHz Tone, Fsi = 96 kHz

+0

-20

-40

-60

d

B

F

-80

S

-100

-120

-140

192 kHz:32 kHz

0 60k10k 20k 30k 40k 50k

192 kHz:48 kHz

192 kHz:96 kHz

Hz

Figure 46. Dynamic Range vs. Output Sample Rate, -

60 dBFS 1 kHz Tone, Fsi = 44.1 kHz

+0

-0.02

-0.04

-0.06

-0.08

d

B

-0.1

F

S

-0.12

-0.14

-0.16

-0.18

-0.2

0 25k5k 10k 15k 20k

Hz

Figure 47. Frequency Response with 0 dBFS Input Figure 48. Passband Ripple, 192 kHz:48 kHz

-120

-122.5

-125

-127.5

-130

-132.5

d

B

-135

F

S

-137.5

-140

-142.5

-145

-147.5

-150

50k 175k75k 100k 125k 150k

Hz

+0

-10

-20

-30

-40

-50

d

-60

B

-70

F

S

-80

-90

-100

-110

-120

-130

-140

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 49. Dynamic Range vs. Output Sample Rate, -

60 dBFS 1 kHz Tone, Fsi = 48 kHz

Figure 50. Linearity Error, 0 to -140 dBFS Input, 200 Hz

Tone, 48 kHz:48 kHz

30 DS641PP2

CS8421

+0

-10

-20

-30

-40

-50

d

-60

B

-70

F

S

-80

-90

-100

-110

-120

-130

-140

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 51. Linearity Error, 0 to -140 dBFS Input, 200 Hz

Tone, 48 kHz:44.1 kHz

+0

-10

-20

-30

-40

-50

d

-60

B

-70

F

S

-80

-90

-100

-110

-120

-130

-140

-140 +0-120 -100 -80 -60 -40 -20

dBFS

+0

-10

-20

-30

-40

-50

d

-60

B

-70

F

S

-80

-90

-100

-110

-120

-130

-140

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 52. Linearity Error, 0 to -140 dBFS Input, 200 Hz

Tone, 48 kHz:96 kHz

+0

-10

-20

-30

-40

-50

d

-60

B

-70

F

S

-80

-90

-100

-110

-120

-130

-140

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 53. Linearity Error, 0 to -140 dBFS Input, 200 Hz

Tone, 96 kHz:48 kHz

+0

-10

-20

-30

-40

-50

d

-60

B

-70

F

S

-80

-90

-100

-110

-120

-130

-140

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 55. Linearity Error, 0 to -140 dBFS Input, 200 Hz

Tone, 44.1 kHz:48 kHz

Figure 54. Linearity Error, 0 to -140 dBFS Input, 200 Hz

Tone, 44.1 kHz:192 kHz

+0

-10

-20

-30

-40

-50

d

-60

B

-70

F

S

-80

-90

-100

-110

-120

-130

-140

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 56. Linearity Error, 0 to -140 dBFS Input, 200 Hz

Tone, 192 kHz:44.1 kHz

DS641PP2 31

CS8421

-110

-115

-120

-125

-130

-135

-140

d

B

-145

F

S

-150

-155

-160

-165

-170

-175

-180

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 57. THD+N vs. Input Amplitude, 1 kHz Tone,

48 kHz:44.1 kHz

-110

-115

-120

-125

-130

-135

-140

d

B

-145

F

S

-150

-155

-160

-165

-170

-175

-180

-140 +0-120 -100 -80 -60 -40 -20

dBFS

-110

-115

-120

-125

-130

-135

-140

d

B

-145

F

S

-150

-155

-160

-165

-170

-175

-180

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 58. THD+N vs. Input Amplitude, 1 kHz Tone,

48 kHz:96 kHz

-110

-115

-120

-125

-130

-135

-140

d

B

-145

F

S

-150

-155

-160

-165

-170

-175

-180

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 59. THD+N vs. Input Amplitude, 1 kHz Tone,

96 kHz:48 kHz

-110

-115

-120

-125

-130

-135

-140

d

B

-145

F

S

-150

-155

-160

-165

-170

-175

-180

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 61. THD+N vs. Input Amplitude, 1 kHz Tone,

44.1 kHz:48 kHz

Figure 60. THD+N vs. Input Amplitude, 1 kHz Tone,

44.1 kHz:192 kHz

-110

-115

-120

-125

-130

-135

-140

d

B

-145

F

S

-150

-155

-160

-165

-170

-175

-180

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 62. THD+N vs. Input Amplitude, 1 kHz Tone,

192kHz:48kHz

32 DS641PP2

CS8421

-110

-115

-120

-125

-130

-135

-140

d

B

-145

F

S

-150

-155

-160

-165

-170

-175

-180

0 20k2.5k 5k 7.5k 10k 12.5k 15k 17.5k

Hz

Figure 63. THD+N vs. Frequency Input, 0 dBFS,

48 kHz:44.1 kHz

-110

-115

-120

-125

-130

-135

-140

d

B

-145

F

S

-150

-155

-160

-165

-170

-175

-180

0 20k2.5k 5k 7.5k 10k 12.5k 15k 17.5k

Hz

-110

-115

-120

-125

-130

-135

-140

d

B

-145

F

S

-150

-155

-160

-165

-170

-175

-180

-140 +0-120 -100 -80 -60 -40 -20

dBFS

Figure 64. THD+N vs. Frequency Input, 0 dBFS,

48 kHz:96 kHz

-110

-115

-120

-125

-130

-135

-140

d

B

-145

F

S

-150

-155

-160

-165

-170

-175

-180

0 20k2.5k 5k 7.5k 10k 12.5k 15k 17.5k

Hz

Figure 65. THD+N vs. Frequency Input, 0 dBFS,

44.1 kHz:48 kHz

Figure 66. THD+N vs. Frequency Input, 0 dBFS,

96 kHz:48 kHz

All performance plots represent typical performance. Measurements for a ll performance plots were taken under the

following conditions, unless otherwise stated:

• VD = 2.5 V, VL = 3.3 V

• Serial Audio Input port set to slave

• Serial Audio Output port set to slave

• Input and output clocks and data are asynchronous

• XTI/XTO = 27 MHz

• Input signal = 1.000 kHz, 0 dBFS

• Measurement Bandwidth = 20 to (Fso/2) Hz

• Word Width = 24 Bits

DS641PP2 33

10.APPLICATIONS

10.1 Reset, Power Down, and Start-Up

When RST is low the CS8421 enters a low power mode, all internal states are reset, and the outputs are

disabled. After RST

(MS_SEL, SAIF, and SAOF) and sets the appropriate mode of operation. After the mo de has been se t (approximately 4 µs) the part is set to normal operation and all outputs are functional.

10.2 Power Supply, Grounding, and PCB Layout

The CS8421 operates from a VD = +2.5 V and VL = +3.3 V or +5.0 V supply. These supplies may be set

independently. Follow normal supply decoupling practices, see Figure 6.

Extensive use of power and ground planes, ground plane fill in unused areas, and surface mount decoupling

capacitors are recommended. Decoupling capacitors should be mounted on the same side of the b oard a s

the CS8421 to minimize inductance effects and all decoupling capacitors sho uld be as close to the CS8421

as possible. The pin of the configuration resistors not connected to MS_SEL, SAIF, and SAOF should be

connected as close as possible to VL or GND.

transitions from low to high the part senses the resistor value on the configuration pins

CS8421

34 DS641PP2

11. PACKAGE DIMENSIONS 20L TSSOP (4.4 mm BODY) PACKAGE DRAWING

N

CS8421

1

23

TOP VIEW

D

E

e

2

b

SIDE VIEW

A2

A1

A

SEATING

PLANE

L

INCHES MILLIMETERS

1

E1

END VIEW

NOTE

DIM MIN NOM MAX MIN NOM MAX

A -- -- 0.043 -- -- 1.10

A1 0.002 0.004 0.006 0.05 -- 0.15

A2 0.03346 0.0354 0 .037 0.85 0.90 0.95

b 0.00748 0.0096 0.012 0.19 0.245 0.30 2,3

D 0.252 0.256 0.259 6.40 6.50 6.60 1

E 0.248 0.2519 0.256 6.30 6.40 6.50

E1 0.169 0.1732 0.177 4.30 4.40 4.50 1

e -- -- 0.026 -- -- 0.65

L 0.020 0.024 0.028 0.50 0.60 0.70

µ

0° 4° 8° 0° 4° 8°

∝

JEDEC #: MO-153

Controlling Dimension is Millimeters.

Notes:

1. “D” and “E1” are reference datums and do not included mold flash or protrusions, but do include mold

mismatch and are measured at the parting line, mold flash or protrusions shall not exceed 0.20 mm per

side.

2. Dimension “b” does not include dambar protrusion/intrusion. Allowable dambar protrusion shall be

0.13 mm total in excess of “b” dimension at maximum material condition. Dambar intrusion shall not reduce dimension “b” by more than 0.07 mm at least material condition.

3. These dimensions apply to the flat section of the lead between 0.10 and 0.25 mm from lead tips.

THERMAL CHARACTERISTICS

Parameter Symbol Min Typ Max Units

Junction to Ambient Thermal Impedance 2 Layer Board

4 Layer Board

θ

JA

-

-

DS641PP2 35

48

38

-

-

°C/Watt

°C/Watt

20-PIN QFN (5 × 5 MM BODY) PACKAGE DRAWING

CS8421

D

Pin #1 Corner

Top View

b

E

A1

A

Side View

E2

L

Bottom View

INCHES MILLIMETERS

D2

e

Pin #1 Corner

NOTE

DIM MIN NOM MAX MIN NOM MAX

A----0.0394----1.001

A1 0.0000 -- 0.0020 0.00 -- 0.05 1

b 0.0091 0.0110 0.0130 0.23 0.28 0.33 1,2

D 0.1969 BSC 5.00 BSC 1

D2 0.1201 0.1220 0.1240 3.05 3.10 3.15 1

E 0.1969 BSC 5.00 BSC 1

E2 0.1202 0.1221 0.1241 3.05 3.10 3.15 1

e 0.0256 BSC 0.65 BSC 1

L 0.0197 0.0236 0.0276 0.50 0.60 0.70 1

JEDEC #: MO-220

Controlling Dimension is Millimeters.

Notes:

1. Dimensioning and tolerance per ASME Y 14.5M-1995.

2. Dimensioning lead width applies to the plated terminal and is m easured between 0 .23mm and 0.33mm

from the terminal tip.

THERMAL CHARACTERISTICS

Parameter Symbol Min Typ Max Units

Junction to Ambient Thermal Impedance 2 Layer Board

4 Layer Board

θ

JA

-

-

36 DS641PP2

128

35

-

-

°C/Watt

°C/Watt

12.REVISION HISTORY

Release Date Changes

A1 July 2004 Initial Advance Release

CS8421

PP1 January 2005 -Updated

-Updated

-Updated

-Updated

-Updated

-Updated Figure 6. “Typical Connection Diagram, Master and Slave Modes”

on page 16

-Added

page 15

Figure 5. “Typical Connection Diagram, No External Master Clock” on

.

-Corrected reference to bypass mode to output only data on

-Added

Section 7.6.1 “Clocking” on page 22.

-Updated

-Updated

-Added Thermal Pad label

-Added Thermal Pad pin description to

-Updated

PP2 July 2005 -Updated

-Corrected

-Corrected

“Features” on page 1.

“Sample Rate with other XTI clocks” on page 11.

“DC Electrical Characteristics” on page 12.

“Digital Input Characteristics” on page 13.

“Digital Interface Specifications” on page 13

.

page 17.

“Master Clock” on page 21.

“Time Division Multiplexing (TDM) Mode” on page 23.

“Pin Descriptions” on page 6.

“QFN Pin Descriptions” on page 8.

“Performance Plots” on page 25.

“Characteristics and Specifications” on page 10.

Section 7.6.1 “Clocking” on page 22.

“Thermal Characteristics” on page 36.

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative.

To find the one nearest to you go to

IIMPORTANT NOTICE

“Preliminary” product information describes products that are in production, but for which full characterization data is not yet available. Cirrus Logic, Inc. and its sub-

sidiaries (“Cirrus”) believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and

is provided “AS IS” wi thout warrant y of any kind ( express or imp lied). Custo mers are advised to obtain the l atest versi on of relevant information to verify, before