Cirrus Logic CS5560 User Manual

5/4/09

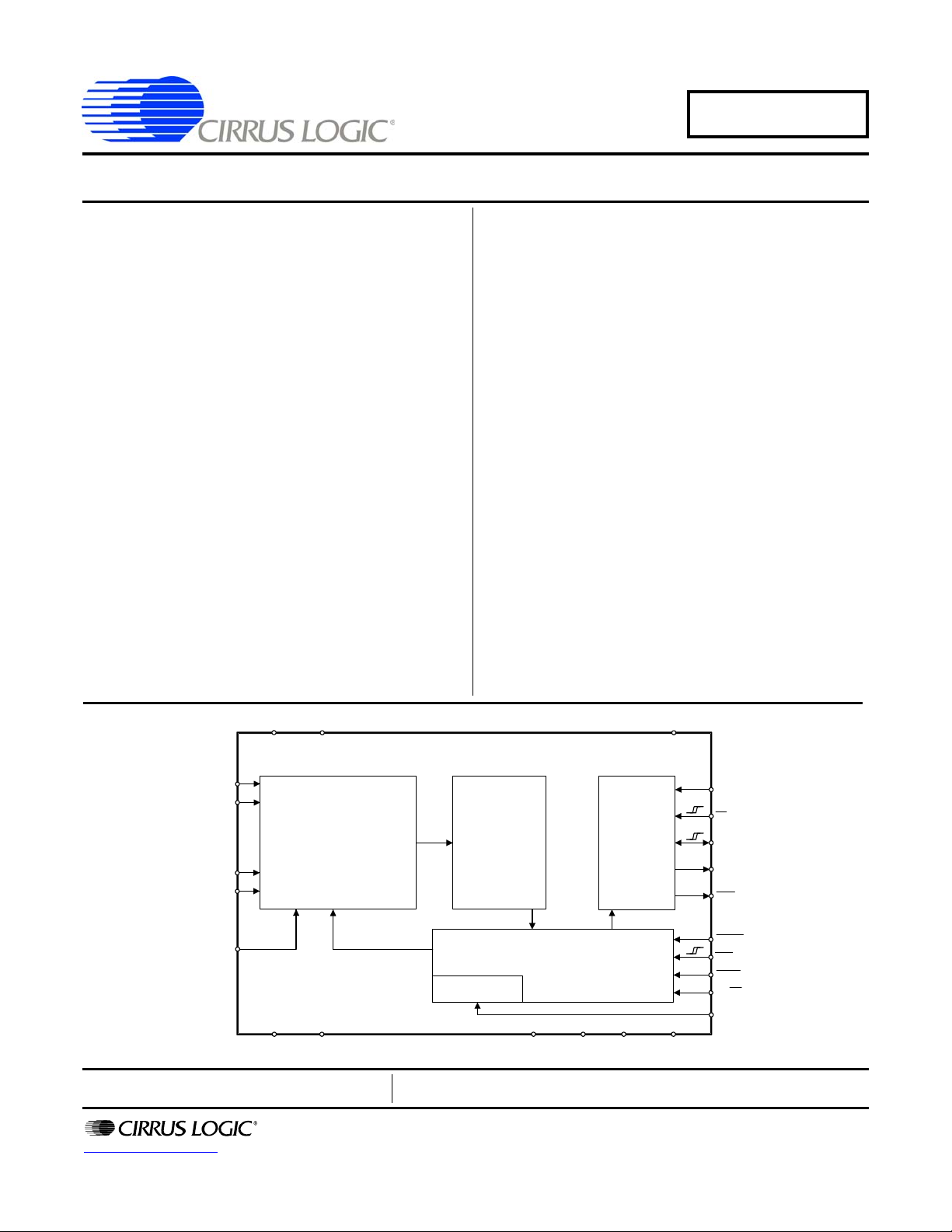

AIN+

AIN-

CS

SCLK

SMODE

VREF+

VREF-

RDY

OSC/CLOCK

GENERATOR

CONV

BP/UP

DIGITAL CONTROL

SERIAL

INTERFACE

ADC

DIGITAL

FILTER

LOGIC

VL

MCLK

SDO

RST

SLEEP

VLR

VLR2

V1-

V2-

BUFEN

V2+

V1+

CS5560

TST

DCR

CS5560

±2.5 V / 5 V, 50 kSps, 24-bit, High-throughput

Features & Description

Differential Analog Input

On-chip Buffers for High Input Impedance

Conversion Time = 20 μS

Settles in One Conversion

Linearity Error = 0.0005%

Signal-to-Noise = 110 dB

24 Bits, No Missing Codes

Simple three/four-wire serial interface

Power Supply Configurations:

- Analog: +5 V / GND; IO: +1.8 V to +3.3 V

- Analog: ±2.5 V; IO: +1.8 V to +3.3 V

Power Consumption:

- ADC Input Buffers On: 90 mW

- ADC Input Buffers Off: 60 mW

General Description

The CS5560 is a single-channel, 24-bit analog-to-digital

converter capable of 50 kSps conversion rate. The input

accepts a fully differential analog input signal. On-chip

buffers provide high input impedance for both the AIN inputs and the VREF+ input. This significantly reduces the

drive requirements of signal sources and reduces errors

due to source impedances. The CS5560 is a delta-sigma

converter capable of switching multiple input channels at

a high rate with no loss in throughput. The ADC uses a

low-latency digital filter architecture. The filter is designed

for fast settling and settles to full accuracy in one conv ersion. The converter's 24-bit data output is in serial form,

with the serial port acting as either a master or a slave. The

converter is designed to support bipolar, ground-referenced signals when operated from ±2.5V analog supplies.

The converter can operate from an analog supply of 0-5V

or from ±2.5V. The digital interface supports standard logic operating from 1.8, 2.5, or 3.3 V.

ΔΣ

ADC

Preliminary Product Information

http://www.cirrus.com

ORDERING INFORMATION:

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

Copyright Cirrus Logic, Inc. 2009

(All Rights Reserved)

See Ordering Information on page 32.

MAY ‘09

DS713PP2

5/4/09

CS5560

TABLE OF CONTENTS

1. CHARACTERISTICS AND SPECIFICATIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

ANALOG CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

SWITCHING CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

DIGITAL CHARACTERISTICS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

DIGITAL FILTER CHARACTERISTICS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

GUARANTEED LOGIC LEVELS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

RECOMMENDED OPERATING CONDITIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12

ABSOLUTE MAXIMUM RATINGS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2. OVERVIEW . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

3. THEORY OF OPERATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

3.1 Converter Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

3.2 Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.3 Voltage Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

3.4 Analog Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.5 Output Coding Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16

3.6 Typical Connection Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.7 AIN & VREF Sampling Structures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.8 Converter Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.9 Digital Filter Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

3.10 Serial Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

3.10.1 SSC Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.10.2 SEC Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3.11 Power Supplies & Grounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

3.12 Using the CS5560 in Multiplexing Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

3.13 Synchronizing Multiple Converters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

4. PIN DESCRIPTIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

5. PACKAGE DIMENSIONS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

6. ORDERING INFORMATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

7. ENVIRONMENTAL, MANUFACTURING, & HANDLING INFORMATION . . . . . . . . . . . . . .32

8. REVISION HISTORY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

2 DS713PP2

5/4/09

CS5560

LIST OF FIGURES

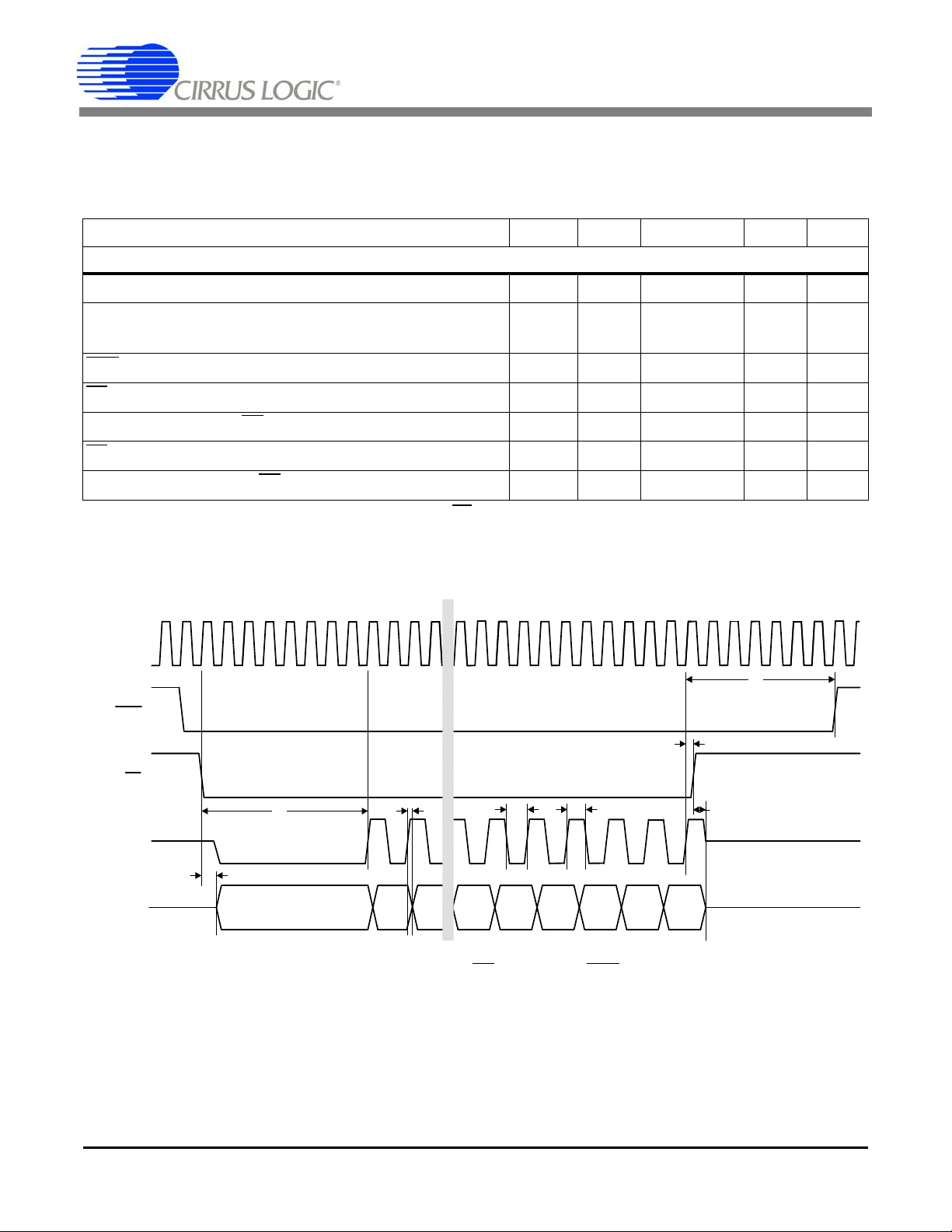

Figure 1. SSC Mode - Read Timing, CS remaining low . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

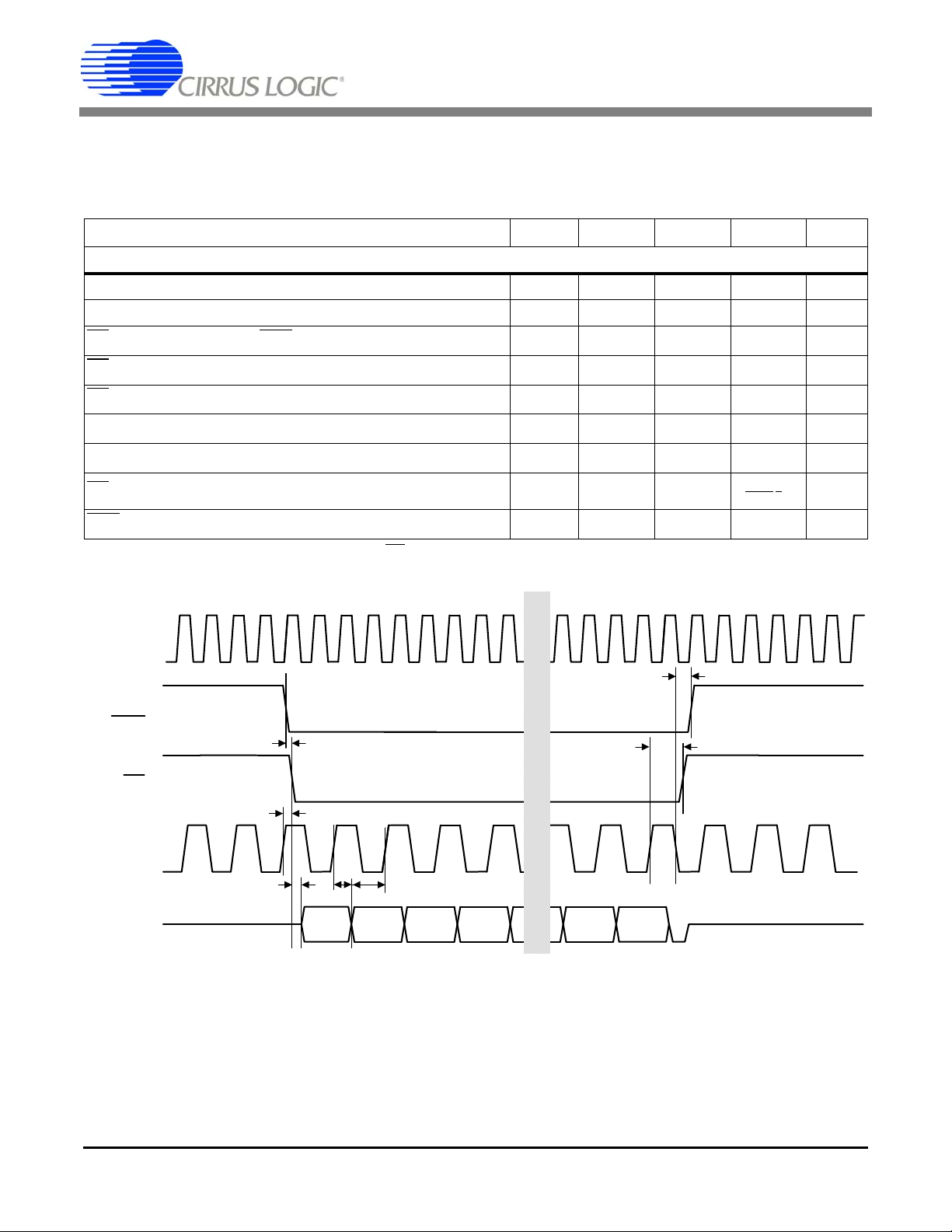

Figure 2. SSC Mode - Read Timing, CS falling after RDY falls . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

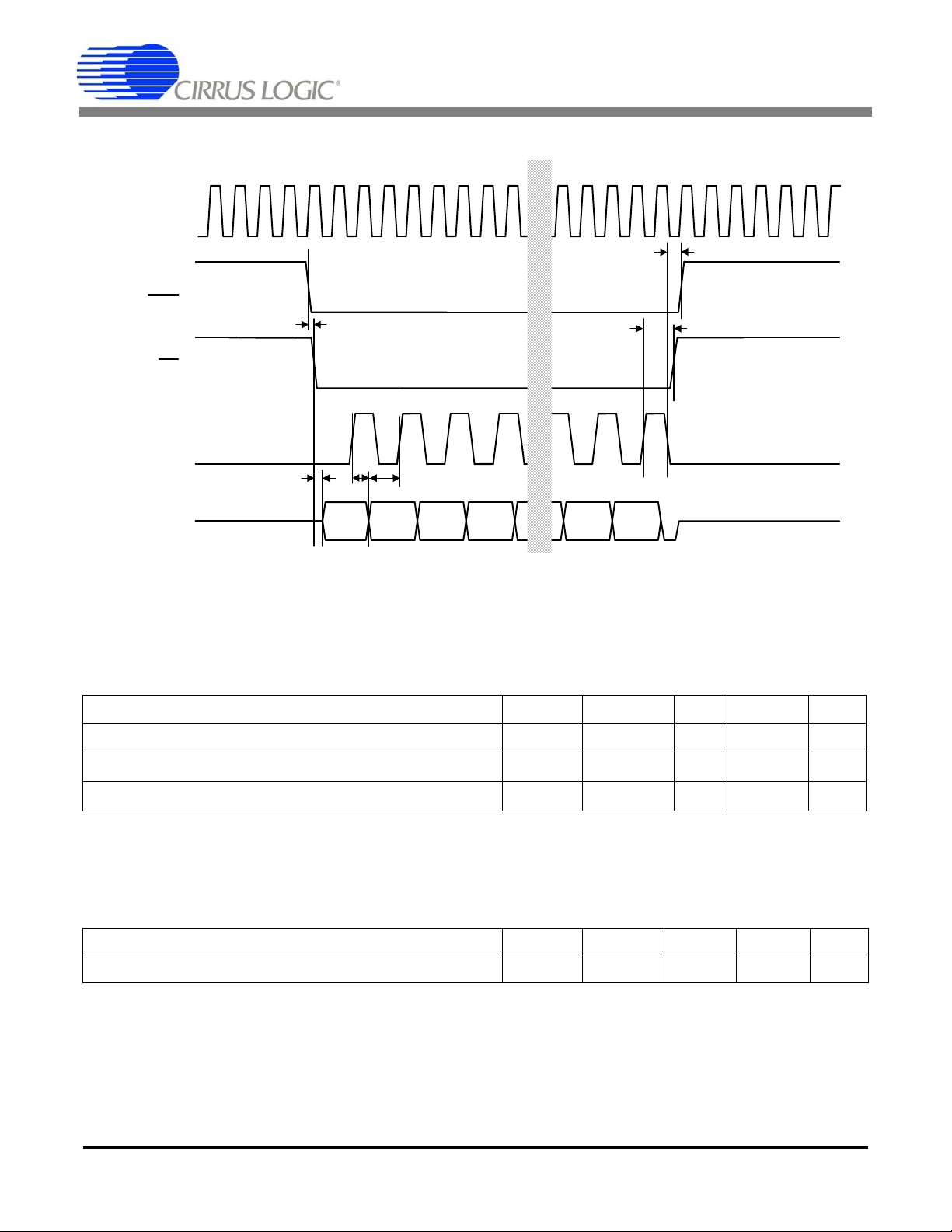

Figure 3. SEC Mode - Continuous SCLK Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Figure 4. SEC Mode - Discontinuous SCLK Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 5. Voltage Reference Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Figure 6. CS5560 Configured Using ±2.5V Analog Supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 7. CS5560 Configured Using a Single 5V Analog Supply . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 8. CS5560 DNL Plot. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 9. Spectral Performance, 0 dB. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 10. Spectral Performance, -6 dB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 11. Spectral Performance, -12 dB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 12. Spectral Performance, -20 dB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 13. Spectral Performance, -40 dB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 14. Spectral Performance, -100 dB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 15. Spectral Performance, -120 dB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 16. Spectral Performance, -130 dB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 17. Spectral Plot of Noise with Shorted Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 18. Noise Histogram (32k Samples) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 19. CS5560 Digital Filter Response (DC to fs/2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 20. CS5560 Digital Filter Response (DC to 5 kHz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 21. CS5560 Digital Filter Response (DC to 4fs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 22. Simple Multiplexing Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 23. More Complex Multiplexing Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

LIST OF TABLES

Table 1. Output Coding, Two’s Complement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 2. Output Coding, Offset Binary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

DS713PP2 3

5/4/09

CS5560

1. CHARACTERISTICS AND SPECIFICATIONS

• Min / Max characteristics and specifications are guaranteed over the specified operating conditions.

• Typical characteristics and specifications are measured at nominal supply voltages and T

• VLR = 0 V. All voltages with respect to 0 V.

= 25°C.

A

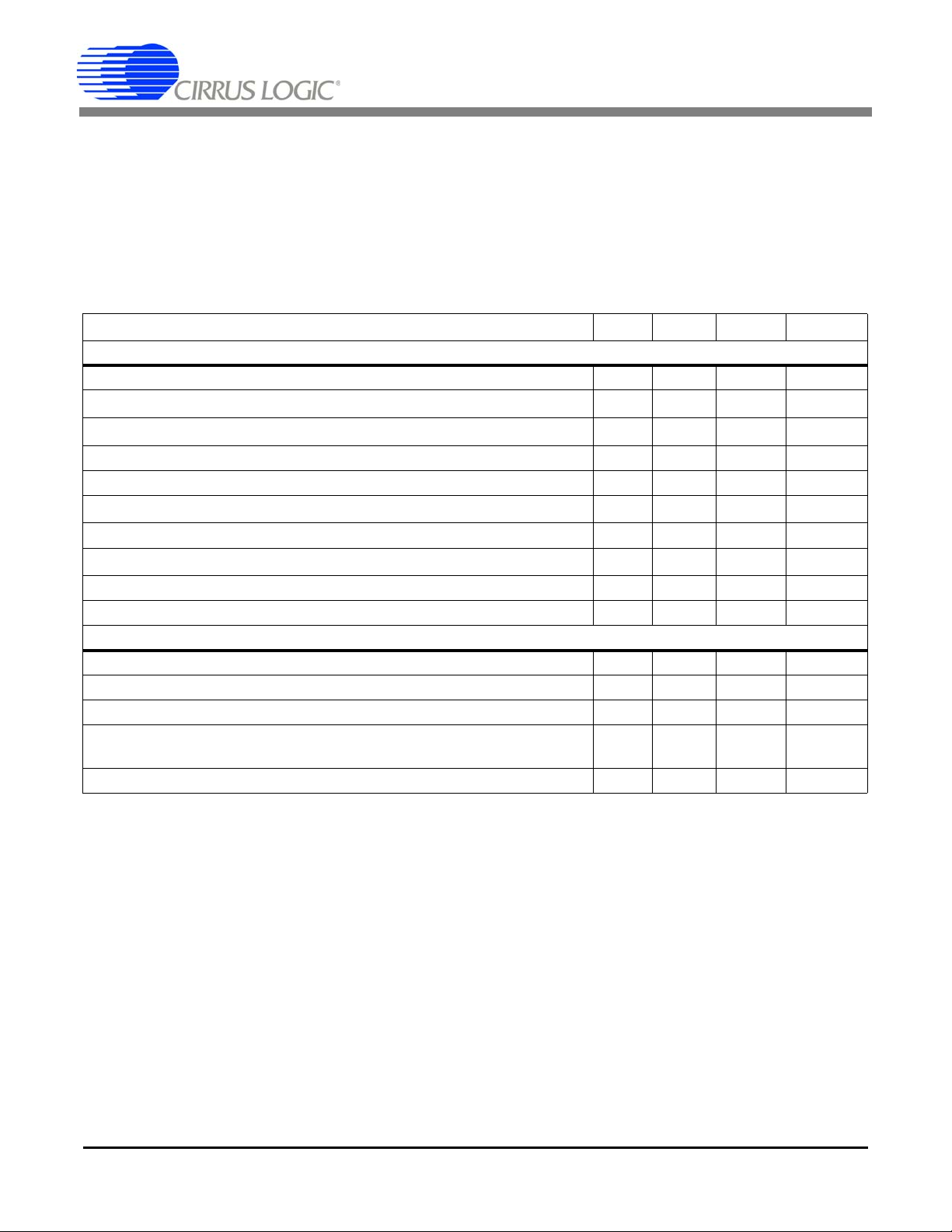

ANALOG CHARACTERISTICS T

±5%; VL -VLR = 3.3 V, ±5%; VREF = (VREF+) - (VREF-) = 4.096V; MCLK = 16 MHz; SMODE = VL.

BUFEN = V1+ unless otherwise stated. Connected per Figure 6. Bipolar mode unless otherwise stated.

Parameter Min Typ Max Unit

Accuracy

Linearity Error - 0.0005 - ±%FS

Differential Linearity Error (Note 1, 2) - ±0.1 - LSB

Positive Full-scale Error - 1.0 - %FS

Negative Full-scale Error - 1.0 - %FS

Full-scale Drift (Note 2) - 1 - ppm / °C

Unipolar Offset (Note 2) - +2000 - LSB

Unipolar Offset Drift (Note 2) - 2 - LSB / °C

Bipolar Offset (Note 2) - ±1000 - LSB

Bipolar Offset Drift (Note 2) - 1 - LSB / °C

Noise - 9.5 - μVrms

Dynamic Performance

Peak Harmonic or Spurious Noise 997 Hz, -0.5 dB Input - -111 - dB

Total Harmonic Distortion 997 Hz, -0.5 dB Input - -108 -95 dB

Signal-to-Noise 108 110 - dB

S/(N + D) Ratio -0.5 dB Input, 997 Hz

-3 dB Input Bandwidth (Note 3) - 42 - kHz

= -40 to +85 °C; V1+ = V2+ = +2.5 V, ±5%; V1- = V2- = -2.5 V,

A

-60 dB Input, 997 Hz95-

109

50

-

-

dB

dB

24

24

24

1. No missing codes is guaranteed at 24 bits resolution over the specified temperature range.

2. One LSB is equivalent to (2 x VREF) ÷ 2

3. Scales with MCLK.

4 DS713PP2

24

or (2 x 4.096) ÷ 16,777,216 = 488 nV.

5/4/09

CS5560

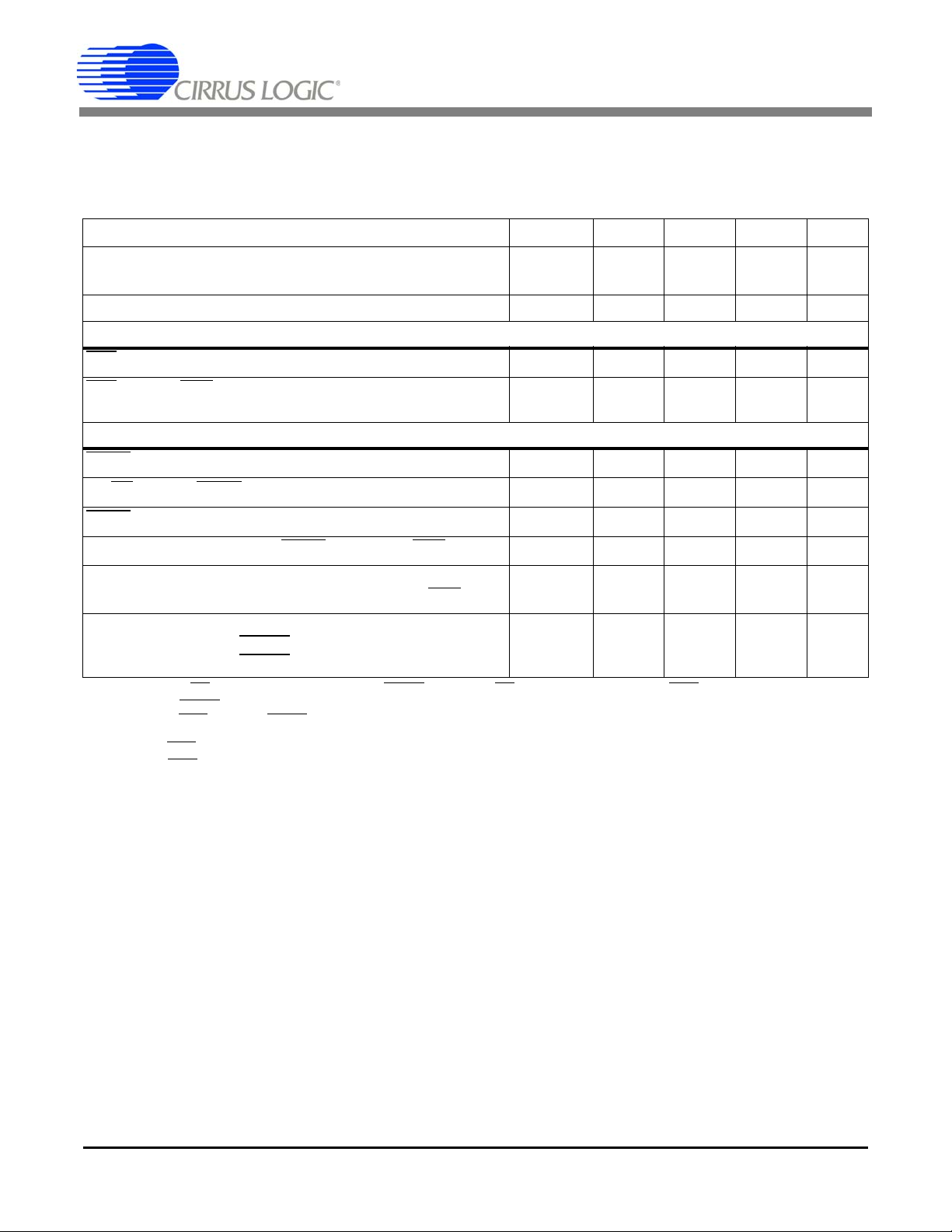

ANALOG CHARACTERISTICS (CONTINUED) T

V2- = -2.5 V, ±5%; VL -VLR = 3.3 V, ±5%; VREF = (VREF+) - (VREF-) = 4.096V; MCLK = 16 MHz; SMODE = VL.;

BUFEN = V1+ unless otherwise stated. Connected per Figure 6.

Parameter Min Typ Max Unit

Analog Input

Analog Input Range Unipolar

Input Capacitance - 10 - pF

CVF Current (Note 4) AIN Buffer On (BUFEN = V+)

AIN Buffer Off (BUFEN = V-)

Common Mode Rejection Ratio (CMRR) 116 130 - dB

Voltage Reference Input

Voltage Reference Input Range

(VREF+) – (VREF-) (Note 5) 2.4 4.096

Input Capacitance - 10 - pF

CVF Current VREF+ Buffer On (BUFEN = V+)

VREF+ Buffer Off (BUFEN = V-)

Power Supplies

DC Power Supply Currents I

Power Consumption Normal Operation Buffers On

= -40 to +85 °C; V1+ = V2+ = +2.5 V, ±5%; V1- =

A

0 to +VREF

Bipolar

VREF-

V1

I

V2

I

VL

Buffers Off

-

-

-

-

-

-

-

-

-

-

±VREF

600

130

3

1

1

-

-

-

90

60

106

-

-

4.2

-

-

-

19

1.8

0.6

90

V

V

nA

μA

V

μA

mA

mA

mA

mA

mA

mW

mW

Power Supply Rejection (Note 6) V1+ , V2+ Supplies

V1-, V2- Supplies

4. Measured using an input signal of 1 V DC.

5. For optimum performance, VREF+ should always be less than (V+) - 0.2 volts to preve nt saturation of the VREF+ input buffer.

6. Tested with 100 mVP-P on any supply up to 2 kHz. V1+ and V2+ supplies at the same voltage potential, V1- and V2- supplies at

the same voltage potential.

60

60

70

70

-

-

dB

dB

DS713PP2 5

5/4/09

SWITCHING CHARACTERISTICS

TA= -40 to +85 °C; V1+ = V2+ = +2.5 V, ±5%; V1- = V2- = -2.5 V, ±5%;

VL - VLR = 3.3 V, ±5%, 2.5 V, ±5%, or 1.8 V, ±5%

Input levels: Logic 0 = 0V = Low; Logic 1 = VD+ = High; CL = 15 pF.

Parameter Symbol Min Typ Max Unit

CS5560

Master Clock Frequency Internal Oscillator

External Clock

XIN

f

clk

12

0.5

14

16

16

16.2

MHz

MHz

Master Clock Duty Cycle 40 - 60 %

Reset

RST

Low Time t

rising to RDY falling Internal Oscillator

RST

External Clock

t

wup

res

1--µs

-

-

120

1536

-

-

µs

MCLKs

Conversion

CONV

Pulse Width t

setup to CONV falling (Note 7) t

BP/UP

low to start of conversion t

CONV

Perform Single Conversion (CONV

high before RDY falling) t

cpw

scn

scn

bus

4--MCLKs

0--ns

--2MCLKs

20 - - MCLKs

Conversion Time (Note 8)

Start of Conversion to RDY

falling t

buh

--324MCLKs

Sleep Mode

SLEEP

SLEEP

7. BP/UP can be changed coincident CONV falling. BP/UP must remain stable until RDY falls.

8. If CONV

If RDY is tied to CONV, conversions will occur every 322 MCLKs.

If CONV is operated asynchronously to MCLK, a conversion may take up to 324 MCLKs.

RDY falls at the end of conversion.

9. RDY

is held low continuously, conversions occur every 320 MCLK cycles.

will fall when the device is fully operational when coming out of sleep mode.

low to low-power state

high to device active (Note 9)

t

t

con

con

-

-

50

3083

-

-

µs

MCLKs

6 DS713PP2

5/4/09

MCLK

RDY

SCLK(o)

SDO

MSB MSB–1

LSB

LSB+1

CS

t

1

t

2

t

3

t

4

t

5

Figure 1. SSC Mode - Read Timing, CS remaining low (Not to Scale)

SWITCHING CHARACTERISTICS (CONTINUED)

TA= -40 to +85 °C; V1+ = V2+ = +2.5 V, ±5%; V1- = V2- = -2.5 V, ±5%;

VL - VLR = 3.3 V, ±5%, 2.5 V, ±5%, or 1.8 V, ±5%

Input levels: Logic 0 = 0V = Low; Logic 1 = VD+ = High; CL = 15 pF.

Parameter Symbol Min Typ Max Unit

Serial Port Timing in SSC Mode (SMODE = VL)

RDY

falling to MSB stable t

Data hold time after SCLK rising t

Serial Clock (Out) Pulse Width (low)

(Note 10, 11) Pulse Width (high)

rising after last SCLK rising t

RDY

10. SDO and SCLK will be high impedance when CS is high. In some systems SCLK and SDO may require pull-down

resistors.

11. SCLK = MCLK/2.

1

2

t

3

t

4

5

CS5560

--2-MCLKs

-10-ns

50

50

-8-MCLKs

-

-

-

-

ns

ns

DS713PP2 7

5/4/09

MCLK

RDY

SCLK(o)

SDO

CS

t

12

t

8

t

13

t

9

t

7

t

11

MSB MSB–1

LSB

LSB+1

t

14

t

10

Figure 2. SSC Mode - Read Timing, CS falling after RDY falls (Not to Scale)

SWITCHING CHARACTERISTICS (CONTINUED)

TA= -40 to +85 °C; V1+ = V2+ = +2.5 V, ±5%; V1- = V2- = -2.5 V, ±5%;

VL - VLR = 3.3 V, ±5%, 2.5 V, ±5%, or 1.8 V, ±5%

Input levels: Logic 0 = 0V = Low; Logic 1 = VD+ = High; CL = 15 pF.

Parameter Symbol Min Typ Max Unit

Serial Port Timing in SSC Mode (SMODE = VL)

Data hold time after SCLK rising t

Serial Clock (Out) Pulse Width (low)

(Note 12, 13) Pulse Width (high)

RDY

rising after last SCLK rising t

falling to MSB stable t

CS

First SCLK rising after CS

hold time (low) after SCLK rising t

CS

SCLK, SDO tristate after CS

12. SDO and SCLK will be high impedance when CS is high. In some systems it may require a pull-down resistor.

13. SCLK = MCLK/2.

falling t

rising t

t

t

10

11

12

13

14

7

8

9

CS5560

-10-ns

50

50

-8-MCLKs

-10-ns

-8-MCLKs

10 - - ns

-5-ns

-

-

-

-

ns

ns

8 DS713PP2

5/4/09

1

SCLK

10

MCLK

SCLK(i)

SDO

CS

RDY

LSBMSB

t

19

t

18

t

20

t

17

t

16

t

15

t

21

Figure 3. SEC Mode - Continuous SCLK Read Timing (Not to Scale)

SWITCHING CHARACTERISTICS (CONTINUED)

TA= -40 to +85 °C; V1+ = V2+ = +2.5 V, ±5%; V1- = V2- = -2.5 V, ±5%;

VL - VLR = 3.3 V, ±5%, 2.5 V, ±5%, or 1.8 V, ±5%

Input levels: Logic 0 = 0V = Low; Logic 1 = VD+ = High; CL = 15 pF.

Parameter Symbol Min Typ Max Unit

Serial Port Timing in SEC Mode (SMODE = VLR)

SCLK(in) Pulse Width (High)

SCLK(in) Pulse Width (Low)

CS

hold time (high) after RDY falling t

hold time (high) after SCLK rising t

CS

CS

low to SDO out of Hi-Z (Note 14) t

Data hold time after SCLK rising t

Data setup time before SCLK rising t

-

-

15

16

17

18

19

CS5560

30 - - ns

30 - - ns

10 - - ns

10 - - ns

-10-ns

-10-ns

10 - - ns

CS

hold time (low) after SCLK rising

RDY

rising after SCLK falling t

14. SDO will be high impedance when CS is high. In some systems it may require a pull-down resistor .

t

20

21

10 - ns

-10-ns

DS713PP2 9

5/4/09

MCLK

SCLK(i)

SDO

CS

RDY

LSBMSB

t

19

t

18

t

20

t

17

t

15

t

21

Figure 4. SEC Mode - Discontinuous SCLK Read Timing (Not to Scale)

CS5560

DIGITAL CHARACTERISTICS

= TMIN to TMAX; VL = 3.3V, ±5% or VL = 2.5V, ±5% or 1.8V, ±5%; VLR = 0V

T

A

Parameter Symbol Min Typ Max Unit

Input Leakage Current I

Digital Input Pin Capacitance C

Digital Output Pin Capacitance C

in

in

out

--2µA

-3-pF

-3-pF

DIGITAL FILTER CHARACTERISTICS

T

= TMIN to TMAX; VL = 3.3V, ±5% or VL = 2.5V, ±5% or 1.8V, ±5%; VLR = 0V

A

Parameter Symbol Min Typ Max Unit

Group Delay - - 160 - MCLKs

10 DS713PP2

Loading...

Loading...