CS5525

CS5526

16-Bit/20-Bit Multi-Range ADC with 4-Bit Latch

Features

l

Delta-Sigma A/D Converter

- Linearity Error: 0.0015%FS

- Noise Free Resolution: 18-bits

l

Bipolar/Unipolar Input Ranges

- 25 mV, 55 mV, 100 mV, 1 V, 2.5 V and 5 V

l

Chopper Stabilized Instrumentation Amplifier

l

On-Chip Charge Pump Drive Circuitry

l

4-Bit Output Latch

l

Simple three-wire serial interface

- SPI™ and Microwire™ Compatible

- Schmitt Trigger on Serial Clock (SCLK)

l

Programmable Output Word Rates

- 3.76 Hz to 202Hz (XIN = 32.768 kHz)

- 11.47 Hz to 616 Hz (XIN = 100 kHz)

l

Output Settles in One Conversion Cycle

l

Simultaneous 50/60 Hz Noise Rejection

l

System and Self-Calibration with

Read/Write Registers

l

Single +5 V Analog Supply

+3.0 V or +5 V Digital Supply

l

Low Power Mode Consumption: 4 mW

- 1.8 mW in 1 V, 2.5 V, and 5 V Input Ranges

General Description

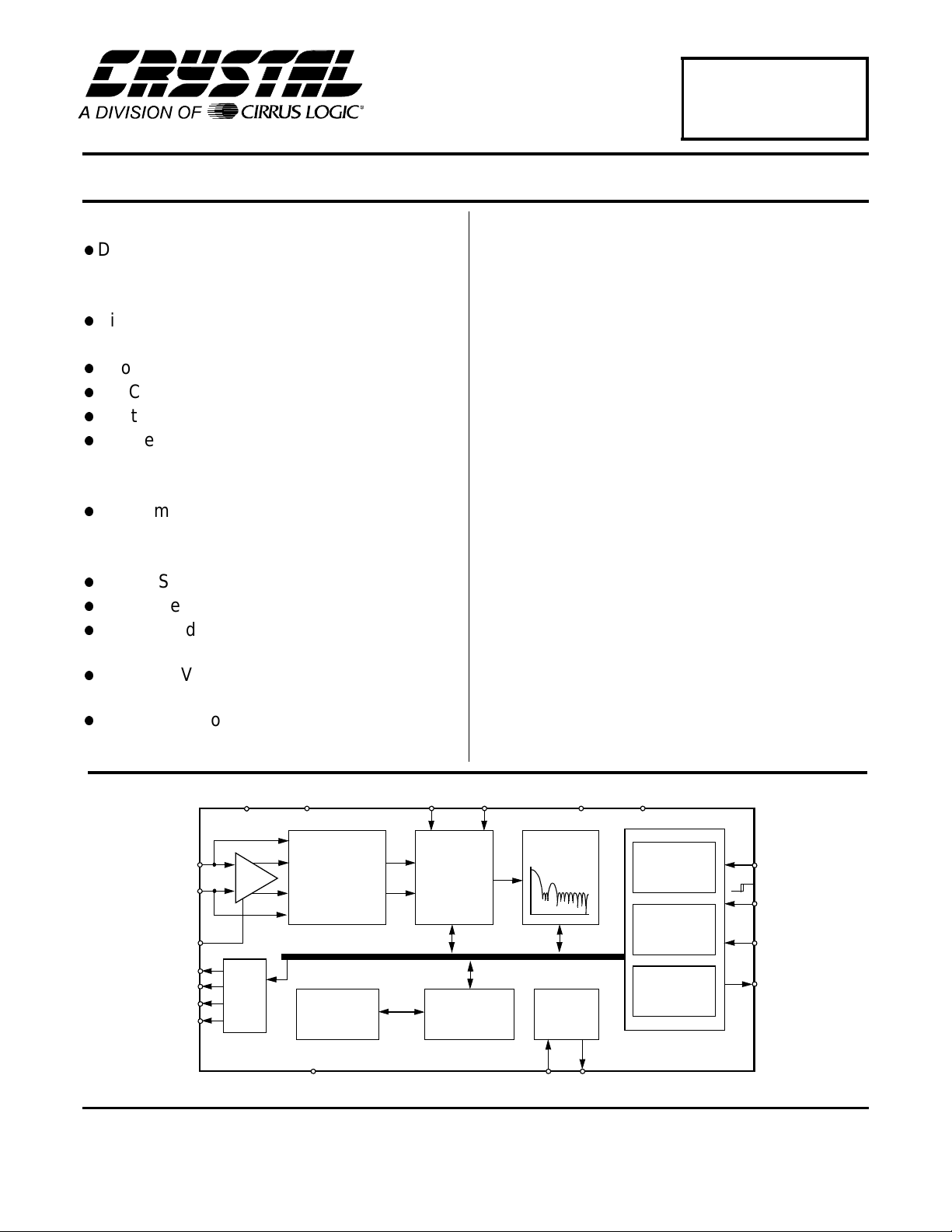

The 16-bit CS5525 and the 20-bit CS5526 ar e highl y integrated

instrumentation amplifier, a PGA (programmable gain

amplifier), eight digital filters, and self and system calibration circuitry.

The converters are designed to provide their own negative supply which enables their on-chip instrumentation

amplifiers to measure bipolar ground-referenced si gnals

≤

±100 mV. By directly supplying NBV with -2.5 V and

with VA+ at 5 V,

can be measured.

The digital filters provide programmable output update

rates between 3.76 Hz to 202 Hz (XIN = 32.768 kHz).

Output word rates can be increased by appr oximately 3X

by using XIN = 100 kHz. Each filter is designed to settle

to full accuracy for its output update rate in one conversion cycle. The filters with word rates of 15 Hz or less

(XIN = 32.768 kHz) reject both 50 and 6 0 Hz (

interference simultaneously.

Low power, single conversion settling time, programmable output rates, and the ability to handle negative input

signals make these single supply products ideal solutions for isolated and n on-isolated applicati ons.

ORDERING INFORMATION

∆Σ

A/D converters which include an

See page 26.

±2.5 V signals (with respect to groun d)

±3 Hz) line

VA+ AGND VREF+ VREF- VD+DGND

AIN+

AIN-

NBV

A0

A1

A2

A3

Cirrus Logic, Inc.

Crystal Semiconductor Products Division

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.crystal.com

+

X20

-

Latch

Programmable

Gain

Calibration

Memory

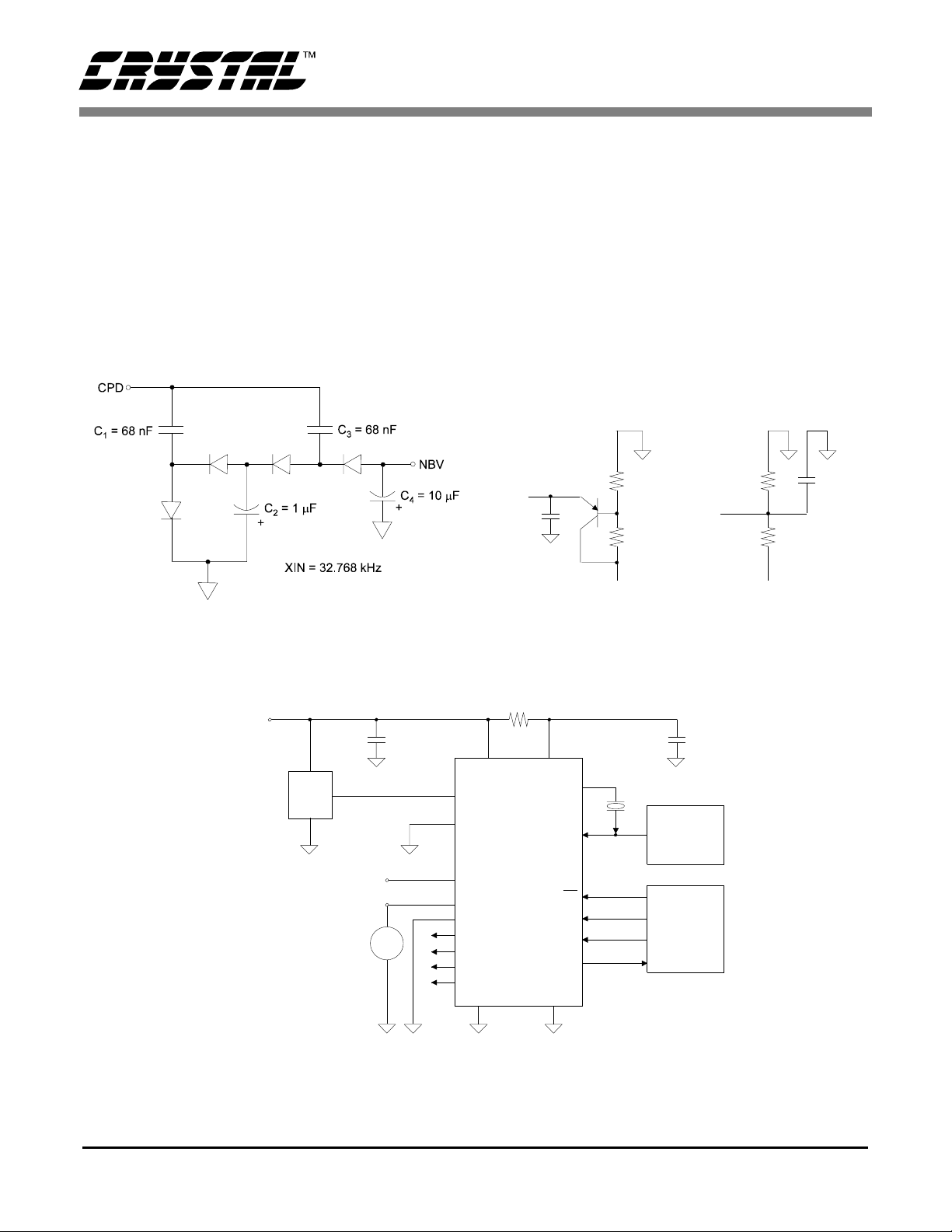

CPD

Differential

4th Order

Delta-Sigma

Modulator

Calibration µC

Copyright Cirrus Logic, I nc. 1998

Digital Filter

Clock

Gen.

XIN XOUT

(All Rights Reserv ed)

Calibration

Register

Control

Register

Output

Register

CS

SCLK

SDI

SDO

JAN ‘98

DS202F1

1

CS5525 CS5526

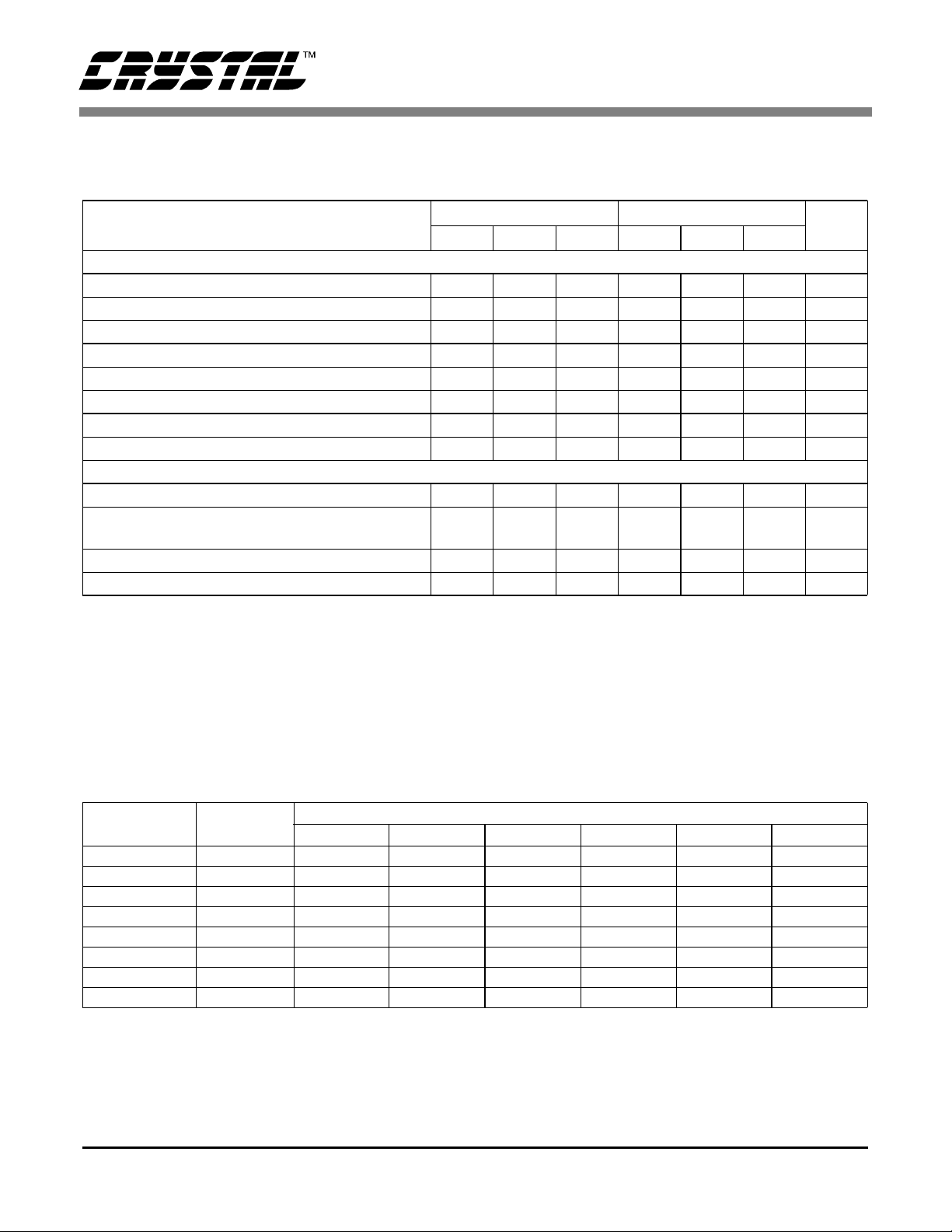

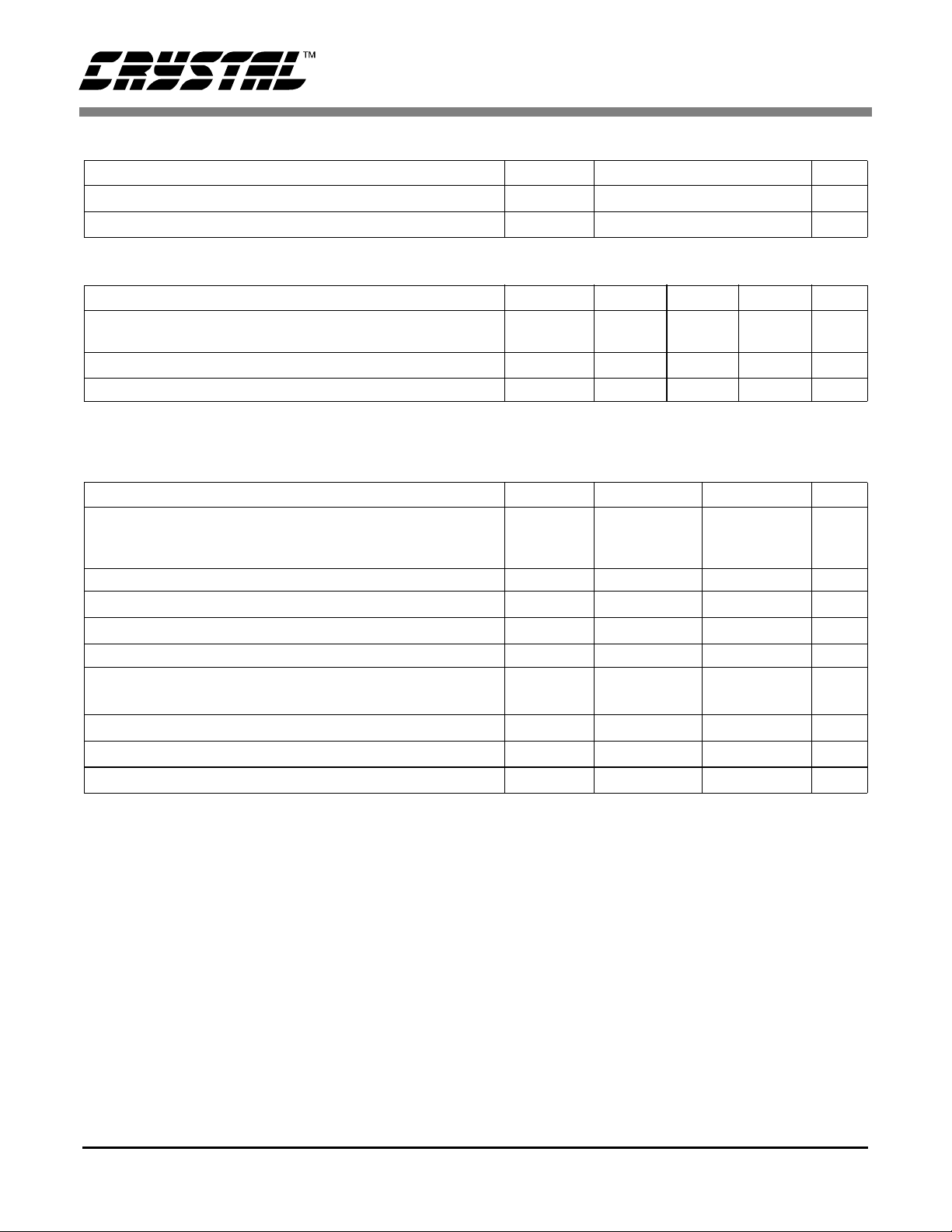

ANALOG CHARACTERISTICS (T

NBV = -2.1 V, FCLK = 32.768 kHz, OWR (Output Word Rate) = 15 Hz, Bipolar Mode, Input Range = ±100 mV;

See Notes 1 and 2.)

Parameter

= 25 °C; VA+, VD+ = 5 V ±5%; VREF+ = 2.5 V, VREF- = AGND,

A

CS5525 CS5526

Min T yp Max Min Typ Max Unit

Accuracy

Linearity Error No Missing Codes 16 - - 20 - - Bits

Bipolar Offset (Note 3) Unipolar Offset (Note 3) Offset Drift (Notes 3 and 4) - 20 - - 20 - nV/°C

Bipolar Gain Error Unipolar Gain Error Gain Drift (Note 4) - 1 3 - 1 3 ppm/°C

±

0.0015±0.003 -

±

1±2 -

±

2

±

8

±

16

±

4-±32

±

31 -

±

62 -

±

0.0007±0.0015 %FS

±

16 ±32 LSB

±

64 LSB

±

8

±

16

±

31 ppm

±

62 ppm

Voltage Reference Input

Range (VREF+) - (VREF-) 1 2.5 3.0 1 2.5 3.0 V

Common Mode Rejection dc

50, 60 Hz

Input Capacitance - 16 - - 16 - pF

CVF Current (Note 5) - 0.6 - - 0.6 - µA/V

-

-

110

130

-

-

-

-

110

130

-

-

dB

dB

Notes: 1. Applies after system calibration at any temperature within -40 °C ~ +85 °C.

2. Specification s gu aranteed by design, characterization, and/or test.

3. Specification applies to the device only and does not include any effects by external parasitic

thermocouples. LSB = LSB

4. Drift over specified temperature range after calibration at power-up at 25 °C.

5. See the section of the data sheet which discusses input models on page 15.

for the CS5525, and LSB20 for the CS5526.

16

RMS NOISE (Notes 6 and 7)

Output Rate

(Hz)

3.76 3.27 90 nV 90 nV 130 nV 1.0 µV 2.0 µV 4.0 µV

7.51 6.55 110 nV 130 nV 190 nV 1.5 µV 3.0 µV 7 µV

15.0 12.7 170 nV 200 nV 250 nV 2.0 µV 5.0 µV 10 µV

30.1 25.4 250 nV 300 nV 500 nV 4.0 µV 10 µV 15 µV

60.0 50.4 500 nV 1.0 µ V 1.5 µV 15 µV 45 µV 85 µV

123.2 (Note 8) 103.6 2.0 µV 4.0 µ V 8.0 µV 72 µV 190 µV 350 µV

168.9 (Note 8) 141.3 10 µV 20.0 µV 30 µV 340 µV 900 µV 2.0 mV

202.3 (Note 8) 169.2 30 µV 55 µV 105 µV 1.1 mV 2.4 mV 5.3 mV

Notes: 6. Wideband noise aliased int o the baseband. Referred to the input . Typical values shown for 25 °C.

7. For Peak-to-Peak Noise multipl y by 6.6 for all ranges and output rat es.

8. For input ranges <100 mV and output word rates >60 Hz, 32.768 kHz chopping frequency is used.

-3 dB Filter

Frequency

25 mV 55 mV 100 mV 1 V 2.5 V 5 V

Specifications are su bject to change without notice.

Input Range, (Bipolar/Unipolar Mode)

2 DS202F1

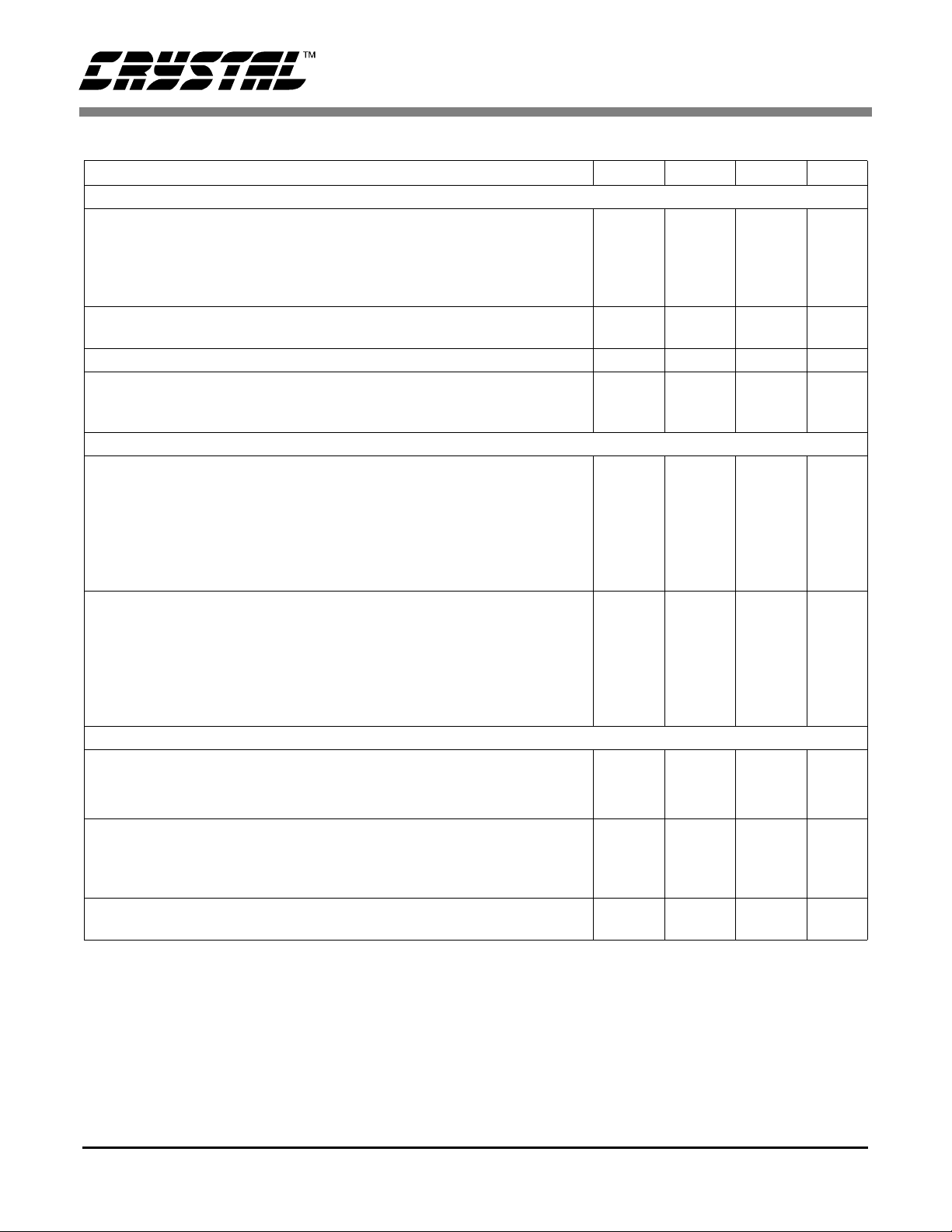

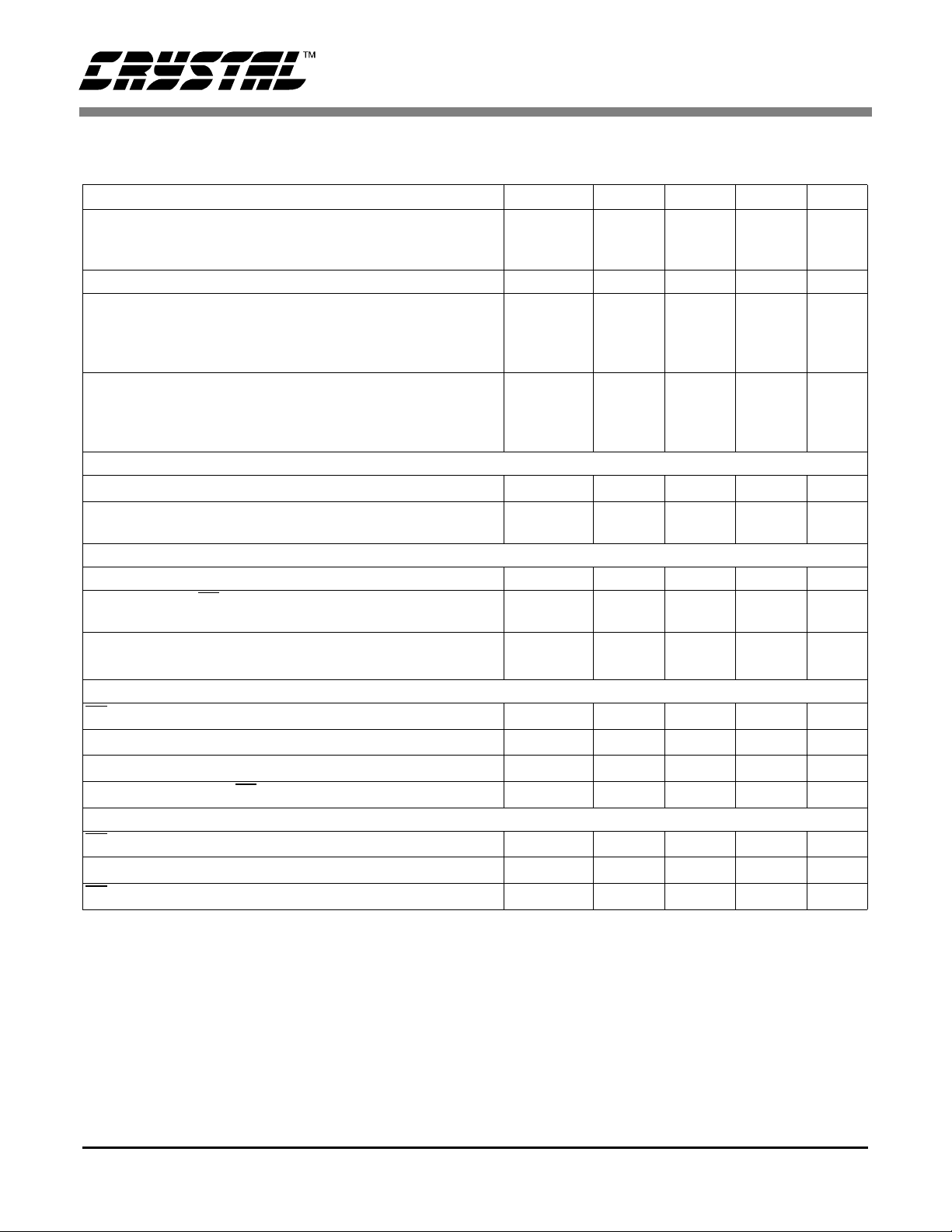

CS5525 CS5526

ANALOG CHARACTERISTICS (Continued)

Parameter Min Typ Max Unit

Analog Input

Common Mode + Signal on AIN+ or AIN- Bipolar/Unipolar Mode

NBV = -1.8 to -2.5 V Range = 25 mV , 55 mV, or 100 mV

Range = 1 V, 2.5 V, or 5 V

NBV = AGND Range = 25 mV, 55 mV, or 100 mV

Range = 1 V, 2.5 V, or 5 V

Common Mode Rejection dc

50, 60 Hz

Input Capacitance - 10 - pF

CVF Current on AIN+ or AIN- (Note 5)

Range = 25 mV, 55 mV, or 100 mV

Range = 1 V, 2.5 V, or 5 V

System Calibration Specifications

Full Scale Calibration Range Bipolar/Unipolar Mode (Note 9)

25 mV

55 mV

100 mV

1 V

2.5 V

5 V

Offset Calibration Range Bipolar/Unipolar Mode

25 mV

55 mV

100 mV (Note 10)

1 V

2.5 V

5 V

Power Supplies

DC Power Supply Currents (Normal Mode) I

Power Consumption Normal Mode (Note 11)

Low Power Mode

St andby

Sleep

Power Supply Rejection dc Positive Supplies

dc NBV

I

NBV

-0.150

NBV

1.85

0.0

-

-

-

-

17.5

38.5

70

0.70

1.75

3.50

-

-

-

-

-

-

A+

I

D+

-

-

-

-

-

-

-

-

-

-

-

-

-

120

120

100

1.2

-

-

-

-

-

-

-

-

-

-

-

-

1.3

15

400

7.5

4.0

1.2

500

95

110

0.950

VA+

2.65

VA+

-

-

300

-

32.5

71.5

105

dB

dB

pA

µA/V

mV

mV

mV

1.30

3.25

VA+

±12.5

±27.5

±50

mV

mV

mV

±0.5

±1.25

±2.50

1.7

30

550

10

6.5

-

-

-

-

mA

µA

µA

mW

mW

mW

µW

dB

dB

V

V

V

V

V

V

V

V

V

V

Notes: 9. The minimum Full Scale Calibration Range (FSCR) is limited by the maximum allowed gain register

value (with margin). The maximum FSCR is limited by the

∆Σ

modulator’s 1’s density range.

10. The maximum full scale signal can be limited by saturation of circuitry within the internal signal path.

11. All outputs unloaded. All input CMOS levels.

DS202F1 3

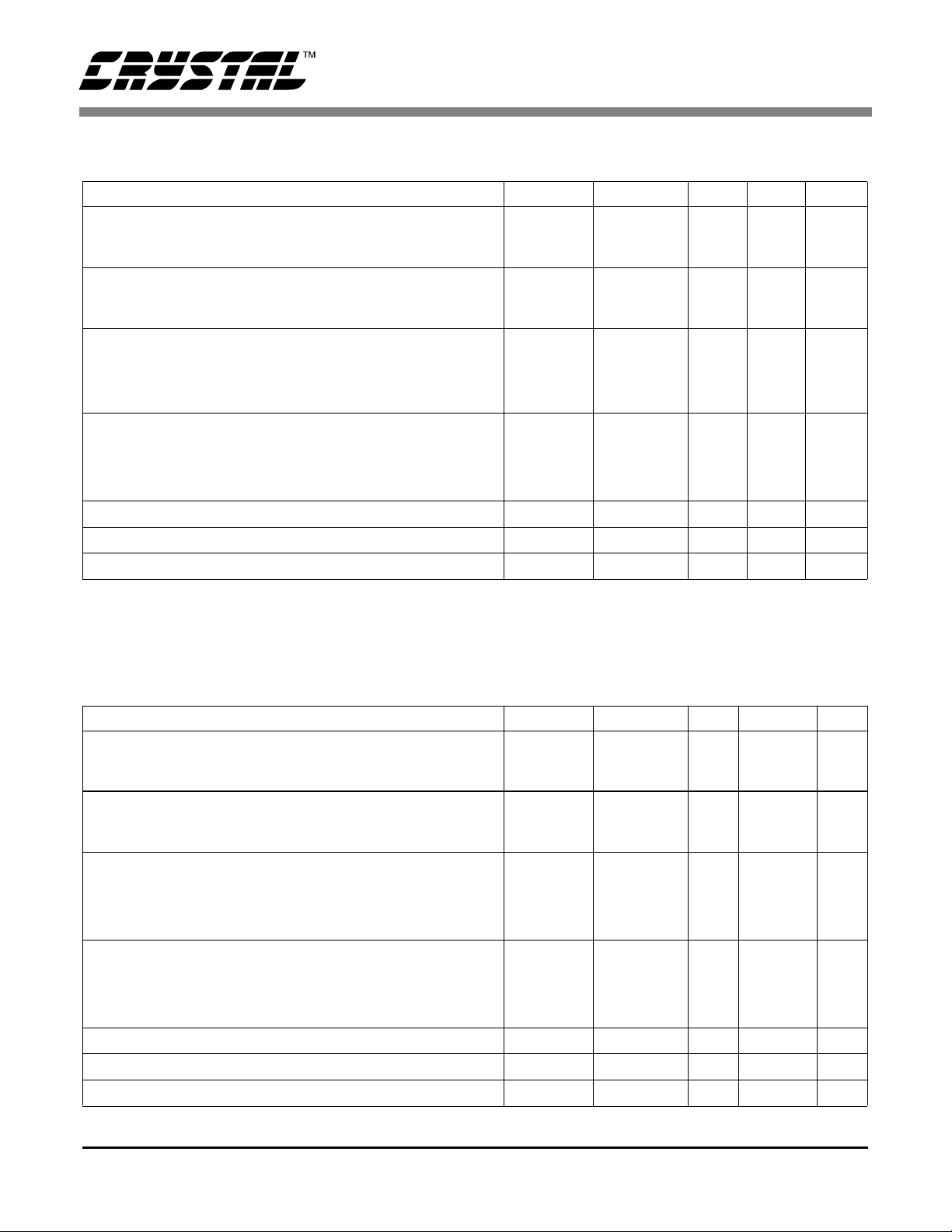

CS5525 CS5526

5 V DIGITAL CHARACTERISTICS (T

= 25 °C; VA+, VD+ = 5 V ±5%; GND = 0;

A

See Notes 2 and 12.))

Parameter Symbol Min Typ Max Unit

High-Level Input Voltage All Pins Except XIN and SCLK

XIN

SCLK

Low-Level Input Voltage All Pins Except XIN and SCLK

XIN

SCLK

High-Level Output Voltage

All Pins Except CPD and SDO (Note 13)

CPD, I

SDO, I

= -4.0 mA

out

= -5.0 mA

out

Low-Level Output Voltage

All Pins Except CPD and SDO, I

CPD, I

SDO, I

= 1.6 mA

out

= 2 mA

out

= 5.0 mA

out

Input Leakage Current I

3-State Leakage Current I

Digital Output Pin Capacitance C

V

IH

0.6 VD+

3.5

(VD+) - 0.4 5

V

IL

-

0.0

-

V

OH

(VA+) - 1.0

(VD+) - 1.0

(VD+) - 1.0

V

OL

-

-

-

in

OZ

out

-±1±10µA

--±10µA

-9-pF

-

-

-

-

-

-

-

-

-

-

-

-

-

VD+

-

0.8

1.5

0.6

-

-

-

0.4

0.4

0.4

V

V

V

V

V

V

V

V

V

V

V

V

Notes: 12. All measurements performed under static conditions.

13. I

3.0 V DIGITAL CHARACTERISTICS (T

= -100 µA unless stated otherwise. (VOH = 2.4 V @ I

out

= 25 °C; VA+ = 5 V ±5%; VD+ = 3.0 V ±10%; GND = 0;

A

See Notes 2 and 12.))

Parameter Symbol Min Typ Max Unit

High-Level Input Voltage All Pins Except XIN and SCLK

XIN

SCLK

Low-Level Input Voltage All Pins Except XIN and SCLK

XIN

SCLK

High-Level Output Voltage

All Pins Except CPD and SDO, I

CPD, I

SDO, I

= -400 µA

out

= -4.0 mA

out

= -5.0 mA

out

Low-Level Output Voltage

All Pins Except CPD and SDO, I

CPD, I

SDO, I

= 400 µA

out

= 2 mA

out

= 5.0 mA

out

Input Leakage Current I

3-State Leakage Current I

Digital Output Pin Capacitance C

out

V

IH

V

IL

V

OH

V

OL

in

OZ

out

= -40 µA.)

0.6 VD+

0.54 VA+

(VD+) - 0.4 5

0.0

(VA+) - 0.3

(VD+) - 1.0

(VD+) - 1.0

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

VD+

-

0.16 VD+

1.5

0.6

-

-

-

0.3

0.4

0.4

V

V

V

V

V

V

V

V

V

V

V

V

-±1±10µA

--±10µA

-9-pF

4 DS202F1

DYNAMIC CHARACTERISTICS

Parameter Symbol Ratio Unit

Modulator Sampling Frequency f

Filter Settling Time to 1/2 LSB (Full Scale S tep) t

CS5525 CS5526

s

s

XIN/2 Hz

1/f

out

s

RECOMMENDED OPERATING CONDITIONS

(AGND, DGND = 0 V; See Note 14.))

Parameter Symbol Min Typ Max Unit

DC Power Supplies Positive Digital

Positive Analog

Analog Reference Voltage (VREF+) - (VREF-) VRef

VD+

VA+

diff

2.7

4.75

5.0

5.0

5.25

5.25

1.0 2.5 3.0 V

V

V

Negative Bias Voltage NBV -1.8 -2.1 -2.5 V

Notes: 14. All voltages with respect to ground.

ABSOLUTE MAXIMUM RATINGS (AGND, DGND = 0 V; See Note 14.)

Parameter Symbol Min Max Unit

DC Power Supplies (Note 15)

Positive Digital

Positive Analog

Negative Bias Voltage Negative Potential NBV +0.3 -3.0 V

Input Current, Any Pin Except Supplies (Note 16 and 17) I

Output Current I

Power Dissipation (Note 18) PDN - 500 mW

Analog Input Voltage VREF pins

AIN Pins

Digital Input Voltage V

Ambient Operating Temperature T

Sto rage Temperature T

VD+

VA+

IN

OUT

V

INR

V

INA

IND

A

stg

-0.3

-0.3

+6.0

+6.0

V

V

-±10mA

-±25mA

-0.3

NBV - 0.3

(VA+) + 0.3

(VA+) + 0.3

V

V

-0.3 (VD+) + 0.3 V

-40 85 °C

-65 150 °C

Notes: 15. No pin should go more negative than NBV - 0.3 V.

16. Applies to all pins including continuous overvoltage conditions at the anal og input (AIN) pins.

17. Transient current of up to 100 mA will not cause SCR latch-up. Maximum input current for a power

supply pin is ±50 mA.

18. Total power dissipation, including all input currents and output currents.

WARNING: Operat ion at or beyond these limits may result in permanent damage to the device.

Normal operation is not guar anteed at these extremes.

DS202F1 5

CS5525 CS5526

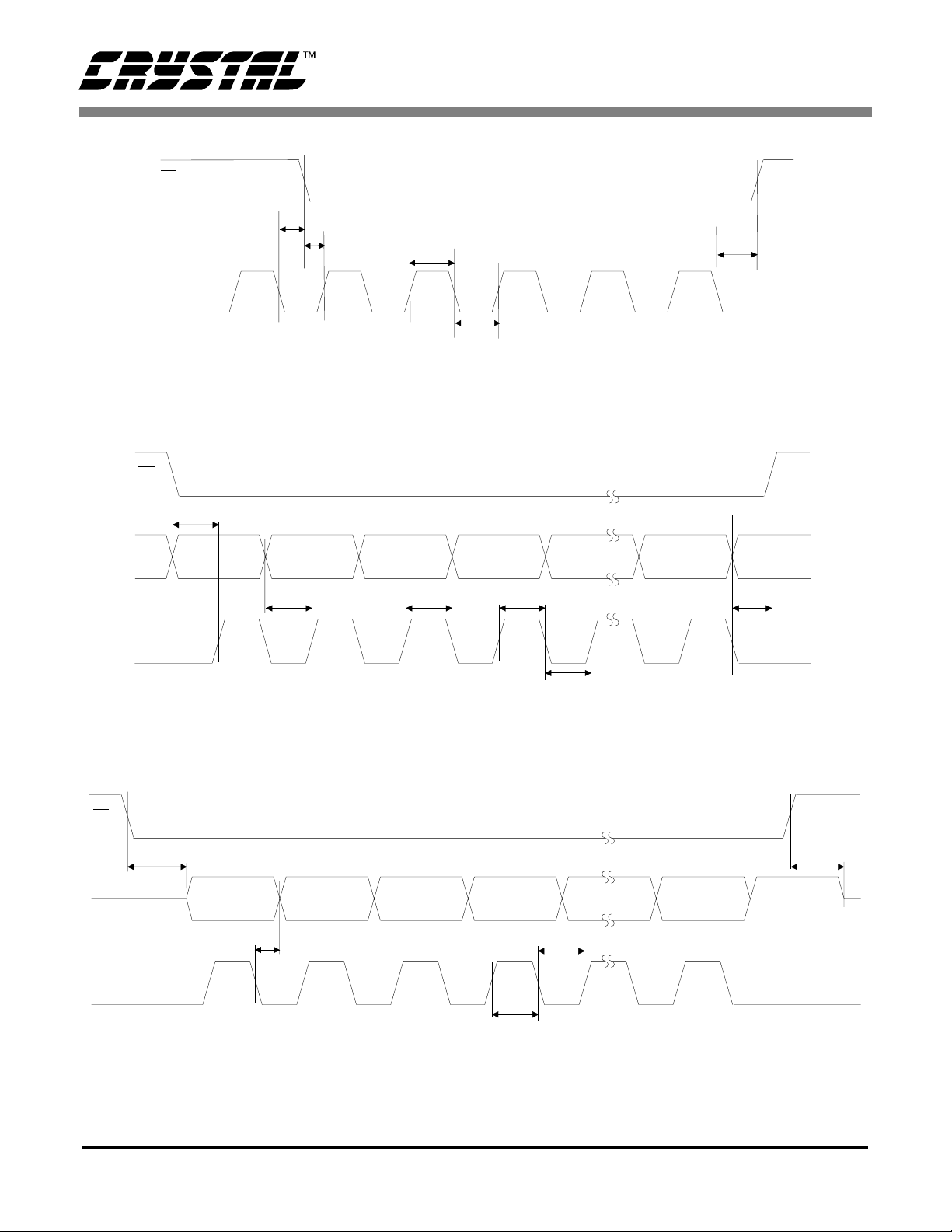

SWITCHING CHARACTERISTICS (T

Input Levels: Logic 0 = 0 V, Logic 1 = VD+; C

= 50 pF.))

L

= 25 °C; VA+ = 5 V ±5%; VD+ = 3.0 V ±10% or 5 V ± 5%;

A

Parameter Symbol Min Typ Max Unit

Master Clock Frequency (Note 19)

Internal Clock

External Clock

XIN

30

30

32.768

32.768

36

100

kHz

Master Clock Duty Cycle 40 - 60 %

Rise Times (Note 20)

Any Digital Input Except SCLK

SCLK

Any Digital Output

Fall Times (Note 20)

Any Digital Input Except SCLK

SCLK

Any Digital Output

t

t

rise

fall

-

-

-

-

-

-

50

50

-

-

-

-

1.0

100

-

1.0

100

-

µs

µs

ns

µs

µs

ns

Start-up

Oscillator Start-up Time XTAL = 32.768 kHz (Note 21) t

Power-on Reset Period t

ost

por

- 500 - ms

- 1003 - XIN

cycles

Serial Port Timing

Serial Clock Frequency SCLK 0 - 2 MHz

SCLK Falling to CS

Falling for continuous running SCLK

t

0

100 - - ns

(Note 22)

Serial Clock Pulse Width High

Pulse Width Low

t

1

t

2

250

250

-

-

-

-

ns

ns

SDI Write Timing

CS Enable to Valid Latch Clock t

Data Set-up Time pr io r to S C L K rising t

Data Hold Time After SCLK Rising t

SCLK Falling Prior to CS

Disable t

3

4

5

6

50 - - ns

50 - - ns

100 - - ns

100 - - ns

SDO Read Timi ng

CS to Data Valid t

SCLK Falling to New Data Bit t

Rising to SDO Hi-Z t

CS

7

8

9

- - 150 ns

- - 150 ns

- - 150 ns

Notes: 19. Device parameters are specified with a 32.768 kHz clock; however , clocks up to 100 kHz can be used

for increased th roughput.

20. Specified using 10% and 90% points on waveform of interest. Output loaded with 50 pF.

21. Oscillator start-up time varie s wi th cr yst al par ameter s. Thi s s pecifi cati on do es not appl y when using an

external clock source.

22. Applicable when SCLK is cont inuously running.

6 DS202F1

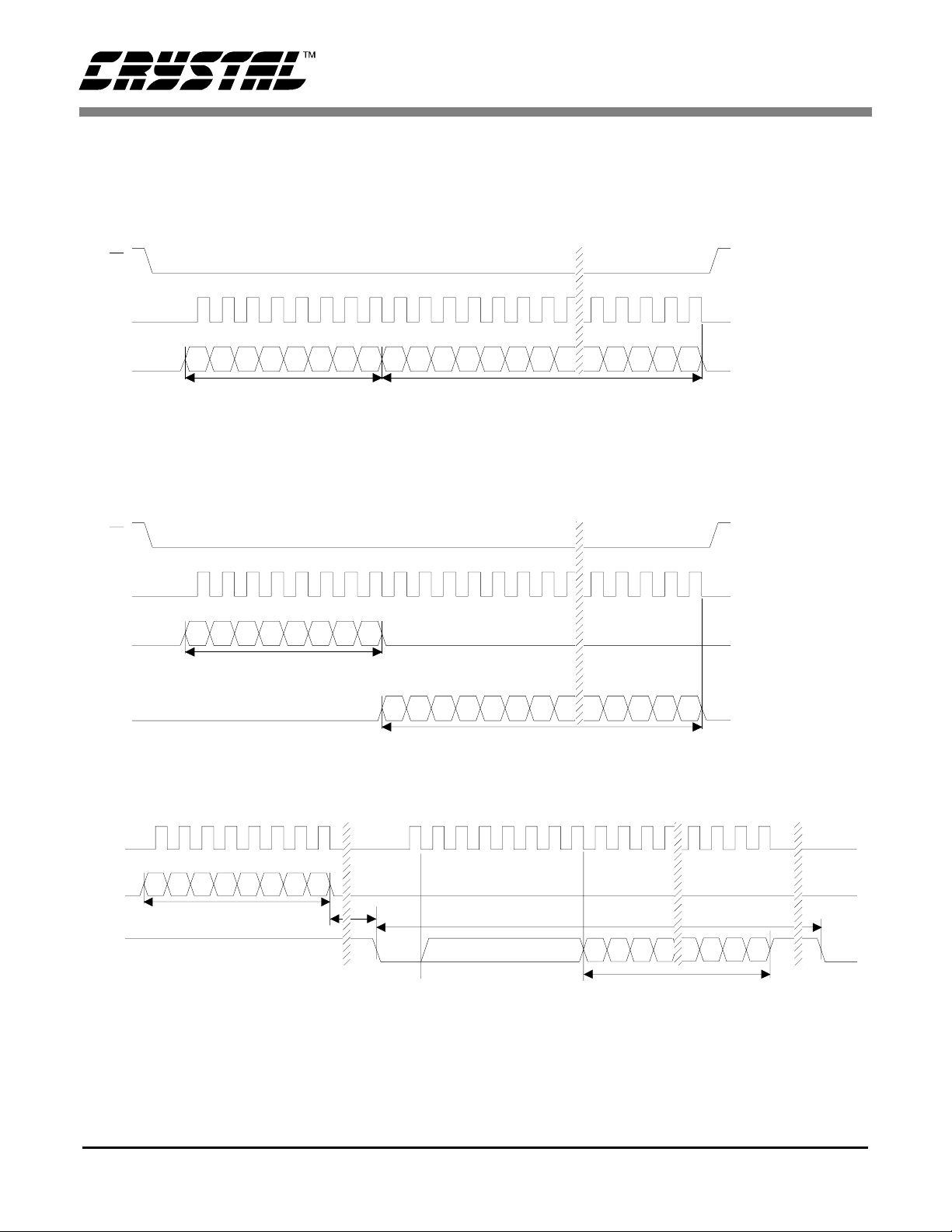

CS

CS

SCLK

CS5525 CS5526

t

0

t

t

t

3

1

t

2

Continuous Running SCLK Timing (Not to Scale)

t

3

6

CS

SDO

SCLK

SCLK

t

7

MSB

MSB

MSB-1 LSBSDI

t

4

t

5

t

1

t

2

t

6

SDI Write Timing (Not to Scale)

t

9

MSB-1 LSB

t

8

t

2

t

1

SDO Read Timing (Not to Scal e)

DS202F1 7

CS5525 CS5526

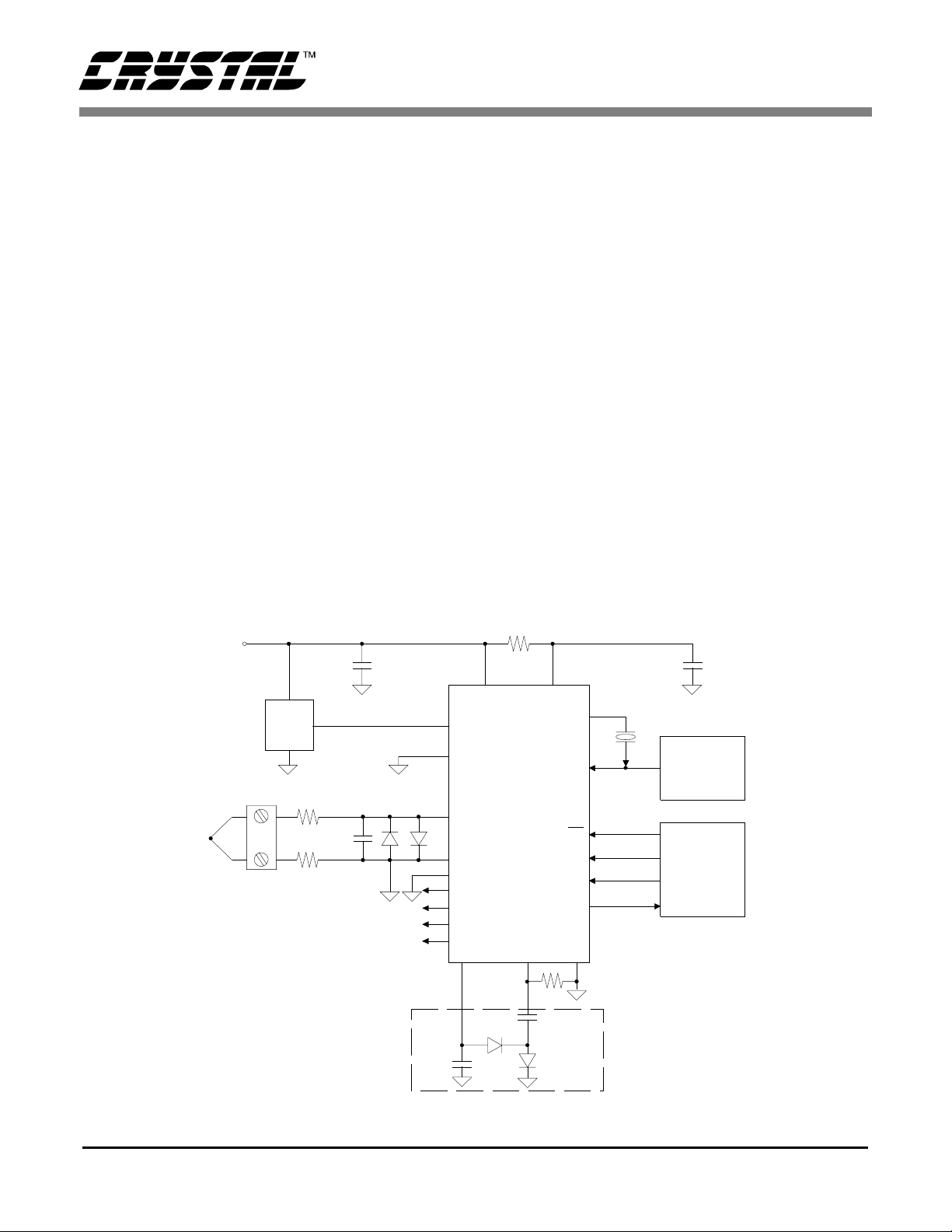

GENERAL DESCRIPTION

The CS5525 and CS55 26 ar e 16 -bit an d 20- bit pin

compatible converters which include a chopperstabilized instrumentation amplifier input, and an

on-chip programmable gain amplifier. They are

both optimized for measuring low-level unipolar or

bipolar signals in pro cess control and med ical applicatio ns .

The CS552 5/26 also include a fou rth order deltasigma modulator, a calibration microcontroller,

eight digital filters, a 4-bit analog latch, and a serial

port. The digital fil ters provide an y one of ei ght

different outpu t update rates.

The CS5525/26 include a CPD (Charge Pump

Drive) output (shown in Figure 1). CPD provides a

negative bias voltage to the on-chip instrumentation amplifier when used with a combination of external diodes and capacitors. This enables the

CS5525/26 to me asure negative voltag es with re-

spect to ground, making the converters ideal for

thermocou p l e te mperature measurement s .

Theory of Operation

The CS5525/26 A/D converters are designed to operate from a single +5 V analog supply and provide

several different input ranges. See the Analog

Characteristics section on page 3 for details.

Figure 1 illustrates the CS5525/26 connected to

generate their o wn negative bias supply using the

on-chip CPD (Charge Pump Drive). This enables

the CS5525/ 26 to measure ground referenc ed signals with magnitudes down to NBV (Negative Bias

Voltage, approximately -2.1 V in this example).

Figure 2 illustrates a charge pump circuit when the

converters are p owered from a +3.0 V di gital sup ply. Alternative ly, the ne gative bi as supply c an be

generated from a negative supply voltage or a resistive divider as illustrated in Fig ure 3.

+5V

Analog

Supply

2.5V

Up to ± 100 mV Input

10 k

Ω

0.1 µF

Ω

10 k

Note: Cold-junction

measurement is performed

by a second A/D or via a

multiplexer.

Logic Outputs:

A0 - A3 Switch from VA+ to AGND.

0.1 µF0.1

BAV199

20

19

3

4

1

16

15

7

6

10 µF

10

Ω

213

VA+

VREF+

VREF-

AIN+

AINAGND

A3

A2

A1

A0

1N4148

+

VD+

CS5525

CS5526

CPD

8

*5MΩ

0.015 µF

1N4148

XOUT

XIN

CS

SCLK

SDI

SDO

DGNDNBV

10

32.768 ~ 100 kHz

9

18

11

17

14

125

*

Optional, see Charge

Pump Drive section.

Charg e-pump ne twork

for VD+ = 5V only and

XIN = 32.768 kHz.

Optional

Source

Serial

Interface

µ

F

Clock

Data

Figure 1. CS5525/26 Configured to use on-chip charge pump to supply NBV.

8 DS202F1

CS5525 CS5526

F

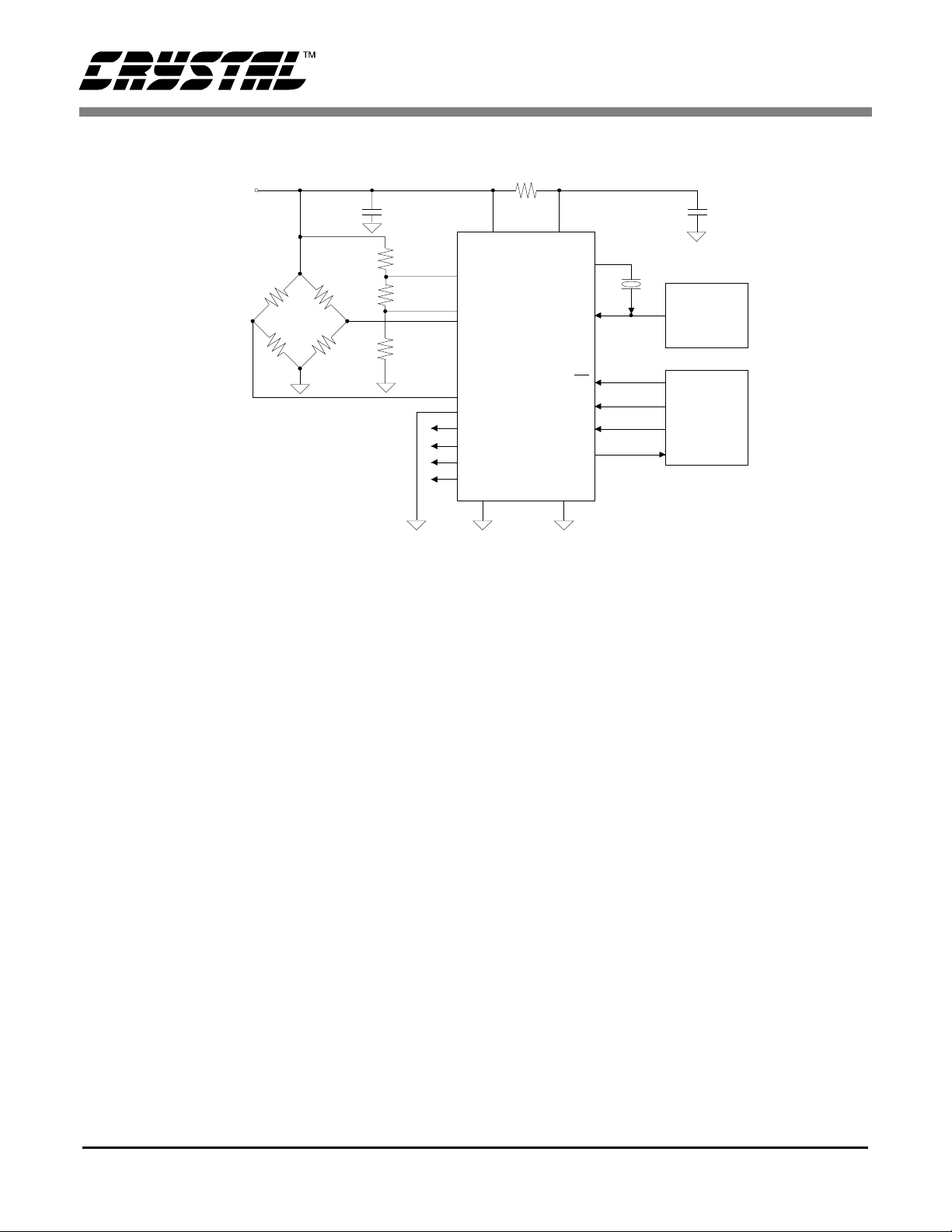

Figure 4 illustrates the CS5525/26 connected to

measure ground referenced unipolar signals of a

positive polarity using the 1 V, 2.5 V, and 5 V input

voltage ranges on the converter. For the 25 mV, 55

mV, and 100 mV ranges the signal must have a

common mo de nea r +2.5 V (NBV = 0V).

The CS5525/26 are optimized for the measurement

of thermocouple outputs, but they are also well

suited for the measurement of ratiometric bridge

transducer outputs. Figure 5 illustrates the

CS5525/26 c onnected to measure the output of a

ratiometric differential bridge transducer while operating from a single +5 V supply .

2N5087

or similar

NBV

10µF

+

Figure 2. Charge Pump Drive Circuit for VD+ = 3 V. Figure 3. Alternate NBV Circuits.

-5V

34.8K

30.1K

2.0K

NBV

2.1K

-5V

+

10

µ

10

+5V

Analog

Supply

2.5V

0 to +5V Input

CM = 0 to VA+

0.1 µF

+

-

20

19

3

4

1

16

15

7

6

VREF+

VREF-

AIN+

AIN-

AGND

A3

A2

A1

A0

Ω

213

VA+

5

CS5525

CS5526

CPD

8

VD+

XOUT

XIN

CS

SCLK

SDI

SDO

DGNDNBV

12

10

32.768 ~ 100 kHz

9

18

11

17

14

0.1

Optional

Clock

Source

Serial

Data

Interface

Figure 4. CS5525/26 Configured for ground-referenced Unipolar Signals.

µ

F

DS202F1 9

+5V

Analog

Supply

CS5525 CS5526

10

Ω

0.1 µF

213

CS5525

CS5526

CPD

8

VD+

XOUT

SCLK

SDO

DGNDNBV

XIN

CS

SDI

12

10

32.768 ~ 100kHz

9

18

11

17

14

VA+

20

VREF+

19

30mV

F.S.

+

3

16

15

7

6

4

1

VREFAIN+

AINAGND

A3

A2

A1

A0

5

0.1 µF

Optional

Clock

Source

Serial

Data

Interface

Figure 5. CS5525/26 Configured for Single Supply Bridge Measurement.

System Initialization

When powe r t o the CS5525/26 is ap pl ie d, they are

held in a reset cond ition until their 32 .768 kHz oscillators have started and their start-up counter-timer elapses. Due to the high Q of a 32.768 kHz

crystal, the oscillators take 400-600 ms to start. The

converter’s counter-timer counts no more than

1024 oscillator clock cycles to make sure the oscillator is fully stable. During this time-out period the

serial port logic is reset and the RV (Re set Valid)

bit in the configuration register is set. A reset can be

initiate d at an y tim e by wri ti ng a l og ic 1 t o the R S

(Reset System) bit in the configuration register.

This aut omatic all y sets th e RV bit u ntil th e RS b it

is writte n to lo gic 0, and the c on fig ura tion regi st er

is read. After a reset, the on-chip registers are initialized to the following s tates and the conv erters

are ready to perform conversion s.

Command Operation

The CS5525/26 include a microcontroller with five

registers used t o co ntr ol th e conve rter. Ea ch regi ster is 24-bits in length except the 8 -bit command

register (command, configuration, offset, gain, and

conversion data). After a system initialization or reset, the serial port is initialized to the command

mode and t he converter stays in thi s mode until a

valid 8-bit command is received (the first 8-bits

into the serial port). Table 1 lists all t h e va lid commands. Once a valid 8-bit command (a read or a

write comma nd word) is received and i nterpreted

by the comma nd register, the seria l port ent ers the

data mode. In data mode the next 24 serial clock

pulses shift data e it he r i nto or out of the se rial port

(72 serial clock pul ses a re needed if set- up re gi ster

is selected). See Table 2 for configuring the

CS5525/26.

configuration register: 000040(H)

offset register: 000000(H)

gain register: 800000(H)

10 DS202F1

CS5525 CS5526

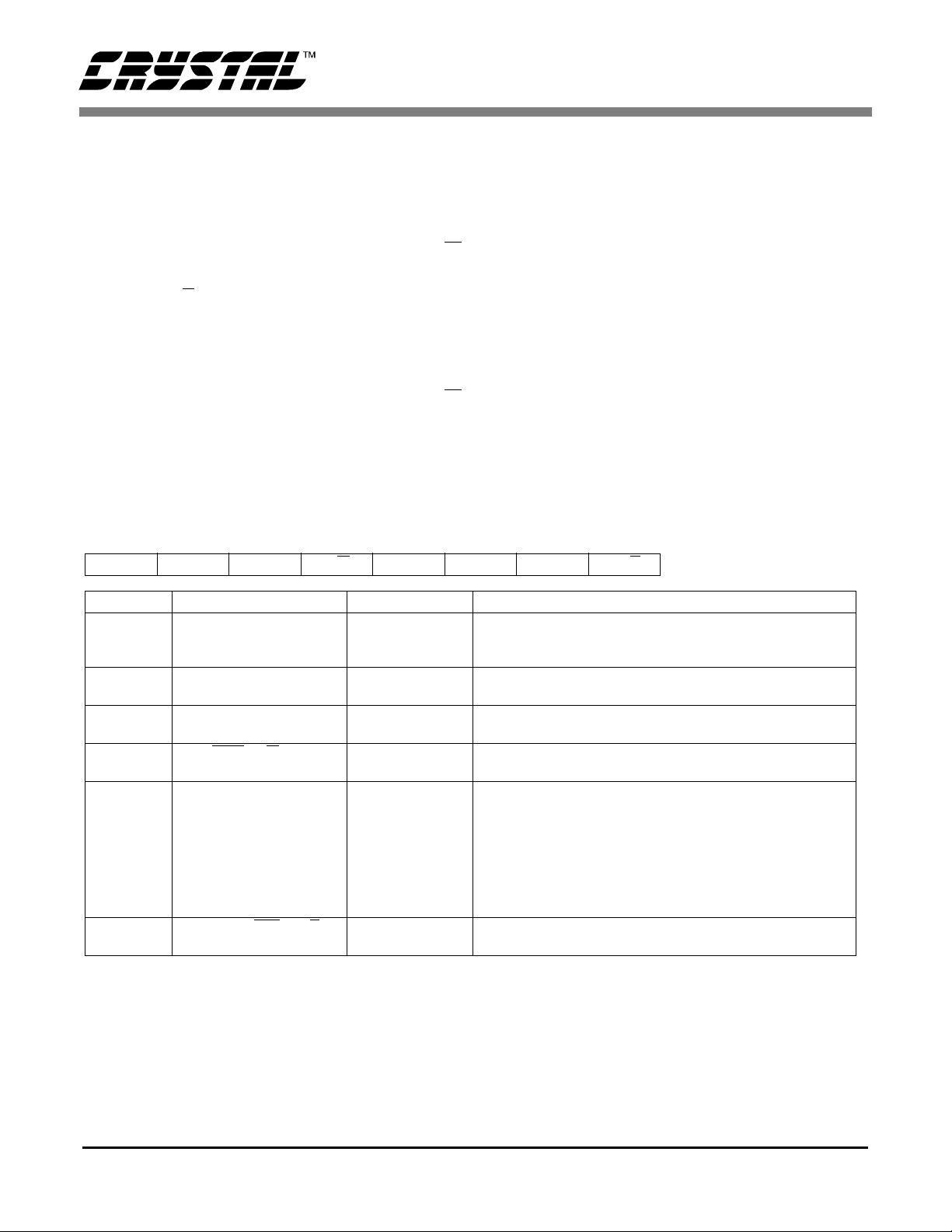

Reading/Writing On-Chip Registers

The CS5525/26’s offset, gain, and configuration

registers are read/writable while the conversion

data register is read only.

CC, and PS/R bi ts must be logic 0 and the CB (MSB)

bit must be a logi c 1. The r egister to be written is selected with the RSB2-RSB0 bits of the command

word. Figure 6 illustrates the serial sequence necessary to write to, or read from the serial port.

To perform a read from a specific register, the R/W

bit of the command word must be a logic 1. The SC,

CC, and PS/R

bits must be logic 0 and the CB

(MSB) bit must be a logic 1. The register to be written is selected with the RSB2-RSB0 bits of the

command word.

If the Set -up R egist ers ar e ch osen wi th t he R SB2RSB0 bits, the re gisters are re ad or written in t he

following sequ ence: Offset, Gain and Config uration. Th is is a ccomp lish ed by follow ing o ne 8-b it

command word with three 2 4-bit data words for a

total of 72 dat a bits.

To perform a writ e to a specific registe r, the R/W

bit of the command word must be a lo gic 0. The SC,

Command Register

D7(MSB)D6D5D4D3D2D1D0

CB SC CC R/W RSB2 RSB1 RSB0 PS/R

BIT NAME VALUE FUNCTION

D7 Command Bit, CB 0

D6 Single Conversion, SC 0

D5 Continuous Conversions,

CC

D4 Read/Write, R/W 0

D3-D1 Register Select Bit,

RSB2-RSB0

D0 Power Save/Run, PS/R 0

000

001

010

011

100

101

110

111

Table 1. Command Set

1

1

0

1

1

1

Null command (no operation). All command bits, including

CB must be 0.

Logic 1 for executable commands.

Single Conversion not active.

Perform a conversion.

Continuous Conversions not active.

Perform conversions continuously.

Write to selected register.

Read from selected register.

Offset Register

Gain Register

Configuration Register

Conversion Data Register (read only)

Set-up Registers (Offset, Gain, Configuration)

Reserved

Reserved

Reserved

Run

Power Save

DS202F1 11

CS5525 CS5526

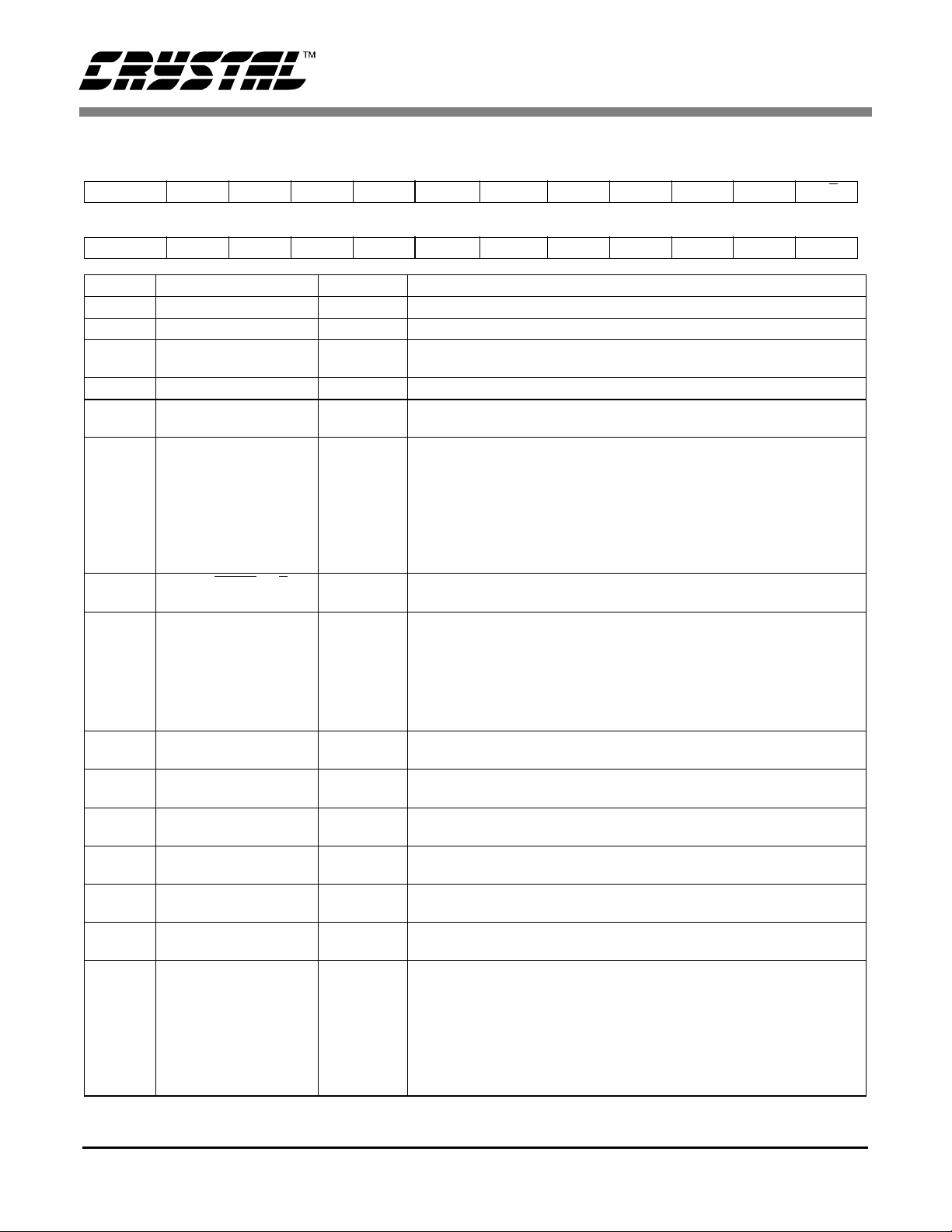

Confi

guration Register

D23(MSB) D22 D21 D20 D19 D1 8 D17 D16 D15 D14 D13 D12

A3 A2 A1 A0 NU CFS NU LPM WR2 WR1 WR0 U/B

D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

G2 G1 G0 PD RS RV PF PSS DF CC2 CC1 CC0

BIT NAME VALUE FUNCTION

D23-D20 Latch Outputs, A3-A0 0000 R* L atch Output Pins A3-A0 mimic the D23-D20 Register bits.

D19 Not Used, NU 0 R Must always be logic 0.

D18 Chop Frequency Select,

CFS

D17 Not Used, NU 0 R Must always be logic 0.

D16 Low Power Mode, LPM 0

D15-D13 Word Rate, WR2-0

Note: For

XIN = 32.768kHz

D12 Unipolar/Bipolar, U/B 0

D11-D9 Gain Bits, G2-G0 000

D8 Pump Disable, PD 0

D7 Reset System, RS 0

D6 Reset Valid , RV 0

D5 Port Flag, PF 0

D4 Power Save Select, PSS 0

D3 Done Flag, DF 0

D2-D0 Ca libration Control Bits,

CC2-CC0

0

1

1

000

001

010

011

100

101

110

111

1

001

010

011

100

101

110/111

1

1

1R

1

1

1

000

001

010

011

100

101

110

111

R 256 Hz Amplifier chop frequency

32768 Hz Amplifier chop frequency

R Normal Mode

Reduced Power mode

R 15.0 Hz (2182 XIN cycles)

30.1 Hz (1090 XIN cycles)

60.0 Hz (546 XIN cycles)

123.2 Hz (266 XIN cycles)

168.9 Hz (194 XIN cycles)

202.3 Hz (162 XIN cycles)

3.76 Hz (8722 XIN cycles)

7.51 Hz (4362 XIN cycles)

R Bipolar Measurement mode

Unipolar Measurement mode

R 100 mV (assumes VREF = 2.5V)

55 mV

25 mV

1V

5.0 V

2.5 V

Not Used.

R Charge Pump Enabled

For PD = 1, the CPD pin goes to a Hi-Z output state.

R Normal Operation

Activate a Reset cycle. To return to Normal Operation write bit to zero.

No reset has occurred or bit has been cleared (read only).

Valid Reset has occurred. (Cleared when read.)

R Port Flag mode inactive

Port Flag mode active

R Standby Mode (Oscillator active, allows quick power-up)

Sleep Mode (Oscillator inactive)

R Done Flag bit is cleared (read only).

Calibration or Conversion cycle completed (read only).

R Normal Operation (no calibration)

Offset -- Self-Calibration

Gain -- Self-Calibration

Offset Self-Calibration followed by Gain Self-Calibration

Not used.

Offset -- System Calibration

Gain -- System Calibration

Not Used.

* R indicates the bit value after the part is reset

Table 2. Configuration Register

12 DS202F1

CS

SCLK

CS5525 CS5526

SDI

CS

SCLK

SDI

SDO

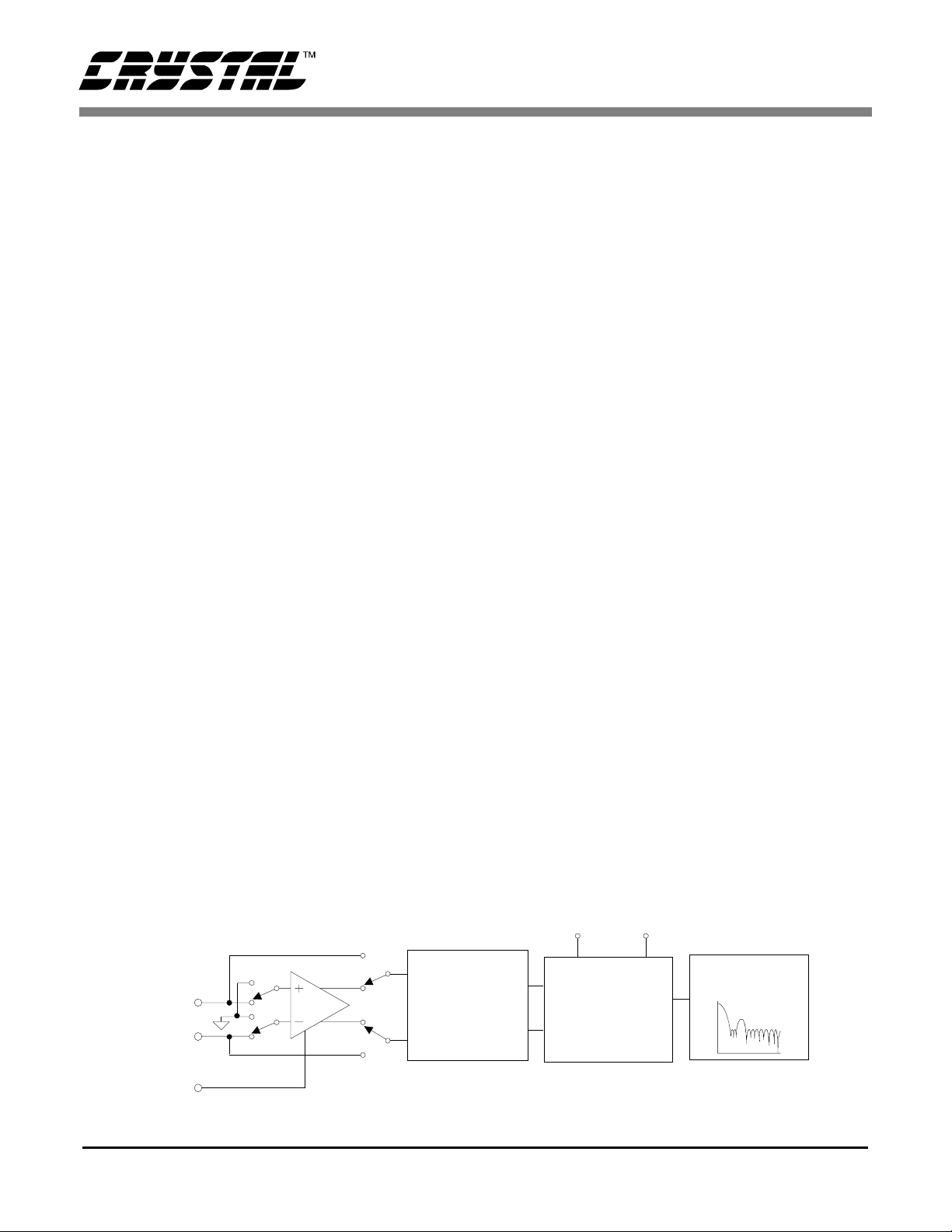

Command Time

8 SCLKs

Command Time

8 SCLKs

MSB

Write Cycle

MSB

Read Cycle

LSB

Data Time 24 SCLKs

(or 72 SCLKs for Set-up Registers)

LSB

Data Time 24 SCLKs

(or 72 SCLKs for Set-up Registers)

SCLK

SDI

t *

Command Time

8 SCLKs

SDO

* td = XIN/OWR clock cycles for each conversion except the

first conversion which will take XIN/OWR + 7 clock cycles

d

SDO Continuous Conversion Read (PF bit = 1)

8 SCLK s Clear SDO Flag

MSB

Data Time

24 SCLKs

XIN/OWR

Clock Cycles

LSB

Figure 6. Command and Data Word Timing.

DS202F1 13

CS5525 CS5526

Analog Input

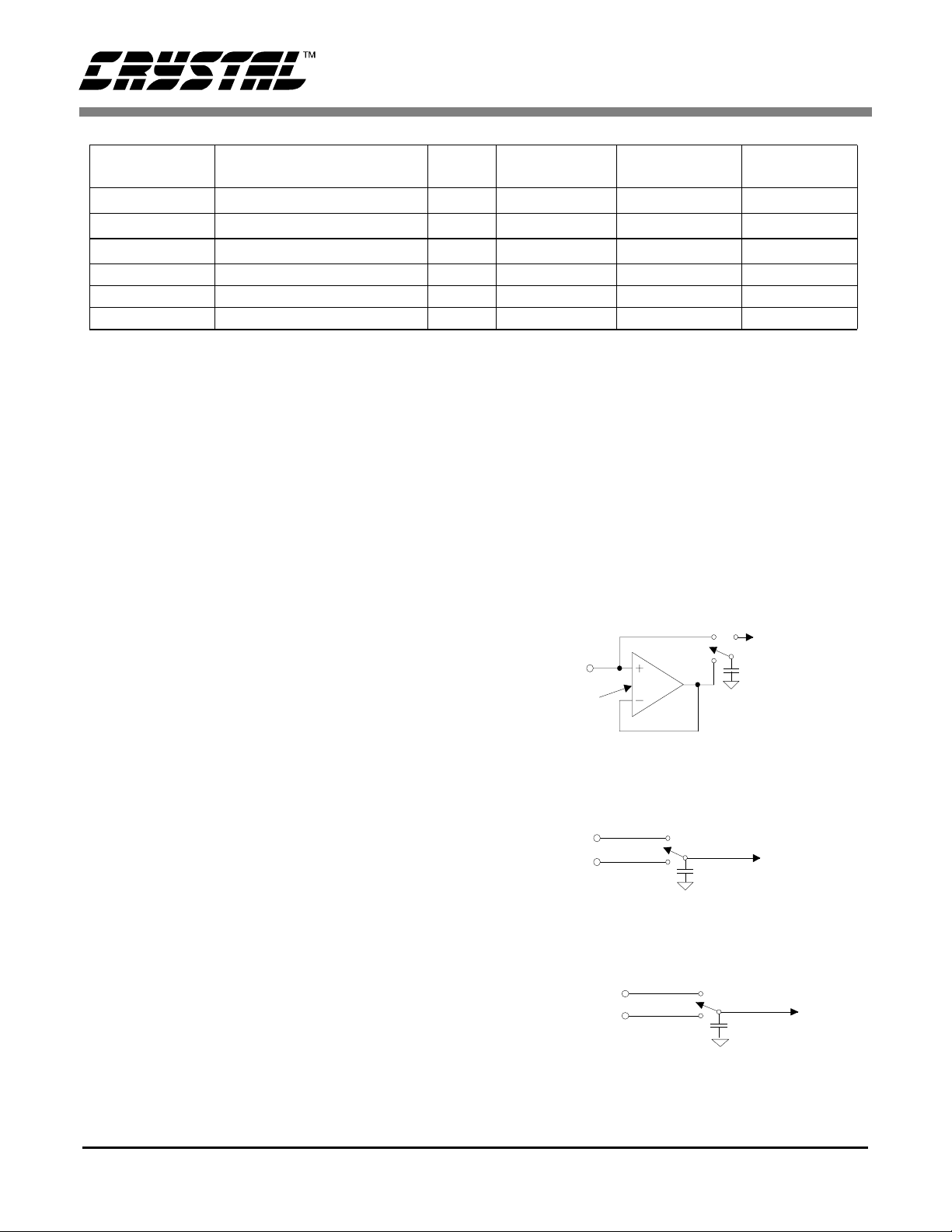

Figure 7 illustr ates a blo ck diagr am of t he analog input signal path inside the CS5525/26. The front end

consists of a chopper-stabilized instrumentation amplifier with 20X gain and a programmable gain section. The instrumentation amplifie r is powered from

VA+ and from the NBV (Negative Bias Volt age) pin

allowing the CS5525/26 to be operated in either of

two analog input configurations. The NBV pin can

be biased to a negative voltage between -1.8 V and

-2.5 V, or tied to AGND. The choice of the operating

mode for the NBV voltage depends upon the input

signal and its common mode voltage.

For the 25 mV, 55 mV, and 100 mV input ranges, the

input signals to AIN+ and AIN- are amplified by the

20X instrumentation amplifier. For ground referenced signals with magnitudes less then 100 mV, the

NBV pin should be biased with -1.8 V to -2.5 V. If

NBV is tied between -1. 8 V and -2.5 V, the (Com mon Mode + Signal) input on AIN+ and AIN- must

stay between -0.150 V and 0.950 V to ensure proper operation. Alternatively, NBV can be tied to

AGND where the input (Common Mode + Signal)

on AIN+ and AIN- must stay b etween 1.85 V and

2.65 V to ensure tha t the ampl ifier ope rates prop erly.

For the 1 V, 2.5 V, and 5 V input ranges, the instrumentation amplifi er is bypassed and the input signals are directly connected to the Programmable

Gain block. With NBV tied between -1.8 V and

-2.5 V, the (Common Mode + Signal) input on

AIN+ and AIN- must stay between NBV and VA+.

Alternatively, NBV can be tied to AGND where

the input (Com mon Mode + Sig nal) on AIN+ and

AIN- pins can span the entire range between

AGND and VA+.

The CS5525/26 can accommodate full scale ranges

other than 25 mV, 55 mV, 100 mV, 1 V, 2.5 V and

5 V by performin g a syste m calibr ation wi thin the

limits specified. See the Calibration section fo r

more details. Another way to change the full scale

range is to increase or to decrease the voltage reference to ot her than 2.5 V. Se e the Vo ltage Refer-

ence sectio n for more detail s.

Three factor s set the op erating limits for t he input

span. They include: instrumentation amplifier satu-

ration, modulator 1’s density, and a lower reference

voltage. When the 25 mV, 55 mV or 100 mV range

is selected, the input signal (including the common

mode voltage and the amplifier offset voltage)

must not caus e the 20 X amp lifier to saturat e in ei ther its inp ut s tag e o r outpu t s tage . To pre vent sat uration the absolute voltages on AIN+ and AINmust stay within the limits specified (refer to the

‘Analog Input’ table on pag e 3). Addit ional ly, t he

differential output voltage of the amplifier must not

exceed 2.8 V. The equation

ABS(VIN + VOS) x 20 = 2.8 V

defines the diffe rential output li mit, where

VIN = (AIN+) - (AIN-)

is the differentia l input volt age and VOS is the absolute maximum offset voltage for the instrumentation amplifier (VOS will not exceed 40 mV). If the

VREF+

AIN+

AIN-

NBV

14 DS202F1

X20

Figure 7. Block Diagram of Analog Signal Path

Programmable

Gain

Differential 4th

order delta-

sigma modulator

VREF-

Digital Filter

CS5525 CS5526

F

Input Range

± 25 mV

± 55 mV

± 100 mV

± 1.0 V - 2.5V 2.5 ± 1.0 V ± 1.5 V

± 2.5 V - 2.5V 1.0 ± 2.5 V ± 5.0 V

± 5.0 V - 2.5V 0.5 ± 5.0 V 0V, VA+

Note: 1. The converter ’s actual input range, the delta-sigma’s nominal full scale input, and the delta-sigma’s

(1)

maximum full scale input all scale directly with the value of the voltage reference. The values in the

table assume a 2.5 V VREF voltage.

Table 3. Relationship between Full Scale Input, Gain Factors, and Internal Analog Signal Limitations

differential output voltage from the amplifier exceeds 2.8 V, the amplifier may saturate, which will

cause a measure ment error.

The input voltage into the modulator must not

cause the mo dulat or to exce ed a lo w of 20 perce nt

or a high of 80 percent 1’s density. The nominal full

scale input span of the modu lator (from 3 0 pe rcent

Max. Differential Output

20X Amplifier

(2)

2.8 V

(2)

2.8 V

(2)

2.8 V

VREF Gain Factor

2.5V 5 ± 0.5 V ± 0.75 V

2.5V 2.272727... ± 1.1 V ± 1.65 V

2.5V 1.25 ± 2.0 V ±3.0 V

Note: Residual nois e appear s in the conve rter’ s base band f or

output wor d rat es gr eater t han 60 Hz if CFS is logic 0. By s etting CFS to logic 1, the amplifier’s chop frequency chops at

32768 Hz eliminating the residual noise, but increasing the

current.

For physical inp ut capac itance see ‘Input Capac itance’ specification under ‘Analog Characteristics’ on page 3.

Note that C=48 pF is for i nput curr ent modeli ng only.

25mV, 55mV, and 100mV Ranges

∆-Σ Nominal

Differential Input

(1)

(1)

∆-Σ

Max. Input

to 70 percent 1’s density) is determined by the

VREF voltage divi de d by the Gain Factor. See Ta ble 3 to determine if the CS5525/26 are being used

properly. For example, in the 55 mV rang e to determine the nominal input voltage to the modulator,

divide VREF (2.5 V) by the Gain Factor (2.2727).

When a sma ller voltage referen ce is used, the re -

AIN

V ≤ 25mV

os

i = fV C

osn

CFS = 0 , f = 256 Hz

CFS = 1 , f = 32.768 kHz

C = 48p

sulting code widths are smaller causing the converter output codes to exhibit more changing codes

for a fixed amount of noi se. T able 3 i s based u pon

a VREF = 2.5 V. For other values of VREF, the values in Table 3 must be scale d a cc ordingly.

Figure’s 8 and 9 il lustrate the inp ut m odels f or t he

AIN and VREF pins. The dynamic input current for

each of the pins can be determined from the models

shown and is dependent upon the setting of the CFS

(Chop Frequency Select) bit. The effective input

AIN+

Figure 8. Input models for AIN+ and AIN- pins

1V, 2.5 V, and 5V Ranges

AIN-

i = [(V ) - (V )] fC

n

AIN+ AIN-

f = 32. 7 68 kH z

VREF+

VREF-

C = 32pF

C = 16pF

impedance for the AIN+ and AIN- pins remains

i = [(VREF+) - (VREF-)] fC

constant for the three low level measurement ranges (25 mV, 55 mV, and 100 mV). The input current

Figure 9. Input model for VREF+ and VREF- pins.

n

f = 32.768 kHz

is lowest w it h the CF S bit cleared to logic 0.

DS202F1 15

CS5525 CS5526

Charge Pump Drive

The CPD (Charge Pump Drive) pin of the converters can be used with ext ernal component s (shown

in Figure 1) to develop an appropriate negative bias

voltage for the NBV pin. When CPD is used to generate the N BV, the NBV vol tage is regul ated with

an internal regulator loop referenced to VA+.

Therefore, any change on VA + re s u lt s in a propor-

tional change on NBV. With VA+ = 5 V, NBV’s

regulation is set proportional to VA+ at approximately -2.1 V.

Figure 3 illustrates a means of supplying NBV voltage from a -5 V supply. For groun d based signals

with the instru mentation amplifie r engaged (w hen

in the 25mV, 55mV, or 100mV ranges), the voltage

on the NBV pin should at no t ime be l ess negati ve

than -1.8 V or m ore negati ve than - 2.5 V. To prevent excessive vol tage stress to the chip the NBV

voltage should not be more nega ti ve tha n -3. 0 V.

The components in Figure 1 are the preferred components for the CPD filter. H owever, smalle r capacitors ca n be used w ith accept able resul ts. The

µF ensures very low r ipple on NBV. Int rinsic

10

safety require ment s prohi bit th e u se o f ele ctrolyt ic

capacitors. In this case, two 0.47

itors in paralle l ca n be used.

The CPD pi n itself is a tri-s tate output and enters

tri-state whenever the converters are placed into the

Sleep Mode, Standby Mode, or when the charge

pump is disabled (when the Pump Disa ble bit, bit

D8 in the configuration register, is set). Once in tristate, the digital current can increase if this CPD

output floats near 1/2 digital supply. T o ensure the

CPD pin stays near ground and to minimize the

digital cur rent, a dd a 5MΩ re sistor be tween it and

DGND (see Figure 1). If the resistor is left out, the

digital supply current may increase from 2 µA to 10

µA.

µF ceramic capac-

Voltage Reference

The CS5525/ 26 are speci fied for ope ration wit h a

2.5 V reference voltage between the VREF+ and

VREF- pins of the devices. For a single-ended reference volta ge, such as t he LT1019-2 .5, the refer ence’s output is connected to the VREF+ pin of the

CS5525/26. The ground referenc e for the LT1019-

2.5 is connec te d to the VREF- pin.

The differential voltage between the VREF+ and

VREF- can be any vo lt age from 1.0 V up to 3.0 V,

however, the VRE F- pin can not go belo w analog

ground.

Calibration

The CS5525/26 offer five different calibration

functions including self calibration and system calibration. How ever, after the CS 5525/26 are reset,

they can perform measurements without being calibrated. In this case, th e convert ers will uti lize the

initialize d values of the on-chip regi sters (Gain =

1.0, Offset = 0.0) to ca lcula te out put wor ds for the

±

100 mV ra nge. Any in itial offset and g ain errors

in the internal circuitry of the chips will remain.

The gain and offset registers, which are used for

both self and system calibration, are used to set the

zero and full-scale points of the converter’s transfer

-24

-23

). The

i–

2

i

pro-

function. One LSB in the offset register is 2

portion of the input span (bipolar span is 2 times the

unipolar span). Th e MSB in the offset reg ister determines i f the offset to be trimmed is p ositive or

negative (0 positive, 1 negative). The converters

can typically trim ±50 percent of the input span.

The gain register spans from 0 to (2 - 2

decimal equ iva lent meaning of the gain regi ste r is

N

Db020b121–b222–…bN2

==

++++ b

N–

∑

i0=

where the binary numbers have a value of either

zero or one (b

4 for details.

Table

corresponds to the MSB ). Refer to

0

16 DS202F1

CS5525 CS5526

Offset Register

MSB LSB

-2

-3

-4

-5

Register

Reset (R) 0 00000 0 0 0 0 0 0

Sign

2

2

2

2

-6

2

-19

2

-20

2

-21

2

-22

2

-23

2

≈

-24

2

One LSB represents 2

-24

proportion of the input span (b ipolar span is 2 times unipolar span)

Offset and data word bits align by MSB (bit MSB-4 of offset register changes bit MSB-4 of data)

Gain Register

MSB LSB

0

-1

-2

-3

-4

Register

Reset (R) 1 00000 0 0 0 0 0 0

The gain register span is from 0 to (2-2

2

2

2

2

2

-23

). After Reset the MSB = 1, all other bits are 0.

-5

2

Table 3.

Table 4. Offset and Gain Registers

The offset and gain cal ibration steps each take one

conversion cycle to complete. At the end of the calibration step, the calibration control bits will be set

back to logic 0, and the DF (D one Flag) bit w il l be

set to a logic 1. For the combination self-calibration (CC2-CC0= 011; offset followed by gain), the

calibration will take two conversion cycles to complete and wil l set the DF bi t after t he gain c alibra tion is comple ted. The DF bit will be cl eared any

time the d ata register , the offset r egister, the gain

register, or the set up register is rea d. Reading the

configuration register alone will not clear the DF

bit.

-18

2

-19

2

-20

2

-21

2

-22

2

≈

of the modulat or are connected together and then

routed to the VREF - pin as shown i n Figure 11.

For self-calibrat ion of gain, the differentia l inputs

of the modulator are connected to VREF+ and

S1

OPEN

AIN+

AIN-

S2

CLOSED

+

X20

-

-23

2

+

-

Self Calibration

Figure 10. Self Calibration of Offset (Low Ranges).

The CS5525/ 26 offer b oth sel f o ffset a nd sel f gain

calibrations. For the self-calibration of offset in the

25 m V, 55 m V, and 100 mv ranges, the conv erter

internally ties the inputs of the instrumentation amplifier toge the r and rou tes them to the AIN- pi n as

shown in Figure 10. For pro per self-ca libration o f

offset to occur in the 25 mV , 55 mV, and 100 mV

AIN+

AIN-

VREF-

+

X20

-

ranges, the AIN- pin must be at the proper common-mode-vol tage (i.e . AIN- = 0V, NBV must be

between -1.8 V to -2.5 V). For self- calibration of

offset in the 1.0 V, 2.5 V, and 5 V ranges, the inputs

DS202F1 17

Figure 11. Self Calibration of Offset (High Ranges).

S1

OPEN

S2

OPEN

S4

CLOSED

+

S3

CLOSED

-

Reference

+

-

AIN+

AIN-

VREF+

VREF-

CS5525 CS5526

OPEN

+

X20

OPEN

CLOSED

CLOSED

+

-

External

Connections

+

0V

-

+

CM

-

AIN+

AIN-

+

X20

-

+

-

Figure 12. Self Calibration of Gain (All Ranges).

VREF- as shown in Figure 12. For any input range

other than the 2.5 V range, the modulator gain error

can not be completely calibrated out. This is due to

the lack of an accurate full scale voltage internal to

the chips . T he 2.5 V range is an exceptio n be cause

the external reference voltage is 2.5 V nominal and

is used a s the full s cale volta ge. In additi on, w hen

self-calibrat io n of gain is pe rfor med in the 25 mV,

55 mV, and 100 mV input ranges, the instrumenta-

tion amplifier’s gain is not calibrated. These two

factors can leave the converters with a gain error of

up to ±20% after self-calibration of gain. Therefore, a system ga in i s required to get better ac curacy, except for the 2.5 V range .

System Calibration

For the system calibration functions, the user must

supply the converters calibration signals which represent ground and full sc al e. When a system offset

calibration is performed , a ground ref ere nce signal

must be applied to the converter. See Figures 13

and 14. As shown in Figures 15 and 16, the user

must input a signal representing the positive full

scale point to perform a system gain calibration. In

either ca se, the cali bration signal s must be w ithin

the specified calibration limits for each specific

calibration step (refer to the System Calibration

Specifications).

Figure 13. System Calibration of Offset (Low Ranges).

External

Connections

0V

CM

AIN+

+

-

AIN-

+

-

+

X20

-

+

-

Figure 14. System Calibration of Offset (High Ranges).

External

Connections

+

X20

-

Full Scale

CM

AIN+

+

-

AIN-

+

-

Figure 15. System Calibration of Gain (Low Ranges)

External

Connections

+

X20

-

Full Scale

CM

AIN+

+

-

AIN-

+

-

+

-

+

-

Figure 16. System Calibration of Gain (High Ranges).

18 DS202F1

CS5525 CS5526

Assuming a system can provide two known voltages, equation s can allow the us er to m anual ly co m-

pute the calib ration reg ister’s val ues based on two

uncalibrate d c onversions. The offset and g ai n calibration registers are used to adjust a typical conversion as follows:

23

Rc = (Ru + Co>>4) * Cg / 2

.

Calibration can be performed using the follow ing

equations:

Co = (Rc0/G - Ru0) << 4

23

Cg = 2

* G

where G = (Rc1 - Rc0)/(Ru 1-Ru0).

Note: Uncalibr ated conv ersions imply t hat the gain and offset

registers are at default {gain register = 0x800000 (Hex) and

offset register = 0x000000 (Hex)}.

The variables are defined below.

V0 = First calibration voltage

V1 = Second calibration voltage (greater than V0)

Ru = Result of any uncalibrated conversion

Ru0 = Result of uncalibrated conversion V0

(20-bit integer or 2’s complement)

Ru1 = Result of uncalibrated conversion of V1

(20-bit integer or 2’s complement)

Rc = Result of any conversion

Rc0 = Desired calibration result of converting V0

(20-bit integer or 2’s complement)

Rc1 = Desired calibration result of converting V1

(20-bit integer or 2’s complement)

Co = Offset calibration register value (24-bit 2’s

complement)

Cg = Gain calibration register value

(24-bit integer)

>> = The shift right operator (e.g. x >>2 is x shift-

ed right 2 bits)

<< = The shift left operator (e.g. x<<2 is x

shifted left 2 bit s)

Note: The shift operators are used here to align the decimal

points of words of various lengths. Data to the right of the

decimal point may be used in the c al cul at ion s s hown. For the

CS5525 all conversion results (Ru, Rc...) are 16 bits instead

of 20 bits. To get the equations to work correctly pad the 16

bit results with four zeros (on the right).

Calibration Tips

Calibration step s are perfo rm ed at th e ou tput word

rate selected by the WR2-WR0 bits of the configuration register. Since higher word rates result in

conversion words with more peak-to-peak noise,

calibration should be performed at lower output

word rates. Also, to minimize digital noise near

the devices, the user should wait fo r each calibration step to be completed before reading or writing

to the serial port.

For maximum accuracy, calibrations should be performed for offset and gain for each gain setting (selected by changing the G2-G0 bits of the

configuration register). And if factory calibration is

performed using the system calibration capabilities

of the CS5525/26 , the offset and ga in register contents can be read by the system microcontroller and

recorded in EEPROM. These same calibration

words can then be uploaded into the offset and gain

registers of the conv erters when power is first ap plied to the system, or when the gain range is

changed.

Two final tips include two ways to determine when

calibration is com plete : 1) wait for SDO to fal l. It

falls to logic 0 if the PF (Port Flag) bit of the configuration register is set to logic 1; or 2) poll the DF

(Done Flag) bit in t he configuration register which

is set at completion of calibration. Whichever

method is u sed, the ca libration c ontrol bits (C C2CC0) will return to logic 0 upon completion of any

calibration.

Limitations in Calibration Range

System ca libration can be limited by sig nal headroom in the analog signal path inside the chip as

discussed under the Analog Input section of this

data sheet . System cal ibration can al so be limited

by the intrinsic ga in errors of the instrumentat ion

amplifier a nd the mo dulator. Fo r gain ca libratio ns

DS202F1 19

CS5525 CS5526

the input signal can be reduced to the point in

which the gain register reac hes its upper limi t of 2.0

(decimal) [FFFFFF Hex] (this is most likely to occur with an input signal approximately 1/2 the

nominal rang e). Alte rna tive ly, the in put sig nal c an

be increased to a point in which the modulator

reaches its one’s density upper limit of 80% (this is

most likely to occur with an in put signal approxi mately 1.5 times the no minal ra ng e). Also, for full

scale inputs larger than the nominal full scale value

of the range selected, there is some voltage at

which the various internal circuits may saturate due

to limited amplifier headroom (this is most likely to

occur on the 100 mV range setting when NBV = -

1.8 V).

Analog Output Latch Pins

The A3-A0 pin s of the conve rters m imic th e D23D20 bits of the configu ration register. A3-A0 can

be used to control multiplexers and other logic

functions outside the converter. The outputs can

sink or source at least 1 mA, but it is recommended

to limit drive currents to less than 20µA to redu ce

self-heat ing of the chip. Thes e outputs are power ed

from VA+, hence, their output voltage for a logic 1

will be limi t ed to the VA+ vo ltage.

Serial Port Interface

The CS5525/26 serial interface consist of four pins,

SCLK, SDO, SDI, and CS

held low (logic 0) before SCLK tra nsitions c an be

recognized by the port logic. The SDO output will

be held at high impedance any time CS

If the CS

three wire interface.

The SCLK inpu t is desi gned wi th a Sc hm itt- tri gger

input to al lo w an opto is olat or w ith s low er ri se and

fall times to directl y drive the pin.

The SDO output is c apable of si nking or sourc ing

up to 5 mA to directl y drive a n optois olator LE D.

SDO will have less than a 400 mV loss in t he drive

voltage when sink ing or sourcing 5 mA.

pin is tied low, th e por t can func tion as a

. The CS pin must be

is a logic 1.

Serial Port Initialization

The serial port is initialized to the command mode

whenever a powe r-on reset is performed inside the

converter, whe n the port initia lization sequenc e is

completed, or whenever a command byte, data

word sequence is completed. The port initialization

sequence in volves clocking 15 (or m ore) bytes of

all 1's, f ollowed by one byte w i th the foll ow ing bit

contents (11111110). This sequence places the

chips in the command m ode where it w aits for a

valid command.

Performing Conversions (With PF bit = 0)

Setting the SC (Single Conversion) bit of the command word to a logic 1 with the CB bit = 1, all other

command bits = 0, the CS5525/CS5526 will perform one conversion. At the completion of the conversion the DF (Done Flag) bit of the configuration

register wi ll be set t o a logi c 1. The us er can re ad

the configuration register to determine if the DF bit

is set. If DF has been set, a command can be issued

to read the conversion data register to obtain the

conversion data word. Th e DF bit of the c onfiguration regist er will be cleare d to logic 0 when the

data register, the gain register, the offset register, or

the set-up registers are read. Reading only the configuration regi ster will not cle ar th e DF fl ag bi t.

If an SC command is issued to the converters while

they are performing a conversion, the filter will restart a co nvol ution cycle t o perform a ne w conversion.

Performing Conversions (With PF bit = 1)

Setting the PF bit of th e c onfigu rati on regi ste r to a

logic 1 enables the SDO output pin to behave as a

flag signal whenever conversions are completed.

This eliminates the need for the user to read the DF

flag bit of the configuration register to determine if

the conversion data word is available.

If the SC (Single Conversion) com mand is issued

(SC = 1, CB= 1, all othe r command bits = 0) the

SDO pin will go low at the completion of a conver-

20 DS202F1

CS5525 CS5526

sion. The user would then issue 8 SCLKs (with

SDI = logic 0) to clear the SDO flag. Upon the falling edge of the 8th SCLK, the SDO pin will present

the first bit (MSB) of the conversion word. 24

SCLKs (high, then low) are required to read the

conversion word from the port. Th e user must not

give an explicit command to read the conversion

data regist er wh en t he P F bit is set to logic 1. Th e

data conversion word must be read before a new

command can be entered (if the SC command is

used with PF = 1).

If the CC (Continuous Conversion) command is issued (CC = 1, CB =1 , all o the r com man d bit s = 0 )

the SDO pin will go low at the completion of a conversion. The user would then issu e 8 SCLKs (with

SDI = logic 0) to clear the SDO flag. Upon the falling edge of the 8th SCLK, the SDO pin will present

the first bit (MSB) of the conversion word. 24

SCLKs (high, then low) are required to read the

conversion word from the port . The user must not

give an explicit command to read the conversion

data regist er when the PF bit is set to lo gic 1. Whe n

operating in the continuous conversion mode , the

user need not read every conversion. If the user

does nothing after SDO falls, SDO will rise one

XIN clock cycle before the next conversion word is

availabl e and then fall again to sign al that a nother

conversion word is availabl e. If the us er begins to

clear the SDO flag and read the conversion data,

this actio n must be finishe d before the con version

cycle which is occurring in the background is complete if the user wants to be able to read the new

conversion da ta.

To exit the con ti nuous conversion m ode, issue any

valid command to the SDI input when the SDO flag

falls. If a C C command is is sued to the conv erter

while it is pe rforming a conversion, th e filter will

restart a convo lution cycle to perfor m a new conversion.

Output Word Rate Selection

The WR2-WR0 bits of the configuration register

set the output conversion word ra te of the co nverters as shown in Table 2. The word rates indicated

in the table a ssume a mas ter clock of 3 2.768 kHz.

Upon reset the converters are set to operate with an

output word rate of 15.0 Hz.

Clock Generator

The CS5525/26 include a gate which can be connected with an external cry stal to p rovide th e master

clock for the chips. They ar e designed to o perate us-

ing a low-cost 32.768 kHz “tuning fork” type crystal. One lead of the crystal should be connected to

XIN and the other to XOUT. Lead lengths should be

minimized to reduce stray capa citance.

The converters will operate with an external

(CMOS compa tible) clock with f requencies up to

three times the typi cal crysta l frequenc y of 32.768

kHz. Figure 17 details the converter’s performance

at increased clock rates.

Figure 17. High Speed Clock Performance

The 32.768 kHz crystal is normally specified as a

time-keeping crystal with tight specifications for

both initial fr eque ncy and for drif t over temperatu re.

To maintain excellent frequency stability, these

crystals are specified only over limited operating

temperature ranges (i.e. -10 °C to +60 °C). However,

applications with the CS55 25/26 don’t generally require such tight tolerances. When 32.768 kHz surface mount crystals are used, it is recommended that

protection components, an external resistor and capacitor as shown in Figure 18, be used.

DS202F1 21

CS5525 CS5526

VA+ VD+

XOUT

CS5525

CS5526

Figure 18. Surface Mount Crystal Connection Diagram

500 k

XIN

Ω

20 pF

32.768 kHz

Digital Filter

The CS5525/26 have eight different linear phase

digital filters which set the output word rates

(OWRs) a s stated in Table 2. Th ese rates assume

that XIN is 32.768 kHz. Each of the filters has a

magnitude response similar to that shown in Figure

19. The filters are optimized to settle to full accuracy every conversion and yield better than 80 dB rejection for both 50 and 60 Hz with output word

rates at or below 15.0 Hz.

The convert er’s digital fi lters scale wit h XIN. For

example with an output word rate of 15 Hz, the filter’s corner fre quenc y is typi call y 1 2.7 Hz . If XI N

is increased to 64 .536 kHz the O WR doubles and

the filter’s corner fre quency moves to 25 .4 Hz.

Output Coding

The CS5525/26 out put data in binary fo rm at when

operating in unipolar mode and in two's complement when operating in bipolar m ode.

The output conversion word is 24 bits, or three

bytes long, as shown in Table 5. The MSB is output

Figure 19. Filter Response

(Norma lized to Output W ord Rate = 1)

first followed by the rest of the data bits in descending order. For the CS5525 the last byte is composed

of bits D7-D4, which are al ways logic 1; D3-D2,

which are always logic 0; and bits D1-D0 which are

the two fla g bits. For the CS552 6 the last byt e includes data bits D7-D4, D3-D2 wh ich are alwa ys

logic 0 and the two flag bits.

The OF (Overra nge Flag) bit is set to a logic 1 any

time the input signal is: 1) more positive than positive full scale, 2) more negative than zero (unipolar

mode), 3) more negative than negative full scale

(bipolar mode). It is cl eared back to logic 0 when ever a conversion word occurs which is not overranged.

The OD (Oscillation Detect) bit is set to a logic 1 any

time that an oscillatory condition is detected in the

modulator. This does not occur under normal operating conditions, but may occur whenever the input

Output Conversion Data CS5525 (16 bits + flags)

D23 D22 D21 D20 D19 D18 D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

MSB1413121110987654321LSB111100ODOF

Output Conversion Data CS5526 (20 bits + flags)

D23 D22 D21 D20 D19 D18 D17 D16 D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

MSB181716151413121110987654321LSB00ODOF

Table 5. Data Conversion Word

22 DS202F1

CS5525 CS5526

CS5525 16-Bit Output Coding CS5526 20-Bit Output Coding

Unipolar Input

Voltage

>(VFS-1.5 LSB) FFFF >(VFS-1.5 LSB) 7FFF >(VFS-1.5 LSB) FFFFF >(VFS-1.5 LSB) 7FFFF

VFS-1.5 LSB

VFS/2-0.5 LSB

+0.5 LSB

<(+0.5 LSB) 0000 <(-VFS+0.5 LSB) 8000 <(+0.5 LSB) 00000 <(-VFS+0.5 LSB) 80000

Note: VFS in the table equals the voltage bet ween ground and full scale for any of the unipolar gain ranges, or the

voltage between ±full scale for any of the bipolar gain ranges. See text about error flags under overrange

conditions.

to the converters is extremely overr anged. If the OD

bit is set, the conversion data bits can b e completely

erroneous. The OD flag bi t will be cleared t o logic 0

when the modulator becomes stable. Table 6 illus trates the output coding for t h e CS 5525/26.

Offset

Binary

FFFF

-----

FFFE

8000

-----

7FFF

0001

-----

0000

Bipolar Input

Voltage

VFS-1.5 LSB

-0.5 LSB

-VFS+0.5 LSB

Two’s

Complement

7FFF

-----

7FFE

0000

-----

FFFF

8001

-----

8000

Table 6. 5525/26 Output Coding

Unipolar Input

Voltage

VFS-1.5 LSB

VFS/2-0.5 LSB

+0.5 LSB

command wor d a re se t to lo gic 1. T he p ar ticu la r

power save mode ente red depends on state of bit

D4 (the Power Save Select bit) in the configuration

register. If D4 is logic 0, t he converte rs enters the

standby mode re ducing the p ower consumpt ion to

Offset

Binary

FFFFF

-----

FFFFE

80000

-----

7FFFF

00001

-----

00000

Bipolar Input

Voltage

VFS-1.5 LSB

-0.5 LSB

-VFS+0.5 LSB

Two’s

Complement

7FFFF

-----

7FFFE

00000

-----

FFFFF

80001

-----

80000

1.2mW. The standby mode leaves the oscillator

Power Consumption

The CS5525/26 accommodate four power consumption modes: normal, low po wer, standby, and

sleep. The no rmal mode, the defau lt mode, is entered after a power-on-reset and typically consumes 7.5 mW. The low power mode is an alter nate

mode that reduces the consumed power to 4 mW. It

is entered by se tting b it D16 (the low po wer mode

bit) in the co nfiguration register to l ogic 1. Since

the converter’s noise performance improves with

and the on-chip bias generator running. This allows

the converters to quickly return to the normal or

low power m od e once th e PS /R

bit is set back to a

logic 1. If D4 in the confi guration register and CB

and PS/R

in the com mand word are set to logic 1,

the sleep mode is entered reducing the consumed

power to less than 500 µW. Since the sleep mode

disables the oscillat or, approximatel y a 500ms oscillator sta rt-up del ay peri od is requ ired b efore re turning to the normal or low power mode.

increased power consumption, slightly degraded

noise or lineari ty performa nce should be expected

in the low power mode. The final two modes are referred to as the power save modes. They power

down most of the analog portion of the chips and

stop filter convolutions. The power save modes are

entered whenever the PS/R

bit and the CB bit of the

PCB Layout

The CS5525/ 26 should be pl aced entirel y over an

analog ground plane with both the AGND and

DGND pins of the device connected to the analog

plane. Place th e analog-d igit al plane split immedi ately adjacent to the digital portion of the chi p .

DS202F1 23

PIN DESCRIPTIONS

CS5525 CS5526

ANALOG GROUND AGND VREF+ VOLTAGE REFERENCE INPUT

POSITIVE ANALOG POWER VA+ VREF- VOLTAGE REFERENCE INPUT

DIFFERENTIAL ANALOG INPUT AIN+ CS

DIFFERENTIAL ANALOG INPUT AIN- SDI SERIAL DATA INPUT

NEGATIVE BIAS VOLTAGE NBV A3 LOGIC OUTPUT

LOGIC OUTPUT A0 A2 LOGIC OUTPUT

LOGIC OUTPUT A1 SDO SERIAL DATA OUTPUT

CHARGE PUMP DRIVE CPD VD+ POSITIVE DIGITAL POWER

CRYSTAL IN XIN DGND DIGITAL GROUND

CRYSTAL OUT XOUT SCLK SERIAL CLOCK INPUT

1

2

3

4

5

6

7

8

9

10 11

20

19

18

17

16

15

14

13

12

CHIP SELECT

Clock Generator

XIN; XOUT - Crystal In; Crystal Out, Pins 9, 10.

A gate inside the chip is conn ected to these pins a nd can be used with a crystal to provi de the

master clock for the device. Alternatively, an external (CMOS compatible) clock can be

supplied into t he XIN pin to pro vide the m aster clock for the device .

Control Pins and Serial Data I/O

CS - Chip Select, Pin 18.

When active low, the port will recognize SCLK. When high the SDO pin will output a high

impedance s tate. C S

should be changed wh en SCLK = 0 .

SDI - Serial Data Input, Pin 17.

SDI is the input pi n of the seria l input port . Data will be input at a rat e determine d by SCLK.

SDO - Serial Data Ou tput, Pin 14.

SDO is the serial data output. It will output a high impedance state if CS

SCLK - Serial Clock Input, Pin 11.

A clock signal on this pin determines the input/output rate of the data for the SDI/SDO pins

respective ly. Th is input is a Schmitt trig ger to allow for slow rise time signals. Th e SCLK pin

will recogniz e clocks onl y when CS

is low.

A0, A1, A2, A3 - Logic Outputs, Pin 6, 7, 15, 16.

The logic states of A0-A3 mimic the states of the D20-D23 bits of the configuration register.

Logic Output 0 = AGND, and Logic Output 1 = VA+.

= 1.

24 DS202F1

Measurement and Reference Inputs

AIN+, AIN- - Differential Analog Input, Pins 3, 4.

Differential input pins into the device.

VREF+, VREF- - Vo ltage Reference Input, Pins 20, 19.

Fully differential i nputs which e stablish the voltage re ference for the on-chip mod ulator.

NBV - Negative Bia s Voltage, Pin 5.

Input pin to supply the negative supply voltage for the 20X gain instrumentation amplifier.

May be tied to AGND if AIN+ and AIN- inputs are centered around +2.5 V; or it may be tied

to a negati ve supply voltag e (-2.1 V typical ) to allow the am plifier to handle low level signal s

more negative t han ground.

CPD - Charge Pump Drive, Pin 8.

Square wave outp ut used to provide ene rgy for the charge pum p.

Power Supply Connections

CS5525 CS5526

VA+ - Positive Anal og Power, Pin 2.

Positive analog supply voltage. Nominally +5 V.

VD+ - Positive Digital Power, Pin 13.

Positive digital supp ly voltage . Nominally +3. 0 V or +5 V.

AGND - Analog Ground, Pin 1.

Analog Ground.

DGND - Digital Ground, Pin 12.

Digital Ground.

DS202F1 25

SPECIFICATION DEFINITIONS

Linearity Error

The deviation of a code from a straight line which connects the two endpoints of the A/D

Converter transfer function. One endpoint is located 1/2 LSB below the first code transition

and the other endpoint is located 1/2 LSB beyond the code transition to all ones. Units in

percent of full -scale.

Differential Nonline arity

The deviati on of a code’s wi dth from the ideal width. Units in LSBs.

Full Scale Error

The deviation of the last code transition from the ideal [{(VREF+) - (VREF-)} - 3/2 LSB].

Units are in LSBs.

Unipolar Offset

The deviation of the first code transition from the ideal (1/2 LSB above the voltage on the

AIN- pin.). When in un ipolar mode (U/B

CS5525 CS5526

bit = 1). Units are in LSBs.

Bipolar Offset

The deviation of the mid-scale tra nsition (111...111 to 000...000) from th e ideal (1/2 LSB belo w

the voltag e on the A IN- pin). When in bi polar mo de (U/B

ORDERING GUIDE

Model Number Linearity Error (Max) Temperature Range Package

CS5525-AP ±0.003% -40°C to +85°C 20-pin 0.3" Plastic DIP

CS5525-AS ±0.003% -40°C to +85°C 20-pin 0.2" Plastic SSOP

CS5526-BP ±0.0015% -40°C to +85°C 20-pin 0.3" Plastic DIP

CS5526-BS ±0.0015% -40°C to +85°C 20-pin 0.2" Plastic SSOP

bit = 0). Uni ts are in LSBs.

SPI™ is a trademark of Motorola Inc., Microwire™ is a trademark of National Semiconduct or Corp.

26 DS202F1

20 PIN PLASTIC (PDIP) PACKAGE DRAWING

D

1

TOP VIEW

DIM MIN MAX MIN MAX

A 0.155 0.180 3.94 4.57

A1 0.020 0.040 0.51 1.02

b 0.015 0.022 0.38 0.56

b1 0.050 0.065 1.27 1.65

c 0.008 0.015 0.20 0.38

D 0.960 1.040 24.38 26.42

E 0.240 0.260 6.10 6.60

e 0.095 0.105 2.41 2.67

eA 0.300 0.325 7.62 8.25

L 0.125 0.150 3.18 3.81

∝

E

A1

A

L

SEATING

PLANE

b1

e

BOTTOM VIEW

b

INCHES MILLIMETERS

0° 15° 0° 15°

CS5525 CS5526

∝

eA

SIDE VIEW

c

Notes: 1. Positional toleranc e of lead s shall be within 0.25 mm (0.010 in.) at maximum material condition, in

relation to seating plane and each other.

2. Dimension eA to center of leads when formed parallel.

3. Dimension E does not include mold flash.

DS202F1 27

CS5525 CS5526

20 PIN SSOP PACKAGE DRAWING

N

1

23

TOP VIEW

D

E

e

2

b

SIDE VIEW

A2

A1

A

SEATING

PLANE

L

INCHES MILLIMETERS

1

E1

END VIEW

NOTE

DIM MIN MAX MIN MAX

A -- 0.084 -- 2.13

A1 0.002 0.010 0.05 0.25

A2 0.064 0.074 1.62 1.88

b 0.009 0.015 0.22 0.38 2,3

D 0.272 0.295 6.90 7.50 1

E 0.291 0.323 7.40 8.20

E1 0.197 0.220 5.00 5.60 1

e 0.024 0.027 0.61 0.69

L 0.025 0.040 0.63 1.03

∝

0° 8° 0° 8°

Notes: 1. “D” and “E1” are reference datums and do not included mold flash or pr otrusions, but do include mold

mismatch and are measured at t he parting line, mold flash or pr otrusions shall not exceed 0.2 0 mm per

side.

2. Dimension “b” does not include dambar protrusion/intrusion. Allowable dambar protrusion shall be

0.13 mm total in excess of “b” dimension at maximum material condition. Dambar intrusion shall not

reduce dimension “b” by more than 0.07 mm at least material condition.

3. These dimensions apply to the flat section of the lead between 0.10 and 0.25 mm from lead tips.

28 DS202F1

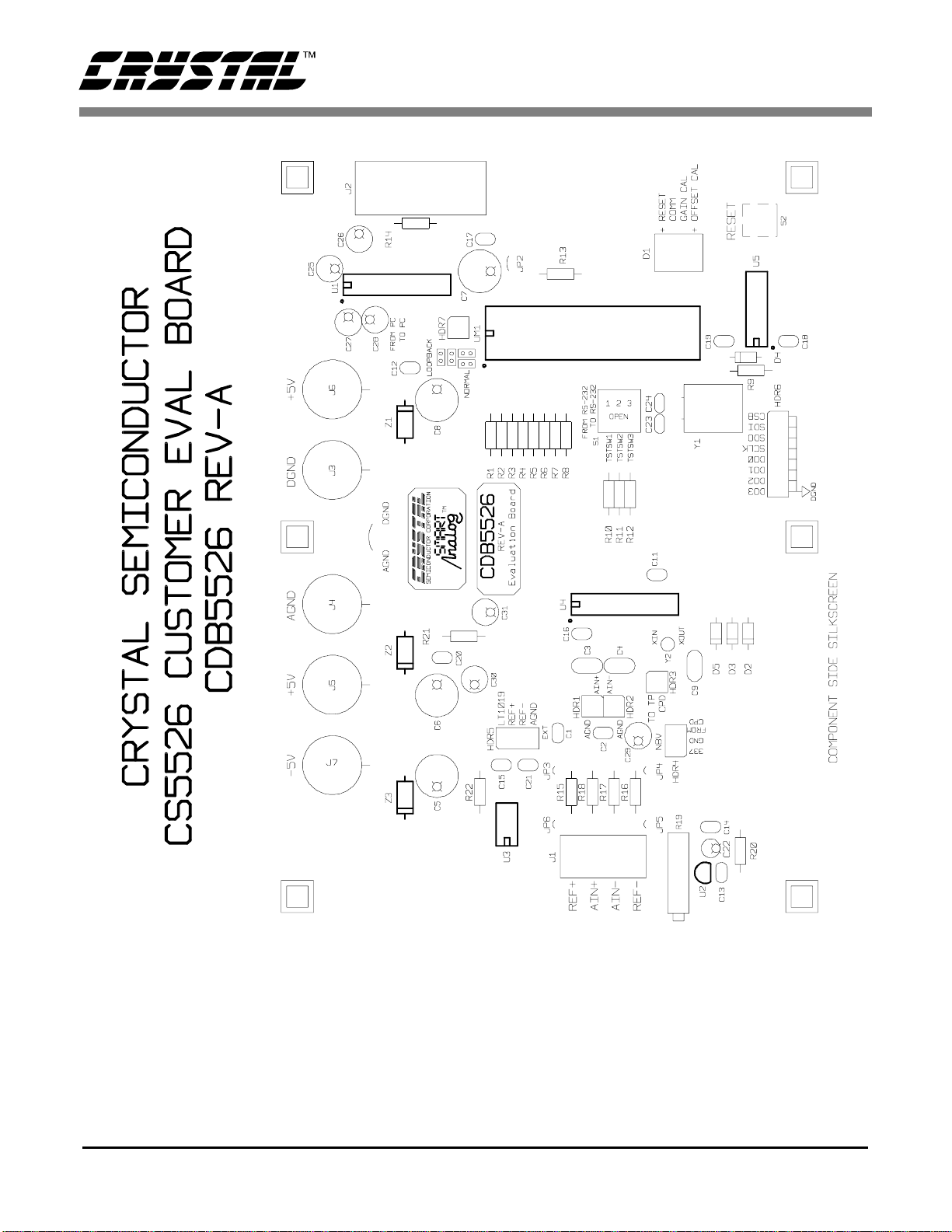

CDB5525

CDB5526

CDB5525/26 Evaluation Board and Software

Features

l

Direct Thermocouple Interface

l

RS-232 Serial Communication with PC

l

On-board 80C51 Microcontroller

l

On-board Voltage Reference

l

Lab Windows/CVITM Evaluation Software

- Register Setup & Chip Control

- FFT Analysis

- Time Domain Analysis

- Noise Histogram Analysis

l

On-board Charge Pump Drive Circuitry

l

Integrated RS-232 Test Mode

AGND

REF+

-5 ANALOG +5 ANALOG

J1

VOLTAGE

REFERENCE

CS5526

General Description

The CDB5525/26 is an inexpensive tool designed to

evaluate the performance of the CS5525 and CS5526,

16-bit and 20-bit Multi-Range Analog-to-Digital Converters (ADC).

The evaluation board includes an LT1019 voltage reference, an 80C51 microcontroller, an RS232

driver/receiver , and fir mware. The 8051 cont rols the serial communication between the evaluation board and

the PC via the firmware, thus, enabling quick and easy

access to all of the CS5525/26’s registers.

The CDB5525/26 also includes software for Time Do-

main Analysis, Histogram Analysis, and Frequency

Domain Analysis.

ORDERING INFORMATION: CDB5526

DGND +5 DIGI TAL

RS232

CONNECTOR

80C51

MICROCONTROLLER

TEST

SWITCHES

OFF ON

1

2

3

AIN+

AIN-

REF-

NBV DRIVE

CIRCUITRY

CRYSTAL

32768Hz

AIN+

AIN-

CPD

NBV

XIN

XOUT

Preliminary Product Information

Cirrus Logic, Inc.

Crystal Semiconductor Products Division

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.crystal.com

RS232

DRIVER/RECEIVER

LEDs

RESET

CIRCUITRY

CS

SDI

SDO

SCLK

A3

A2

A1

A0

HDR6

CRYSTAL

11.0592MHz

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

Copyright Cirrus Logic, I nc. 1998

(All Rights Reserv ed)

JAN ‘98

DS202DB5

29

CDB5525 CDB5526

PART I: HARDWARE

Introduction

The CDB5525/26 evaluation board provides a

quick means of testing the CS5525 and CS5526

Analog-to-Digital Converters (ADCs). The board

TM

interfaces the CS5525/26 to an IBM

PC via an RS-232 interface while operating from a

+5V and -5V power supply. To accomplish this, the

board comes equipped with an 80C51 microcontroller and a 9- pin RS-232 cable physic ally interfaces the evaluation board to the PC. Ad ditionally,

analysis software provides easy access to the internal registers of the converter, and provides a means

to displa y the converter ’s time do main, freq uency

domain, and noise histogram perf ormance.

compatible

Evaluation Board Overview

The board is partitioned into two main sections: analog and digital. The a nalog section consists of t h e

CS5525 or t he CS5526, a precision vo ltage refer ence, and the circuit ry to ge nerate a negat ive volt age. The digital section consists of the 80C51

microcontroller, the hardware test switches, the reset circuitry, and the RS-232 interface.

The CS5525/26 is designed to digitize low level

signals while operating from a 32.768 KHz crystal.

As shown in Figure 1, a therm ocou ple can be connected to th e conve rter’ s inpu ts vi a J1’s AIN+ and

AIN- inputs. Note, a sim pl e RC network filters the

thermocouple’s output to reduce any interference

picked up by the thermoc ouple lead s .

The eval uation board provides two voltage reference options, on-board and external. With HDR5’s

jumpers in positions 1 and 4, t he LT1019 provides

2.5 volts (the LT10 19 wa s chos en for it s low drif t,

typically 5ppm/°C). By setting HDR5’s jumpers to

position 2 and 3, the user can supply a n external

voltage reference to J1’s REF+ and REF- inputs

(Application Note 4 in the back of the 1995 Crystal

Semiconduct or Data Acquisi tion Databook de tails

various voltage references).

TM

The ADC serial interface is SPI

TM

MICROWIRE

lines (CS

the 80C51 mi crocontrol ler via port on e. To inter face an external microcontroller, these control lines

are also conn ected t o HDR6. How ever to ac complish this, the evaluation board must be modified in

one of three ways: 1) cut the interface control traces

going to the microcontroller, 2) remove resistors

R1-R8, or 3) remove the microcontrol le r.

Figure 2 illustrates the schematic of the digital section. It contains the microcontroller, a Motorola

MC145407 inte rface chip, and test switch es. The

test switches aid in debugging communication

problems between the CDB5525/26 and the PC.

The microcontroller derives its clock from an

11.0592 MHz cry stal. From this, the controller is

configured to communicate via RS-232 at 9600

baud, no parity, 8-bi t data, and 1 stop bit.

, SDI, SDO, and SCLK) are connected to

compatibl e. The in terf ace contr ol

and

30 DS202DB5

CDB5525 CDB5526

REF+

AIN+

AIN-

REF-

+5V Analog

JP6

J1

JP5

+5V Analog

C21

0.1µF

-5V Analog

C22

1µF

+5V Analog

R18

301

R17

301

JP3

JP4

+

Ω

4700pF

Ω

R15

301

R16

301

U3

LT1019

2.5V

LM337_LZ

ADJ

C13

0.1µF

0.1µF

C2

Ω

4700pF

Ω

D2

BAT85

U2

+

C16

C1

VOUTVIN

R22

50

HDR1

7

HDR2

Ω

1, AGND

2, AIN+

1, AIN2, AGND

1,LT1019

2,REF+

3,REF4,AGND

C15

0.1µF

+

HDR4

R20

Ω

1k

R19

Ω

1k

C30

10µF

0.68µF

HDR5

C29

10µF

3

2

1

C3

0.68µF

C4

20

19

G

3

N

3

D

7

R21

Ω

10

2

1

VA+

AGND