Page 1

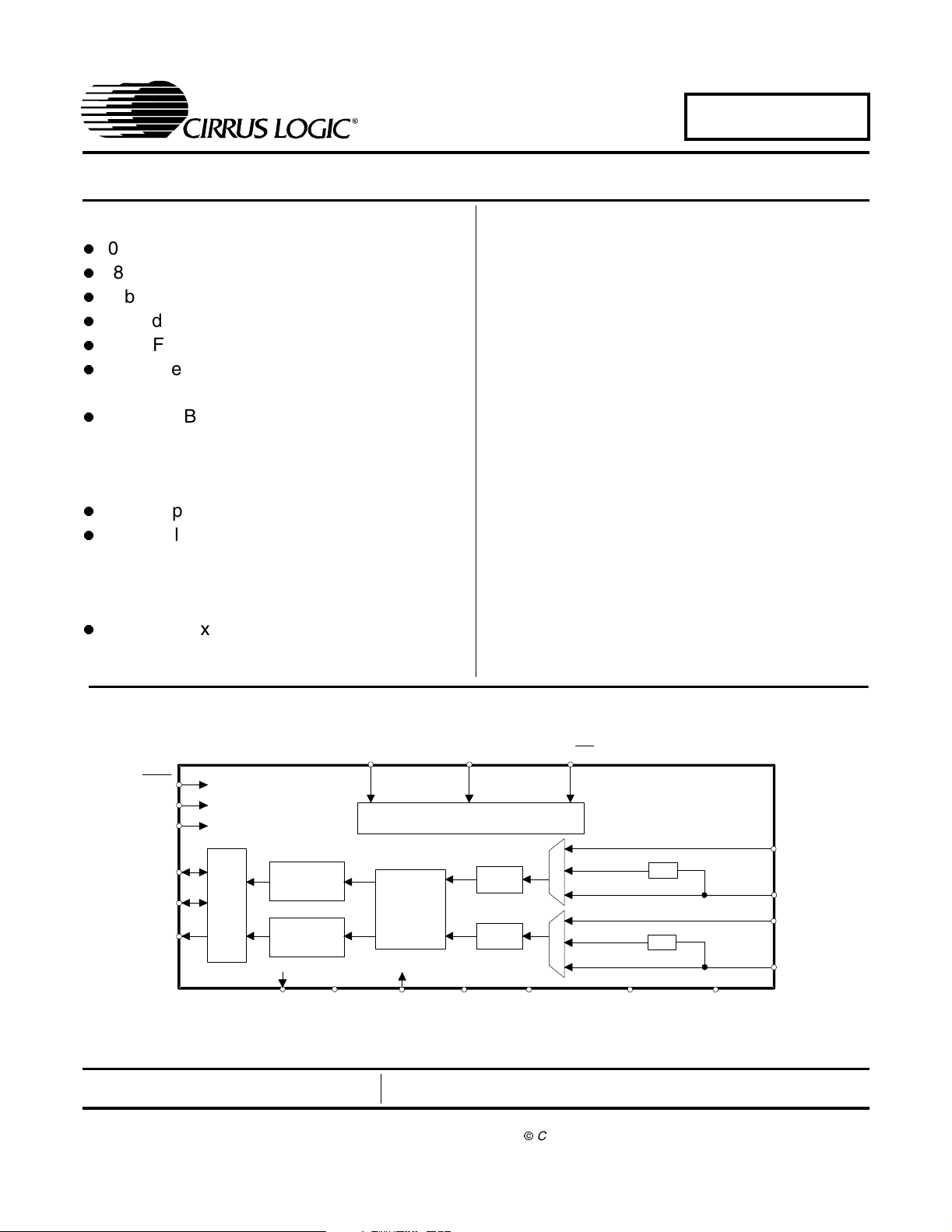

CS53L32A

Low Voltage, Stereo A/D Converter

Features

20-Pin TSSOP package

1.8 to 3.3 volt supply

24-bit conversion / 96 kHz sample rate

98 dB dynamic range at 3 V supply

-88 dBFS THD+N

Low power consumption

– 9.7 mW at 1.8 V

Up to 32 dB gain

–20dBgainstep

– 12 dB variable input gain, 1 dB steps

– Changes made at zero crossings

Stereo inputs

Digital volume control

– 96 dB attenuation, 1 dB step size

–Mute

– Soft ramping

2:1 input mux

II

Description

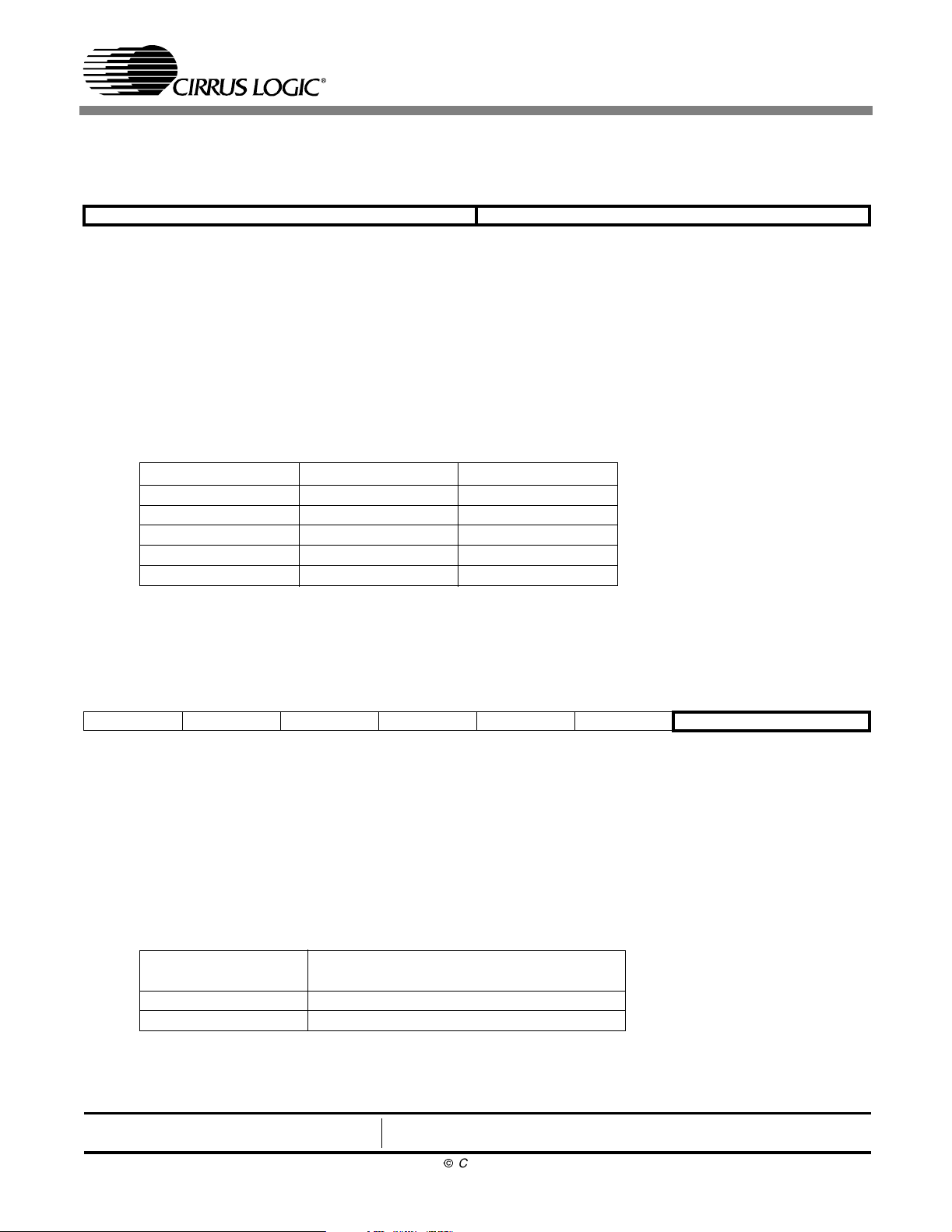

The CS53L32A is a highly integrated, 24-bit, 96 kHz audio ADC providing stereo analog-to-digital converters

using delta-sigma conversion techniques. This device includes volume control and line level inputs in a 20-pin

TSSOP package.

The CS53L32A is based on delta-sigma modulation allowing infinite adjustment of the sample rate between

2 kHz and 100 kHz simply by changing the master clock

frequency.

The CS53L32A contains adjustable analog gain, a 2:1

input mux, and digital attenuation.

The CS53L32A operates from a +1.8 V to +3.3 V supply.

These features are ideal for portable MP3 players, MD

recorders/players, digital camcorders, PDAs, set-top

boxes, and other portable systems that require extremely low power consumption in a minimum of space.

ORDERING INFORMATION

CS53L32A-KZ 20-pinTSSOP, -10to70°C

CDB53L32A Evaluation Board

SCL/CCLK/ SDA/CDIN/DIF

RST

VA

VL

Serial Port

Attenuator

0-96 dB

Attenuator

0-96 dB

GND VQ

LRCK

SCLK

SDOUT

Preliminary Product Information

Cirrus Logic, Inc.

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

ChSEL

Control Port

Digital

Filters

MCLK

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

ADC

ADC

FILT+ RE F_GND

CopyrightCirrus Logic, Inc. 2002

AD0/CS/DIV

Gain

Gain

AFLTL AFLTR

(All Rights Reserved)

AIN_L 1

AIN_L2

AIN_R1

AIN_R2

JUL ‘00

DS513PP1

1

Page 2

TABLE OF CONTENTS

1. CHARACTERISTICS/SPECIFICATIONS .................................................................................5

ANALOG CHARACTERISTICS ................................................................................................ 5

ANALOG CHARACTERISTICS ................................................................................................ 6

POWER AND THERMAL CHARACTERISTICS....................................................................... 7

DIGITAL CHARACTERISTICS................................................................................................. 8

ABSOLUTE MAXIMUM RATINGS ........................................................................................... 8

RECOMMENDED OPERATING CONDITIONS ....................................................................... 8

SWITCHING CHARACTERISTICS .......................................................................................... 9

SWITCHING CHARACTERISTICS - CONTROL PORT - TWO WIRE MODE....................... 11

SWITCHING CHARACTERISTICS - CONTROL PORT - SPI MODE.................................... 12

2. TYPICAL CONNECTION DIAGRAM .................................................................................... 13

3. REGISTER QUICK REFERENCE ..........................................................................................14

3.1 I/O and Power Control (address 01h) ............................................................................... 14

3.2 Interface Control (address 02h) ........................................................................................ 14

3.3 Analog I/O Control (address 03h) ..................................................................................... 15

3.4 Left Channel Digital Volume Control (address 04h).......................................................... 16

3.5 Right Channel Digital Volume Control (address 05h) .......................................................16

3.6 Analog Gain Control (address 06h) .................................................................................. 16

3.7 Clip Detection Status (address 07h) ................................................................................. 16

4. REGISTER DESCRIPTION .................................................................................................... 17

4.1 Gain Enable ...................................................................................................................... 17

4.2 Analog Input Multiplexer ................................................................................................... 17

4.3 Power-Down ..................................................................................................................... 18

4.4 Control Port Enable........................................................................................................... 18

4.5 Master Clock Divide.......................................................................................................... 19

4.6 Master Clock Ratio............................................................................................................ 19

4.7 Master Mode..................................................................................................................... 20

4.8 Digital Interface Format..................................................................................................... 20

4.9 Left/Right Channel Mute ................................................................................................... 21

4.10 Soft Ramp and Zero Cross Enable ................................................................................. 21

4.11 Independent Volume Control Enable .............................................................................. 22

4.12 Left Channel Volume = Right Channel Volume .............................................................. 23

4.13 High-Pass Filter Freeze .................................................................................................. 23

4.14 Volume Control ...............................................................................................................24

4.15 Left/Right Analog Gain.................................................................................................... 25

CS53L32A

Contacting Cirrus Logic Support

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at:

http://www.cirrus.com/corporate/contacts/

I2C is a r egistered trademark of Philips Semiconductors.

Preliminary product i nformation describes products which are in production, but for which full characterization data is not yet availabl e. Advance product information describes products which are in development and subject to development changes. Cir rus Logic, Inc. has made best efforts to ensure that the information

contained in this document is accurate and reli able. However, the information i s subject to change without notice and is provided “AS IS” without warranty of

any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this i nformation, nor for i nfri ngements of patents or other rights

of third parties. This document is the property o f Ci rrus Logic, Inc. and implies no license under patents, copyrights, t rademarks, or trade secr ets. No part of

this publication may be copied, reproduced, stored in a retrieval system, or transmitted, i n any form or by any means (electronic, mechanical, photographic, or

otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic website or disk may be printed for use by the user. However, no

part of the print out or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical,

photographic, or otherwise) wi thout the prior written consent of Cirrus Logic, Inc.Furthermore, no part of thi s publication may be used as a basis for manufacture

or sale of any items without the pri or written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appeari ng

in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

Preliminary Product Information

2 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 3

4.16 Clip Detection ................................................................................................................. 25

5. PIN DESCRIPTION ................................................................................................................. 26

6. PIN DESCRIPTION ................................................................................................................. 26

6. PIN DESCRIPTION ................................................................................................................. 26

6. APPLICATIONS ..................................................................................................................... 29

6.1 Grounding and Power Supply Decoupling ....................................................................... 29

6.2 Oversampling Modes ....................................................................................................... 29

6.3 Recommended Power-up Sequence ............................................................................... 29

7. CONTROL PORT INTERFACE ............................................................................................. 29

7.1 SPI Mode ......................................................................................................................... 29

7.2 Two Wire Mode ............................................................................................................... 29

7.3 Memory Address Pointer (MAP)....................................................................................... 30

8. PARAMETER DEFINITIONS .................................................................................................. 36

9. REFERENCES ........................................................................................................................ 36

10. PACKAGE DIMENSIONS .................................................................................................... 37

LIST OF FIGURES

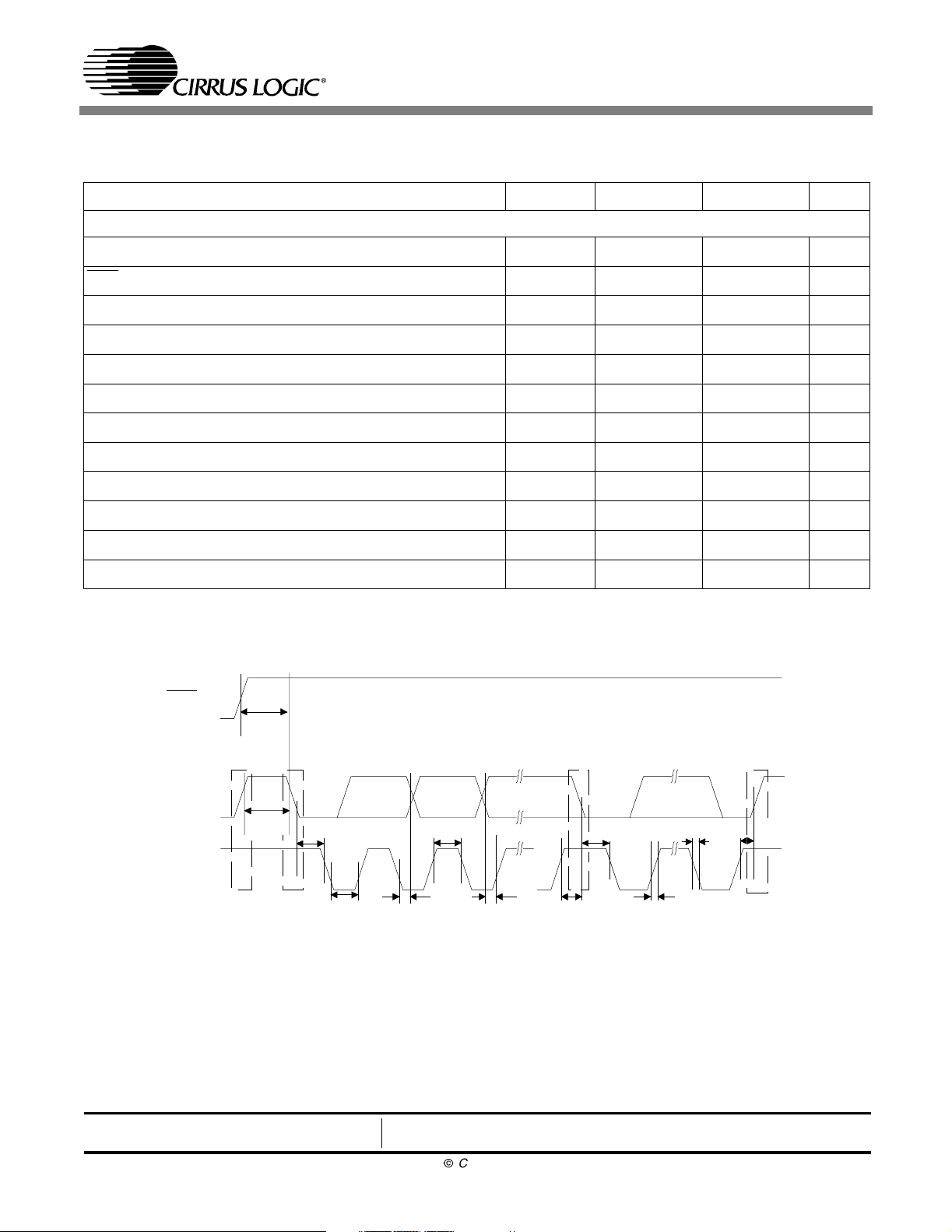

Figure 1. SCLK to LRCK and SDATA, Slave Mode...................................................................... 10

Figure 2. SCLK to LRCK and SDATA, Master Mode.................................................................... 10

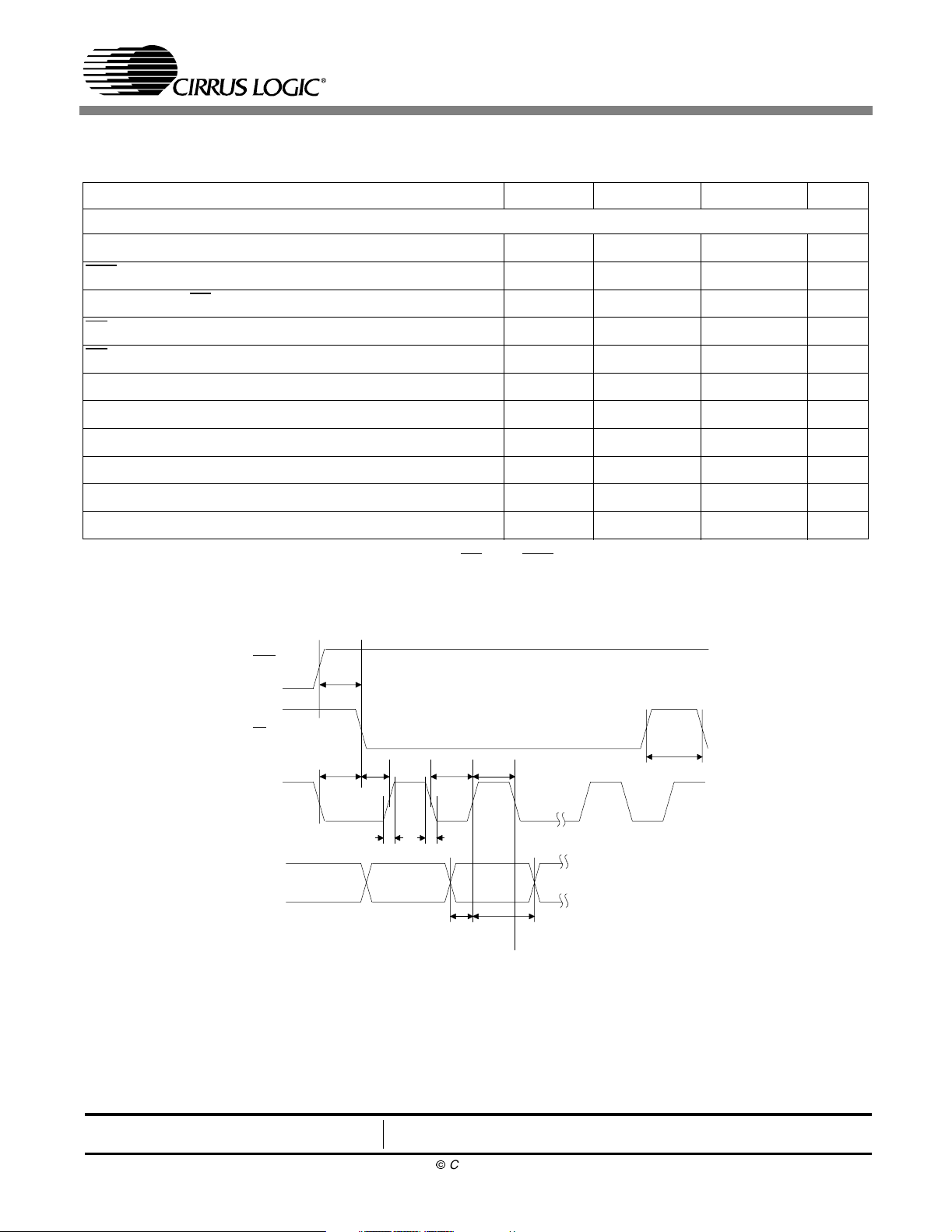

Figure 3. Control Port Timing - Two Wire Mode............................................................................ 11

Figure 4. Control Port Timing - SPI Mode ..................................................................................... 12

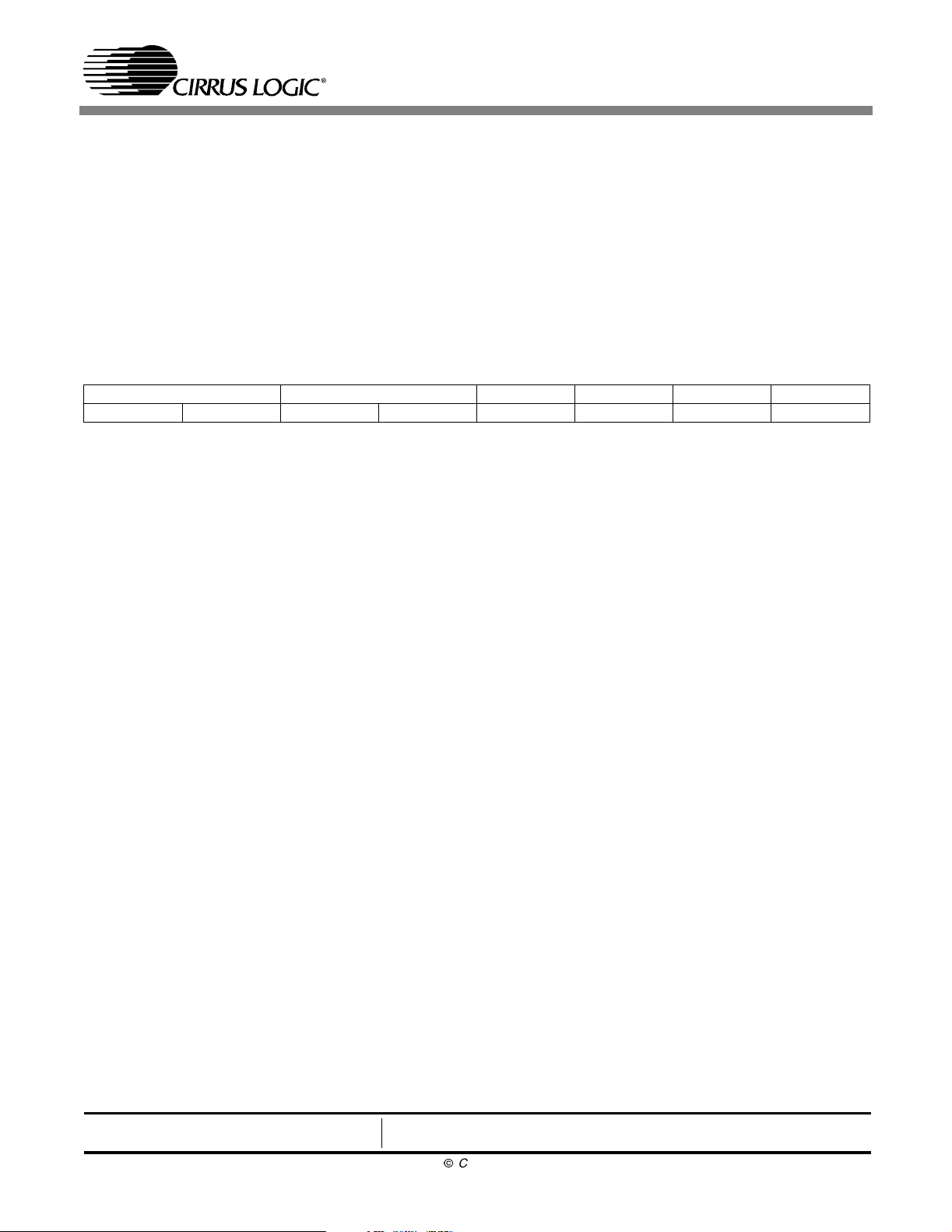

Figure 5. Typical Connection Diagram.......................................................................................... 13

Figure 6. Control Port Timing, SPI Mode ...................................................................................... 31

Figure 7. Control Port Timing, Two Wire Mode............................................................................. 31

Figure 8. Base-Rate Stopband Rejection...................................................................................... 32

Figure 9. Base-Rate Transition Band............................................................................................ 32

Figure 10. Base-Rate Transition Band (Detail) ............................................................................. 32

Figure 11. Base-Rate Passband Ripple........................................................................................ 32

Figure 12. High-Rate Stopband Rejection .................................................................................... 32

Figure 13. High-Rate Transition Band........................................................................................... 32

Figure 14. High-Rate Transition Band (Detail) .............................................................................. 33

Figure 15. High-Rate Passband Ripple......................................................................................... 33

Figure 16. Line Input Test Circuit.................................................................................................. 33

Figure 17. CS53L32A Control Port Mode - Serial Audio Format 0 (I

Figure 18. CS53L32A Control Port Mode - Serial Audio Format 1 ............................................... 34

Figure 19. CS53L32A Control Port Mode - Serial Audio Format 3 ............................................... 34

Figure 20. CS53L32A Control Port Mode - Serial Audio Format 4 ............................................... 34

Figure 21. CS53L32A Control Port Mode - Serial Audio Format 5 ............................................... 34

Figure 22. CS53L32A Control Port Mode - Serial Audio Format 6 ............................................... 35

Figure 23. CS53L32A Stand-Alone Mode - Serial Audio Format 0 (I

Figure 24. CS53L32A Stand-Alone Mode - Serial Audio Format 1............................................... 35

CS53L32A

2

S)....................................... 33

2

S) ...................................... 35

Preliminary Product Information

DS513PP1 3

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 4

LIST OF TABLES

Table 1. Analog Input Options .......................................................................................................17

Table 2. Power-Down Enable........................................................................................................ 18

Table 3. Control Port Enable......................................................................................................... 18

Table 4. Master Clock Divide Select ............................................................................................. 19

Table 5. MCLK/LRCK Ratios......................................................................................................... 19

Table 6. Master/Slave Mode Selection.......................................................................................... 20

Table 7. Digital Interface Format ...................................................................................................20

Table 8. Left/Right Channel Mute Enable ..................................................................................... 21

Table 9. Analog Volume Control ...................................................................................................22

Table 10. Digital Volume Control................................................................................................... 22

Table 11. Independent Volume Control Enable ............................................................................ 22

Table 12. High-Pass Filter Enable................................................................................................. 23

Table 13. Example Volume Settings ............................................................................................. 24

Table 14. Example Gain Settings.................................................................................................. 25

Table 15. Clip Detection Status Bits.............................................................................................. 25

Table 16. Common Clock Frequencies ......................................................................................... 26

Table 16. Common Clock Frequencies ......................................................................................... 26

Table 16. Common Clock Frequencies ......................................................................................... 26

Table 17. Digital Interface Format - DIF (Stand-Alone Mode) ....................................................... 27

Table 18. Channel Select Options................................................................................................. 27

CS53L32A

Preliminary Product Information

4 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 5

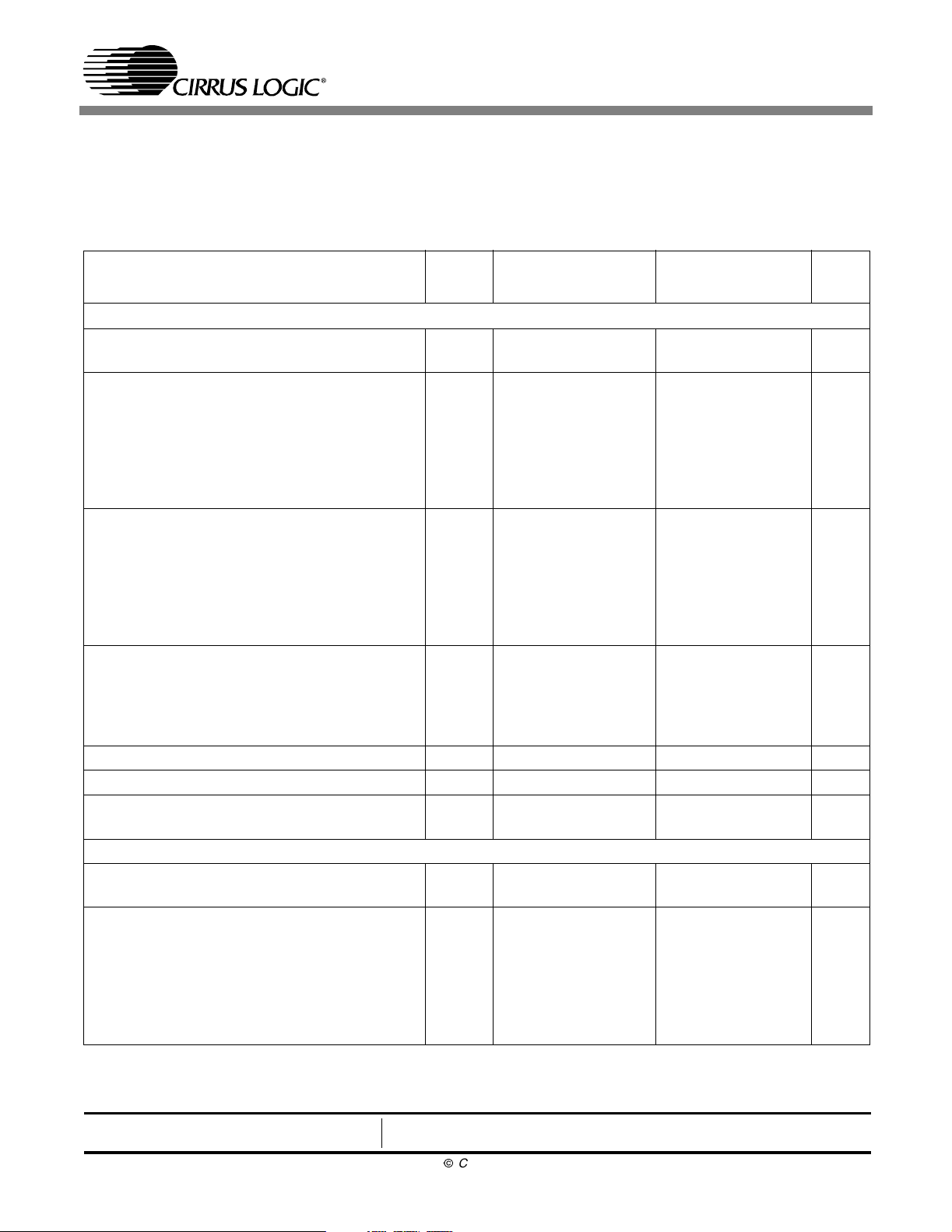

1. CHARACTERISTICS/SPECIFICATIONS

CS53L32A

ANALOG CHARACTERISTICS (T

GND = 0 V; MCLK = 12.288 MHz; Fs for Base-rate Mode = 48 kHz, SCLK = 3.072 MHz, Measurement Bandwidth

10 Hz to 20 kHz, unless otherwise specified; Fs for High-Rate Mode = 96 kHz, SCLK = 6.144 MHz, Measurement

Bandwidth 10 Hz to 20 kHz, unless otherwise specified.)

Parameter Symbol

Analog Input Characteristics for VA = 1.8 V

Dynamic Range A-weighted

unweighted

Total Harmonic Distortion + Noise (Note 1)

18 to 24-Bit -1 dB

-20 dB

-60 dB

16-Bit -1 dB

-20 dB

-60 dB

Dynamic Range (PGA on)*

0dBGain

A-weighted

unweighted

12 dB Gain

A-weighted

unweighted

Total Harmonic Distortion + Noise (PGA on)*

(Note 1) 0 dB Gain

18 to 24-Bit -1 dB

12 dB Gain

18 to 24-Bit -1 dB

Interchannel Isolation 1 kHz - 90 - - 90 - dB

Interchannel Gain Mismatch - 0.1 - - 0.1 - dB

Offset Error with High Pass Filter

HPF frozen with HPFREEZE

Analog Input Characteristics for VA = 3.0 V

Dynamic Range A-weighted

unweighted

Total Harmonic Distortion + Noise (Note 1)

18 to 24-Bit -1 dB

-20 dB

-60 dB

16-Bit -1 dB

-20 dB

-60 dB

*PGA : Programmable Gain Amplifier

= 25° C; GND = 0 V Logic "1" = VL = 1.8 V; Logic "0" =

A

Base-rate Mode High-rate Mode

TBD

TBD

THD+N

-

-

-

-

-

-

-

-

-

-

THD+N

-

-

-

-

TBD

TBD

THD+N

-

-

-

-

-

-

93

90

-88

-70

-30

-86

-68

-28

90

87

85

82

85

83

-

TBD

96

93

-88

-73

-33

-86

-68

-28

-

-

TBD

-

-

-

-

-

-

-

-

-

-

-

0

-

-

-

TBD

-

-

-

-

-

TBD

TBD

-

-

-

-

-

-

-

-

-

-

-

-

-

-

TBD

TBD

-

-

-

-

-

-

94

91

-88

-71

-31

-86

-68

-28

89

86

86

83

84

82

-

TBD

98

95

-85

-75

-35

-83

-65

-28

-

-

TBD

-

-

-

-

-

-

-

-

-

-

-

0

-

-

-

TBD

-

-

-

-

-

UnitMin Typ Max Min Typ Max

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

LSB

dB

dB

dB

dB

dB

dB

dB

dB

Note: 1. Referenced to typical full-scale differential input voltage (0.5 Vrms).

Preliminary Product Information

DS513PP1 5

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

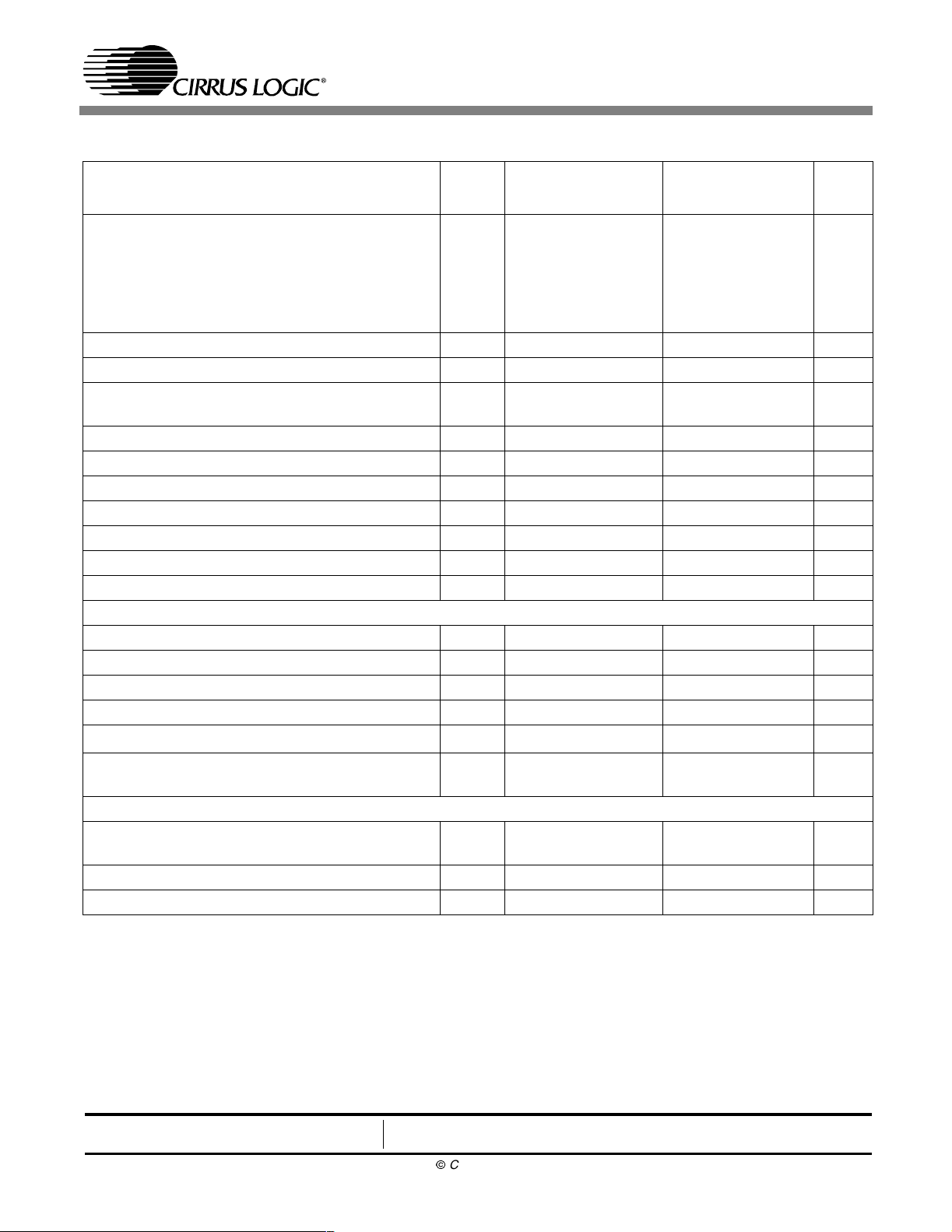

Page 6

ANALOG CHARACTERISTICS (CONTINUED)

CS53L32A

Base-rate Mode High-rate Mode

Parameter Symbol

Total Harmonic Distortion + Noise (PGA on)*

(Note 1)

0dBGain

18 to 24-Bit -1 dB

12 dB Gain

18 to 24-Bit -1 dB

Interchannel Isolation 1 kHz - 90 - - 90 - dB

Interchannel Gain Mismatch - 0.1 - - 0.1 - dB

Offset Error with High Pass Filter

HPF frozen with HPFREEZE

Full Scale Input Voltage TBD VA/3.6 TBD TBD VA/3.6 TBD Vrms

Gain Drift - 100 - - 100 - ppm/°C

Input Resistance 10 - - 10 - - kΩ

Input Capacitance - - 15 - - 15 pF

Programmable Gain Characteristics

Gain Step Size - 1.0 - - 1.0 - dB

Absolute Gain Step Error - - TBD - - TBD dB

A/D Decimation Filter Characteristics (Note 2)

Passband (Note 3) 0 - 23.5 0 - 47.5 kHz

Passband Ripple -0.08 - +0.17 -0.09 - 0 dB

Stopband (Note 3) 27.5 - - 64.1 - - kHz

Stopband Attenuation (Note 4) -60.3 - - -48.4 - - dB

Group Delay (Fs = Output Sample Rate) (Note 5) t

Group Delay Variation vs. Frequency ∆t

THD+N

gd

gd

-

-

-

-

- 10/Fs - - 2.7/Fs - s

- - 0.03 - - 0.007µs

78

73

-

TBD

-

-

0

-

-

-

-

-

77

76

-

TBD

UnitMin Typ Max Min Typ Max

-

dB

-

dB

0

LSB

-

High Pass Filter Characteristics

Frequency Response -3 dB (Note 3)

-0.1 dB

Phase Deviation @ 20 Hz (Note 3) - 10 - - 10 - Degree

Passband Ripple (Note 2) - - 0.17 - - 0.09 dB

*PGA : Programmable Gain Amplifier

Notes: 2. Filter response is not tested but is guaranteed by design.

3. Filter characteristics scale with output sample rate. For output sample rates, Fs, other than 48 kHz, the

0.01 dB passband edge is 0.4535x Fs and the stopband edge is 0.625x Fs.

4. The analog modulator samples the input at 6.144 MHz for an Fs equal to 48 kHz. There is no rejection

of input signals which are multiples of the sampling frequency ( n x 6.144 MHz ±21.8 kHz where

n = 0,1,2,3...).

5. Group delay for Fs = 48 kHz, t

Preliminary Product Information

6 DS513PP1

= 15/48 kHz = 312 µs.

gd

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

-

3.7

-

24.2

-

-

-

3.7

-

24.2

-

Hz

-

Hz

Page 7

CS53L32A

POWER AND THERMAL CHARACTERISTICS

Base-rate Mode High-Rate Mode

Parameters Symbol Min Typ Max Min Typ Max Units

Power Supplies

-

Power Supply Current- VA=1.8 V

Normal Operation VL=1.8 V

I

Power Supply Current- VA=1.8 V

Power Down Mode (Note 6) VL=1.8 V

I

Power Supply Current- VA=3.0 V

Normal Operation VL=3.0 V

I

Power Supply Current- VA=3.0 V

Power Down Mode VL=3.0 V

I

Total Power Dissipation- All Supplies=1.8 V

Normal Operation All Supplies=3.0 V

Package Thermal Resistance θ

Power Supply Rejection Ratio (1 kHz)

PSRR -

(Note 7) (60 Hz)

I

A

D_IO

I

A

D_IO

I

A

D_IO

I

A

D_IO

JA

6.0

-

150

-

100

-

-

-

-

-

-

-

0

9

260

250

0

11

28

-75- -75-°C/Watt

60

-

40

Chip Power

Analog/Digital Converter - 11 - - 14.5 - mA

A/D Converter & Programmable Gain Amplifier - 13 - - 16.5 - mA

-

-

-

-

-

-

-

-

TBD

TBD

-

-

-

-

-

-

-

-

-

-

-

-

-

-

7.6

300

250

0

11.5

520

500

0

-

-

-

-

-

-

-

-

14.536TBD

TBDmWmW

60

40

-

-

mA

µA

µA

µA

mA

µA

µA

µA

dB

dB

Notes: 6. Power Down Mode is defined as the chip being held in reset with MCLK being applied. To lower power

consumption further, remove MCLK.

7. Valid with the recommended capacitor values on FILT+ and VQ as shown in Figure 5.

Preliminary Product Information

DS513PP1 7

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 8

CS53L32A

DIGITAL CHARACTERISTICS (T

= 25° C; VL = 1.7 V - 3.6 V; GND = 0 V)

A

Parameters Symbol Min Typ Max Units

High-Level Input Voltage

Low-Level Input Voltage

High-Level Output Voltage V

Low-Level Output Voltage V

Leakage Current I

V

IH

V

IL

OH

OL

in

0.7•VL - - V

- - 0.3•VL V

0.7•VL - - V

- - 0.3•VL V

--±10µA

Input Capacitance - 8 - pF

ABSOLUTE MAXIMUM RATINGS (GND = 0 V; all voltages with respect to ground.)

Parameters Symbol Min Max Units

DC Power Supplies: Positive Analog

Digital I/O

Input Current, Any Pin Except Supplies I

Digital Input Voltage V

Ambient Operating Temperature (power applied) T

Storage Temperature T

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation is

not guaranteed at these extremes.

VA

VL

IND

stg

-0.3

-0.3

in

-±10mA

4.0

4.0

V

V

-0.3 VL+0.4 V

A

-55 125 °C

-65 150 °C

RECOMMENDED OPERATING CONDITIONS (GND = 0V; all voltages with respect to ground.)

Parameters Symbol Min Typ Max Units

Ambient Temperature T

DC Power Supplies: Positive Analog

Digital I/O

A

VA

VL

-10 - 70 °C

1.7

1.7

-

-

3.6

3.6

V

V

Preliminary Product Information

8 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 9

CS53L32A

1

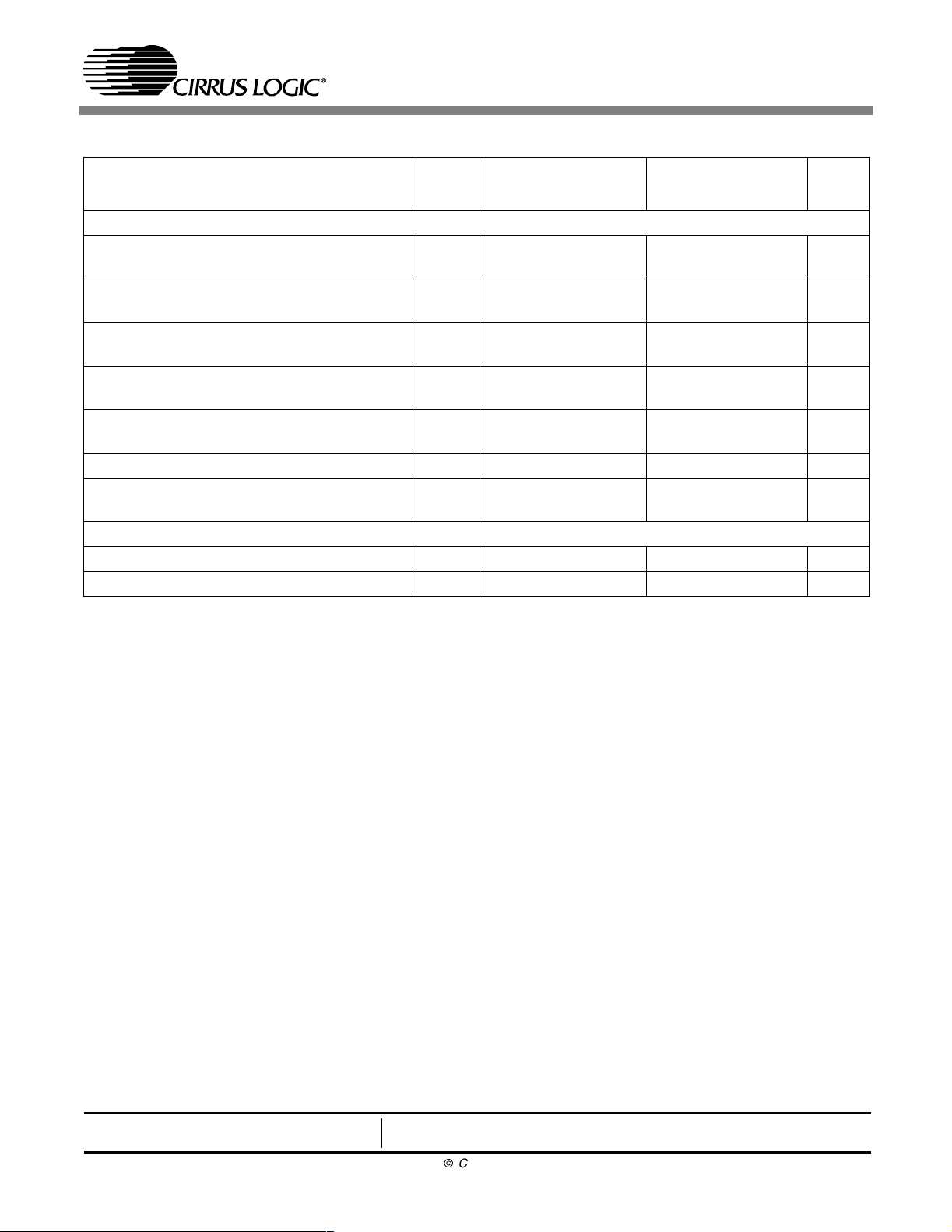

SWITCHING CHARACTERISTICS (T

Logic 1 = VL, C

=20pF)

L

= -10 to 70° C; VA = 1.7 V - 3.6 V; Inputs: Logic 0 = GND,

A

Parameters Symbol Min Typ Max Units

Input Sample Rate Base Rate Mode

High Rate Mode

Fs

Fs

2

50

-

-

50

100

kHz

kHz

MCLK Pulse Width High MCLK/LRCK = 1024 8 - - ns

MCLK Pulse Width Low MCLK/LRCK = 1024 8 - - ns

MCLK Pulse Width High MCLK/LRCK = 768 10 - - ns

MCLK Pulse Width Low MCLK/LRCK = 768 10 - - ns

MCLK Pulse Width High MCLK/LRCK = 512 15 - - ns

MCLK Pulse Width Low MCLK/LRCK = 512 15 - - ns

MCLK Pulse Width High MCLK / LRCK = 384 or 192 21 - - ns

MCLK Pulse Width Low MCLK / LRCK = 384 or 192 21 - - ns

MCLK Pulse Width High MCLK / LRCK = 256 or 128 31 - - ns

MCLK Pulse Width Low MCLK / LRCK = 256 or 128 31 - - ns

Master Mode

SCLK Falling to LRCK Edge t

SCLK Falling to SDATA Valid t

slrd

sdo

-20 - 20 ns

0 - 20 ns

SCLK Duty Cycle 40 50 60 %

Slave Mode

LRCK Duty Cycle 40 50 60 %

SCLK Pulse Width Low t

SCLK Pulse Width High t

SCLK Period Base Rate Mode

High Rate Mode

SCLK Falling to LRCK Edge t

SCLK Falling to SDATA Valid Base Rate Mode

High Rate Mode

sclkl

sclkh

t

sclkw

t

sclkw

slrd

t

dss

t

dss

20 - - ns

20 - - ns

1

--------- ------------128()Fs

1

--------- ---------

64()Fs

-

-

-

-

-20 - 20 ns

-

-

-

(512)Fs

-

1

(256)Fs

ns

ns

ns

ns

Preliminary Product Information

DS513PP1 9

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 10

CS53L32A

SCLK

LRCK

SDATA

SCLK

t

sclkh

t

sclkl

t

slrd

t

dss

MSB

Figure 1. SCLK to LRCK and SDATA, Slave Mode

t

sclkw

t

slrd

LRCK

t

sdo

SDATA

MSB MSB-1

Figure 2. SCLK to LRCK and SDATA, Master Mode

Preliminary Product Information

10 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 11

CS53L32A

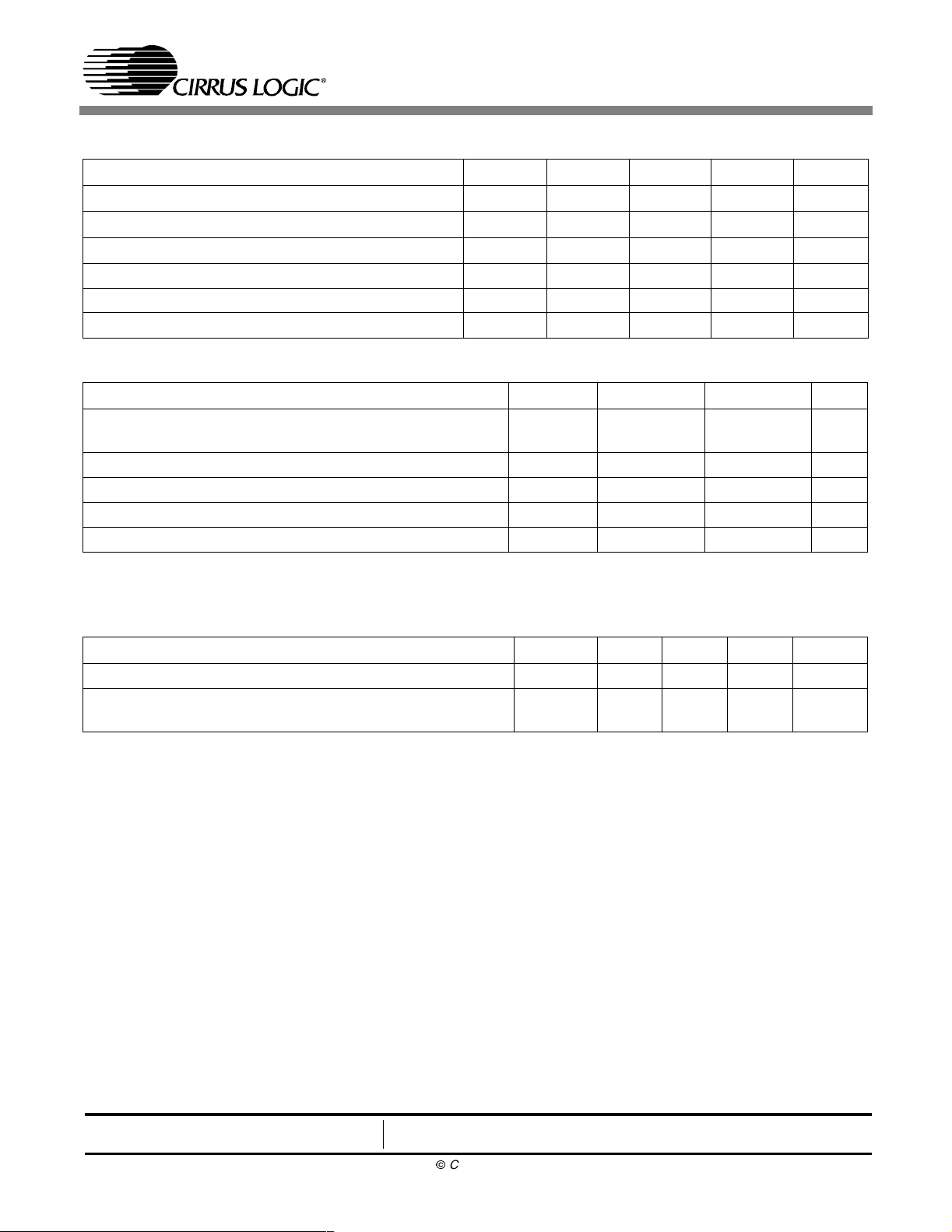

SWITCHING CHARACTERISTICS - CONTROL PORT - TWO WIRE MODE

(TA= 25° C; VL = 1.7 V - 3.6 V; Inputs: logic 0 = GND, logic 1 = VL, CL=30pF)

Parameter Symbol Min Max Unit

Two Wire Mode

SCL Clock Frequency f

RST

Rising Edge to Start t

Bus Free Time Between Transmissions t

Start Condition Hold Time (prior to first clock pulse) t

Clock Low time t

Clock High Time t

Setup Time for Repeated Start Condition t

SDA Hold Time from SCL Falling (Note 8) t

SDA Setup time to SCL Rising t

Rise Time of Both SDA and SCL Lines t

Fall Time of Both SDA and SCL Lines t

Setup Time for Stop Condition t

scl

irs

buf

hdst

low

high

sust

hdd

sud

r

f

susp

Note: 8. Data must be held for sufficient time to bridge the transition time, t

RST

t

irs

Stop S tart

Repeated

Start

- 100 KHz

500 - ns

4.7 - µs

4.0 - µs

4.7 - µs

4.0 - µs

4.7 - µs

0-µs

250 - ns

-25ns

-25ns

4.7 - µs

,ofSCL.

f

Stop

SDA

SCL

t

buf

t

t

hdst

low

t

hdd

t

high

t

sud

t

sust

t

hdst

t

f

t

r

t

susp

Figure 3. Control Port Timing - Two Wire Mode

Preliminary Product Information

DS513PP1 11

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 12

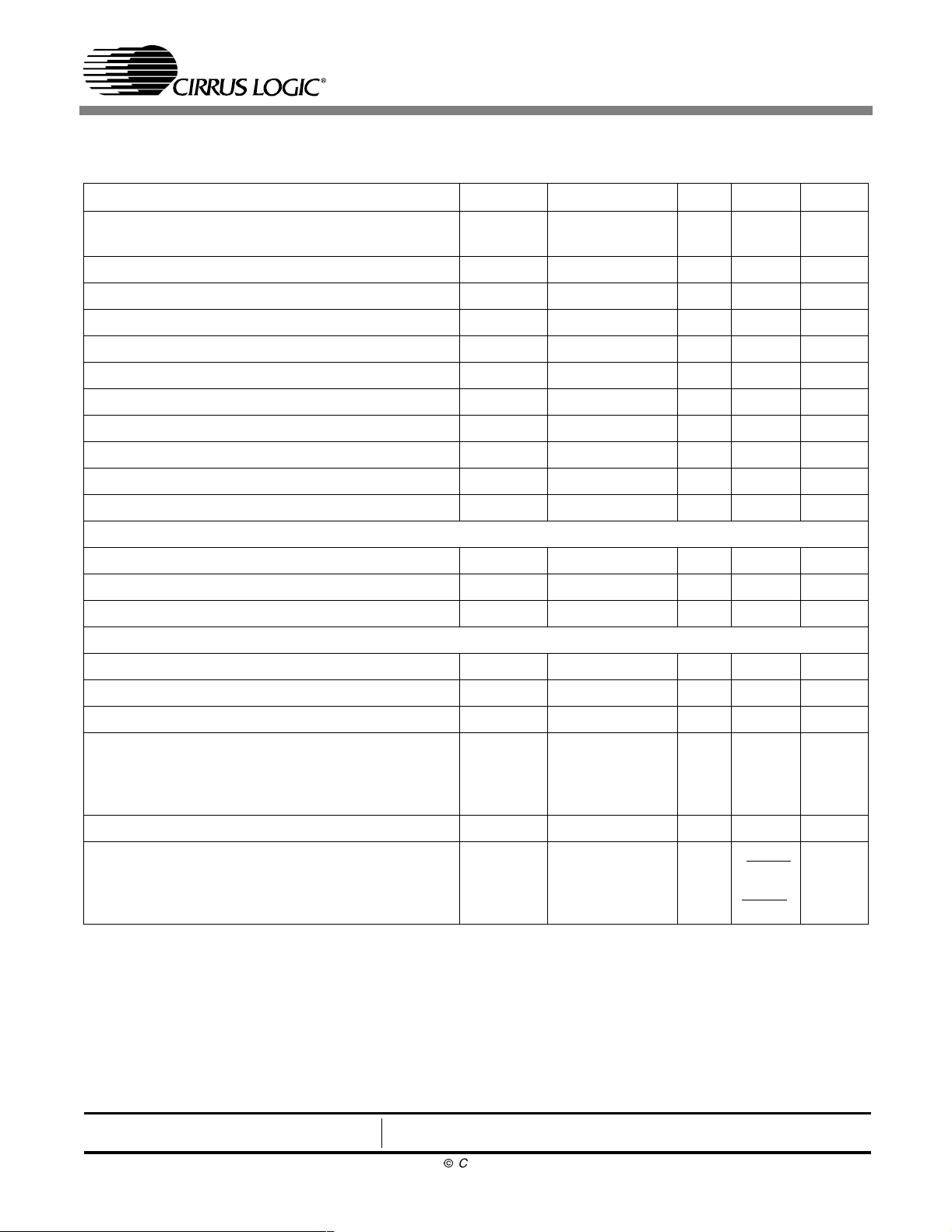

SWITCHING CHARACTERISTICS - CONTROL PORT - SPI MODE

(TA=25°C; VL = 1.7V - 3.6V; Inputs: logic 0 = GND, logic 1 = VL, CL=30pF)

Parameter Symbol Min Max Unit

SPI Mode

CCLK Clock Frequency f

Rising Edge to CS Falling t

RST

CCLK Edge to CS

High Time Between Transmissions t

CS

Falling to CCLK Edge t

CS

Falling (Note 9) t

CCLK Low Time t

CCLK High Time t

CDIN to CCLK Rising Setup Time t

CCLK Rising to DATA Hold Time (Note 10) t

Rise Time of CCLK and CDIN (Note 11) t

Fall Time of CCLK and CDIN (Note 11) t

sclk

srs

spi

csh

css

scl

sch

dsu

dh

r2

f2

-6MHz

500 - ns

500 - ns

1.0 - µs

20 - ns

66 - ns

66 - ns

40 - ns

15 - ns

- 100 ns

- 100 ns

CS53L32A

Notes: 9. t

10. Data must be held for sufficient time to bridge the transition time of CCLK.

11. For F

only needed before first falling edge of CS after RST rising edge. t

spi

<1MHz.

SCLK

RST

CS

CCLK

CDIN

t

t

srs

spi

t

css

t

r2

t

t

scl

t

t

f2

dsu

sch

t

dh

Figure 4. Control Port Timing - SPI Mode

= 0 at all other times.

spi

t

csh

Preliminary Product Information

12 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 13

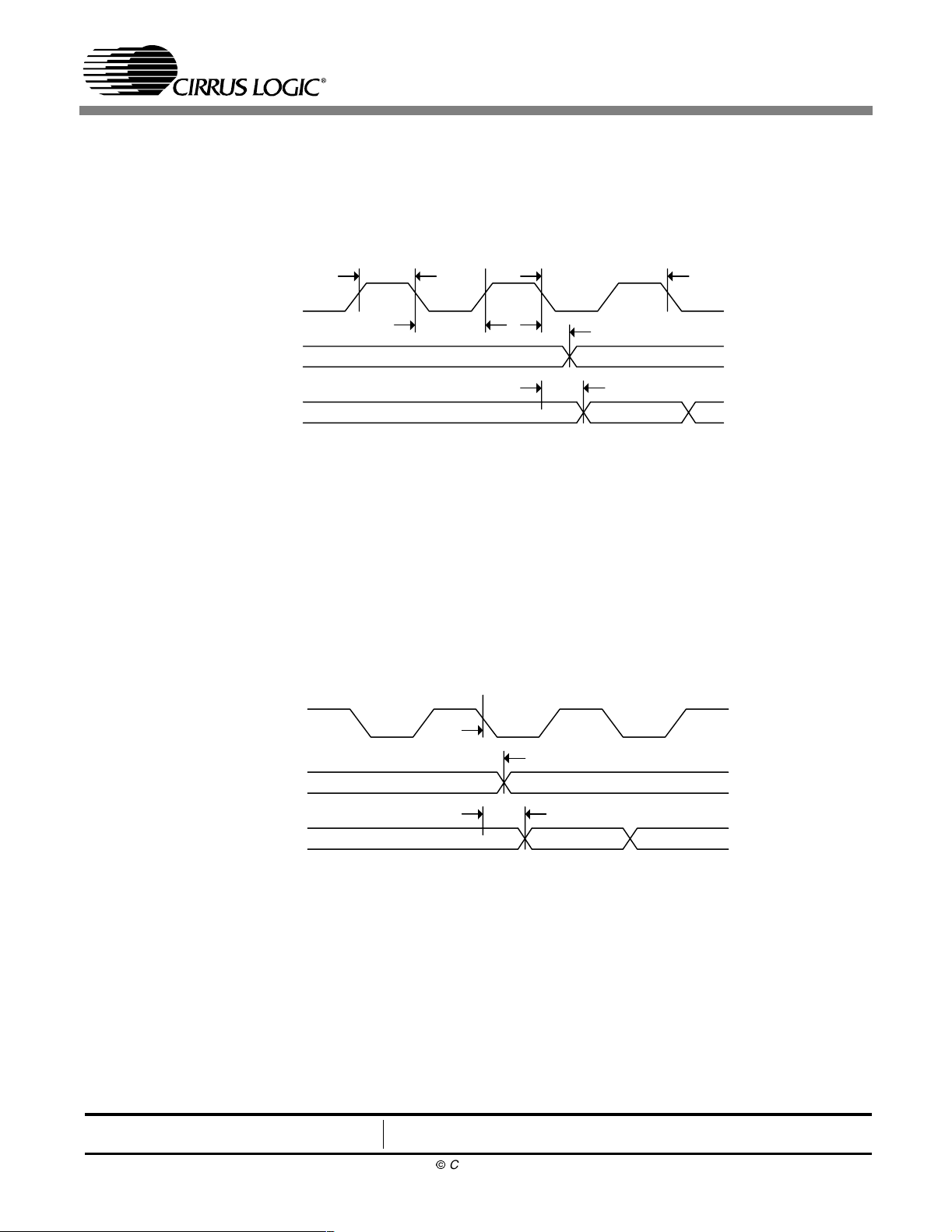

2. TYPICAL CONNECTION DIAGRAM

*Ferrite

1.8to3.3V

Supply

bead

1.0 µF

+

0.1 µF

5

VA

CS53L32A

1.8to3.3V

Supply

*Ferrite

bead

1.0 µF

Ω

150

Ω

150

Ω

150

Ω

150

+

0.47 µF

**

0.47 µF

**

0.47 µF

**

0.47 µF

**

1

0.1 µF

18

0.01 µF

17

0.01 µF

15

0.01 µF

14

0.01 µF

VL

AIN_L1

AIN_R1

AIN_L2

AIN_R2

CS53L32A

SDA/CDIN/DIF

SCL/CCLK/ChSEL

FILT+

REF_GND

VQ

MCLK

LRCK

SCLK

SDOUT

RST

AD0/CS/DIV

13

16

19

2

7

3

4

20

10

1.0 µF

+

9

8

1.0 µF

+

Digital

Audio

Source

µc/

Mode

Configuration

**Optional if analog input

circuit is biased within

±5% of CS53L32

nominal bias voltage

* Optional

AFLTL

AFLTR

GND

12

11

1nF1nF

6

Figure 5. Typical Connection Diagram

Preliminary Product Information

DS513PP1 13

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 14

CS53L32A

3. REGISTER QUICK REFERENCE

** “default” ==> bit status after power-up-sequence or reset.

3.1 I/O and Power Control (address 01h)

76543210

RESERVED BOOST AINMUX1 AINMUX0 RESERVED RESERVED PDN CP_EN

00000010

BOOST 20 dB Digital Gain

Default = ‘0’

0 - Disabled

1 - Enabled

AINMUX Analog Input Mulitplexer

Default =’0’.

0 - AIN_L1/AIN_R1 direct to A/D (default)

1 - AIN_L2/AIN_R2 direct to A/D

2 - AIN_L2/AIN_R2 through PGA to A/D

3-Reserved

PDN Power-Down

Default =’1’.

0 - Disabled

1 - Enabled

CP_EN Control Port Enable

Default =’0’.

0 - Disabled

1 - Enabled

3.2 Interface Control (address 02h)

76543210

RESERVED MCLKDIV RATIO1 RATIO0 MASTER DIF2 DIF1 DIF0

00000000

MCLKDIV Master Clock Divider

Default =’0’.

0 - Disabled

1 - Enabled

RATIO1-0 Master Clock Ratio

Default =’0’.

0 - 128x (default)

1 - 192x

2 - 256x

3 - 384x

MASTER Master Mode

Default =’0’.

0-SlaveMode

1 - Master Mode

Preliminary Product Information

14 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 15

CS53L32A

DIF2-0 Digital Interface Format

Default = ‘0’.

2

0-I

S, up to 24-bit Data, Data valid on positive edge of SLCK (default)

1 - Left Justified, up to 24-bit Data, Data valid on positive edge of SLCK

2-Reserved

3 - Right Justified, 16-bit Data, Data valid on positive edge of SLCK

4 - Right Justified, 24-bit Data, Data valid on positive edge of SLCK

5 - Right Justified, 18-bit Data, Data valid on positive edge of SLCK

6 - Right Justified, 20-bit Data, Data valid on positive edge of SLCK

7-Reserved

3.3 Analog I/O Control (address 03h)

76543210

MUTEL MUTER SOFT ZC RESERVED INDVC L=R HPFREEZE

00110000

MUTEL Left Channel Mute

Default = ‘0’.

0 - Disabled

1 - Enabled

MUTER Right Channel Mute

Default = ‘0’.

0 - Disabled

1 - Enabled

SOFT Soft Digital/Analog Volume Control

Default = ‘1’.

0 - Disabled

1 - Enabled

ZC Analog Zero Cross Detection Control

Default = ‘1’.

0 - Disabled

1 - Enabled

INDVC Independent Volume Control Enable

Default = ‘0’.

0 - Disabled

1 - Enabled

L=R Left Channel Volume = Right Channel Volume

Default = ‘0’.

0 - Left channel volume is determined by the left channel volume control registers and right

channel volume is determined by the right channel volume control registers.

1 - Left and right channel volumes are determined by the left channel volume control registers

and the right channel volume control registers are ignored.

HPFREEZE High-pass filter freeze

Default = ‘0’.

0 - Disabled

1 - Enabled

Preliminary Product Information

DS513PP1 15

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 16

CS53L32A

3.4 Left Channel Digital Volume Control (address 04h)

3.5 Right Channel Digital Volume Control (address 05h)

76543210

VOL7 VOL6 VOL5 VOL4 VOL3 VOL2 VOL1 VOL0

00000000

VOL7-0 Volume

Default = ‘0’.

(Refer to Table 13)

3.6 Analog Gain Control (address 06h)

76543210

LVOL3 LVOL2 LVOL1 LVOL0 RVOL3 RVOL2 RVOL1 RVOL0

00000000

LVOL3-0 Left Analog Gain

Default = ‘0’.

(Refer to Table 14)

RVOL3-0 Right Analog Gain

Default = ‘0’.

(Refer to Table 14)

3.7 Clip Detection Status (address 07h)

76543210

RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED CLIP_L_FLAG CLIP_R_FLAG

00000000

CLIP_L_FLAG Left Channel Clip Detection

CLIP_R_FLAG Right Channel Clip Detection

Default = ‘0’.

0 - No Clipping Detected

1 - Clipping Detected

Preliminary Product Information

16 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 17

CS53L32A

4. REGISTER DESCRIPTION

4.1 GAIN ENABLE

I/O and Power Control Register (address 01h)

76543210

RESERVED BOOST AINMUX1 AINMUX0 RESERVED RESERVED PDN CP_EN

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0 - Disabled

Function:

Applies a 20 dB digital gain to the input signal, regardless of the input path.

4.2 ANALOG INPUT MULTIPLEXER

I/O and Power Control Register (address 01h)

76543210

RESERVED BOOST AINMUX1 AINMUX0 RESERVED RESERVED PDN CP_EN

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0 - AIN_L1/AIN_R1 direct to A/D

Function:

The analog input multiplexer selects the input channel as well as the input path associated with various gain stages.

AINMUX MODE

0 AIN_L1/AIN_R1 direct to A/D

1 AIN_L2/AIN_R2 direct to A/D

2 AIN_L2/AIN_R2 through PGA to A/D

3 Reserved

Table 1. Analog Input Options

Preliminary Product Information

DS513PP1 17

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 18

CS53L32A

4.3 POWER-DOWN

I/O and Power Control Register (address 01h)

76543210

RESERVED BOOST AINMUX1 AINMUX0 RESERVED RESERVED PDN CP_EN

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

1-Enabled

Function:

The entire device will enter a low-power state whenever this function is activated. The power-down

bit defaults to ‘enabled’ on power-up and must be disabled before normal operation will begin. The

contents of the control registers are retained when this mode is enabled.

PDN MODE

0 Disabled

1 Enabled

Table 2. Power-Down Enable

4.4 CONTROL PORT ENABLE

I/O and Power Control Register (address 01h)

76543210

RESERVED BOOST AINMUX1 AINMUX0 RESERVED RESERVED PDN CP_EN

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0 - Disabled

Function:

The CS53L32A will enter Control Port mode when this bit is enabled. Stand-Alone is the default power up mode. See Section 6.3, Recommended Power-up Sequence, for more details.

CP_EN MODE

0Disabled

1 Enabled

Table 3. Control Port Enable

Preliminary Product Information

18 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 19

CS53L32A

4.5 MASTER CLOCK DIVIDE

Interface Control Register (address 02h)

76543210

RESERVED MCLKDIV RATIO1 RATIO0 MASTER DIF2 DIF1 DIF0

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0 - Disabled

Function:

Divides MCLK by two prior to all other chip circuitry.

MCLKDIV MODE

0 Disabled

1 Enabled

Table4.MasterClockDivideSelect

4.6 MASTER CLOCK RATIO

Interface Control Register (address 02h)

76543210

RESERVED MCLKDIV RATIO1 RATIO0 MASTER DIF2 DIF1 DIF0

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0 - 128x

Function:

Sets the ratio of MCLK to LRCK.

RATIO1,0 MCLK/LRCK RATIO (MCLKDIV=0) MCLK/LRCK RATIO (MCLKDIV=1)

0 128x 256x

1 192x 384x

2 256x 512x

3 384x 768x

Table 5. MCLK/LRCK Ratios

Preliminary Product Information

DS513PP1 19

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 20

CS53L32A

4.7 MASTER MODE

Interface Control Register (address 02h)

76543210

RESERVED MCLKDIV RATIO1 RATIO0 MASTER DIF2 DIF1 DIF0

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0-SlaveMode

Function:

Configures the device for master or slave operation when in Control Port mode.

MASTER MODE

0 Slave Mode

1 Master Mode

Table 6. Master/Slave Mode Selection

4.8 DIGITAL INTERFACE FORMAT

Interface Control Register (address 02h)

76543 210

RESERVED MCLKDIV RATIO1 RATIO0 MASTER DIF2 DIF1 DIF0

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0-Format0(I2S, up to 24-bit data, Data valid on positive edge of SCLK)

Function:

The required relationship between the Left/Right clock, serial clock and serial data is defined by the

Digital Interface Format and the options are detailed in Figures 17 through 20.

DIF2 DIF1 DIF0 DESCRIPTION Format FIGURE

000

0 0 1 Left Justified, up to 24-bit Data, Data valid on positive edge of SCLK 1 18

0 1 0 Reserved 2 0 1 1 Right Justified, 16-bit Data, Data valid on positive edge of SCLK 3 18

1 0 0 Right Justified, 24-bit Data, Data valid on positive edge of SCLK 4 19

1 0 1 Right Justified, 18-bit Data, Data valid on positive edge of SCLK 5 20

1 1 0 Right Justified, 20-bit Data, Data valid on positive edge of SCLK 6 21

1 1 1 Reserved 7 -

2

S, up to 24-bit Data, Data valid on positive edge of SCLK

I

Table 7. Digital Interface Format

017

Preliminary Product Information

20 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 21

CS53L32A

4.9 LEFT/RIGHT CHANNEL MUTE

Analog I/O Control (address 03h)

76543210

MUTEL MUTER SOFT ZC RESERVED INDVC L=R HPFREEZE

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0 - Disabled

Function:

Digital mute of the left and right channels.

MUTEL/

MUTER

0 Disabled

1 Enabled

Table 8. Left/Right Channel Mute Enable

MODE

4.10 SOFT RAMP AND ZERO CROSS ENABLE

Analog I/O Control Register (address 03h)

76543210

MUTEL MUTER SOFT ZC RESERVED INDVC L=R HPFREEZE

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

11 - Soft Ramp and Zero Cross enabled

Function:

Soft Ramp Enable

Soft Ramp allows level changes, both muting and attenuation, to be implemented via an incremental

ramp. Digital volume control is ramped from the current level to the new level at a rate of 1/8 dB per

left/right clock period. Analog volume control is ramped in 1 dB steps every 8 left/right clock periods

in Base Rate mode, and 1 dB every 16 left/right clock periods in High Rate mode.

Zero Cross Enable

Zero Cross Enable dictates that signal level changes, either by attenuation changes or muting, will

occur on a signal zero crossing to minimize audible artifacts. The requested level change will occur

after a timeout period of 512 sample periods in BRM or 1024 sample periods in HRM (approximately

10.7 ms at 48 kHz sample rate) if the signal does not encounter a zero crossing. The zero cross function is independently monitored and implemented for each channel.

Preliminary Product Information

DS513PP1 21

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 22

CS53L32A

Soft Ramp and Zero Cross Enable

Soft Ramp and Zero Cross Enable dictates that signal level changes, either by attenuation changes

or muting, will occur in 1 dB steps and be implemented on a signal zero crossing. The level change

will occur after a timeout period of 512 sample periods in BRM or 1024 sample periods in HRM (approximately 10.7 ms at 48 kHz sample rate) if the signal does not encounter a zero crossing. The

zero cross function is independently monitored and implemented for each channel.

SOFT/ZC ANALOG VOLUME CONTROL MODES

00 Change volume immediately

01 Change volume at next zero cross time

10 Change volume in 1 dB steps

11 Change volume in 1 dB steps at every zero cross time

Table 9. Analog Volume Control

.

SOFT DIGITAL VOLUME CONTROL MODES

0 Change volume immediately

1 Change volume in1/8 dB steps

Table 10. Digital Volume Control

4.11 INDEPENDENT VOLUME CONTROL ENABLE

Analog I/O Control Register (address 03h)

76543210

MUTEL MUTER SOFT ZC RESERVED INDVC L=R HPFREEZE

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0 - Disabled

Function:

When this function is disabled, the AIN_L and AIN_R volume levels are controlled by the Left and

Right Volume Control registers and the Independent Analog Gain Control registers are ignored.

When this function is enabled, the volume levels are determined by both the Volume Control registers

and the Independent Analog Gain Control registers.

INDVC MODE

0 Disabled

1 Enabled

Table 11. Independent Volume Control Enable

Preliminary Product Information

22 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 23

CS53L32A

4.12 LEFT CHANNEL VOLUME = RIGHT CHANNEL VOLUME

Analog I/O Control (address 03h)

76543210

MUTEL MUTER SOFT ZC RESERVED INDVC L=R HPFREEZE

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0 - Disabled

Function:

When this function is disabled, the left channel volume is determined by the left channel volume control register and right channel volume is determined by the right channel volume control register.

When enabled, the left and right channel volumes are determined by the left channel volume control

register and the right channel volume control register is ignored.

4.13 HIGH-PASS FILTER FREEZE

Analog I/O Control Register (address 03h)

76543210

MUTEL MUTER SOFT ZC RESERVED INDVC L=R HPFREEZE

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0 - Disabled

Function:

The high-pass filter works by continuously subtracting a measure of the dc offset from the output of

the decimation filter. If the HPFREEZE bit is taken low during normal operation, the current value of

the dc offset is frozen and this dc offset will continue to be subtracted from the conversion result. This

feature makes it possible to perform a system calibration by:

1) removing the signal source at the input to the subsystem containing the CS53L32A,

2) running the CS53L32A with the HPFREEZE bit high until the filter settles, approximately

one second,

3) taking the HPFREEZE bit low, thus disabling the high-pass filter and freezing the stored dc offsett.

A system calibration performed in this way will eliminate offsets anywhere in the signal path between

the calibration point and the CS53L32A.

HPFREEZE MODE

0Frozen

1 Enabled

Table 12. High-Pass Filter Enable

Preliminary Product Information

DS513PP1 23

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 24

CS53L32A

4.14 VOLUME CONTROL

Left Channel Volume Control Register (address 04h)

Right Channel Volume Control Register (address 05h)

76543210

VOL7 VOL6 VOL5 VOL4 VOL3 VOL2 VOL1 VOL0

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0 - 0 dB (No attenuation)

Function:

The Volume Control allows the user to alter the signal level in 1 dB increments from +12 to -96 dB, when

the INDVC bit is disabled. When INDVC is enabled, the Volume Control can be altered in 1 dB increments

from 0 to -96 dB. Volume settings are decoded as shown in Table 13, using a 2’s complement code. The

volume changes are implemented as dictated by the Soft and Zero Cross bits in the Analog I/O Control

register. All volume settings less than -96 dB are equivalent to muting the channel.

Binary Code Decimal Value Volume Setting

00001010 12 +12 dB

00000111 7 +7 dB

00000000 0 0 dB

11000100 -60 -60 dB

10100110 -90 -90 dB

Table 13. Example Volume Settings

Preliminary Product Information

24 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 25

CS53L32A

4.15 LEFT/RIGHT ANALOG GAIN

ADC Independent Analog Gain Control Register (address 06h)

76543210

LVOL3 LVOL2 LVOL1 LVOL0 RVOL3 RVOL2 RVOL1 RVOL0

Access:

R/W in Two Wire Mode and write only in SPI.

Default:

0-0dB(NoGain)

Function:

The level of the left and right analog channels can be adjusted in 1 dB increments as dictated by the

Soft Ramp and Zero Cross bits from 0 to +12 dB when routed throgh the PGA via the AINMUX bits

in Control Port mode or the CH_SEL pins in Stand-Alone mode. Levels are decoded as shown in

Table 14. Levels above +12 dB are interpreted as +12 dB.

Binary Code Decimal Value Volume Setting

0000 0 0 dB

0010 2 +2 dB

1010 6 +6 dB

1001 9 +9 dB

1100 12 +12 dB

Table 14. Example Gain Settings

4.16 CLIP DETECTION

Clip Detection Status Register (address 07h)

76543210

RESERVED RESERVED RESERVED RESERVED RESERVED RESERVED CLIP_L_FLAG CLIP_R_FLAG

Access:

Read only in Two Wire Mode and unavailable in SPI.

Default:

0 - No Clipping Detected

Function:

The Clip Flags indicate when there is an over-range condition anywhere in the CS53L32A internal signal

path. These bits are “sticky”. They constantly monitor the ADC signal path and are set to 1 when an overrange condition occurs. They are reset to 0 when read.

CLIP_L_FLAG

CLIP_R_FLAG

0 Signal within normal range

1 Signal is over-range

Table 15. Clip Detection Status Bits

Condition

Preliminary Product Information

DS513PP1 25

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 26

5. PIN DESCRIPTION

CS53L32A

Interface Power VL RST Reset

Master Clock MCLK VQ Quiescent Voltage

Serial Clock SCLK AIN_L1 Analog Input 1 Left

Serial Audio Data Out SDOUT AIN_R1 Analog Input 1 Right

Analog Power VA REF_GND Reference Ground

Ground GND AIN_L2 Analog Input 2 Left

Left/Right Clock LRCK AIN_R2 Analog Input 2 Right

AD0/CS

/DIV AD0/CS/DIV FILT+ Positive Voltage Reference

SDA/CDIN/DIF SDA/CDIN/DIF AFLTL Anti-Aliasing Capacitor

SCL/CCLK/ChSEL SCL/CCLK/ChSEL AFLTR Anti-Aliasing Capacitor

Interface Power 1 VL (Input) - Digital interface power supply. Typically 1.8 to 3.3 VDC.

Master Clock 2 MCLK (Input) - The master clock frequency must be either 256x, 384x,

512x, 768x or 1024x the input sample rate in Base Rate Mode (BRM) and

128x, 192x, 256x, 384x the input sample rate in High Rate Mode (HRM).

Table 18 illustrates several standard audio sample rates and the required

master clock frequencies.

Serial Clock 3 SCLK (Input/Output) - Clocks the individual bits of the serial data out of the

SDOUT pin. The required relationship between the Left/Right clock, serial

clock and serial data is defined by the DIF2-0 bytes when in Control Port

mode or by the DIF1-0 pins when in Stand-Alone mode.

Serial Audio Data Out 4 SDOUT (Output) - Two's complement MSB-first serial data is output on this

pin. The data is clocked out of SDOUT via the serial clock and the channel is

determined by the Left/Right clock. The required relationship between the

Left/Right clock, serial clock and serial data is defined by the DIF2-0 bytes

when in Control Port mode or by the DIF pin when in Stand-Alone mode.

Analog Power 5 VA (Input) - Analog power supply. Typically 1.8 to 3.3 VDC.

Ground 6 GND (Input) - Ground Reference.

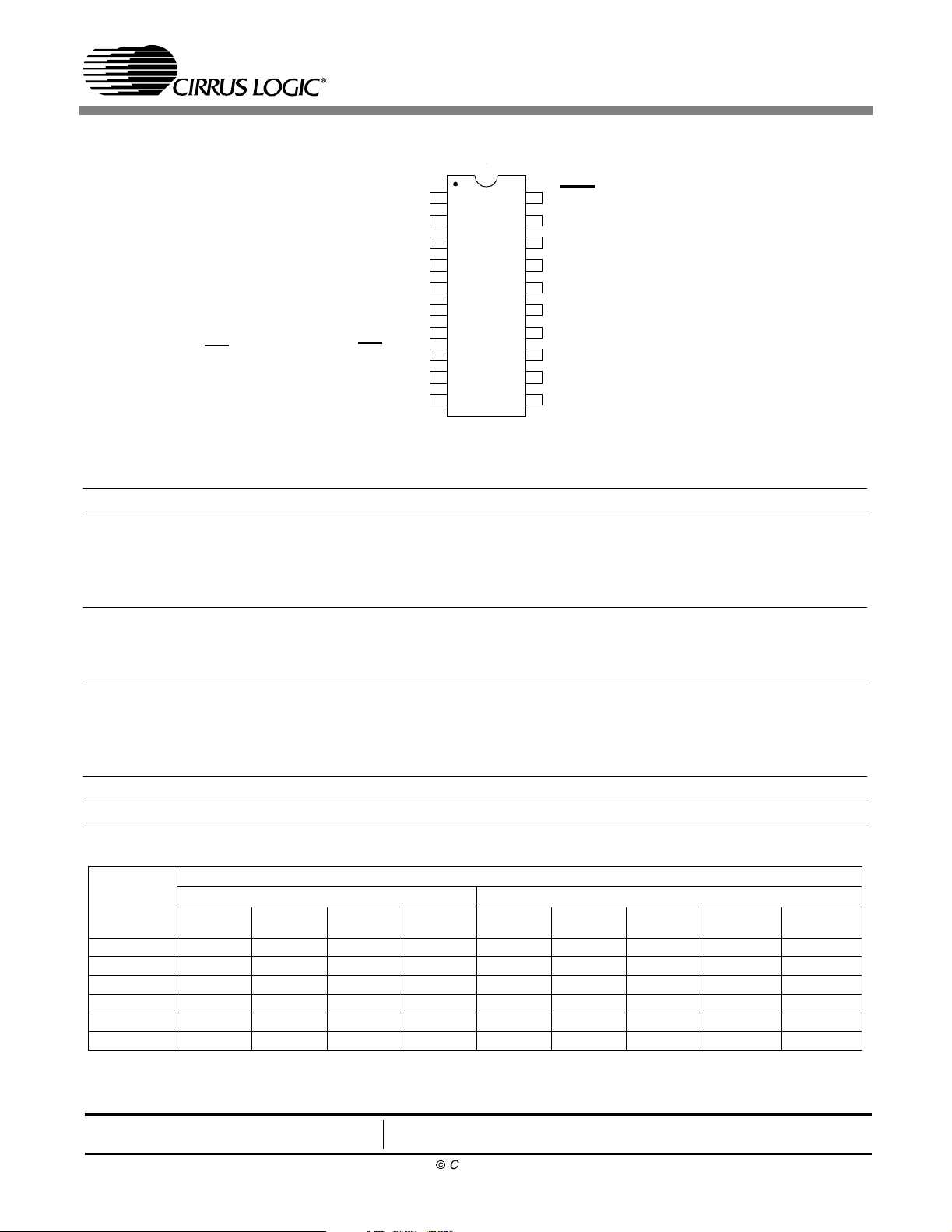

1

1

2

2

3

4

5

5

6

6

7

8

9

10 11

20

19

18

17

16

15

14

13

12

MCLK (MHz)

Sample

Rate

(kHz)

32 4.0960 6.1440 8.1920 12.2880 8.1920 12.2880 16.3840 24.5760 32.7680

44.1 5.6448 8.4672 11.2896 16.9344 11.2896 16.9344 22.5792 32.7680 45.1584

48 6.1440 9.2160 12.2880 18.4320 12.2880 18.4320 24.5760 36.8640 49.1520

64 8.1920 12.2880 16.3840 24.5760 - - - - -

88.2 11.2896 16.9344 22.5792 33.8688 - - - - 96 12.2880 18.4320 24.5760 36.8640 - - - - -

* MCLKDIV = 1 in Control Port mode or DIV= Hi when in Stand-Alone mode

128x 192x 256x* 384x* 256x 384x 512x 768x* 1024x*

Preliminary Product Information

26 DS513PP1

HRM BRM

Table 18. Common Clock Frequencies

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 27

CS53L32A

Left/Right Clock 7 LRCK (Input/Output) - The Left/Right clock determines which channel is cur-

rently being output on the serial audio data line SDOUT. The frequency of

the Left/Right clock must be at the input sample rate. The required relationship between the Left/Right clock, serial clock and serial data is defined by

the DIF2-0 bytes when in Control Port mode or by the DIF pin when in

Stand-Alone mode.

Address Bit 8 AD0/CS

address bit. CS

MCLK Divide Enable 8 DIV (Stand-Alone Mode) (Input) - When high, the chip will enter High Rate

Mode. When this pin is low, the chip will enter Base Rate Mode.

Serial Control Data I/O 9 SDA/CDIN (Control Port Mode) (Input/Output) - In Two Wire mode,SDA is

a data I/O line. CDIN is the input data line for the control port interface in SPI

mode.

Digital Interface Format 9 DIF (Stand-Alone Mode) (Input) - The required relationship between the

Left/Right clock, serial clock and serial data is defined by the Digital Interface

Format.

(Control Port Mode) (Input) - In Two Wire mode, AD0 is a chip

is used to enable the control port interface in SPI mode.

DIF DESCRIPTION

0

1 Left Justified, up to 24-bit data

2

I

S, up to 24-bit data

Table 16. Digital Interface Format - DIF

(Stand-Alone Mode)

Serial Control

Interface Clock

Channel Select 10 ChSEL (Stand-Alone Mode) (Input) - The analog data path is determined

10 SCL/CCLK (Control Port Mode) (Input) - Clocks the serial control data into

or from SDA/CDIN/DIF.

by the Channel Select bit. These options are detailed in Table 17.

ChSEL DESCRIPTION

0 Channel 1 directly to A/D

1 Channel 2 with 32dB of gain

Table 17. Channel Select Options

Anti-Aliasing Capacitors 11 , 12 AFLTR, AFLTL (Output) - Anti-aliasing capacitors for the left and right chan-

nels. An external capacitor is required from AFLTR and AFLTL to ground, as

shown in Figure 4. AFLTR and AFLTL are not intended to supply external

current, and any current drawn from these pins will alter device performance.

Positive Voltage

Reference

Analog Inputs 14, 15, 17, and 18 AIN_R1, AIN_L1, AIN_R2, AIN_L2 (Input) - Channel 1/Channel 2 analog

Reference Ground 16 REF_GND (Input) - Ground reference for the internal sampling circuits. Must

13 FILT+ (Output) - Positive reference for internal sampling circuits. An exter-

nal capacitor is required from FILT+ to ground, as shown in Figure 5. The

recommended value will typically provide 60 dB of PSRR at 1 kHz and

40 dB of PSRR at 60 Hz. FILT+ is not intended to supply external current.

FILT+ has a typical source impedence of 250 kΩ and any current drawn

from this pin will alter device performance.

inputs.

be connected to ground.

Preliminary Product Information

DS513PP1 27

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 28

CS53L32A

Quiescent Voltage 19 VQ (Output) - Filter connection for internal A/D converter quiescent refer-

ence voltage. A capacitor must be connected from VQ to ground. VQ is not

intended to supply external current. VQ has a typical source impedence of

250 kΩ and any current drawn from this pin will alter device performance.

Reset 20 RST

(Input) - The device enters a low power mode and all internal registers

are reset to their default settings, including the control port, when low. When

high, the control port becomes operational and the PDN bit must be cleared

before normal operation will occur. The control port cannot be accessed

when Reset is low.

Preliminary Product Information

28 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 29

CS53L32A

6. APPLICATIONS

6.1 Grounding and Power Supply Decoupling

As with any high resolution converter, the

CS53L32A requires careful attention to power supply and grounding arrangements to optimize performance. Figure 5 shows the recommended power

arrangement with VA and VL connected to clean

supplies. Decoupling capacitors should be located

as close to the device package as possible.

6.2 Oversampling Modes

The CS53L32A operates in one of two oversampling modes. Base Rate Mode supports input sample rates up to 50 kHz while High Rate Mode

supports input sample rates up to 100 kHz. See

Table 18 for more details.

6.3 Recommended Power-up Sequence

1) Hold RST low until the power supply, master,

and left/right clocks are stable. In this state, the

control port is reset to its default settings and

VQ will remain low.

2) Bring RST high. The device will remain in a

low power state with VQ low and will initiate

the Stand-Alone power-up sequence. The control port will be accesable at this time. If control port operation is desired, write the CP_EN

bit prior to the completion of the Stand-Alone

power-up sequence, approximately

1024 LRCK cycles. Writing this bit will halt

the Stand-Alone power-up sequence and initialize the control port to its default settings.

The desired register settings can be loaded

while keeping the PDN bit set to 1.

3) If Control Port mode is selected via the CP_EN

bit, set the PDN bit to 0 which will initiate the

power-up sequence, which requires approxi-

mately 50 µS.

7. CONTROL PORT INTERFACE

The control port is used to load all the internal settings. The operation of the control port may be

completely asynchronous with the audio sample

rate. However, to avoid potential interference problems, the control port pins should remain static if

no operation is required.

The control port has 2 modes: SPI and Two Wire.

If Two Wire operation is desired, AD0/CS should

be tied to VL or GND. If the CS53L32A ever detects a high to low transition on AD0/CS

after pow-

er-up, SPI mode will be selected.

7.1 SPI Mode

In SPI mode, CS is the CS53L32A chip select signal, CCLK is the control port bit clock, CDIN is the

input data line from the microcontroller and the

chip address is 0010000. All signals are inputs and

data is clocked in on the rising edge of CCLK. All

CS53L32A registers are write-only in SPI mode.

Figure 6 shows the operation of the control port in

SPI mode. To write to a register, bring CS

first 7 bits on CDIN form the chip address, and

must be 0010000. The eighth bit is a read/write indicator (R/W

), which must be low to write. The

next 8 bits form the Memory Address Pointer

(MAP), which is set to the address of the register

that is to be updated. The next 8 bits are the data

which will be placed into the register designated by

the MAP.

The CS53L32A has a MAP auto increment capability, enabled by the INCR bit in the MAP. If

INCR is a zero, then the MAP will stay constant for

successive writes. If INCR is set to a 1, then MAP

will auto increment after each byte is written, allowing block writes of successive registers.

low. The

Preliminary Product Information

DS513PP1 29

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 30

CS53L32A

7.2 Two Wire Mode

In Two Wire mode, SDA is a bidirectional data

line. Data is clocked into and out of the part by the

clock, SCL, with the clock to data relationship as

shown in Figure 7. There is no CS

forms the partial chip address and should be tied to

VL or GND as required. The upper 6 bits of the 7

bit address field must be 001000. To communicate

with the CS53L32A the LSB of the chip address

field, which is the first byte sent to the CS53L32A,

should match the setting of the AD0 pin. The eighth

bit of the address byte is the R/W

read, low for a write). If the operation is a write, the

next byte is the Memory Address Pointer which selects the register to be read or written. See Section

7.3, Memory Address Pointer (MAP). If the operation is a read, the contents of the register pointed to

7.3 MEMORY ADDRESS POINTER (MAP)

pin. Pin AD0

bit (high for a

by the Memory Address Pointer will be output. Setting the auto increment bit in MAP, allows successive reads or writes of consecutive registers. Each

byte is separated by an acknowledge bit.

Note: The Two-Wire control port mode is compatible

with the I

2

Cprotocol.

76543210

INCR Reserved Reserved Reserved Reserved MAP2 MAP1 MAP0

00000000

INCR (Auto MAP Increment Enable)

Default = ‘0’.

0 - Disabled

1 - Enabled

MAP0-2 (Memory Address Pointer)

Default = ‘000’.

Preliminary Product Information

30 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 31

CS

CCLK

CS53L32A

CDIN

CHIP

ADDRESS

0010000

R/W

MAP

MSB

byte 1

DATA

LSB

byte n

MAP = Memory Address Pointer

Figure 6. Control Port Timing, SPI Mode

N ote 1

SDA

001000

ADDR

AD0

R/W

ACK

DATA

1-8

ACK

DATA

1-8

ACK

SCL

Start

Note: If o peration is a w rite, this byte conta in s the M em ory A ddress Po inter, M AP.

Figure 7. Control Port Timing, Two Wire Mode

Stop

Preliminary Product Information

DS513PP1 31

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 32

CS53L32A

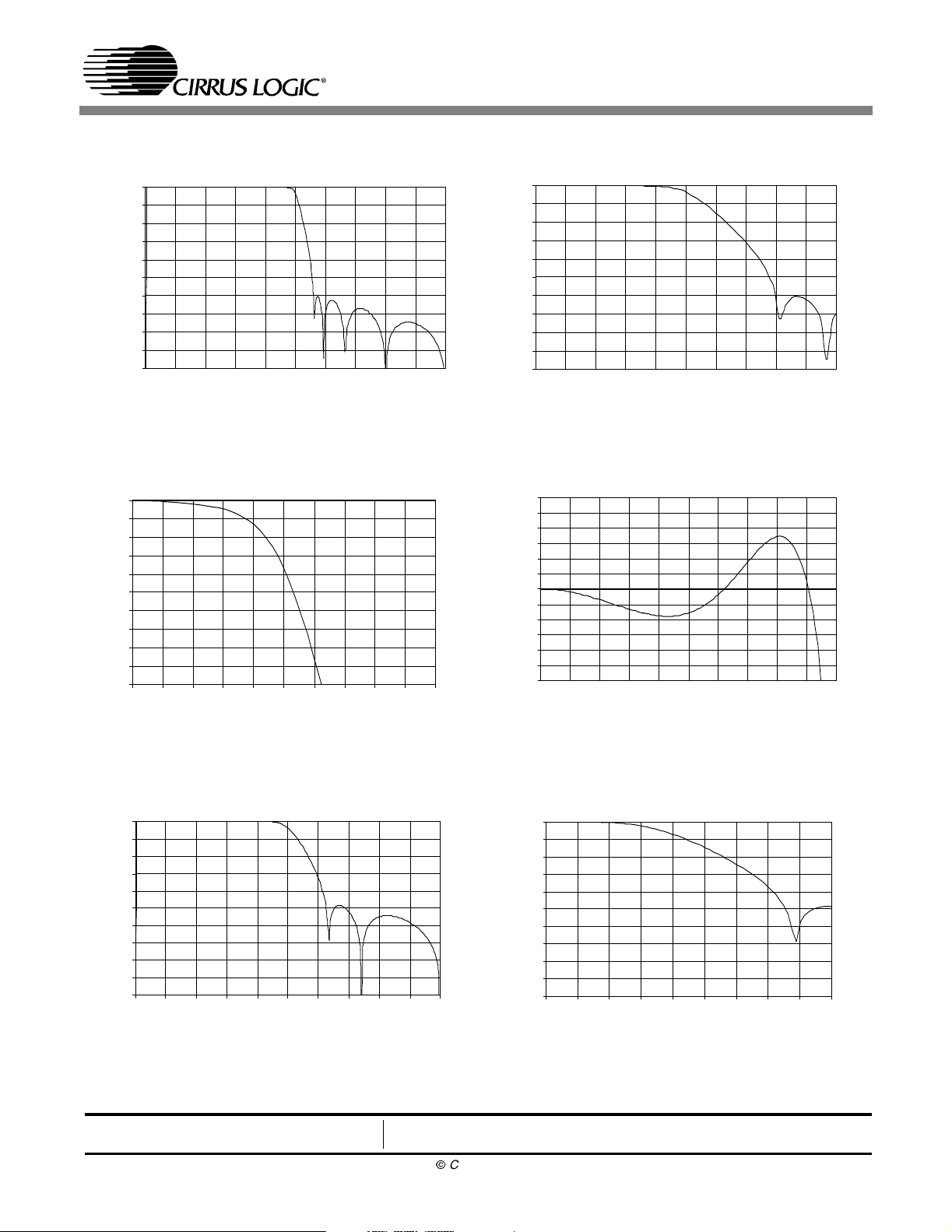

0

-10

-20

-30

-40

-50

-60

Amplitude dB

-70

-80

-90

-100

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1

Frequency (normali zed to Fs)

0

-10

-20

-30

-40

-50

-60

Amplitude dB

-70

-80

-90

-100

0.4 0. 42 0. 44 0.46 0.48 0.5 0. 52 0.54 0.56 0. 58 0.6

Frequency (normal ize d to Fs)

Figure 8. Base-Rate Stopband Rejection Figure 9. Base-Rate Transition Band

0

-1

-2

-3

-4

-5

-6

Amplitude dB

-7

-8

-9

-10

0.45 0. 46 0.47 0.48 0.49 0.5 0.51 0. 52 0. 53 0.54 0. 55

Frequency (normali zed to Fs)

0.3

0.25

0.2

0.15

0.1

0.05

0

-0.05

-0.1

Amplitude dB

-0.15

-0.2

-0.25

-0.3

0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5

Fre que ncy ( norma li ze d to Fs)

Figure 10. Base-Rate Transition Band (Detail) Figure 11. Base-Rate Passband Ripple

0

-10

-20

-30

-40

-50

-60

Amplitude dB

-70

-80

-90

-100

0 0.1 0.2 0.3 0.4 0.5 0. 6 0. 7 0. 8 0. 9 1

Frequency (normal ized to Fs)

0

-10

-20

-30

-40

-50

-60

Amplitude dB

-70

-80

-90

-100

0.4 0.43 0.46 0.49 0.52 0.55 0.58 0.61 0.64 0.67

Freque ncy (normal ize d to Fs)

Figure 12. High-Rate Stopband Rejection Figure 13. High-Rate Transition Band

Preliminary Product Information

32 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 33

CS53L32A

0

-1

-2

-3

-4

-5

-6

Amplitude dB

-7

-8

-9

-10

0. 45 0. 46 0. 47 0.48 0. 49 0.5 0. 51 0. 52 0. 53 0. 54 0. 55

Freque ncy (normal iz ed to Fs)

0. 3

0.25

0. 2

0.15

0. 1

0.05

0

-0.05

-0.1

Ampl itude dB

-0.15

-0.2

-0.25

-0.3

0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 0.5

Frequency (normalized to Fs)

Figure 14. High-Rate Transition Band (Detail) Figure 15. High-Rate Passband Ripple

Ω

150

0.47 µF

AIN_xx

Figure 16. Line Input Test Circuit

LRCK

SCLK

SDATA +3 +2 +1

MSB

-1 -2 -3 -4 -5 +3 +2 +1

Left Channel

+5 +4

Left Justified, up to 24-Bit Data. Data Valid on Rising

Edge of SCLK.

Figure 18. CS53L32A Control Port Mode - Serial Audio Format 1

LSB

0.01 µF

MSB

-1 -2 -3 -4

GND

+5 +4

Right Channel

LSB

Preliminary Product Information

DS513PP1 33

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 34

CS53L32A

LRCK

SCLK

SDATA +3 +2 +1

MSB

-1 -2 -3 -4 -5

Left Channel

+5 +4

I2S, up to 24-Bit Data. Data Valid on Rising Edge of

SCLK.

Figure 17. CS53L32A Control Port Mode - Serial Audio Format 0 (I2S)

LRCK

SCLK

SDATA

Left Channel

Right Justified, 16-Bit Data. Data Valid on Rising Edge of

32 clocks

SCLK. SCLK Must Have at Least 32 Cycles per LRCK

Period.

Figure 19. CS53L32A Control Port Mode - Serial Audio Format 3

LSB

654321 098715 14 13 12 11 10 65432 1098715 14 13 12 11 10

MSB

-1 -2 -3 -4

+5 +4

Right Channel

Right Channel

+3 +2 +1

LSB

LRCK

SCLK

SDATA

Left Channel

0

23 22 21 20 19 18

32 clocks

Right Justified, 24-Bit Data. Data Valid on Rising Edge of

65432107

23 22 21 20 19 18

Right Channel

65432107

SCLK. SCLK Must Have at Least 48 Cycles per LRCK

Period.

Figure 20. CS53L32A Control Port Mode - Serial Audio Format 4

Preliminary Product Information

34 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 35

CS53L32A

LRCK

SCLK

SDATA

LRCK

SCLK

SDATA

Right Channel

10

Left Channel

654321098715 14 13 12 11 10

32 clocks

Right Justified, 18-Bit Data. Data Valid on Rising Edge of

SCLK. SCLK Must Have at Least 36 Cycles per LRCK

Period.

Figure 21. CS53L32A Control Port Mode - Serial Audio Format 5

Left Channel

10 6543210987

17 16 17 16

19 18 19 18

15 14 13 12 11 10

32 clocks

6543210987

15 14 13 12 11 10

Right Channel

Right Justified, 20-Bit Data. Data Valid on Rising Edge of

SCLK. SCLK Must Have at Least 40 Cycles per LRCK

Period.

654321098715 14 13 12 11 1017 16 17 16

Figure 22. CS53L32A Control Port Mode - Serial Audio Format 6

LRCK

SCLK

SDATA +3 +2 +1

MSB

-1 -2 -3 -4 -5

Left Channel

+5 +4

I2S, up to 24-Bit Data. Data Valid on Rising Edge of

SCLK

Figure 23. CS53L32A Stand-Alone Mode - Serial Audio Format 0 (I2S)

LSB

MSB

-1 -2 -3 -4

Right Channel

+3 +2 +1

+5 +4

LSB

Preliminary Product Information

DS513PP1 35

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 36

CS53L32A

LRCK

SCLK

SDATA +3 +2 +1

MSB

-1 -2 -3 -4 -5 +3 +2 +1

Left Channel

+5 +4

Left Justified, up to 24-Bit Data. Data Valid on Rising

Edge of SCLK.

Figure 24. CS53L32A Stand-Alone Mode - Serial Audio Format 1

LSB

MSB

-1 -2 -3 -4

Right Channel

+5 +4

LSB

Preliminary Product Information

36 DS513PP1

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrusLogic,Inc.2002

(All Rights Reserved)

Page 37

8. PARAMETER DEFINITIONS

Total Harmonic Distortion + Noise (THD+N)

The ratio of the rms value of the signal to the rms sum of all other spectral components over the specified

bandwidth (typically 10 Hz to 20 kHz), including distortion components. Expressed in decibels.

Dynamic Range

The ratio of the full scale rms value of the signal to the rms sum of all other spectral components over the

specified bandwidth. Dynamic range is a signal-to-noise measurement over the specified bandwidth

made with a -60 dBFS signal. 60 dB is then added to the resulting measurement to refer the measurement

to full scale. This technique ensures that the distortion components are below the noise level and do not

effect the measurement. This measurement technique has been accepted by the Audio Engineering Society, AES17-1991, and the Electronic Industries Association of Japan, EIAJ CP-307.

Interchannel Isolation

A measure of crosstalk between the left and right channels. Measured for each channel at the converter's

output with all zeros to the input under test and a full-scale signal applied to the other channel. Units in

decibels.

Interchannel Gain Mismatch

The gain difference between left and right channels. Units in decibels.

CS53L32A

Gain Error

The deviation from the nominal full scale analog output for a full scale digital input.

Gain Drift

The change in gain value with temperature. Units in ppm/°C.

9. REFERENCES

1. "How to Achieve Optimum Performance from Delta-Sigma A/D & D/A Converters" by Steven Harris.

Paper presented at the 93rd Convention of the Audio Engineering Society, October 1992.

2. CDB53L32 Evaluation Board Datasheet.

3. “The I

http://www.semiconductors.philips.com

2

C-Bus Specification: Version 2.0” Phillips Semiconductors, December 1998.

Preliminary Product Information

DS513PP1 37

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

CopyrightCirrus Logic, Inc. 2002

(All Rights Reserved)

Page 38

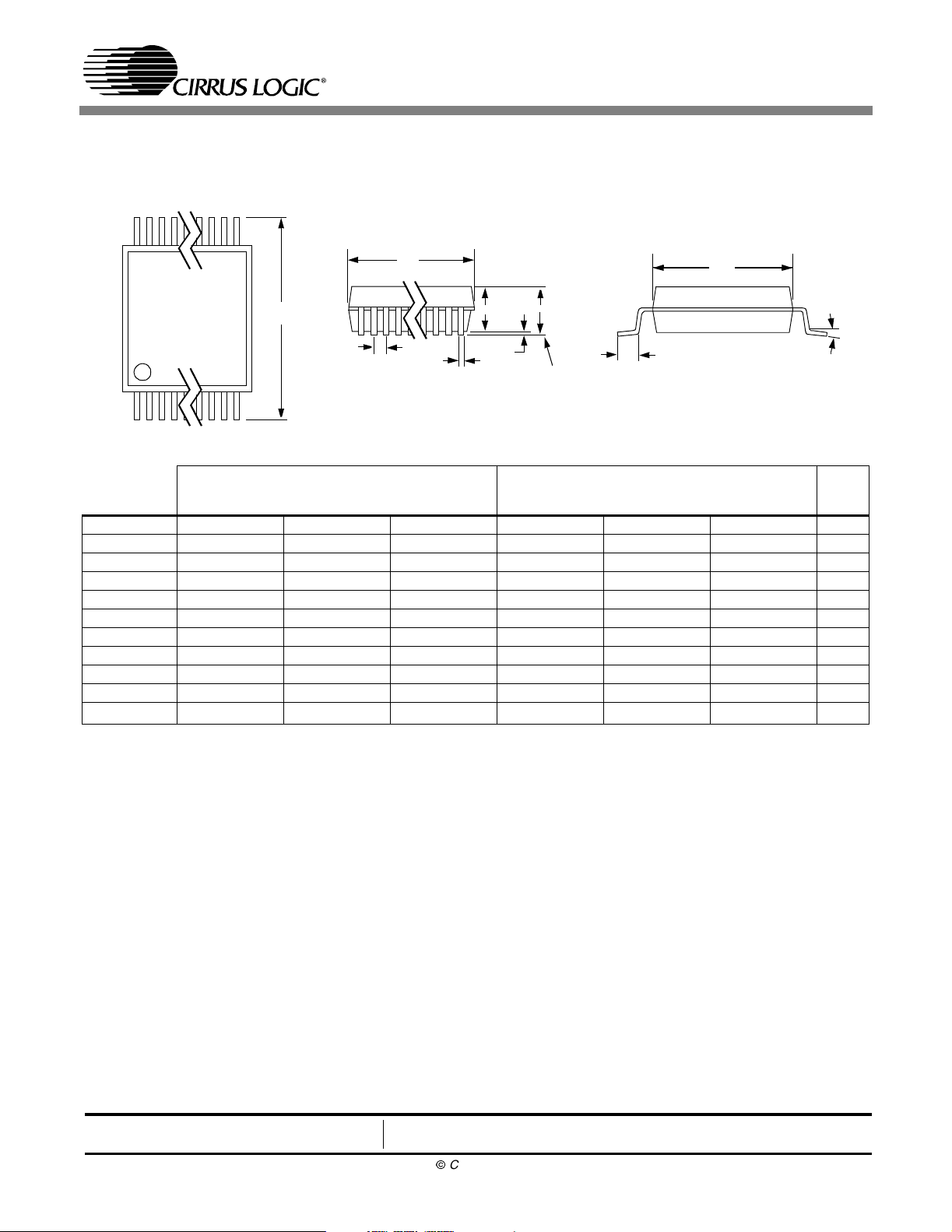

10. PACKAGE DIMENSIONS

20L TSSOP (4.4 mm BODY) PACKAGE DRAWING

N

CS53L32A

1

23

TOP VIEW

D

E

e

2

b

SIDE VIEW

A2

A1

A

SEATING

PLANE

L

INCHES MILLIMETERS

1

E1

END VIEW

NOT

DIM MIN NOM MAX MIN NOM MAX

A -- -- 0.043 -- -- 1.10

A1 0.002 0.004 0.006 0.05 -- 0.15

A2 0.03346 0.0354 0.037 0.85 0.90 0.95

b 0.00748 0.0096 0.012 0.19 0.245 0.30 2,3

D 0.252 0.256 0.259 6.40 6.50 6.60 1

E 0.248 0.2519 0.256 6.30 6.40 6.50

E1 0.169 0.1732 0.177 4.30 4.40 4.50 1

e -- -- 0.026 -- -- 0.65

L 0.020 0.024 0.028 0.50 0.60 0.70

∝

0° 4° 8° 0° 4° 8°

∝

E

JEDEC #: MO-153

Controlling Dimension is Millimeters.

Notes: 1. “D” and “E1” are reference datums and do not included mold flash or protrusions, but do include mold

mismatch and are measured at the parting line, mold flash or protrusions shall not exceed 0.20 mm per

side.

2. Dimension “b” does not include dambar protrusion/intrusion. Allowable dambar protrusion shall be

0.13 mm total in excess of “b” dimension at maximum material condition. Dambar intrusion shall not