Page 1

CS4235

2

2

Advanced Product Databook

FEATURES

■ Compatible with Sound Blaster™, Sound Blaster

Pro™, and Windows Sound System™

■ Advanced MPC3-Compliant Input and Output

Mixer

■ Enhanced Stereo Full Duplex Operation

■ Dual Type-F DMA Support

■ Integrated CrystalCl ear™ 3D Stereo

Enhancement

■ Industry Leading Delta-Sigma Data Converters

(86 dB FS A)

■ Internal Default PnP Resources

■ CS9236 Wavetable Interface

■ CS4610 Audio Accelerator Interface

■ CS4236B/CS4237B/CS4238B Register

Compatible

CrystalClear™

Low Cos t IS A Audi o S yste m

DESCRIPTION

The CS4235 is a single chip multimedia audio system

that is pin-compatible to the CS423xB for many designs. The product includes an integrated FM

synthesizer and a Plug-and-Play interface. In addition,

the CS4235 includes hardware master volume control

pins as well as extensive power management and 3D

sound technology. The CS4235 is compatible with the

Microsoft

run software written to the Sound Blaster and Sound

Blaster Pro interfaces. The CS4235 is fully compliant

with Microsoft’s PC’97 and PC’98 audio requirements.

ORDERING INFO

®

Windows Sound System standard and will

CS4235-JQ 100 pin TQFP, 14x14x1.4mm

CS4235-KQ 100 pin TQFP, 14x14x1.4mm

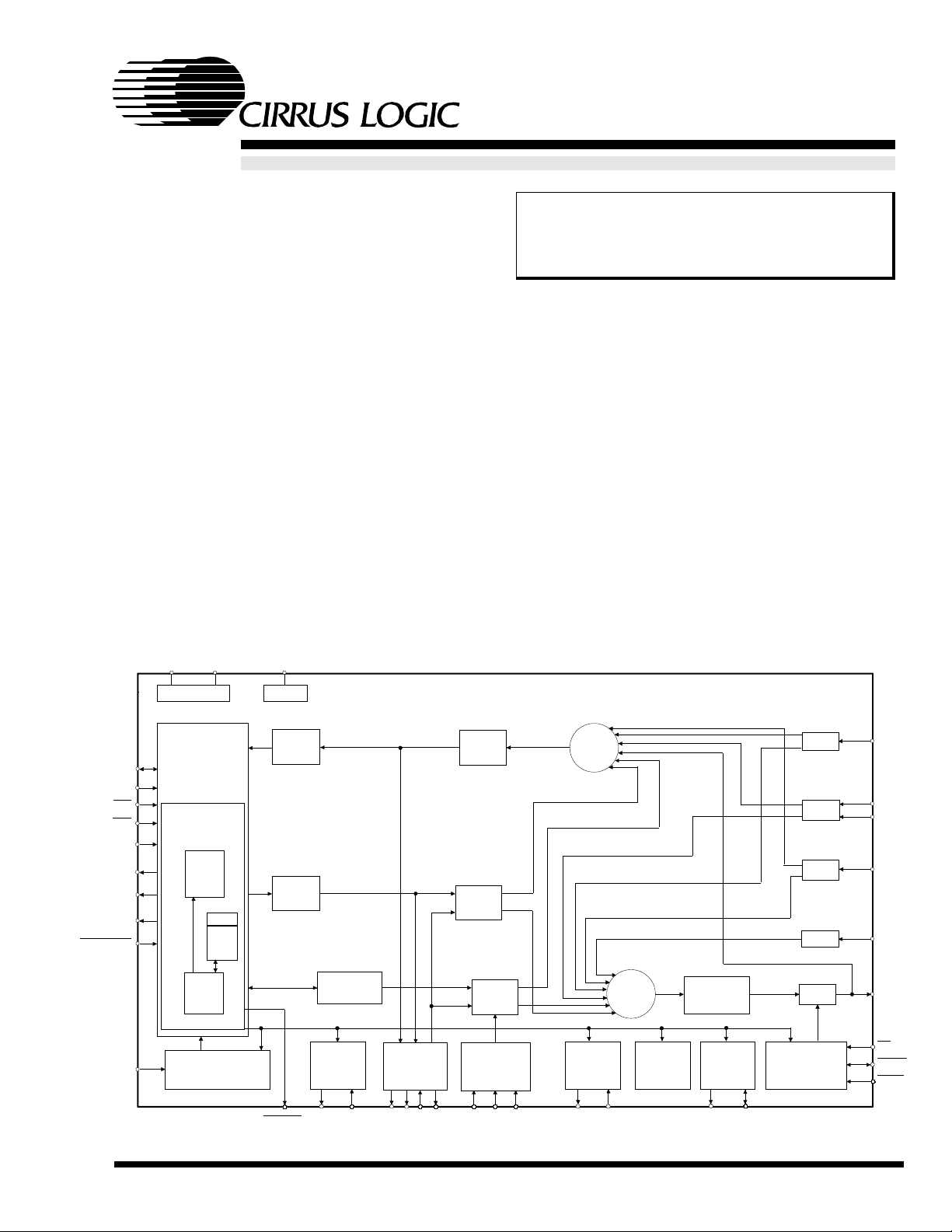

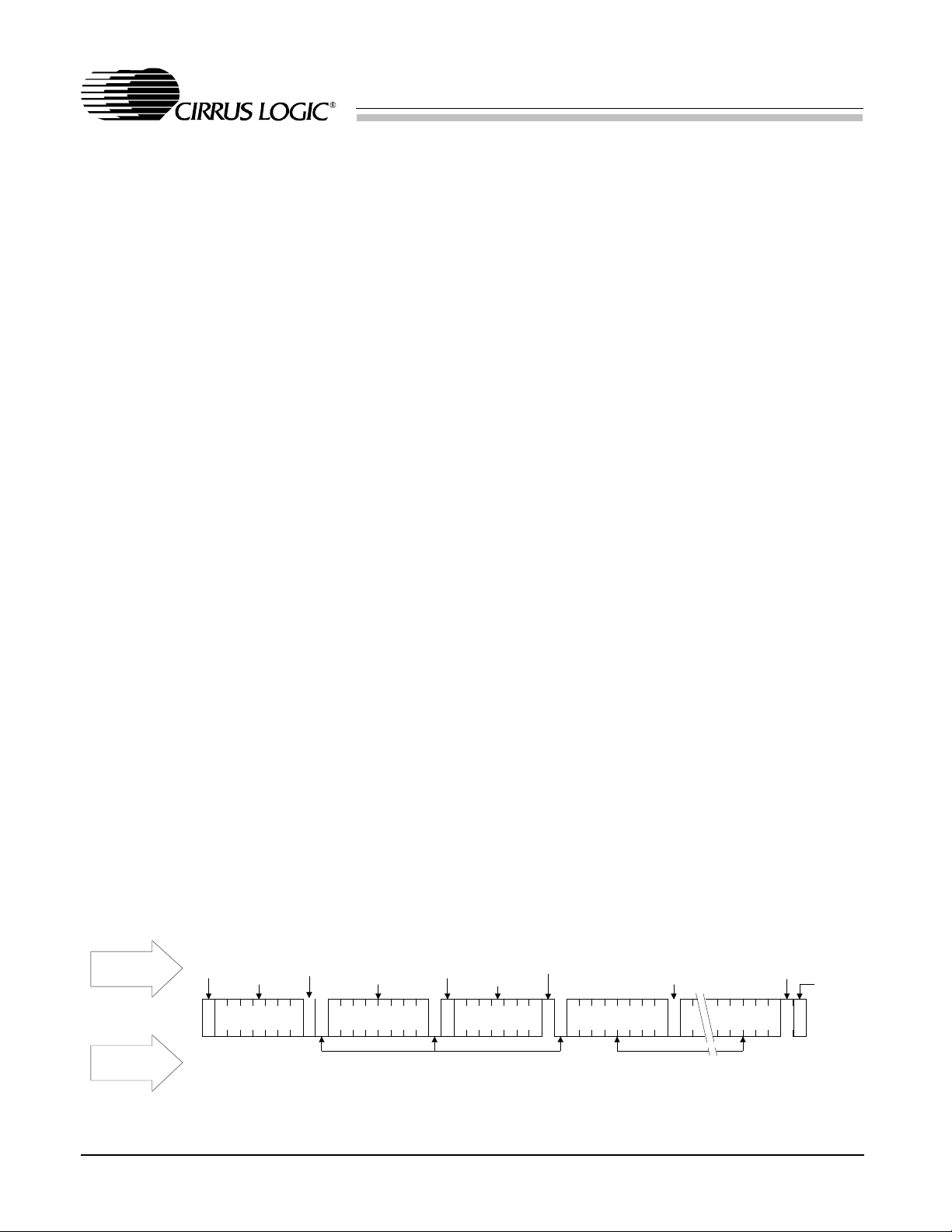

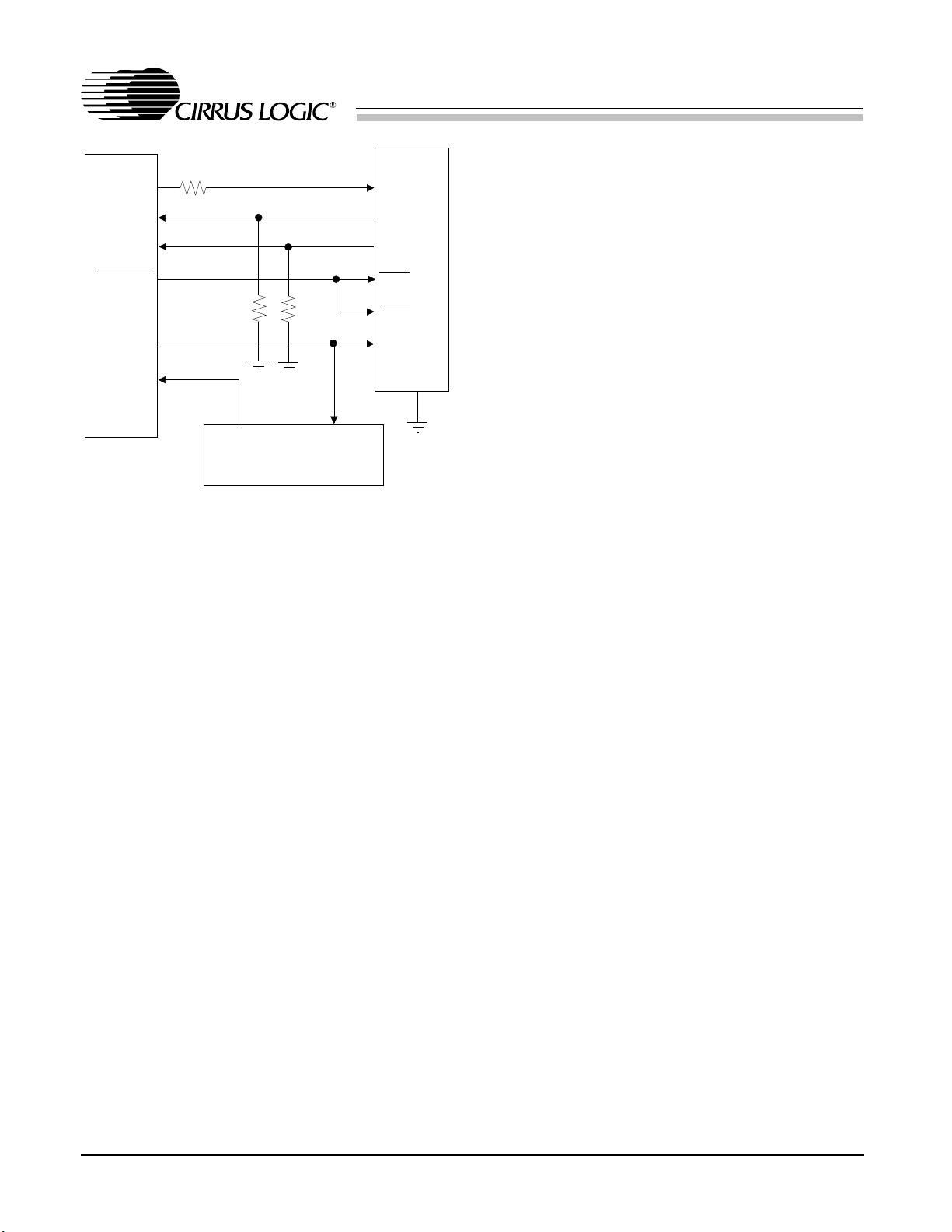

SD<7:0>

SA<11:0>

IOR

IOW

AEN

IOCHRDY

IRQ<A:G>

DRQ<A:C>

DACK<A:C>

SA<12:15)

(CDROM)

VREFXTALI XTALO

OSCILLATOR VREF

ISA

BUS

INTERFACE

PLUG

AND

PLAY

CODEC

REG

I/F

Config

IO

IRQ

DMA

Decode

Logic

CD-ROM or

Upper Address Bits

FIFO

FIFO

FM

Synthesizer

ANALOG

JOYSTICK

LOGIC

CS4610

INTERFACE

Stereo

ADC1

Stereo

DAC1

Stereo

DAC2

CS9236

WAVETABLE

INTERFACE

INPUT MIXER

Σ

OUTPUT MIXER

MPU-401

UART

with

FIFOS

Σ

WSS

SBPRO

Registers

3D

Enhancement

EEPROM

Interface

GAIN

GAIN

GAIN

ATTN

ATTN

Hardware

Volume Control

L/RAUX1

L/RAUX

CMAUX

MIC

MIN

L/ROUT

UP

DOWN

MUTE

BRESET

JOYSTICK MIDI

SERIAL PORT

NOV ‘97 DS252PP2

SERIAL PORT

Copyright Cirrus Logic, I nc. 1997

(All Rights Reserv ed)

SCL

SDA

Page 2

CrystalClear 16-Bit Audio Motherboard Example Design

TM

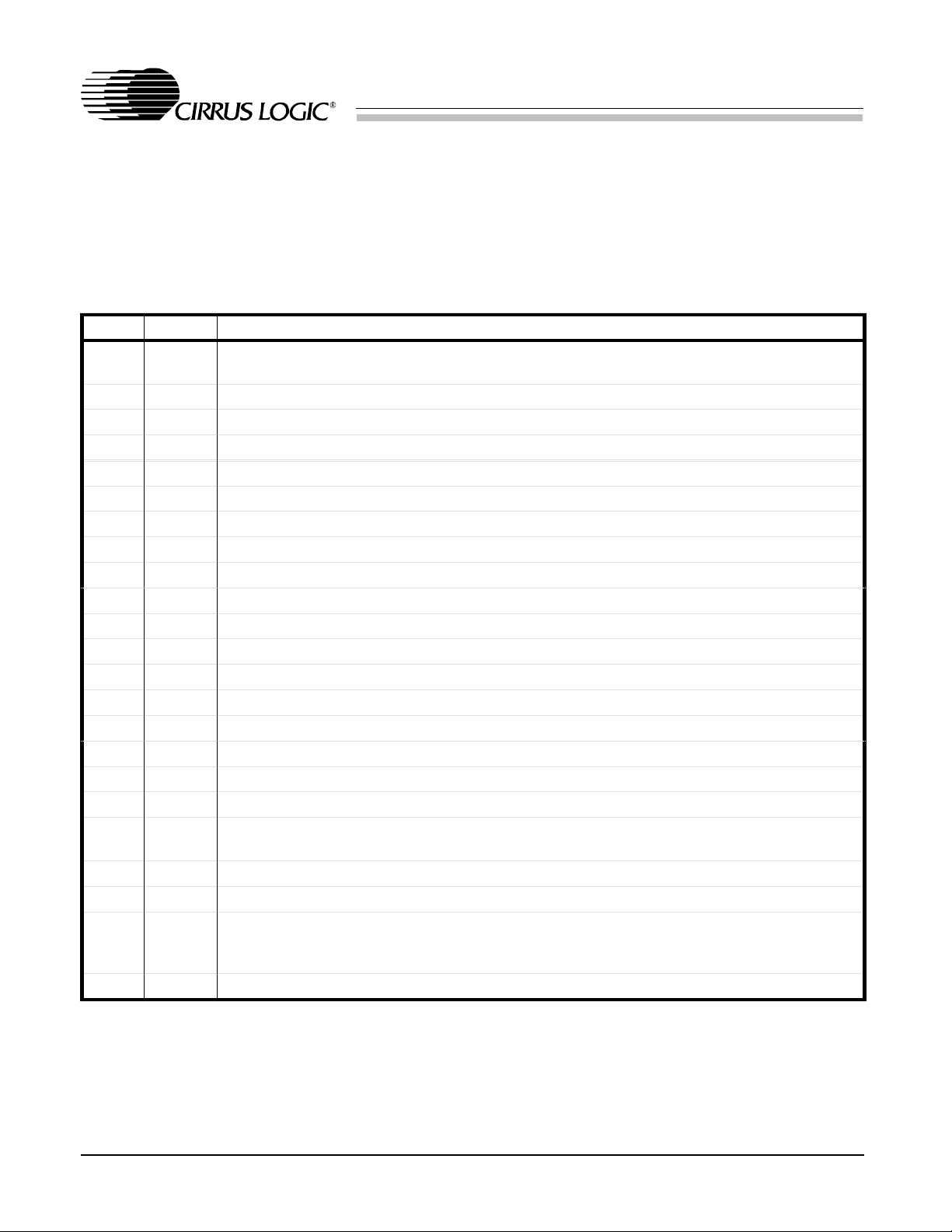

TABLE OF CONTENTS

CRD4235-8

CS4235 PERFORMANCE SPECIFICATIONS... 3

GENERAL DESCRIPTION ............... ...... ......... ... 12

ISA Bus Interface ... ......... ...... ......... ...... ...... ...... 13

PLUG AND PLAY........... ......... ...... ......... ......... ... 15

PnP Data ............... ...... ......... ...... ...... ......... ...... 16

Loading Resource Data.............. ...... ......... ...... 16

Loading Firmware Patch Data . ............ ......... ... 18

The Crystal Key........ ...... ...... ......... ...... ......... ... 18

Bypassing Plug and Play ...... ...... ......... ...... ...... 19

Crystal Key 2 .................. ...... ......... ...... ......... ... 20

Hardware Configuration Data........ ......... ......... 20

Hostload Procedure..... ......... ...... ......... ...... ...... 24

External E

2

PROM ........ ...... ...... ......... ...... ......... 25

WINDOWS SOUND SYSTEM CODEC.............. 26

Enhanced Functions (MODEs) ... ......... ......... ... 27

FIFOs............ ...... ......... ...... ......... ...... ...... ......... 27

WSS Codec PIO Register I nterface.......... ...... 27

DMA Interface.. ......... ...... ...... ......... ...... ...... ...... 28

Sound System Codec Register Interface ........ 29

Direct Mapped Registe rs (R0-R3) ............... 30

I/O Data Register s (R3)............. ...... ......... ... 31

Indirect Mapped Regi sters (I0-I31) .............. 32

WSS Extended Registers (X0-X31) ............44

SOUND BLASTER INTERFACE ...... ...... ......... ... 53

Mode Switching ........... ...... ...... ......... ...... ......... 53

Sound Blaster Dire ct Register Interface. ...... ... 53

Sound Blaster Mixer Registers............... ...... ... 54

GAME PORT INTERFACE......... ...... ......... ...... ... 55

CONTROL INTERFACE .... ......... ......... ............ ... 57

Control Register I nterface ..... ...... ...... ......... ...... 57

Control Indirect Registers (C0- C9)............ ...... 59

MPU-401 INTERFACE . ............ ......... ......... ......... 62

MPU-401 Register Interface....... ......... ............ 62

MIDI UART ............... ...... ......... ...... ...... ......... ... 63

MPU-401 "UART" Mode Operatio n........ ......... 63

FM SYNTHESIZER ..................... ...... ......... ...... ... 63

CDROM INTERFACE ........... ......... ...... ...... ......... 64

CS4610 DSP SERIAL DATA PORT ............ ...... 64

CS9236 WAVETABLE SERIAL DATA PORT... 66

WSS CODEC SOFTWARE DESCRIPTION .......67

Calibration .......... ...... ......... ...... ...... ......... ...... .... 67

Changing Sampling Rate ................. ...... ...... .... 68

Changing Audio Data Fo rmats ...... ...... ......... .... 6 9

Audio Data Formats . ............ ......... ......... .......... 69

DMA Registers ..................... ...... ...... ......... ...... . 69

WSS Codec Interrupt .. ......... ......... ............ ....... 71

Error Conditions ....... ......... ...... ...... ......... ...... .... 7 1

DIGITAL HARDWARE DESCRIPTION.. ......... .... 7 2

Bus Interface .................. ...... ......... ...... ...... .......72

Volume Control Interf ace ........... ...... ...... ......... . 72

Crystal/Clock ......... ...... ......... ...... ...... ......... ...... . 73

General Purpose Output Pins.......... ......... ....... 73

Reset and Power Down . ...... ......... ...... ......... .... 7 3

Address Port Configurati on........... ......... ...... .... 73

Multiplexed Pin Co nfiguration ....... ...... ......... .... 7 4

ANALOG HARDWARE DESCRIPTION ............. 74

Line-Level Inputs Plus MPC Mixe r... ...... ......... . 74

Microphone Level Inp ut.. ......... ...... ...... ......... .... 7 5

Mono Input ......... ......... ...... ......... ...... ...... ......... . 75

Line-Level Outputs ............... ...... ......... ...... ...... . 75

Miscellaneous Analo g Signals ......... ...... ......... . 76

GROUNDING AND LAYOUT........... ......... ...... .... 76

POWER SUPPLIES..... ...... ...... ......... ...... ......... ....76

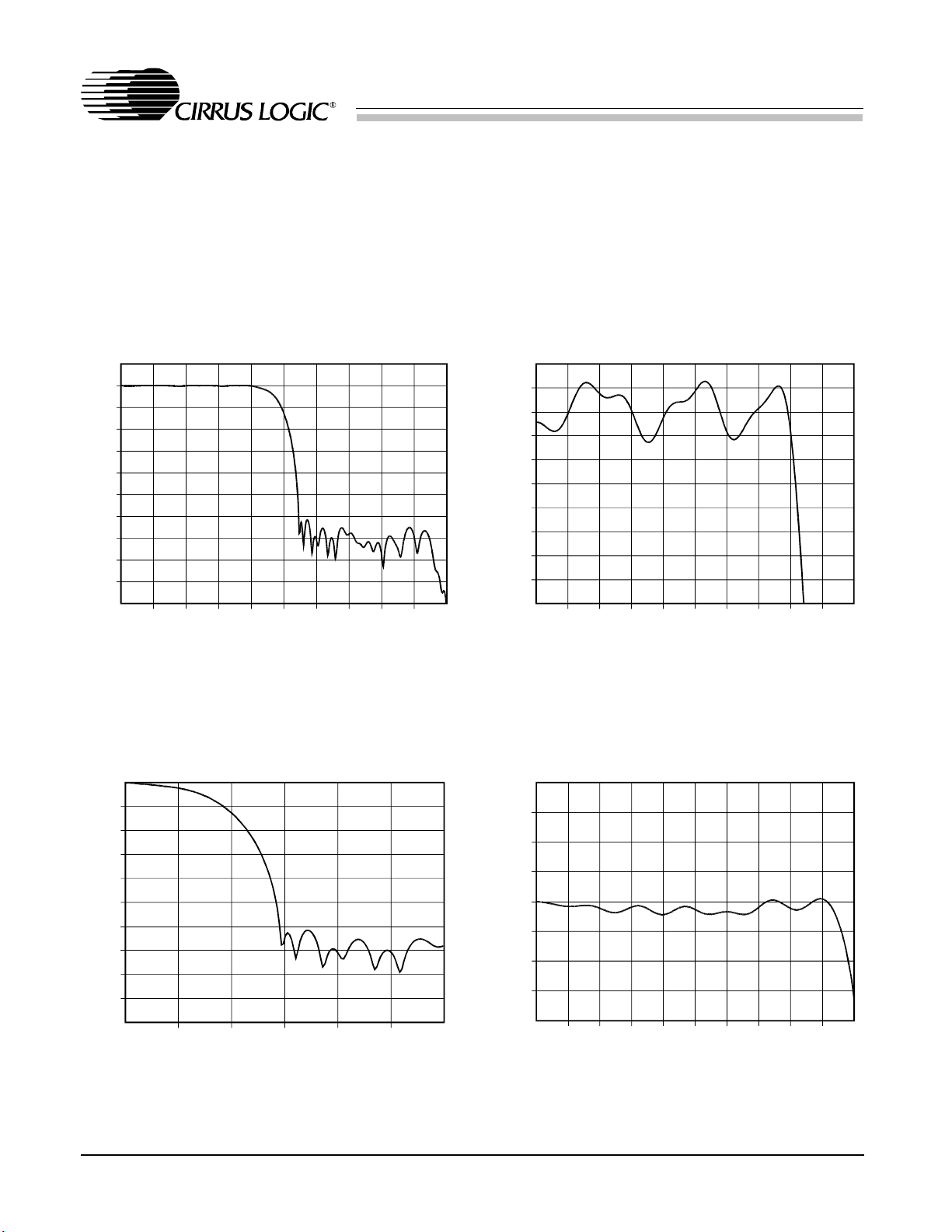

ADC/DAC FILTER RESPONSE . ...... ......... ...... .... 78

PIN DESCRIPTIONS ..................... ......... ...... .......80

ISA Bus Interface Pins...... ...... ......... ...... ......... . 81

Analog Inputs ........ ......... ...... ......... ...... ...... .......82

Analog Outputs ...... ...... ......... ...... ...... ......... ...... . 83

MIDI Interface.............. ...... ......... ...... ......... ...... . 84

External Peripheral Signals.. ...... ...... ......... ...... . 84

Joystick Interf ace ...... ......... ...... ......... ...... ...... .... 85

CS4610 DSP Serial Port Interface ...... ......... .... 8 5

CS9236 Wavetable Serial Port Interface ......... 85

CDROM Interface.. ......... ...... ...... ......... ...... ...... . 86

Volume Control... ......... ......... ............ ......... ....... 87

Miscellaneous.. ...... ......... ...... ...... ......... ...... .......87

Power Supplies ........... ...... ......... ...... ...... ......... . 88

PARAMETER DEFINITIONS... ......... ...... ......... .... 8 9

PACKAGE PARAMETERS.............. ......... ......... . 90

APPENDIX A: DEFAULT PnP DATA. ......... .......91

APPENDIX B: CS4235 DIFFERENCES ... ...... .... 93

Windows 95 and Windows 3.1 are trademarks; Microsoft, Windows and Windows Sound System are registered

trademarks of Microsoft Corporation.

Sound Blaster and Sound Blaster Pro are trademarks of Creative Labs.

Ad Lib is a trademark of Adlib Corporation.

CrystalClear is a trademark of Cir rus Logic, I nc.

2

DS252PP2

Page 3

CrystalClear Low Cost ISA Audio System

TM

CS4235

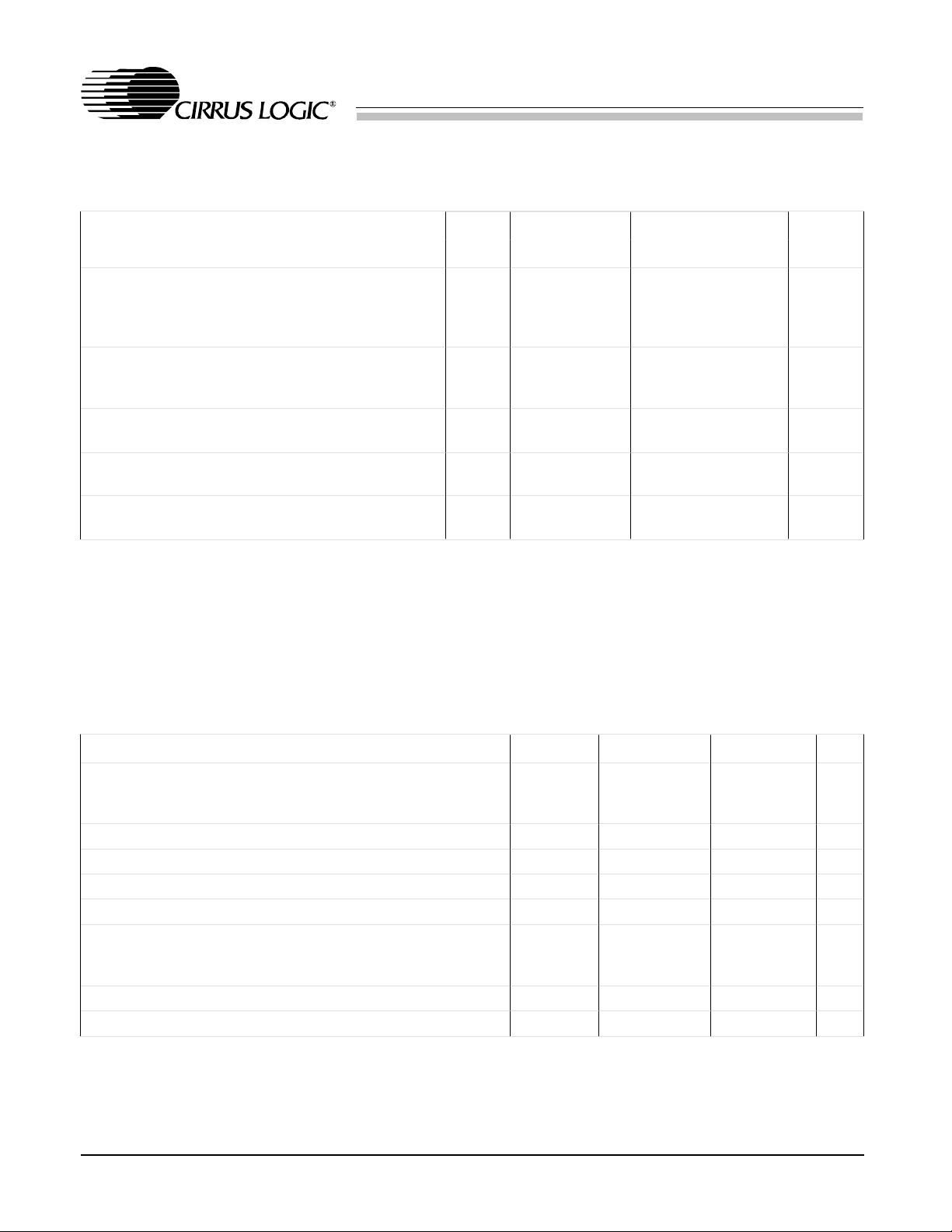

ANALOG CHARACTERISTICS (T

= 25 °C; VA, VD1, VDF1-VDF3 = +5 V;

A

Input Levels: Logic 0 = 0 V, Logic 1 = VD1; 1 kHz Input Sine wave; Sample Frequency, Fs = 44.1 kHz;

Measurement Bandwidth is 20 Hz to 20 kHz, 16-bit linear coding. )

CS4235-JQ CS4235-KQ

Parameter* Symbol Min Typ Max Min Typ Max Units

Analog Input Characteristics (A-D-PC)

- Volume set to 0 dB unless otherwise specified.

ADC1 Resolution (Note 1) 16 - - 16 - - Bits

ADC1 Differential Nonlinearit y (Note 1) - -

Frequency Response: Ac = ±1 dB

Dynamic Range AUX1, AUX2

(Note 2) MIC

Total Harmonic Distortion+Noise AUX1, AUX2

-3 dB FS input (Note 2) MIC

Interchannel Isolat ion (Note 1): Left to Right

10 kHz input AUX1/2 to MIC

AUX1 to AUX2

Interchannel Gain Mismatch AUX1, AUX2

MIC

FR - - - 20 19000 Hz

DR ---80

-75

THD+N ---66

-66

-

-80

-

-80

-

-80

-

-

±0.5

-

-

-

-

-

-

-

-

±0.5

-

±0.5

ADC1 Offset Error 0 dB Gain - - - -

--

-80

-72

-75

-72

-70

-

-

-

-

-85

-80

-80

-80

-80

-80

-90

-

-

±10 ±200

±0.5

-

-

-

-

-

-

-

±0.5

±0.5

LSB

dB FS A

dB FS A

dB FS A

dB FS A

dB

dB

dB

dB

dB

LSB

Full Scale Input Voltage:

(MGE/MBST=1) MIC

(MGE/MBST=0) MIC

AUX1, AUX2, MIN

Gain Drift Input Resistance (Note 1): MIC

AUX1, AUX2, MIN

0.25

2.5

2.5

82011

0.28

2.8

2.8

±100

23

-

0.25

-

-

--

-

-

2.5

2.5

±100

8

20

0.28

2.8

2.8

11

23

-

-

-

V

V

V

-ppm/°C

-

-

kΩ

kΩ

Input Capacitance (Note 1) - - 15 - - 15 pF

Notes: 1. This specification is guaranteed by characterization, no production testing.

2. MGE or MBST = 1 (see WSS Indirect Reg I0 or X2).

pp

pp

pp

*Parameter definitions are given at the end of this data sheet.

Specifications are subject to change without notice.

DS252PP2 3

Page 4

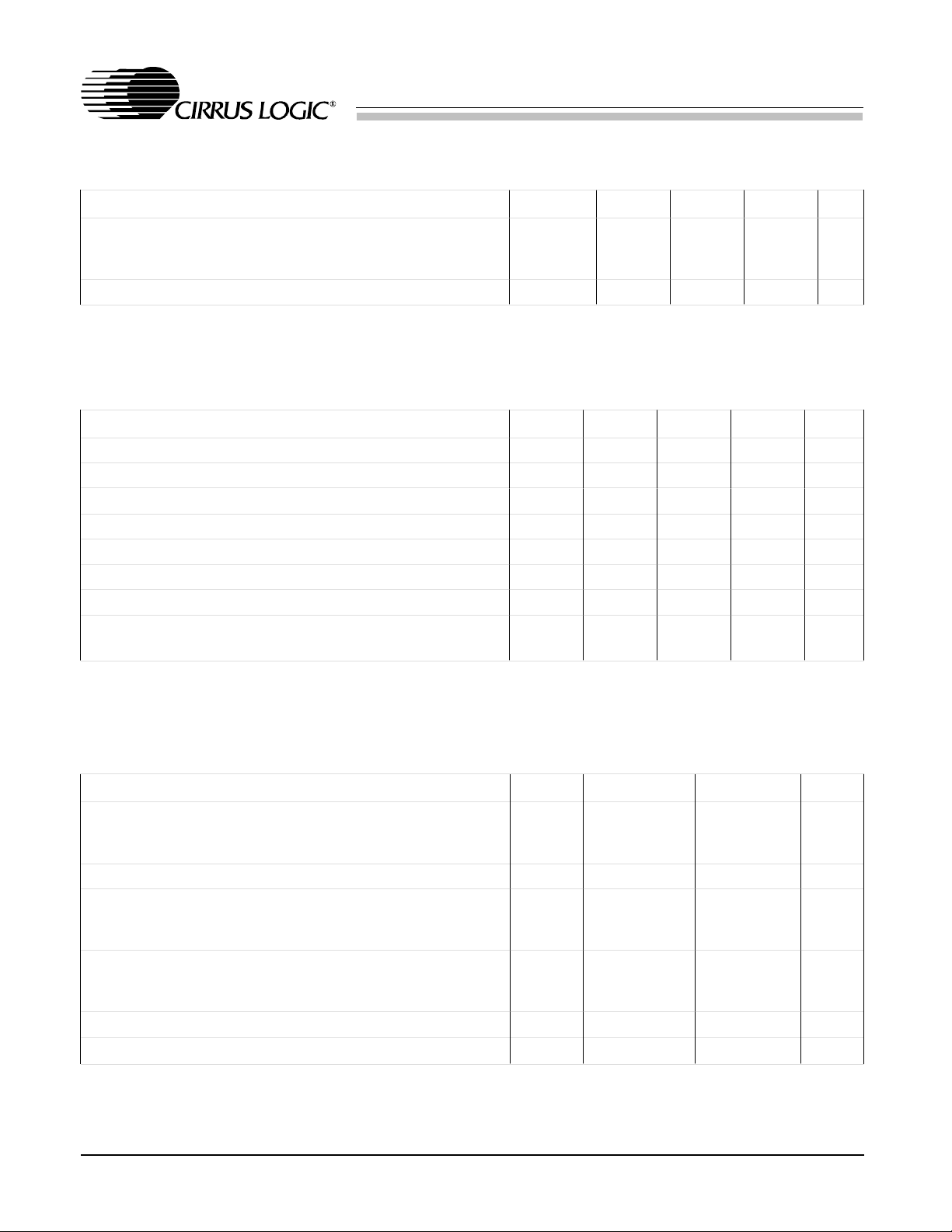

ANALOG CHARACTERISTICS (Continued)

Parameter* Symbol Min Typ Max Min Typ Max Units

CrystalClear Low Cost ISA Audio System

CS4235-JQ CS4235-KQ

TM

CS4235

Analog Output Characteristics (PC-D-A)

DAC1 Resolution (Note 1) 16 - - 16 - - Bits

DAC1 Differential Nonlinearit y (Note 1) - -

DAC1 Frequency Response: Ac = ±1 dB

DAC1 Dynamic Range DR - -86 - -80 -86 - dB FS A

DAC1 Total Harmonic Distort ion+Noise:

-3 dB FS inp ut (Note 3)

DAC1 Interchannel Isolation (Notes 1,3) - -95 - -80 -95 - dB

DAC1 Interchannel Gain Mismatch Voltage Reference Output - VREF 2.0 2.2 2.5 2.0 2.2 2.5 V

Voltage Reference Output Current - VREF

(Notes 1,4)

DAC1 Programmable Attenuation Span 90 94.5 - 90 94.5 - dB

DAC1 Atten. Step Size: Greater than -82.5 dB

-82.5 dB to -94.5 dB

DAC1 Offset Voltage - - - Full Scale Output Voltage (Note 3) 2.5 2.8 3.3 2.5 2.8 3.3 Vpp

Gain Drift (Note 1) - 100 - - 100 - ppm/°C

Deviation from Linear Phase (Note 1)

(Passband)

External Load Impedance (Note 1) 10 - - 10 - Mute A tte nua tio n (Note 1) 80 - - 80 - - dB

- Volume set to 0 dB unless otherwise specified.

±0.5

FR - - - 20 - 19000 Hz

THD+N - -80 - -74 -80 - dB FS A

±0.1 ±0.5

- 100 400 - 100 400

1.3

1.0

- - 1 - - 1 Degr ee

1.5

1.5

1.721.3

--

-

±0.1 ±0.5

1.5

1.0

1.5

±1 ±10

±0.5

1.7

2

LSB

dB

µA

dB

dB

mV

kΩ

Power Supply

Power Supply Current Digital, Operating

Analog, Operating

Total Operating

Total Power Down

Power Supply Rejection, 1 kHz (Note 1) 40 - - 40 - - dB

Notes: 3. 10 kΩ, 100 pF load.

4. DC current only. If dynamic loading exists, then the voltage reference output must be buffered

or the performance of ADCs and DACs will be degraded.

-

-

-

-

70

30

100

-

-

-

-

-

-

70

80

-

30

35

-

100

-

-

-

1

mA

mA

mA

mA

4 DS252PP2

Page 5

CrystalClear Low Cost ISA Audio System

TM

CS4235

MIXERS (T

1 kHz Inpu t S ine w ave, Me asu remen t B and widt h i s 20 H z t o 20 kHz .)

Mixer Gain Range Span AUX1, AUX2

Step Size MIC, AUX1, AUX2

Frequency Response: Ac = ±1 dB (N otes 1, 3)

(A-A)

Dynamic Range (Notes 1,3)

(A-A)

Total Harmonic Distortion+Nois e (Notes 1,3)

(A-A) -3 dB FS input

= 25 °C; VA, VD1, VDF1-VDF3 = +5 V; Input Levels: Logic 0 = 0 V, Logic 1 = VD1;

A

CS4235-JQ CS4235-KQ

Parameter* Symb ol Min T yp Max Min Typ Max Units

-

MIC

Hardware Master

DAC1, DAC2

Hardware Master

DAC1, DAC2

FR - - - 20 - 20000 Hz

DR - -88 - -90 -97 - dB FS A

THD+N - -85 - -85 -90 - dB FS A

-

-

-

-

-

-

--

-

-

-

-

-

-

-

-

-

42

40

75

85

1.3

1.6

0.9

45

45

86

94.5

1.5

2.0

1.5

-

-

-

-

1.7

2.4

2.0

dB

dB

dB

dB

dB

dB

dB

ABSOLUTE MAXIMUM RATINGS (AGND, DGND, SGND = 0 V, all voltages with respect to 0 V.)

Parameter Symbol Min Max Units

Power Supplies: Digital

Analog

Total Power Dissipation (Supplies, In puts, Outputs) - 1 W

Input Current per Pin (Except Supply Pins) -10.0 +10.0 mA

Outpu t Cu rren t pe r P in (Exce pt S upp ly P ins) -50 +50 mA

Analog Input Voltage -0.3 VA+0.3 V

Digital Input Voltage: SA<15:0>, IOR, IOW, AEN

SD<7:0>, DACK<A:C>

All other digital inputs

Ambient Temperature (Power Applied) -55 +125 °C

Storage Temperature -65 +150 °C

Warning: Operation beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

DS252PP2 5

VD1

VDF1-VDF3

VA

-0.3

-0.3

-0.3

-0.3

-0.3

6.0

6.0

6.0

VD1+0.3

VDF+0.3

V

V

V

V

V

Page 6

RECOMMENDED OPERATING CONDITIONS

(AGND, DGND, SGND = 0 V, a ll voltages with r espect to 0 V.)

Parameter Symbol Min Typ Max Unit s

CrystalClear Low Cost ISA Audio System

TM

CS4235

Power Supplies: Digital (Note 5)

Digital Filtered

Analog

Operating Ambient Temperature T

VD1

VDF1-VDF3

VA

A

4.75

4.75

4.75

5.0

5.0

5.0

5.25

5.25

5.25

02570°C

Note 5: VD1 su pplie s the pow er to th e ISA in terf ace pins .

ADC1/DAC1 DIGITAL FILTER CHARACTERISTICS (Not e 1)

Parameter Symbol M in Typ Max Units

Passband 0 - 0.40xFs Hz

Frequency Response -1.0 - +0.5 dB

Passband Ripple (0-0.40xFs) - -

±0.1

Transition Band 0.40xFs - 0.60xFs Hz

Stop Band 0.60xFs - - Hz

Stop Band Rejection 74 - - dB

Group Delay - - 10/Fs s

Group Delay Variation vs. Frequency ADC1

DAC1

-

-

-

-

0.0

0.1/Fs

dB

V

V

V

µs

µs

DIGITAL CHARACTERISTICS

= 25 °C; VA, VDF1-VDF3 = +5 V, VD1 = +5 V; AGND, DGND1, SGND1-SGND4 = 0 V.)

(T

A

Parameter Symbol Min Max Units

High-level Input Voltage UP/DOWN/MUTE

Other Digital Inputs

XTALI

Low-level Input Voltage V

High-level Output Voltage: ISA Bus Pins I0 = -24. 0 mA

V

IOCHRDY, SDA (Note 6)

All Others I0 = -1.0 mA

Low-level Output Voltage: ISA Bus Pins I0 = 24.0 mA

V

MCLK, SDOUT, MIDOUT, IOCHRDY I0 = 8.0 mA

All Others I0 = 4.0 mA

V

IH

IL

OH

OL

3.0

2.0

VDF-1.0

-0.8V

2.4

-

2.4

-

-

Input Leakage Current (Digital Inputs) -10 10

Output Leakage Curr ent (High-Z Digital Outputs) -10 10

Note 6. Open Collector pins. High level output voltage dependent on external pull up (required) used and

number of per ipherals (gat es) attached.

6 DS252PP2

-

-

-

VD1

VDF

VDF

0.4

0.4

0.4

V

V

V

V

V

V

V

V

V

µA

µA

Page 7

CrystalClear Low Cost ISA Audio System

TM

CS4235

Timing Parameters (T

= 25 °C; VA, VD1, VDF1-VDF3 = +5 V; outputs loaded with 30 pF;

A

Input Levels: Logic 0 = 0 V, Logic 1 = VDF, Rise/Fall time = 2 ns; Input/Output reference levels = 2.5 V)

Parameter Symbol Min Max Units

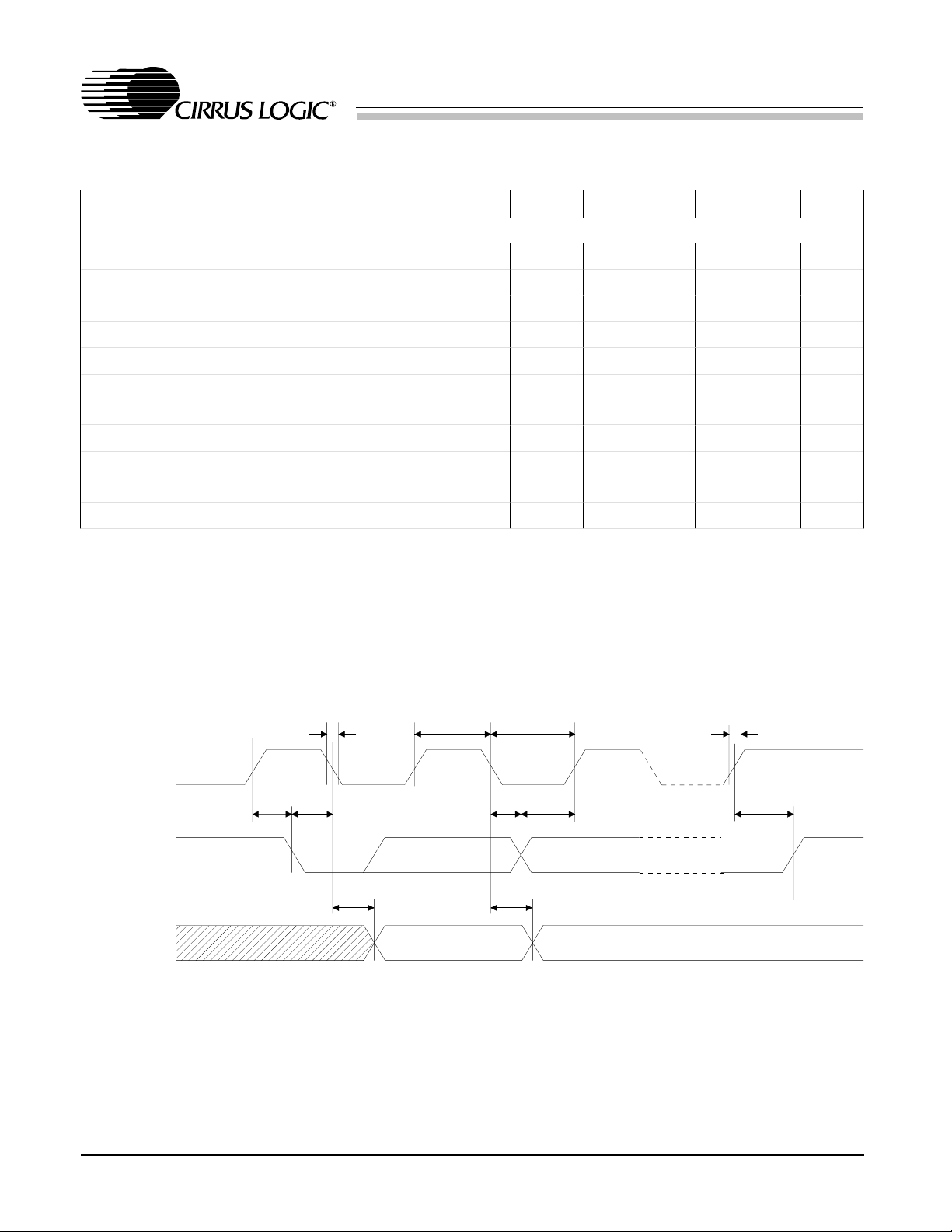

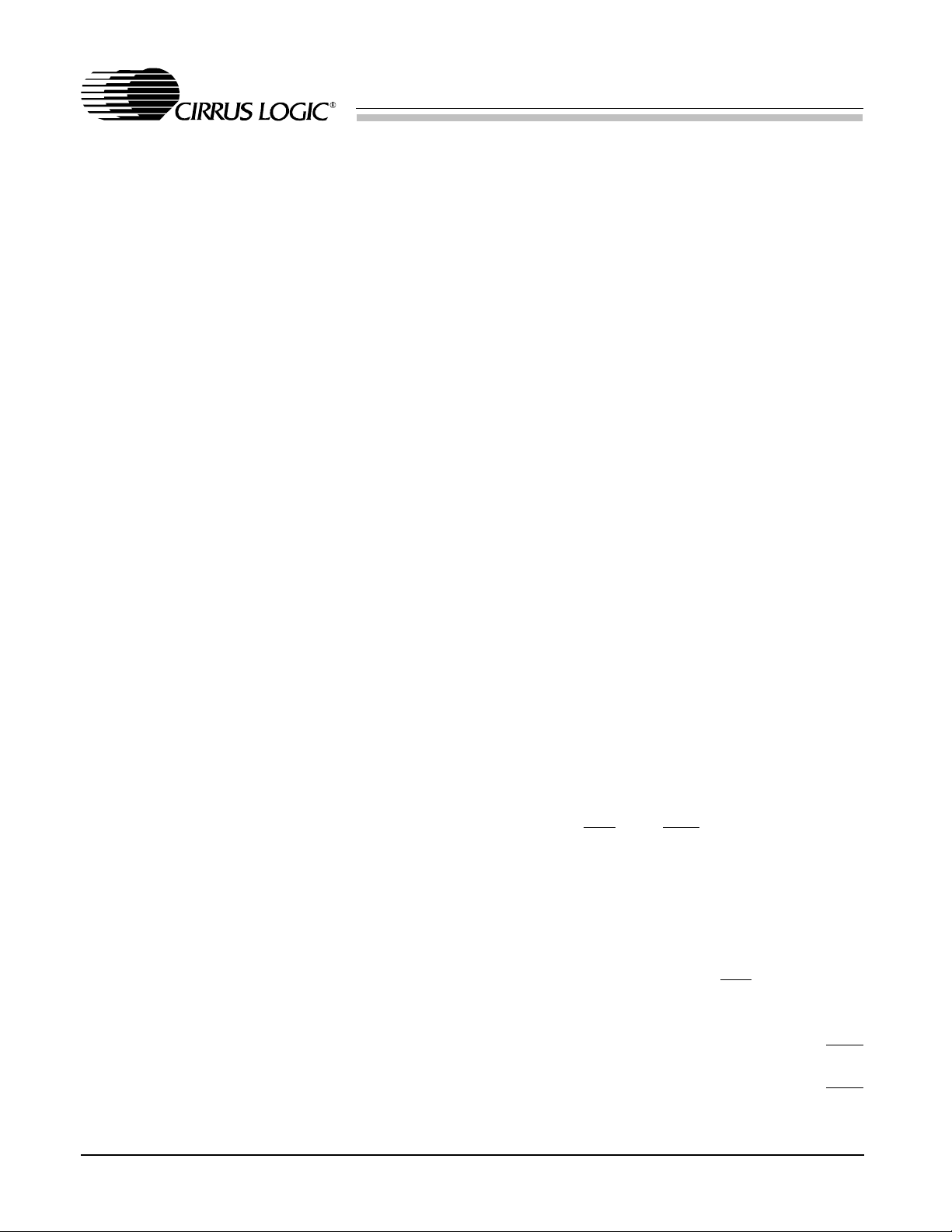

E2PROM Timing

SCL Low to SDA Data Out Valid t

Start Condition Hold Time t

Clock Low Period t

Clock High Period t

Start Condition Setup Time (for a Repeated Start Condition) t

Data In Hold Time t

Data In Setup Time t

SDA and SCL Ris e Time (Note 7) t

SDA and SCL Fall Time t

Stop Condition Setup Time t

Data Out Hold Time t

(Note 1)

AA

HD:STA

LSCL

HSCL

SU:STA

HD:DAT

SU:DAT

R

F

SU:STO

DH

03.5

4.0 -

4.7 -

4.0 -

4.7 0-

µs

µs

µs

µs

µs

µs

250 - ns

-1

µs

- 300 ns

4.7 -

µs

0-ns

Notes 7. Rise time on SDA is determined by the capacitance of the SDA line with all connected gates and the

exter nal pul lup re sisto r requi red.

t

t

F

HSCL

t

LSCL

t

R

SCL

t

SU:STA

t

HD:STA

t

HD:DAT

t

SU:DAT

t

SU:STO

SDA (IN)

t

AA

t

DH

SDA (OUT)

E2PROM 2-Wire Interface Timing

DS252PP2 7

Page 8

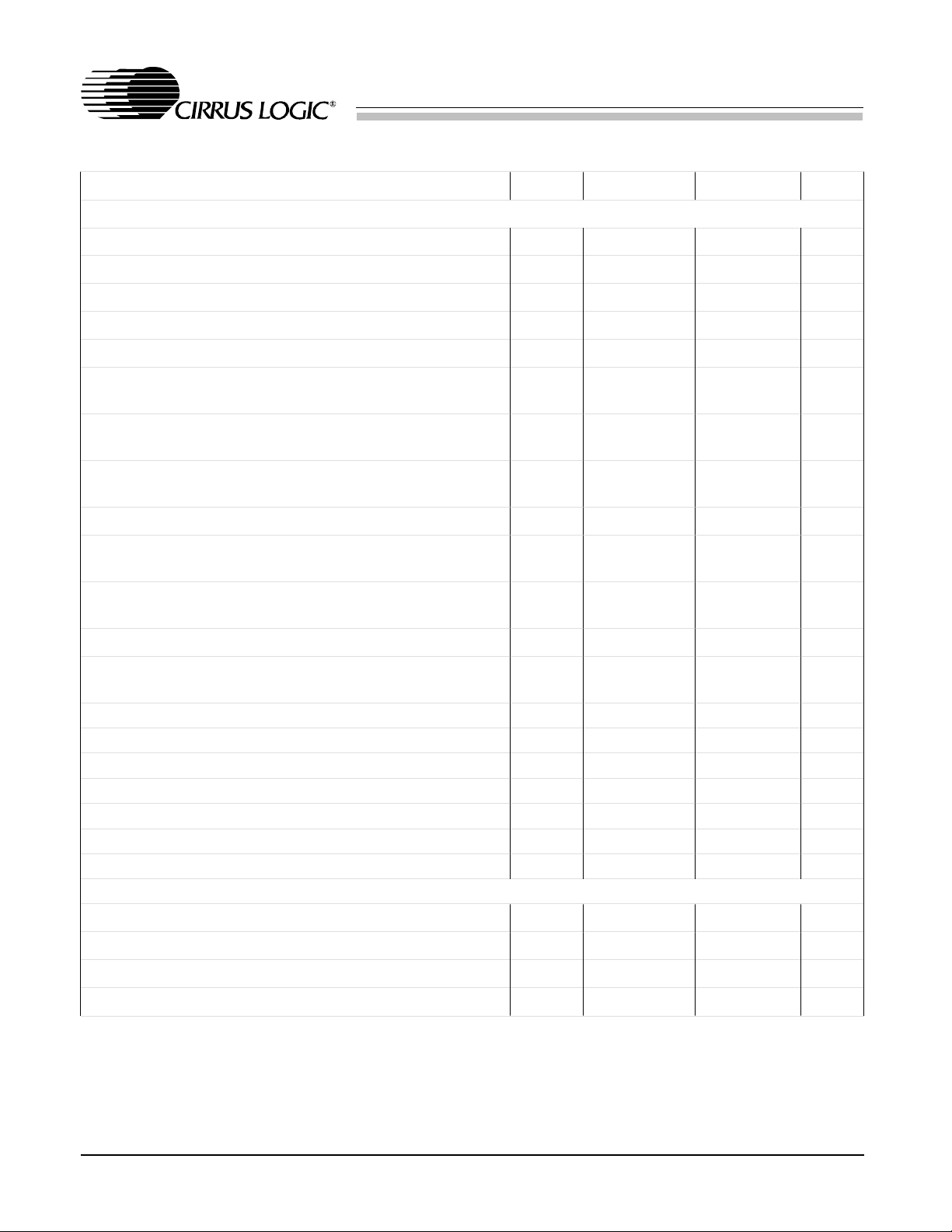

TIMING PARAMETERS (Continued)

Parameter Symbol Min Max Units

Paral lel Bu s Ti min g

CrystalClear Low Cost ISA Audio System

TM

CS4235

IOW or IOR strobe width t

Data valid to IOW rising edge (write cycle) t

IOR falling edge to data valid (read cycle) t

SA <> and AEN setup to IOR or IOW fa lling edge t

SA <> and AEN hold from IOW or IOR rising edge t

DACK<> inactive to IOW or IOR falling edge ( DMA cycle

immedi atel y f ollo wed by a no n-DM A cyc le ) (Not e 8)

DACK<> active from IOW or IOR rising edge (non-DMA

cycle completion followed by DMA cycle) (Note 8)

DACK<> setup to IOR fa lling edge (DMA cycle s)

DACK<> setup to IOW fallin g edge (Note 8)

Data hold from IOW rising edge t

DRQ<> hold from IOW or IOR falling edge DTM(I10) = 0

(assumes no more DMA cycles needed) DTM(I10) = 1

Time between rising edge of IOW or IOR to ne xt falling

edge of IOW or IOR

Data hold from IOR rising edge t

DACK<> hold from IOW rising edge

DACK<> hold from IOR rising edge

STW

WDSU

RDDV

ADSU

ADHD

t

SUDK1

t

SUDK2

t

DKSUa

t

DKSUb

DHD2

t

DRHD

t

BWDN

DHD1

t

DKHDa

t

DKHDb

90 - ns

22 - ns

-60ns

22 - ns

10 - ns

60 - ns

0-ns

25

25

-

-

ns

ns

15 - ns

-

-25

45

ns

-

80 - ns

025ns

25

25

-

-

ns

ns

RESDRV puls e width hi gh (Note 1) t

RESDRV

Initialization Time (Note 1, 9) t

EEPROM Read Time (Note 1, 10) t

EEPROM

INIT

1-ms

310ms

1190ms

XTAL, 16.9344 MHz, frequency (Notes 1, 11) 16.92 16.95 MHz

XTALI high time (Notes 1, 11) 24 - ns

XTALI low time (Notes 1, 11) 24 - ns

Sampl e Frequ ency (Note 1) F s 3.91 8 50 k Hz

CS4610 DSP Serial Port Timing

SCLK r isin g t o SD OUT v al id (Note 1) t

SCLK rising to FSYNC transition (Note 1) t

SDIN valid to SCLK falling (Note 1) t

SDIN hold after SCLK falling (Note 1) t

PD1

PD2

S1

H1

-60ns

-20 2 0 ns

30 - ns

30 - ns

Notes: 8. AEN must be high during DMA cycles.

9. I nitialization time depends on the power supply circuitry, as well as the the type of clock used.

10. EEPROM read time is dependent on amount of data in EEPROM. Minimum time relates to no

EEPROM present. Maximum time relates to EEPROM data size of 1k bytes.

11. The Sample frequency specification must not be exceeded.

8 DS252PP2

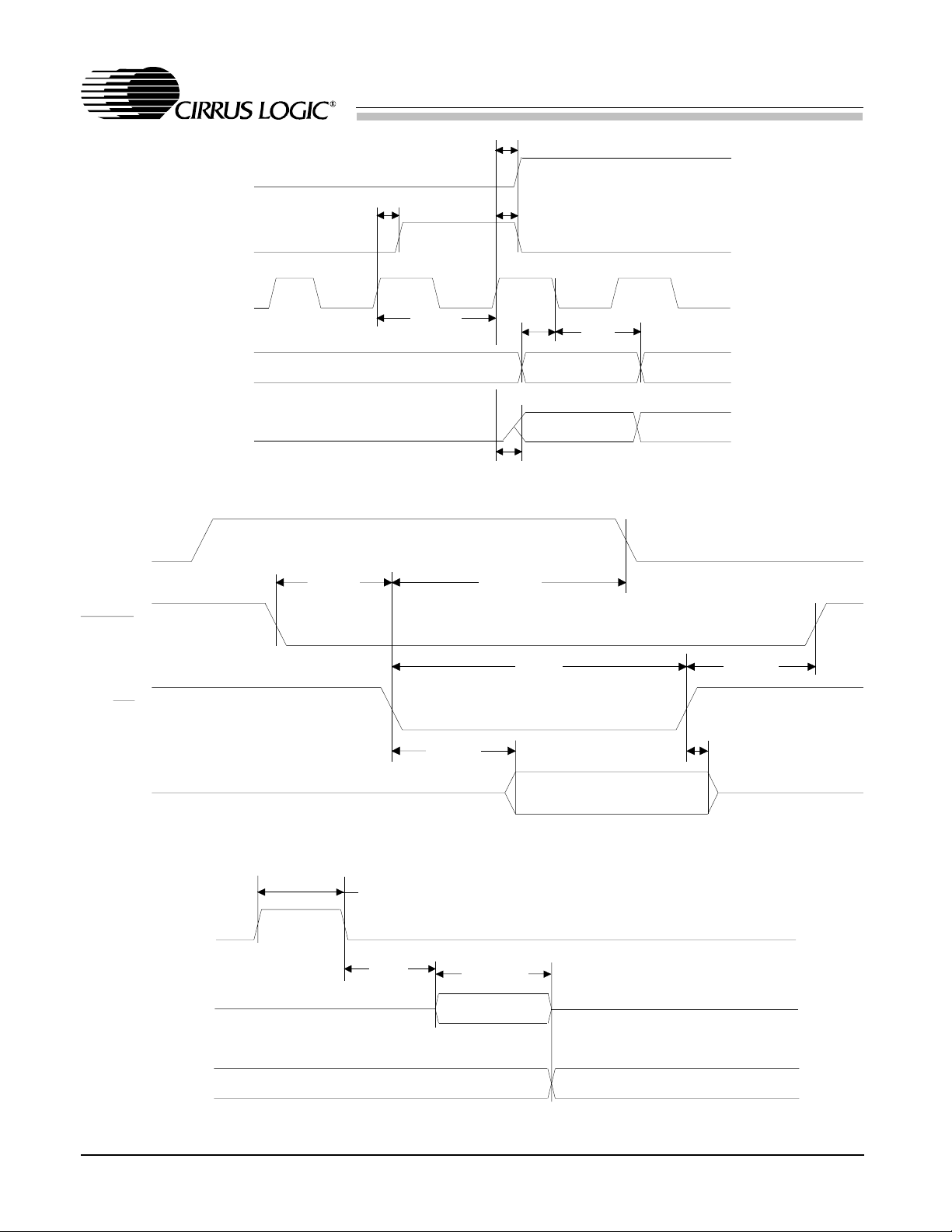

Page 9

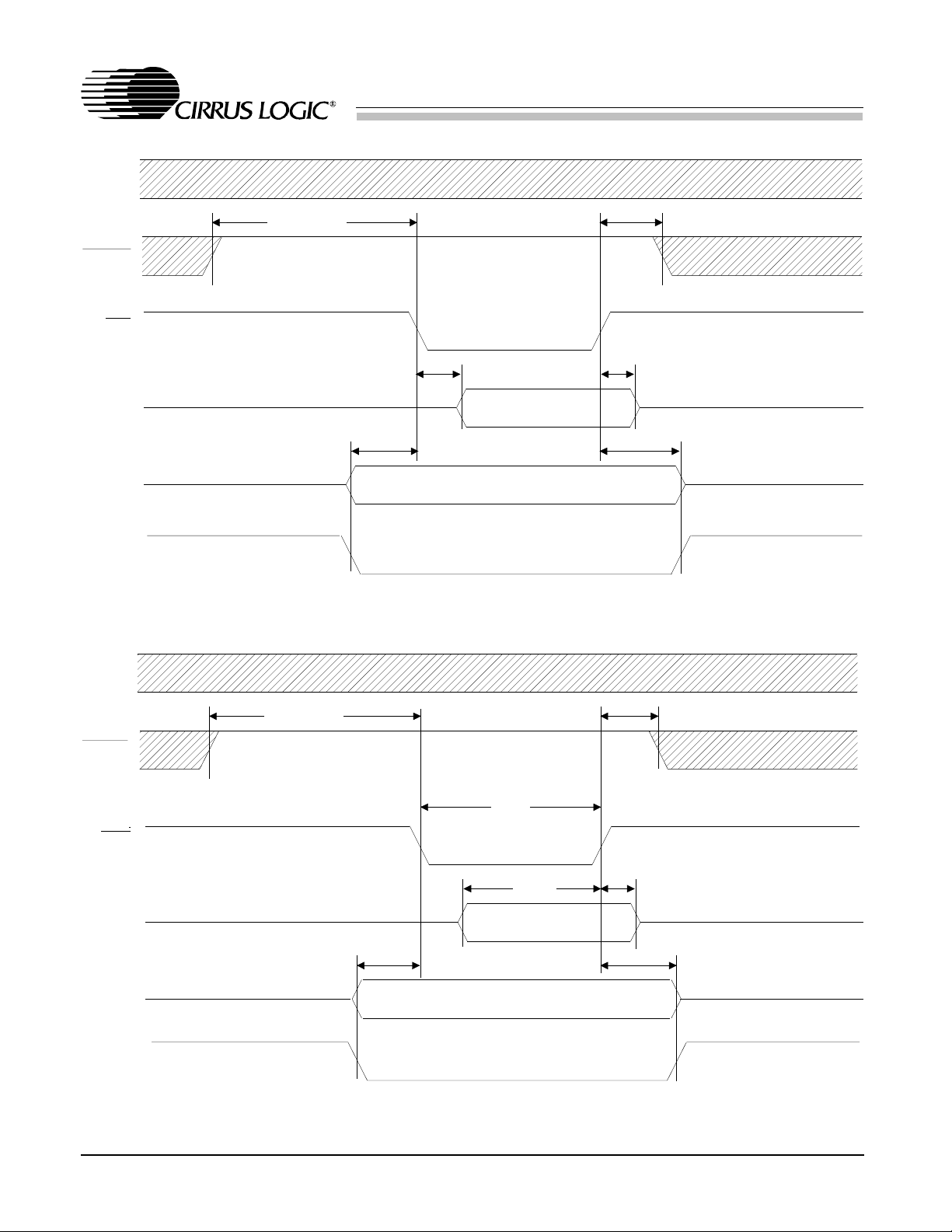

FSYNC

SF1,0=01,10

t

pd2

CrystalClear Low Cost ISA Audio System

TM

CS4235

DRQ<>

DACK<>

FSYNC

SCLK

SDIN

SDOUT

SF1,0=00

t

DKSUa

t

pd2

t

sckw

t

pd1

CS4610 DSP Seri al Port Timing

t

DRHD

t

pd2

t

s1

MSB, Left

MSB, Left

t

STW

t

h1

t

DKHDb

IOR

SD<7:0>

RESDRV

SCL/SDA

SD<>

SA<>

t

RDDV

8-Bit Mono DMA Read/Capture Cycl e

t

RESDRV

t

INIT

t

EEPROM

EEPROM read

Cod ec respo nd s to ISA activity

Reset Timing

t

DHD1

DS252PP2 9

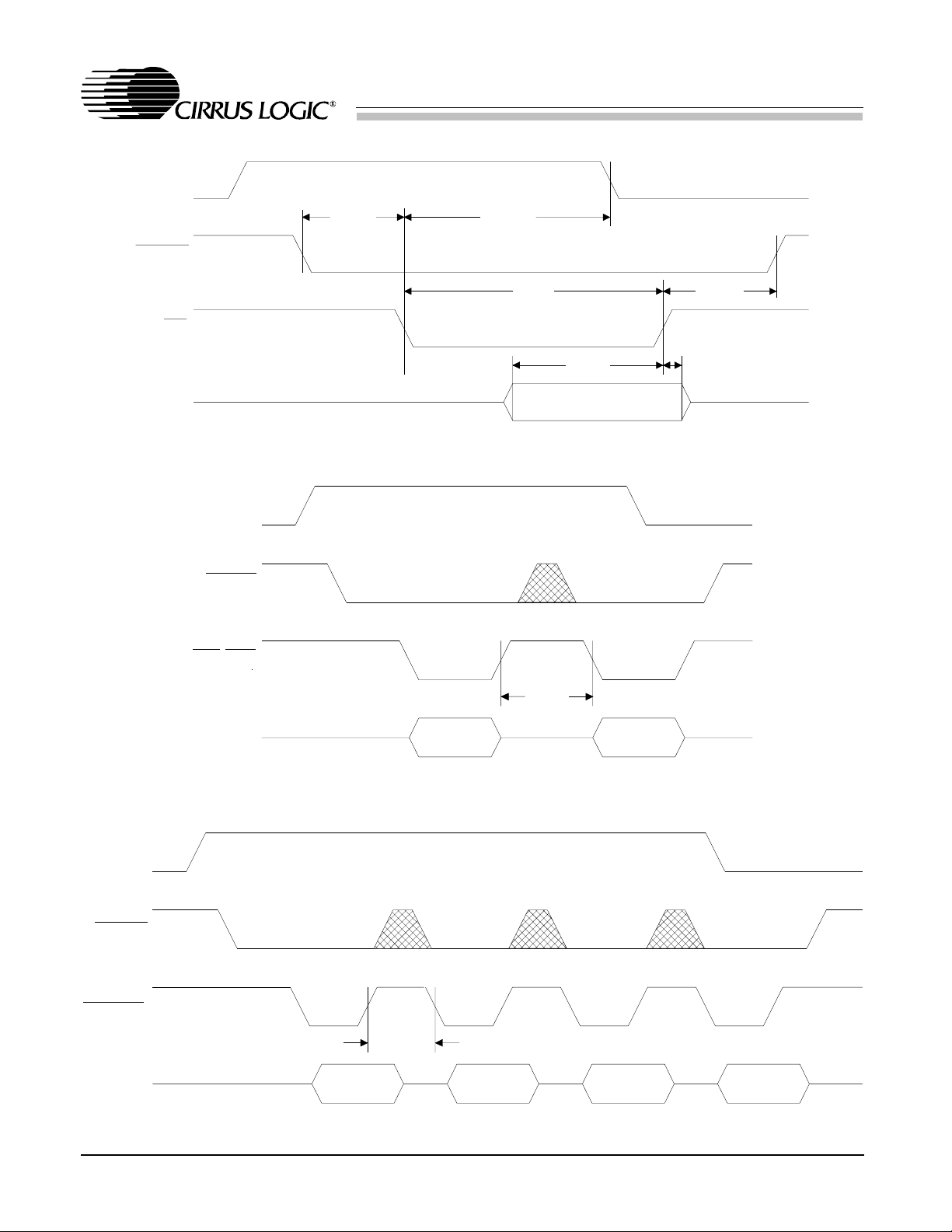

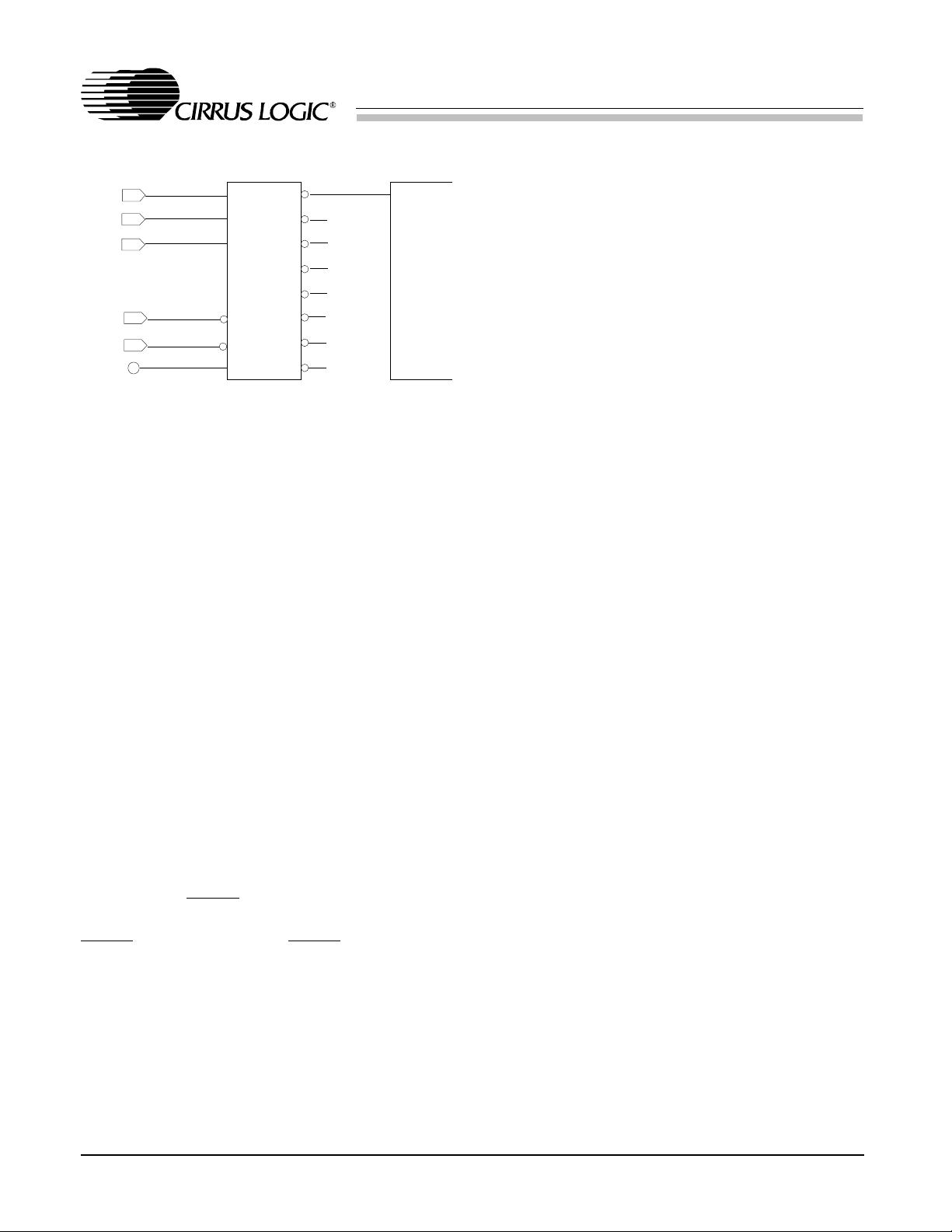

Page 10

DRQ<>

CrystalClear Low Cost ISA Audio System

TM

CS4235

DACK<>

IOW

SD<7: 0>

DRQ<>

DACK<>

IOR/IOW

t

DKSUb

t

DRHD

t

STW

t

WDSU

8-Bit Mono DMA Write/Playback Cycle

t

DHD2

t

DKHDa

DRQ<>

DACK<>

IOR/IOW

SD<7:0>

SD<7 :0>

t

BWDN

LEFT/LOW

BYTE

8-Bit Stereo or 16-Bi t Mono DMA Cycle

t

BWDN

LEFT/LOW

BYTE

LEFT/HIGH

BYTE

16-Bit Stereo DMA Cycle

RIGHT/HIGH

BYTE

RIGHT/LOW

BYTE

RIGHT/HIGH

BYTE

10 DS252PP2

Page 11

DRQ<>

CrystalClear Low Cost ISA Audio System

TM

CS4235

DACK<>

IOR

SD<>

SA<>

AEN

t

SUDK1

t

RDDV

t

ADSU

I/O Read Cycle

t

SUDK2

t

DHD1

t

ADHD

DRQ<>

DACK<>

IOW

SD<>

SA<>

AEN

t

SUDK1

t

STW

t

ADSU

I/O Write Cycle

t

WDSU

t

SUDK2

t

DHD2

t

ADHD

DS252PP2 11

Page 12

CrystalClear Low Cost ISA Audio System

TM

CS4235

GENERAL DESCRIPTION

This device i s comprised of six phys ical devices

along with Plug-and-Play support for one additional extern al device. The intern al devices ar e:

Windows Sound System Codec

Sound Blaster Pro Compatibl e Interface

Game Port (Joystick)

Control

MPU-401

FM Synthesizer

The external device is :

IDE CDROM

On power up, this part requires a RESDRV signal to initialize the internal configuration. When

initially p owered up, the p art is isolate d from the

bus, and each d evice supported by the part must

be activated via software. Once activated, each

device responds to the resources given (Address,

IRQ, and DMA channels). The devices listed

above are grouped into five logical devices, as

shown in Figure 1 (bracketed features are supported, but typically not used). The five logical

devices are:

LOGICAL DEVICE 0:

Windows Sound System Codec (WSS Codec)

Adlib/Sound Bl aster-compatible Synt hesizer

Sound Blaste r Pro Compati ble Interf ace

LOGICAL DEVICE 1: Game Port

LOGICAL DEVICE 2: Control

LOGICAL DEVICE 3: MPU401

Interrupts and DMA channels. The WSS Codec,

FM synthesizer, and the SBPro compatible devices are in ternal t o the part.

Logical Dev ice 1 is the Game Port that supports

up to two joysti ck devices.

Logical Device 2 is the Control device that supports global features of t he part. Th is device u ses

I/O locations to control power management,

joystick rate, and PnP resource data load ing.

Logical Device 3 is the MPU-401 interface. The

MPU-401 MIDI interface includes a 16-byte

FIFO for data transmitted out the MIDOUT pin

and a 16-byte FIFO for data received from the

MIDIN pin.

Logical Device 4 supports an IDE CDROM device. Although this logical device is listed as a

CDROM, any exte rnal device that fits within the

resources listed above may be substituted. This

interface, is generic and can support devices using 1 to 127 I/O loc ations for the base ad dress, 1

to 8 I/O locat ions for the alternate base address,

an interrupt, and a DMA channel.

ISA Bus Interface

The 8-bit parallel I/O and 8-bit parallel DMA

ports provide an interface which is compatible

with the Industry Standard Architecture (ISA)

bus. The ISA Interface enables the host to communicate with the various functional blocks

within the part via two types of accesses: Programmed I/O ( PIO) acce ss, and DMA access.

LOGICAL DEVICE 4: CDROM

Logical Device 0 consists of three physical devices. The WSS Codec and the Synthesizer are

grouped together since the original Windows

Sound System card expected an FM synthesizer

if the codec was pre sent. The Sound Blaster Pro

Compatible interface, SBPro, is also grouped to

allow the WSS Codec and the SBPro to share

12

A number of configuration registers must be programmed prior to any accesses by the host

computer. The configuration registers are programmed via a Plug-and-Play configuration

sequence or via configuration software provided

by Cirrus Logic.

DS252PP2

Page 13

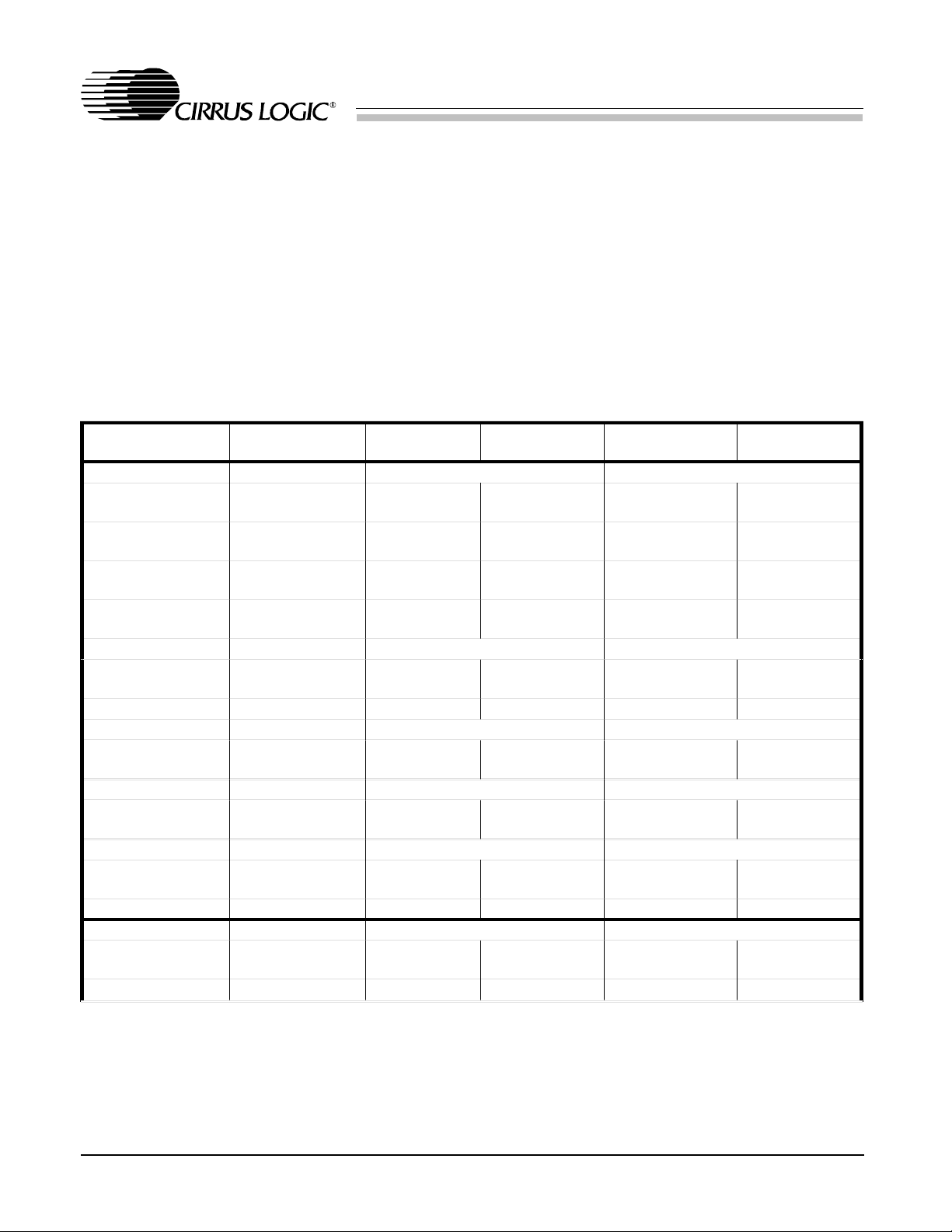

PnP ISA Bus

Interface

CrystalClear Low Cost ISA Audio System

TM

CS4235

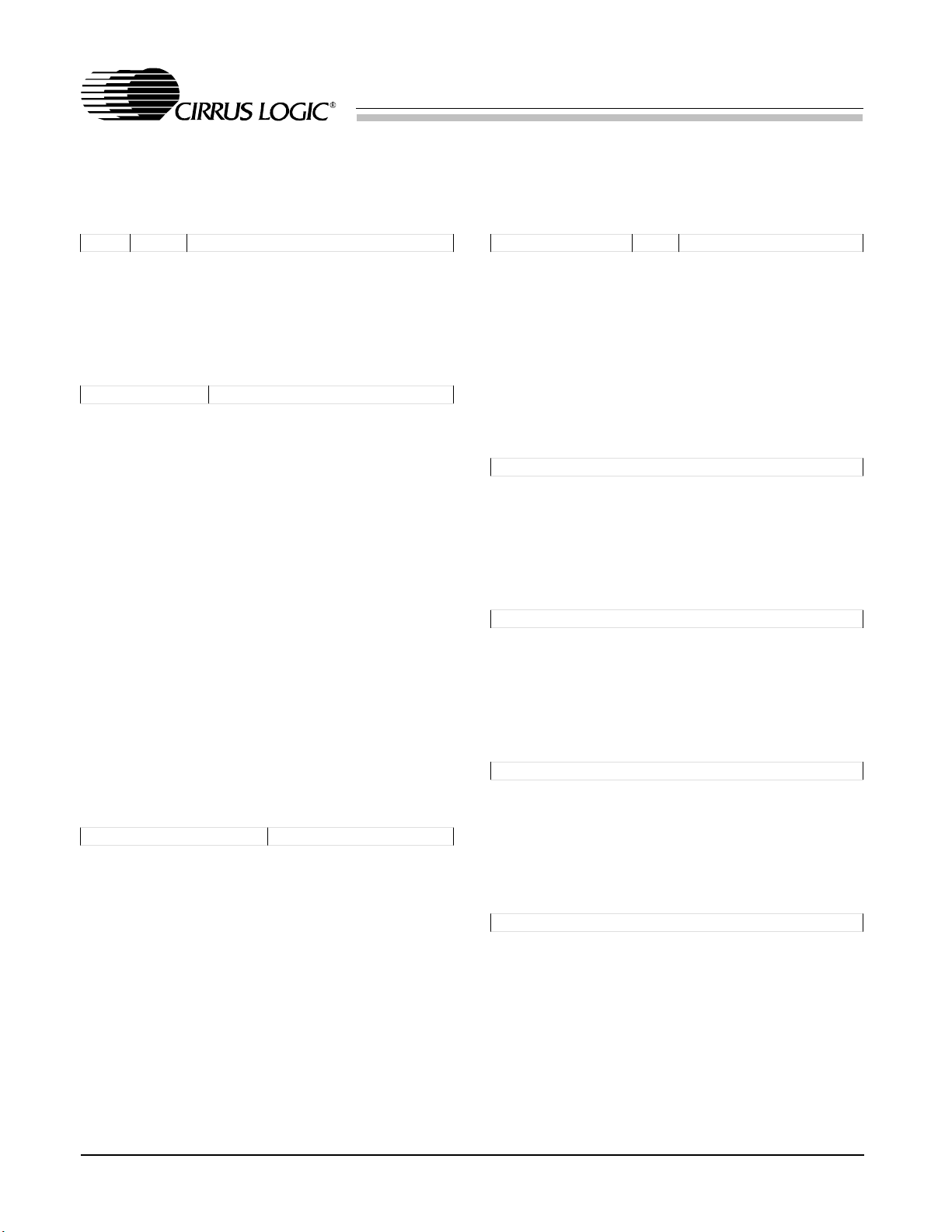

Logical Device 0

WSS Codec:

I/O: WSSbase

2 DMA Chan.

1 Interrupt

Logical Device 1

Game Port:

I/O: GAMEbase

Logical Device 2

I/O: CTRLbase

[1 Interrupt]

Figure 1. Lo gi cal De vices

Synthesis:

I/O: SYNbase

[1 Interrupt]

SBPro:

I/O: SBbase

(DMA shared)

(Interrupt shared)

I/O CYCLES

Every devic e that is enabled, requires I/O space.

An I/O cycle begins when the part decodes a

valid address on the bus while the DMA acknowledge signals are inactive and AEN is low.

The

IOR and IOW signals determine the direction of the data tr ansfer. For read cycles, the par t

will drive data on the SD<7:0> lines while the

host a sserts the

IOR strobe. Write cycles require

the host to assert data on the SD<7:0> lines and

strobe the

ing edge of the

IOW signal. Data is latched on the ris-

IOW strobe.

I/O ADDRESS DECODING

The logical devices use 10-bit or 12-bit address

decoding. The Synthesizer, Sound Blaster, Game

Control:

Logical Device 3

MPU-401:

I/O: MPUbase

1 Interrupt

Logical Device 4

CDROM:

I/O:

CDbase

ACDbase

[1 Interrupt]

[1 DMA Chan.]

Port, MPU-401, and CDROM devices support

10-bit address decoding, while the Windows

Sound System and Control devices support 12bit addres s decoding. Devi ces that support 10-b it

address decoding, require A10 and A11 be zero

for proper decode; therefore, no aliasing occurs

through t he 12-bi t address sp ace.

To p revent aliasing into the upper address space,

a "16-bit decode" opt ion may be used, where the

upper address bits SA12 through SA15 are connected to the part. SA12 -SA15 are then decod ed

to be 0,0,0,0 for all logical device address decoding. When the upper address bits are used,

the CDROM interface is no longer available

since the upper address pins are multiplexed

with the CDROM pins (See Reset and Power

Down section). If the CDROM is needed, the

circuit shown in Figure 2 can replace the SA12

through SA15 pins and provide the same functionality. Four cascaded OR gates, using a

74ALS32, can replace the ALS138 in Figure 2,

but causes a gr eater delay in add ress decoding .

DS252PP2

13

Page 14

CrystalClear Low Cost ISA Audio System

TM

CS4235

ISA Bus

SA12

SA13

SA14

SA15

AEN

+5V

Figure 2 . 16 -b it Dec ode Circ uit

74ALS138

1

A

2

B

3

C

4

G2A

5

G2B

6

G1

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

15

AEN

DMA CYCLES

The part supports up to three 8-bit ISA-compatible DMA channels. The default hardware

connections, which can be changed through the

hardware conf iguration d ata, are:

D M A A = I SA DMA channel 0

D M A B = I SA DMA c han nel 1

D M A C = I SA DMA c han nel 3

The typical configuration would require two

DMA channels. One for the WSS Codec and

Sound Blaster playback, and the other for WSS

Codec capture (to support full-duplex). The

CDROM, if used, can also su pport a DMA channel, although t his is not ty pical.

DMA cycles are distinguished from control register cycles by the generation of a DRQ (DMA

Request). The host acknowledges the request by

generating a

DACK (DMA Acknowledge) signal. The t ransfer of audio data occurs during the

DACK cycle. During the DACK cycle the address lines are ign ored.

The digital audio data interface uses DMA request/grant pins to transfer the digital audio data

between the part and the ISA bus. Upon receipt

of a DMA request, the host processor responds

with an acknowledge signal and a command

strobe which tran sfers data to and from the part,

eight bits at a time. The request pin stays active

until the ap propriate number of 8-bit cycles have

occurred. The number of 8-bit tran sfers will vary

depending on the digital audio data format, bit

resolution, and o peration mode.

The DMA request signal can be asserted at any

time. Once asserted, the DMA request will remain asserted until a complete DMA cycle

occurs. A complete DMA cycle consists of one

or more bytes depending on which device internal to the pa rt is generatin g the request.

INTERRUPTS

For Plug-and-Play flexibility, seven interrupt

pins are supported, although only one or two are

typically used. The default hardware connections, which can be modified through the

hardware config uration data, are:

IRQ A = ISA Interrupt 5

IRQ B = ISA Interrupt 7

IRQ C = ISA Interrupt 9

IRQ D = ISA In terrupt 11

IRQ E = ISA Interrupt 12

IRQ F = ISA In terrupt 15

IRQ G is new and defaults to not being connected for backwards compatibility. This new

interrupt pin would typically be connected to

ISA Interrupt 10. New designs that use IRQ G

must change the Hardware Configuration Data to

indicate which ISA Interrupt is connected to

IRQ G.

The typical configuration would support two interrupt sources: one shared between the WSS

Codec and the Sound Blaster Pro co mpatible devices, and the other for the MPU401 device.

Interrupts are also supported for th e FM Synthesizer, Control, and CDROM devices, but are

typically n ot used.

14

DS252PP2

Page 15

CrystalClear Low Cost ISA Audio System

TM

CS4235

PLUG AND PLAY

The Plug-and-Play (PnP) interface logic is compatible with the Intel/Microsoft Plug-and-Play

specification, version 1.0a, for an ISA-bus device. Since the part is an ISA-bus device, it only

supports ISA-compatible IRQs and DMA channels. Plug and Play compatibility allows the PC

to automatically configure the part into the system upon power up. Plug and Play capability

optimally resolves conflicts between Plug and

Play and non-Plug and Play devices within the

system. Alternatively, the PnP feature can be bypassed. See the Bypassing PnP section for more

information. For a detailed Plug-and-Play protocol description, please refer to the Plug and Play

ISA Specifica tion.

To s upport Plug-and-Play in ISA systems that do

not have a PnP BIOS or a PnP-aware operating

system, the Configuration Manager (CM) TSR

and an ISA Configuration Utility (ICU) from Intel Corp. are used to provide these functions.

The CM isolates the cards, assigns Card Select

Numbers, reads PnP card resource requirements,

and allocates resources to the cards based on

system resource availability. The ICU is used to

keep the BIOS and t he CM informed of the current system configuration. It also aids users in

determining configurations for non-PnP ISA

cards. A more thorough discussion of the Configuration Manager and the ISA Configuration

Utility can be found in the Product Development

Information document of the Plug and Play Kit

by Intel Corp. In a PnP BIOS system, the BIOS

is responsible for configuring all system board

PnP devices. Some systems require additional

software to aid the BIOS in co nfiguring PnP ISA

cards. The PnP BIOS can execute all PnP functions independently of the type of operating

system. However, if a PnP aware operating system is present, the PnP responsibilities are s hared

between the BIOS and the ope rating system. For

more information regarding PnP BIOS, please

refer to the latest revision of the Plug and Play

BIOS Specification published by Compaq Computer, Phoenix Technologies, and Intel.

The Plug and Play configuration sequence maps

the various functional blocks of the part (logical

devices) into the host system address space and

configures both th e DMA and interru pt channels.

The host has access to the part via three 8-bit

auto-configuration ports: Address port (0279h),

Write Data port (0A79h), and relocatable Read

Data port (020Bh - 03FFh ). The read data port is

relocated automatically by PnP software when a

conflict occurs. Note that the Address Port can

be moved for motherboard devices. See the Ad-

dress Port Configuration section for more

details.

The configu ration sequen ce is as fo llows:

1. Host send s a software key whic h places all

PnP cards in the sleep state (or Plug-andPlay mode).

2. The CS4 235 is isola ted from the sy stem using

an isolation s equence.

3. A unique identifier (h andle) is ass igned to t he

part and the reso urce data is read.

4. After all cards’ resource requirements are de-

termined, the host uses the handle to assign

conflict- free resour ces

5. After the c onfiguration reg isters have been

programmed, e ach configu red logical device

is activated.

6. The part is then removed from Plug-and-Pla y

mode.

Upon power-up, th e chip is inactive and must be

enabled via software. The CS4235 monitors

writes to the Address Port . If the host sends a

PnP initiation key, consisting of a series of 32

predefined byte writes, the hardware will detect

DS252PP2

15

Page 16

CrystalClear Low Cost ISA Audio System

TM

CS4235

the key an d place the part into the Plug-and-Pla y

(PnP) mode. Another method to prog ram the part

is to use a special Crystal initiation key which

functions like the PnP initiation key, but can be

invoked by the user at any time. However, the

Crystal Key only supports one Audio Codec per

system. The Crystal key and special commands

are detailed in the Crystal Key and Bypassing

PnP sections.

The isolation sequence uses a unique 72-bit serial identifier. The host performs 72 pairs of I/O

read accesses to the Read Data port. The identifier determines what data is put on the data bus

in respons e to th ose read acc esses. When the isolation sequence is complete, the CM assigns a

Card Select Number (CSN) to the part. This

number distingu ishes the CS4235 from the other

PnP devices in the system. The Configuration

Manager (CM) then reads t he resource data from

the CS4235. The 72-bit identifier and the resource data is either stored in an external

user-programmable E

2

PROM, or loaded via a

"hostload" procedure from BIOS before PnP

software is initi ated.

The CM determines the necessary resource requirements fo r the system and then pr ograms the

part through the configurat ion registers . The configuration register data is written one logical

device at a time. After all logical devices have

been configured , CM activates each device individually. Each logical device is now availa ble on

the ISA bus and responds to the programmed

address rang e, DMA channels, and interrup ts that

have been all ocated to t hat logical de vice.

PnP Data

Hardware Configuration and Plug-and-Play re-

source data can be loaded into the part’s RAM.

The data may be stored in an external E

2

PROM

or may be downloaded from the host. Internal

default PnP data is provided for motherboard designs.

To load the data, refer to the Loading Resource

Data section. The following is the Plug-and-Play

resource data:

The first nine bytes of the PnP resource data are

the Plug-and-Play ID, which uniquely identifies

the Audio Codec from other PnP devices. The

PnP ID is broken down as follows:

0Eh, 63h - Crystal ID - ’CSC’ in compressed

ASCII. (See the PnP Spec for more

information)

42h - OEM ID. A unique OEM ID must be ob-

tained from Crystal for e ach unique

Crystal product used .

25h - Crystal produc t ID for the CS4235

FFh, FFh, FFh, FFh - Serial number. This can

be modified by each OE M to uniquel y

identify their card.

??h - Checksum.

Of the 9-byte serial number listed above, Cirrus

software uses the first two bytes to indicate the

presence of a CS4235, and the fourth byte, 0x25 ,

to indicate the CS4235; therefore, these three

bytes must not b e altered. The de fault PnP ID, in

hex, is 0E634236FFFFFFFFA9 for backwards

compatibility.

The next 3 bytes are the PnP version number.

The default is versio n 1.0a: 0Ah , 10h, 05h.

The next seque nce of bytes are the ANSI i dentifier string. The default is: 82h, 0Eh, 00h,

’Crystal Cod ec’, 00h.

The logical device data must be entered using

the PnP ISA Specification for mat. Typical logical

device values are found in Table 1. Internal default E

2

PROM data is found in Appendix A.

Loading Resource Data

2

A s e r i al E

PROM interface allo ws user-programmable serial number and resource data to be

stored in an external E

2

PROM. The interface is

compatible with devices from a number of ven-

16

DS252PP2

Page 17

CrystalClear Low Cost ISA Audio System

TM

CS4235

dors and th e size may vary accor ding to specific

customer requirements. The maximum size for

resource data supported by the part’s internal

RAM is 384 bytes of combined Hardware Configuration and PnP resource data. With the

addition of the 4-byte header, the maximum

amount of E

2

PROM space used would be 388

bytes. However, the part also supports firmware

upgrades v ia the E

upgrades, t he E

2

PROM. To support firmware

2

PROM size must be great er than

770 bytes. After power-up, the existence of an

2

E

PROM is checked by reading the first two

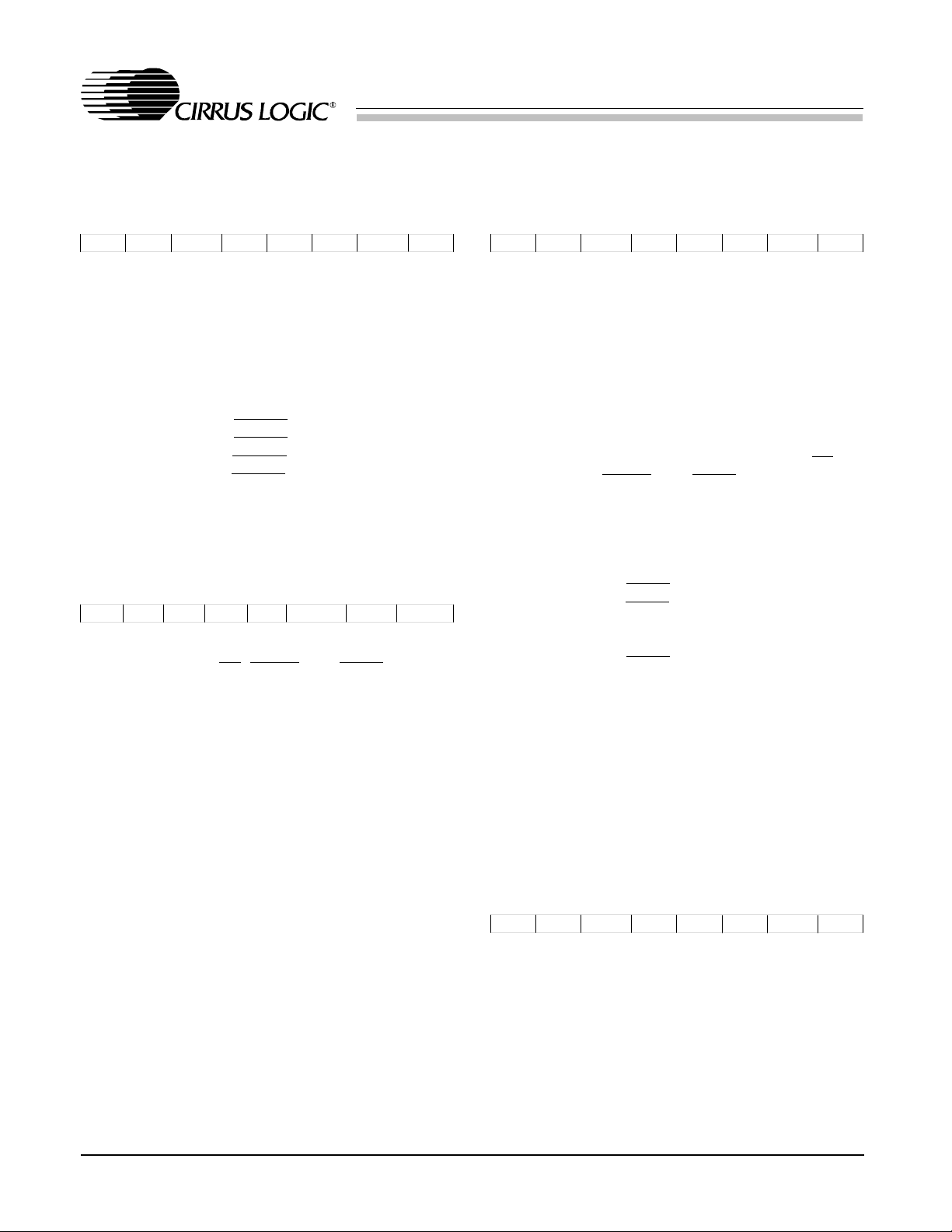

Physical Device Logical Device Best Choice Acceptable

WSS 0 ANSI ID = CSC0000 ANSI ID = WSS/SB

16-bit address

decode

high true

edge sensitive

8-bit, count by

byte, type A

same DMA1

Synthesis 0

16-bit address

decode

SB Pro 0

16-bit address

decode

Game Port 1 ANSI ID = CSC0001 ANSI ID = GAME

16-bit address

decode

Control 2 ANSI ID = CSC0010 ANSI ID = CTRL

16-bit address

decode

MPU401 3 ANSI ID = CSC0003 ANSI ID = MPU

16-bit address

decode

WSSbase

Length/Alignment

IRQ 5

DMA0

(playback)

(record)

SYNbase

Length/Alignment

IRQ ---- ---- --- -

SBbase

Length/Alignment

GAMEbase

Length/Alignment

CTRLbase

Length/Alignment

IRQ ----

MPUbase

Length/Alignment

IRQ 9 9,11,12,15 ----

534h

4/4

(SB share)

1

(SB share)

0, 3 0, 1, 3 ----

388h

4/8

220h

16/32

200h

8/8

120-FF8h

8/8

330h

2/8

bytes from the E

two bytes from the E

BBh, then the rest of the E

loaded into the internal RAM. If the first two

bytes are n’t correct, the E

to exist. For motherboard designs, internal default PnP data is provided or a Hostload

sequence can be used to update the resource

data. If the part is installed on a plug-in card,

then an external E

that the proper PnP resource data is loaded into

the internal RAM prior to a PnP sequence. See

Choice 1

534-FFCh

4/4

5,7,9,11,12,15

(SB share)

1, 3

(SB share)

388h

4/8

220-260h

16/32

208h

8/8

330-360h

2/8

2

PROM interface. If the first

2

PROM port read 55h and

2

PROM is assumed not

2

PROM is required to ensure

Sub opti mal

Choice 1

534-FFCh

4/4

5, 7, 9, 11, 12, 15

(SB share)

0, 1, 3

(SB share)

388-3F8h

4/8

220-300h

16/32

330-3E0h

2/8

2

PROM data is

Sub optimal

Choice 2

---- Feature not supported in the listed configuration, but is supported through customization.

Table 1. Typ ical Moth erboard Pl ug-and- Play Reso urce Data

DS252PP2

17

Page 18

CrystalClear Low Cost ISA Audio System

TM

CS4235

the External E2PROM section for more information on the serial E

2

E

PROM programming.

The format for the data stored in the E

2

PROM interface and

2

PROM is

as follows:

2 bytes E

2 bytes length o f resource data i n E

2

PROM validation: 55h , BBh

2

PROM

19 bytes Hardware Co nfiguration

9 bytes Plug and Play ID

3 bytes Plug and Play v ersion number

Variable number of bytes of user defined

ASCII ID string

Logical Device 0 (Windows Sound System,

FM Synthesizer, Sound Blaster Pro) data

patches in E

2

PROM, gives the maximum functionality at power-up without the need for a

software driver.

The firmware patch data is typically included at

the end of th e PnP resource data. Cirrus provide s

a utility that will read in patch data from a file,

and append it to the PnP resource data. The

patch file must be obt ained from Cirrus.

The Crystal K ey

NOTE: The Crystal Key cannot differentiate between mult iple Cirrus Au dio Codec s in a sys tem;

therefore, ONLY ONE audio part is allowed in

systems using th e Crystal Key. To allow multiple

parts in a system, the Plug-and-Play isolation sequence must be used since it supports multiple

parts via the serial identifier used in the isolation

sequence. Crystal Key 2 is also designed to allow motherboard and add-in card chips to

co-exist in a system.

Logical Device 1 ( Game Port) data

Logical Device 2 ( Control) dat a

Logical Device 3 ( MPU-401) data

Logical Device 4 ( CD-ROM) data

End of Resource b yte & checksum byt e

Firmware patch code.

The default internal E

2

PROM data, in assembly

format, can be found in Appendix A.

Loading Firmware Patc h Data

An external E2PROM is read during the powerup sequence that stores Hardware Configuration

and PnP data, and firmware patch data. The part

contains RAM and ROM to run the core processor. The RAM allows updates to the core

processor functionality. Placing the firmware

The Crystal ke y places the part in the config uration mode. Once the Crystal key has been

initiated, an alternate method of programming

the configuratio n registers may be used. This alternate method is referred to as the "SLAM"

method. The SLAM method allows the user to

directly access the configuration registers, configure, and activate the chip, and then,

optionally, disable the PnP and/or Crystal key

feature. Th e SLAM method uses command s that

are similar to t he PnP commands; howeve r, they

are different since the user has direct access to

the configuration registers. To use the SLAM

method, see the Bypassing PnP section.

The following 32 bytes, in hex, are the Crystal

key:

96, 35, 9A, CD, E6, F3, 79, BC,

5E, AF, 57, 2B, 15, 8A, C5, E2,

F1, F8, 7C, 3E, 9F, 4F, 27, 13,

18

09, 84, 42, A1, D0, 68, 34, 1A

DS252PP2

Page 19

Bypassing Plug and Pla y

The SLAM method allo ws the user to bypass th e

Plug and Play features and, as an option, allows

the part t o act like a non-Plug and Play or legacy

device; however, the SLAM method only supports one Cirrus Audio IC per system. The user

directly prog rams the resou rces into the p art, and

then optional ly disables the PnP and/or the Crystal Key, which forces the part to disregard any

future PnP or Crystal initiation key sequences

(All activated logical devices appear as legacy

devices to PnP). The Crystal and PnP keys can

also be disabled through the E

2

PROM. The

SLAM method uses the Address Port (AP) s imilarly to Plug-an d-Play. Although the stand ard AP

is 279h, two other selections are available for

non-standard implementations. See the Address

Port Configurat ion section for more detai ls.

To use the SLAM method, the following sequence must be foll owed:

1. Host sends 32-byte Crystal key to the AP,

chip enters configura tion mode.

CrystalClear Low Cost ISA Audio System

TM

CS4235

Interrupt Select 0 (2 2h, xxh)

Interrupt Select 1 (2 7h, xxh)

DMA Select 0 (2Ah, xxh )

DMA Select 1 (25h, xx h)

Activate Device (3 3h, 01h)

(33h, 00h de activates a d evice)

4. Repeat #3 for each logical device to be enabled. (Not all d evices need b e enabled.)

5. Host activate s chip by writing a 79h to AP.

6. (Optional) Hos t disables PnP Key by writing

a 55h to CTRLbase+5. The part will n ot participate i n any future PnP cycles. The Crystal

Key can als o be disabled by writing a 56h to

CTRLbase+5.

NOTE: To enable the PnP/Crystal Keys after

they have been disabled by the SLAM

method, bring the RESDRV pin to a logic

high or remove power from th e device.

2. Host programs CSN (Card Select Number)

by writing a 06h a nd 00h to th e AP.

3. Host programs the configuration registers of

each logical devic e by writing to the AP. The

following data is the maximum amount of information per devic e. All current devices onl y

need a subset of this data:

Logical Device ID (1 5h, xxh)

xxh is logical d evice number: 0-5

I/O Port Base Address 0 (47h, xxh, xxh)

high byte , l ow byte

I/O Port Base Address 1 (48h, xxh, xxh)

high byte , l ow byte

I/O Port Base Address 2 (42h, xxh, xxh)

high byte , l ow byte

DS252PP2

The following illustrates typical data sent using

the SLAM method.

006h, 001h ; CSN=1

015h, 000h ; LOGICAL DEVICE 0

047h, 005h, 034 h ; WSSbase = 0x534

048h, 003h, 088 h ; SYNbase = 0x388

042h, 002h, 020 h ; SBbase = 0x220

022h, 005h ; WSS & SB IRQ = 5

02Ah, 001h ; WSS & SB DMA0 = 1

025h, 003h ; WSS capture DMA1 = 3

033h, 001h ; activate log ical device 0

015h, 001h ; LOGICAL DEVICE 1

047h, 002h, 000 h ; GAMEbase = 0x200

033h, 001h ; activate log ical device 1

19

Page 20

CrystalClear Low Cost ISA Audio System

TM

CS4235

015h, 002h ; LOGICAL DEVICE 2

047h, 001h , 020h ; CTRLbase = 0x1 20

033h, 001h ; activate l ogical dev ice 2

015h, 003h ; LOGICAL DEVICE 3

047h, 003h , 030h ; MPUbase=0x330

022h, 009h ; MPU IRQ = 9

033h, 001h ; activate l ogical dev ice 3

079h ; activate audi o device

If all the above data is s ent, after th e Crystal ke y,

all devices except the CDROM will respond to

the appropr iate resources given.

Crystal Key 2

A new feature of this part is the addition of another way to bypass the PnP interface using a

new key, designated Crystal Key 2 (CK2). This

new key is designed for Codecs on the motherboard that are hidden from normal PnP. The

following 32 bytes, in hex, are Crystal Key 2

followed by the upper 8 bits of the Read Data

port (RDP):

95, B1, D8, 6C, 36, 9B, 4D, A6,

D3, 69, B4, 5A, AD, D6, EB, 75,

BA,DD, EE, F7, 7B, 3D, 9E, CF,

67, 33, 19, 8C, 46, A3, 51, A8, <RDP>

This key differs g reatly from the o riginal Crystal

Key in that th e 33rd byte defin es the upper 8 b its

of the 10-bit Read Data port address, with the

lower 2 bits equal to 11. As an example, if the

RDP byte is 0x82, then the actual Read Data

port is 0x20B. Another difference is that the

original Crystal Key uses custom commands and

is write-only; whereas, CK2 places the part in a

PnP Configuration state and uses standard PnP

commands to access PnP configuration regis ters.

Since CK2 is unique to th e CS4235, the PnP isolation sequenc e is bypassed.

CK2 differs from normal Pn P i n that the RDP is

read/write instead of read-only. In PnP the RDP

is read-on ly and a second add ress, design ated the

Write Data Port (0xA79), is used to write data

into PnP registers. Using CK2, all configuration

is done throu gh the RDP, there is no Write Data

Port. When finished, a Wait-for-Key command

should be issued to the Address Port which

places the part back in the normal mode of operation. Not e that the Addres s Port (AP) can also

be moved away from the normal PnP location of

0x279. See the Address Port Configuration sec-

tion for more information.

The CK2 configura tion sequenc e is as follows:

1. CK2 32 bytes are sent to the Address Port followed by the u pper 8 bits of th e RDP.

2. The AP and RDP are used to read/write configuration informati on in normal PnP fashion.

6. A Wait-for-Key command is sent removing

the part from the c onfiguration s tate.

The particular PnP register is set using the Address Port and the data for that register is

read/written to/from the RDP. As an example,

when finished configuring the part, to send the

Wait-for-Key co mmand, a 0x02 is sent to the AP

(selecting the Config. Control register) and a

0x02 is sent to the RDP. This causes the part to

exit the conf iguration state and enter normal operation (Wait-for-Key).

Hardware Configuration Data

The Hardware Configuration data contains mapping information that links interrupt and DMA

pins with actual interrupt numbers used by PnP

and SLAM procedures. The Hardware Configuration data p recedes the PnP Resource d ata.

The Hardware Config uration data is either 19 or

23 bytes lon g and contains the data necessary to

configure the part. If an E

2

PROM is not used

20

DS252PP2

Page 21

CrystalClear Low Cost ISA Audio System

TM

CS4235

(Hostload), the first four bytes are not needed;

therefore, the configurat ion data is on ly 19 bytes

long. The configuration data maps the many

functions of the logical devices to the physical

pins of the ch ip. Table 2 lists the Hardware Configuration by tes. The detailed b it descriptions for

listed as "res" in the bit position (and shou ld be

written to 0), "rbc" is "reserved, backwards compatible" for bits that were used on previous

chips, but are no longer required on this chip.

These bits are read/writable but should generally

be set to 0 for bac kwards compatibi lity.

each byte follows. While the reserved bits are

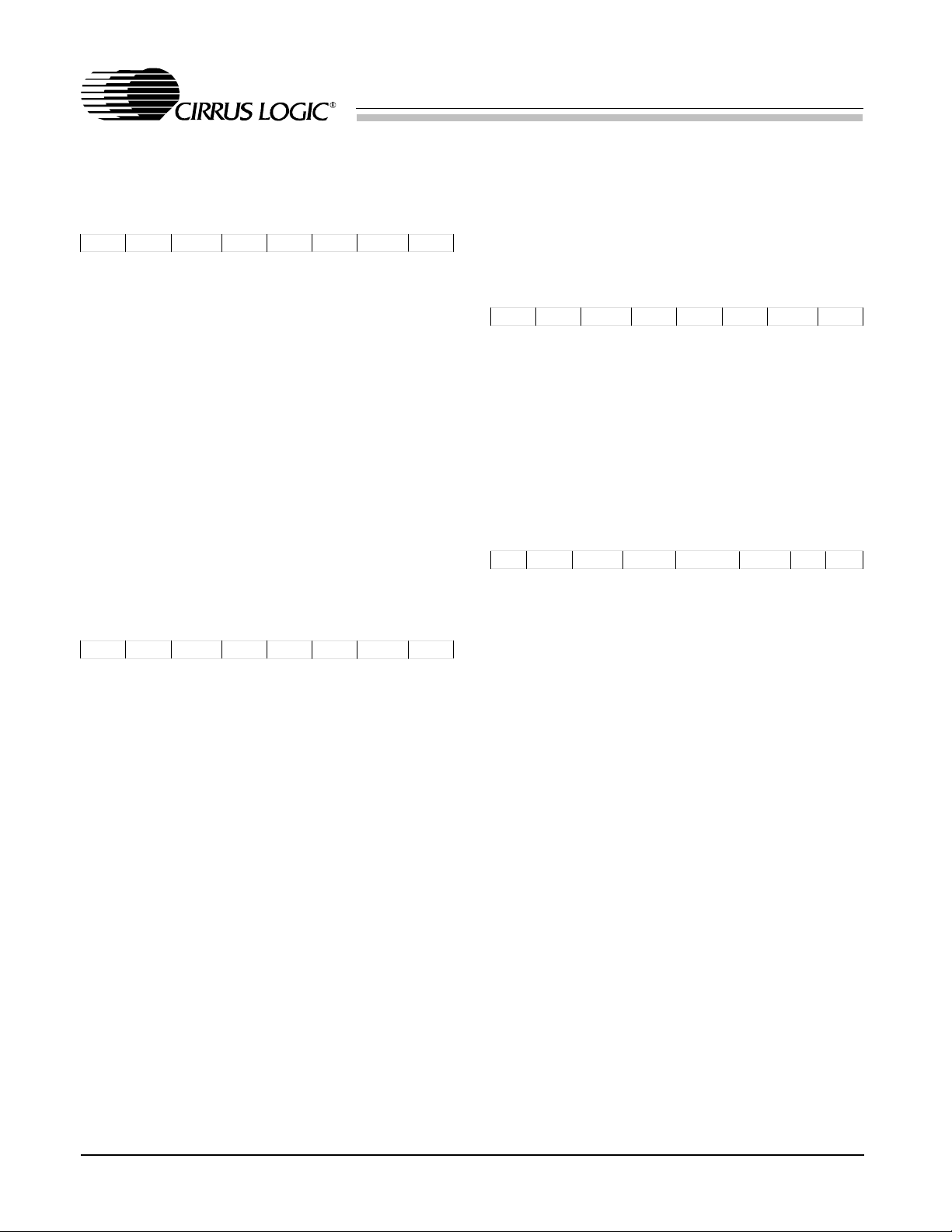

BYTE Default Description

155h E

The first two bytes indicate that the E

2 BBh E2PROM validation byte 2

3 00h High byte for length of data in E2PROM

4 DDh Low byte for length of data in E2PROM

5 00h Alternate CDROM (Logical De vice 4), ACDbase, Add ress lengt h mask

6 03h RESERVED

7 80h Misc. Configuration Bits: CDROM Interrupt Polarity, Key Disables, VCEN

8 00h Global Configuration Byte: IFM, VCF1, WTEN

9 05h Code Base Byte

10 20h FM Volume Scaling

11* 04h RESERVED - Must be 0x04

12* 08h RESERVED - Must be 0x08

13* 10h RESERVED - Must be 0x10

14 80h Mono and DSP Port Control

15 00h E

16 00h Global Configuration Byte 2: EECS, AUX1R, 3DEN, DSPD1, PSH

17 08h CDROM (Logical Device 4), CDbase, Address length

18* 48h RESERVED - Must be 0x48

19 75h IRQ A/B Selection: Lower nibble = A, Upper nibble = B.

Along with next two bytes - specify hardware interrupts tied to IRQA-IRQF pins

20 B9h IRQ C/D Selection: Lower nibble = C, Up per nibble = D.

21 FCh IRQ E/F Selection: Lower nibble = E, Upper nibble = F.

22 10h DMA A/B Selection: Lower nibble = A, Upper nibble = B.

This byte and the next byte specify hardware DRQ/DACKs tied to the DMAA-DMAC pins

23 03h DMA C/IRQ G Selection: Lower nibble = DMA C, Upper nibble = IRQ G

2

PROM validation byte 1.

2

PROM Checksum

and the 7th IRQ pin - IRQ G

2

PROM exists.

2

NOTE:The first fo ur bytes are exclusiv e to the E

* Currently not supported. Must be set to default values given in the table.

Table 2. Hardware Con figuration Data

DS252PP2

PROM and are not used in the Hostload mode.

21

Page 22

CrystalClear Low Cost ISA Audio System

TM

CS4235

HW Config. Byte 5: A CDbase Address Lengt h

Mask, Default = 0 0000000

D7 D6 D5 D4 D3 D2 D1 D0

res res res res res CM2 CM1 CM0

CM2-CM0 Address bit masks for the Alternate

CDROM address decode, ACDbase.

See the

for more details on ACDbase.

ACDbase must be on the same paragraph boundry as the address lengh

decode.

000 001 011 111 xxx - all others, RESERVED

CDROM Interface

ACDCS low for 1 byte

ACDCS low for 2 bytes

ACDCS low for 4 bytes

ACDCS low for 8 bytes

section

HW Config. Byte 7: Misc. Configu ration Bits ,

Default = 10000000

D7 D6 D5 D4 D3 D2 D1 D0

IHCD rbc PKD CKD CK2D VCEN rbc rbc

VCEN Volume Control Enable. When set,

UP, DOWN, and MUTE pins be-

the

come active and provide a hardware

master volume control.

CK2D Crystal Key 2 disable. When set,

block s the part from re ceiv ing the

2nd Crystal key.

CKD Crystal Key disable. When set, blocks

the part from receiving the Crystal

key.

HW Config. Byt e 8: Global Confi guration By te,

Default = 1000000 0

D7 D6 D5 D4 D3 D2 D1 D0

IFM VCF1 rbc res WTEN rbc res res

WTEN Wavetable Serial Port Enable. When

set, enables the CS9236 SingleChip Wavetable Music Synthesizer

serial port pins. This function is also

available in C8. NOTE: The DSP

SPE bit in I16 must be 0 for the

wavetable port to be enabled.

VCF1 Hardware Volume Control Format.

This bit controls the format of the

hardware volume control pins

DOWN, and MUTE. The volume control is enabled by setting VCEN in

the previous Hardwar e Configuration

byte. VCF1 is also available through

C8.

MUTE is a momentary switc h.

0 -

MUTE togg les be tween m ute and

un-mute . Pre ssing t he up or do wn

switch a lwa ys un -mut es.

MUTE is not used. Two button

1 -

volume control. Pressing the up

and down buttons simultaneously

causes the volume to mute.

Pressing up or down un-mutes.

IFM Internal FM. When set, the internal

FM synthesizer is enabled. When

clear, FM is disabled.

UP,

HW Config. Byt e 9: Code Base Byte,

PKD PnP Key disable. When set, blocks

the part from receiving the Plug-andPlay key.

IHCD Int errupt High - CDROM. When set,

CDINT is active high. When clear,

CDINT is active low.

22

Default = 0000010 1

D7 D6 D5 D4 D3 D2 D1 D0

CB7 CB6 CB5 CB4 CB3 CB2 CB1 CB0

CB7-CB0 Code Base Byte. Determines the code

base located in the E

correct, the Firmware code after the

PnP resource data is not loaded.

0x05 - CS4235 E

0x06 - CS4235 Host Load

2

PROM. If not

2

PROM Load

DS252PP2

Page 23

HW Config. Byte 10: FM Volume Scal ing,

Default = 00100000

D7 D6 D5 D4 D3 D2 D1 D0

res FMS2 FMS1 FMS0 res res res res

CrystalClear Low Cost ISA Audio System

MIM Mono In mute. When set, th e MIN

TM

analog input is muted. When clear,

MIN is mixed into the output mixer

at a level set by MIA.

CS4235

HW Config. Byt e 15: E2PROM Checksum

FMS2-FMS0 FM Volume Scaling relative to wave-

table digital input . These bits set the

default FM volume level relative to

the CS9236 wavetable interface

port. Once initialized, t hese bits can

be controlled through X19. These

bits are provided for backwards compatibility with previous chips.

010 - 0 dB

011 - +6 dB

100 - -12 dB

101 - -6 dB

110 - +12 dB

111 - +1 8 dB

HW Config. Byte 14: M ono & DSP Port

Control, Default = 1 0000000

D7 D6 D5 D4 D3 D2 D1 D0

MIM res res res SF1 SF0 SPE MIA

This register sets the power up defaults for these features. After power-up, I16 may be used to control the

DSP serial port, and I26 may be used to control the

Mono Input.

MIA Mono Input Attenuate. When set, the

MIN input is attenuat ed 9 dB. When

clear, the MIN volume is 0 dB.

SPE DSP Serial Port Enable. When set,

the DSP serial por t is enabled.

SF1,0 DSP Serial Port Format. Selects the

format of the serial port once enabled by SPE. See the

Audio Data Port

tails.

00 - 64-bit enhanced.

01 - 64 bit.

10 - 32 bit.

11 - ADC/DAC.

section for more de-

DSP Serial

Default = xxxx xxxx

D7 D6 D5 D4 D3 D2 D1 D0

EC7 EC6 EC 5 EC 4 EC3 EC2 EC1 EC0

EC7-EC0 E2PROM checksum byte. Starts with

the first byte of the size (after

55h/BBh) and ends with the last programme d byte of the E

valid if EECS in Hardware Configuration Byte 16 is set.

2

PROM. Only

HW Config. Byt e 16: Global Conf ig. Byte 2

Default = 0000000 0

D7 D6 D5 D4 D3 D2 D1 D0

res EEC S AUX1 R 3DEN DSPD1 PSH res res

This register sets the power up defaults for these features . Afte r powe r-up, X 18 may be used t o cont rol all

bits except EECS.

PSH Playback Sample Hold. W hen set, the

last sample is held in DAC1 when

PEN is cleared. When clear, zero is

sent to DAC1 when PEN is cleared .

DSPD1 DSP port controls DAC1. When set,

the serial DSP port controls DAC1 instead of the ISA playback FIFO.

3DEN 3D Sound Enable. When set, 3D

sound is enabled on L/ROUT.

AUX1R AUX1 Remap. When set, writes to

I18/19 (DAC2 volume) also control

the AUX1 volume. When clear,

I18/19 control DAC2 volume and

I2/3 control AUX1 volume. This bit

provides some backwards compat ibility when AUX1 analog inputs are

substituted for LINE analog inputs

which ar e no lon ger ava ilabl e.

EECS EEPROM Checksum. If set, indicates

that Hardware Configurat ion Byte 15

is a checksum for the entire

EEPROM (starting after 55h/BBh).

DS252PP2

23

Page 24

CrystalClear Low Cost ISA Audio System

TM

CS4235

HW Config. Byte 17: CDbase Addre ss Length,

Default = 00000100

D7 D6 D5 D4 D3 D2 D1 D0

CAL7 CAL6 CAL5 CAL4 CAL3 CAL2 CAL1 CAL0

CAL7-CAL0 CDbase Address Length. Determines

the address length decode for the

primary CDROM address, CDbase.

CDbase must be on the same paragraph boundry as the address lengh

decode.

00000001 00000010 00000100 00001000 00010000 00100000 01000000 10000000 xxx - all others, RESERVED

CDCS low for 1 byte

CDCS low for 2 bytes

CDCS low for 4 bytes

CDCS low for 8 bytes

CDCS low for 16 bytes

CDCS low for 32 bytes

CDCS low for 64 bytes

CDCS low for 128 bytes

Bytes 19 throu gh 21 map t he interrup t number to

the actual interrupt pins A - F. As shown in Table 2, the byte 20 default is 0xB9; therefore,

IRQ C, which is the lower nibble, maps to the

ISA interrupt 9. Likewise IRQ D, which is the

upper nibble, maps to the ISA interrupt 11

(0Bh).

Byte 22 maps the DMA channel number to the

actual DMA pins A and B. As shown in the table, the byte 22 default is 0x10; therefore,

DRQA/

DACKA is the lower nibble which maps

to the ISA DMA channel 0. Likewise

DRQB/

DACKB is the upper nibble which maps

to the ISA DMA channel 1.

Byte 23 maps DMA C and IRQ G. The lower

nibble maps DMA C and defaults to DMA 3.

The upper nibble supports a seventh IRQ,

IRQ G. The default is disabled (0), providing

backwards compatibi lity with o ther Cirrus Audio

parts. If IRQ G is connected to an ISA interrupt

(typically 10), the n this byte must be modified to

reflect the hardware connection.

Hostload Procedure

This procedure is provided for backwards compatibility with the CS4236. Since the E

2

PROM

allows all resource and firmware patch data to be

loaded at power-up, this procedure is typically

only used with motherboard devices that do not

include a n E

2

PROM. To download Pn P resou rce

data from the host to the part’s internal RAM,

use the followin g sequence:

1. Configure Control I/O base address,

CTRLbase, by one of two methods: regular

PnP cycle or Crystal Key method.

a. The host can use the regular PnP cycle to

program the C TRLbase, and then place the

chip in the wait_ for_key_state

b. If the Crystal Key method is us ed:

First, send the 32 -byte Crystal key to I/O

address port (AP).

Second, configure logical device 2 base

address, CTRLbase, by writing to AP

(15h, 02h, 47h , xxh, xxh, 33h, 01h, 79 h).

Note: The two xxh represen t the base_ address_high and base_address_low

respectively. The default is: 01h, 20h.

2. Write 57h (Jump to ROM) command to

CTRLbase+5.

3. Download t he PnP Resource dat a.

a. Send downlo ad command by writin g AAh

to CTRLbase +5.

b. Send starting download address (4000h)

by writing low byte (00h) first, and then

high byte (40 h) to CTRLbase+ 5.

c. Send the Hardware Configuration and re-

source data in successive bytes to

CTRLbase+5. This includes the Hardware

Configuration and the PnP resource data.

24

DS252PP2

Page 25

CrystalClear Low Cost ISA Audio System

TM

CS4235

The PnP resource format is described in

the PnP Data sect ion. The resource header

should not contain the first four bytes

which are only used for E

2

PROM loads.

d. End download by writing 00h to

CTRLbase+6.

4. Download Firmware data. Contact Cirrus

Logic for the BIOS kit which give s examples

of how to download firmware .

5. If any of the Hardware Configuration Data

(first 19 bytes) has changed, 5Ah must be

written to CTRLbase+5 to force the part to

internally up date this info rmation.

The new PnP data is loaded and the part is ready

for the next PnP cycle.

External E

2

PROM

The Plug and Play specification defines 32 bits

of the 72-bit Serial Identifier as being a user de-

2

fined serial number. The E

PROM is used to

change the user section of the identifier, store

default resource data for PnP, Hardware Configuration data specific to the CS4235, and

firmware patches to upgrade the core processor

functionality.

the address to zero. Then another start bit and

device address, followed by all the data. Since

the part us es the sequen tial read propert ies of the

2

E

PROM, only one E2PROM, is supported

(ganged E

Some E

2

PROMs are not support ed).

2

PROMs that are compatible with this

interface are:

Atmel AT24Cxx series

MicroChip 24LCxxB s eries

National NM24CxxL series

Ramtron FM24Cxx series

SGS Thompson ST24Cxx series

Xicor X24Cxx series

where the xx is replaced by 02, 04, 08, or 16

based on the size of the E

2

PROM desired. The

size of 08 (1k bytes) is preferred since it allows

the maximum flexibility for upgrading firmware

patches. Other E

2

PROMs compatible with Figure 3 and the timing parameters listed in the

front of the dat a sheet may also be used.

The maximum Hardware Configuration and PnP

resource RAM data supported is 384 bytes, and

a four byte header; therefore, the maximum

amount of data storage, without firmware

patches, in E

maximum size E

2

PROM would be 388 bytes. The

2

PROM needed is 770 bytes, to

allow the i nclusion of firmware patches after t he

PnP resource data.

2

The E

PROM interface uses an industry standard

2-wire interface consisting of a bi-directional

data line and a clock line driven from the part.

After power-on the part looks for the existence

of an E

2

PROM device and loads the user defined data. The existence is determined by the

first two bytes read (0x55 fo llowed by 0xBB). If

the first t wo bytes are corre ct, the part reads th e

next two bytes to determine the length of data in

the E

2

PROM. The length bytes indicate the

number of bytes left to be read (not including

the two validati on bytes or two length bytes). As

shown in Figure 3, the E

2

PROM is read using a

start bit follo wed by a dummy write, to initialize

DS252PP2

If an external E

2

PROM exists, it is accessed by

the serial interface and is connected to the SDA

and SCL pins. The two-wire in terface is controlled by three bits in the Control logical device,

Hardware Control Register (CTRLbase+1). The

serial data can be written to or read from the

2

E

PROM by sequentiall y writing or reading that

register. The three register bits, D0, D1, D2 are

labeled CLK, DOUT, and DIN/EEN respectively.

The DIN/EEN bit, when written to a one, enables the E

2

PROM serial interface. When the

DIN/EEN bit is written to a zero, the serial interface is disabled. The DIN/EEN bit is also the

Data In (DIN) signa l to read back data from the

2

E

PROM. The SDA pin is a bi-direction al open-

25

Page 26

CrystalClear Low Cost ISA Audio System

TM

CS4235

drain data line supporting DIN and DOUT;

therefore, to read the correct data, the DOUT bit

must be set to a one prior to performing a read

of the register. Otherwise, the data read back

from DIN/EEN will be all zeros. The E

2

PROM

data can then be read from the DIN/EEN bit.

The CLK bit timing is controlled by the host

software. This is the serial clock for the

2

E

PROM output on the SCL pin. The DOUT bit

is used to write/program the data out to the

2

E

PROM. An external pull-up resistor is required on SDA because it is an open-drain

output. Use the guidelines in the specific

2

E

PROM data sheet to select the value of the

pull-up resistor (a typical value would be

3.3 kΩ).

Programming the E

2

PROM:

1. Configure Control I/O base address by one

of two methods: regular PnP cycle or Crystal

Key method.

a. The hos t can use the regular Pn P cycle to

program the logical device 2 I/O base address, and then place the chip in the

wait_for_key_state

b. If the Crystal Ke y method is used:

First, write to the AP, send the 32-byte

Crystal key.

2. Refer to the specific data sheet for the

2

E

PROM you are using for timing requirements and data format. Also, refer to the

Loading Resource Data section of this data

sheet for the E

3. Send the E

2

PROM resource data format.

2

PROM data in successive bits to

CTRLbase+1 (Hardware Control Register)

while following the E

2

PROM data sheet for-

mat.

The E

2

PROM now contains the PnP resource

data. For this new data to take effect, the part

must be reset, causing the part to read the

2

E

PROM during initialization. Cirrus can pro-

vide a utility, RESOURCE.EXE, to program

2

E

PROMs through the Con trol logical device in-

terface.

WINDOWS SOUND SYSTEM CODEC

The WSS Codec software interface consists of

4 I/O locations starting at the Plug and Play ad-

dress ’WSSbase’, and supports 12-bit address

decoding. If the upper address bits, SA12-SA15

are used, they must be 0 to decode a valid address. The WSS Codec also requires one

interrupt and one or preferably two DMA channels, one for playback and one for capture. S ince

the WSS Codec and Sound Blaster device are

mutually exclusive, the two devices share the

same interrupt and DMA playback channel.

Crystal IC

EEPROM

26

Second, configure the Control I/O base

address by writing 15h, 02h, 47h, 01h,

20h, 33h, 01 h, 79h t o the AP.

Start

Part

Address

S

10100000A00000000AS

Write

Bank

Address

Figure 3. EE PROM F ormat

Start

Acknowledge Data

The WSS functions include stereo Analog-toDigital and Digital-to-Analog converters (ADCs

and DACs), analog mixing, anti-aliasing and reconstruction filters, line and microphone level

Part

Address

10100001

Read

Acknowledge

A

Data DataP1

A

No

Acknowledge

Stop

DS252PP2

Page 27

inputs, simu ltaneous capture and playbac k (at independent sampl e frequencies) and a parallel bus

interface.

Enhanced Functions (MODEs)

The initial state is labeled MODE 1 and forces

the part to appear as a CS4248. The more popular second mode, MODE 2, forces the part to

appear as a CS4231 super set and is compatible

with the CS4232. To switch from MODE 1 to

MODE 2, the CMS1,0 bits, in the MODE and

ID register (I12), should be set to 10 respectively. When MODE 2 is selecte d, the bit IA4 in

the Index Address register (R0) will be decoded

as a valid index pointer providing 16 additional

registers and increased functionality over the

CS4248.

To r everse the procedure, set the CMS1,0 bits to

00 and the part will resume operation in

MODE 1. Except for the Capture Data Format

(I28), Capture Base Count (I30/31), and Alternate Feature Status (I24) registers, all other

Mode 2 functions retain their values when returning to Mode 1.

CrystalClear Low Cost ISA Audio System

TM

CS4235

FIFOs

The WSS Codec contains 16-sample FIFOs in

both the playback and capture digital audio data

paths. The FIFOs are transparent and have no

programming as sociated wit h them.

When playback is enabled, the playback FIFO

continually requests data until the FIFO is full,

and then makes requests as positions inside the

FIFO are emptie d, thereby keeping the playback

FIFO as full as possible. Thus when the system

cannot respond with in a sample period, the FIFO

starts to empty, avoiding a momentary loss of

audio data. If the FIFO runs out of data, the last

valid sample can be continuously output to the

DACs (if DACZ in I16 is clear) which will

eliminate pops from occu rring.

When capture is enabled, the capture FIFO tries

to continually stay empty by making requests

every sample period. Thus when t he system cannot respond within a sample period, the capture

FIFO starts filling, thereby avoiding a loss of

data in the audi o data stream.

MODE 3 is selected by setting CMS1,0 to 11.

MODE 3 allows access to a third set of "extended registers" which are designated X0-X31.

The extended registers are accessed throu gh I23.

The additional MODE 3 functions are:

1. A full symmetrical mixer. This changes the in put multiplexe r to a input mix er.

2. Indep endent sample freque ncy control on t he

ADCs and DACs.

3. Programmable Gain and Att enuation o n the

Microphone inp uts.

DS252PP2

WSS Codec PIO Regist er Interface

Four I/O mapped locations are available for accessing the Codec functions and mixer. The

control registers allow access to status, audio

data, and all indirect registers via the index registers. The

IOR and IOW signals are used to

define the read and write cycles respectively. A

PIO access to the Codec begins when the host

puts an address on to th e ISA b us which matches

WSSbase and drives AEN low. WSSbase is programmed during a Plug and Play configuration

sequence. Once a valid base address has been

decoded t hen the as sertion of

IOR will caus e the

WSS Codec to drive data on the ISA data bus

lines. Write cycl es require the ho st to assert data

on the ISA data bus lines and strobe the

IOW

signal. The WSS Codec will latch data into the

PIO register on the rising edge of the

IOW

strobe.

27

Page 28

CrystalClear Low Cost ISA Audio System

TM

CS4235

The audio data interface typically uses DMA request/grant pins to transfer the digital audio data

between the WSS Codec and the bus. The WSS

Codec is responsible for asserting a request sig-

nal whenever the Codec’s internal buffers need

updating. The bus responds wit h an acknowl edge

signal and strobes data to and from the Codec,

8 bits at a time. The WSS Codec keeps the request pin active until the appropriate number of

8-bit cycles have occurred to transfer one audio