Page 1

Semiconductor Corporation

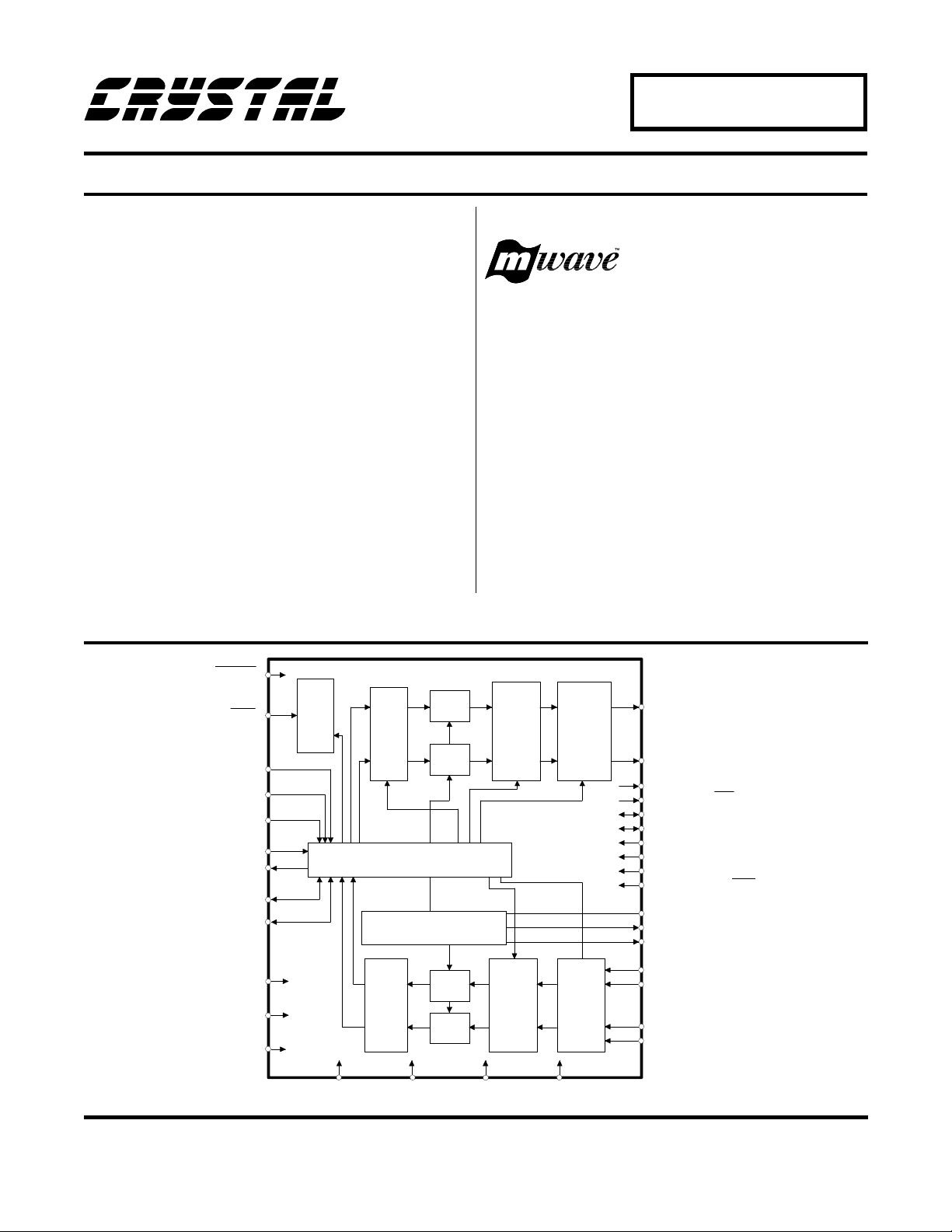

16-Bit Stereo Audio Codec

CS4216

Features

CMOS Stereo Audio Input/Output System

••

Delta-Sigma A/D Converters

Delta-Sigma D/A Converters

Input Anti-Alias ing and Output

Smoothing Filters

Programmable Input Gain and

Output Attenu ation

Sample Frequencies of 4 kHz to 50 kHz

••

CD Quality Noise and Distortion

••

< 0.01 %THD

Internal 64X Oversampling

••

Low Power Dissipation: 80 mA

••

1 mA Power-Down Mode

General Description

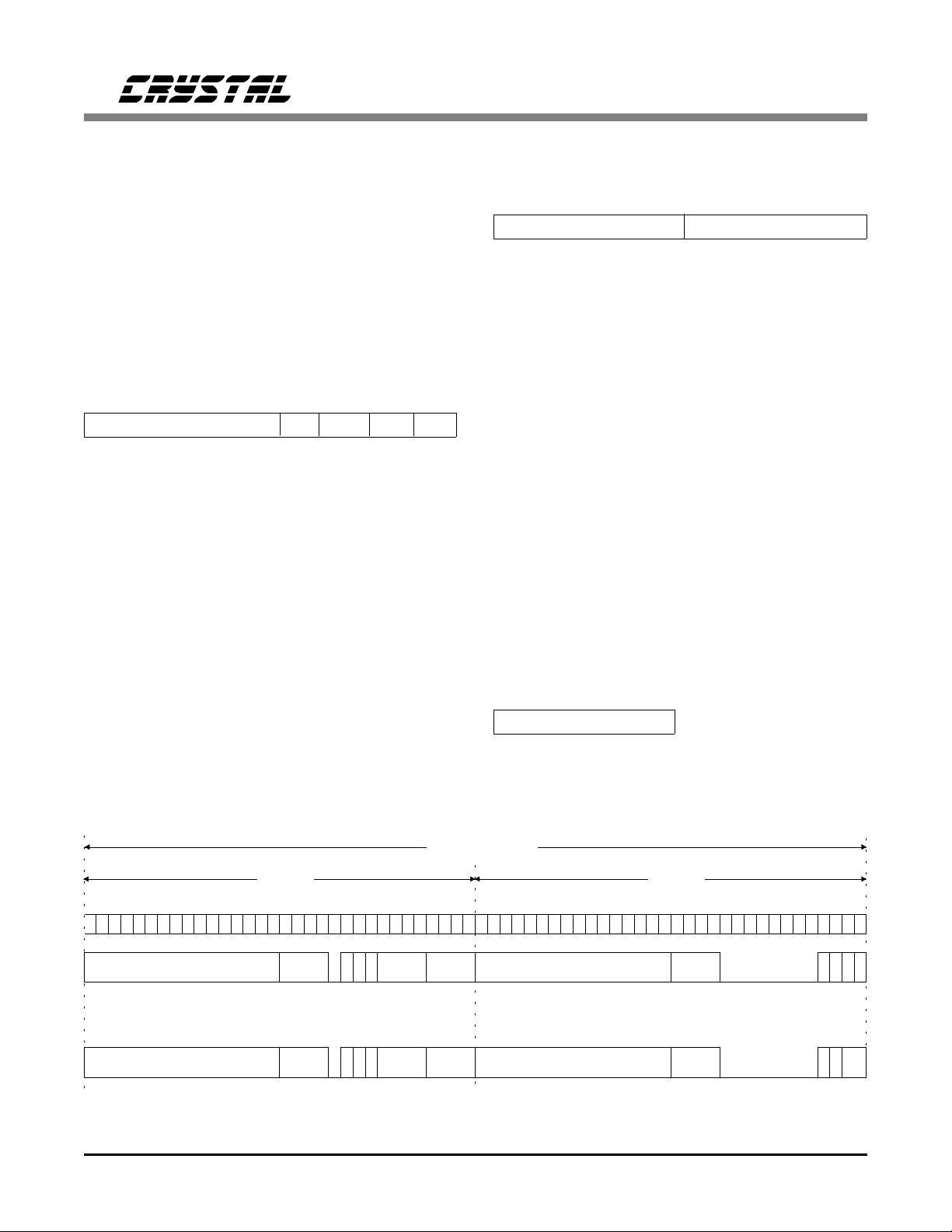

The CS4216 is an Mwave

audio codec.

The CS4216 Stereo Audio Codec is a monolithic

CMOS device for computer multimedia, automotive,

and portable audio applications. It performs A/D and

D/A conversion, filtering, and level setting, creating 4

audio inputs and 2 audio outputs for a digital computer

system. The digital interfaces of left and right channels

are multiplexed into a single serial data bus with word

rates up to 50 kHz per channel. Up to 4 CS4216 devices can be attached to a single hardware bus.

Both the ADCs and the DACs use delta-sigma modulation with 64X oversampling. The ADCs include a digital

decimation filter which eliminates the need for external

anti-aliasing filters. The DACs include output smoothing

filters on-chip.

Ordering Information:

CS4216-KL 0° to 70°C 44-pin PLCC

CS4216-KQ 0° to 70°C 44-pin TQFP

CDB4216 Evaluation Board

TM

RESET

PDN

SMO DE3

SMO DE2

SMO DE1

SDIN

SDOUT

SCLK

SSYNC

MF7:SFS1/F2

MF8:SFS2/F3

CLKIN

D/A

POWER

CONTROL

SERIAL INTERFACE CONTRO L

VD

DIGITAL

FILTERS

D/A

VOLTAG E R EFER ENC E

A/D

DIGITAL

FILTERS

A/D

VA

DGND AGND

OUTPUT

INPUT

GAIN

ATTENUATION

OUTPUT

LOU T

MUTE

ROUT

DO1

MF5:DO2/IN T

MF2:DO3/F2/CDIN

MF1:DO4/F1/CDOUT

DI1

MF6:DI2/F1

MF 3:DI3/F3/CCL K

MF4:DI4/MA/CCS

REFGND

REFBYP

REFBUF

LIN1

LIN2

INPUT

MUX

RIN1

RIN2

Crystal Semiconductor Corporation

P.O. Box 17847, Austin, TX 78760

(512) 445-7222 FAX: (512) 445-7581

Copyright Crystal Semicondutor Corporation 1993

(All Rights Reserved)

Oct ’93

DS83F2

1

Page 2

CS4216

RECOMMENDED OPERATING CONDITIONS (AGND, DGND = 0V, all voltages with re-

spect to 0V.)

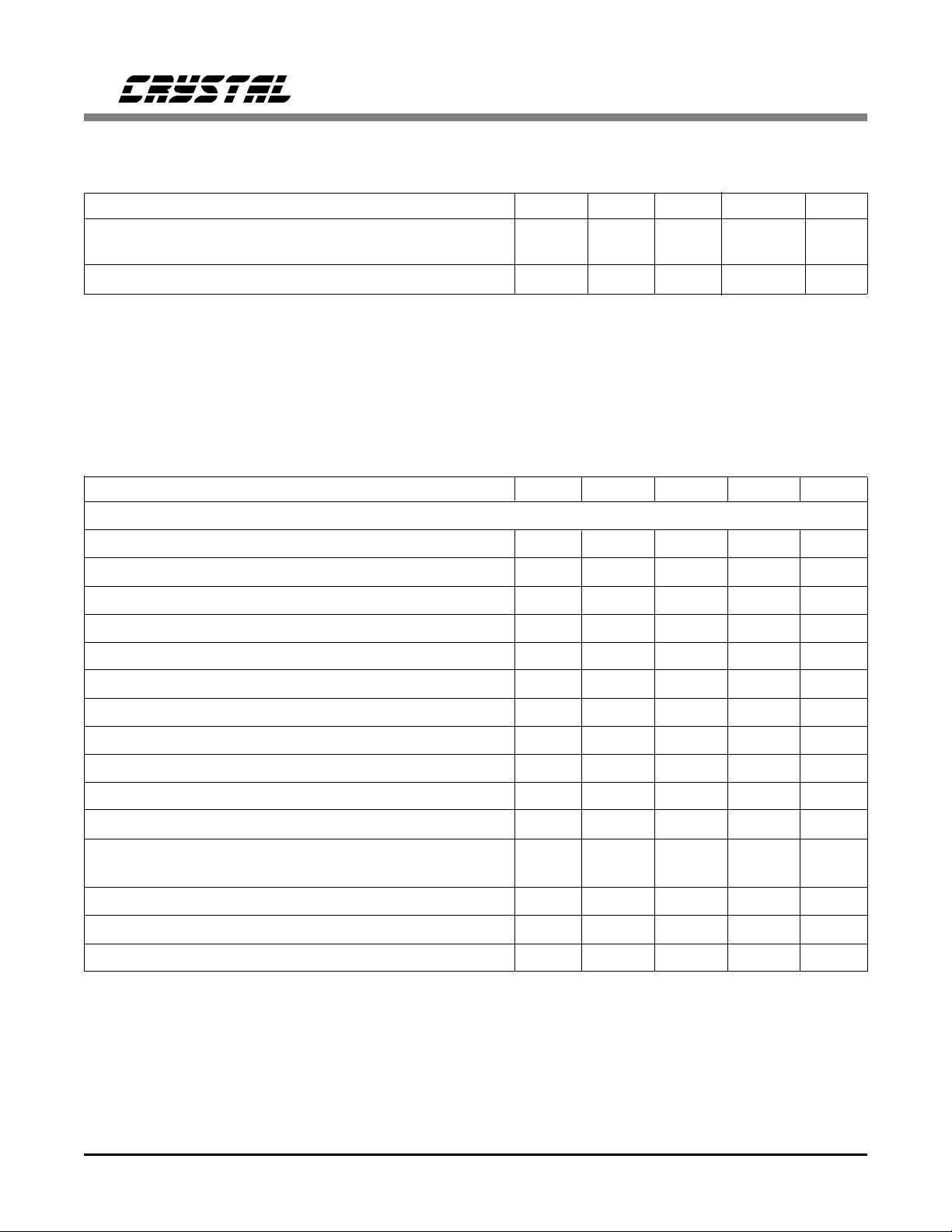

Parameter Symbol Min Typ Max Units

Power Supplies: Digital VD 4.75 5.0 5.25 V

Analog VA 4.75 5.0 5.25 V

Operating Ambient Temperature T

ANALOG CHARACTERISTICS( T

Logic 1 = VD; 1 kHz Input Sine Wave; CLKIN = 24.576 MHz; SM1; Conversion Rate = 48 kHz; SCLK =

12.288 MHz; Measurement Bandwidth is 10 Hz to 20 kHz; Unless otherwise specified.)

Parameter * Symbol Min Typ Max Units

Analog Input Characteristics

ADC Resolution 16 - - Bits

ADC Differential Nonlinearity (Note 1) - - ±0.9 LSB

Instantaneous Dynamic Range IDR 80 85 - dB

Total Harmonic Distortion THD - - 0.01 %

Interchannel Isolation - 80 - dB

Interchannel Gain Mismatch - - ±0.5 dB

Frequency Response (Note 1) -0.5 - +0.2 dB

- Minimum gain setting (0 dB); unless otherwise specified.

= 25°C; VA, VD = +5V; Input Levels: Logic 0 = 0V,

A

A

02570°C

Programmable Input Gain Span 21 22.5 24 dB

Gain Step Size - 1.5 - dB

Absolute Gain Step Error - - 0.75 dB

Gain Drift - 100 - ppm/°C

Offset Error DC Coupled Inputs - ±10 ±100 LSB

AC Coupled Inputs - ±150 ±400 LSB

Full Scale Input Voltage 2.5 2.8 3.1 V

Input Resistance (Notes 1,2) 20 - - kΩ

Input Capacitance (Note 1) - - 15 pF

Notes: 1. This specification is guaranteed by characterization, not production tes ting.

2. Input resistance is for the input selec ted. Non-selected inputs have a very high (>1M Ω) input resistanc e.

* Parameter definitions are given at the end of this data sheet.

MwaveTM is a trademark of the IBM Corporation.

Specifications are subject to change without notice.

2 DS83F2

pp

Page 3

ANALOG CHARACTERISTICS (Continued)

Parameter * Symbol Min Typ Max Units

CS4216

Analog Output Characteristics

DAC Resolution 16 - - Bits

DAC Differential Nonlinearity (Note 1) - - ±0.9 LSB

Total Dynamic Range TDR - 93 - dB

Instantaneous Dynamic Range IDR 80 83 - dB

Total Harmonic Distortion (Note 4) THD - - 0.02 %

Interchannel Isolation (Note 4) - 80 - dB

Interchannel Gain Mismatch - - ±0.5 dB

Frequency Response (Note 1) -0.5 - +0.2 dB

Programmable Output Attenuation Span (Note 3) -45 -46.5 - dB

Attenuation Step Size (Note 3) - 1.5 - dB

Absolute Attenuation Step Error (Note 3) - - 0.75 dB

Gain Drift - 100 - ppm/°C

REFBUF Output Voltage (Note 5) 1.9 2.2 2.5 V

Offset Voltage - 10 - mV

Full Scale Output Voltage (Note 4) 2.5 2.8 3.1 V

Deviation from Linear Phase (Note 1) - - 1 Degree

- Minimum Attenuation; Unless Otherwise Specified.

Maximum output current= 400 µA

pp

Out of Band Energy (22 kHz to 100 kHz) - -60 - dB

Power Supply

Power Supply Current (Note 6) Operating - 80 100 mA

Power Down - - 1 mA

Power Supply Rejection (1 kHz) - 40 - dB

Notes: 3. Tested in SM3, Slave sub-mode, 128 BPF.

4. 10 kΩ, 100 pF load.

5. REFBUF load current must be DC. To drive dynamic loads, REFBUF must be buffered.

AC variations in REFBUF current may degrade ADC and DAC performance.

6. Typically current: VA = 30mA, VD = 50mA. Power supply current does not include output loading.

* Parameter definitions are given at the end of this data sheet.

DS83F2 3

Page 4

CS4216

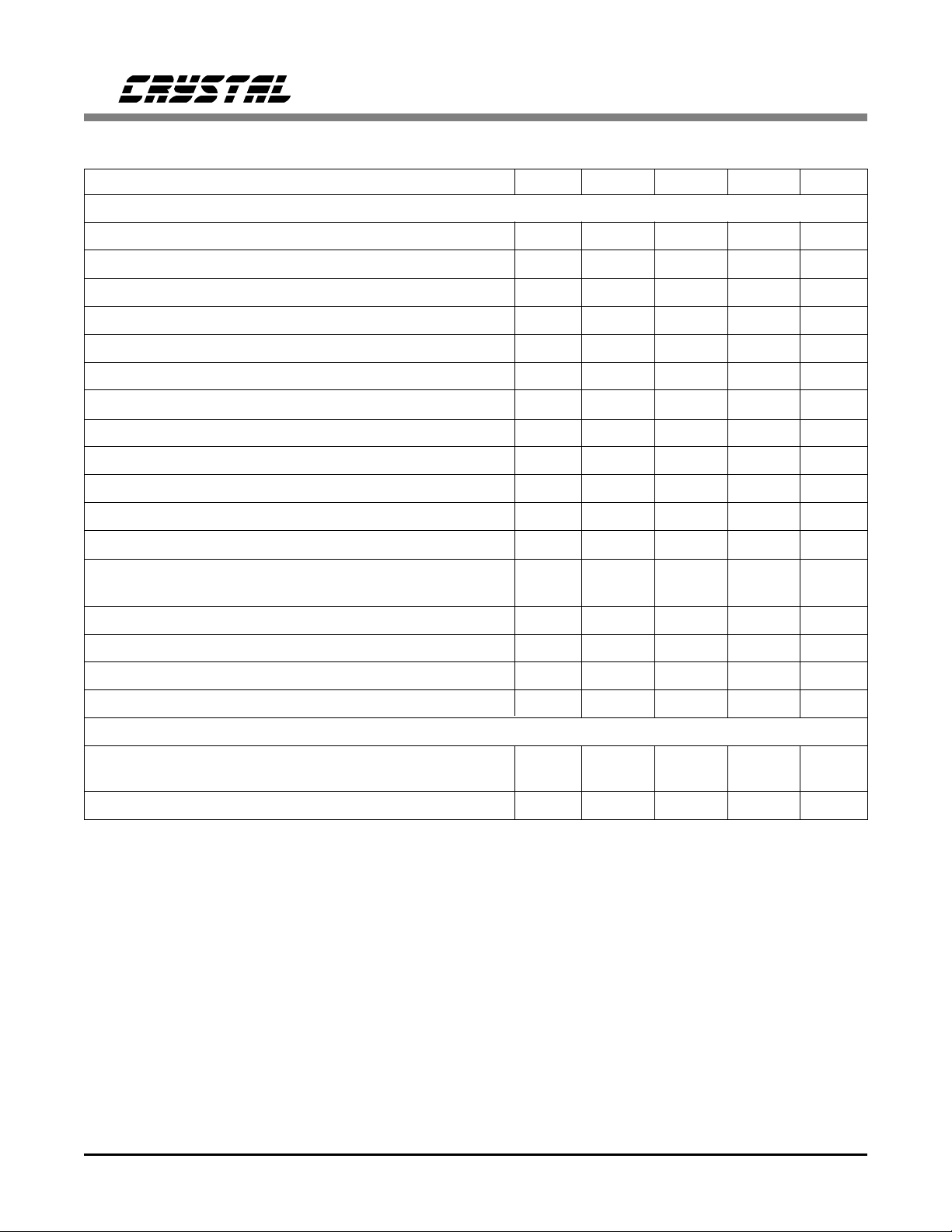

SWITCHING CHARACTERISTICS (T

Levels: Logic 0 = 0V, Logic 1 = VD)

Parameter Symbol Min Typ Max Units

Input clock (CLKIN) frequency SM1: CLKIN 2.048 24.576 25.6 MHz

SM2, SM3, SM4: CLKIN 1.024 12.288 12.8 MHz

CLKIN low time t

CLKIN high time t

Sample Rate (Note 1) Fs 4 - 50 kHz

DI pins setup time to SCLK edge (Note 1) t

DI pins hold time from SCLK edge (Note 1) t

DO pins delay from SCLK edge t

SCLK and SSYNC output delay

from CLKIN rising

SCLK period Master Mode (Note 7) t

SCLK high time Slave Mode t

SCLK low time Slave Mode t

SDIN, SSYNC setup time to SCLK edge Slave Mode t

SDIN, SSYNC hold time from SCLK edge Slave Mode t

SDOUT delay from SCLK edge t

Output to Hi-Z state bit 64 (Note 1) t

Output to non-Hi-Z bit 1 (Note 1) t

RESET pulse width low 500 - - ns

Master Mode (Note 1) t

= 25°C; VA, VD = +5V, outputs loaded with 30 pF; Input

A

ckl

ckh

s2

h2

pd2

pd3

sckw - 1/(Fs*bpf) - s

Slave Mode

sckh

sckl

s1

h1

pd1

hz

nz

15 - - ns

15 - - ns

10 - - ns

8--ns

30 - - ns

- - 50 ns

75 - - ns

30 - - ns

30 - - ns

15 - - ns

10 - - ns

- - 28 ns

- - 12 ns

15 - - ns

CCS low to CCLK rising SM4 (Note 1) t

CDIN setup to CCLK falling SM4 (Note 1) t

CCLK low to CDIN invalid (hold time) SM4 (Note 1) t

CCLK high time SM4 (Note 1) t

CCLK low time SM4 (Note 1) t

CCLK Period SM4 (Note 1) t

CCLK rising to CDOUT data valid SM4 (Note 1) t

CCLK rising to CDOUT Hi-Z SM4 (Note 1) t

CCLK falling to CCS high SM4 (Note 1) t

Notes: 7. When the CS4216 is in master mode (SSYNC and SCLK outputs), the SCLK duty cycle is 50%.

The equation is based on the selected sample frequency (Fs) and the number of bits per frame (bpf) .

4 DS83F2

cslcc

discc

ccdih

cclhh

cclhl

cclkw

ccdov

ccdot

cccsh

25 - - ns

15 - - ns

10 - - ns

25 - - ns

25 - - ns

75 - - ns

- - 30 ns

- - 30 ns

0--ns

Page 5

CS4216

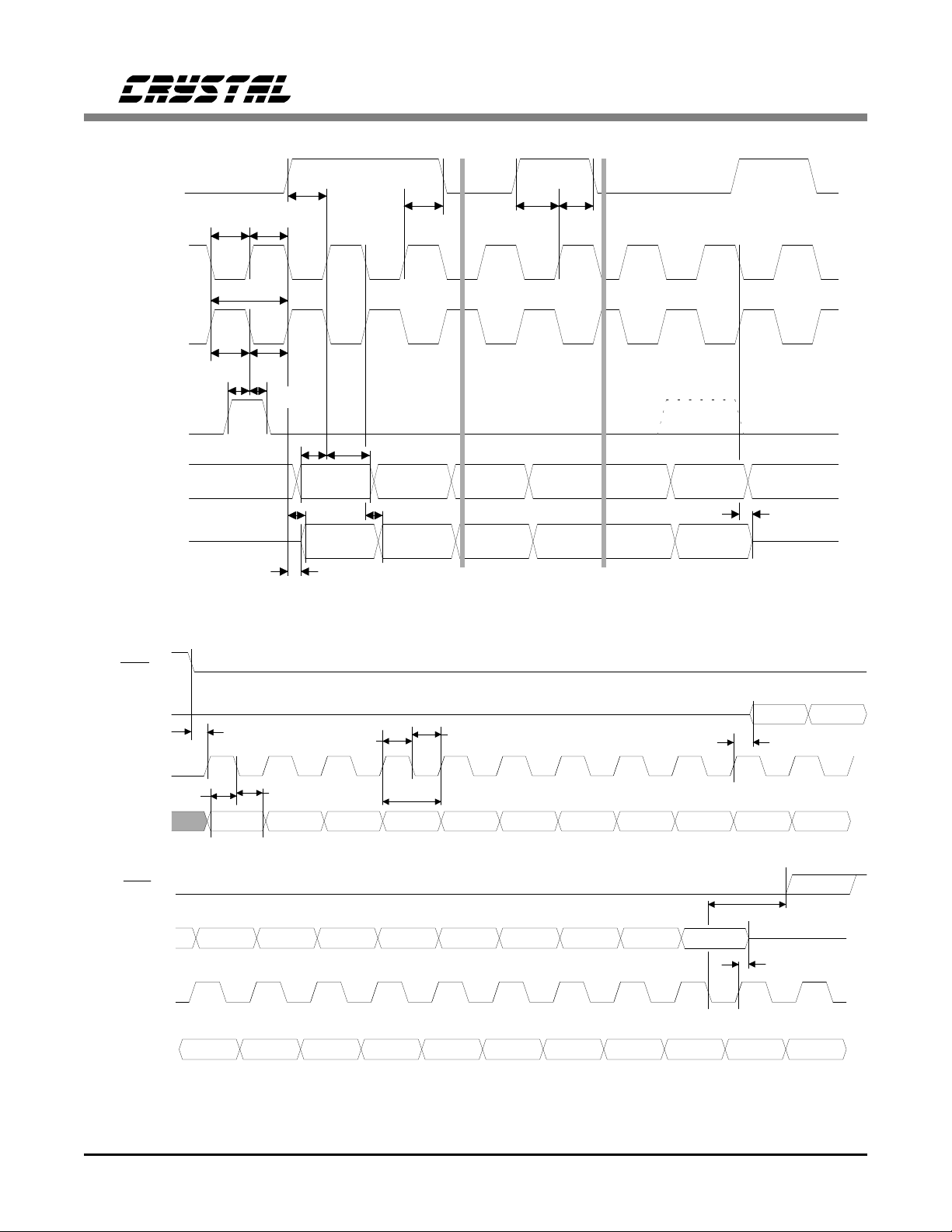

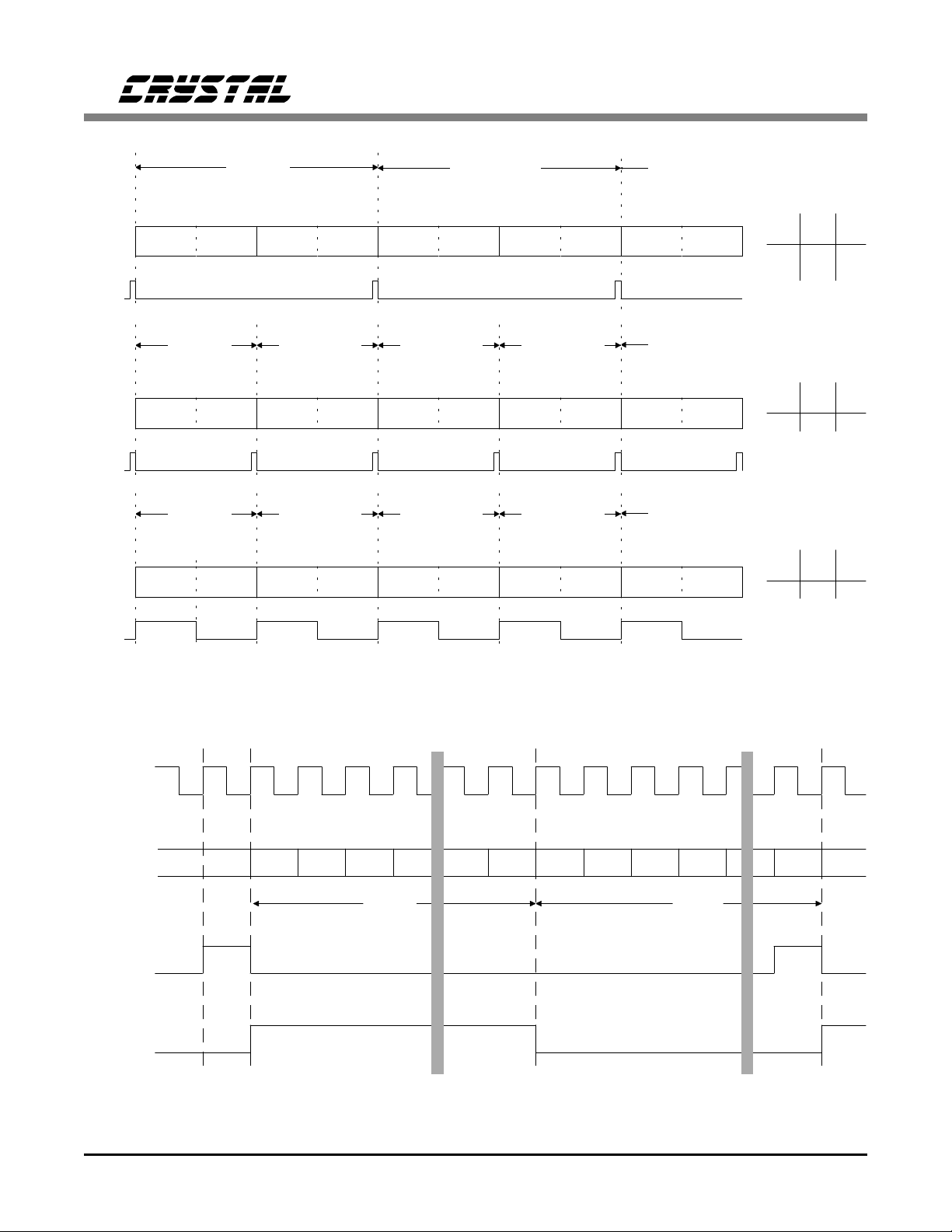

SSYNC

[SM1, SM2\

SCLK

[SM1,SM2\

SCLK

[SM3,SM4\

SSYNC

[SM3,SM4\

SDIN

SDOUT

t

sckltsckh

t

sckw

t

sckhtsckl

t

s1

[SM1,SM2,SM3\

(SM4)

[SM1,SM2,SM3\

(SM4)

Bit 32

(Bit 32)

Bit 32

(Bit 32)

*Word Sync

t

s1th1

Bit 33

(Bit 1)

Bit 33

(Bit 1)

Bit 63

(Bit 31)

Bit 63

(Bit 31)

(Bit 32)

Frame Sync

t

s1

t

h1

t

h1

t

t

h1

s1

Bit 1 Bit 2

t

pd1

Bit 1

t

nz

t

pd1

Bit 2

* Optional

Bit 64

Bit 64

(Bit 32)

*Word Sync

t

hz

MF4:CCS

MF1:CDOUT

MF3:CCLK

t

MF2:CDIN

MF4:CCS

MF1:CDOUT

MF3:CCLK

MF2:CDIN

discc

RGain2

Serial Audio Port Timing

ccdov

t

cccsh

0

LCL

11

ADV

t

cslcc

t

ccdih

t

cclkh

0MSK

DO1

LAtt4

t

cclkl

t

cclkw

LAtt3 LAtt2

LAtt1

LAtt0

t

RAtt4 RAtt3 RAtt2

123 5 89467 10

0

DI1

ADV

0

0000

t

ccdot

0

0

RGain1

1

RGain0

Err1

Err0

LCL RCL

0

24 28 29 3231302726252322

Serial Mode 4. Control Data Serial Port Timing

DS83F2 5

Page 6

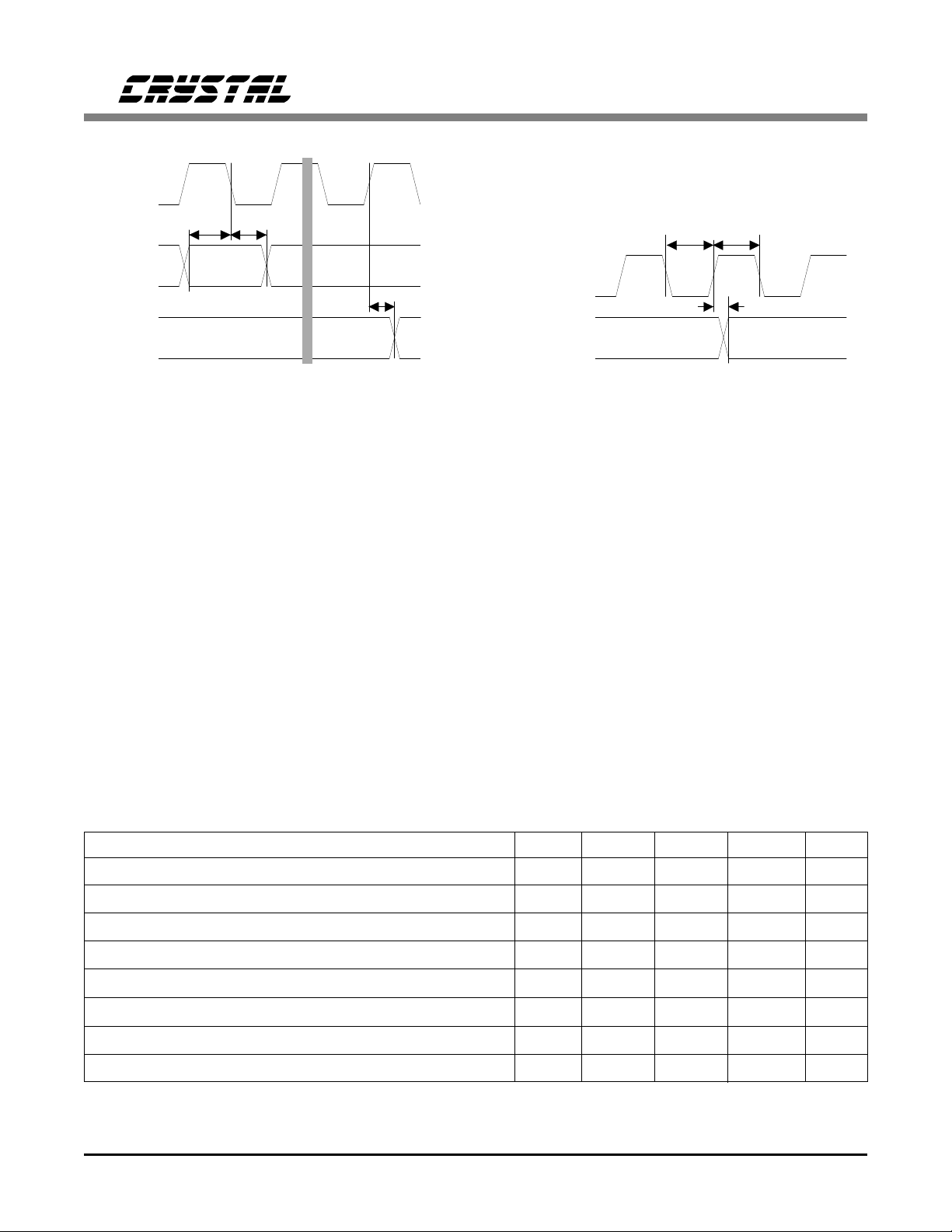

SCLK*

t

s2

t

h2

t

ckl

CS4216

t

ckh

DIx

DOx

* SCLK is inverted for SM1 and SM2

DI/DO Timing

t

pd2

CLKIN

SCLK

SSYNC

(Master Mode)

SCLK & SSYNC Output Timing

t

pd3

(Master Mode)

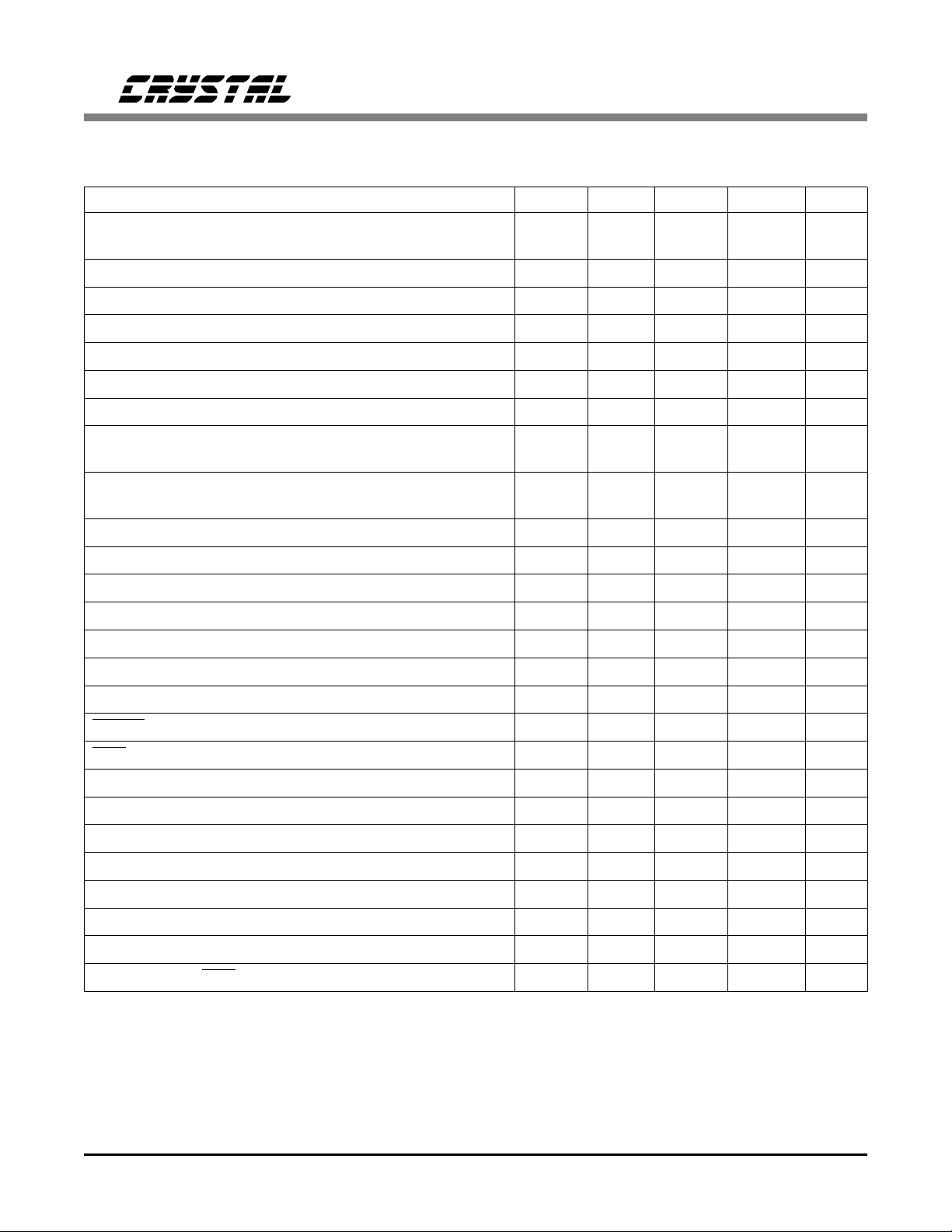

DIGITAL CHARACTERISTICS (T

Parameter Symbol Min Typ Max Units

High-level Input Voltage V

Low-level Input Voltage V

High-level Output Voltage at I0 = -2.0 mA V

Low-level Output Voltage at I0 = +2.0 mA V

Input Leakage Current (Digital Inputs) - - 10 µA

Output Leakage Current (High-Z Digital Outputs) - - 10 µA

Output Capacitance C

Input Capacitance C

6 DS83F2

= 25°C; VA, VD = 5V)

A

OH

OL

OUT

IH

IL

IN

VD-1.0 - - V

--1.0V

VD-0.3 - - V

--0.1V

- - 15 pF

- - 15 pF

Page 7

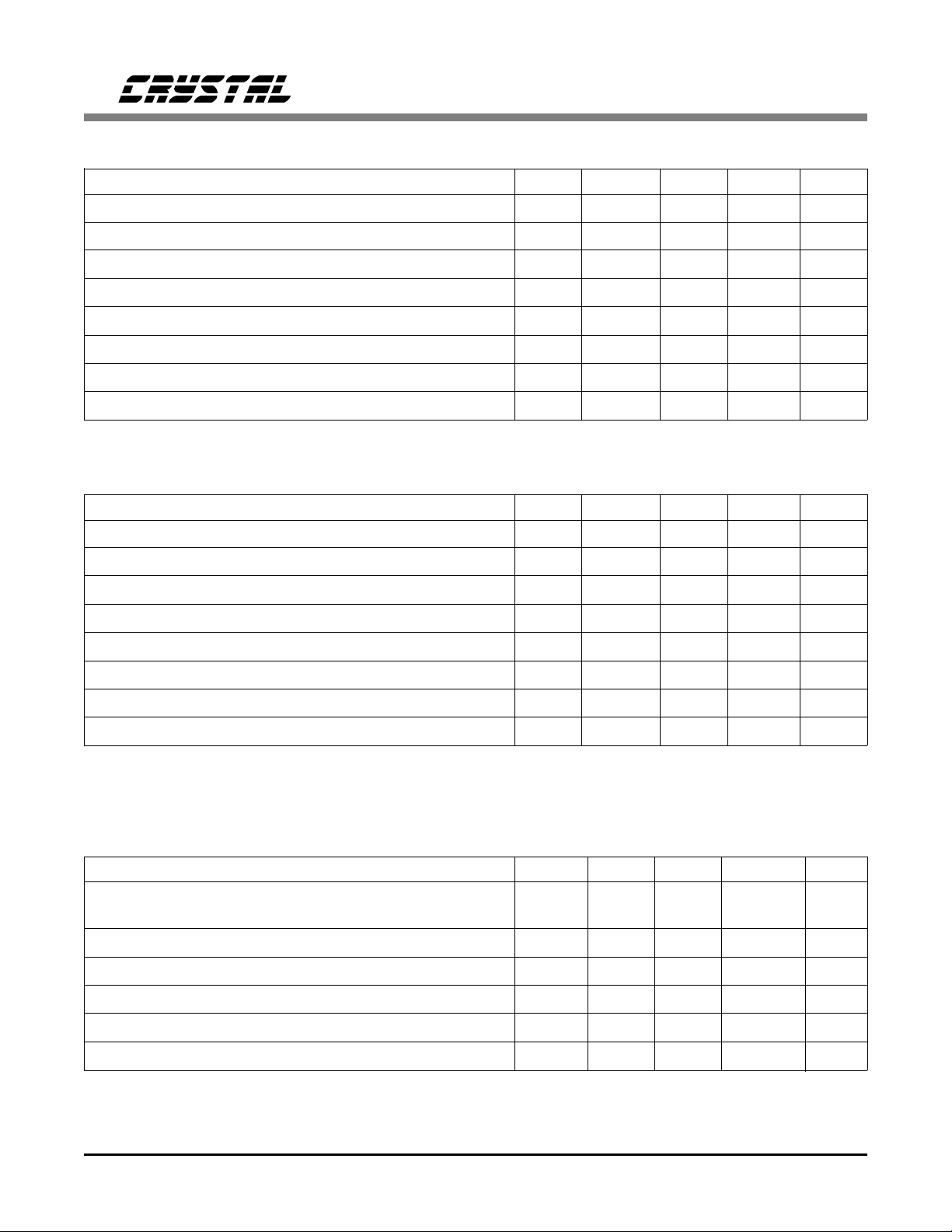

CS4216

A/D Decimation Filter Characteristics

Parameter Symbol Min Typ Max Units

Passband (Fs is conversion freq.) 0 - 0.45Fs Hz

Frequency Response -0.5 - +0.2 dB

Passband Ripple - - ±0.2 dB

Transition Band 0.45Fs - 0.55Fs Hz

Stop Band ≥ 0.55Fs - - Hz

Stop Band Rejection 80 - - dB

Group Delay - 16/Fs - s

Group Delay Variation vs. Frequency - 0.0 µs

D/A Interpolation Filter Characteristics

Parameter Symbol Min Typ Max Units

Passband (Fs is conversion freq.) 0 - 0.45Fs Hz

Frequency Response -0.5 - +0.2 dB

Passband Ripple - - ±0.1 dB

Transition Band 0.45Fs - 0.55Fs Hz

Stop Band ≥ 0.55Fs - - Hz

Stop Band Rejection 74 - - dB

Group Delay - 16/Fs - s

Group Delay Variation vs. Frequency - - 0.1/Fs µs

ABSOLUTE MAXIMUM RATINGS (AGND, DGND = 0V, all voltages with respect to 0V.)

Parameter Symbol Min Typ Max Units

Power Supplies: Digital VD -0.3 - 6.0 V

Analog VA -0.3 - 6.0 V

Input Current (Except Supply Pins) - - ±10.0 mA

Analog Input Voltage -0.3 - VA+0.3 V

Digital Input Voltage -0.3 - VD+0.3 V

Ambient Temperature (Power Applied) -55 - +125 °C

Storage Temperature -65 - +150 °C

Warning: Operation beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

DS83F2 7

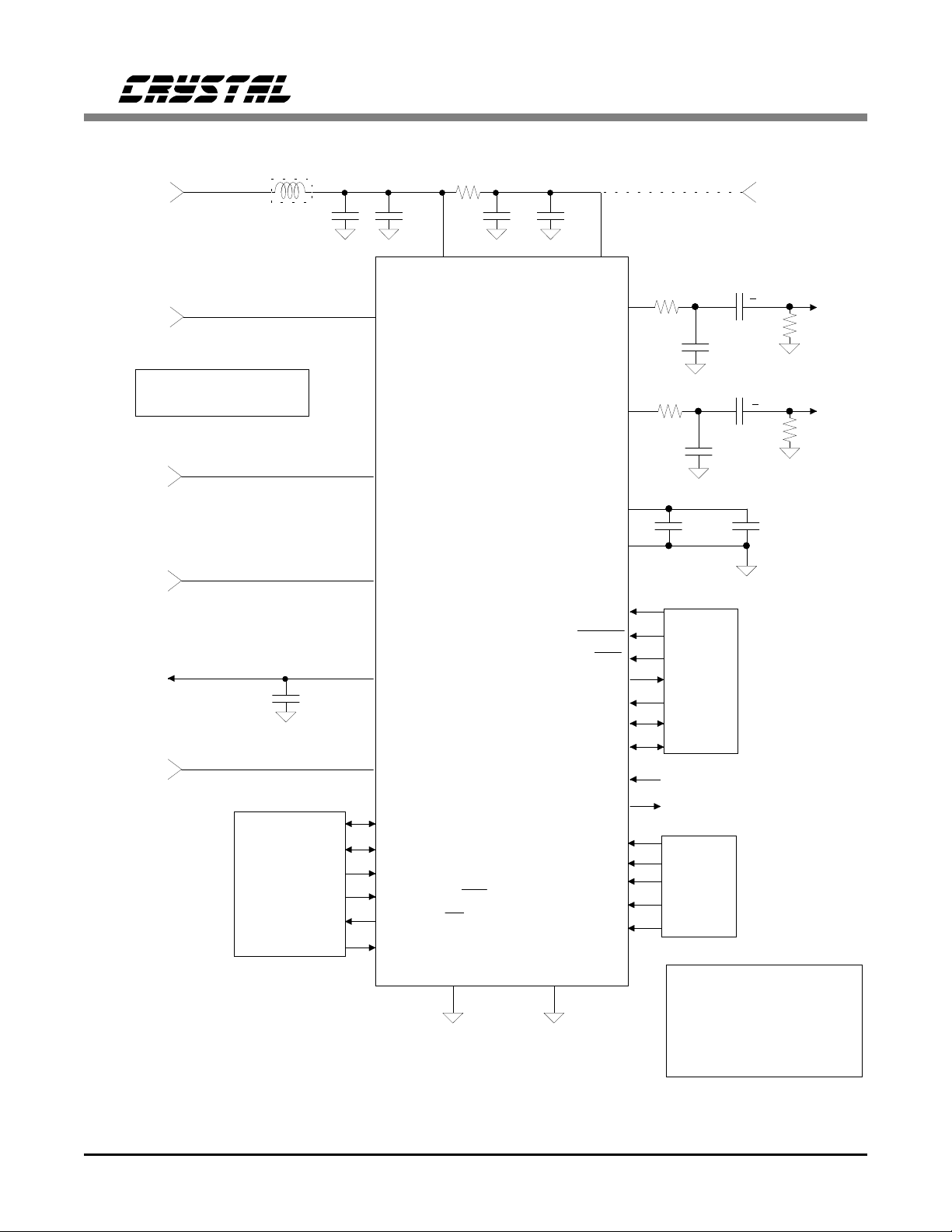

Page 8

CS4216

+5V

Supply

Line In 2

Right

See

for su ggested input ciruits.

Line In 2

Left

Line In 1

Right

To Optional

Inp ut B u ffe rs

Line In 1

Left

Analog Inputs

Fe rrite B ea d

section

0.47µF

P a r a lle l Bits

or

Sub-Mode

Settings

or

C o n tro l P o rt

2.0

1 µF

+

0.1 µF

4

26

RIN2

28

LIN2

25

RIN1

20

REFBUF

27

LIN1

40

MF1:DO4/F1/CDOUT

39

MF2:DO3/F2/CDIN

35

MF3:DI3/F3/CCLK

36

MF4:DI4/MA/CCS

38

MF5:DO2/INT

34

MF6:DI2/F1

+

CS4216

1 µF

F

0.1

µ

24

VAVD

ROUT

LOU T

REFBYP

REFGND

CLKIN

RESET

PDN

SDOUT

SDIN

SCLK

SSYNC

SMODE3

SMODE2

SMODE1

MF7:SFS1

MF8:SFS2

If a separate +5V

Analog supply is used, rem ove

the 2.0 ohm resistor

15

600

0.0022µF

16

600

0.0022

21

22

3

2

13

43

42

44

1

33

37

41

32

29

31

30

0.1 µF

C o ntro lle r

DI1

DO1

Mode

Setting

+

NPO

+

NPO

+5V

Analog

>

1.0 µF

40 k

> 1.0 µF

40 k

F

µ

+

10 µF

Right

Audio

Output

Left

Audio

Output

AGND D GND

23 5

Note: AG N D and DG N D pins MUST be on the same gro und plane

R e fe r to th e

section for terminating

unused line inputs.

All other unused inputs

shou ld b e ti e d to GN D. All N C

pins should be left floating.

Analog Inputs

Figure 1. Typical Connection Diagram

8 DS83F2

Page 9

OVERVIEW

CS4216

The CS4216 contains two analog-to-digital converters, two digital-to-analog converters,

adjustable input gain, and adjustable output level

control. Since the converters contain all the required filters in digital or sampled analog form,

the filters’ frequency responses track the sample

rate of the CS4216. Only a single-pole RC filter

is required on the analog inputs and outputs. The

RC filter acts as a charge reserve for the

switched-capacitor input and buffers op-amps

from a switched-capacitor load. Communication

with the CS4216 is via a serial port, with separate pins for data into the device, and data from

the device. The filters and converters operate

over a sample rate range of 4 kHz to 50 kHz.

FUNCTIONAL SPECIFICATIONS

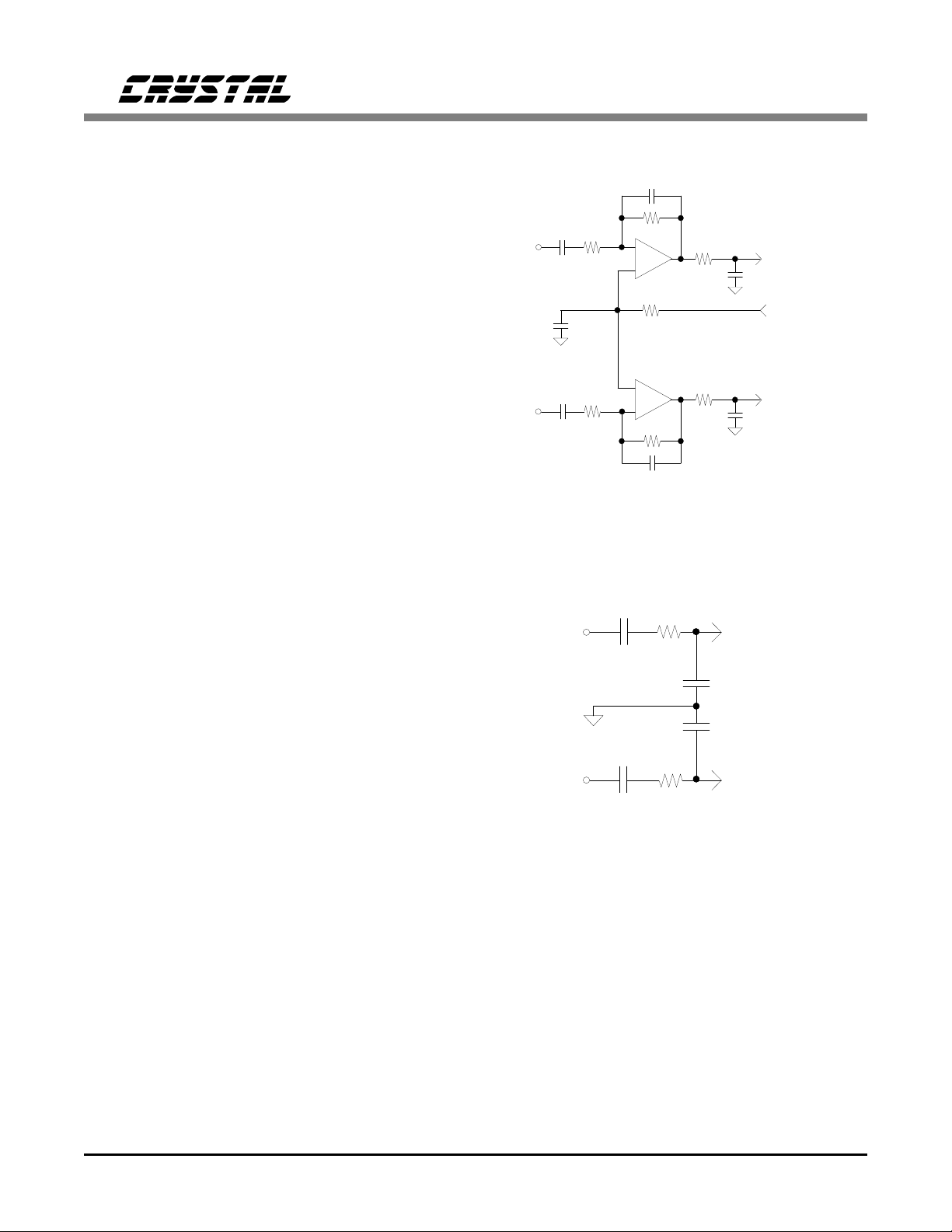

Analog Inputs and Outputs

Figure 1 illustrates the suggested connection diagram to obtain full performance from the

CS4216. The line level inputs, LIN1 or LIN2

and RIN1 or RIN2, are selected by an internal

input multiplexer. This multiplexer is a source

selector and is not designed for switching between inputs at the sample rate.

Unused analog inputs that are not selected have

a very high input impedance, so they may be

tied to AGND directly. Unused analog inputs

that are selected should be tied to AGND

through a 0.1 µF capacitor. This prevents any

DC current flow.

The analog inputs are single-ended and internally biased to the REFBUF voltage (nominally

2.2 V). The REFBUF output pin can be used to

level shift an input signal centered around

0 Volts as shown in Figure 2. The input buffers

shown have a gain of 0.5, yielding a full scale

input sensitivity of 2 V

with the CS4216 pro-

rms

56 pF

Line In

Right

Example

Op-Amps

are

MC34072

or

LT1013

Line In

Left

20 k0.47 uF

0.47 uF

0.47 uF 20 k

Op-amps are run

from VA+5V and

AGND

10 k

_

+

5 k

_

+

10 k

56 pF

150

0.01 uF

NPO

150

0.01 uF

NPO

RINx

(PLCC pin 25 or 26)

REFBUF

LINx

(PLCC pin 27 or 28)

Figure 2. DC Coupled Input.

0.47 uF

Line In

Right

Line In

Left

150

0.01 uF

NPO

NPO

0.01 uF

150

0.47 uF

RINx

(PLCC pin 25 or 26)

LINx

(PLCC pin 27 or 28)

Figure 3. AC Coupled Input

grammable gain set to 0. If the source impedance is very low, then the inputs can be AC

coupled with a series 0.47 µF capacitor, eliminating the need for external op-amps (see Figure

3). However, the use of AC coupling capacitors

will increase DC offset at 0dB gain (see Analog

Characteristics Table).

The analog outputs are also single-ended and

centered around the REFBUF pin. AC coupling

capacitors of >1 µF are recommended.

DS83F2 9

Page 10

CS4216

Offset Calibration

Both input and output offset voltages are minimized by internal calibration. Offset calibration

occurs after exiting a reset or power down condition. During calibration, which takes 194 frames,

output data from the ADCs will be all zeros, and

will be flagged as invalid. Also, the DAC outputs

will be muted. After power down mode or power

up, RESET should be held low for a minimum

of 50 ms to allow the voltage reference to settle.

Input Gain and Output Level Settin g

Input gain is adjustable from 0 dB to +22.5 dB

in 1.5 dB steps. In serial modes SM1 and SM2,

the output level attenuation is adjustable from

0 dB to -22.5 dB. In serial modes SM3 and

SM4, the output level attenuation is adjustable

from 0 dB to -46.5 dB. Both input and output

gain adjustments are internally made on zerocrossings of the analog signal, to minimize

"zipper" noise. The gain change automatically

takes effect if a zero crossing does not occur

within 512 frames.

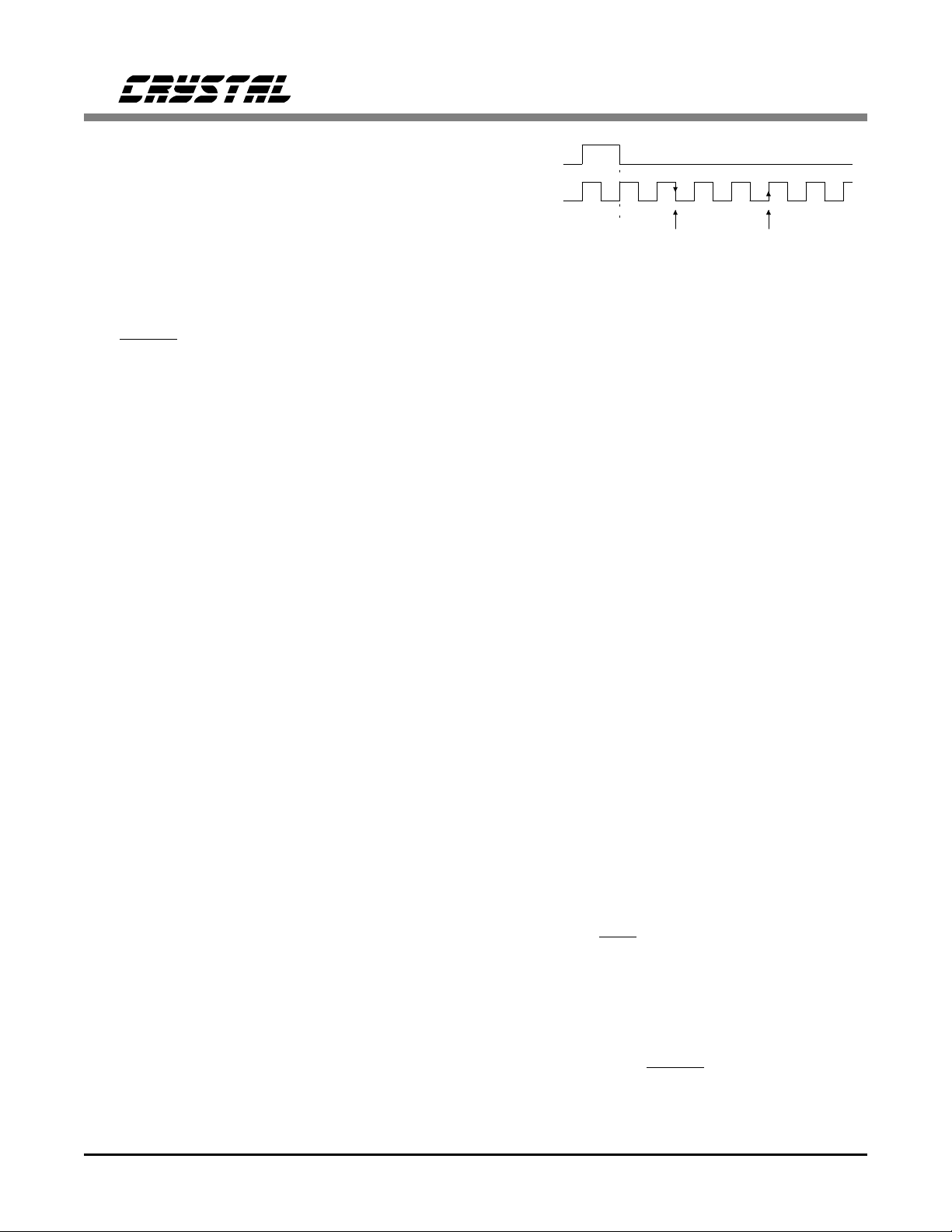

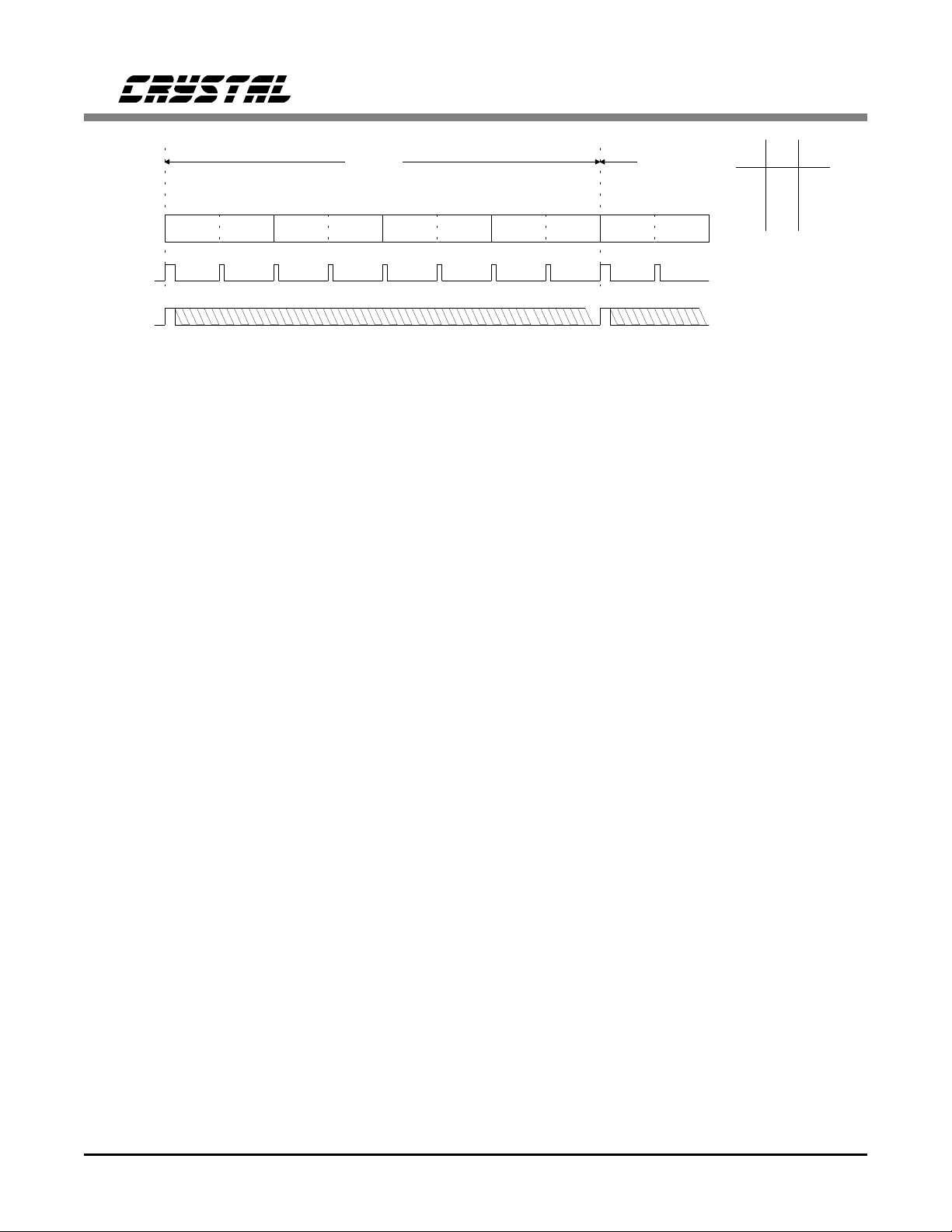

SSYNC

SCLK

(SM3)

Start of

Frame

Figure 4. Digital Input/Output Timing

DI pins

latched

DO pins

update

Parallel Dig ital Input/ Output Pin s

Parallel digital inputs are general purpose pins

whose value is reflected in the serial data output

stream to the processor. Parallel digital outputs

provide a way to control external devices using

bits in the serial data input stream. All parallel

digital pins, with the exception of DI1 and DO1,

are multifunction and are defined by the serial

mode selected. Serial modes 1 and 2 define all

multifunction pins as general purpose digital inputs and outputs. In Serial mode 3 only two

digital inputs and two digital outputs are available. In serial mode 4 only one digital input and

digital output exists. Figure 4 shows when the DI

pins are latched, and when the DO pins are updated in SM3 and SM4.

Muting and the ADC Valid Counter

The mute function allows the output channels to

be silenced. It is the controlling processor’s responsibility to reduce the signal level to a low

value before muting, to avoid an audible click.

The outputs should be muted before changing

the sample frequency.

The serial data stream contains a "Valid Data"

indicator for the A/D converters which is false

until enough clocks have passed since reset, or

low-power (power down mode) operation to have

valid A/D data from the filters, i.e., until calibration time plus the full latency of the digital

filters has passed.

Reset and Power Down Modes

Reset places the CS4216 into a known state and

must be held low for at least 50 ms after powerup or a hard power down. Reset must also occur

when the codec is in master mode and a change

in sample frequency is desired. In reset, the digital outputs are driven low. Reset sets all control

data register bits to zero.

Hard power down mode may be initiated by

bringing the PDN pin low. All analog outputs

will be driven to the REFBUF voltage which

will then decay to zero. All digital outputs will

be driven low and then will go to a high impedance state. Minimum power consumption will

occur if CLKIN is held low. After leaving the

power down state, RESET should be held low

for 50 ms to allow the analog voltage reference

to settle before calibration is started.

10 DS83F2

Page 11

CS4216

Alternatively, soft power down may be initiated,

in slave mode, by reducing the SC LK frequency

below the minimum CLKIN/12. In soft power

down the analog outputs are muted and the serial

data from the codec will indicate invalid data

and the appropriate error code. The parallel bit

I/O is still functional in soft power down mode.

This is, in effect, a low power mode with only

the parallel bit I/O unit functioning.

Audio Serial Interface

In serial modes 1, 2, and 3, the audio serial port

uses 4 pins: SDOUT, SDIN, SCLK and SSYNC.

SDIN carries the D/A converters’ input data and

control bits. Input data is ignored for frames not

allocated to the selected CS4216. SDOUT carries the A/D converters’ output data and status

bits. SDOUT goes to a high-impedance state

during frames not allocated to the selected

CS4216. SCLK clocks data in to and out of the

CS4216. The rising edge of SCLK clocks data

out on SDOUT. The falling edge latches data on

SDIN into the port (SC LK polarity is inverted in

Serial Modes 1&2). SSYNC indicates the start of

a frame and/or sub-frame. SCLK and SSYNC

must be synchronous to the master clock.

audio data which reduces the number of bits on

the audio port from 64 to 32 per codec.

The serial port protocol is based on frames consisting of 1, 2, or 4 sub-frames. The frame rate is

the system sample rate. Each sub-frame is used

by one CS4216 device. Up to 4 CS4216s may be

attached to the same serial control lines. SFS1

and SFS2 are tied low or high to indicate to each

CS4216 which sub-frame is allocated for it to

use.

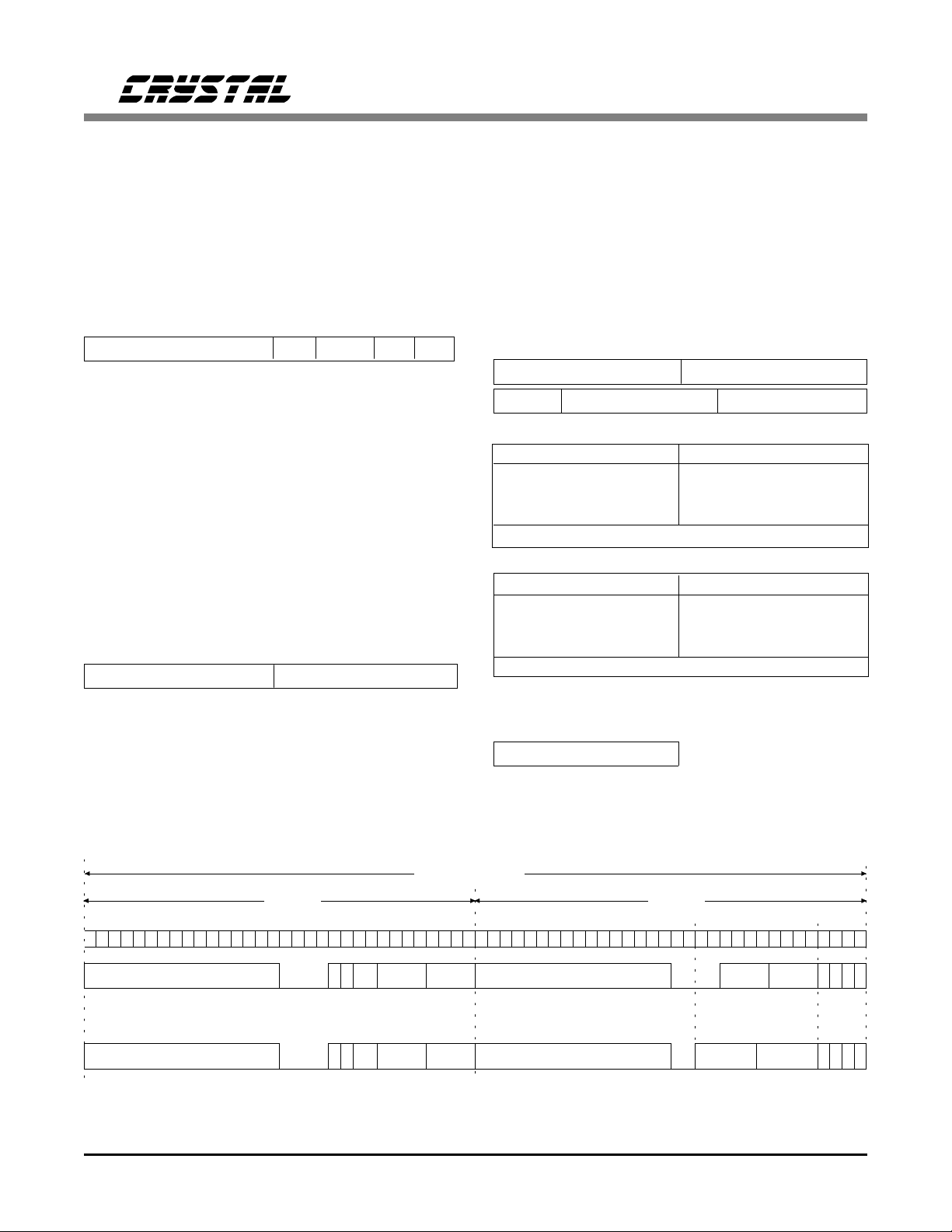

Serial Data Format

In serial modes 1, 2, and 3, a sub-frame is

64 bits in length and consists of two 16-bit audio

values and two 16-bit control fields. In serial

mode 4 a sub-frame is 32 bits in length and only

contains the two 16-bit audio values; th e control

data is loaded through a separate port. The audio

data is MSB first, 2’s complement format. The

sub-frame bit assignments for serial modes 1, 2,

and 3, are numbered 1 through 64 and are shown

in Figures 5 and 6. Control data bits all reset to

zero.

CS4216 SERIAL INTERFACE MODES

Serial mode 4 is similar to serial mode 3 with

the exception of the control information. In serial

mode 4 the control information is entered

through a separate asynchronous control port.

Therefore, the audio serial port only contains

The CS4216 has 4 serial port modes, selected by

the SMODE1, SMODE2 and SMODE3 pins. In

all modes, CLKIN, SCLK and SSYNC must be

derived from the same clock source. SM1 is an

easy interface to ASICs that use a change in the

SCLK-to-CLKIN ratio to determine the sample

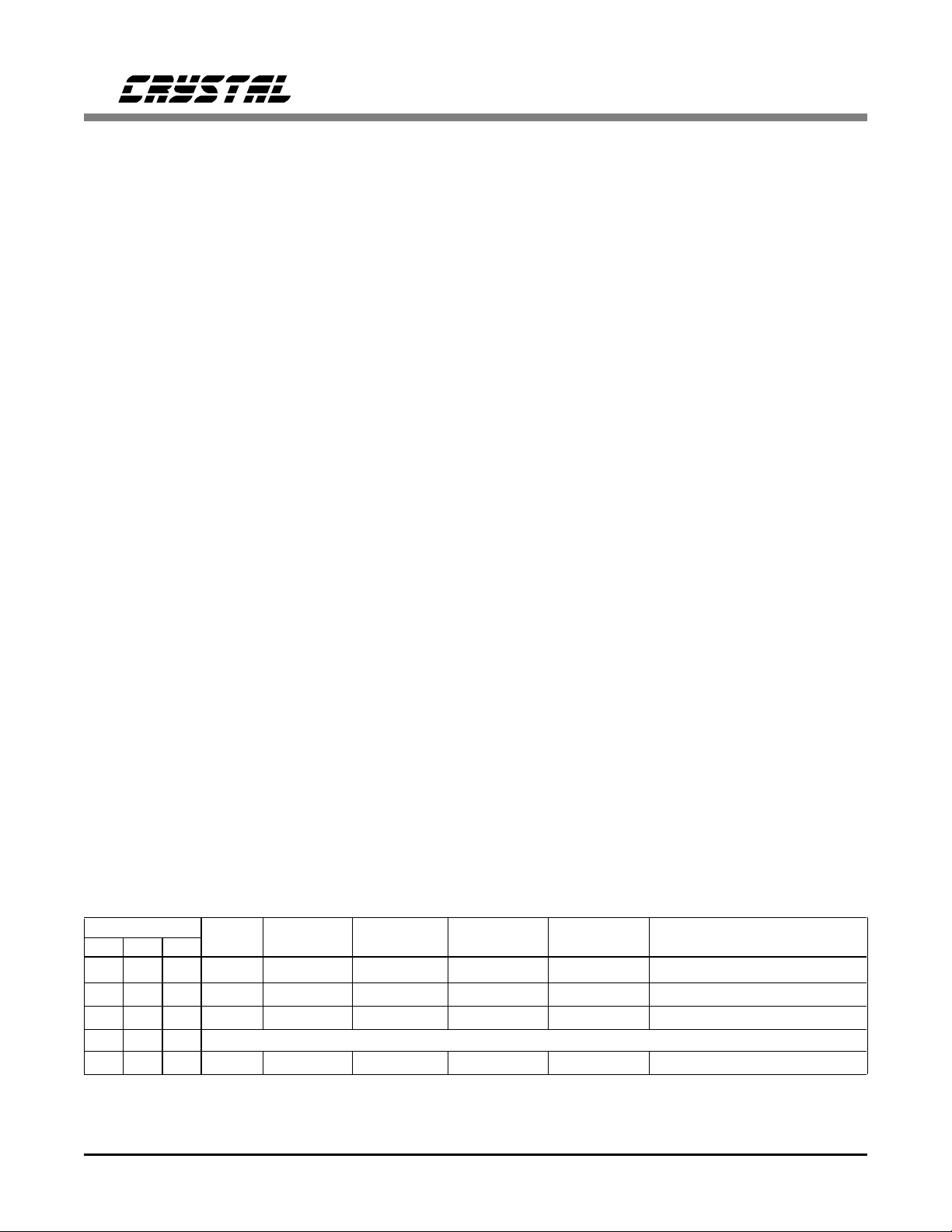

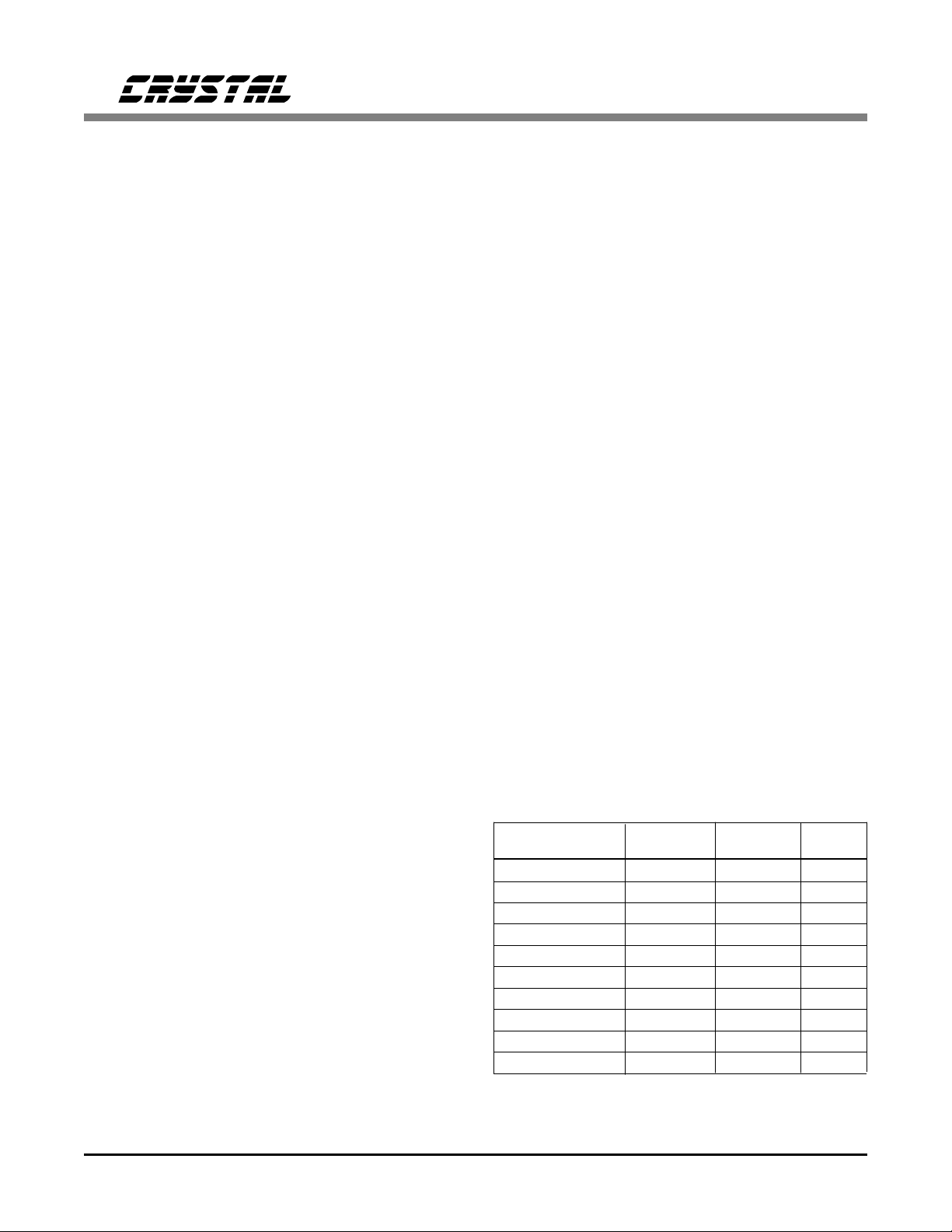

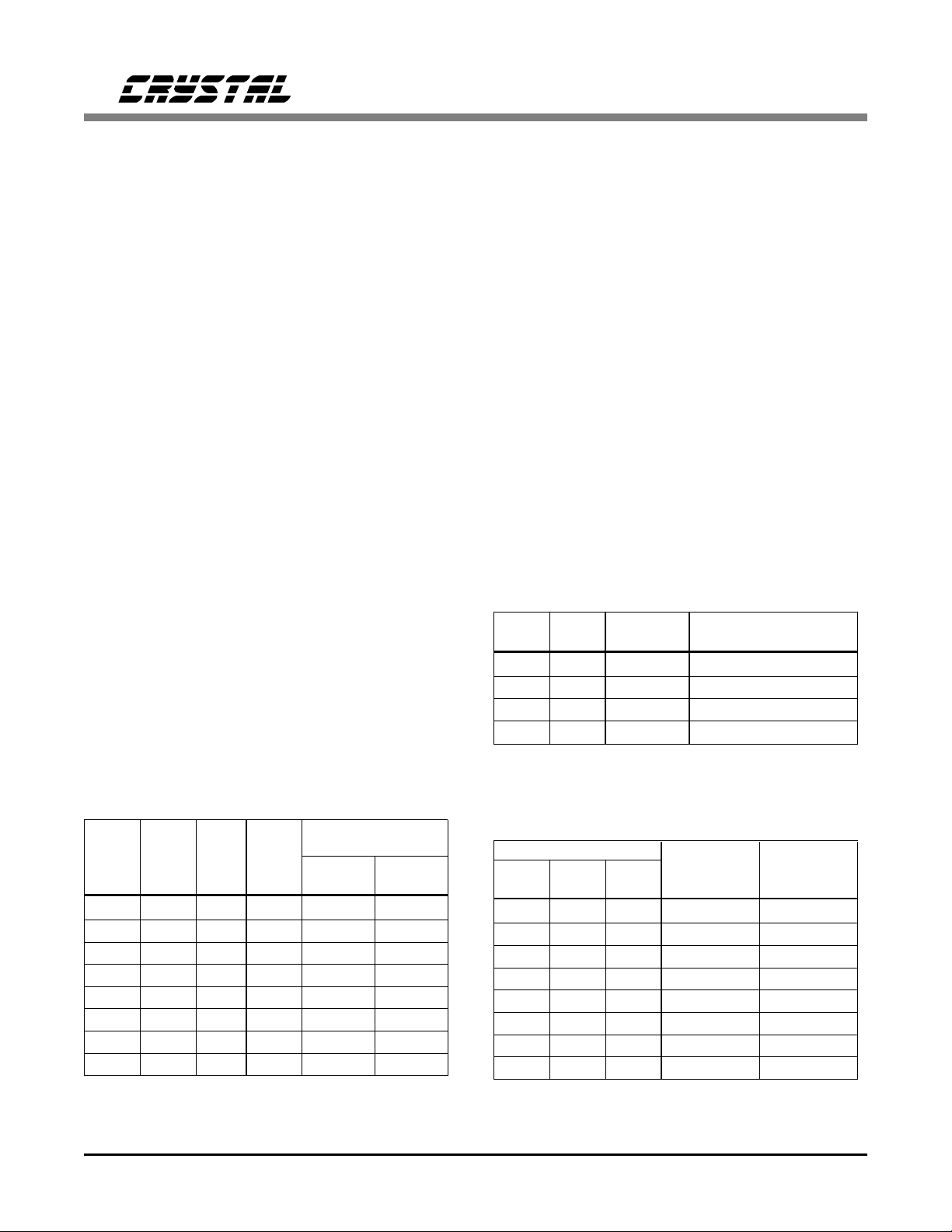

SMODE PINS Serial SCLK Bit Sub-frame Bits per SCLK & Master

3 2 1 Mode Center Width Frame (BPF) SSYNC Frequency

0 0 0 SM1 Rising 64 bits 256 Slave CLKIN = 512×Fs

0 0 1 SM2 Rising 64 bits 256 Slave SCLK = 256×Fs

0 1 0 SM3 Falling 64 bits 64/128/256 Master/Slave CLKIN/SCLK = 256×Fs

011 Factory Test mode

1 x x SM4 Falling 32 bits

†

Contains audio data only. Control information is entered through a separate serial por t.

DS83F2 11

†

32/64/128†Master/Slave CLKIN = 256×Fs

Table 1. Serial Port Modes

Page 12

CS4216

INPUT DATA BIT DEFINITIONS

Sub-frame bits 1 to 16

Left DAC Audio Data, MSB first, 2’s complement coded.

Sub-frame Bits 17 to 24

17 18 19 20 21 22 23 24

0000EXPMUTE ISLISR

EXP Expand bit

Reserved. Must be set to zero.

MUTE Mute D/A Outputs

0 - Normal Outputs

1 - Mute Outputs

ISL Select Left Input Mux

0 - Select LIN1

1 - Select LIN2

ISR Select Right Input Mux

0 - Select RIN1

1 - Select RIN2

Sub-frame Bits 25 to 32

25 26 27 28 29 30 31 32

LG3 LG2 LG1 LG0 RG3 RG2 RG1 RG0

LG3-LG0 Sets left input gain.

LG3 is the MSB. LG0 represents 1.5 dB.

0000 = no gain.

1111 = +22.5 dB gain

RG3-RG0 Sets right input gain.

RG3 is the MSB. RGO represents 1.5 dB.

0000 = no gain

Sub-frame Bits 33 to 48

Right DAC audio data MSB first, 2’s complement coded.

Sub-frame Bits 49 to 50

Must be zero.

Sub-frame Bits 51 to 60

51 52 53 54 55 56 57 58 59 60

LA4 LA3 LA2 LA1 LA0 RA4 RA3 RA2 RA1 RA0

*

†

0 0 LA3 LA2 LA1 LA0 RA3 RA2 RA 1 RA0

LA4-LA0 Sets left output attenuation

†SM1, 2

LA3 is the MSB.

0000 = no attenuation

1111 = -22.5 dB

*SM3,4

LA4 is the MSB.

00000 = no attenuation

11111 = -46.5 dB

LA0 represents 1.5 dB.

RA4-RA0 Sets r ight output attenuation

†SM1, 2

RA3 is the MSB.

0000 = no attenuation

1111 = -22.5 dB

*SM3,4

RA4 is the MSB.

00000 = no attenuation

11111 = -46.5 dB

RA0 represents 1.5 dB.

Sub-frame Bits 61 to 64

61 62 63 64

DO1 DO2 DO3 DO4

DO1-DO4 Set the logic level on the 4 digital output

pins. In SM3 DO3 and DO4 are not

available. In SM4 DO2, DO3, & DO4

are not available.

Sub-frame

Sub-frame

01

MSB

MSB

DAC - Left Word

DAC - Left Word

Word A

16

17

LSB

0000

LSB

0000

22

23

21

In

M

EXP

Sel.

In

M

Sel.

EXP

25

24

30

A/D Gain

30

A/D Gain

28

Left

Left

29

30

Right

A/D Gain

SM1 and SM2

30

Right

A/D Gain

SM3

32

33

MSB

MSB

DAC - Right Word

DAC - Right Word

Word B

51

LSB

0000

40

Left

LSB

D/A Att.

00

524853

56

57

55

30

30

Left

D/A Att.

Right

D/A Att.

40

Right

D/A Att.

60

61

DO1

DO1

DO2

XX

DO2

DO3

Figure 5. Serial Data Input Format - SM1, SM2, and SM3.

12 DS83F2

64

DO4

Page 13

CS4216

OUTPUT DATA BIT DEFINITIONS

Sub-frame Bits 1 to 16

Left ADC Audio Data, MSB first, 2’s complement coded.

Sub-frame Bits 17 to 24

17 18 19 20 21 22 23 24

RESERVED 0 ADV LCL RCL

ADV ADC Valid data bit.

0- Invalid ADC data

1- Valid A DC data

Indicates ADC has completed initialization

after power-up, low power mode,

or mute.

LCL Left ADC clipping indicator

0- Normal

1- Clipping

RCL Right ADC clipping indicator

0- Normal

1- Clipping

RESERVED bits can be 0 or 1

Sub-frame Bits 25 to 32

25 26 27 28 29 30 31 32

ER3 ER2 ER1 ER0 Ver3 Ver2 Ver1 Ver0

ER3-ER0 Error Word

0000 - Normal – No errors.

0001 - Input Sub-frame Bit 21 is set.

Control data will not be loaded

0010 - Sync Pulse is inc orrect.

Causes the analog output to mute.

0011 - SCLK is outside the allowable

range. Analog output mutes.

Ver3-Ver0 CS4216 Version Number

0000 = "A" (see Appendix A)

0001 = "B", "C", . . . (This data sheet)

Sub-frame Bits 33 to 48

Right ADC Audio Data, MSB first, 2’s complement coded.

Sub-frame Bits 49 to 60

These bits are reserved, and can be 0 or 1.

Sub-frame Bits 61 to 64

61 62 63 64

DI1 DI2 DI3 DI4

DI1-DI4 These bits follow the state of the Digital

Input pins. In SM3 DI3 and DI4 are used

and unavailable. In SM4 DI2, DI3, & DI4

are not available as input bits.

Sub-frame

Sub-frame

Word B

48

XXXX

LSB

LSB

XXXX

535657

55

52

00010000

00010000

60

61

DI1

DI1

DI2

DI3

XX

DI2

01

MSB

MSB

ADC - Left Word

ADC - Left Word

Word A

16

17

.

XXXX

LSB

XXXX

LSB

212425

22

23

LCL

0

ADV

0

LCL

ADV

28

29

30

RCL

30

RCL

30

Version

Error

SM1 and SM2

30

Version

Error

32

SM3

33

ADC - Right Word

MSB

ADC - Right Word

MSB

Figure 6. Serial Data Output Format - SM1, SM2, a nd SM3.

DS83F2 13

64

DI4

Page 14

CS4216

frequency. SM2 is similar to SM1 except that

CLKIN is not used and SCLK becomes the mas-

ter clock and is fixed at 256×Fs. SM3 was

designed as an easy interface to general purpose

DSPs and provides extra features such as one

more bit of attenuation, a master mode, and variable frame sizes. SM4 is similar to SM3 but

splits the audio data from the control data

thereby reducing the audio serial bus bandwidth

by half. The control data is transmitted through a

control serial port in SM4.

Table 1 lists the serial port modes available,

along with some of the differences between

modes. The first three columns in Table 1 select

the serial mode. The "SCLK Bit Center" column

indicates whether SCLK is rising or falling in

the center of a bit period. The "Sub-frame

Width" column indicates how many bits are in

an individual codec’s sub-frame. SM4 differs

from all other modes by separating the control

data from the audio data. In both SM1 and SM2,

there are 256 bits per frame which allows up to

four codecs to occupy the same bus. In SM3 and

SM4, the number of bits per frame is programmable. In SM1 and SM2, SCLK and SSYNC

must be generated externally; whereas, in SM3

and SM4 the CS4216 can optionally generate

those signals. In all modes, SCLK and SSYNC

must be synchronous to the master clock. The

last column in Table 1 lists the master frequency

used by the codec. In SM1, the master frequency, input on CLKIN, is 512 times the

highest sample frequency available. In SM2, the

master frequency is fixed at 256 times the sample frequency and, in this mode, SCLK is the

master clock. In SM3, the master frequency is

256 times the highest frequency available and is

input on CLKIN or SCLK, based on the submode used. In SM4, the master frequency is also

256 times the highest frequency available and is

input on CLKIN.

SERIAL MODE 1, SM1

Serial Mode 1 is a slave mode selected by setting SMODE3 = SMODE2 = SMODE1 = 0.

SCLK and SYNC must be synchronous the master clock. SM1 uses a two bit wide (minimum)

frame sync with an optional word sync. In this

mode, SSYNC low for one SCLK period followed by SSYNC high for a minimum of two

SCLK periods indicates the beginning of a

frame. The first bit of the frame starts with the

rising edge of SSYNC. An optional word sync,

being one SCLK period high, may be used to

indicate the start of a new 32-bit word. Figures 5

and 6 contain the serial data format for SM1. In

this serial mode, the ratio of two clocks are used

to select sample frequency. These are the master

clock CLKIN and the serial clock SCLK.

CLKIN should be set to 512×Fs

Fs

is the maximum required sample rate.

max

max

, where

SCLK must be externally set to a value of

CLKIN/N, such that SCLK equals 256 times the

desired sample rate. The codec uses the ratio between CLKIN and SCLK to set the internal

sample frequency and causes the CS4216 to go

into soft power down mode if the SCLK frequency drops to <CLKIN/12. Even if only 1

CS4216 is used, the timing for 4 devices must be

maintained. Table 2 shows some example sample

rates for SM1.

Sample Rate SCLK CLKIN N

kHz MHz MHz

48 12.288 24.576 2

32 8.192 24.576 3

24 6.144 24.576 4

19.2 4.9152 24.576 5

16 4.096 24.576 6

12 3.072 24.576 8

9.6 2.4576 24.576 10

8 2.048 24.576 12

7.2 1.843 22.116 12

44.1 11.2896 22.5792 2

Table 2. SM1 - Example Clock Frequencies

14 DS83F2

Page 15

DATA

SSYNC

or

SSYNC

FRAME n

256 SCLK Periods

Sub-frame 1 Sub-frame 2 Sub-frame 3 Sub-frame 4

Word A Word B Word A Word B Word A Word B Word A Word B

FS

WS WS WS WS WS WS WS

Figure 7. SM1, SM2 - 256 Bits pe r Frame.

FRAME (n+1)

Sub-frame 1

Word A Word B

FS

WS

CS4216

MF8: MF7: Sub-

SFS2 SFS1 frame

0

0

0

1

1

FS = Frame Sync

Low followed by

Two High Bits

WS =

1

1

2

0

3

4

1

One High

Optional

Not Needed

SERIAL MODE 2, SM2

Serial Mode 2 is enabled by setting SMODE3 =

SMODE2 = 0, and SMODE1 = 1. SM2 is simi-

lar to SM1 except that SCLK is fixed at 256 ×

Fs and is the master clock instead of CLKIN.

The CLKIN pin is ignored in this mode and

should be tied low. In SM2, the sample frequency will scale linearly with the frequency of

SCLK. Up to four codecs may occupy the serial

bus since each codec requires only 64 bit periods

and a frame is fixed at 256 bit periods. The serial data format is the same as SM1 and is

illustrated in Figures 5 and 6.

The multifunction pins in SM2 are defined identically to SM1. See Serial Mode 1, SM1 section

for more details.

SERIAL MODE 3, SM3

Serial Mode 3 is enabled by setting

SMODE3 = 0, SMODE2 = 1 and SMODE1 = 0.

This mode is designed to interface easily to

DSPs and has the added versatility of a programmable number of bits per frame, a master mode,

and one extra bit of D/A attenuation. In SM3,

two of the parallel digital input bits and two of

the parallel digital output bits are available.

Master Clock Frequency

In SM3, the master clock, CLKIN, must be

256 × Fs

. For example, given a 48 kHz maxi-

max

mum sample frequency, the master clock

frequency must be 12.288 MHz. SCLK and

SSYNC must be synchronous to CLKIN.

D/A Attenuation

SM3 has one more bit per channel allocated for

D/A attenuation which doubles the attenuation

range. Figure 5 illustrates the serial data in,

SDIN, sub-frame for all SM3 sub-modes. The

upper portion of this figure shows modes SM1

and SM2 where the D/A attenuation is located in

Word B, bits 53 through 60. Four bits allow attenuation on each channel from 0 dB down to

-22.5 dB using 1.5 dB steps. In SM3 the attenuation bits are still located in Word B, but start at

bit 51 of the sub-frame. This allows five bits of

attenuation per channel instead of four, producing an attenuation range for each channel from

0 dB down to -46.5 dB.

In SM3 MF5:DO2 is a general purpose output

and MF6:DI2 is a general purpose input. The

other six multifunction pins are used to select

sub-modes under SM3.

SM3 is divided into two sub-modes, Master and

Slave. In Master sub-mode, the CS4216 generates SSYNC and SCLK, while in Slave

sub-mode SSYNC and SCLK must be generated

DS83F2 15

Page 16

CS4216

externally. In Master sub-mode, the serial port

signal transitions are controlled with respect to

the internal analog sampling clock to minimize

the amount of digital noise coupled into the analog section. Since SSYNC and SCLK are

externally derived in Slave sub-mode, optimum

noise management cannot be obtained; therefore,

Master sub-modes should be used whenever possible.

Master Sub-Mode (SM3)

Master sub-mode is selected by setting

MF4:MA = 1, which configures SSYNC and

SCLK as outputs from the CS4216. During

power down, SSYNC and SCLK are driven high

impedance, and during reset they both are driven

low. In Master sub-mode the number of bits per

frame determines how many codecs can occupy

the serial bus and is illustrated in Figure 8.

Bits Per Frame (Master Sub-Mode)

MF8:SFS2 selects the number of bits per frame.

The two options are MF8:SFS2 = 1 which selects 128 bits per frame, and MF8:SFS2 = 0

which selects 64 bits per frame.

Selecting 128 bits per frame (MF8:SFS2 = 1) allows two CS4216s to operate from the same

serial bus since each codec requires 64 bit periods. The sub-frame used by an individual codec

is selected using MF7:SFS1. MF7:SFS1 = 0 selects sub-frame 1 which is the first 64 bits

following the SSYNC pulse. MF7:SFS1 = 1 selects sub-frame 2 which is the last 64 bits of the

frame.

Selecting 64 bits per frame (MF8:SFS2 = 0) allows only one CS4216 to occupy the serial port.

Since there is only one sub-frame (which is

equal to one frame), MF7:SFS1 is defined differently in this mode. MF7:SFS1 selects the format

of SSYNC. MF7:SFS1 = 0 selects an SSYNC

pulse one SCLK period high, directly preceding

the data as shown in the center portion of Fig-

ure 8. This format is used for all other Master

and Slave sub-modes in SM3. If MF7:SFS1 = 1,

an alternate SSYNC format is chosen in which

SSYNC is high during the entire Word A

(32 bits), which includes the left sample, and

low for the entire Word B (32 bits), which includes the right sample. This alternate format for

SSYNC is illustrated in the bottom portion of

Figure 8 and is only available in Master submode with 64 bits per frame. A more detailed

timing diagram for the 64 bits-per-frame Master

sub-mode is shown in Figure 9.

Sample Frequency Selection (Master Sub-Mode)

In SM3, Master sub-mode, the multifunction

pins MF1:F1, MF2:F2, and MF3:F3 are used to

select the sample frequency divider. Table 3 lists

the decoding for the sample frequency select

pins where the sample frequency selected is

CLKIN/N. Also shown are the sample frequencies obtained by using one of two example

master clocks: either 12.288 MHz or

11.2896 MHz. The codec must be reset when

changing sample frequencies to allow the codec

to calibrate to the new sample frequency.

Slave Sub-Mode (SM3)

In SM3, Slave sub-mode is selected by setting

MF4:MA = 0 which configures SSYNC and

SCLK as inputs to the CS4216. These two signals must be externally derived from CLKIN. In

Slave sub-mode, the phase relationship between

SCLK/SSYNC and CLKIN cannot be controlled

since SCLK and SSYNC are externally derived.

Therefore, the noise performance may be slightly

worse than when using the master sub-mode.

The number of sub-frames on the serial port is

selected using MF1:F1 and MF2:F2. In Slave

sub-mode MF3:F3 works as a general purpose

input. Figures 10 through 12 illustrate the Slave

sub-mode formats.

16 DS83F2

Page 17

CS4216

DATA

SSYNC

DATA

SSYNC

DATA

FRAME n

128 SCLK Periods

Sub-frame 1 Sub-frame 2

Word A Word B Word A Word B

FRAME n

FRAME (n+1)

64 SCLK Periods

Sub-frame 1

Word A Word B

FRAME n

64 SCLK Periods

Sub-frame 1

Word A Word B

Sub-frame 1

Word A Word B

FRAME (n+1)

Sub-frame 1

Word A Word B

FRAME (n+2)

Sub-frame 1

Word A Word B

FRAME (n+2)

Sub-frame 1

Word A Word B

FRAME (n+2)

Sub-frame 1

Word A Word B

Sub-frame 2

Word A Word B

FRAME (n+3)

Sub-frame 1

Word A Word B

FRAME (n+3)

Sub-frame 1

Word A Word B

FRAME (n+3)

Sub-frame 1

Word A Word B

FRAME (n+4)

Sub-frame 1

Word A Word B

FRAME (n+4)

Sub-frame 1

Word A Word B

MF8: MF7: Sub-

SFS2 SFS1 frame

110

1

1

2

MF8: MF7: Sub-

SFS2 SFS1 frame

00

1

MF8: MF7: Sub-

SFS2 SFS1 frame

01

1

SSYNC

SCLK

SDIN

SDOUT

SSYNC

(MF7:SFS1=0)

SSYNC

(MF7:SFS1=1)

MSB

Figure 8. SM3, Master Sub-Mode.

MSB

LSB

Word A

32 CLOCKS

LSB

Word B

32 CLOCKS

Figure 9. Detailed Master Sub-Mode, 64 BPF.

DS83F2 17

Page 18

CS4216

Bits per Frame (Slave Sub-Mode)

In Slave sub-mode, MF1:F1 and MF2:F2 select

the number of bits per frame which determines

how many CS4216’s can occupy one serial port.

Table 4 lists the decoding for MF1:F1 and

MF2:F2.

When set for 64 SCLKs per frame, one device

occupies the entire frame; therefore, a sub-frame

is equivalent to a frame. MF7:SFS1 and

MF8:SFS2 must be set to zero. See Figure 10.

When set for 128 SCLKs per frame, two devices

can occupy the serial port, with MF7:SFS1 selecting the particular sub-frame. MF8:SFS2 must

be set to zero. See Figure 11.

When set for 256 SCLKs per frame (MF1:F1,

MF2:F2 = 10), four devices can occupy the serial port. In this format both MF8:SFS2 and

MF7:SFS1 are used to select the particular subframe. See Figure 12.

In all three of the above Slave sub-mode formats, the frequency of the incoming SCLK

signal, in relation to the master clock provided

on the CLKIN pin, determines the sample frequency. The CS4216 determines the ratio of

SCLK to CLKIN and sets the internal operating

frequency accordingly. Table 5 lists the SCLK to

CLKIN frequency ratio used to determine the

codec’s sample frequency. To obtain a given

sample frequency, SCLK must equal CLKIN divided by the number in the table, based on the

number of bits per frame. As an example, assuming 64 BPF (bits per frame) and

CLKIN = 12.288 MHz, if a sample frequency of

24 kHz is desired, SCLK must equal CLKIN divided by 8 or 1.536 MHz.

When MF1:F1 = MF2:F2 = 1, SCLK is used as

the master clock and is assumed to be 256 times

the sample frequency. In this mode, CLKIN is

ignored and the sample frequency is linearly

scaled with SCLK. (The CLKIN pin must be

tied low.) This mode also fixes SCLK at 256 bits

per frame with MF7:SFS1 and MF8:SFS2 selecting the particular sub-frame.

MF1: MF2: Bits per Sample Frequency/

F1 F2 Fr ame SCLK

0 0 64 ratio to CLKIN sensed

0 1 128 ratio to CLKIN sensed

1 0 256 ratio to CLKIN sensed

1 1 256 fixed†. = 256×Fs

†

SCLK is master clock. CLKIN is not used.

Table 4. SM3-Slave, Bits per Frame.

Fs (kHz)

MF1: MF2: MF3: N with CLKIN

F1 F2 F3 12.288 11.2896

MHz MHz

0 0 0 256 48.00 44.10

0 0 1 384 32.00 29.40

0 1 0 512 24.00 22.05

0 1 1 640 19.20 17.64

1 0 0 768 16.00 14.70

1 0 1 1024 12.00 11.025

1 1 0 1280 9.60 8.82

1 1 1 1536 8.00 7.35

Table 3. SM3-Master, Fs Select

18 DS83F2

SCLK to CLKIN Ratio Fs (kHz) Fs (kHz)

BPF BPF BPF with CLKIN with CLKIN

256 128 64 12.288 MHz 11.2896 MHz

1 2 4 48.00 44.10

1.5 3 6 32.00 29.40

2 4 8 24.00 22.05

2.5 5 10 19.20 17.64

3 6 12 16.00 14.70

4 8 16 12.00 11.025

5 10 20 9.60 8.82

6 12 24 8.00 7.35

Table 5. SM3-Slave, Fs Select.

Page 19

CS4216

SERIAL MODE 4, SM4

Serial mode 4 is enabled by setting

SMODE3 = 1. Both Master and Slave submodes are available and are selected by setting

the SMODE2 and SMODE1 pins as shown in

Table 6. In Master sub-mode, the phase relationship between SCLK/SSYNC and CLKIN is

controlled to minimize digital noise coupling

into the analog section. Therefore, Master submode may yield slightly better noise

performance than Slave sub-mode. In Slave submode, SCLK and SSYNC must be synchronous

to the master clock.

In serial mode 4, SM4, the CLKIN frequency

must be 256 times the highest sample frequency

needed. Also, SM4 has five attenuation bits for

FRAME n

64 SCLK Periods

FRAME (n+1)

FRAME (n+2)

each D/A output channel. SM4 differs from SM3

in that SM4 splits the audio data from the control data with the control data input on an

independent serial port. This reduces the audio

serial bus bandwidth in half, providing an easier

interface to low-cost DSPs. The audio serial port

sub-frame is illustrated in Figure 13 for SM4.

Interrupt Pin - MF5:INT

Serial Mode 4 also defines the multifunction pin

MF5:INT as an open-collector interrupt pin. In

SM4, this pin requires a pullup resistor and will

go low when the ADV bit or DI1 pin change, or

a rising edge on the LCL or RCL bits, or by

exiting an SCLK out of range condition (Error = 3). The interrupt may be masked by setting

the MSK bit in the control serial data port.

FRAME (n+3)

DATA

SSYNC

DATA

SSYNC

DATA

SSYNC

Sub-frame 1

Word A Word B

Sub-frame 1

Word A Word B

Sub-frame 1

Word A Word B

Sub-frame 1

Word A Word B

Figure 10. SM3-Slave - 64 BPF; MF1:F1, MF2:F2 = 00

FRAME n

128 SCLK Periods

Sub-frame 1 Sub-frame 2

Word A Word B Word A Word B

Sub-frame 1

Word A Word B

FRAME (n+1)

Sub-frame 2

Word A Word B

Figure 11. SM3- Sl av e - 128 BPF; MF1:F1, MF2:F2 = 01

FRAM E n

256 SC LK P eriods

Su b -fra m e 1 Su b -fra me 2 S u b -frame 3 Su b -frame 4

Word A Word B Word A Word B Word A Word B Word A Word B

FRAME (n+2)

Sub-frame 1

Word A Word B

FRAME (n+1)

Sub-fram e 1

Wo rd A Word B

MF8: MF7: Sub-

SFS1 frame

SFS2

001

MF8: MF7: Sub-

SFS2 SFS1 frame

00011

2

MF8: MF7: Sub-

SFS2 SFS1 fram e

0

0

1

1

0

1

1

2

0

3

1

4

Figure 12. SM3- Sl av e - 256 BPF; MF1:F1, MF2:F2 = 10

DS83F2 19

Page 20

CS4216

MF5:INT is reset by reading the control serial

port.

Master Sub-Mode (SM4)

Master sub-mode configures SSYNC and SCLK

as outputs from the CS4216. During power

down, SSYNC and SCLK are driven high impedance, and during reset they both are driven

low. There are two SM4 Master sub-modes. One

allows 32 bits per frame and the other allows 64

bits per frame. As shown in Table 6, the

SMODE1 and SMODE2 pins select the particular Master sub-mode (as well as the Slave

sub-mode). When SMODE1 is set to zero,

SMODE2 selects either Master sub-mode with

32-bit frames, or Slave sub-mode.

SMODE1,SMODE2 = 00 selects Master submode where a frame = sub-frame = 32 bits. This

sub-mode allows only one codec on the audio

serial bus, with the first 16 bits being the left

channel and the second 16 bits being the right

channel. The Applications of SM4 section contains more information on low-cost

implementations of this sub-mode.

SMODE1 = 1 selects Master sub-mode with a

frame width of 64 bits. This sub-mode allows up

to two codecs to occupy the same bus. SMODE2

is now used to select the particular time slot. If

SMODE2 = 0 the codec selects time slot 1,

which is the first 32 bits. If SMODE2 = 1 the

codec selects time slot 2, which is the second

32 bits.

In Master sub-mode, multifunction pins MF6:F1,

MF7:F2, and MF8:F3 select the sample frequency as shown in Table 7. This table indicates

how to obtain standard audio sample frequencies

given one of two CLKIN frequencies:

12.288 MHz or 11.2896 MHz. Other CLKIN

frequencies may be used with the corresponding

sample frequencies being CLKIN/N. The codec

must be reset when changing sample frequencies

to allow a new calibration to occur.

SMODE1 SMODE2 SM4, Sub-Mode

0 0 Master, 32 BPF

0 1 Slave, 128/64/32 BPF

1 0 Master, 64 BPF, TS1

1 1 Master, 64 BPF, TS2

Table 6. SM4 Sub-Modes.

(master)

SSYNC

(slave)

SCLK

SDOUT

SDIN

23

ADC - Right Word

DAC - Right Word

32

LSB

LSB

1

MSB

MSB

8

ADC - Left Wo rd

DAC - Left Word

Figure 13. SM4-Audio Serial Port, 32 BPF

Slave Sub-Mode (SM4)

In SM4, Slave sub-mode is selected by setting

SMODE1,SMODE2 = 01. This mode configures

SSYNC and SCLK as inputs to the CS4216.

These two signals must be externally derived

from CLKIN. Since the CS4216 has no control

over the phase relationship of SSYNC and

Sub-Frame

9

16

LSB

LSB

17

MSB

MSB

24

25

ADC - Right Word

DAC - Right Word

32

LSB

LSB

1

MSB

MSB

ADC - Left Word

DAC - Left Word

14

20 DS83F2

Page 21

CS4216

SCLK to CLKIN, the noise performance in

Slave sub-mode may be slightly worse than

when using Master sub-mode. The CS4216 internally sets the sample frequency by sensing the

ratio of SCLK to CLKIN; therefore, for a given

CLKIN frequency, the sample frequency is selected by changing the SCLK frequency.

SM4-Slave allows up to four codecs to occupy

the same audio serial port. Table 8 lists the pin

configurations required to set the serial audio

port up for 32, 64, or 128 bits-per-frame (BPF).

Since each codec requires one sub-frame of

32 bits, 64 bits-per-frame allows up to two

codecs to occupy the same audio serial port, and

128 bits-per-frame allows up to four codecs to

occupy the same audio serial port. When set up

for more than one codec on the bus, other pins

are needed to select the particular time slot (TS)

associated with each codec. MF8:SFS2 selects

the time slot when in 64 BPF mode, and

MF8:SFS2 and MF7:SFS1 select one of four

time slots when in 128 bits-per-frame mode. Table 8 lists the decoding for time slot selection.

In SM4-Slave, the frequency of the incoming

SCLK signal, in relation to CLKIN, determines

the sample frequency on the CS4216. The

CS4216 determines the ratio of SCLK to CLKIN

and sets the internal sample frequency accord-

Fs (kHz)

MF6: MF7: MF8: N with CLKIN

F1 F2 F3 12.288 11.2896

MHz MHz

0 0 0 256 48.00 44.10

0 0 1 384 32.00 29.40

0 1 0 512 24.00 22.05

0 1 1 640 19.20 17.64

1 0 0 768 16.00 14.70

1 0 1 1024 12.00 11.025

1 1 0 1280 9.60 8.82

1 1 1 1536 8.00 7.35

ingly. Table 9 lists the SCLK to CLKIN frequency ratio used to determine the codec’s

sample frequency. SCLK must equal CLKIN divided by the number in the table, based on the

selected bits per frame. As an example, assuming

32 BPF and CLKIN = 11.2896 MHz, if a sample

frequency of 11.025 kHz is desired, SCLK must

equal CLKIN divided by 32 or 352.8 kHz.

Serial Cont rol Port (SM4)

Serial Mode 4 separates the audio data from the

control data. Since control data such as gain and

attenuation do not change often, this mode reduces the bandwidth needed to support the audio

serial port.

The control information is entered through a

separate port that can be asynchronous to the

audio port and only needs to be updated when

changes in the control data are needed. After a

reset or power down, the control port must be

written once to in itialize it if the port will be accessed to read or write control bits. This initial

write is considered a "dummy" write since the

data is ignored by the codec. A second write is

needed to configure the codec as desired. Then,

the control port only needs to be written to when

a change is desired, or to obtain the status information. The control port does not function if the

master clock is not operating. When the control

MF6: MF7: MF8: Bits Per Time

F1 SFS1 SFS2 Frame Slot

(BPF) (TS)

000 32 1

001 Reserved

010 64 1

011 64 2

100 128 1

110 128 2

101 128 3

111 128 4

Table 7. SM4-Master, Fs Select

DS83F2 21

Table 8. SM4-Slave, Audio Port BPF & TS Select

Page 22

CS4216

port is used asynchronously to the audio port,

the noise performance may be slightly degraded

due to this asynchronous digital noise.

Since control data does not need to be accessed

each audio frame, an interrupt pin, MF5:INT, is

included in this mode and will go low when

status has changed. The control port serial data

format is illustrated in Figure 14. The control

port uses one of the multifunction pins as a chip

select line, MF4:CCS, that must be low for entering control data. Although only 23 bits

contain useful data on MF2:CDIN, a minimum

of 31 bits must be written. If more than 31 bits

are written without toggling MF4:CCS, only the

first 31 are recognized. MF1:CDOUT contains

SCLK to CLKIN Ratio Fs (kHz) Fs (kHz)

BPF BPF BPF with CLKIN with CLKIN

128 64 32 12.288 MHz 11.2896 MHz

2 4 8 48.00 44.10

3 6 12 32.00 29.40

4 8 16 24.00 22.05

5 10 20 19.20 17.64

6 12 24 16.00 14.70

8 16 32 12.00 11.025

10 20 40 9.60 8.82

12 24 48 8.00 7.35

Table 9. SM4-Slave, Fs Select.

status information that is output on the rising

edge of MF3:CCLK. Status information is repeated at the end of the frame, bits 25

through 30, to allow a simple 8-bit shift and

latch register to store the most important status

information using the rising edge of MF4:CCS at

the latch control (see Figure 17).

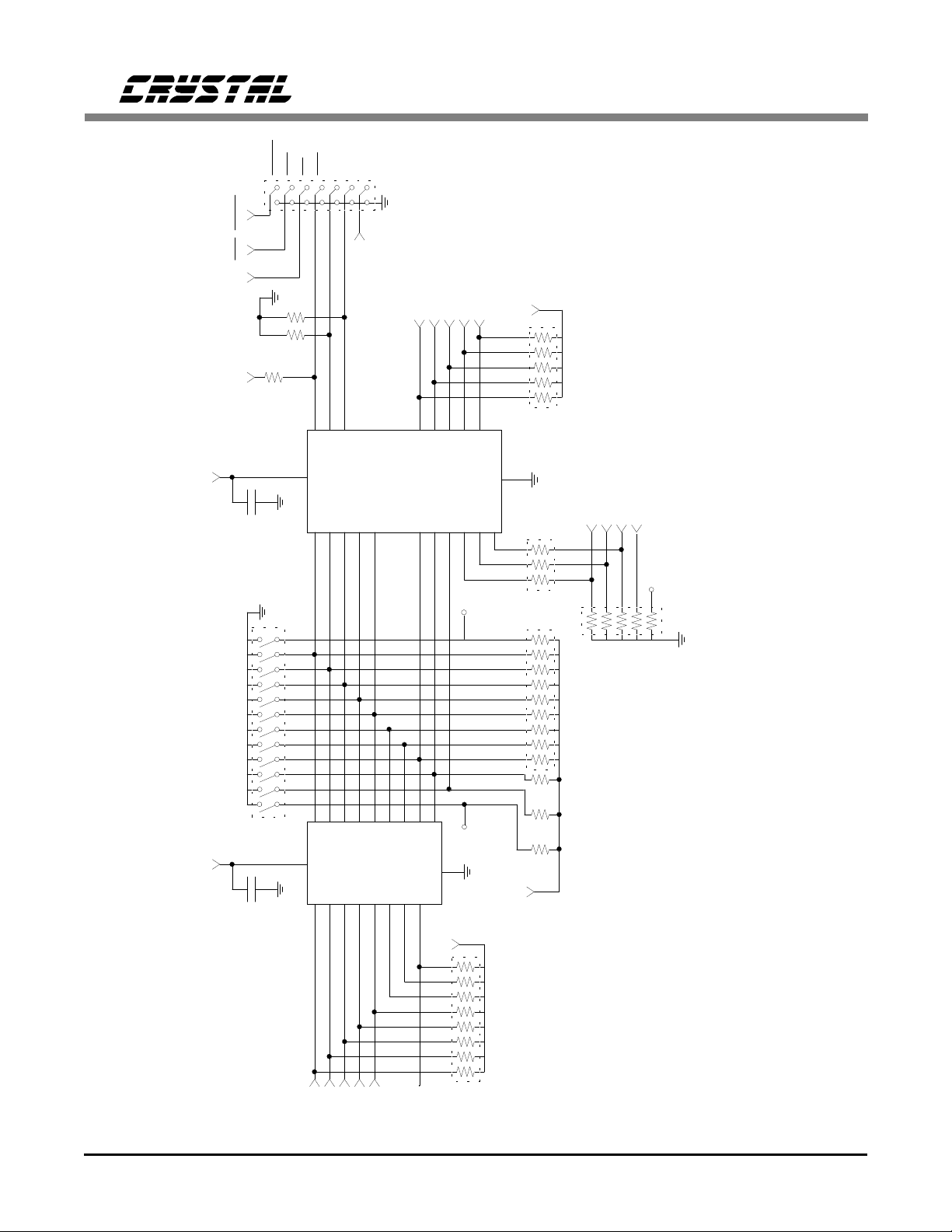

Applications of SM4

Figure 15 illustrates one method of using serial

mode 4 wherein a DSP controls the audio serial

port and a microcontroller controls the control

port. Each controller is run independently and

the micro updates the control information only

when needed, or when an interrupt from the

CS4216 occurs.

Figure 16 illustrates the minimum interface to

the CS4216. In this application, the DSP sends

and receives stereo DAC and ADC information.

The CS4216 is configured for 32 bits per frame,

Master sub-mode. The control data resets to all

zeros, which configures the CS4216 as a simple

stereo codec: no gain, no attenuation, line inputs

#1, and not muted.

Figure 17 illustrates how to use all the CS4216

features with a low cost DSP that cannot support

the interrupt rate of SM3. Using SM4 (32 bits

MF4:CCS

MF3:CCLK

1

40

MF2:CDIN

MF1:CDOUT

22 DS83F2

MSK

0

DO1

Left

D/A Att.

8

9

40

Right

D/A Att.

DI1

LCL

RCL

ADV

Figure 14. SM4 - Control Serial Port

16

17

30

In

M

Sel.

1030

Err Version

0

Left

A/D Gain

24

25

30

Right

A/D Gain

0001

00000000

10

LCL

Err

DI1

RCL

32

ADV

Page 23

CS4216

per frame, Master sub-mode) reduces the DSP

interrupts in half since the control data is split

from the audio data. This circuit is comprised of

three independent sections which may individually be eliminated if not needed.

To load control data into the codec, three

HC597’s are utilized. These are both latches that

store the DSP-sent control data, and shift registers that shift the data into the codec. The codec

uses an inverted SSYNC signal to copy the

latches to the shift registers every frame. In this

diagram the DSP is assumed to have a data bus

bandwidth of at least 24 bits. If the DSP has less

than 24_bits, the three HC597s must be split into

two addresses. Since the HC597 internal latches

are copied to the shift registers, the latches continually hold the DSP-sent data; therefore, the

SDOUT

SDIN

SSYNC

SCLK

CS4216

SM4

MF1:CDOUT

MF2:CDIN

MF4:CCS

MF3:CCLK

MF5:INT

RESET

MF6:F1

MF7:F2

MF8:F3

43

42

44

40

39

36

35

38

34

31

30

1

DSP

VD+

Micro-

Controller

Serial

Port

IRQ

2

General

Purpose

Port

Pins

DSP only needs to write data to the latches when

a change is desired.

The second section is comprised of an HC595

shift register and latch that is clocked by an inverted SCLK The data shifted into the HC595 is

transferred to the HC595’s latch by the SSYNC

signal. This HC595 captures the 8 bits prior to

the SSYNC signal (which is also MF4:CC S) going high. As shown in Figure 14, and assuming

the MF4:CCS (SSYNC) signal rises at bit 32,

the 8-bits prior to MF4:CCS rising are a copy of

all the important status bits. This allows one shift

register to capture all the important information.

The interrupt pin cannot reliably be used in this

configuration since the interrupt pin is cleared by

reading the control port which occurs asynchro-

SDOUT

SDIN

SSYNC

SCLK

CS4216

SM4

32 BPF

MF3:CCLK

MF4:CCS

MF5:INT

MF1:CDOUT

MF2:CDIN

RESET

MF6:F1

MF7:F2

MF8:F3

43

42

44

35

36

38

40

39

34

31

30

1

VD+

2

Hard Wired or

DIP Switch

DSP

selectable

Figure 15. SM4 - Microcontr oller Interface

DS83F2 23

Figure 16. SM4 - Minimum DSP Interface

Page 24

CS4216

SDOUT

SDIN

SSYNC

SCLK

MF3:CCLK

MF4:CCS

MF5:INT

MF2:CDIN

43

42

1

44

35

36

38

39

DOUT

LOAD

DSP

VD+

HC597 HC597 HC597

DIN

CS4216

SM4

32 BPF

MF1:CDOUT

RESET

MF6:F1

MF7:F2

MF8:F3

40

2

34

31

30

SCLK

LCLK

AIN

HC595

HC574

OE

A

B

C

D

E

F

G

H

0

ADV

DI1

RCL

LCL

ERR0

ERR1

0

CS_STATUS

CS_FS

Figure 17. SM4 - Enhanced DSP Interface

CS_CONTROL

24+ bit DSP Data Bus

24 DS83F2

Page 25

CS4216

nously (every audio frame) with respect to the

interrupt occurrence.

The third section is only needed if sample frequencies need to be changed. This section is

comprised of an HC574 octal latch that can be

replaced by general purpose port pins if available. This section controls the sample frequency

selection bits: MF6:F1, MF7:F2, MF8:F3 and

the RESET pin. The codec must be reset when

changing sample frequencies.

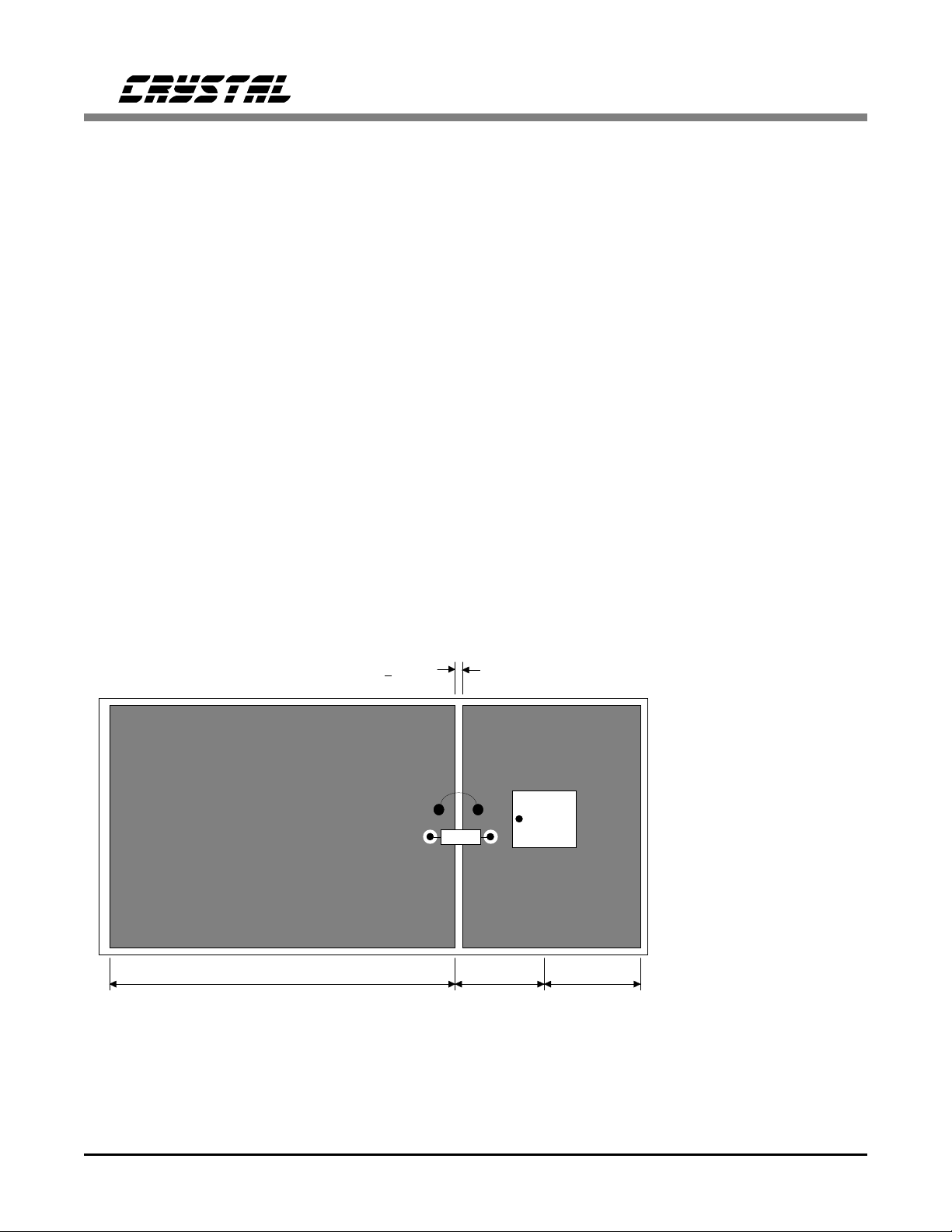

Power Supply and Grounding

The CS4216, along with associated analog circuitry, should be positioned in an isolated section

of the circuit board, and have its own, separate,

ground plane. On the CS4216, the analog and

digital grounds are internally connected; therefore, the AGND and DGND pins must be

externally connected with no impedance between

them. The best solution is to place the entire

chip on a solid ground plane as shown in Figure 18. Preferably, it should also have its own

power plane. The +5V supply must be connected

to the CS4216 via a ferrite bead, positioned

closer than 1" to the device. The VA supply can

be derived from VD, as shown in Figure 1. Alternatively, a separate +5V analog supply may be

used for VA, in which case, the 2.0 Ω resistor

between VA and VD should be removed. A single connection between the CS4216 ground

(analog ground) and the board digital ground

should be positioned as shown in Figure 18.

Figure 19 illustrates the optimum ground and decoupling layout for the CS4216 assuming a

surface-mount socket and leaded decoupling capacitors. Surface-mount sockets are useful since

the pad locations are identical to the chip pads;

therefore, assuming space for the socket is left

on the board, the socket can be optional for production. Figure 19 depicts the top layer,

containing signal traces, and assumes the bottom

or inter-layer contains a fairly solid ground

plane. The important points are that there i s solid

ground plane under the codec on the same layer

as the codec and it connects all ground pins with

thick traces providing the absolute lowest impedance between ground pins. The decoupling

capacitors are placed as close as possible to the

device which, in this case, is the socket boundary. The lowest value capacitor is placed closest

to the codec. Vias are placed near the AGND and

DGND pins, under the IC, and should attach to

the solid ground plane on another layer. The

negative side of the decoupling capacitors should

also attach to the same solid ground plane.

Traces and vias bringing power to the codec

should be large, which minimizes the impedance.

Although not shown in the figures, the trace layers (top layer in the figures) should have ground

plane fill in-between the traces to minimize coupling into the analog section. See the CDB4216

evaluation board as an example.

If using all surface-mount components, the decoupling capacitors should be placed on the

same layer as the codec and in the positions

shown in Figure 20. The vias shown are assumed

to attach to the appropriate power and ground

layers. Traces and vias bringing power to the

codec should be as large as possible to minimize

the impedance.

If using a through-hole socket, effort should be

made to find a socket with minimum height,

DS83F2 25

Page 26

which will minimize the socket impedance.

When using a through hole socket, the vias under the codec in Figure 19 are not needed since

the pins serve the same function.

ADC and DAC Filter Response Plots

Figures 21 - 26 shows the overall frequency response, passband ripple and transition band for

the CS4216 ADCs and DACs. Figure 27 shows

the DACs’ deviation from linear phase.

Fs is defined as the selected sample frequency

and is also the SSYNC frequency. Since the

sample frequency is programmable, the filters

will adjust to the selected sample frequency.

CS4216

Digital

Ground

Plane

CPU & Digital

Logic

>1/8"

Analog

Ground

Ground

Connection

+5V

Ferrite

Bead

Figure 18. CS4216 Board Layout Guideline

CS4216

Codec

digital

signals

Plane

Codec

analog

signals &

Components

Note that the CS4216

is oriented with its

digital pins towards the

digital end of the board.

26 DS83F2

Page 27

CS4216

1.0 uF

+

Analog

1

Supply

Digital

Supply

1.0 uF

+

0.1 uF

+

10 uF

0.1 uF 0.1 uF

Figure 19. CS42 16 Deco upling Layout Guideline

+

Analog

Supply

Digital

Supply

+

1.0 uF

1

0.1 uF 0.1 uF

+

0.1 uF

1.0 uF

10 uF

Figure 20. CS4216 Surface Mount Decoupling Layout

DS83F2 27

Page 28

CS4216

10

0

-10

-20

-30

-40

-50

Magnitude (dB)

-60

-70

-80

-90

-100

0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

Input Frequency (Fs)

Figure 21. CS4216 ADC Frequency Response

0

-10

-20

-30

-40

-50

Magnitude (dB)

-60

-70

-80

-90

-100

0.40 0.42 0.44 0.46 0.48 0.50 0.52 0.54 0.56 0.58 0.60

Input Frequency (Fs)

0.6

0.4

0.2

-0.0

-0.2

Magnitude (dB)

-0.4

-0.6

-0.8

-1.0

-1.2

0.00 0.05 0.10 0.15 0.20 0.25 0.30 0.35 0.40 0.45 0.50

Input Frequency (Fs)

Figure 22. CS4216ADC Passband Ripple

10

0

-10

-20

-30

-40

-50

Magnitude (dB)

-60

-70

-80

-90

-100

0.0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1.0

Input Frequency (Fs)

Figure 23. CS4216 ADC Transition Band

0.2

0.1

-0.0

-0.1

-0.2

-0.3

Magnitude (dB)

-0.4

-0.5

-0.6

-0.7

-0.8

0.00 0.05 0.10 0.15 0.20 0.25 0.30 0.35 0.40 0.45 0.50

Input Frequency (Fs)

Figure 25. CS4216 DAC Passband Ripple

Figure 24. CS4216 DAC Frequency Response

0

-10

-20

-30

-40

-50

Magnitude (dB)

-60

-70

-80

-90

-100

0.40 0.42 0.44 0.46 0.48 0.50 0.52 0.54 0.56 0.58 0.60

Input Frequency (Fs)

Figure 26. CS4216 DAC Transition Band

28 DS83F2

Page 29

2.5

2.0

1.5

1.0

0.5

0.0

-0.5

Phase (degrees)

-1.0

-1.5

-2.0

-2.5

0.00 0.05 0.10 0.15 0.20 0.25 0.30 0.35 0.40 0.45 0.50

Input Frequency (Fs)

Figure 27. CS4216 DAC Deviation from Linear Phase

CS4216

DS83F2 29

Page 30

PIN DESCRIPTIONS

SSYNC

RESET SCLK

CLKIN SDOUT

VD SDIN

DGND SMODE3

NC MF1:DO4/F1/CDOUT

NC MF2:DO3/F2/CDIN

NC MF5:DO2/INT

NC DO1

NC MF4:DI4/MA/CCS

NC MF3:DI3/F3/CCLK

NC MF6:DI2/F1

PDN DI1

NC SMODE2

ROUT MF7:SFS1/F2

LOUT MF8:SFS2/F3

44

1

2

3

4

5

6

7

8

9

10

11 23

12 14 16 18 20 22

4042 343638

CS4216

44-PIN

TQFP

(Q)

Top View

33

32

31

30

29

28

27

26

25

24

NC SMODE1

NC LIN2

NC LIN1

REFBUF RIN2

REFBYP RIN1

REFGND VA

AGND

CS4216

SM MF1 MF2 MF3 MF4 MF5 MF6 MF7 MF8

1 DO4 DO3 DI3 DI4 DO2 DI2 SFS1 SFS2

2 DO4 DO3 DI3 DI4 DO2 DI2 SFS1 SFS2

3 F1F2F3MADO2DI2SFS1SFS2

4-SL CDOUT CDIN CCLK CCS INT F1 SFS1 SFS2

4-MA CDOUT CDIN CCLK CCS INTF1F2F3

30 DS83F2

Page 31

SSYNC

RESET SCLK

CLKIN SDOUT

VD SDIN

DGND SMODE3

NC MF1:DO4/F1/CDOUT

NC MF2:DO3/F2/CDIN

NC MF5:DO2/INT

NC DO1

NC MF4:DI4/MA/CCS

NC MF3:DI3/F3/CCLK

NC MF6:DI2/F1

PDN DI1

NC SMODE2

ROUT MF7:SFS1/F2

LOUT MF8:SFS2/F3

7

8

9

10

11

12

13

14

15

16

17 29

18 20 22 24 26 28

1246404244

CS4216

CS4216

44-PIN

44-PIN

PLCC

PLCC

(L)

(L)

Top View

Top View

39

38

37

36

35

34

33

32

31

30

NC SMODE1

NC LIN2

NC LIN1

REFBUF RIN2

REFBYP RIN1

REFGND VA

AGND

CS4216

SM MF1 MF2 MF3 MF4 MF5 MF6 MF7 MF8

1 DO4 DO3 DI3 DI4 DO2 DI2 SFS1 SFS2

2 DO4 DO3 DI3 DI4 DO2 DI2 SFS1 SFS2

3 F1F2F3MADO2DI2SFS1SFS2

4-SL CDOUT CDIN CCLK CCS INT F1 SFS1 SFS2

4-MA CDOUT CDIN CCLK CCS INTF1F2F3

Power Supply

VD - Digital +5V Supply, PIN 4(L), 42(Q).

+5V digital supply.

VA - Analog +5V Supply, PIN 24(L), 18(Q).

+5V analog supply.

DGND - Digital Ground, PIN 5(L), 43(Q).

Digital ground. Must be connected to AGND with zero impedance.

DS83F2 31

Page 32

AG ND - Analog Ground, PIN 23(L), 17(Q).

Analog ground. Must be connected to DGND with zero impedance.

Analog Inputs

RIN1 - Right Input #1, PIN 25(L), 19(Q).

Right analog input #1. Full scale input, with no gain, is 1 Vrms, centered at REFBUF.

RIN2 - Right Input #2, PIN 26(L), 20(Q).

Right analog input #2. Full scale input, with no gain, is 1 Vrms, centered at REFBUF.

LIN1 - Left Input #1, PIN 27(L), 21(Q).

Left analog input #1. Full scale input, with no gain, is 1 Vrms, centered at REFBUF.

LIN2 - Left Input #2, PIN 28(L), 22(Q).

Left analog input #2. Full scale input, with no gain, is 1 Vrms, centered at REFBUF.

Analog Outputs

ROUT - Right Channel Output, PIN 15(L), 9(Q).

Right channel analog output. Maximum signal is 1 Vrms centered at REFBUF.

CS4216

LOUT - Left Channel Output, PIN 16(L), 10(Q).

Left channel analog output. Maximum signal is 1 Vrms centered at REFBUF.

REFBYP - Analog Reference Decoupling, PIN 21(L), 15(Q).

A 10 µF and 0.1 µF capacitor must be attached between REFBYP and REFGND.

REFGND - Analog Reference Ground Connection, PIN 22(L), 16(Q).

Connect to AGND.

REFBUF - Buffered Reference Out, PIN 20(L), 14(Q).

A nominal +2.2 V output for setting the bias level for external analog circuits.

Serial Digital Audio Interface Si gnals

SDIN - Serial Port Data In, PIN 42(L), 36(Q).

Digital audio data to the DACs and level control information is received by the CS4216 via

SDIN.

SDOUT - Serial Port Data Out, PIN 43(L), 37(Q).

Digital audio data from the ADCs and status information is output from the CS4216 via

SDOUT.

SCLK - Serial Port Bit Clock, PIN 44(L), 38(Q).

SCLK controls the digital audio data on SDOUT and latches the data on SDIN.

32 DS83F2

Page 33

SSYNC - Serial Port Sync Signal, PIN 1(L), 39(Q).

Indicates the start of a digital audio frame in SM3 and SM4, and also the start of a word in

SM1 & SM2.

SMODE1 - Serial Mode Select, PIN 29(L), 23(Q).

One of three pins that select the serial mode and function of the multifunction pins.

SMODE2 - Serial Mode Select, PIN 32(L), 26(Q).

One of three pins that select the serial mode and function of the multifunction pins.

SMODE3 - Serial Mode Select, PIN 41(L), 35(Q).

One of three pins that select the serial mode and function of the multifunction pins. This pin

has an internal pull-down making this revision backwards compatible with a previous version

(Revision A or Version3-Version0 bits = 0000).

Multifunction Digital Pins

MF1:DO4 - Parallel Digital Bit Output #4 in SM1/SM2, PIN 40(L), 34(Q).

In serial modes 1 and 2 this pin reflects the value of the DO4 bit in the sub-frame.

MF1:F1 - Format bit 1 in SM3, PIN 40(L), 34(Q).

In serial mode 3 this pin is a format bit and is used as one of three sample frequency select pins

when in master mode, or as one of two bits-per-frame select pins when in slave mode.

CS4216

MF1:CDOUT - Control Data Output in SM4, PIN 40(L), 34(Q).

In serial mode 4 this pin is the data output for the control port which contains status

information.

MF2:DO3 - Parallel Digital Bit Output #3 in SM1/SM2, PIN 39(L), 33(Q).

In serial modes 1 and 2 this pin reflects the value of the DO3 bit in the sub-frame.

MF2:F2 - Format bit 2 in SM3, PIN 39(L), 33(Q).

In serial mode 3 this pin is a format bit and is used as one of three sample frequency select pins

when in master mode, or as one of two bits-per-frame select pins when in slave mode.

MF2:CDIN - Control Data Input in SM4, PIN 39(L), 33(Q).

In serial mode 4 this pin is the control port data input which contains data such as gain and

attenuation settings as well as input select, mute, and digital output bits.

MF3:DI3 - Parallel Digital Bit Input #3 in SM1/SM2/SM3 (Slave), PIN 35(L), 29(Q).

In serial modes 1 and 2 this pin value is reflected in the DI3 bit in the sub-frame.

MF3:F3 - Format bit 3 in SM3 (Master), PIN 35(L), 29(Q).

In serial mode 3 this pin is a format bit and is used as one of three sample frequency select pins

when in master mode. In slave mode, the pin reverts to being a general purpose input.

MF3:CCLK - Control Data Clock in SM4, PIN 35(L), 29(Q).

In serial mode 4 this pin is the control port serial bit clock which latches data from CDIN on

the falling edge, and outputs data onto CDOUT on the rising edge.

DS83F2 33

Page 34

MF4:DI4 - Parallel Digital Bit Input #4 in SM1/SM2, PIN 36(L), 30(Q).

In serial modes 1 and 2 this pin value is reflected in the DI4 bit in the sub-frame.

MF4:MA - Master Sub-Mode in SM3, PIN 36(L), 30(Q).

In serial mode 3 this pin selects either master or slave mode. When MF4:MA = 1, the codec is

in master mode and outputs SSYNC and SCLK. When MF4:MA = 0, the codec is in slave

mode and receives SSYNC and SCLK from an external source that must be frequency locked to

CLKIN.

MF4:CCS - Control Data Chip Select in SM4, PIN 36(L), 30(Q).

In serial mode 4 this pin is the control port chip select signal. When low, the control port data is

clocked in CDIN and status data is output on CDOUT. When CCS goes high, control data is

latched internally. This data remains active until new data is clocked in. The control port may

also be asynchronous to the audio data port.

MF5:DO2 - Parallel Digital Bit Output #2 in SM1/SM2/SM3, PIN 38(L), 32(Q).

In serial modes 1, 2, and 3 this pin reflects the value of the DO2 bit in the sub-frame.

MF5:INT - Interrupt in SM4, PIN 38(L), 32(Q).

In serial mode 4 this pin is an active low interrupt signal that is maskable using the MSK bit in

the control port serial data stream. INT is an open-collector output and requires and external

pull-up resistor. Assuming the mask bit is not set, and interrupt is triggered by a change in ADV

or DI1, or a rising edge on LCL or RCL, or a exiting an SCLK out of range condition

(Error = 3)

CS4216

MF6:DI2 - Parallel Digital Bit Input #2 in SM1/SM2/SM3, PIN 34(L), 28(Q).

In serial modes 1, 2, and 3 this pin value is reflected in the DI2 bit of the sub-frame.

MF6:F1 - Format Bit 1 in SM4, PIN 34(L), 28(Q).

In serial mode 4 this pin is a format bit and is used as one of three sample frequency select pins

when in master mode. In slave mode, MF6:F1 helps determine the number of sub-frames within

a frame.

MF7:SFS1 - Sub-Frame Select 1 in SM1/SM2/SM3/SM4-SL, PIN 31(L), 25(Q).

In serial modes 1, 2, and 3, MF7:SFS1 helps select the sub-frame that this particular CS4216 is

allocated. In slave sub-mode of serial mode 4, this pin is one of two pins used as a sub-frame

select when MF6:F1 = 1 (128-bit frames). When MF6:F1 = 0, this pin is used to select the

frame sizes of 32 or 64 bits.

MF7:F2 - Format Bit 2 in SM4-MA, PIN 31(L), 25(Q).

In master sub-mode of serial mode 4, this pin is used as one of three sample frequency select

pins.

MF8:SFS2 - Sub-Frame Select 2 in SM1/SM2/SM3/SM4-SL, PIN 30(L), 24(Q).

In serial modes 1, 2, 3, and slave sub-mode of 4, MF8:SFS2 helps select the sub-frame that this

particular CS4216 is allocated.

MF8:F3 - Format Bit 3 in SM4-MA, PIN 30(L), 24(Q).

In master sub-mode of serial mode 4, this pin is a format bit and is one of three sample

frequency select pins.

34 DS83F2

Page 35

Miscellaneous

RESET - Reset Input, PIN 2.(L), 40(Q).

Resets the CS4216 into a known state, and must be initiated after power-up or power-down

mode. Releasing RESET caused the CS4216 to initiate a calibration sequence. RESET should

also be initiated when changing sample frequencies in any master sub-mode.

CLKIN - Master Clock, PIN 3(L), 41(Q).

CLKIN is the master clock that operates the internal logic. In serial mode 1,