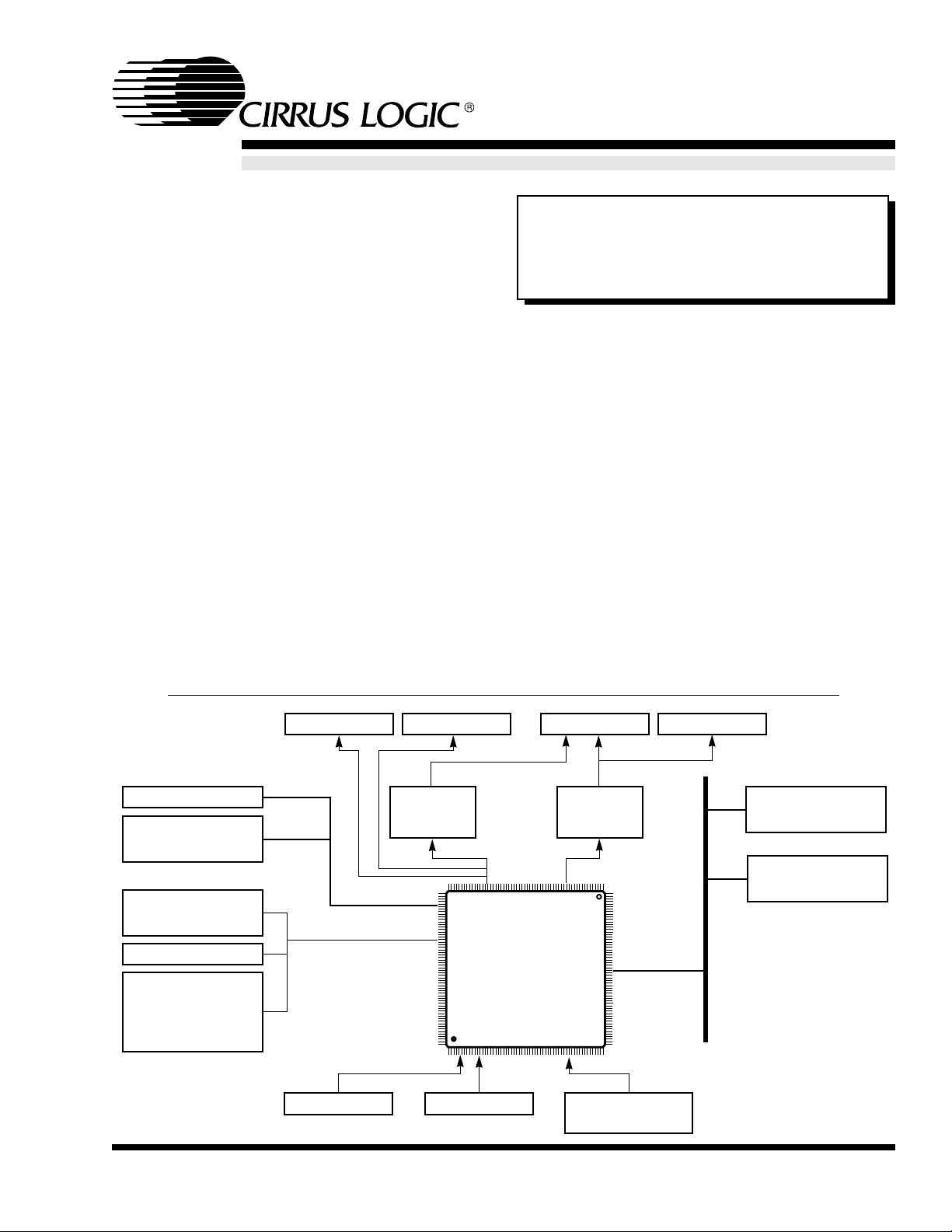

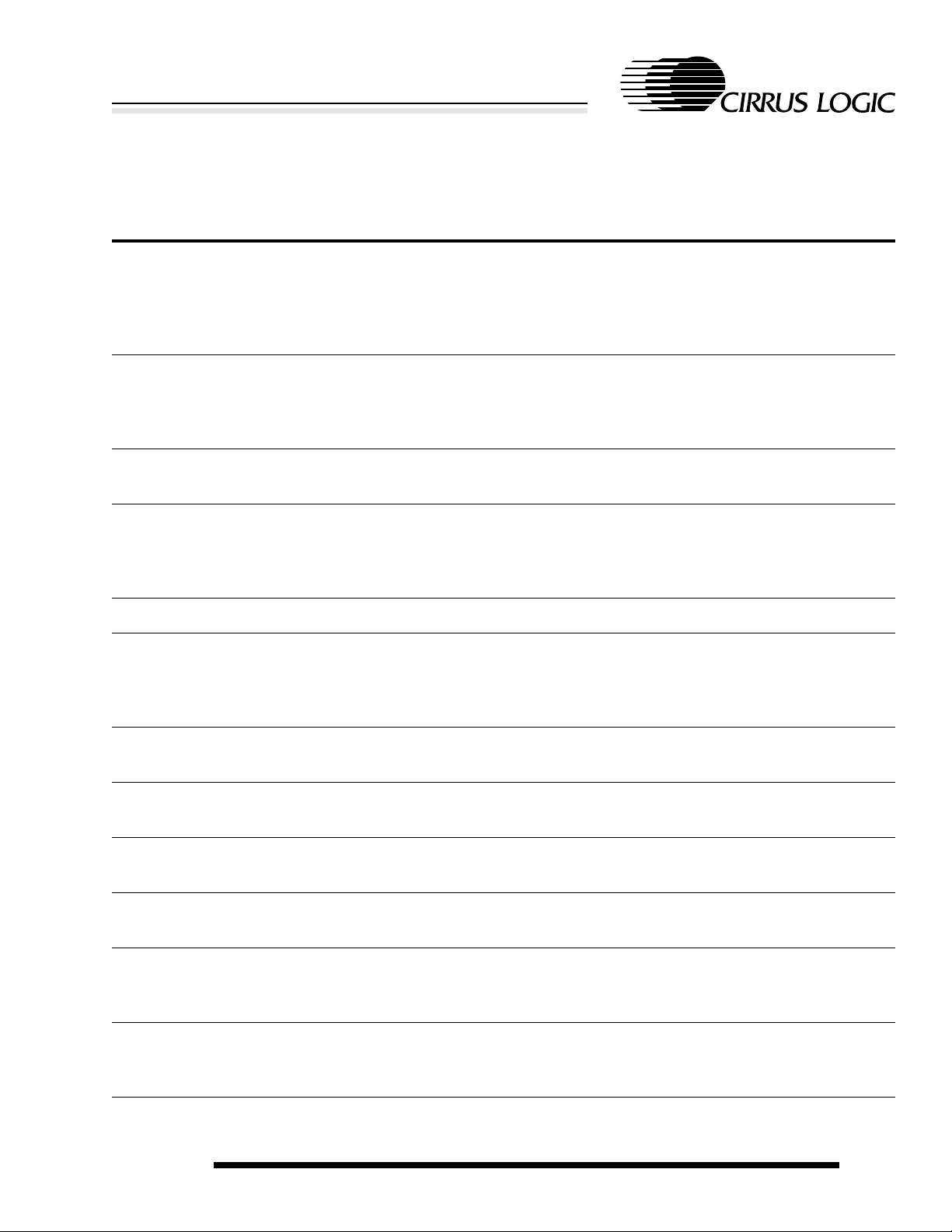

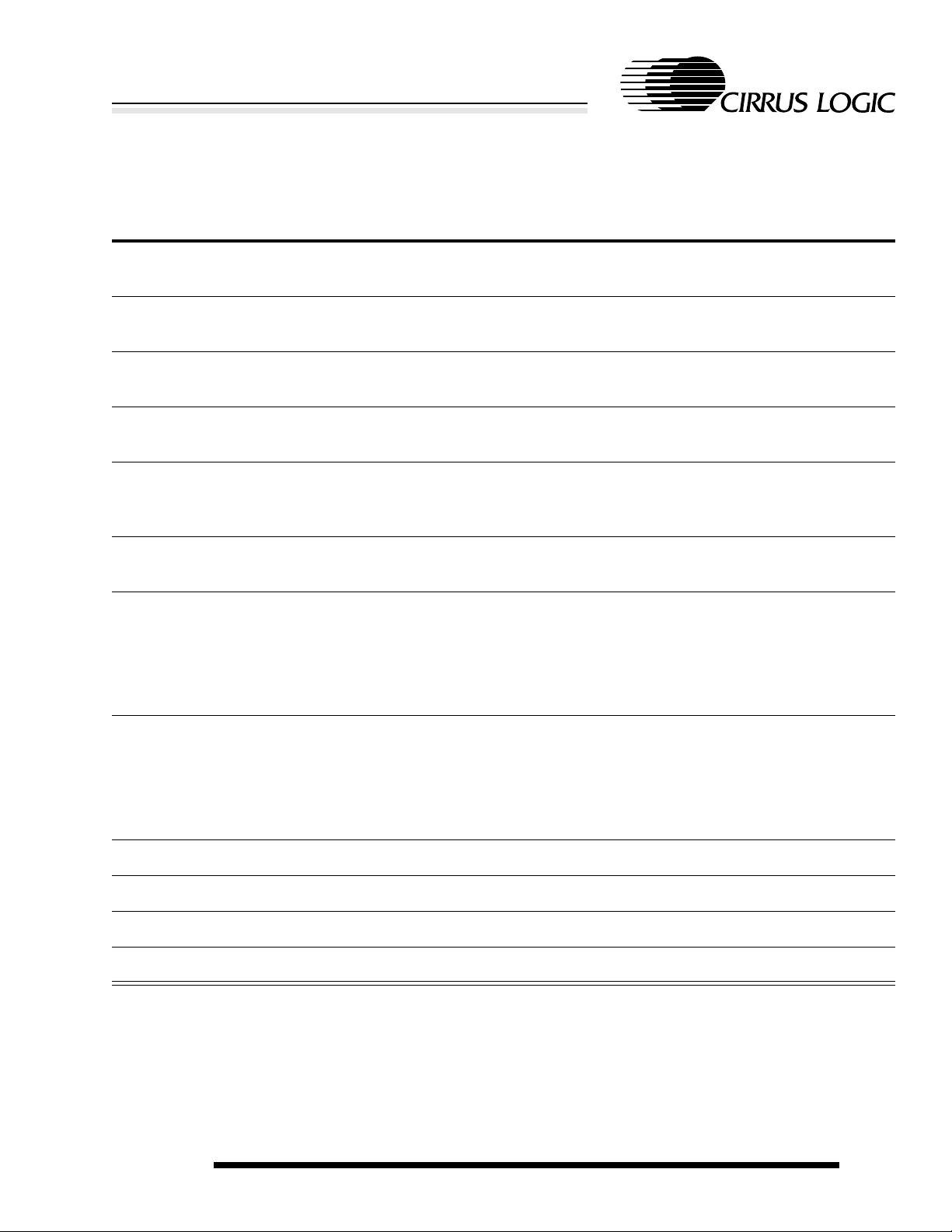

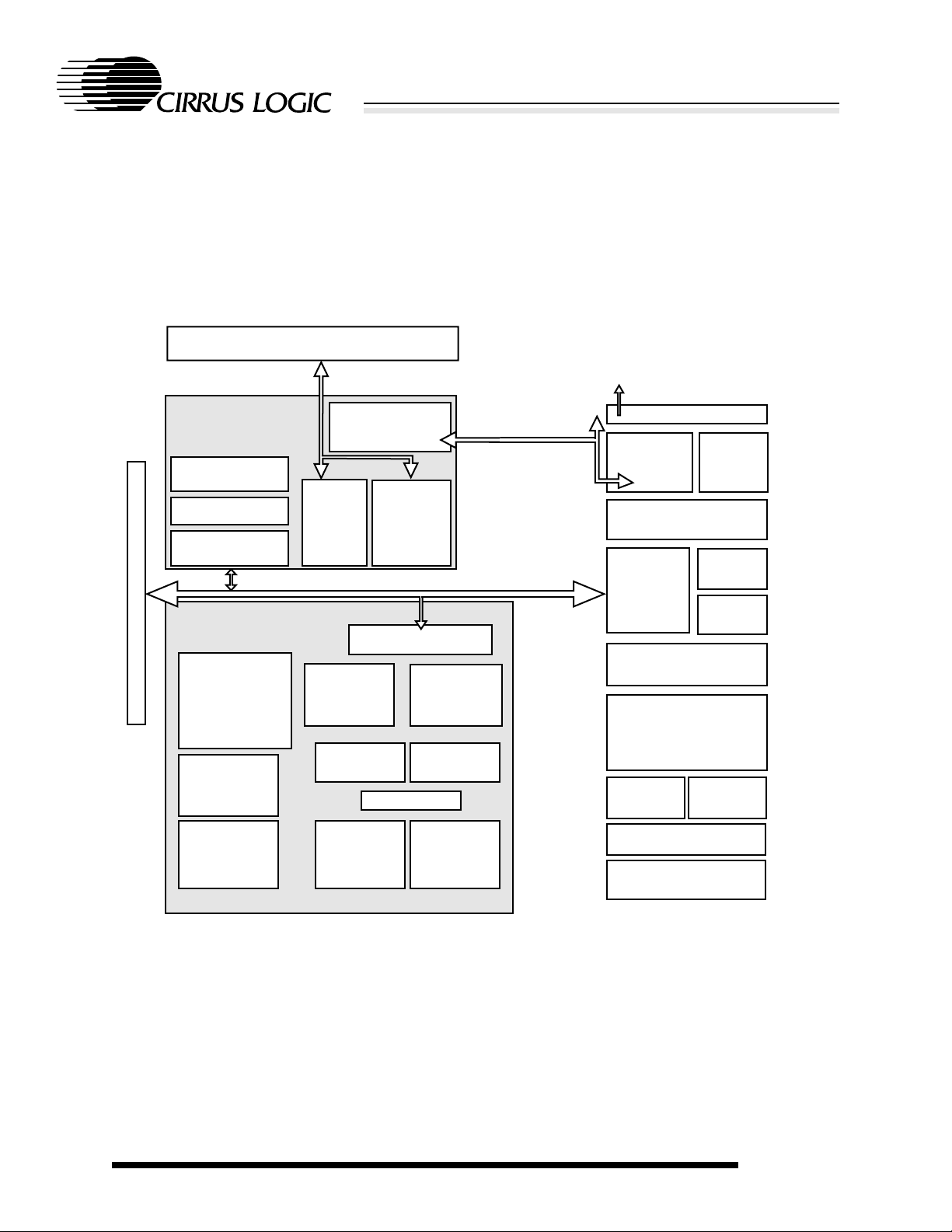

COLOR LCD

SVGA MONITOR

TV

HEADPHONES

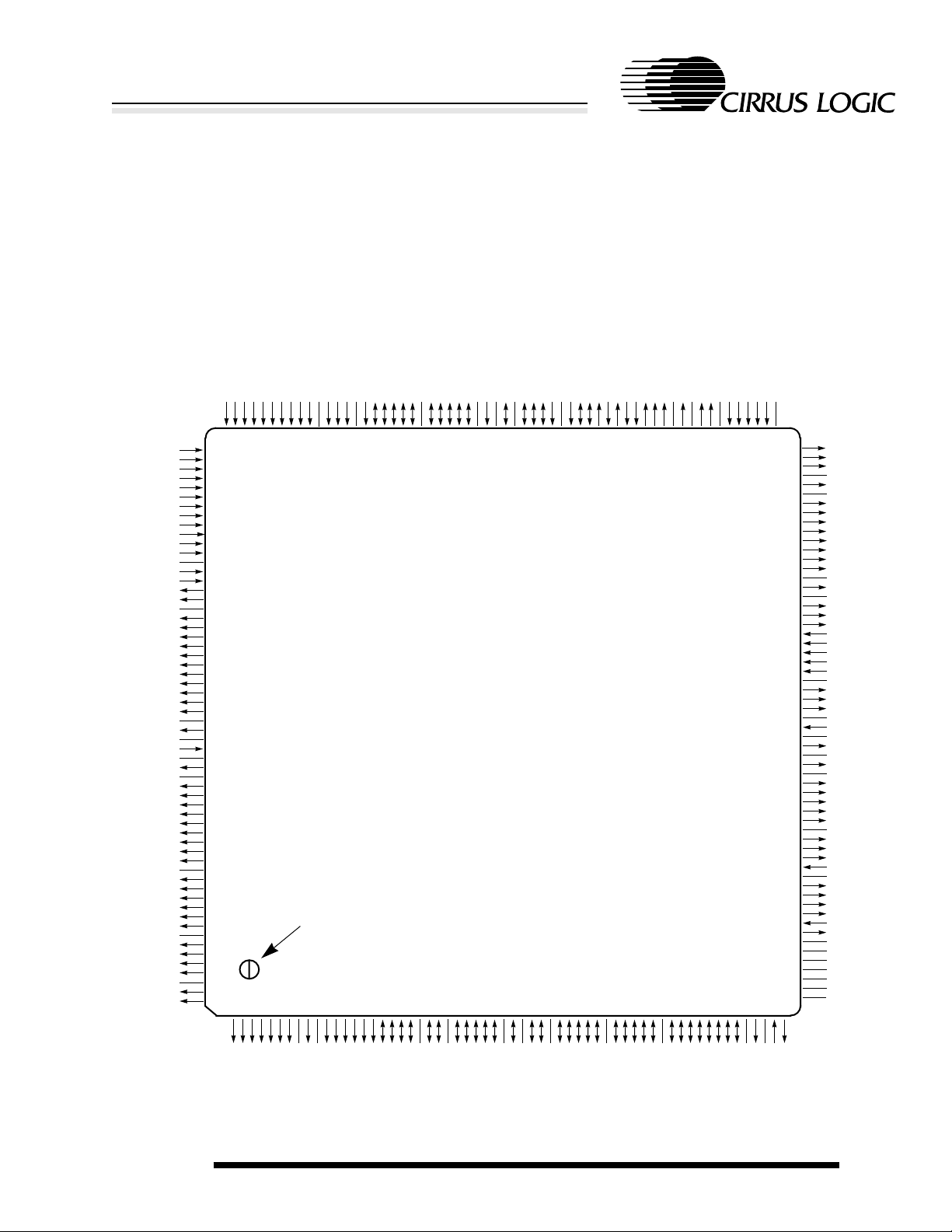

CL-PS7500FE

240-PIN PQFP

2*PS/2 PORTS

2 ANALOG

INPUTS

VIDEO O/P

(RGB)

AUDIO O/P

(32 BIT)

KEYBOARD MOUSE

GAMES DEVICE

(ANALOG)

FRONT PANEL:

STATUS LEDs

RUN/STANDBY SW

REALTIME CLOCK

CONFIG. MEMORY

(NON-VOL.)

DRAM

(4 MBYTE, TYP)

ROM

56k MODEM

CL-MD34XX

ETHERNET

CS89XX

ENCODER

PAL/NTSC

MEMORY BUS

I/O PORT

CD-DAC

CS4333

ISA-STYLE

BUS

■

■

■

■

CL-PS7500FE

Advance Data Book

FEATURES

Availab le in 56- and 40-MHz speed grades

System-on-a-chip solution

— 32-bit ARM7 processor with MMU

— 4K unified cache

— FPU (floating point unit)

— Graphics controller drives CRT or LCD

— CD-quality sound audio controller

— DRAM controller

— ROM/Flash controller

— Three-channel DMA for video, cursor, and sound

— PC-style I/O bus

— Two-state power management

— Eight general-purpose I/O lines

Performance

— 50 Vax -MIPS (Dhrystone

— Up to 12 Mflops, double-precision FP (LINPACK)

) at 56 MHz

FPU

— Implements ANSI/IEEE Std 754-1985

— Single, double, and e xtended precision

System-on-a Chip for

Internet Appliance

OVERVIEW

The Cirrus Logic CL-PS7500FE is designed to be

used in internet appliances such as the network

computer, smart-TV, intranet terminal, screen

phones, DVD play ers, and so on.

The massively integrated CL-PS7500FE offers a

complete system-on-a-chip solution that includes a

32-bit ARM CPU with cache and MMU, CRT and

LCD controller, memory controller , FPU, CD-quality

sound controller, interface to the Cirrus Logic DSP

device for 56K modem and speakerphone, and a

PC-type I/O bus. To handle streaming of audio and

video data on the Internet, the CL-PS7500FE

includes a double-precision FPU to accelerate

software codecs.

(cont.) (cont.)

Functional

Block Diagram

June 1997Version 2.0

■

■

■

■

■

CL-PS7500FE

System-on-a-Chip for Internet Appliance

FEATURES

CRT or color/monochrome LCDs

— Resolutions up to 1024 × 768

— 256-entry 28-bit video palette

— Single- and dual-scan panel LCDs (16-bit grayscale)

Serial CD digital sound (32-bit) output

Supports EDO and Fast page mode DRAMs

— Up to 132 Mbytes/sec. (peak) using 64-MHz memory

clock and 32-bit-wide DRAM

— Programmable 16- or 32-bit-wide memory system

— Speed-critical paths are pipelined

OVERVIEW

(cont.)

(cont.)

The video controller features RGB drive of a SVGA

monitor or a color LCD. It also incorporates various

sync inputs, which when combined with an external

encoder, permit the use of interlaced TV displays.

The device incorporates a digital audio controller

with a 32-bit serial interface for connection to the

Cirrus Logic, CS4333 CD-DAC device. The

CL-PS7500FE can also interface to the Cirrus Logic

56K, FastPath modem chipset ideal for Internet

access over a PO TS line .

PC-style I/O bus (40-MHz) for connection to any

Cirrus Logic peripheral device

— 56k fax/modem chipset

— CS89XX Ethernet controller

— Can be expanded to 32 bits with external transceivers

ROM/FLASH

— Supports two 16-Mbyte banks

— Individual read timings

— Burst mode reads

— Allows for writes under register control for FLASH

The CL-PS7500FE supports UMA (unified memory

architecture); EDO DRAMs can be used to achieve

high-memory bandwidth.

The CL-PS7500FE is the main computing engine in

the NC platform defined by Oracle

, and runs the

NC operating system and applications.

The device is available in a 240-pin PQFP (plastic

quad flat pack) package.

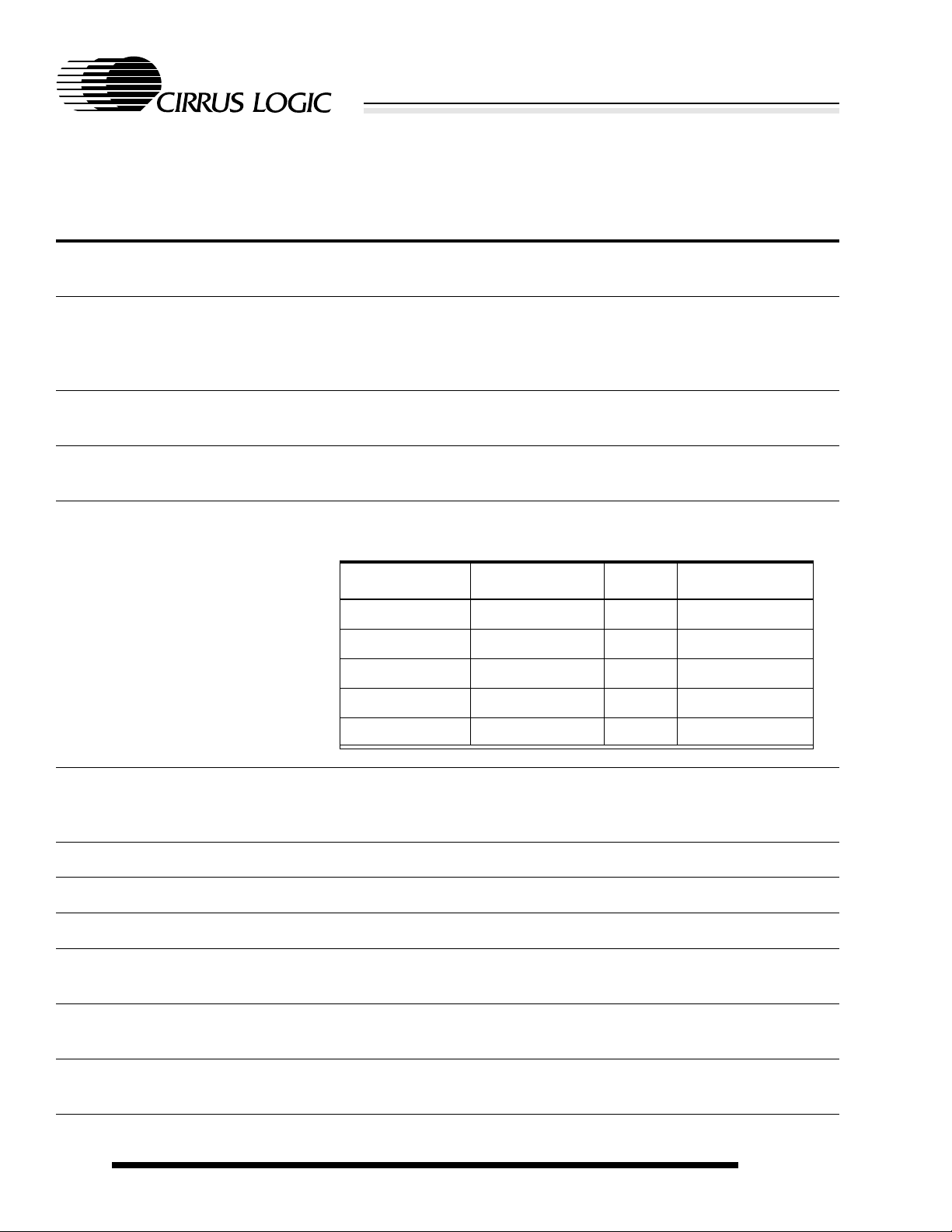

The CL-PS7500FE is availab le in two speed grades:

●

ARM CPU running at 40 MHz; memory clock

running up to 64 MHz

●

ARM CPU running at 56 MHz; memory clock

running up to 64 MHz

2

ADVANCE DATA BOOK v2.0

June 1997

CL-PS7500FE

System-on-a-Chip for Internet Appliance

3

ADVANCE DATA BOOK v2.0

June 1997

CL-PS7500FE

System-on-a-Chip for Internet Appliance

TABLE OF CONTENTS

CONVENTIONS .....................................................................................................................12

1. PIN INFORMATION...............................................................................................................13

1.1 Pin Diagram......................................................................................................................................13

1.2 Block Diagram..................................................................................................................................14

2. PIN DESCRIPTIONS.............................................................................................................15

2.1 CL-PS7500FE Pin Descriptions .......................................................................................................15

2.2 Power and Ground Pins....................................................................................................................22

2.3 Numerical Pin Listing........................................................................................................................24

3. FUNCTIONAL DESCRIPTION..............................................................................................27

3.1 Functional Block Diagram.................................................................................................................27

3.2 ARM Processor Macrocell................................................................................................................27

3.3 FPA Macrocell...................................................................................................................................27

3.4 Video and Sound Macrocell..............................................................................................................29

3.5 Clock Control and Power Management............................................................................................29

3.6 Memory System ...............................................................................................................................29

3.6.1 DMA..................................................................................................................................30

3.6.2 I/O Control........................................................................................................................30

3.7 Other Features .................................................................................................................................31

3.8 Test Modes.......................................................................................................................................31

3.9 Structure of the CL-PS7500FE.........................................................................................................31

3.9.1 Register Programming......................................................................................................32

3.9.2 Interaction Between Macrocells........................................................................................32

3.10 Resetting CL-PS7500FE Systems ...................................................................................................32

4. THE ARM PROCESSOR MA CROCELL..............................................................................33

4.1 Architecture ......................................................................................................................................33

4.2 Instruction Set ..................................................................................................................................33

4.3 Memory Interface..............................................................................................................................34

4.4 Clocks and Synchronous/Asynchronous Modes..............................................................................34

5. IDC .........................................................................................................................................35

5.1 Cacheable Bit...................................................................................................................................35

5.2 IDC Operation...................................................................................................................................35

5.2.1 IDC V alidity.......................................................................................................................35

5.2.2 Software IDC Flush...........................................................................................................35

5.2.3 Doubly-Mapped Space.....................................................................................................35

5.2.4 Read-Locked-Write...........................................................................................................36

5.3 IDC Enable/Disable and Reset.........................................................................................................36

5.3.1 Enable the IDC.................................................................................................................36

5.3.2 Disable the IDC.................................................................................................................36

5.4 Write Buffer (WB) .............................................................................................................................36

5.4.1 Bufferable Bit ....................................................................................................................36

5.4.2 Write Buffer Operation......................................................................................................36

5.4.3 Enable the Write Buffer.....................................................................................................37

5.4.4 Disable the Write Buffer....................................................................................................37

5.5 Coprocessors ...................................................................................................................................37

June 1997

ADVANCE DATA BOOK v2.0

TABLE OF CONTENTS

3

CL-PS7500FE

System-on-a-Chip for Internet Appliance

6. ARM PROCESSOR MMU.................................................................................................... 38

6.1 MMU Program-Accessible Registers................................................................................................38

6.1.1 Translation Table Base Register ......................................................................................39

6.1.2 Domain Access Control Register......................................................................................39

6.1.3 Fault Status Register........................................................................................................39

6.1.4 Fault Address Register.....................................................................................................39

6.2 Address Translation..........................................................................................................................39

6.3 Translation Process..........................................................................................................................40

6.3.1 TTB (Translation Table Base)............................................................................................40

6.3.2 Level One Fetch................................................................................................................40

6.3.3 Level One Descriptor........................................................................................................41

6.3.4 P age Table Descriptor.......................................................................................................41

6.3.5 Section Descriptor............................................................................................................42

6.4 Translating Section References........................................................................................................42

6.4.1 Lev el Two Descriptor.........................................................................................................42

6.5 Translating Small Page References..................................................................................................44

6.6 Translating Large Page References.................................................................................................45

6.7 MMU Faults and CPU Aborts...........................................................................................................47

6.8 Fault Address and Fault Status Registers (FAR, FSR).....................................................................47

6.9 Domain Access Control....................................................................................................................48

6.10 Fault-Checking Sequence................................................................................................................48

6.10.1 Alignment Fault.................................................................................................................49

6.10.2 Translation Fault................................................................................................................50

6.10.3 Domain Fault ....................................................................................................................50

6.10.4 Permission Fault...............................................................................................................50

6.11 External Aborts.................................................................................................................................50

6.11.1 Interaction of the MMU, IDC, and Write Buffer..................................................................51

7. REGISTER DESCRIPTIONS................................................................................................ 52

7.1 Register Configuration......................................................................................................................52

7.1.1 Big and Little Endian (the Bigend Bit)...............................................................................52

7.1.2 Configuration Bits for Backward Compatibility..................................................................53

7.2 Operating Mode Selection................................................................................................................54

7.3 Registers ..........................................................................................................................................55

7.3.1 PSRs (Program Status Registers)....................................................................................56

7.4 Exceptions........................................................................................................................................57

7.4.1 FIQ....................................................................................................................................57

7.4.2 IRQ...................................................................................................................................58

7.4.3 Abort.................................................................................................................................58

7.4.4 Software Interrupt.............................................................................................................59

7.4.5 Undefined Instruction Trap................................................................................................60

7.4.6 Vector Summary...............................................................................................................60

7.4.7 Exception Priorities...........................................................................................................61

7.4.8 Interrupt Latencies............................................................................................................61

7.4.9 Reset................................................................................................................................61

7.5 Configuration Control Registers .......................................................................................................62

7.5.1 Backward Compatibility ....................................................................................................62

7.5.2 Internal Coprocessor Instructions.....................................................................................62

7.5.3 Registers ..........................................................................................................................63

7.6 Register 1: Control (Write only)........................................................................................................64

4

TABLE OF CONTENTS

ADVANCE DATA BOOK v2.0

June 1997

CL-PS7500FE

System-on-a-Chip for Internet Appliance

7.7 Register 2: Level One Page Table (Write only).................................................................................64

7.8 Register 3: Domain Access Control (Write only)..............................................................................64

7.9 Register 4: Reserved........................................................................................................................64

7.10 Register 5: Fault Status/Translation Lookaside Buffer Flush ............................................................65

7.11 Register 6: Fault Address/TLB Purge...............................................................................................65

7.12 Register 7: IDC Flush (Write only)....................................................................................................65

7.13 Registers 8–15: Reserved................................................................................................................65

8. MEMORY MAP......................................................................................................................66

9. MEMORY SUBSYSTEMS.....................................................................................................67

9.1 ROM Interface..................................................................................................................................67

9.1.1 ROM Bank Configuration and Timing ...............................................................................68

9.2 DRAM Interface................................................................................................................................69

9.2.1 DRAM Control Registers..................................................................................................69

9.2.2 DRAM Address Multiplexing............................................................................................70

9.2.3 Selection Between 16- and 32-bit DRAM.........................................................................70

9.2.4 EDO and Timing Mode Selection .....................................................................................71

9.2.5 DRAM Refresh..................................................................................................................72

9.2.6 DRAM Self-Refresh..........................................................................................................73

9.2.7 Non-Sequential Access Time and RAS Precharge ..........................................................73

9.3 DMA Channels .................................................................................................................................74

9.3.1 Video DMA.......................................................................................................................74

9.3.2 Cursor DMA.....................................................................................................................75

9.3.3 Sound DMA.....................................................................................................................75

9.3.4 The Sound DMA State Machine.......................................................................................76

10. MEMORY AND I/O PROGRAMMERS’ MODEL...................................................................78

10.1 Introduction.......................................................................................................................................78

10.2 Register Summary............................................................................................................................78

10.3 Register Descriptions .......................................................................................................................81

10.3.1 IOCR (0x00) — I/O Control...............................................................................................81

10.3.2 KBDDAT (0x04) — Keyboard Data...................................................................................81

10.3.3 KBDCR (0x08) — Keyboard Control.................................................................................82

10.3.4 IOLINES (0x0C) — IOP[7:0] Port Control.........................................................................83

10.3.5 IRQSTA (0x10) — IRQ A Interrupts Status.......................................................................83

10.3.6 IRQRQA (0x14) — IRQ A Interrupts Request/Clear.........................................................84

10.3.7 IRQMSKA (0x18) — IRQ A Interrupts Mask.....................................................................84

10.3.8 SUSMODE (0x1C) — SUSPEND Mode...........................................................................85

10.3.9 IRQSTB (0x20) — IRQ B Interrupts Status ......................................................................85

10.3.10 IRQRQB (0x24) — IRQ B Interrupts Request ..................................................................86

10.3.11 IRQMSKB (0x28) — IRQ B Interrupts Mask.....................................................................86

10.3.12 STOPMODE (0x2C) — STOP Mode................................................................................87

10.3.13 FIQST (0x30) — FIQ Interrupts Status.............................................................................87

10.3.14 FIQRQ (0x34) — FIQ Interrupts Request.........................................................................87

10.3.15 FIQMSK (0x38) — FIQ Interrupts Mask ...........................................................................88

10.3.16 CLKCTL (0x3C) — Clock Control.....................................................................................88

10.3.17 T0low (0x40) — Timer 0 Low Bits.....................................................................................89

10.3.18 T0high (0x44) — Timer 0 High Bits...................................................................................89

10.3.19 T0GO (0x48) — Timer 0 Go Command............................................................................89

10.3.20 T0LAT (0x4C) — Timer 0 Latch Command.......................................................................89

June 1997

ADVANCE DATA BOOK v2.0

TABLE OF CONTENTS

5

CL-PS7500FE

System-on-a-Chip for Internet Appliance

10.3.21 T1low (0x50) — Timer 1 Low Bits.....................................................................................89

10.3.22 T1high (0x54) — Timer 1 High Bits ..................................................................................89

10.3.23 T1GO (0x58) — Timer 1 Go Command............................................................................90

10.3.24 T1LAT (0x5C) — Timer 1 Latch Command ......................................................................90

10.3.25 IRQSTC (0x60) — IRQ C Interrupts Status......................................................................90

10.3.26 IRQRQC (0x64) — IRQ C Interrupts Request..................................................................90

10.3.27 IRQMSKC (0x68) — IRQ C Interrupts Mask ....................................................................90

10.3.28 VIDMUX (0x6C) — Video LCD and Serial Sound MUX Control.......................................91

10.3.29 IRQSTD (0x70) — IRQ D Interrupts Status......................................................................91

10.3.30 IRQRQD (0x74) — IRQ D Interrupts Request..................................................................92

10.3.31 IRQMSKD (0x78) — IRQ D Interrupts Mask ....................................................................92

10.3.32 ROMCR1:0 (0x80 and 0x84) — ROM Control..................................................................93

10.3.33 REFCR (0x8C) — Refresh Period....................................................................................94

10.3.34 ID0 (0x94) — Chip ID Number (Low Byte) .......................................................................94

10.3.35 ID1 (0x98) — Chip ID Number (High Byte) ......................................................................94

10.3.36 VERSION (0x9C) — Chip Version Number......................................................................94

10.3.37 MSEDAT (0xA8) — Mouse Data.......................................................................................94

10.3.38 MSECR (0xAC) — Mouse Control....................................................................................95

10.3.39 IOTCR (0xC4) — I/O Timing Control ................................................................................95

10.3.40 ECTCR (0xC8) — I/O Expansion Card Timing Control....................................................95

10.3.41 ASTCR (0xCC) — I/O Asynchronous Timing Control.......................................................96

10.3.42 DRAMCR (0xD0) — DRAM Control .................................................................................96

10.3.43 SELFREF (0xD4) — DRAM Self-Refresh Control............................................................97

10.3.44 ATODICR (0xE0) — A-to-D Interrupt Control ...................................................................97

10.3.45 ATODSR (0xE4) — A-to-D Status ....................................................................................98

10.3.46 ATODCC (0xE8) — A-to-D Convertor Control..................................................................98

10.3.47 ATODCNT1 (0xEC) — A-to-D Counter 1..........................................................................99

10.3.48 ATODCNT2 (0xF0) — A-to-D Counter 2...........................................................................99

10.3.49 ATODCNT3 (0xF4) — A-to-D Counter 3...........................................................................99

10.3.50 ATODCNT4 (0xF8) — A-to-D Counter 4...........................................................................99

10.3.51 SDCURA (0x180) — Sound DMA Current A....................................................................99

10.3.52 SDENDA (0x184) — Sound DMA End A........................................................................100

10.3.53 SDCURB (0x188) — Sound DMA Current B..................................................................100

10.3.54 SDENDB (0x18C) — Sound DMA End B.......................................................................101

10.3.55 SDCR (0x190) — Sound DMA Control...........................................................................102

10.3.56 SDST (0x194) — Sound DMA Status.............................................................................102

10.3.57 CURSCUR (0x1C0) — Cursor DMA Current .................................................................103

10.3.58 CURSINIT (0x1C4) — Cursor DMA INIT........................................................................103

10.3.59 VIDCURB (0x1C8) — Duplex LCD Video DMA Current B .............................................103

10.3.60 VIDCURA (0x1D0) — Video DMA Current A..................................................................104

10.3.61 VIDEND (0x1D4) — Video DMA End.............................................................................104

10.3.62 VIDSTART (0x1D8) — Video DMA Start........................................................................104

10.3.63 VIDINITA (0x1DC) — Video DMA INIT A........................................................................105

10.3.64 VIDCR (0x1E0) — Video DMA Control...........................................................................106

10.3.65 VIDINITB (0x1E8) — Duplex LCD Video DMA INIT B....................................................107

10.3.66 DMAST/DMARQ/DMAMSK (0x1F0,0x1F4,0x1F8) — DMA Interrupt Control................108

6

TABLE OF CONTENTS

ADVANCE DATA BOOK v2.0

June 1997

CL-PS7500FE

System-on-a-Chip for Internet Appliance

11. I/O SUBSYSTEMS ..............................................................................................................109

11.1 Introduction.....................................................................................................................................109

11.2 I/O Address Space Usage..............................................................................................................109

11.3 Additional I/O Chip Select Decode Logic........................................................................................110

11.4 Simple 8-MHz I/O ...........................................................................................................................111

11.5 Module I/O......................................................................................................................................111

11.6 PC Bus-Style I/O ............................................................................................................................111

11.7 DMA During I/O Cycles ..................................................................................................................114

11.8 Clock Synchronization Conditions..................................................................................................114

11.9 Keyboard/mouse Interface..............................................................................................................114

11.10 Analog-to-Digital Converter Interface .............................................................................................116

11.10.1 Counters.........................................................................................................................116

11.10.2 Interrupt Control..............................................................................................................116

11.10.3 Status of Interface...........................................................................................................117

11.10.4 Control............................................................................................................................118

11.10.5 Comparators...................................................................................................................118

11.10.6 Converter Operation.......................................................................................................118

11.11 Timers.............................................................................................................................................119

11.11.1 Programming the Timers ................................................................................................120

11.11.2 Timer interrupts ..............................................................................................................120

11.12 General-Purpose, 8-bit-wide, I/O Port ............................................................................................120

11.13 ID and OD Open-Drain I/O Pins .....................................................................................................121

11.14 Version and ID Registers................................................................................................................121

11.15 Interrupt Control .............................................................................................................................121

12. VIDEO FEATURES..............................................................................................................124

12.1 Pixel Clock......................................................................................................................................124

12.2 Palette ............................................................................................................................................126

12.2.1 Palette Updating.............................................................................................................126

12.3 Cursor.............................................................................................................................................126

12.3.1 Cursor in HiRes Mode ....................................................................................................127

12.3.2 Cursor in LCD Mode.......................................................................................................127

12.4 HiRes Support................................................................................................................................127

12.4.1 CL-PS7500FE Support for HiRes Mode.........................................................................127

12.5 Liquid Crystal Displays ...................................................................................................................129

12.5.1 LCD Grayscaling.............................................................................................................129

12.5.2 Dual-Panel LCDs (Duplex Mode)....................................................................................129

12.5.3 Single-Panel Color LCDs................................................................................................130

12.6 External Support.............................................................................................................................130

12.6.1 ECLK ..............................................................................................................................131

12.6.2 Power Saving Considerations.........................................................................................131

12.6.3 Vertical and Horizontal Synchronization.........................................................................131

12.6.4 GENLOCK......................................................................................................................131

12.7 Analog Outputs...............................................................................................................................131

12.7.1 DAC Control....................................................................................................................131

12.7.2 Pedestal Current.............................................................................................................132

12.7.3 Video DAC Currents .......................................................................................................132

12.7.4 Monochrome Output.......................................................................................................132

June 1997

ADVANCE DATA BOOK v2.0

TABLE OF CONTENTS

7

CL-PS7500FE

System-on-a-Chip for Internet Appliance

13. SOUND FEATURES ........................................................................................................... 133

13.1 Sound.............................................................................................................................................133

13.2 The Sound FIFO.............................................................................................................................133

13.3 The Digital Serial Sound Interface..................................................................................................133

13.3.1 Timing Formats...............................................................................................................133

14. VIDEO AND SOUND MACR OCELL.................................................................................. 135

14.1 Features .........................................................................................................................................135

14.1.1 Flexible Video System ....................................................................................................135

14.1.2 Hardware Cursor ............................................................................................................135

14.1.3 Palette.............................................................................................................................135

14.1.4 Pixel Clock......................................................................................................................136

14.1.5 Display Modes................................................................................................................136

14.1.6 Power Management........................................................................................................136

14.1.7 On-chip Sound System...................................................................................................136

15. VIDEO MACR OCELL INTERFACE.................................................................................... 138

15.1 Bus Interface ..................................................................................................................................138

15.2 Setting the FIFO Preload Value......................................................................................................138

15.2.1 Example..........................................................................................................................139

16. THE VIDEO SOUND AND PROGRAMMER’S MODEL.................................................... 140

16.1 The Video and Sound Macrocell Registers....................................................................................140

16.2 Video Palette: Address 0x0............................................................................................................142

16.3 Video Palette Address Pointer: Address 0x1..................................................................................142

16.4 LCD Offset Registers: Addresses 0x30 and 0x31..........................................................................143

16.5 Border Color Register: Address 0x4...............................................................................................144

16.6 Cursor Palette: Addresses 0x5–0x7...............................................................................................144

16.7 Horizontal Cycle Register (HCR): Address 0x80............................................................................145

16.8 Horizontal Sync Width Register (HSWR): Address 0x81................................................................145

16.9 Horizontal Border Start Register (HBSR): Address 0x82...............................................................145

16.10 Horizontal Display Start Register (HDSR): Address 0x83..............................................................146

16.11 Horizontal Display End Register (HDER): Address 0x84...............................................................146

16.12 Horizontal Border End Register (HBER): Address 0x85 ................................................................146

16.13 Horizontal Cursor Start Register (HCSR): Address 0x86...............................................................147

16.14 Horizontal Interlace Register (HIR): Address 0x87.........................................................................147

16.15 Horizontal Test Registers: Addresses 0x88 and 0x8H....................................................................147

16.16 Vertical Cycle Register (VCR): Address 0x90................................................................................147

16.17 Vertical Sync Width Register (VSWR): Address 0x91 ....................................................................148

16.18 Vertical Border Start Register (VBSR): Address 0x92....................................................................148

16.19 Vertical Display Start Register (VDSR): Address 0x93...................................................................148

16.20 Vertical Display End Register (VDER): Address 0x94....................................................................149

16.21 Vertical Border End Register (VBER): Address 0x95.....................................................................149

16.22 Vertical Cursor Start Register (VCSR): Address 0x96....................................................................149

16.23 Vertical Cursor End Register (VCER): Address 0x97.....................................................................150

16.24 Vertical Test Registers: Addresses 0x98, 0x9A and 0x9C..............................................................150

16.25 External Register (EREG): Address 0xC........................................................................................151

16.26 Frequency Synthesizer Register (FSYNREG): Address 0xD .........................................................152

16.27 Control Register (CONREG): Address 0xE....................................................................................153

16.28 Data Control Register (DCTL): Address 0xF..................................................................................154

16.29 Sound Frequency Register (SFR): Address 0xB0..........................................................................154

16.30 Sound Control Register (SCTL): Address 0xB1.............................................................................155

8

TABLE OF CONTENTS

ADVANCE DATA BOOK v2.0

June 1997

CL-PS7500FE

System-on-a-Chip for Internet Appliance

17. FPA COPROCESSOR MACROCELL ................................................................................156

17.1 FPA Functional Blocks....................................................................................................................157

17.1.1 Coprocessor Interface ....................................................................................................157

17.1.2 Instruction Issuer ............................................................................................................157

17.1.3 The Load-Store Unit .......................................................................................................157

17.1.4 The Register Bank..........................................................................................................157

17.1.5 The Arithmetic Unit.........................................................................................................158

18. FLOATING-POINT COPROCESSOR PROGRAMMER’S MODEL...................................160

18.1 Overview.........................................................................................................................................160

18.1.1 Floating-Point Status Register........................................................................................160

18.1.2 Floating-Point Control Register.......................................................................................160

18.2 Floating-Point Operation.................................................................................................................160

18.3 ARM Integer and Floating-Point Number Formats .........................................................................161

18.3.1 Integer.............................................................................................................................161

18.3.2 IEEE Single Precision (S)...............................................................................................161

18.3.3 IEEE Double Precision (D) .............................................................................................161

18.3.4 IEEE Extended Double Precision (E) .............................................................................162

18.3.5 Packed Decimal (P)........................................................................................................163

18.3.6 Expanded Packed Decimal (EP).....................................................................................163

18.4 The Floating-Point Status Register (FPSR)....................................................................................164

18.4.1 System ID Byte...............................................................................................................164

18.4.2 Exception Trap Enable Byte............................................................................................165

18.4.3 System Control Byte.......................................................................................................165

18.4.4 Cumulative Exception Flags Byte...................................................................................166

18.5 The Floating-Point Control Register (FPCR)..................................................................................168

19. FLOATING-POINT INSTRUCTION SET.............................................................................170

19.1 Coprocessor Data Transfer.............................................................................................................170

19.1.1 LDF/STF — Load and Store Floating.............................................................................170

19.1.2 Assembler Syntax...........................................................................................................171

19.1.3 Load and Store Multiple Floating Instructions ................................................................172

19.1.4 Assembler Syntax — Form 1..........................................................................................173

19.1.5 Assembler Syntax — Form 2..........................................................................................174

19.2 Coprocessor Data Operations........................................................................................................174

19.2.1 Dyadic Operations..........................................................................................................174

19.2.2 Monadic Operations........................................................................................................175

19.2.3 Library Calls....................................................................................................................175

19.2.4 Backwards Compatibility.................................................................................................175

19.3 Coprocessor Register Transfer.......................................................................................................178

19.3.1 Compare Operations ......................................................................................................179

19.4 FPA Instruction Set........................................................................................................................180

19.4.1 Infinities and NaNs..........................................................................................................180

19.4.2 Exceptional Conditions...................................................................................................180

19.5 Floating-point Support Code ..........................................................................................................182

19.5.1 IEEE Standard Conformance .........................................................................................182

19.6 Instruction Cycle Timing .................................................................................................................183

19.6.1 Instruction Classification.................................................................................................184

19.6.2 Perf ormance Tuning........................................................................................................185

June 1997

ADVANCE DATA BOOK v2.0

TABLE OF CONTENTS

9

CL-PS7500FE

System-on-a-Chip for Internet Appliance

20. BUS INTERFACE................................................................................................................ 187

20.1 Bus Arbitration................................................................................................................................187

20.2 Bus Cycle Types.............................................................................................................................187

20.3 Video DMA Bandwidth....................................................................................................................188

20.4 Video DMA Latency........................................................................................................................188

21. CLOCKS, POWER SAVING, AND RESET........................................................................ 191

21.1 Clock Control..................................................................................................................................191

21.1.1 Video and Sound Subsystem Clocks..............................................................................191

21.1.2 I/O Clock Outputs...........................................................................................................191

21.1.3 Synchronous/Asynchronous Mode for the ARM Processor............................................191

21.1.4 Clock Prescalars.............................................................................................................192

21.1.5 Clocking Schemes..........................................................................................................192

21.2 Power Management........................................................................................................................192

21.2.1 SUSPEND Mode............................................................................................................193

21.2.2 STOP Mode....................................................................................................................194

21.3 Reset..............................................................................................................................................195

22. ELECTRICAL SPECIFICATIONS ...................................................................................... 196

22.1 Absolute Maximum Ratings............................................................................................................196

22.2 DC Specifications...........................................................................................................................197

22.2.1 DC Specifications — Digital Values................................................................................197

22.3 Derating..........................................................................................................................................198

22.4 AC Parameters — List of Timing Figures .......................................................................................199

22.5 System Reset Timing .....................................................................................................................200

22.6 Memory Subsystems......................................................................................................................201

22.7 I/O Subsystems..............................................................................................................................209

22.8 System Timing (Clocks)..................................................................................................................222

23. P A CKA GE........................................................................................................................... 225

23.1 240-Pin PQFP Package Example...................................................................................................225

24. ORDERING INFORMATION EXAMPLE............................................................................ 226

10

TABLE OF CONTENTS

ADVANCE DATA BOOK v2.0

June 1997

CL-PS7500FE

System-on-a-Chip for Internet Appliance

Appendixes

A. INITIALIZATION AND BOOT SEQUENCE........................................................................227

1. Introduction.....................................................................................................................................227

2. Sample Boot Sequence..................................................................................................................227

3. Other Methods................................................................................................................................228

B. DUAL-PANEL LIQUID CRYSTAL DISPLAYS...................................................................229

1. Programming the Video Subsystem...............................................................................................229

2. Configuring DMA within the CL-PS7500FE....................................................................................230

3. Cursor.............................................................................................................................................230

4. Video Frame Buffer Restrictions.....................................................................................................231

C. USING ASTCR AT HIGH MEMCLK FREQUENCIES........................................................232

1. Using ASTCR.................................................................................................................................232

2. ASTCR I/O Cycle Type and Hold Times.........................................................................................233

3. Example..........................................................................................................................................233

D. EXPANDING PC-STYLE I/O TO 32 BITS ..........................................................................234

1. 32-Bit I/O ........................................................................................................................................234

E. CL-PS7500FE VIDEO CLOCK SOUR CES.........................................................................236

1. Introduction.....................................................................................................................................236

2. Clock Sources ................................................................................................................................236

3. Using the Phase Comparator.........................................................................................................237

4. Phase Comparator Reset...............................................................................................................240

4.1 Reset Procedure.............................................................................................................240

F . CL-PS7500FE TEST MODES..............................................................................................241

1. Introduction.....................................................................................................................................241

2. Test Modes Description ..................................................................................................................241

G. CL-PS7500FE PINOUT DIFFERENCES FROM THE ARM7500 ......................................243

1. Introduction.....................................................................................................................................243

INDEX .................................................................................................................................245

June 1997

ADVANCE DATA BOOK v2.0

TABLE OF CONTENTS

11

CL-PS7500FE

System-on-a-Chip for Internet Appliance

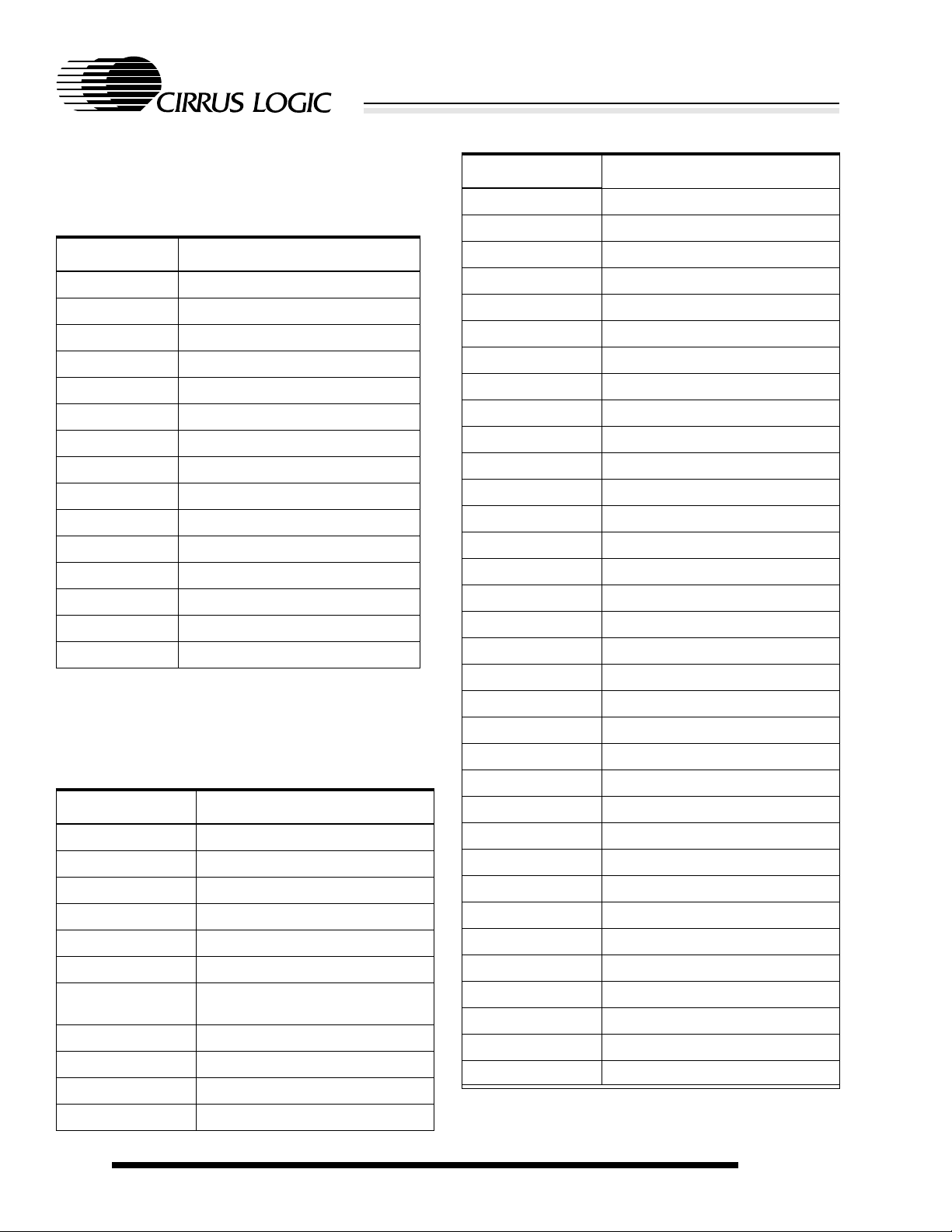

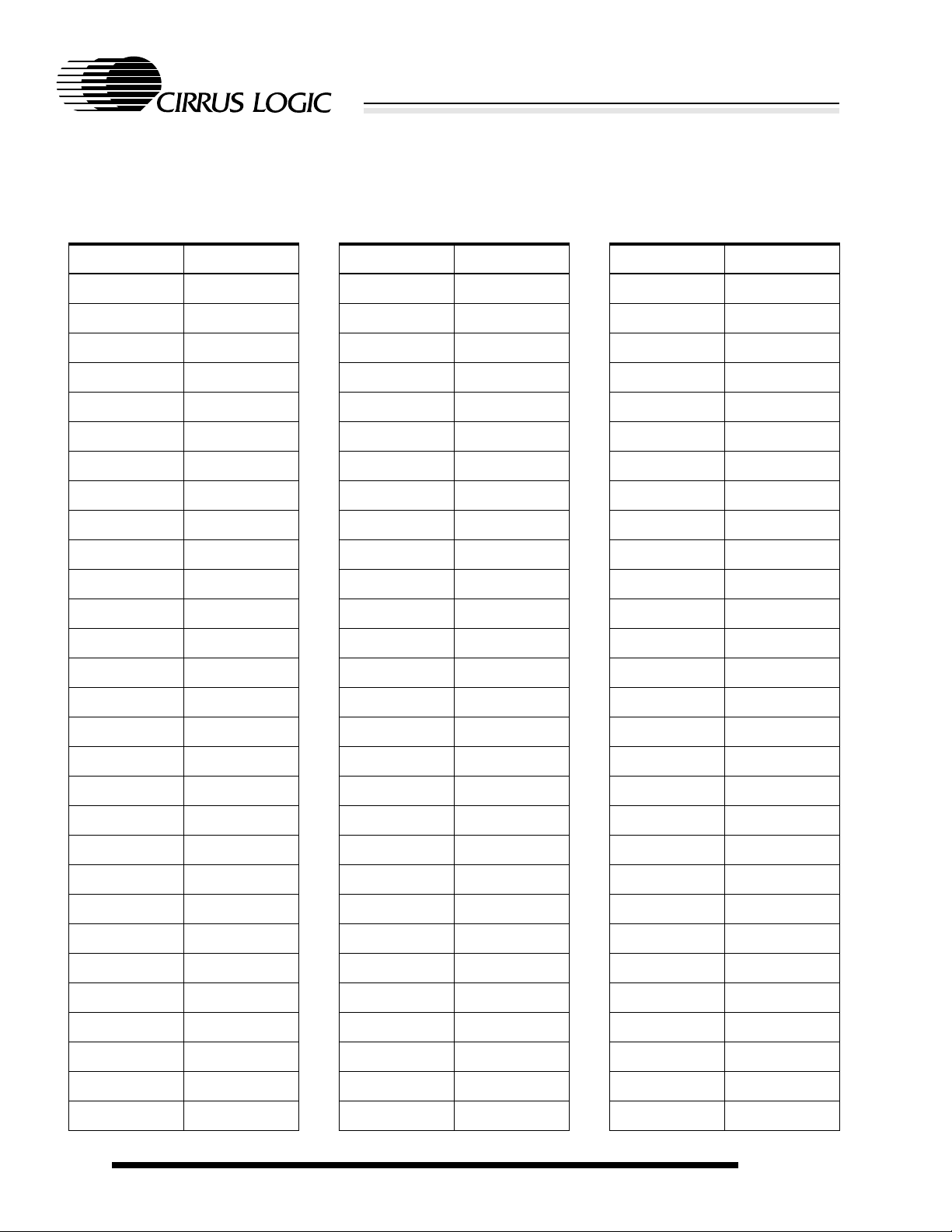

CONVENTIONS

Abbreviations

Symbol Units of measure

bpp bits-per-pixel

°C degree Celsius

Hz hertz (cycles per second)

Kbyte kilobyte (1,024 bytes)

kHz kilohertz

kΩ kilohm

Mbyte megabyte (1,048,576 bytes)

MHz megahertz (1,000 kilohertz)

µF microfarad

µs microsecond (1,000 nanoseconds)

mA milliampere

ms millisecond (1,000 microseconds)

ns nanosecond

pV picovolt

qword quad word

The use of ‘tbd’ indicates values that are ‘to be

determined’; ‘n/a’ designates ‘not available’; ‘n/c’

indicates a pin that is a ‘no connect’.

Acronyms

Acronym Definition

Acronym Definition

DRAM dynamic random-access memory

DVD digital video disk

EDO extended data out

FIFO first in/first out

FPA floating point accelerator

FPU floating point unit

GPIO general-purpose IO

HBM human body model

IC integrated circuit

IDC instruction and data cache

ISA industry standard architecture

LSB least-significant bit

LUT lookup table

MFLOPS million floating points per second

MMU memory management unit

MSB most-significant bit

MUX multiplexer

NaN not a number

PC program counter

PLL phased-locked loop

PQFP plastic quad-flat pack

RAM random-access memory

RISC reduced instruction set computer

ROM read-only memory

(cont.)

AC alternating current

ALU arithmetic logic unit

AP access permissions

A-to-D analog-to-digital

BIOS basic input/output system

CISC complex instruction set computer

CMOS

CRT cathode ray tube

DAC digital-to-analog converter

DC direct current

DMA direct memory access

12

CONVENTIONS

complementary metal-oxide semiconductor

R/W read/write

SRAM static random-access memory

SWI software interrupt instruction

TLB translation look-aside buffer

TTB translation table base

UMA unified memory architecture

VCO voltage-controlled oscillator

VRAM video random-access memory

WB write buffer

XIP execute-in-place

ADVANCE DATA BOOK v2.0

June 1997

CL-PS7500FE

System-on-a-Chip for Internet Appliance

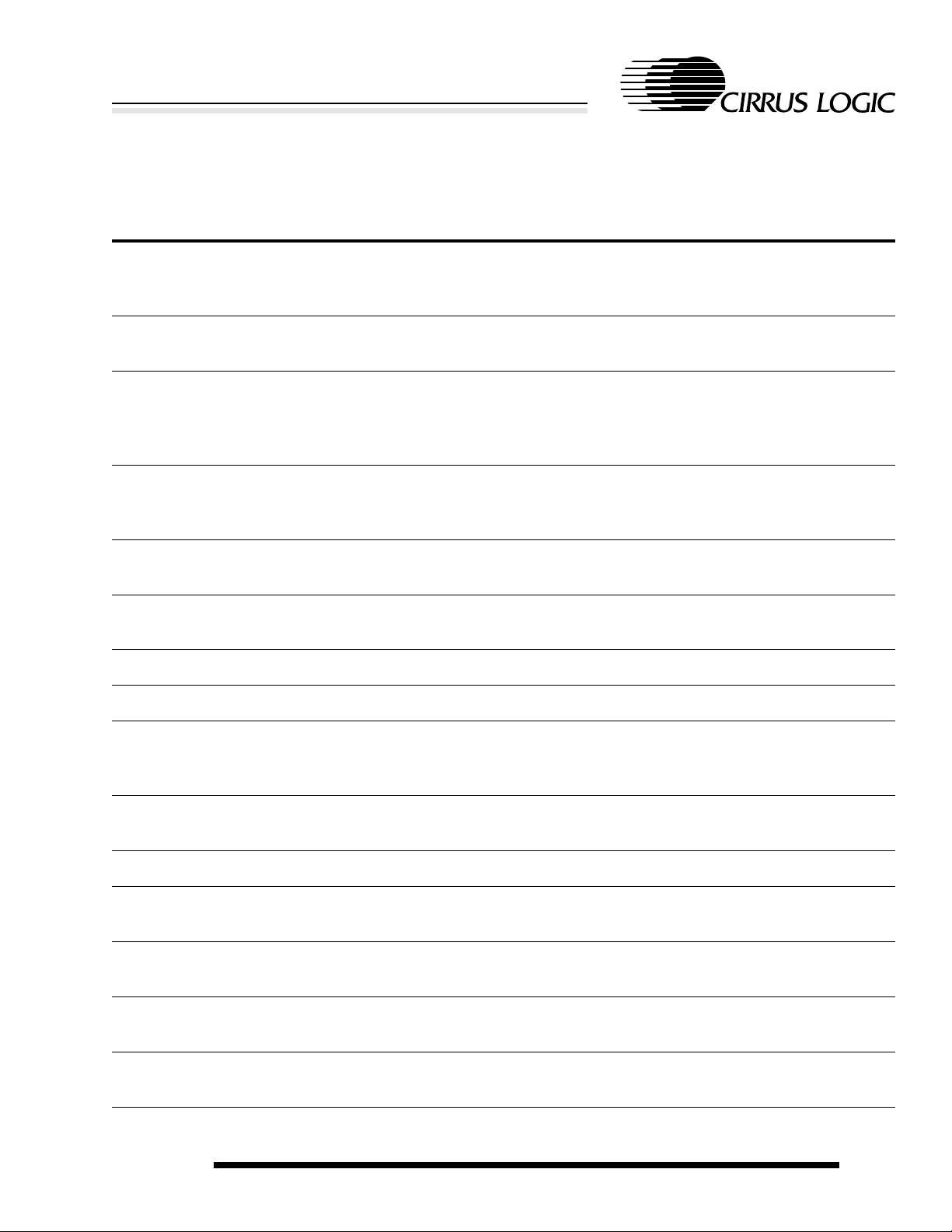

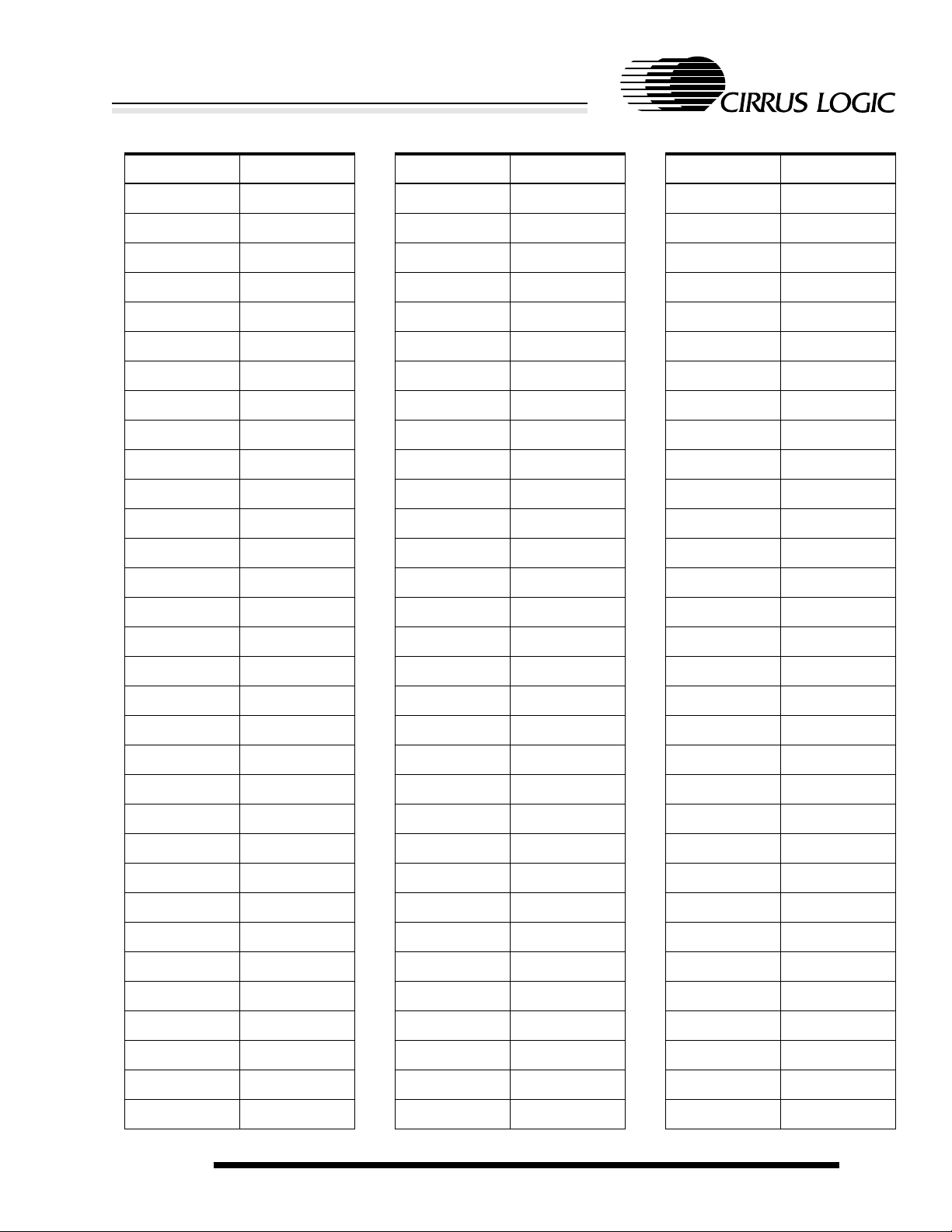

1. PIN INFORMATION

The CL-PS7500FE is available in a 240-pin PQFP (plastic quad flat pack) configuration.

1.1 Pin Diagram

ID

IOP0

IOP1

IOP2

IOP3

IOP4

IOP5

IOP6

IOP7

nPOR

VSSKBDATA

KBCLK

MSDATA

VDDMSCLK

BD0

BD1

BD2

BD3

BD4

VSSBD5

BD6

BD7

BD8

BD9

VDD_CORE

MEMCLK

VSS_CORE

BD10

VDDBD11

BD12

BD13

nEVENT2

VSSI_OCLK

BD14

BD15

nROMCS

nRESET

RESET

SnA

OSCDELAY

OSCPOWER

nWE

nCAS0

VDDnCAS1

VSSnCAS2

nCAS3

VSS_ATOD

ATOD0

ATOD1

ATOD2

180

179

178

177

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

OD1

OD0

SETCS

INT9

nINT4

INT5

READY

nIOGT

nBLI

nXIPMUX16

nINT1

INT2

nEVENT1

nXIPLATCH

nSIOCS2

V

nSIOCS1

nEASCS

nMSCS

nBLO

nRBE

nWBE

CLK2

REF8M

CLK8

CLK16

nIORQ

V

nIOR

VSS_CORE

CPUCLK

VDD_CORE

nIOW

V

nCCS

nCDACK

IORNW

nPCCS2

nPCCS1

LNBW

LA0

LA1

LA2

V

LA3

LA4

LA5

LA6

LA7

LA8

V

LA9

LA10

LA11

LA12

V

LA13

LA14

181

182

183

184

185

186

187

188

189

190

191

192

V

193

SS

194

195

TC

196

197

198

DD

199

200

201

202

203

204

205

206

207

208

209

210

SS

211

212

213

214

215

216

DD

217

218

219

220

221

222

223

224

225

226

SS

227

228

229

230

231

232

233

DD

234

235

236

237

238

SS

239

240

1234567891011121314151617181920212223242526272829303132333435363738394041424344454647484950515253545556575859

Pin 1 indicator

CL-PS7500FE

240-Pin PQFP

124

ATOD3

ATODREF

123

122

VDD_ATOD

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

nRAS0

nRAS1

nRAS2

V

DD

nRAS3

V

SS

RA0

RA1

RA2

RA3

RA4

RA5

RA6

RA7

V

DD

RA8

V

SS

RA9

RA10

RA11

INT7

nINT6

nINT3

nINT8

nTEST

VSS_ANALOG

GOUT

BOUT

ROUT

VDD_ANALOG

VIREF

VDD_CORE

HSYNC

VSS_CORE

VSYNC

V

SS

ED0

ED1

ED2

ED3

ED4

V

DD

ED5

ED6

ED7

HCLK

V

SS

ECLK

SYNC

WS

SDCLK

SCLK

SDO

VSS_CORE

V

SS

VDD_CORE

V

SS

V

SS

V

DD

V

DD

LA17

LA18

LA19

LA20

LA21

V

LA22

LA23

LA24

LA25

LA26

LA27

LA28

LA15

LA16

June 1997 13

ADVANCE DATA BOOK v2.0 PIN INFORMATION

SS

DD

V

D31

D30

D29

D28

SS

DD

V

V

D27

D26

D25

D24

D23

D22

D21

VSS_CORE

D20

D19

VDD_CORE

D18

SS

V

D17

D16

D15

D14

D13

DD

V

D12

D11

D10

D9

SS

D8

D7D6D5D4D3D2D1

V

SS

DD

D0

V

V

VCLKI

VCLKO

PCOMP

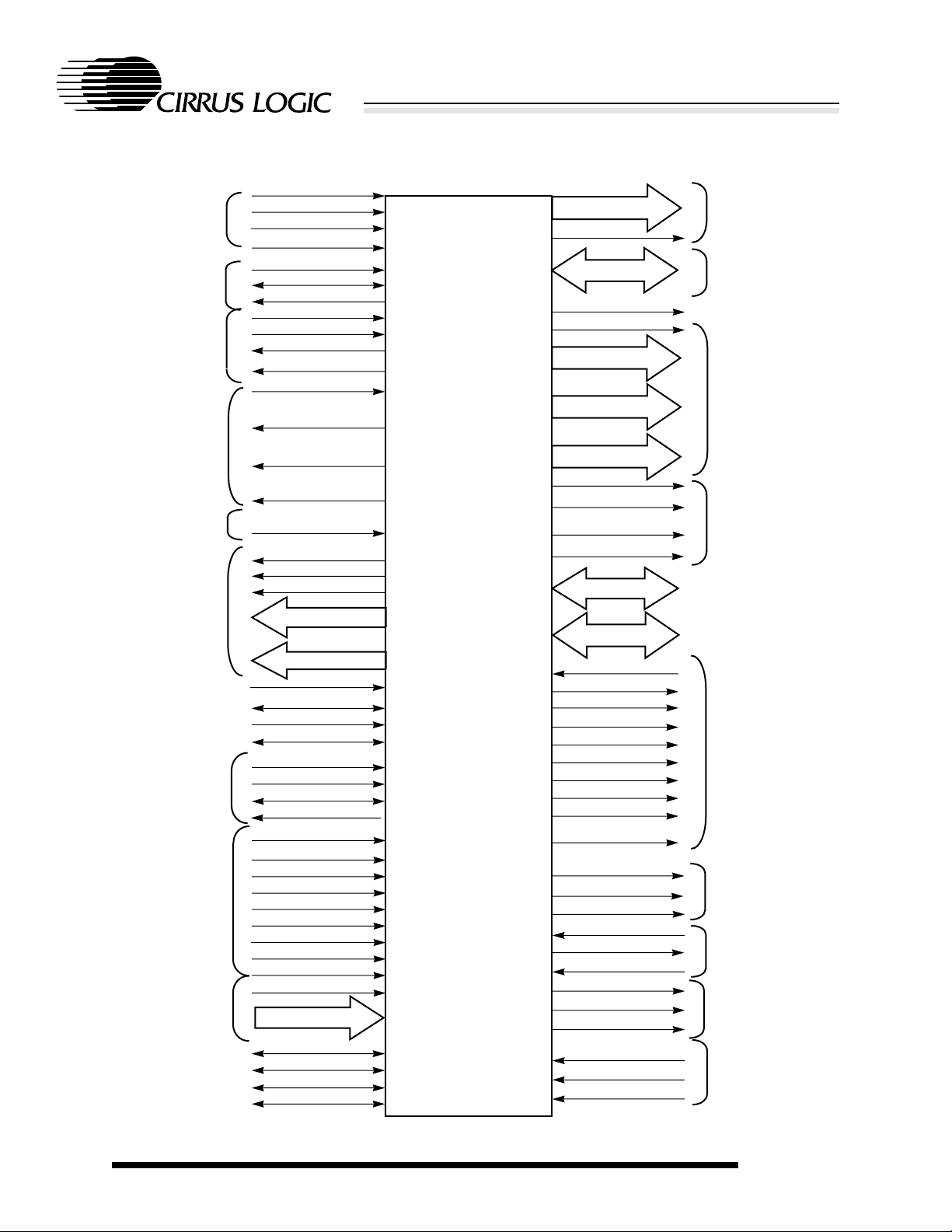

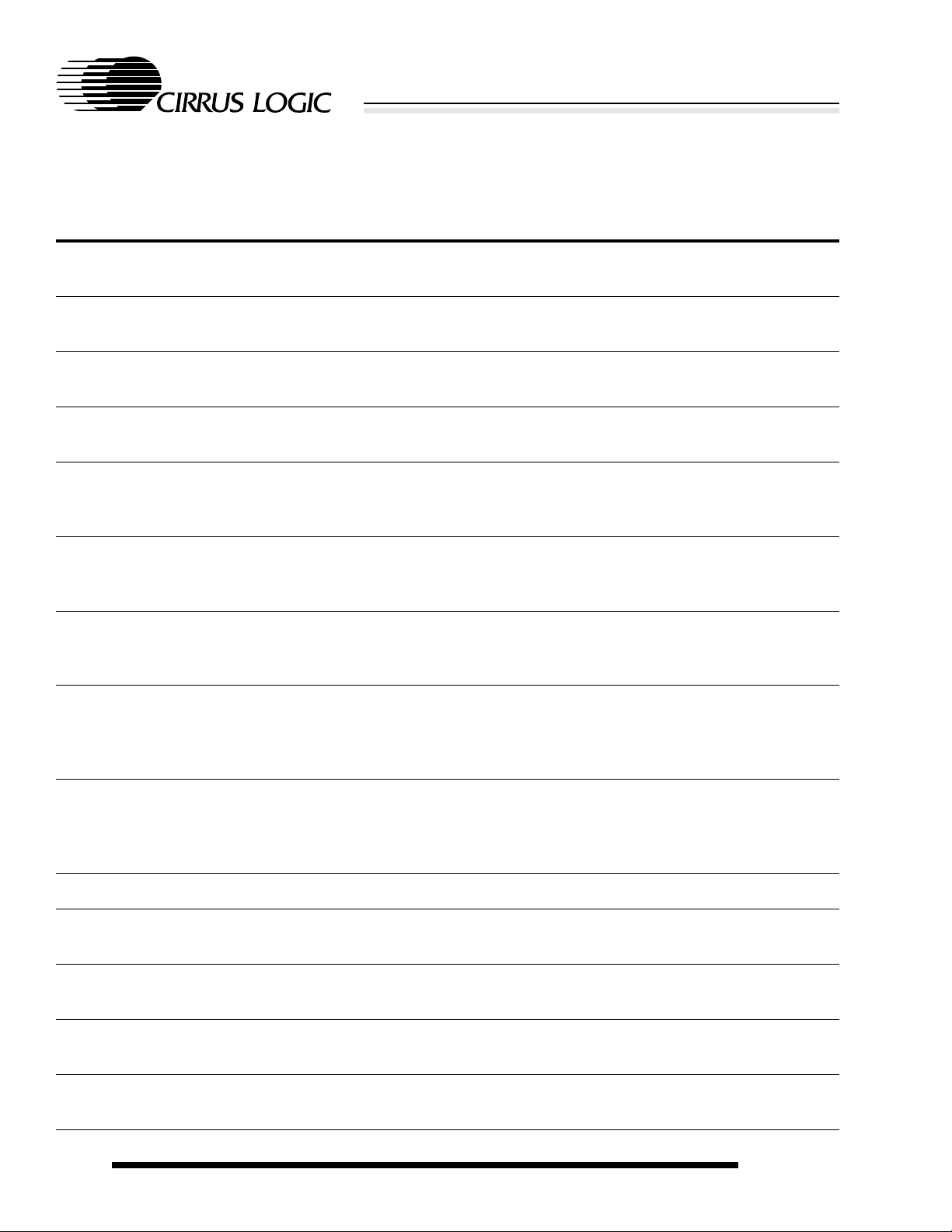

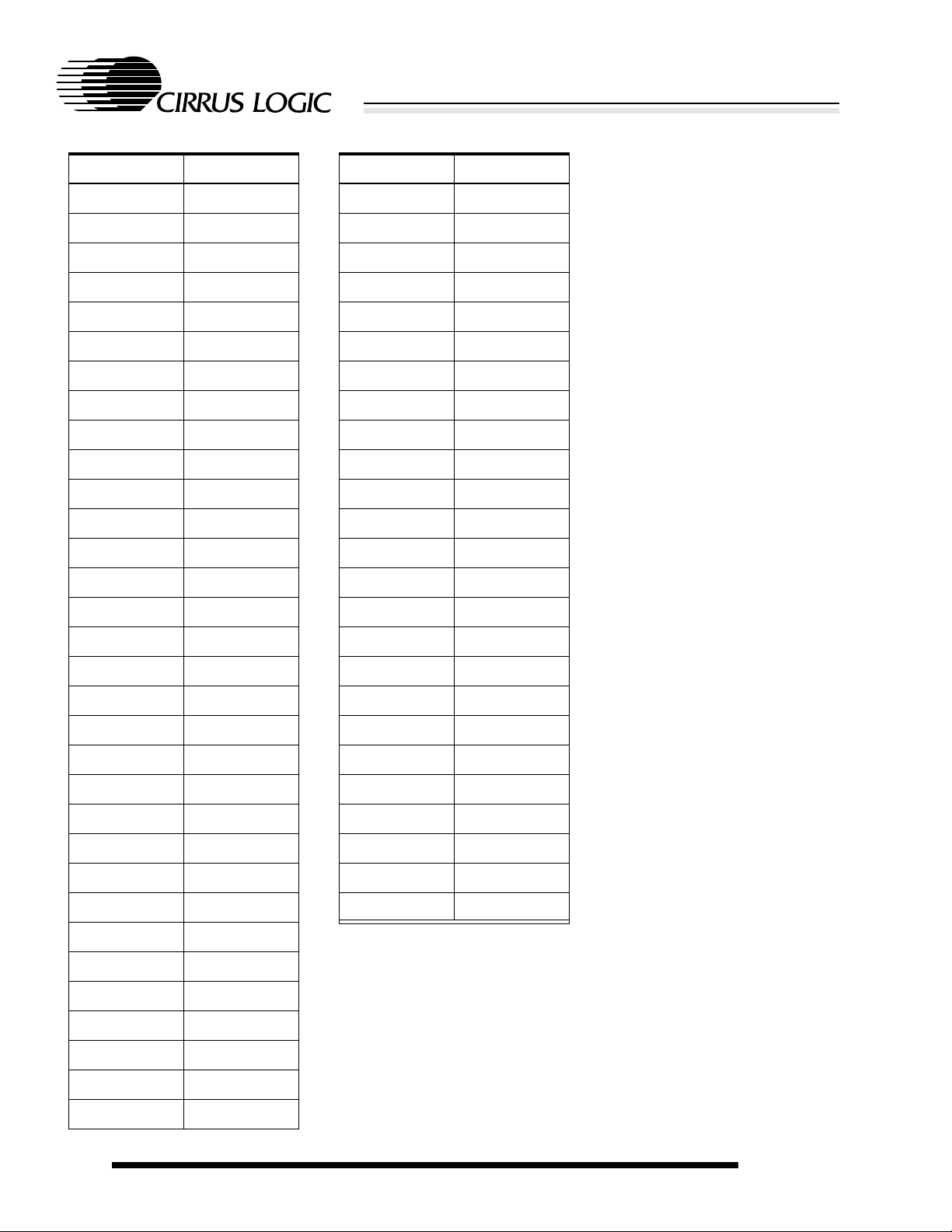

1.2 Block Diagram

CL-PS7500FE

System-on-a-Chip for Internet Appliance

MAIN

CLOCKS/CONTROL

RESET

VIDEO

CLOCKS AND

CONTROL

SOUND

SYSTEM

REFERENCE

CURRENT

VIDEO

OUTPUTS

POWER

MANAGEMENT

EXTERNAL

INTERRUPT

SOURCES

A-TO-D

CONVERTORS

KBD/MOUSE

INTERFACE

SNA

CPUCLK

MEMCLK

I_OCLK

nPOR

nRESET

RESET

HCLK

VCLKI

VCLKO

PCOMP

SCLK

WS

SDO

SDCLK

VIREF

HSYNC

VSYNC

ECLK

ED[7:0]

RGB OUTPUTS

nTEST

OD[1:0]

SYNC

ID

nEVENT1

nEVENT2

OSCDELAY

OSCPOWER

nINT6

nINT3

nINT8

INT7

INT9

nINT4

INT5

nINT1

INT2

ATODREF

ATOD[3:0]

MSECLK

MSEDAT

KBCLK

KBDAT

CL-PS7500FE

LA[28:0]

LNBW

D[31:0]

nROMCS

nWE

RA[11:0]

nCAS[3:0]

nRAS[3:0]

CLK2

CLK8

REF8M

CLK16

IOP[7:0]

BD[15:0]

SETCS

nCCS

nCDACK

TC

nPCCS2

nPCCS1

nSIOCS1

nMSCS

nEASCS

nSIOCS2

nBLO

nWBE

nRBE

nBLI

nIORQ

nIOGT

nIOR

nIOW

IORNW

nXIPLATCH

nXIPMUX16

READY

LATCHED

ADDRESS

BUS AND

DATA

BUS

I/O CHIP

SELECTS

I/O R/W

CONTROL

PIN INFORMATION

ADVANCE DATA BOOK v2.0

June 199714

CL-PS7500FE

System-on-a-Chip for Internet Appliance

2. PIN DESCRIPTIONS

This chapter gives the name, type, and relevant details of each of the CL-PS7500FE signals.

NOTE: When output signals are placed in the high-impedance state for long periods, ensure that they do not ‘float’

to an undefined logic level.

The following abbreiviations are used to indicate signal types.

IC

OCZ

IT Input, TTL threshold

ICS Input, CMOS Schmitt

IA Input, analog

OA Output, analog

BTZ Bidirectional, CMOS output, TTL threshold input level

TOD Open-drain, TTL input

CSOD Open-drain, CMOS schmitt input

IAOD Input, analog with programmable internal pull-down transistor

Input, CMOS threshold

Output, CMOS levels, tristate

For outputs and bidirectional signals, drive strength is classified 1, 2, or 3. See Chapter 22 for DC and AC

characteristics.

2.1 CL-PS7500FE Pin Descriptions

Name Type

LA[28:0] OCZ 2 LATCHED ADDRESS BUS: This bus is the latched version of the

Drive

Strength

Description

ARM address for memory accesses, changing on the falling edge of

the internal MCLK signal.

LNBW OCZ 2 LA TCHED NO T BYTE WORD: This is a latched v ersion of the inter-

nal NBW signal from the ARM processor, changing on the falling

edge of the internal MCLK signal.

D[31:0] BTZ 2 DATA: The main data bus for the CL-PS7500FE. All exter nal data

transfers happen through this bus. When the CL-PS7500FE is configured for operation in 16-bit mode, only the lo wer 16 bits are used.

SnA IC SYNCHRONOUS/NOT ASYNCHRONOUS: This pin is set accord-

ing to the relationship required between the internal clock signals,

MCLK and FCLK, for the ARM.

If this pin is set high, both the memory system and the CPU are

driven from the MEMCLK pin, and the required synchronous timing

relationship between the ARM processor clocks is generated automatically on-chip. If different clocks are to be used for the MEMCLK

and CPUCLK inputs, the SnA pin must be set low.

June 1997 15

ADVANCE DATA BOOK v2.0 PIN DESCRIPTIONS

CL-PS7500FE

System-on-a-Chip for Internet Appliance

2.1 CL-PS7500FE Pin Descriptions

Name Type

Drive

Strength

(cont.)

Description

BOUT AO BLUE ANALOG OUTPUT: The video signal analog outputs are

designed to drive doubly-terminated 75-Ω lines.

ECLK OCZ 3 EXTERNAL CLOCK: When enabled, this clock validates the data

on ED[7:0]. In normal video mode, it runs at the pix el rate , but when

LCD data is being produced, it runs at a quarter of the pixel rate.

ED[7:0] OCZ 2 EXTERNAL DATA: This is the digital video output port of the

CL-PS7500FE. From this, the digital equivalent of the analog output

can be produced in any color , or data from the external palette may

be produced. This can be used for a variety of purposes such as

fading or supremacy. Also, data for driving LCD panels is output

from this port. Data produced is validated b y ECLK.

GOUT AO GREEN ANALOG OUTPUT: The video signal analog outputs are

designed to drive doubly-terminated 75-Ω lines.

HCLK IT HIGH SPEED CLOCK: This is the clock used with video sub-

system.

HSYNC OCZ 3 HORIZONTAL SYNCHRONIZATION: There are two synchroniza-

tion outputs on

the CL-PS7500FE, HSYNC and VSYNC . Dependent

on the state of bits 17 and 16 in the video External register, either a

horizontal or a composite (NOR) sync can be output on this pin, in

either polarity . The width of the HSYNC pulse is definable in units of

2 pixels.

PCOMP OCZ 1 PHASE COMPARATOR OUTPUT: Used with VCLK pins.

ROUT AO RED ANALOG OUTPUT: The video signal analog outputs are

designed to drive doubly-terminated 75-Ω lines.

SCLK IT SOUND CLOCK: This signal can be used to clock the sound sys-

tem, when a clock asynchronous to the internal video reference

clock is required.

SDCLK OCZ 2 SERIAL DA TA CLOCK: This clock v alidates serial sound data on its

rising edge.

SDO OCZ 2 SERIAL DATA OUT: Serial sound data is output from this pin.

SYNC IT EXTERNAL SYN: This signal is used to synchronize CL-PS7500FE

with another video system.

VCLKI IC PHASE COMPARATOR CLOCK IN (for video subsystem).

VCLKO OCZ 2 PHASE COMPARATOR CLOCK OUT (for video subsystem).

PIN DESCRIPTIONS

ADVANCE DATA BOOK v2.0

June 199716

CL-PS7500FE

System-on-a-Chip for Internet Appliance

2.1 CL-PS7500FE Pin Descriptions

Name Type

Drive

Strength

(cont.)

Description

VIREF IA VIDEO REFERENCE CURRENT: The video DACs need a refer-

ence current to calibrate them. A constant current source is recommended, although a resistor up to V

is sufficient for many

DD

applications. This current also generates the constant source f or the

A-to-D comparators.

VSYNC OCZ 3 VERTICAL SYNCHRONIZATION: Dependent on the state of bits

19 and 18 in the external register, either a ver tical or a composite

(XNOR) sync can be output on this pin, in either polarity. The width

of the VSYNC pulse can be defined in units of a raster.

WS OCZ 2 WORD SELECT: This signal denotes whether the output serial data

is for the left-hand or right-hand stereo channel.

nTEST IT TEST MODE INPUT: This pin should be held permanently high. It

is only intended to be used during production test of the

CL-PS7500FE. An on-chip pull-up resistor is included, but it is

advised to apply an external pull-up resistor to this pin.

nWE OCZ 2 WRITE ENABLE: This is a active-low signal.

RA[11:0] OCZ 2 DRAM ROW/COLUMN MULTIPLEXED ADDRESS BUS:

Addresses for this bus are decoded from the ARM processor

address for normal memory accesses, and are generated by the

DMA controller for DMA.

nRAS[3:0] OCZ 3 DRAM ROW ADDRESS STROBES: Each of these selects one of

the four banks of DRAM available.

nCAS[3:0] OCZ 3 DRAM COLUMN ADDRESS STROBES: These select the byte

within the word for DRAM accesses.

ATOD[3:0] IAOD ANALOG-TO-DIGITAL: These are the four A-to-D channel input

voltages.

ATODREF IA ANALOG-TO-DIGITAL REFERENCE: This is the reference v oltage

for the A-to-D converter comparators.

OSCPOWER OCZ 1 OCILLA TOR PO WER: This is the enab le signal for the system oscil-

lator(s). When low, this signal can be used to disable the external

oscillator(s).

OSCDELAY CSOD 1 OCILLATOR DELAY: This signal requires an RC netw ork to gener-

ate a fixed delay when restarting the system oscillator(s) on exit

from STOP mode.

June 1997 17

ADVANCE DATA BOOK v2.0 PIN DESCRIPTIONS

CL-PS7500FE

System-on-a-Chip for Internet Appliance

2.1 CL-PS7500FE Pin Descriptions

Name Type

Drive

Strength

(cont.)

Description

RESET OCZ 2 RESET OUTPUT: This is the synchronized version of internal sys-

tem reset signal.

nRESET CSOD 2 RESET: This is an open-drain output and a ‘soft’ reset input. This pin

is sampled every 1µs for reset events, so to guarantee a successful

reset, a reset pulse applied to this pin must be longer than 1µs (1µs,

assuming the internal I/O clock is 32 MHz).

nROMCS OCZ 1 ROM CHIP SELECT: This signal goes low to indicate a ROM

access.

I_OCLK IC I/O SYSTEM CLOCK: This clock input should always be 32 MHz

when in Divide-by-1 mode, and 64 MHz in Divide-by-2 mode.

MEMCLK IC MEMORY SYSTEM CLOCK: In synchronous mode, the ARM pro-

cessor FCLK is also driven from this clock.

CPUCLK [MHz] MEMCLK [MHz] SnA Notes

Low 40 High

40 56 Low

40 64 Low

Low 56 High Recommended

56 64 Low

CPUCLK IC This clock creates FCLK for the ARM CPU in asynchronous mode.

When SnA is high, this signal should be permanently tied high or

low.

BD[15:0] BTZ 2 This is the main external 16-bit I/O bus.

MSCLK TOD 2 MOUSE CLOCK: An open-drain pin for the mouse PS/2 interface.

MSDATA TOD 2 MOUSE DATA: An open-drain pin for the mouse PS/2 interface.

KBCLK TOD 2 KEYBOARD CLOCK: An open-drain pin for the keyboard PS/2

interface.

KBDATA TOD 2 KEYBOARD DATA: An open-drain pin for the keyboard PS/2 inter-

face.

nPOR ICS POWER ON RESET: Any low transitions on this pin are detected

and stretched to ensure a full reset.

PIN DESCRIPTIONS

ADVANCE DATA BOOK v2.0

June 199718

CL-PS7500FE

System-on-a-Chip for Internet Appliance

2.1 CL-PS7500FE Pin Descriptions

Name Type

Drive

Strength

(cont.)

Description

IOP[7:0] TOD 1 I/O PORT : This is the 8-bit-wide I/O port. Each bit is directly control-

lable through an CL-PS7500FE register, and can be used as an

interrupt source if required.

ID TOD 1 ID: This pin activates a system ID chip. It is forced low during the

power-on reset sequence.

OD[1:0] TOD 1 OPEN DRAIN 1:0: These are the tw o open-drain pins, which (unlike

the IOP[7:0] bus) cannot be used to generate interrupts, but can be

used as general-purpose I/O pins (for example to communicate with

a realtime clock chip).

SETCS IC This signal selects between two address decoding options for the

three main I/O chip selects. It aff ects the outputs nEASCS , nMSCS,

and nSIOCS2.

nINT1 IT This is a falling-edge-triggered interrupt. The nINT1 value can be

read directly in the IOCR I/O control register.

INT2 IT This is a rising-edge-triggered interrupt pin that can generate an

IRQ interrupt.

nINT3 IT This is an active-low interrupt that can generate an IRQ interrupt.

nINT4 IT This is an active-low interrupt that can generate an IRQ interrupt.

INT5 IT This is an active-high interrupt that can generate either an IRQ or a

FIQ interrupt, depending on the status of the relevant mask register

bits.

nINT6 IT This is an active-low interrupt that can generate either an IRQ or a

FIQ interrupt, depending on the programming of the mask registers.

INT7 IT This is an active-high interrupt that can generate an IRQ interrupt.

nINT8 IT This is an active-low interrupt that can generate either a FIQ or an

IRQ interrupt.

INT9 IT This is an active-high interrupt that can only generate a FIQ (highest

priority) interrupt.

nEVENT1 IT This is the active-low asynchronous event pin 1. A falling edge ter-

minates the STOP or SUSPEND power-saving modes.

nEVENT2 IT This is the active-low asynchronous event pin 2. A falling edge ter-

minates the STOP or SUSPEND power-saving modes.

June 1997 19

ADVANCE DATA BOOK v2.0 PIN DESCRIPTIONS

CL-PS7500FE

System-on-a-Chip for Internet Appliance

2.1 CL-PS7500FE Pin Descriptions

Name Type