Cirrus Logic CL-GD5446 (64-bit VisualMedia Accelerator) GD5446 Technical Reference Manual Nov 1996

CL-GD5446 Extended Display Modes Summary

Mode

No.

58, 6A 102 16/256K 800 × 600 100 × 37 56, 60, 72, 75

5C 103 256/256K 800 × 600 100 × 37 56, 60, 72, 75, 85

5D 104 16/256K 1024 × 768 128 × 48 43i

5E 100 256/256K 640 × 400 80 × 25 70

5F 101 256/256K 640 × 480 80 × 30 60, 72, 75, 85

60 105 256/256K 1024 × 768 128 × 48 43i, 60, 70, 72, 75, 85

64 111 64K 640 × 480 – 60, 72, 75, 85

65 114 64K 800 × 600 – 56, 60, 72, 75, 85

66 110 32K 640 × 480 – 60, 72, 75, 85

67 113 32K 800 × 600 – 56, 60, 72, 75, 85

68 116 32K 1024 × 768 – 43i, 60, 70, 75, 85

69 119 32K 1280 × 1024 – 43i, 60

6C 106 16/256K 1280 × 1024 160 × 64 43i

6D 107 256/256K 1280 × 1024 160 × 64 43i, 60, 75

71 112 16M 640 × 480 – 60, 72, 75, 85

74 117 64K 1024 × 768 – 43i, 60, 70, 75, 85

VESA

No.

Colors

Display

Resolution

Chars. Refresh (Hz)

a

, 60, 70, 72, 75

75 11A 64K 1280 × 1024 – 43i

78 115 16M 800 × 600 – 56, 60, 72, 75, 85

79 118 16M 1024 × 768 – 43i, 60, 70, 75, 85

7B – 256/256K 1600 × 1200 – 48i

7C – 256/256K 1152 × 864 – 70, 75

a. ‘i’ indicates interlaced.

Refer to Table 3-2, “Cirrus Logic Extended Display Modes,” on page 3-25.

CL-GD5446

Technical Reference Manual

November 1996

Second Edition

Notice

Cirrus Logic Inc. has made best efforts to ensure that the information contained in this document

is accurate and reliable. However, the information is subject to change without notice. No

responsibility is assumed by Cirrus Logic Inc. for the use of this information, nor for infringements

of patents or other rights of third parties. Cirrus, Cirrus Logic, AccuPak, DIVA, FastP ath, FasText,

FeatureChips, Good Data, Laguna, Laguna3D, MediaDAC, MotionVideo, SimulSCAN, S/LA,

SMASH, SofTarget, TextureJet, TVTap, UXART, VisualMedia, VPM, V-Port, Voyager, WavePort,

and WebSet are trademarks of Cirrus Logic Inc., which may be registered in some

jurisdictions. Other trademarks in this document belong to their respective companies. CR US and

Cirrus Logic International, Ltd. are trade names of Cirrus Logic Inc.

Copyright Notice

This document is the property of Cirrus Logic Inc. and implies no license under patents, copyrights, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrie v al

system, or transmitted, in any form or by an y means, electronic, mechanical, photog raphic, or otherwise, or used as the basis for manufacture or sale of any items without the prior written consent

of Cirrus Logic Inc.

Copyright

1995, 1996— Cirrus Logic, Inc. All rights reserved.

Contents

CONTENTS

The following are the differences between the December 1995 and November 1996 versions of

this technical reference manual:

●

CL-GD5446 Technical Reference Manual

Revision History

Information pertaining to the Revision B device has been added

November 1996 ii Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual

CONTENTS

Table of Contents

1. INTRODUCTION ..................................................................................... 1-2

1.1 Scope of Document............................................................................................. 1-2

1.2 Chip Types Covered............................................................................................ 1-2

1.3 Intended Audience .............................................................................................. 1-2

1.4 Conventions ........................................................................................................ 1-2

2. OVERVIEW ............................................................................................. 2-2

2.1 Features.............................................................................................................. 2-2

2.2 Major Components.............................................................................................. 2-4

2.3 VGA Core............................................................................................................ 2-4

2.4 PCI Bus Interface.............................................................................................. 2-12

2.5 BitBLT Engine ................................................................................................... 2-12

2.6 Video Capture ................................................................................................... 2-13

2.7 Video Window and Video Display ..................................................................... 2-13

2.8 Hardware/Software Compatibility...................................................................... 2-14

2.9 Computer Display Subsystem Architecture....................................................... 2-14

3. DATA BOOK ........................................................................................... 3-1

4. VGA CORE REGISTERS ....................................................................... 4-2

4.1 POS94: POS102 Access Control........................................................................ 4-5

4.2 POS102: POS102............................................................................................... 4-6

4.3 VSSM: 3C3 (Planar) Sleep Address ................................................................... 4-7

4.4 VSSM: 46E8 (Adapter) Sleep Address ............................................................... 4-8

4.5 MISC: Miscellaneous Output............................................................................... 4-9

4.6 FC: Feature Control........................................................................................... 4-11

4.7 FEAT: Input Status Register 0........................................................................... 4-12

4.8 STAT: Input Status Register 1........................................................................... 4-13

4.9 Pixel Mask......................................................................................................... 4-14

4.10 Palette Address (Read Mode, Write only)........................................................ 4-15

4.11 DAC State (Read only)..................................................................................... 4-16

4.12 Palette Address (Write Mode).......................................................................... 4-17

4.13 Palette Data....................................................................................................... 4-18

4.14 SRX: Sequencer Index...................................................................................... 4-19

4.15 SR0: Sequencer Reset...................................................................................... 4-20

4.16 SR1: Sequencer Clocking Mode....................................................................... 4-21

4.17 SR2: Sequencer Plane Mask............................................................................ 4-22

4.18 SR3: Sequencer Character Map Select............................................................ 4-23

4.19 SR4: Sequencer Memory Mode........................................................................ 4-25

4.20 CRX: CRTC Index............................................................................................. 4-26

4.21 CR0: CRTC Horizontal Total............................................................................. 4-29

Copyright 1996 – Cirrus Logic Inc. iii November 1996

CONTENTS

4.22 CR1: CRTC Horizontal Display End.................................................................. 4-30

4.23 CR2: CRTC Horizontal Blanking Start............................................................... 4-31

4.24 CR3: CRTC Horizontal Blanking End................................................................ 4-32

4.25 CR4: CRTC Horizontal Sync Start .................................................................... 4-34

4.26 CR5: CRTC Horizontal Sync End...................................................................... 4-35

4.27 CR6: CRTC Vertical Total................................................................................. 4-37

4.28 CR7: CRTC Overflow........................................................................................ 4-38

4.29 CR8: CRTC Screen A Preset Row-Scan .......................................................... 4-39

4.30 CR9: CRTC Character Cell Height.................................................................... 4-40

4.31 CRA: CRTC Text Cursor Start .......................................................................... 4-41

4.32 CRB: CRTC Text Cursor End............................................................................ 4-42

4.33 CRC: CRTC Screen Start Address High........................................................... 4-43

4.34 CRD: CRTC Screen Start Address Low............................................................ 4-44

4.35 CRE: CRTC Text Cursor Location High............................................................ 4-45

4.36 CRF: CRTC Text Cursor Location Low............................................................. 4-46

4.37 CR10: CRTC Vertical Sync Start....................................................................... 4-47

4.38 CR11: CRTC Vertical Sync End........................................................................ 4-48

4.39 CR12: CRTC Vertical Display End.................................................................... 4-50

4.40 CR13: CRTC Offset (Pitch)............................................................................... 4-51

4.41 CR14: CRTC Underline Row Scanline.............................................................. 4-52

4.42 CR15: CRTC Vertical Blank Start...................................................................... 4-53

4.43 CR16: CRTC Vertical Blank End....................................................................... 4-54

4.44 CR17: CRTC Mode Control............................................................................... 4-55

4.45 CR18: CRTC Line Compare.............................................................................. 4-57

4.46 CR22: Graphics Data Latches Readback (Read only)..................................... 4-58

4.47 CR24: Attribute Controller Toggle Readback (Read only) ............................... 4-59

4.48 CR26: Attribute Controller Index Readback (Read only).................................. 4-60

4.49 GRX: Graphics Controller Index........................................................................ 4-61

4.50 GR0: Set/Reset / Background Color Byte 0...................................................... 4-62

4.51 GR1: Set/Reset Enable / Foreground Color Byte 0........................................... 4-63

4.52 GR2: Color Compare......................................................................................... 4-64

4.53 GR3: Data Rotate.............................................................................................. 4-65

4.54 GR4: Read Map Select ..................................................................................... 4-66

4.55 GR5: Graphics Controller Mode........................................................................ 4-67

4.56 GR6: Miscellaneous.......................................................................................... 4-69

4.57 GR7: Color Don’t Care...................................................................................... 4-70

4.58 GR8: Bit Mask................................................................................................... 4-71

4.59 ARX: Attribute Controller Index......................................................................... 4-72

4.60 AR0–ARF: Attribute Controller Palette.............................................................. 4-73

4.61 AR10: Attribute Controller Mode ....................................................................... 4-74

4.62 AR11: Overscan (Border) Color........................................................................ 4-76

4.63 AR12: Color Plane Enable ................................................................................ 4-77

CL-GD5446 Technical Reference Manual

November 1996 iv Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual

4.64 AR13: Pixel Panning ......................................................................................... 4-78

4.65 AR14: Color Select............................................................................................ 4-79

CONTENTS

5. BITBLT EXTENSION REGISTERS ........................................................ 5-2

5.1 GR10–GR15: Color Expansion Foreground/Background Colors........................ 5-3

5.2 GR20–GR21: BLT Width Byte 0, 1...................................................................... 5-4

5.3 GR22–GR23: BLT Height Byte 0, 1 .................................................................... 5-5

5.4 GR24–GR25: BLT Destination Pitch Byte 0, 1.................................................... 5-6

5.5 GR26–GR27: BLT Source Pitch Byte 0, 1 .......................................................... 5-7

5.6 GR28–GR2A: BLT Destination Start Byte 0, 1, 2................................................ 5-8

5.7 GR2C–GR2E: BLT Source Start Byte 0, 1, 2...................................................... 5-9

5.8 GR2F: BLT Destination Left-Side Clipping........................................................ 5-10

5.9 GR30: BLT Mode .............................................................................................. 5-11

5.10 GR31: BLT Start/Status..................................................................................... 5-13

5.11 GR32: BLT ROP (Raster Operation)................................................................. 5-15

5.12 GR33: BLT Mode Extensions............................................................................ 5-17

5.13 GR34–GR35: Transparent BLT Key Color Byte 0, 1......................................... 5-18

6. VIDEO CAPTURE AND PLAYBACK REGISTERS ............................... 6-2

6.1 CR31: Video Window Horizontal Zoom Control.................................................. 6-4

6.2 CR32: Video Window Vertical Zoom Control ...................................................... 6-5

6.3 CR33: Video Window Horizontal Region 1 Size.................................................. 6-6

6.4 CR34: Video Window Region 2 Width................................................................. 6-7

6.5 CR35: Video Window Region 2 Source Data Size.............................................. 6-8

6.6 CR36: Video Window Horizontal Overflow.......................................................... 6-9

6.7 CR37: Video Window Vertical Start................................................................... 6-10

6.8 CR38: Video Window Vertical End.................................................................... 6-11

6.9 CR39: Video Window Vertical Overflow............................................................ 6-12

6.10 CR3A–CR3B: Video Buffer 1 Start Address Byte 0, 1 ...................................... 6-13

6.11 CR3C: Video Buffer 1 Start Address Byte 2...................................................... 6-14

6.12 CR3D: Video Buffer Address Offset.................................................................. 6-15

6.13 CR3E: Video Window Master Control............................................................... 6-16

6.14 CR3F: Miscellaneous Video Control ................................................................. 6-18

6.15 CR50: Video Capture Control............................................................................ 6-20

6.16 CR51: Video Capture Data Format................................................................... 6-22

6.17 CR52: Video Capture Horizontal Data Reduction............................................. 6-23

6.18 CR53: Video Capture Vertical Data Reduction ................................................. 6-24

6.19 CR54: Video Capture Horizontal Delay............................................................. 6-25

6.20 CR56: Video Capture Vertical Delay................................................................. 6-26

6.21 CR57: Video Capture Maximum Height............................................................ 6-27

6.22 CR58: Video Capture Miscellaneous Control.................................................... 6-28

6.23 CR59–CR5A: Video Buffer 2 Start Address Byte 0, 1....................................... 6-29

6.24 CR5B: Video Window Brightness Adjust........................................................... 6-30

Copyright 1996 – Cirrus Logic Inc. v November 1996

CONTENTS

6.25 CR5C: Luminance-Only Capture Control.......................................................... 6-31

6.26 CR5D: Video Window Pixel Alignment.............................................................. 6-32

6.27 CR5E: Double-Buffer Control............................................................................ 6-33

6.28 GR1C–GR1F: Chroma Key............................................................................... 6-35

CL-GD5446 Technical Reference Manual

7. PCI CONFIGURATION REGISTERS ..................................................... 7-2

7.1 PCI00: PCI Device/Vendor ID............................................................................. 7-3

7.2 PCI04: PCI Status/Command.............................................................................. 7-4

7.3 PCI08: PCI Class Code....................................................................................... 7-5

7.4 PCI10: PCI Display Memory Base Address........................................................ 7-6

7.5 PCI14: PCI Relocatable I/O / GPIO Base Address (Revision A)......................... 7-7

7.6 PCI14: PCI VGA/BitBLT Register Base Address (Revision B)............................ 7-8

7.7 PCI18: PCI GPIO Base Address (Revision B).................................................... 7-9

7.8 PCI2C: PCI Subsystem/Subsystem Vendor ID (Revision B) ............................ 7-10

7.9 PCI30: PCI Expansion ROM Base Address Enable.......................................... 7-11

7.10 PCI3C: PCI Interrupt ......................................................................................... 7-12

8. MISCELLANEOUS EXTENSION REGISTERS ..................................... 8-2

8.1 SR6: Key............................................................................................................. 8-4

8.2 SR7: Extended Sequencer Mode........................................................................ 8-5

8.3 SR8: DDC2B/EEPROM Control.......................................................................... 8-7

8.4 SR9–SRA: Scratch Pad 0, 1............................................................................... 8-9

8.5 SRB–SRE: VCLK0–VCLK3 Numerator............................................................. 8-10

8.6 SRF: DRAM Control.......................................................................................... 8-11

8.7 SR10: Graphics Cursor X Position.................................................................... 8-13

8.8 SR11: Graphics Cursor Y Position.................................................................... 8-14

8.9 SR12: Graphics Cursor Attribute....................................................................... 8-15

8.10 SR13: Graphics Cursor Pattern Address Offset................................................ 8-16

8.11 SR14–SR15: Scratch Pad 2, 3.......................................................................... 8-17

8.12 SR16: Display FIFO Threshold Control............................................................. 8-18

8.13 SR17: Configuration Readback and Extended Control..................................... 8-19

8.14 SR18: Signature Generator Control.................................................................. 8-20

8.15 SR19: Signature Generator Result Low-Byte.................................................... 8-22

8.16 SR1A: Signature Generator Result High-Byte .................................................. 8-23

8.17 SR1B–SR1E: VCLK0–VCLK3 Denominator and Post-Scalar........................... 8-24

8.18 SR1F: MCLK Select.......................................................................................... 8-25

8.19 GR9: Offset Register 0...................................................................................... 8-26

8.20 GRA: Offset Register 1...................................................................................... 8-28

8.21 GRB: Graphics Controller Mode Extensions..................................................... 8-29

8.22 GRC: Color Key/Chroma Key Compare............................................................ 8-31

8.23 GRD: Color Key/Mask/Chroma Key.................................................................. 8-32

8.24 GRE: Power Management ................................................................................ 8-33

8.25 GR16: Active Display Line Readback Byte 0.................................................... 8-35

November 1996 vi Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual

8.26 GR17: Active Display Line Readback Byte 1.................................................... 8-36

8.27 GR18: Extended DRAM Controls...................................................................... 8-37

8.28 GR19: GPIO Port Configuration........................................................................ 8-39

8.29 GR1A–GR1B: Scratch Pad 4, 5........................................................................ 8-40

8.30 CR19: Interlace End.......................................................................................... 8-41

8.31 CR1A: Miscellaneous Control ........................................................................... 8-42

8.32 CR1B: Extended Display Controls .................................................................... 8-44

8.33 CR1C: Sync Adjust and GENLOCK.................................................................. 8-46

8.34 CR1D: Overlay Extended Control ..................................................................... 8-48

8.35 CR25: Part Status (Read only).......................................................................... 8-50

8.36 CR27: ID (Read only)........................................................................................ 8-51

8.37 HDR: Hidden DAC Register.............................................................................. 8-52

CONTENTS

9. PROGRAMMING NOTES ....................................................................... 9-2

9.1 Introduction.......................................................................................................... 9-2

9.2 Resource Addressing.......................................................................................... 9-2

9.3 Pixel Addressing and Formats .......................................................................... 9-11

9.4 BitBLT Engine ................................................................................................... 9-18

9.5 Video Window ................................................................................................... 9-31

9.6 Video Capture ................................................................................................... 9-41

9.7 Overlay: CL-GD543X/’4X Compatibility............................................................. 9-47

9.8 Hardware Cursor............................................................................................... 9-53

9.9 Frequency Synthesizer Programming............................................................... 9-54

9.10 Power Management.......................................................................................... 9-57

9.11 CRTC Programming.......................................................................................... 9-58

9.12 Chip Identification.............................................................................................. 9-61

9.13 CL-GD5446 Interrupt System............................................................................ 9-61

9.14 Programming Examples.................................................................................... 9-62

10. DETAILED PIN DESCRIPTIONS ......................................................... 10-2

10.1 Host Interface: PCI Bus..................................................................................... 10-2

10.2 Video Interface.................................................................................................. 10-4

10.3 Display Memory Interface.................................................................................. 10-6

10.4 General-Purpose I/O......................................................................................... 10-7

10.5 V-Port

10.6 Miscellaneous Pins............................................................................................ 10-8

10.7 Clock Synthesizer.............................................................................................. 10-8

10.8 Power and Ground............................................................................................ 10-9

............................................................................................................. 10-7

11. ELECTRICAL SPECIFICATIONS ........................................................ 11-2

11.1 Absolute Maximum Ratings............................................................................... 11-2

11.2 DC Specifications (Digital)................................................................................. 11-3

11.3 DAC Characteristics.......................................................................................... 11-4

11.4 AC Specifications.............................................................................................. 11-5

Copyright 1996 – Cirrus Logic Inc. vii November 1996

CONTENTS

CL-GD5446 Technical Reference Manual

APPENDIXES

A1 CONNECTOR PINOUTS ......................................................................A1-2

A2 REVISION B NOTES ............................................................................A2-2

1. INTRODUCTION .............................................................................................. A2-2

2. DESIGN CHANGES .........................................................................................A2-2

2.1 PCI10 Claims 32 Mbytes....................................................................... A2-2

2.2 PCI14 Supports VGA and BitBLT Registers......................................... A2-2

2.3 PCI18 Supports GPIO........................................................................... A2-2

2.4 PCI2C Supports Subsystem and Subsystem Vendor ID ...................... A2-2

2.5 General-Purpose I/O Configuration....................................................... A2-3

B1 LAYOUT GUIDELINES .........................................................................B1-2

1. INTRODUCTION .............................................................................................. B1-2

2. PARTS PLACEMENT AND ADAPTER CARDS ..............................................B1-2

2.1 PCI Bus Adapter Card........................................................................... B1-2

2.2 Motherboard.......................................................................................... B1-3

3. POWER ............................................................................................................ B1-3

4. GROUND ......................................................................................................... B1-4

5. DECOUPLING CAPACITORS .........................................................................B1-5

6. SYNTHESIZER ................................................................................................B1-6

7. IREF CIRCUITRY ............................................................................................. B1-6

8. RGB LINES ...................................................................................................... B1-6

9. DRAM ARRAY ................................................................................................. B1-6

B2 PCI BUS REFERENCE DESIGN ..........................................................B2-2

1. INTRODUCTION .............................................................................................. B2-2

2. PCI BUS INTERFACE ...................................................................................... B2-2

2.1 Bus Connections................................................................................... B2-2

2.2 INTR# Pin............................................................................................. B2-3

2.3 VGA BIOS............................................................................................. B2-3

3. DISPLAY MEMORY INTERFACE .................................................................... B2-3

3.1 Memory Configurations......................................................................... B2-3

3.2 Damping Resistors................................................................................ B2-3

4. MONITOR INTERFACE ................................................................................... B2-4

4.1 RGB Lines............................................................................................. B2-4

4.2 Sync Lines............................................................................................. B2-4

4.3 Monitor ID.............................................................................................. B2-4

5. FEATURE CONNECTOR ................................................................................ B2-5

6. VMI HOST PORT ............................................................................................. B2-6

7. POWER DISTRIBUTION AND CONDITIONING ............................................. B2-8

7.1 Introduction ........................................................................................... B2-8

7.2 Dedicated Ground Plane....................................................................... B2-8

7.3 Dedicated Power Plane......................................................................... B2-8

November 1996 viii Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual

7.4 Power Bypassing.................................................................................. B2-8

7.5 Analog Power Conditioning................................................................... B2-9

8. CONFIGURATION RESISTORS ..................................................................... B2-9

9. DUAL-FREQUENCY SYNTHESIZERS SUPPORT ....................................... B2-10

9.1 Synthesizer Reference........................................................................ B2-10

9.2 Synthesizer Filters.............................................................................. B2-10

10. DAC CURRENT REFERENCE ...................................................................... B2-10

11. PCI BUS SCHEMATICS ................................................................................ B2-10

CONTENTS

B3 MEMORY CONFIGURATIONS AND TIMING ......................................B3-2

1. INTRODUCTION .............................................................................................. B3-2

2. DRAM CONFIGURATIONS ............................................................................. B3-2

3. CL-GD5440/’46 DUAL LAYOUT CONSIDERATIONS ..................................... B3-3

4. DRAM CONNECTION TABLES .......................................................................B3-3

5. DRAM TIMING REQUIREMENTS ...................................................................B3-7

5.1 Extended RAS# Timing......................................................................... B3-7

5.2 EDO Timing.......................................................................................... B3-7

5.3 DRAM Timing Equations Evaluated...................................................... B3-8

6. MCLK vs. DISPLAY MODE REQUIREMENTS ..............................................B3-11

7. BANDWIDTH NOTE FOR CL-GD5440 WITH 64-BIT INTERFACE .............. B3-12

B4 CURRENT REFERENCE ......................................................................B4-2

1. INTRODUCTION .............................................................................................. B4-2

2. RSet: FULL-SCALE CURRENT SET RESISTOR VALUE ...............................B4-2

B5 CONFIGURATION NOTES ...................................................................B5-2

1. INTRODUCTION .............................................................................................. B5-2

2. CONFIGURATION SUMMARY ........................................................................ B5-2

3. CONFIGURATION DETAILS ........................................................................... B5-3

B6 SIGNATURE GENERATOR .................................................................B6-2

1. INTRODUCTION .............................................................................................. B6-2

2. TESTING .......................................................................................................... B6-2

B7 PIN SCAN .............................................................................................B7-2

1. INTRODUCTION .............................................................................................. B7-2

2. TEST METHOD ................................................................................................ B7-2

2.1 Entering Pin-Scan Mode....................................................................... B7-2

2.2 Exiting Pin-Scan Mode.......................................................................... B7-2

3. PIN SCAN ORDER .......................................................................................... B7-2

B8 DDC2B/I

1. INTRODUCTION .............................................................................................. B8-2

2

C SUPPORT ..........................................................................B8-2

B9 GENLOCK SUPPORT ..........................................................................B9-2

1. INTRODUCTION .............................................................................................. B9-2

2. GENLOCK ON THE CL-GD5446 ..................................................................... B9-2

3. VSYNC GENLOCK PROGRAMMING ............................................................. B9-3

4. HSYNC GENLOCK PROGRAMMING .............................................................B9-3

Copyright 1996 – Cirrus Logic Inc. ix November 1996

CONTENTS

CL-GD5446 Technical Reference Manual

B10MANUFACTURING TEST ..................................................................B10-2

1. INTRODUCTION ............................................................................................B10-2

2. OPERATING INSTRUCTIONS ......................................................................B10-2

3. INSTALLING AND STARTING MFGTST .......................................................B10-2

3.1 Command Line Options...................................................................... B10-3

4. USING MFGTST ............................................................................................B10-4

4.1 Special Keystrokes.............................................................................. B10-4

5. UPDATES ......................................................................................................B10-6

B11GENERAL-PURPOSE I/O ..................................................................B11-2

1. INTRODUCTION ............................................................................................B11-2

2. GPIO CONFIGURATION ...............................................................................B11-2

3. PINS REDEFINED .........................................................................................B11-3

4. CYCLE TIMING CONTROL ...........................................................................B11-4

5. GPIO PROGRAMMING EXAMPLE ...............................................................B11-7

C1 SOFTWARE SUPPORT .......................................................................C1-2

1. INTRODUCTION ..............................................................................................C1-2

2. CL-GD5446 VGA SOFTWARE UTILITIES ......................................................C1-2

2.1 CLMODE — A Display Mode Configuration Utility................................ C1-2

2.2 VGA.EXE — RAMBIOS Utility.............................................................. C1-2

2.3 OEMSI

2.4 WINMODE Utility................................................................................... C1-3

3. CL-GD5446 VGA SOFTWARE DRIVERS .......................................................C1-4

3.1 Driver Applicability................................................................................. C1-4

(OEM System Integration) Utility.............................................. C1-3

C2 VGA BIOS .............................................................................................C2-2

1. BIOS OVERVIEW ............................................................................................C2-2

1.1 Main BIOS Features.............................................................................. C2-2

1.2 Extended Display Mode Support........................................................... C2-2

1.3 Direct-Color Operation.......................................................................... C2-2

1.4 High Performance................................................................................. C2-2

1.5 System Integration................................................................................ C2-3

1.6 Customization....................................................................................... C2-3

1.7 Compatibility.......................................................................................... C2-3

2. CL-GD5446 VGA BIOS INITIALIZATION .........................................................C2-3

3. VIDEO BIOS INTERRUPT VECTORS .............................................................C2-5

4. INTERRUPT 10h: INDEX .................................................................................C2-6

5. DESCRIPTION OF FUNCTIONS .....................................................................C2-8

5.1 Function 00h: Set Display Mode.............................................. C2-8

5.2 Function 01h: Set Cursor Type................................................ C2-9

5.3 Function 02h: Set Cursor Position......................................... C2-10

5.4 Function 03h: Get Cursor Position......................................... C2-10

November 1996 x Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual

5.5 Function 04h: Get Light Pen Position

(no longer supported) .........................................................................C2-11

5.6 Function 05h: Select Active Display Page.......................................... C2-11

5.7 Function 06h: Window Scroll Up......................................................... C2-11

5.8 Function 07h: Window Scroll Down.................................................... C2-12

5.9 Function 08h: Read Character/Attribute at Cursor Position................ C2-12

5.10 Function 09h: Write Character/Attribute at Cursor Position................ C2-13

5.11 Function 0Ah: Write Character at Cursor Position.............................. C2-14

5.12 Function 0Bh, Subfunction 00h: Set Background/Border Color.......... C2-14

5.13 Function 0Bh, Subfunction 01h: Select Palette Set............................ C2-15

5.14 Function 0Ch: Write Dot (Pixel) .......................................................... C2-15

5.15 Function 0Dh: Read Dot (Pixel).......................................................... C2-15

5.16 Function 0Eh: Write Character to Active RAM in Teletype Mode....... C2-16

5.17 Function 0Fh: Get Display State......................................................... C2-16

5.18 Function 10h, Subfunction 00h: Set Individual Palette Register

(Internal Palette Register) ...................................................................C2-16

5.19 Function 10h, Subfunction 01h: Set Overscan (Border)

Register ..............................................................................................C2-17

5.20 Function 10h, Subfunction 02h: Set All Palette Registers and

OverScan Register .............................................................................C2-17

5.21 Function 10h, Subfunction 03h: Toggle Intensify/Blinking Bit............. C2-17

5.22 Function 10h, Subfunction 07h: Read Individual Palette Register

(Internal Palette Register) ...................................................................C2-18

5.23 Function 10h, Subfunction 08h: Read OverScan (Border) Register... C2-18

5.24 Function 10h, Subfunction 09h: Read All Palette Registers and OverScan

Register ..............................................................................................C2-18

5.25 Function 10h, Subfunction 10h: Set Individual Color Register

(RAMDAC/External Palette Registers) ...............................................C2-18

5.26 Function 10h, Subfunction 12h: Set Block of Color Registers............ C2-19

5.27 Function 10h, Subfunction 13h: Select Color Page

(Not valid in Mode 13h) .......................................................................C2-19

5.28 Function 10h, Subfunction 15h: Read Individual Color Register

(RAMDAC/External Palette Registers) ...............................................C2-20

5.29 Function 10h, Subfunction 17h: Read Block of Color Registers......... C2-20

5.30 Function 10h, Subfunction 1Ah: Read Current State of Color Page

(Not valid in Mode 13h) .......................................................................C2-21

5.31 Function 10h, Subfunction 1Bh: Sum Color Values to

Grayshades ........................................................................................C2-21

5.32 Function 11h, Subfunction 00h: Load User Text Font ........................ C2-21

5.33 Function 11h, Subfunction 01h: Load 8 × 14 ROM Font..................... C2-22

5.34 Function 11h, Subfunction 02h: Load 8 × 8 ROM Font....................... C2-23

5.35 Function 11h, Subfunction 03h: Select Block Specifier ...................... C2-24

5.36 Function 11h, Subfunction 04h: Load 8 × 16 ROM Font..................... C2-25

CONTENTS

Copyright 1996 – Cirrus Logic Inc. xi November 1996

CONTENTS

5.37 Function 11h, Subfunction 10h: Load User Text Font and Reprogram

Controller ............................................................................................ C2-25

5.38 Function 11h, Subfunction 11h: Load 8 × 14 ROM Font and Reprogram

Controller ............................................................................................ C2-27

5.39 Function 11h, Subfunction 12h: Load 8 × 8 ROM Font and Reprogram

Controller ............................................................................................ C2-28

5.40 Function 11h, Subfunction 14h: Load 8 × 16 ROM Font and Reprogram

Controller ............................................................................................ C2-29

5.41 Function 11h, Subfunction 20h: Set Pointer of User’s Graphics Font Table

to Interrupt 1Fh ...................................................................................C2-30

5.42 Function 11h, Subfunction 21h: Set Pointer of User’s Graphics Font Table

to Interrupt 43h ...................................................................................C2-31

5.43 Function 11h, Subfunction 22h: Set Pointer of ROM 8 × 14 Graphics

Font Table to Interrupt 43h .................................................................C2-31

5.44 Function 11h, Subfunction 23h: Set Pointer of ROM 8 × 8 Graphics

Font Table to Interrupt 43h .................................................................C2-32

5.45 Function 11h, Subfunction 24h: Set Pointer of ROM 8 × 16 Graphics

Font Table to Interrupt 43h .................................................................C2-32

5.46 Function 11h, Subfunction 30h: Get Pointer Information of

Fonts ...................................................................................................C2-33

5.47 Function 12h, Subfunction 10h: Get Current Display

Configuration ......................................................................................C2-33

5.48 Function 12h, Subfunction 20h: Alternate PrintScreen Handler ......... C2-34

5.49 Function 12h, Subfunction 30h: Select Scanlines for

Text Modes ......................................................................................... C2-34

5.50 Function 12h, Subfunction 31h: Enable/Disable Default Palette

Loading ............................................................................................... C2-35

5.51 Function 12h, Subfunction 32h: Enable/Disable Display.................... C2-35

5.52 Function 12h, Subfunction 33h: Enable/Disable

Summing-to-Grayshades ....................................................................C2-35

5.53 Function 12h, Subfunction 34h: Enable/Disable Cursor

Emulation ............................................................................................C2-36

5.54 Function 12h, Subfunction 35h: Switch Display.................................. C2-36

5.55 Function 12h, Subfunction 36h: Enable/Disable Screen Display........ C2-37

5.56 Function 13h: Write Teletype String.................................................... C2-37

5.57 Function 1Ah, Subfunction 00h: Get Display Combination Code

(DCC) ..................................................................................................C2-38

5.58 Function 1Ah, Subfunction 01h: Set Display Combination Code

(DCC) ..................................................................................................C2-38

5.59 Function 1Bh: Collection of Display Information................................. C2-39

5.60 Function 1Ch, Subfunction: 00h: Get Buffer Size for

Display State .......................................................................................C2-42

5.61 Function 1Ch, Subfunction 01h: Saving Display State ....................... C2-42

5.62 Function 1Ch, Subfunction 02h: Restore Display State...................... C2-43

6. VGA SLEEP MODE AND DISPLAY SWITCHING .........................................C2-44

7. ADDRESS MAPS ...........................................................................................C2-44

CL-GD5446 Technical Reference Manual

November 1996 xii Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual

CONTENTS

C3 BIOS EXTENSIONS .............................................................................C3-2

1. INTRODUCTION ..............................................................................................C3-2

2. CIRRUS LOGIC EXTENSIONS .......................................................................C3-2

2.1 Function Summary................................................................................ C3-2

2.2 Inquire VGA Type.................................................................................. C3-3

2.3 Inquire BIOS Version Number............................................................... C3-4

2.4 Inquire Cirrus Logic Design Revision Code .......................................... C3-4

2.5 Return Installed Memory....................................................................... C3-4

2.6 Inquire User Options............................................................................. C3-4

2.7 Query Display Mode Availability............................................................ C3-5

2.8 Read Monitor ID/Type........................................................................... C3-5

2.9 Set Monitor Type................................................................................... C3-5

2.10 Process Generic Fixup Table................................................................ C3-7

2.11 Return Chip Capabilities....................................................................... C3-7

2.12 Get High Refresh.................................................................................. C3-7

2.13 Set High Refresh................................................................................... C3-7

3. VESA

3.1 Goals and Objectives............................................................................ C3-8

3.2 Standard VGA BIOS ............................................................................. C3-9

3.3 Super VGA Mode Numbers .................................................................. C3-9

4. EXTENDED VESA

4.1 Status Information............................................................................... C3-10

4.2 Function 00h — Return Super VGA Information................................. C3-10

4.3 Function 01h — Return Super VGA Mode Information....................... C3-12

4.4 Function 02h — Set Super VGA Display Mode .................................. C3-17

4.5 Function 03h — Return Current Display Mode................................... C3-17

4.6 Function 04h — Save/Restore Super VGA Display State................... C3-17

4.7 Function 05h — CPU Display Memory Window Control..................... C3-18

4.8 Function 06h — Set/Get Logical Scanline Length .............................. C3-19

4.9 Function 07h — Set/Get Display Start................................................ C3-20

4.10 Function 08h — Set/Get DAC Palette Control.................................... C3-20

4.11 Function 15h — Display Identification Extensions.............................. C3-22

SUPER VGA STANDARD ................................................................... C3-8

BIOS FUNCTIONS ........................................................C3-10

D1 CIRRUS LOGIC BBS, FTP, AND WWW ..............................................D1-2

1. INTRODUCTION ..............................................................................................D1-2

2. FIRST-TIME LOG ON ......................................................................................D1-3

3. UPGRADED ACCESS .....................................................................................D1-3

3.1 Using the FTP Server............................................................................ D1-3

3.2 Web Access.......................................................................................... D1-4

E1 GLOSSARY ..........................................................................................E1-2

BIBLIOGRAPHY ......................................................................................................... E1-13

Copyright 1996 – Cirrus Logic Inc. xiii November 1996

CONTENTS

CL-GD5446 Technical Reference Manual

INDEXES

REGISTER INDEX ..................................................................................F-2

INDEX ..................................................................................................... F-8

November 1996 xiv Copyright 1996 – Cirrus Logic Inc.

1

Introduction

INTRODUCTION CL-GD5446 Technical Reference Manual

1. INTRODUCTION

1.1 Scope of Document

This manual provides a technical discussion of the CL-GD5446 VisualMedia accelerator. This

manual includes descriptions of each major component integrated into the device, a data book,

detailed information on each register, a BIOS description, and appendices intended to assist hardware and software designers.

1.2 Chip Types Covered

This manual documents the CL-GD5446. Table 1-1 shows the production versions covered.

Table 1-1. Production Versions Covered

Revision A B

CL-GD5446

The CL-GD5446 ID register — CR27, reads back a value specifying the CL-GD5446. Refer to

Chapter 8, “Miscellaneous Extension Registers”, for further information. The ID is also in register

PCI00.

✔✔

1.3 Intended Audience

This manual is intended for a technically sophisticated audience. It is assumed that the reader is

familiar with assembly language progr amming on the 8088/8086, 80286/80386/80486, P entium

or similar microprocessor, and understands the fundamentals of computer generated graphics

display technology.

Hardware engineers should find Chapter 3, “Data Book”, useful. It contains the pinouts and pin

summary. In addition, Chapter 10 contains the detailed pin descriptions and Chapter 11 contains

the DC and AC specifications. Appendix B1 and Appendix B2 contain board design and layout

information.

Software engineers should find Chapters 4–8 (register descriptions) useful for BIOS- and driverlevel codes. All registers are described to the bit level. Chapter 9 contains programming notes.

1.4 Conventions

This section discusses conventions used throughout this document. Conventions include acronyms, abbreviations, and nomenclature usage. For a quick reference of acronyms see Table 1-2.

,

Bits

Bits are always listed in descending order, most-significant (highest number) to least-significant

(lowest number). When discussing a bit field within a register or memory, the bit number of the

most-significant bit is given on the left, follo wed b y a colon (:) and then the bit number of the leastsignificant bit (for example, bits 7:0). A field consists of a set of adjoining bits with common functionality. Registers consist of fields of one or more bits.

November 1996 1-2 Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual INTRODUCTION

Table 1-2. Acronym Quick Reference

Acronym Definition

AC alternating current

ALU arithmetic logic unit

ATE automatic test equipment

BIOS basic input/output system

BitBLT, BLT bit boundary block transfer

bpp bits per pixel

CAD computer-aided design

CAS column address strobe

CGA color graphics adapter

CLUT color lookup table

CMOS complementary metal-oxide

CPU central processing unit

CRT cathode ray tube

CRTC CRT controller

DAC digital-to-analog converter

DC direct current

DDA digital differential algorithm

DDC display data channel

DMI desktop management signaling

DPMS display power management

DRAM dynamic random access memory

dword doubleword

EEPROM electrically erasable/programmable

EGA enhanced graphics adapter

EPROM electrically programmable read-only

EV AFC extended VESA

FIFO first in/first out

GPIO general-purpose IO

GSC graphics system controller

GUI graphical user interface

HDR Hidden DAC register

HRQ host read queue

HSYNC/VSYNC horizontal/vertical synchronization

HWQ host write queue

IC integrated circuit

I/O input/output

LBI local bus interface

LSB least-significant bit

semiconductor

signaling

read-only memory

memory

connector

advanced feature

Acronym Definition

LUT lookup table

MA memory arbiter

MC memory controller

MCC monochrome-to-color converter

MD memory data

MMI/O memory-mapped I/O

MSB most-significant bit

OFU operand fetch unit

OSU operand storage unit

PCI peripheral component

PFS programmable frequency

PLL phase-locked loop

PQFP plastic quad-flat pack

qword two dwords

RAC Rambus

RAM random-access memory

RAS row address strobe

RDRAM Rambus

RGB red, green, and blue

RIF Rambus

ROPs raster operations

RSU result storage unit

R/W read/write

SC serial clock

SG signature generator

SGRAM synchronous graphics RAM

SRAM static random-access memory

TSR terminate and stay resident

TTL transistor-transistor logic

VBE VESA BIOS extensions

VBI vertical blanking interval

VDD virtual device driver

VESA

VGA video graphics array

VL VESA

VPM video port manager

VRAM video random-access memory

WE transparency write enable

interconnect

synthesizer

access channel

dynamic random-access

memory

interface

Video Electronics Standards

Association

local

Copyright 1996 – Cirrus Logic Inc. 1-3 November 1996

INTRODUCTION CL-GD5446 Technical Reference Manual

Acronyms

Throughout this manual, the first usage of all acronyms has the definition follo wing in parentheses.

Table 1-2 on page 1-3 lists most of the acronyms used in this manual. F or further definitions, refer

to Appendix E1, “Glossary and Bibliography”.

Abbreviations

The unit ‘Kbyte’ designates 1024 bytes. The unit ‘Mbyte’ designates 1,048,576 bytes (1024

squared). The unit ‘Gbyte’ designates 1,024 megabytes. The unit ‘Hz’ designates hertz. The unit

‘kHz’ designates 1,000 hertz. The unit ‘MHz’ designates 1,000 kilohertz. The unit ‘ns’ designates

nanosecond. The unit ‘µs’ designates microsecond (1,000 nanoseconds). The unit ‘ms’ designates millisecond (1,000 microseconds). The unit ‘mA’ designates milliampere. The use of ‘tbd’ in

tables indicates values that are ‘to be determined’. The unit ‘µF’ designates the capacitance measurement micro-farad (10

-6

farad). N/A designates ‘not av ailab le’. The use of ‘n/c’ indicates the pin

is a ‘no connect’.

Numeric Naming

Hexadecimal numbers are represented with all letters in upper case and a lower-case ‘h’ is

appended to them (for example, ‘14h’, ‘3A7h’, and ‘C000h’ are hexadecimal numbers). Programming examples may use the C convention (prepend 0x to a hex number). Numbers not indicated

by an ‘h’ are decimal. Octal numbers are not used in this manual.

Reserved

When a system memory or I/O address is referred to as ‘reserved’, it indicates that writing to that

address is not permitted. Reserved bits

must

be written as ‘0’ to maintain upward compatibility.

Read-Only

The word ‘read-only’ is used to indicate registers and bits that can be read, but not written to.

November 1996 1-4 Copyright 1996 – Cirrus Logic Inc.

2

Overview

OVERVIEW CL-GD5446 Technical Reference Manual

2. OVERVIEW

The CL-GD5446 VisualMedia accelerator is a 64-bit DRAM based SV GA controller with hardwareaccelerated BitBLT, video playback, and video capture to the frame buffer.

The CL-GD5446 combines the Cirrus Logic V -P ort with a multi-format frame buff er for cost eff ective video playback. The V-Por t captures real-time video into the frame buffer with optional data

reduction. The video is typically displayed in the hardware video window with optional interpolated

zooming. The video can be of a different format (for example, 16-bpp YUV 4:2:2) than the graphic

format (for example, 8-bpp palettized VGA format).

The CL-GD5446 features a 64-bit GUI BitBLT engine with double-b uffered, memory-mapped control registers. Transparency is supported with color expansion for all color depths, and supported

without color expansion for 8- and 16-bpp graphics modes.

Highly integrated, the CL-GD5446 includes a programmable dual-frequency synthesizer and palette DA C, allowing a motherboard video playback solution with as fe w as three ICs plus the video

decoder.

Production Revision B of the CL-GD5446 is specifically designed for compliance with PC97. The

differences between Revision A and Revision B are detailed in Appendix A2, “Revision B Notes”.

2.1 Features

Table 2-1 presents a list of the major features of the CL-GD5446 VisualMedia accelerator.

Table 2-1. CL-GD5446 Features List

GUI acceleration width (in bits) 64

Maximum dot clock 135 MHz

Maximum memory clock 80 MHz

Multimedia ready

Integrated video playback support

Video capture

Video windowing

Color key, chroma key occlusion support

YUV and AccuPak video support

Unique planar assist video support

Multi-format frame buffer

Features CL-GD5446

✔

✔

✔

✔

✔

✔

✔

✔

Color space conversion

Interpolated zooming (independent for X and Y)

November 1996 2-2 Copyright 1996 – Cirrus Logic Inc.

✔

✔

CL-GD5446 Technical Reference Manual OVERVIEW

Table 2-1. CL-GD5446 Features List

(cont.)

Features CL-GD5446

Transparent source BitBLT

Active display line readback

‘Page flip’ support

I2C support

8- or 16-bit General-Purpose I/O bus

DDC2B support

‘Green PC’ power-saving features

Direct PCI bus interface (2.1-compliant)

VESA pass-through feature connector

Resolutions up to 1280 × 1024 (see inside front cover)

Integrated triple 8-bit DAC

Programmable dual-clock synthesizer

64-bit DRAM display memory interface

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

✔

Memory size (Mbytes) 1, 2, 3, 4

4-, 16-bit-wide DRAMs

EDO DRAM support

128K × 16, 128K × 32 DRAM support

16-bit Pixel bus

CL-GD542X register- and software-compatible

Low-power CMOS, 208-pin PQFP/HQFP package

100% hardware- and BIOS-compatible with

IBM

VGA display standards

PC97 compliance Revision B

✔

✔

✔

✔

✔

✔

✔

Copyright 1996 – Cirrus Logic Inc. 2-3 November 1996

OVERVIEW CL-GD5446 Technical Reference Manual

2.2 Major Components

The CL-GD5446 incorporates all of the logic listed in Table 2-2 into a single integrated chip.

These components are discussed in the following sections.

Table 2-2. CL-GD5446 Major Components

Logic Component Section

VGA core: sequencer 2.3.1

VGA core: CRT controller 2.3.2

VGA core: graphics controller 2.3.3

VGA core: attribute controller 2.3.4

VGA core: programmable dual-frequency synthesizer 2.3.5

VGA core: palette DAC 2.3.6

PCI bus interface 2.4

BitBLT engine 2.5

Video capture 2.6

Video window and video display 2.7

General-purpose I/O 2.7.2

DDC2B interface 2.7.1

In describing the CL-GD5446, it is useful to retain the identity of the original major subsections

found in the IBM EGA and VGA controllers. The architectures of these major subsections, as

well as CL-GD5446 enhancements, are further described in the following sections.

NOTE: The diagrams in these sections are functional block diag rams of the components and are not

intended to represent actual implementation.

2.3 VGA Core

2.3.1 Sequencer

The sequencer controls access to the display memory. It ensures that the necessary screen

refresh and dynamic memory refresh cycles are executed, and that the remaining memory

cycles are made availab le f or CPU read/write operations, BitBLT read/write operations, and VPort write operations.

The sequencer consists of a memory arbitrator and memory controller. It accepts requests

from memory address counters associated with the CRTC, and address-transformation logic

associated with the graphics controller . It uses the display FIFOs to deliver data to the displa y

pipeline, and the write buffer to transfer data to the graphics controller. The Memor y

Sequencer registers are described in Chapter 4, “VGA Core Registers”.

The memory controller generates the signals and addresses necessary for accessing display

memory. The memory controller is driven by a MCLK (memory clock) optimized for the speed

of the DRAM used, independent of the VCLK (video clock). The memory controller can

November 1996 2-4 Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual OVERVIEW

generate optimized timing for EDO DRAMs and oper ate with an MCLK of up to 80 MHz. The memory arbitrator and host bus interface are also driven by the MCLK.

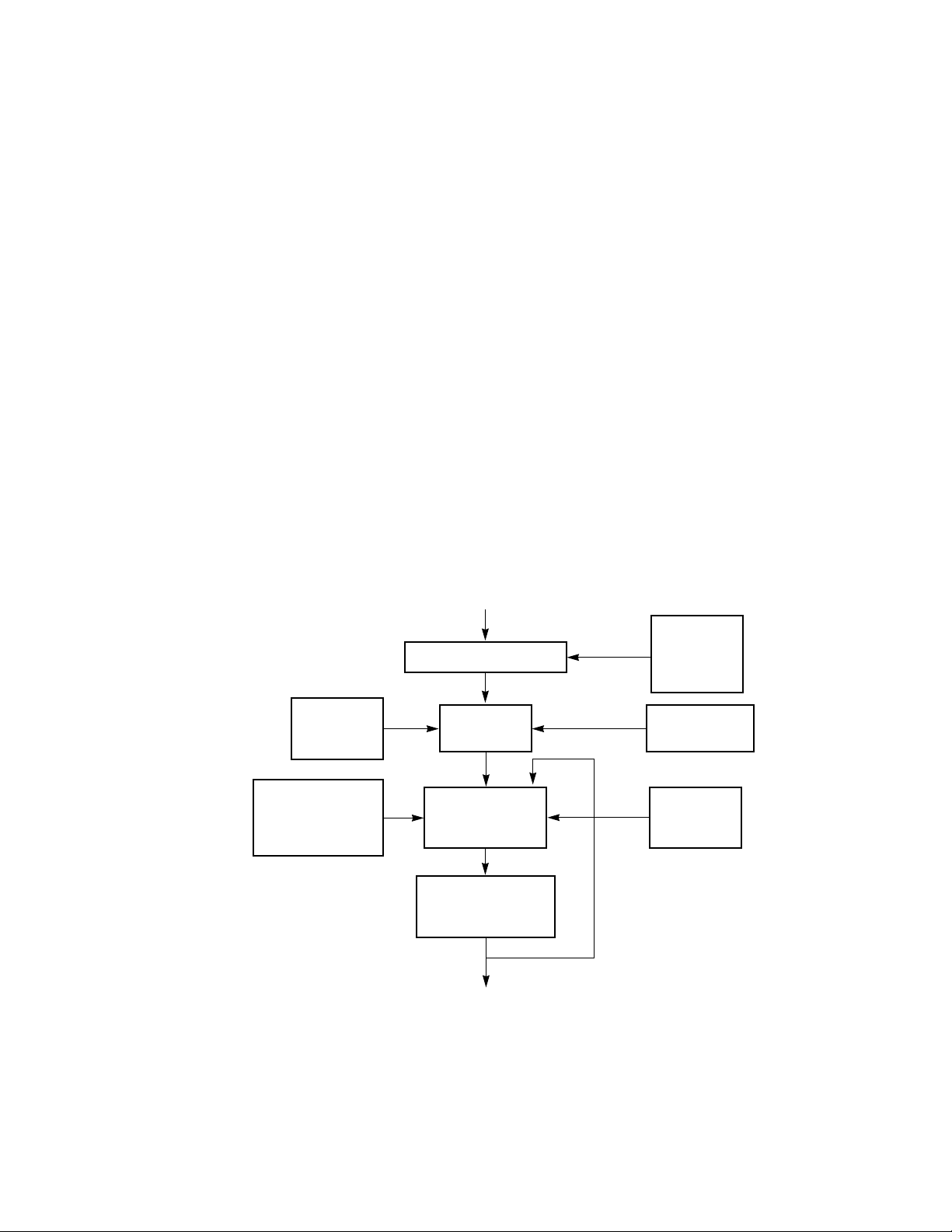

CRT

CONTROLLER

GRAPHICS

CONTROLLER

BITBLT

ENGINE

V-Port

HOST

BITBLT

V-Port

2.3.2 CRT Controller

The CRTC (CRT controller) generates the horizontal and vertical synchronization signals for the

CRT display. The CRTC allows configur able horizontal and vertical timing and polarity , cursor position, horizontal scanlines, and both horizontal and vertical GENLOCK. The CRTC registers are

also described in Chapter 4.

CONTROLS

MA[9:0]

MEMORY

ARBITRATOR

MEMORY DATA

MEMORY

CONTROLLER

DISPLAY FIFOS

MD[63:0]

Figure 2-1. Sequencer Functional Block Diagram

FRAME

BUFFER

The CRTC is software-compatible with IBM VGA hardware. The registers are expanded, as necessary, for high-resolution monitors. The CRTC also provides split-screen capability and smooth

scrolling. A simplified functional diagram of the CRTC is shown in Figure 2-2.

Copyright 1996 – Cirrus Logic Inc. 2-5 November 1996

OVERVIEW CL-GD5446 Technical Reference Manual

D[7:0]

HSYNC

CLOCK

VSYNC

CHARACTER

LINE

COUNTER

HORIZONTAL

COMPARATORSCOUNTER

VERTICAL

COMPARATORS

CURSOR

COMPARATORS

CHARACTER

ADDRESS

COUNTER

REGISTER

CONTROL

BLANK#

HSYNC

REGISTERS

VSYNC

DISPLAY MEMORY

Figure 2-2. CRT Controller Functional Block Diagram

November 1996 2-6 Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual OVERVIEW

2.3.3 Graphics Controller

The graphics controller operates in either text or g raphics modes and has the follo wing major functions:

● Provides the host CPU with a read/write access path to display memory.

● Controls all four memory planes in planar modes (used for 16-color graphics).

● Allows data to be manipulated prior to being written to display memory.

● Formats data for use in various backward-compatibility modes.

● Provides color comparators for use in color painting modes.

● Reads/writes 32- or 64-bit words through the 32- or 64-bit display memory interface.

● Combines display memory data and attributes for output to the Pixel bus.

The graphics controller directs data from the display memory to the attribute controller and CPU.

Figure 2-3 and Figure 2-4 illustrate typical write and read operations.

For a write operation, the data from the CPU bus are combined with the data from the Set/Reset

logic, depending on the write and display modes. In addition, the data can be combined with the

contents of the read latches, and some bits or planes may be masked (prevented from being

changed). See the bit descriptions in Chapter 4, “VGA Core Registers”, for more information.

ENABLE

D[3:0]

WRITE MODE

AND DATA

MODE

FROM CPU DATA BUS

DATA ROTATOR

DATA

SELECT

FUNCTION

SELECTOR

PROCESSOR

LATCH

TO PLANES 0, 1, 2, 3

DATA

ROTATE

REGISTER

SET/RESET

D[3:0]

BIT

MASK

Figure 2-3. Graphics Controller Write Operation

Copyright 1996 – Cirrus Logic Inc. 2-7 November 1996

OVERVIEW CL-GD5446 Technical Reference Manual

The graphics controller is implemented when the CPU is reading data from display memory.

Depending on the read mode, the data returned may be the actual contents of the display memory

or reflect the outcome of comparisons with the color value in one of the Graphics Controller registers. See the descriptions in Chapter 4 for more information.

FROM PLANES 0, 1, 2, 3

READ MAP

REGISTER AND

READ MODE

PROCESSOR

LATCH

COLOR COMPARE

BITS 0–3

COMPARATOR

SELECTOR

COLOR DON’T CARE

BITS 0–3

PLANE

SELECT

TO CPU DATA BUS

Figure 2-4. Graphics Controller Read Operation

November 1996 2-8 Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual OVERVIEW

2.3.4 Attribute Controller

The attribute controller controls the blinking and underline attributes in alphanumeric modes. It

also provides horizontal pixel-panning capability in both alphanumeric and graphics modes. The

attribute controller registers are described in Chapter 4. Figure 2-5 is a functional block diagram

of the attribute controller.

OVERSCAN

REGISTER

PALETTE

DAC

P[7:0]

D[5:0]

ADDRESS REGISTER

AND DECODING

TIMING LOGIC

OUTPUT

LATCHES

AND

LOGIC

ATR[7:0]

CC[7:0]

ATTRIBUTE

LATCHES

AND

LOGIC

MODE CONTROL REGISTER

CONDITION CODE

SHIFT REGISTER

AND LOGIC

CURSOR BLINK

COUNTER

HORIZONTAL PIXEL

PANNING REGISTER

HORIZONTAL PIXEL

PANNING

SHIFT REGISTER

AND LOGIC

COLOR

PALETTE

REGISTERS

COLOR PLANE

ENABLE REGISTER

PALETTE

ADDRESS

AND DECODING

Figure 2-5. Attribute Controller

Copyright 1996 – Cirrus Logic Inc. 2-9 November 1996

OVERVIEW CL-GD5446 Technical Reference Manual

2.3.5 Programmable Dual-Frequency Synthesizer

The CL-GD5446 includes an integrated dual-frequency synthesizer that can be programmed to

generate the VCLK for all supported screen formats, and the MCLK used by the sequencer. The

VCLK synthesizer can support a pixel clock of up to 135 MHz. The MCLK synthesizer can be programmed for up to 80 MHz (for EDO DRAMS). The dual-frequency synthesizer includes an onchip oscillator that requires an inexpensive , two-pin 14.31818-MHz crystal. Alternatively, the dualfrequency synthesizer can use a reference frequency of 14.31818 MHz from an external source.

Figure 2-6 is a functional block diagram of the programmable dual-frequency synthesizer.

VCLK

SELECTION

CRYSTAL

MCLK

SELECTION

OSC

PROGRAMMABLE

VCLK

OSCILLATOR

PROGRAMMABLE MCLK

OSCILLATOR

VCLK

MCLK

Figure 2-6. Programmable Dual-Frequency Synthesizer Functional Diagram

November 1996 2-10 Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual OVERVIEW

2.3.6 Palette DAC

The CL-GD5446 includes an integrated palette DAC that can interface to an analog monitor connector through the appropriate RFI filters. The palette DAC can be programmed for 256 simultaneous colors from a palette of 256K, or it can be programmed for Direct-color mode . In Direct-color

mode, two, three, or four contiguous bytes from the display memory are combined for each pixel.

This allows 32K, 64K, or 16.8 million simultaneous colors on the screen.

The CL-GD5446 supports color space conversion and can display YUV 4:2:2 or AccuPak video

data as well as 8-bpp LUT and 16-bpp RGB in the hardware video window.

Figure 2-7 is a functional block diagram of the palette DAC.

P[31:0]

P[7:0]

VCLK

AccuPak DECODE,

VIDEO PIPELINE

ZOOMING, CSC

LOOKUP

TABLE

256 ×

18

MUX

DAC

R

G

B

Figure 2-7. 256-Color/Direct-Color Palette DAC

Copyright 1996 – Cirrus Logic Inc. 2-11 November 1996

OVERVIEW CL-GD5446 Technical Reference Manual

2.4 PCI Bus Interface

The CL-GD5446 includes a glueless 32-bit PCI bus interface . This interface features full PCI compliance, including optimized PCI burst write, which supports PCI writes to the frame buffer at

greater than 55 Mbytes per second.

The frame buffer is addressable through a 16-Mbyte window consisting of three 4-Mbyte byteswapping apertures, and a special video aperture. The VGA control registers are relocateable

anywhere in the 64-Kbyte space (allowing multiple devices in a single system).

The frame buffer in Revision B of the CL-GD5446 is addressable through two 16-Mbyte windows.

One window is for direct accesses to the frame b uffer; the second window is f or system-to-screen

BitBLTs. The V GA registers in Re vision B of the CL-GD5446 are accessible an ywhere in the memory address space. Revision B of the CL-GD5446 supports Subsystem Vendor ID in PCI2C.

2.5 BitBLT Engine

The CL-GD5446 includes a BitBL T engine f or block tr ansfers within displa y memory at full memory

bandwidth. System-to-display transfers can also be effected with the BitBLT engine.

The CL-GD5446 BitBLT engine suppor ts transparency with color expansion for all graphics formats and transparency without color expansion for 8- and 16-bpp graphics formats.

The BitBL T control registers are doub le-buff ered and memory-mapped. Doub le-buff ered registers,

in conjunction with the autostart feature, allow concurrent operation of the host and the BitBLT

engine. The host can prepare and load the par ameters f or operation n + 1 while the BitBLT engine

is executing operation n. When the current operation completes, the BitBLT engine automatically

loads and begins with the parameters for the next operation.

All 16 two-operand ROPs (raster operations) are implemented in hardware. Color expansion

leverages host bandwidth by up to 32 times.

HOST INTERFACE

DOUBLE-BUFFERED

REGISTERS

COLOR EXPANSION

COLORS

WORKING

REGISTERS

64-BIT DATA FLOW

TRANSPARENCY

COLORS

FRAME

BUFFER

Figure 2-8. BitBLT Engine

November 1996 2-12 Copyright 1996 – Cirrus Logic Inc.

CL-GD5446 Technical Reference Manual OVERVIEW

2.6 Video Capture

The CL-GD5446 V-Port accepts video data from a realtime or recorded source and stores it

into the frame buffer. V-Por t can accept data in YUV 4:2:2, RGB16, or AccuPak formats.

Figure 2-9 shows a V-Port functional block diagram.

Video data can be converted from YUV 4:2:2 to AccuP ak as it is being stored, or it can be decimated as it is being stored. Decimation and AccuPak conversion cannot be used together.

Horizontal and vertical decimation are independently specified. In addition, temporal decimation can be used.

The video capture address can come from either of two register sets, allowing automatic double buffering. When this is used, the video buffers being used for capture and display can be

automatically swapped, ensuring that partial images are not displayed.

The CL-GD5446 has an independent video capture FIFO, allowing simultaneous video capture and occlusion or interpolated Y-zooming (subject to frame buffer bandwidth restrictions).

DECIMATION

CONTROL

V-Port

Figure 2-9. V-Port Functional Block Diagram

2.7 Video Window and Video Display

The CL-GD5446 has a video window timing generator that defines a rectangular area on the

display. This area can display video data or mixed graphics and video data. Video data can

(and typically does) have a for mat different from Graphics data. Typically, Video data also

comes from a separate area in the frame buffer.

YUV (4:2:2 in CCIR601 encoding) data is color space converted to RGB in the video pipeline.

AccuPak data is expanded to YUV 4:2:2 prior to color space conversion.

CAPTURE ADDRESS

GENERATOR LOGIC

VIDEO CAPTURE FIFO

YUV TO ACCUPAK

FRAME

BUFFER

Video data can be zoomed for display in the video window. Zoom factors in the range of 1

through 4 are generally used. X-zooming is always done with interpolation (the intermediate

pixels values are a w eighted av erage of ‘real’ pixels). Y-zooming can be done with interpolation

(2× or above) or line replication. Inter polation zooming produces superior results and should

be used whenever bandwidth requirements permit.

Copyright 1996 – Cirrus Logic Inc. 2-13 November 1996

OVERVIEW CL-GD5446 Technical Reference Manual