Page 1

CDB5343

CDB5343: Evaluation Board for CS5343

Features

Demonstrates Recommended Layout and

Grounding Arrangements

CS8406 Generates S/PDIF and EIAJ-340-

Compatible Digital Audio

Requires Only an Analog Signal Source

and Power Supply for a Complete Analogto-Digital Converter System

Description

The CDB5343 evaluation board is an excellent

means for quickly evaluating the CS5343 24bit, stereo A/D converter. Evaluation requires

a digital signal analyzer, an analog source,

and a power supply.

Also included is an CS8406 digital audio interface transmitter that generates S/PDIF and

EIAJ-340-compatible audio data. The digital

audio data is available via RCA phone and optical connectors.

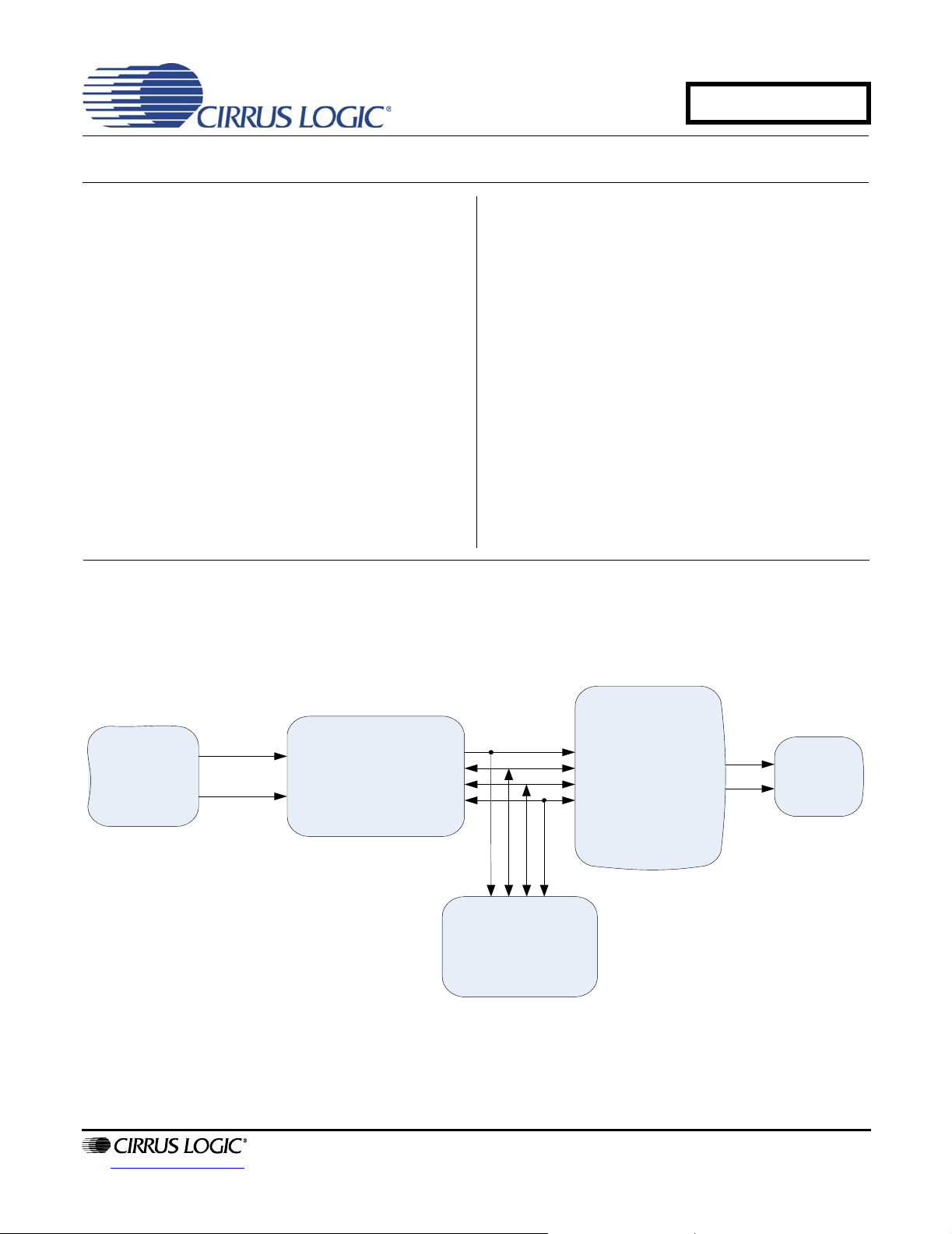

ANALOG

INPU T

http://www.cirrus.com

CS5343

98 dB, 96 kHz, Audio A/D

Converter

Copyright © Cirrus Logic, Inc. 2006

(All Rights Reserved)

I/O FO R

CLOCKS

AND DATA

CS8406

AES/EBU

S/PDIF

TRANSMITTER

S/PDIF

OUTPUT

AUGUST '06

DS687DB2

Page 2

TABLE OF CONTENTS

1. SYSTEM OVERVIEW ............................................................................................................................. 4

1.1 CS5343 ............................................................................................................................................. 4

2. CS8406 DIGITAL AUDIO TRANSMITTER ............................................................................................4

3. CRYSTAL OSCILLATOR ....................................................................................................................... 4

4. CLOCK & DATA I/O HEADER ............................................................................................................... 4

4.1 Clock & Data Routing ....................................................................................................................... 4

4.1.1 MCLK Source . ... .... ...................................... .... ... ... ... ....................................... ... ... .... .............. 4

4.1.2 Sub-Clock Source ....................... ... ....................................... ... .... ... ... ... .... .............................. 4

4.1.3 Data Routing ............................ ... ... .... ... ... ... ....................................... ... .... ... ... ... ... .................. 5

5. POWER ................................................................................................................................................... 5

6. GROUNDING AND POWER SUPPLY DECOUPLING .......................................................................... 5

7. ANALOG INPUT ..................................................................................................................................... 5

8. CONNECTORS ....................................................................................................................................... 6

9. JUMPER AND SWITCH SETTINGS ...................................................................................................... 6

9.1 Jumper J4 ......................................................................................................................................... 6

9.2 Switch S1 .......................................................................................................................................... 6

9.2.1 CS5343 .............................. ... ... ... ... .... ...................................... .... ... ... ... .................................. 6

9.2.2 CS8406 .............................. ... ... ... ... .... ...................................... .... ... ... ... .................................. 7

9.2.3 MCLK .......................... ... ....................................... ... .... ...................................... ..................... 7

9.2.4 SCLK, LRCK ............................... ... ....................................... ... .... ... ... ... .... .............................. 7

9.2.5 SPEED .................................................................................................................................... 7

9.2.6 MCLK/LRCK Ratio ................... ... ... ....................................... ... .... ... ... ... .... .............................. 7

10. RESET .................................................................................................................................................. 8

11. EVALUATING THE CS5344 ................................................................................................................. 8

12. PERFORMANCE PLOTS ..................................................................................................................... 9

13. CDB PERFORMANCE CURVES ....................................................................................................... 12

13.1 Total Harmonic Distortion + Noise (THD+N) ............................................................................... 12

13.2 FFTlm .......................................................................................................................................... 13

14. CDB SCHEMATICS ........................................................................................................................... 14

15. CDB LAYOUT ..................................................................................................................................... 20

16. REVISION HISTORY .......................................................................................................................... 23

CDB5343

2 DS687DB2

Page 3

LIST OF FIGURES

Figure 1. FFT (-1 dB 48 kHz) ...................................................................................................................... 9

Figure 2. FFT (-60 dB, 48 kHz) ................................................................................................................... 9

Figure 3. FFT (48 kHz, No Input) ................................................................................................................ 9

Figure 4. 48 kHz, THD+N vs. Input Freq ..................................................................................................... 9

Figure 5. 48 kHz, THD+N vs. Level ............................................................................................................ 9

Figure 6. 48 kHz, Fade-to-Noise Linearity .................................................................................................. 9

Figure 7. 48 kHz, Frequency Response .................................................................................................... 10

Figure 8. 48 kHz, Crosstalk ....................................................................................................................... 10

Figure 9. FFT (-1 dB 96 kHz) .................................................................................................................... 10

Figure 10. FFT (-60 dB, 96 kHz) ............................................................................................................... 10

Figure 11. FFT (96 kHz, No Input) ............................................................................................................ 10

Figure 12. 96 kHz, THD+N vs. Input Freq ................................................................................................. 10

Figure 13. 96 kHz, THD+N vs. Level ........................................................................................................ 11

Figure 14. 96 kHz, Fade-to-Noise Linearity .............................................................................................. 11

Figure 15. 96 kHz, Frequency Response .................................................................................................. 11

Figure 16. 96 kHz, Crosstalk ..................................................................................................................... 11

Figure 17. CDB5343 THD+N Performance ............................................................................................... 12

Figure 18. FFT from CDB5343 Output ...................................................................................................... 13

Figure 19. CDB Block Diagram ................................................................................................................. 14

Figure 20. CS5343 Analog-to-Digital Converter ........................ ... .... ... ... .......................................... ......... 15

Figure 21. Analog Input ............................................................................................................................. 16

Figure 22. Switches, Crystal Oscillator, and Clock Routing ...................................................................... 17

Figure 23. CS8406 S/PDIF Transmitter .................................................................................................... 18

Figure 24. Power ....................................................................................................................................... 19

Figure 25. CDB Silk-Screen ...................................................................................................................... 20

Figure 26. Topside Layer .......................................................................................................................... 21

Figure 27. Bottomside Layer ..................................................................................................................... 22

CDB5343

LIST OF TABLES

Table 1. System Connections ................ ... ... ... ... .... ..................................................................................... 6

Table 2. CDB5343 S1 Settings ................................................................................................................... 6

DS687DB2 3

Page 4

CDB5343

1. SYSTEM OVERVIEW

The CDB5343 evaluation board is an excellent tool for evaluating the CS5343 Analog-to-Digital Converter (ADC).

A minimum number of passive components condition the analog inpu t signal prior to the CS5343, and the o n-board

CS8406 digital audio interface transmitter provides an easy interface to digital audio signal analyzers including the

majority of digital audio test equipment. Additionally, the CDB5343 features an interface header (J3) for clock and

data I/O.

Figures 19 through Figures 27 show the CDB5343 schematic and layout.

1.1 CS5343

The CS5343 ADC performs stereo 24-bit A/D conversion at sample rates of up to 108 kHz and generates

I²S audio format data. Furthermore, in both Master and Slave Modes the CS5343 supports MCLK/LRCK

ratios of 256x and 384x. The CS5343 product datasheet contains complete device information.

2. CS8406 DIGITAL AUDIO TRANSMITTER

The CS8406 converts the CS5343 output to a standard S/PDIF data stream. Given an MCLK/LRCK ratio equal to

256x, the CS8406 can operate as cloc k master or clock slave, but the CS8406 cannot be used with an MCLK/LRCK

ratio of 384x on this board. Moreover, by de fault on this boa rd, the CS840 6 accepts only I²S audio format; however ,

Section 11. on page 8 describes the procedure of configuring the device for Left-Justified audio format. See the

CS8406 data sheet for complete device information.

3. CRYSTAL OSCILLATOR

Oscillator Y1 provides an on-board system master clock. The oscillator is mounted in pin sockets, allowing for easy

removal or replacement. The board includes a 12.288 MHz crystal oscillator populated at Y1.

4. CLOCK & DATA I/O HEADER

Header J3 makes interfacing to external systems easy. MCLK direction is controlled by switch S1, as is the direction

of the sub-clocks, SCLK and LRCK. The header pins associated with MCLK, SCLK, and LRCK ca n accept 3 .3 V or

5 V input signals, but are fixed at 3.3 V when set as outputs. SDOUT is always a 3.3 V output.

4.1 Clock & Data Routing

The user can configure the source and destinations of the clocks required to support the operation of the

CS5343. Section 4.1.1 through Section 4.1.3 discuss valid configurations.

4.1.1 MCLK Source

The CS5343 and CS8406 must receive a Master Clock. MCLK can come from either the crystal oscillator

installed at Y1 or via header J3. Header J3 can accept a 3.3 V or 5 V logic-level MCLK when configured

as an input, but will output MCLK only at 3.3 V when configured as an output.

4.1.2 Sub-Clock Source

SCLK and LRCK comprise the system sub-clocks and must be either provided to, or generated by, the

CS5343.

4 DS687DB2

Page 5

CDB5343

The CS5343 generates sub-clocks when it is set for Master Mode via DIP switch S1. In this scenario, the

CS8406 should be set to Slave Mode to receive sub-clocks. Similarly, the “SCLK, LRCK” switch should

be closed to direct sub-clocks to the header. The sub-clock output of the J3 header is fixed at 3.3 V.

If the user configures the CS5343 for Slave Mode, the device must receive sub-clocks either from the

CS8406 or from an external source vi a header J3. If the CS8406 is the in tended sub-clock sour ce, DIP

switch S1 must be set such that the CS8406 is in Master Mode and “SCLK, LRCK” are routed to the header. If both the CS5343 and the CS8406 are set to Slave Mode, DIP switch S1 must indicate th at the subclocks come “FROM HDR.” Sub-clock input to header J3 may be either 3.3 V or 5 V.

4.1.3 Data Routing

Audio data from the CS5343 SDOUT pin is routed to header J3 and the CS8406. The SDOUT pin of J3

is always a 3.3 V output. The CS5343 produces data in only I²S audio format; therefore the data capture

device should be set accordingly.

The CS8406 accepts data in I²S audio format, which it converts to S/PDIF and EIAJ-340-comp atible data.

This data is available for capture from either the optical connector (J9) or the RCA jack (J6).

5. POWER

Power must be supplied to the evaluation board through the +5 V binding post (J2). The +5 V input must be referenced to the single black binding post ground connector (J1).

WARNING: Please refer to the CS5343 data sheet for allowable voltage levels.

6. GROUNDING AND POWER SUPPLY DECOUPLING

To optimize performance, PCB designs supporting the CS5343 require car eful attention to power supply, grounding,

and signal routing. Figures 26 and 27 show the basic component/signal interconnect for the CDB5343, and

Figure 25 shows the c omponent placemen t. These figures demonstrate the optimal layout of components used to

support the CS5343. For ex ample, these figures sh ow that the decoupling capacitors are located a s close to the

CS5343 as possible. The layout also shows extensive use of ground plane fill which greatly reduces radiated noise.

7. ANALOG INPUT

The user can input single-ended analog signals via the RCA connectors, J5 and J7. A 2 Vrms single-ended signal

into the RCA connectors will drive the CS5343 inputs to full scale (1 Vrms for VA = 5 V). The input network on the

CDB5343 was designed to demonstrate that the CS5343 will achieve full performance with a source impedance up

to 2.5 kΩ (looking back from the CS5343 inputs) while allowing for 2 Vrms inputs. Another advantage of this circuit

is that it provides an input impedance of 10 kΩ, similar to many commercial audio products.

DS687DB2 5

Page 6

CDB5343

8. CONNECTORS

Table 1 lists the connectors on the CDB5343, the reference designator of each connector, the directionality, and

the associated signal.

REFERENCE

CONNECTOR

+5V J2 INPUT +5 V power to crystal oscillator and DC voltage regulator

GND J1 INPUT Ground connection from the power supply

AINR J7 INPUT Analog input right channel

AINL J5 INPUT Analog input left channel

Co-axial J6 OUTPUT Digital audio (S/PDIF) output

Optical J9 OUTPUT Digital audio (S/PDIF) output

I/O HDR J3 INPUT/OUTPUT Master Clock, Serial Clock, Left/Right Clock, SDOUT

DESIGNATOR INPUT/OUTPUT SIGNAL

Table 1. System Connections

9. JUMPER AND SWITCH SETTINGS

The user can fully configure the CDB5343 with a bank of six DI P switches (S1) and a single jumper setting o n header

J4.

9.1 Jumper J4

This jumper selects the magnitude of VA, either 3.3 V or 5 V. The CS5343 is a single -sup ply de vice; th er efore the magnitude of VA affects the full-scale analog input voltage as well as the digital I/O voltage. Digital

I/O is always fixed at VA, and the full-scale input is nominally 0.56xVA Vpp, as specified in the CS5343 data

sheet. If the user selects 5 V, the CS5343 full-scale analog input voltage is 2.82 Vpp (1 Vrms) and the digital

I/O is set to 5 V. If 3.3 V is selected, the full-scale analog input voltage is 1.86 Vpp (660 mVrms) and digital

I/O is 3.3 V.

9.2 Switch S1

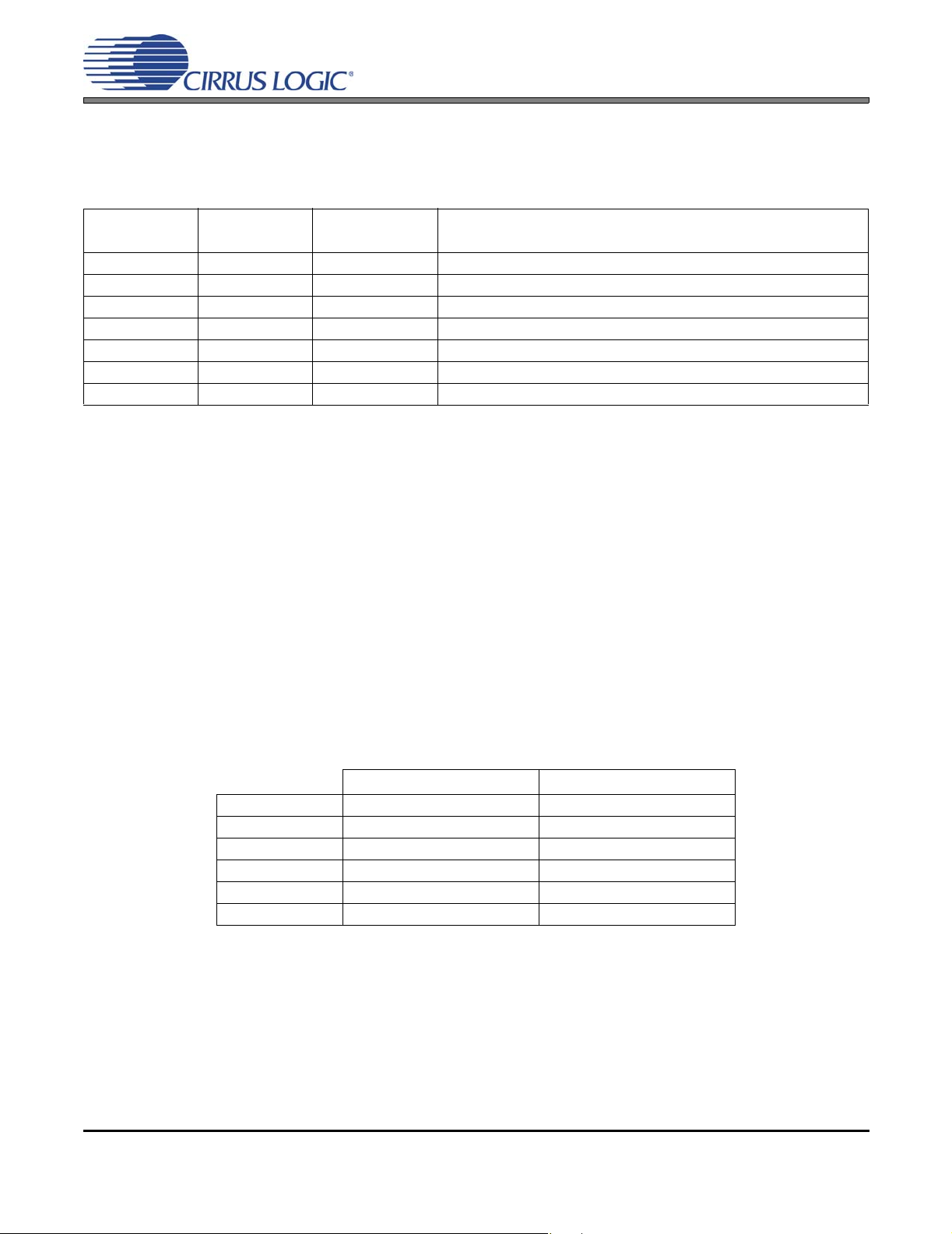

Table 2 shows the available settings for S1 with the default settings.

9.2.1 CS5343

OPEN CLOSED

CS5343 MASTER (default) SLAVE

CS8406 MASTER SLAVE (default)

MCLK FROM HDR TO HDR (default)

SCLK, LRCK FROM HDR TO HDR (default)

SPEED DSM SSM (default)

MCLK/LRCK 256x (default) 384x

T able 2. CDB5343 S1 Settings

This switch configures the CS5343 f or either Ma ster Mode or Slave Mode operation. When set as clock

Master, the CS8406 must be set to “Slave” and “SCLK, L RCK” must be set to “TO HDR.” When CS5343

is configured for Slave Mode, the CS8406 must be set for Master Mode, or “SCLK, LRCK” mu st be set to

“FROM HDR.”

6 DS687DB2

Page 7

Changing the state of this switch while the device is running will have no effect on the CS534 3 a s it mu st

be reset to detect the change. Reset is accomplished by removing and re sto ring po we r to the d evice . Alternatively, removing and restoring MCLK will initiate a reset of the digital section, which is also sufficient

for the CS5343 to detect a change in mode settings.

9.2.2 CS8406

This switch sets the CS8406 for either Master Mode or Slave Mode. In Master Mode, the CS5343 must

be configured as a clock slave and “SCLK, LRCK” se t to “TO HDR.” In S lave Mode, either t he CS5343

can be set to Master Mode or the user can set the “SCLK, LRCK” switch to “FROM HDR.”

9.2.3 MCLK

MCLK can either come from the header, as selected by “FROM HDR,” or from the on-board crystal oscillator (Y1) as selected by “TO HDR.”

9.2.4 SCLK, LRCK

The sub-clocks, SCLK and LRCK, are either produced on board by the CS5343 or the CS8406 or produced externally. If generated by an external device, this switch must be set to “FROM HDR.” If the

CS5343 or CS8406 generate the sub-clocks, this switch must be set to “FROM HDR.”

9.2.5 SPEED

CDB5343

The CS5343 can operate in Single-Speed Mode (SSM) or Double-Speed Mode (DSM) as described in

the CS5343 product datasheet.

In Master Mode, the CS5343 defaults to SSM based on an internal 100 kΩ pull-up r esistor from the LRCK

pin to VA. Setting the “SPEED” switch to “DSM” will place a 10 kΩ pull-down resistor between LRCK and

GND to select Double-Speed Mode. Because the CS5343 determines its Master Mode speed based on

start-up options, the speed mode cannot be toggled during operation. To change the speed in Master

Mode, the device must be reset by removing and restoring power or removing and restoring MCLK.

This switch also configures the MCLK/LRCK ratio for the CS8406. Selecting SSM configures the CS8406

for a 512x MCLK/LRCK ratio while DSM sets an MCLK/LRCK ratio of 256x. In this design, the CS8406

cannot support of a 384x MCLK/LRCK ratio.

9.2.6 MCLK/LRCK Ratio

This switch will configure the CS5343 for either a 256x MCLK/LRCK ratio or a 384x MCLK/LRCK ratio in

Master Mode. In Slave Mode the CS5343 auto-detects the MCLK/LRCK ratio; therefore this configuration

step is unnecessary in Slave Mode. In Master Mode, selection of this parameter is performed via a startup option. An internal 100 kΩ pull-up resistor from the SCLK pin to VA will select 256x by default. An external 10 kΩ pull-down resistor from the SCLK pin to GND will select an MCLK/LRCK ratio of 384x.

Typical applications that use a 384x MCLK/LRCK ratio derive a 48 kHz LRCK from a 18.384 MHz MCLK.

Deriving MCLK from the included 12.288 MHz crystal oscillator will result in a sample rate of 32 kHz.

The CS8406 is not configured to support a 384x MCLK/LRCK ratio in this design; therefore analysis in

this mode must be performed by retrieving data through the interface header (J3).

DS687DB2 7

Page 8

CDB5343

10.RESET

The CS5343 features Power-On Reset which means that performing a full reset of the CS5343 requires a powercycling the device. On the CDB5343, this can be accomplished with by removing and restoring the power-supply or

by removing and restoring the jumper on J3. Alternatively, removing and restoring MCLK to the device will effect a

reset of just the digital port ion of the device. The device en ters Power-Down Mode when MC LK is removed and

draws less current.

11.EVALUATING THE CS5344

The CDB5343 comes with only the CS5343 ADC installed, but some users may want to evaluate the pin-compatible

CS5344 ADC. The two devices perform equivalently, but the CS5344 produces only Le ft-Justified audio format data;

whereas the CS5343 creates only I²S audio format data. By following the four ea sy steps listed below, th e user can

modify the CDB5343 to accommodate the CS5344.

• Step 1: Remove CS5343 populated at U6

• Step 2: Install CS5344 at U6

• Step 3: Remove 0 Ω resistor populated at R36 (this resistor selects I²S Audio Format for the CS8406)

• Step 4: Install 0 Ω resistor at R43 (this resistor selects LJ Audio Format for the CS8406)

8 DS687DB2

Page 9

12.PERFORMANCE PLOTS

CDB5343

+0

-10

-20

-30

-40

-50

d

-60

B

F

-70

S

-80

-90

-100

-110

-120

-130

20 20k50 100 200 500 1k 2k 5k 10k

Hz

Figure 1. FFT (-1 dB 48 kHz) Figure 2. FFT (-60 dB, 48 kHz)

+0

-10

-20

-30

-40

-50

d

-60

B

F

-70

S

-80

-90

-100

-110

-120

-130

20 20k50 100 200 500 1k 2k 5k 10k

Hz

+0

-10

-20

-30

-40

-50

d

-60

B

F

-70

S

-80

-90

-100

-110

-120

-130

20 20k50 100 200 500 1k 2k 5k 10k

+0

-10

-20

-30

-40

d

B

-50

F

S

-60

-70

-80

-90

-100

20 20k50 100 200 500 1k 2k 5k 10k

Hz

Hz

Figure 3. FFT (48 kHz, No Input) Figure 4. 48 kHz, THD+N vs. Input Freq

+0

-10

-20

-30

-40

d

B

-50

F

S

-60

-70

-80

-90

-100

-120 +0-100 -80 -60 -40 -20

dBr

+40

+35

+30

+25

+20

+15

+10

+5

d

B

+0

F

S

-5

-10

-15

-20

-25

-30

-35

-40

-140 +0-120 -100 -80 -60 -40 -20

TTTTTTTTTTTTTTTTTTTT

dBr

Figure 5. 48 kHz, THD+N vs. Level Figure 6. 48 kHz, Fade-to-Noise Linearity

DS687DB2 9

Page 10

CDB5343

+5

+4

+3

+2

+1

d

B

+0

F

S

-1

-2

-3

-4

-5

20 20k50 100 200 500 1k 2k 5k 10k

Hz

+0

-10

-20

-30

-40

-50

-60

d

B

-70

-80

-90

-100

-110

-120

-130

20 20k50 100 200 500 1k 2k 5k 10k

Hz

Figure 7. 48 kHz, Frequency Response Figure 8. 48 kHz, Crosstalk

+0

-10

-20

-30

-40

-50

d

-60

B

F

-70

S

-80

-90

-100

-110

-120

-130

20 20k50 100 200 500 1k 2k 5k 10k

Hz

+0

-10

-20

-30

-40

-50

d

-60

B

F

-70

S

-80

-90

-100

-110

-120

-130

20 20k50 100 200 500 1k 2k 5k 10k

Hz

Figure 9. FFT (-1 dB 96 kHz) Figure 10. FFT (-60 dB, 96 kHz)

+0

-10

-20

-30

-40

-50

d

-60

B

F

-70

S

-80

-90

-100

-110

-120

-130

20 20k50 100 200 500 1k 2k 5k 10k

Hz

+0

-10

-20

-30

-40

d

B

-50

F

S

-60

-70

-80

-90

-100

20 20k50 100 200 500 1k 2k 5k 10k

Hz

Figure 11. FFT (96 kHz, No Input) Figure 12. 96 kHz, THD+N vs. Input Freq

10 DS687DB2

Page 11

CDB5343

+0

-10

-20

-30

-40

d

B

-50

F

S

-60

-70

-80

-90

-100

-120 +0-100 -80 -60 -40 -20

dBr

Figure 13. 96 kHz, THD+N vs. Level Figure 14. 96 kHz, Fade-to-Noise Linearity

+5

+4

+3

+2

+1

d

B

+0

F

S

-1

-2

-3

-4

-5

20 20k50 100 200 500 1k 2k 5k 10k

Hz

+40

+35

+30

+25

+20

+15

+10

+5

d

B

+0

F

S

-5

-10

-15

-20

-25

-30

-35

-40

-140 +0-120 -100 -80 -60 -40 -20

+0

-10

-20

-30

-40

-50

-60

d

B

-70

-80

-90

-100

-110

-120

-130

20 20k50 100 200 500 1k 2k 5k 10k

TTTTTTTT

dBr

Hz

Figure 15. 96 kHz, Frequency Response Figure 16. 96 kHz, Crosstalk

DS687DB2 11

Page 12

12 DS687DB2

13.CDB PERFORMANCE CURVES

13.1 Total Harmonic Distortion + Noise (THD+N)

Figure 17 shows typical THD+N performance of the CS5343 installed on the CDB5343. Performance curves are displayed for each channel

with the CS5343 running at Single-Speed in both Master and Slave Modes and for VA voltages of both +3.3 V and 5 V.

+0

TTTTTTT

-5

-10

-15

-20

-25

-30

-35

-40

-45

d

B

-50

F

S

-55

-60

-65

-70

-75

-80

-85

-90

-95

-100

2k 20k4k 6k 8k 10k 12k 14k 16k 18k

CDB5343 (Rev A device) THD+N vs. Frequency

Hz

+0

-5

-10

-15

-20

-25

-30

-35

-40

-45

-50

-55

-60

-65

-70

-75

-80

-85

-90

-95

-100

d

B

F

S

ColorSweep Trace Line Style Thick Data Axis Comment

1 1 Blue Solid 1 DSP Anlr.THD+N Ampl A Left 5V Master SSM 256x

1 2 Blue Solid 1 DSP Anlr.THD+N Ampl B Right 5V Master SSM 256x

2 1 Red Solid 1 DSP Anlr.THD+N Ampl A Left 5V Slave SSM 256x

2 2 Red Solid 1 DSP Anlr.THD+N Ampl B Right 5V Slave SSM 256x

3 1 Green Solid 1 DSP Anlr.THD+N Ampl A Left 3.3 V Slave SSM 256x

3 2 Green Solid 1 DSP Anlr.THD+N Ampl B Right 3.3 V Slave SSM 256x

4 1 Yellow Solid 1 DSP Anlr.THD+N Ampl A Left 3.3 V Slave SSM 256x

4 2 Yellow Solid 1 DSP Anlr.THD+N Ampl B Right 3.3 V Slave SSM 256x

Figure 17. CDB5343 THD+N Performance

CDB5343

Page 13

DS687DB2 13

13.2 FFTlm

Figure 18 shows a typical FFT of the output from the CS5343 on the CDB5343 with a 2 Vrms, 1 kHz sinewave input. For this plot, the device was

configured for Single-Speed Mode with VA = 5 V.

+0

CS5343 FFT, 1 kHz Full-scale Input, VA = 5 V, SSM Master Mode

+0

-10

-20

-30

-40

-50

-60

-70

-80

d

B

-90

F

S

-100

-110

-120

-130

-140

-150

-160

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

-110

-120

-130

-140

-150

-160

d

B

F

S

-170

-180

20 20k50 100 200 500 1k 2k 5k 10k

Hz

ColorSweep Trace Line Style Thick Data Axis Comment

1 1 Blue Solid 1 Fft.Ch.1 Ampl Left

1 2 Red Solid 1 Fft.Ch.2 Ampl Right

Figure 18. FFT from CDB5343 Output

-170

-180

CDB5343

Page 14

DS687DB2 14

14.CDB SCHEMATICS

Figure 19. CDB Block Diagram

CDB5343

Page 15

DS687DB2 15

Figure 20. CS5343 Analog-to-Digital Converter

CDB5343

Page 16

DS687DB2 16

Figure 21. Analog Input

CDB5343

Page 17

DS687DB2 17

Figure 22. Switches, Crystal Oscillator, and Clock Routing

CDB5343

Page 18

DS687DB2 18

Figure 23. CS8406 S/PDIF Transmitter

CDB5343

Page 19

19 DS687DB2

Figure 24. Power

CDB5343

Page 20

20 DS687DB2

15.CDB LAYOUT

Figure 25. CDB Silk-Screen

CDB5343

Page 21

DS687DB2 21

Figure 26. Topside Layer

CDB5343

Page 22

22 DS687DB2

Figure 27. Bottomside Layer

CDB5343

Page 23

16.REVISION HISTORY

Release Changes

DB1 Initial Release

DB2 Added Performance Plots

CDB5343

Contacting Cirrus Logic Support

For all product questions and inquiries, contact a Cirrus Logic Sales Representative.

To find the one nearest you, go to www.cirrus.com.

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject

to change without not ice and is pr ovided "AS IS" witho ut warr anty of any kind (express or implied). Customers are advised to obtain the latest version of relevant

information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale

supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus

for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third

parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights,

copyrights, trademarks, trade secrets or other inte llectual property rig hts. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent

does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE

IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED,

INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT

THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER’S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL

APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, T O FULLY INDEMNIF Y CIRRUS, ITS OF FICE RS, DI RECTORS, EMPLOYEES, DISTRI BUTORS AND

OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS’ FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION

WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks

or service marks of their respective owners.

DS687DB2 23

Loading...

Loading...