Page 1

AN368

Application Note

Design Guide for a CS1630/31 2-Channel

TRIAC Dimmable SSL Circuit

1 Overview of the CS1630

The CS1630 is a high-performance offline AC /DC LED driver for dimmable and high color rendering index (CRI)

LED replacement lamps and luminaires. It features Cirrus Logic’s proprietary digital dimmer compatibility control

technology and digital correlated color temperature (CCT) control system that enables two-channel LED color mixing. The CS1630 is designed for 120VAC line voltage applications.

The CS1630 integrates a critical conduction mode boost converter, providing power factor correction and superior

dimmer compatibility with a primary-side regulated quasi-resonant second stage, which is configurable for isolated

and non-isolated topologies. The digital CCT control system provides the ability to program dimming profiles, such

as constant CCT dimming and black body line dimming. The CS1630 optimizes LED color mixing by temperature

compensating LED current with an external NTC. The IC controller is also equipped with power line calibration for

remote system calibration and end-of-line programming. The CS1630 provides a register lockout feature for security

against potential access to proprietary registers.

1.1 Features

• Best-in-class Dimmer Compatibility

- Leading-edge (TRIAC) Dimmers, Trailing-edge Dimmers, and Digital Dimmers

• Correlated Color Temperature (CCT) Control System

• Up to 85% Efficiency

• Flicker-free Dimming

• Programmable Dimming Profile

- Constant CCT Dimming and Black Body Line Dimming

• <2% Minimum Dimming Level

• Temperature Compensated LED Current

• End-of-line Programming Using Power Line Calibration

- Lower LED Binning Requirement

• Programmable Series or Parallel 2-Channel Output

- Interleaved Output Eliminates Additional Transformer

• Programmable Quasi-resonant Second Stage with Constant-current Output

- Flyback, Buck, and Tapped Buck

• Register Lockout

• Fast Startup

• Tight LED Current Regulation: Better than ±5%

• Primary-side Regulation (PSR)

• >0.9 Power Factor

• IEC-61000-3-2 Compliant

• Soft Start

• Protections:

- Output Open/ Short and Current-sense Resistor Open/ Short

- External Overtemperature Using NTC

Cirrus Logic, Inc.

http://www.cirrus.com

Copyright Cirrus Logic, Inc. 2012

(All Rights Reserved)

DEC’12

AN368REV2

Page 2

AN368

Contacting Cirrus Logic Support

For all product questions and inquiries contact a Cirrus Logic Sales Representative. To find the one nearest to you

go to www.cirrus.com

IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject

to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant

information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale

supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus

for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third

parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights,

copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives

consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR

USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER

CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK

AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER

OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE,

TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Use of the formulas, equations, calculations, graphs, and/or other design guide information is at your sole discretion and does not guarantee any specific results or

performance. The formulas, equations, graphs, and/or other design guide information are provided as a reference guide only and are intended to assist but not to

be solely relied upon for design work, design calculations, or other purposes. Cirrus Logic makes no representations or warranties concerning the formulas, equations, graphs, and/or other design guide information

Cirrus Logic, Cirrus, the Cirrus Logic logo designs, EXL Core, the EXL Core logo design, TruDim, and the TruDim logo design are trademarks of Cirrus Logic, Inc.

All other brand and product names in this document may be trademarks or service marks of their respective owners.

IMPORTANT SAFETY INSTRUCTIONS

Read and follow all safety instructions prior to using this demonstration board.

This Engineering Evaluation Unit or Demonstration Board must only be used for assessing IC performance in a

laboratory setting. This product is not intended for any other use or incorporation into products for sale.

This product must only be used by qualified technicians or professionals who are trained in the safety procedures

associated with the use of demonstration boards.

Risk of Electric Shock

• The direct connection to the AC power line and the open and unprotected boards present a serious risk of electric

shock and can cause serious injury or death. Extreme caution needs to be exercised while handling this board.

• Avoid contact with the exposed conductor or terminals of components on the board. High voltage is present on

exposed conductor and it may be present on terminals of any components directly or indirectly connected to the AC

line.

• Dangerous voltages and/or currents may be internally generated and accessible at various points across the board.

• Charged capacitors store high voltage, even after the circuit has been disconnected from the AC line.

• Make sure that the power source is off before wiring any connection. Make sure that all connectors are well

connected before the power source is on.

• Follow all laboratory safety procedures established by your employer and relevant safety regulations and guidelines,

such as the ones listed under, OSHA General Industry Regulations - Subpart S and NFPA 70E.

Suitable eye protection must be worn when working with or around demonstration boards. Always

comply with your employer’s policies regarding the use of personal protective equipment.

All components and metallic parts may be extremely hot to touch when electrically active.

2 AN368REV2

Page 3

AN368

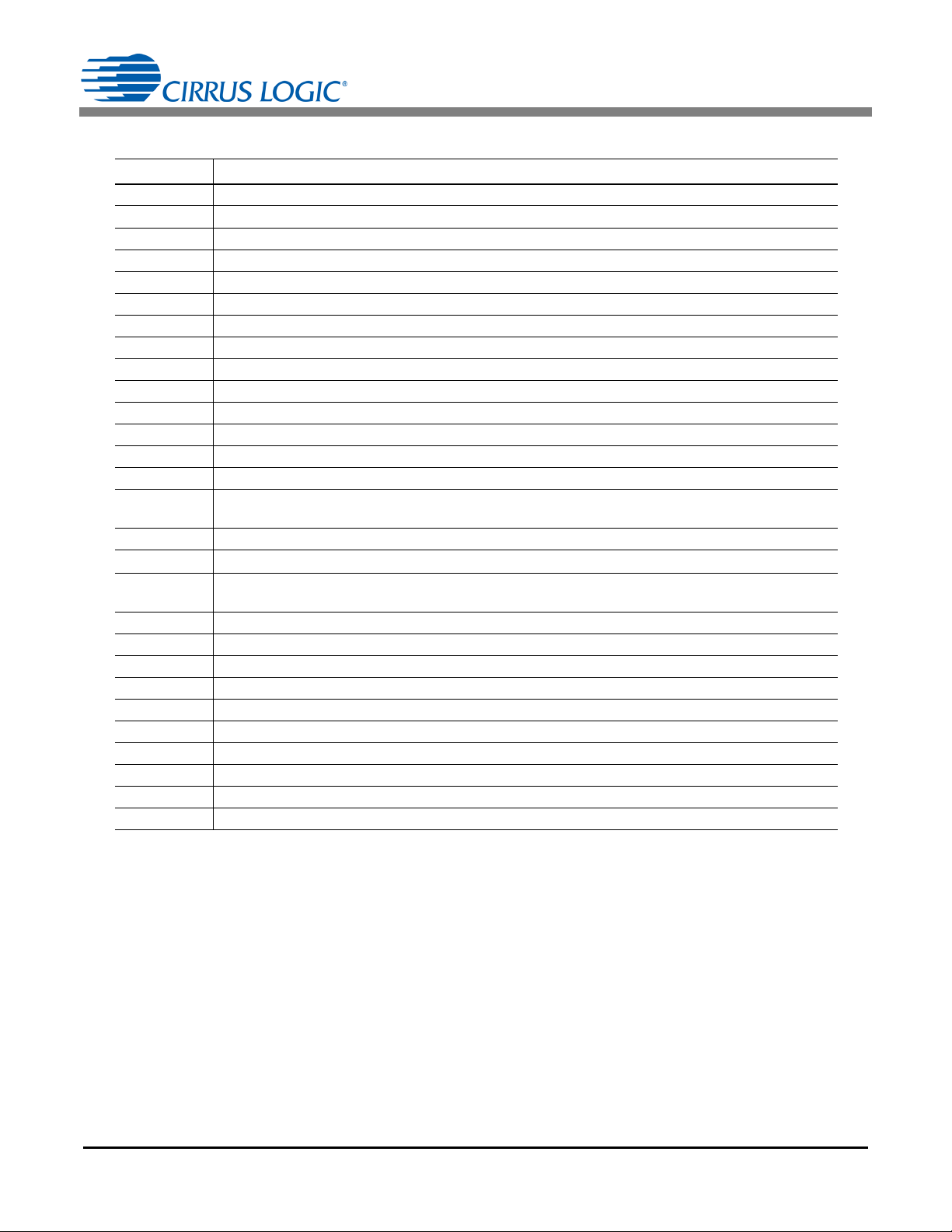

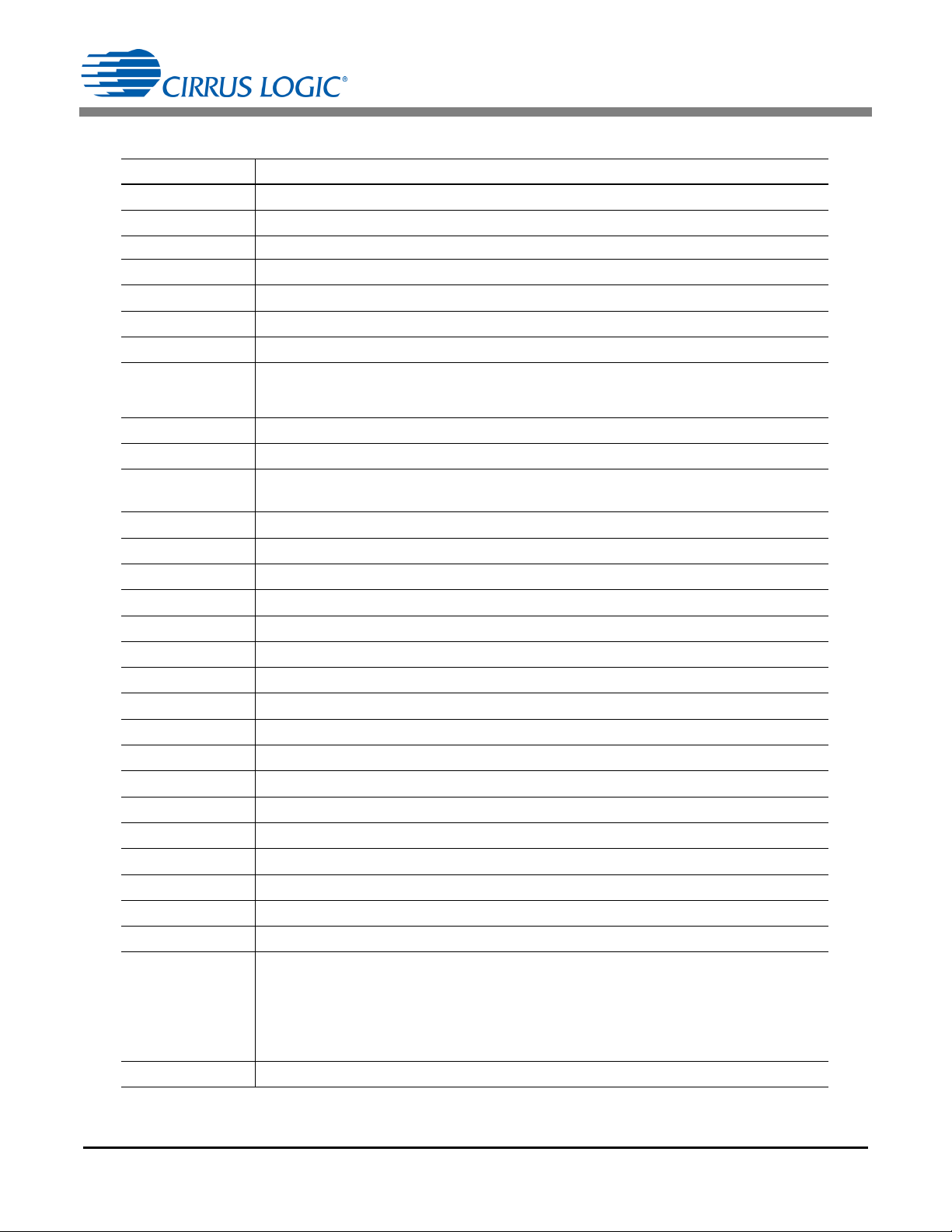

TABLE OF CONTENTS

1 OVERVIEW OF THE CS1630 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

2 INTRODUCTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2.1 Definition of Acronyms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.2 Definition of Symbols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3 DESIGN PROCESS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.1 Operating Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.2 Design Process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.3 Design Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Step 1) Select Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Step 2) Design for a Flyback Topology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

a. Set OTP for a Series Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

b. Selecting a Flyback Topology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Step 3) Determine Second-stage Parameters for a Flyback Topology . . . . . . . . . . . . . . . . . . . . . . . . . 12

a.Set the Value for Boost Output Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

b. Select an Appropriate FET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

c. Determine the Flyback Transformer Turns Ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

d. Select the Full Brightness Switching Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

e. Determine the Flyback Nominal Timing T1 and T2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

f. Calculate the Flyback Primary-side Inductance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

g. Calculate Peak Current on the Flyback Primary-side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

h. Determine the RMS Current in the Winding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

i. Calculate R

j. Calculate Flyback Zero-current Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

k. Determine Output Capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

l. Flyback Transformer Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

m.Recalculate R

Step 4) Tune Second-stage Performance and Limiting Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

a.PID Feedback Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

b. Leading-edge Blanking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

c. Trailing-edge Blanking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

d. Maximum Gate Drive Duration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

e. Minimum Measurable Peak Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

f. T2 Time-out Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

g. Automated Resonant Period Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

h. Switching Frequency Across Dim Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Step 5) Optimize Output Current Regulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

a.Definition and Scope of Second-stage Output Current Regulation . . . . . . . . . . . . . . . . . . . . 24

b. Tune Flyback ZCD Fixed Delays for Optimum Valley-switching Performance . . . . . . . . . . . 25

c. Tune I

PK(FB)

d. Set T2 Offset Delays to Get Optimum Linear Performance . . . . . . . . . . . . . . . . . . . . . . . . . . 27

e. T2 Commutation Time Delay Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

f. Procedure for Measuring the Second-stage Output Current Regulation . . . . . . . . . . . . . . . . 31

Step 6) Synchronizer Circuit Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

a.Phase Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

b. Flyback Mode Operation Using a Dual LED String Synchronizer Circuit . . . . . . . . . . . . . . . . 33

c. Synchronizer Circuit RC Filter Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Step 7) Color System Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.4 Boost Stage Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Step 8) Determine I

PK(BST)

(R21) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Sense

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Sense

Compensations for Optimum Linear Performance . . . . . . . . . . . . . . . . . . . . . . 26

, I

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

SAT

AN368REV2 3

Page 4

AN368

Step 9) Boost Inductor Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Step 10) Determine Boost Output Capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Step 11) Determine Boost Input Capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.5 Completing the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Step 12) Choose Power Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Step 13) Bias Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Step 14) Boost Zero-current Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Step 15) Enable and Tune Protection Mechanisms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

a.Protection Restart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

b. Overcurrent Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

c. Open Loop Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

d. Overvoltage Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

e. Short Circuit Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

f. Voltage Difference Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

g. Boost Overvoltage Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

h. Clamp Overpower Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

i. Link Line Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

j. External Overtemperature Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

k. Internal Overtemperature Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Step 16) Clamp Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Step 17) Designing the EMI Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

a.I

Step 18) Layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

4 DESIGN EXAMPLE . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

4.1 Design Steps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Step 1) Select Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Step 2) Design for a Flyback Topology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

a. Set OTP for a Series Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

b. Selecting a Flyback Topology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Step 3) Determine Second-stage Parameters for a Flyback Topology . . . . . . . . . . . . . . . . . . . . . . . . . . 52

a. Set the Value for Boost Output Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

b. Select an Appropriate FET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

c. Determine the Flyback Transformer Turns Ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

d. Select the Full Brightness Switching Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

e. Determine the Flyback Nominal Timing T1 and T2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

f. Calculate the Flyback Primary-side Inductance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

g. Calculate Peak Current on the Flyback Primary-side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

i. Calculate R

j. Calculate Flyback Zero-current Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

k. Determine Output Capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

l. Flyback Transformer Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

m. Recalculate R

Step 4) Tune Second-stage Performance and Limiting Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

a. PID Feedback Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

b. Leading-edge Blanking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

c. Trailing-edge Blanking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

d. Maximum Gate Drive Duration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

e. Minimum Measurable Peak Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

f. T2 Time-out Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

g. Automated Resonant Period Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Step 5) Optimize Output Current Regulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

a. Definition and Scope of Second-stage Output Current Regulation . . . . . . . . . . . . . . . . . . . . 60

b. Tune Flyback ZCD Fixed Delays for Optimum Valley-switching Performance . . . . . . . . . . . 60

DAC Dithering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Sense

(R21) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Sense

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Sense

4 AN368REV2

Page 5

AN368

c. Tune I

Compensations for Optimum Linear Performance . . . . . . . . . . . . . . . . . . . . . . 60

PK(FB)

d. Set T2 Offset Delays to Get Optimum Linear Performance . . . . . . . . . . . . . . . . . . . . . . . . . . 60

e. T2 Commutation Time Delay Compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

f. Procedure for Measuring the Second-stage Output Current Regulation . . . . . . . . . . . . . . . . 61

Step 6) Synchronizer Circuit Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

a. Phase Synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

b. Flyback Mode Operation Using a Dual LED String Synchronizer Circuit . . . . . . . . . . . . . . . . 61

c. Synchronizer Circuit RC Filter Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Step 7) Color System Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

4.2 Boost Stage Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Step 8) Determine I

PK(BST)

, I

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

SAT

Step 9) Boost Inductor Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Step 10) Determine Boost Output Capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Step 11) Determine Boost Input Capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.3 Completing the Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Step 12) Choose Power Components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Step 13) Bias Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Step 14) Boost Zero-current Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Step 15) Enable and Tune Protection Mechanisms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

a. Protection Restart . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

b. Overcurrent Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

c. Open Loop Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

d. Overvoltage Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

e. Short Circuit Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

f. Voltage Difference Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

j. External Overtemperature Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

k. Internal Overtemperature Protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Step 16) Clamp Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Step 17) Designing the EMI Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

a. I

DAC Dithering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Sense

5 APPENDIX . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

5.1 OTP Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

5.2 Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

5.3 Dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.4 Bill of Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

AN368REV2 5

Page 6

AN368

2 Introduction

This application note provides a guide to designing a solid-state lighting (SSL) LED lamp circuit using Cirrus Logic's

CS1630. The second-stage topology is a flyback topology with a series LED lamp stack as the output configuration.

The first half of the document presents a step-by-step design procedure for calculating the required components for

each stage of the system. The second half of the document supports the design effort by showing an example of a

CS1630 design. The CS1630 example is based on the Cirrus Logic CRD1630-9W reference design. See the

CS1630/31 2-Channel TRIAC Dimmable LED Driver IC data sheet for more details about the CS1630 IC. See the

CRD1630-9W 9 Watt Reference Design and CRD1631-9W 9 Watt Reference Design data sheets for more details

regarding the reference design.

Further Reading

• See the CS1630/31 data sheet DS954 2-Channel TRIAC Dimmable LED Driver IC to review the features

and specifications of the CS1630/31.

• See application note AN372 Design Guide for a CS1612 and CS1613 Dimmer-compatible SSL Circuit for

more information about designing the CS1612/13.

• See customer reference design data sheet DS989RD1 CRD1630-9W 9 Watt Reference Design for more

information about the CRD1630.

• See customer reference design data sheet DS990RD1 CRD1631-9W 9 Watt Reference Design for more

information about the CRD1631.

• See application note AN369 CS1630/31 Device Programmer User Guide for more information about using

the application software to program the CS1630/31.

6 AN368REV2

Page 7

2.1 Definition of Acronyms

Acronym Description

PFC Power Factor Correction

ZCD Zero-current Detection

BOP Boost Overvoltage Protection

COP Clamp Overpower Protection

OVP Second-stage Output Open Circuit Protection and Overvoltage Protection

OCP Second-stage Overcurrent Protection

OLP Second-stage Open Loop Protection

SCP Short Circuit Protection

iOTP Internal Overtemperature Protection

eOTP External Overtemperature Protection

PLC Power Line Calibration

OTP One-time Programmable

LED Light Emitting Diode

TX Transformer

TRIAC

FET Field-effect Transistor

NTC

SSL

CSV Comma-separated Values File

CCT Correlated Color Temperature

DAC Digital-to-Analog Converter

CRM Critical Conduction Mode

DCM Discontinuous Conduction Mode

LSB Least Significant Bit

MSB Most Significant Bit

PID Proportional-integrated-derivative Controller

EMI Electromagnetic Interference

GD Gate Drive

TRIode for Alternating Current, which is an electronic component that can conduct current in either

direction when it is triggered. It is formally called a bidirectional triode thyristor.

Negative Temperature Coefficient thermistor

Solid-state lighting. Refers to a type of lighting that uses semiconductor LEDs as a source of illumination rather than electrical filaments, plasma, or gas.

AN368

AN368REV2 7

Page 8

2.2 Definition of Symbols

T1

CH1

TT

CH1

----------------

T1

CH2

TT

CH2

----------------

Symbol Description

F

sw

& F

F

sw1

sw2

TT Second-stage switching period

& TT

TT

T1

T2

T3

CH1

CH1

CH1

CH1

& T1

& T2

& T3

CH2

CH2

CH2

CH2

Second-stage switching frequency

Switching frequency for channel 1 and channel 2

Switching period for channel 1 and channel 2

Second-stage primary FET ‘ON’ time for channel 1 and channel 2

Second-stage secondary rectifier diode conduction time for channel 1 and channel 2

Time the second-stage FET and rectified diode are ‘OFF’ for channel 1 and channel 2

AN368

D

MODE1

I

PK1(FB)

I

MODE1

V

MODE1

GAIN

R

I

V

NTC

CH1

DR

& D

V

IN

Reflected

V

CLAMP

I

PK(FB)

& I

& I

& V

R

Sense

& T

I

PK(BST)

L

P

L

BST

V

BST

N

V

CH1

V

CH2

& I

P

OUT

I

Red

I

White

dim

& GAIN

MODE2

PK2(FB)

MODE2

MODE2

NTC

CH2

DTR

Duty ratio for Mode 1 and Mode 2

Input line voltage

Voltage across secondary winding reflected onto primary

Primary clamping voltage above boost output voltage (V

BST

)

Maximum second-stage peak current in primary-side FET

Maximum second-stage peak current in primary-side FET for Mode 1 and Mode 2

Output current for Mode 1 and Mode 2

Output voltage for Mode 1 and Mode 2

Second-stage primary current sense resistor

Negative temperature coefficient resistance and corresponding temperature

Maximum boost inductor current

Second-stage primary inductance

Boost inductance

Boost output voltage

Flyback transformer turns ratio N

P/NS

Channel 1 secondary output VDC (channel 1 LED string supply voltage)

Channel 2 secondary output VDC (channel 2 LED string supply voltage)

Channel 1 and channel 2 LED string current

Load power = Power to the LED string

Output current that flows through the amber/red color LED string

Output current that flows through the white/blue color LED string

The CS1630/31 color control system has the ability to maintain a constant CCT or change

CCT as the light dims. OTP configurations allow the selection of the dimming profile. A

specific CCT profile can be programmed to the digital mapping device. The mapping is

two-dimensional: one current versus temperature profile is generated for each dim level.

The CS1630/31 provides two-dimensional mapping for the color LED’s current only, and

one-dimensional mapping (current versus dim level) for the other string.

The dim-regulated gain and dim-regulated plus temperature-regulated gain

8 AN368REV2

Page 9

AN368

TX1

Z3

L1

L3

R14

R6

R7

R13

R8

R1

Q2

L2

Z2

C23

D7

D2

Q4

Q1

D3

R17

R18

R22

R23

Q5

R21

R27

R5

BR1

F1

R33

D8

R36

CS1630 /31

IAC

FBAUX

BSTOUT CLAMP

GD

FBSEN SE

eOTP

VDD

SOURCE

CY

D2

L

N

AC Mains

D1

R25

R9

R11

R24

D4

BSTAUX

R24

Boost

Gate Bias

Steady State

Supply

Active

Clamp

Second S tage

Flyback

EMI

C11

C17 C12

C5

C9

C11

C6

C1

C4

C13

R3

D6

U2

C10

C8

C15

D5

D

GND

_

Q

VCC

D15

R12

D10

Q3

R2

C16

SGND GND

GND

IGND

C24

R29

NTC

D9

Phase

Sync

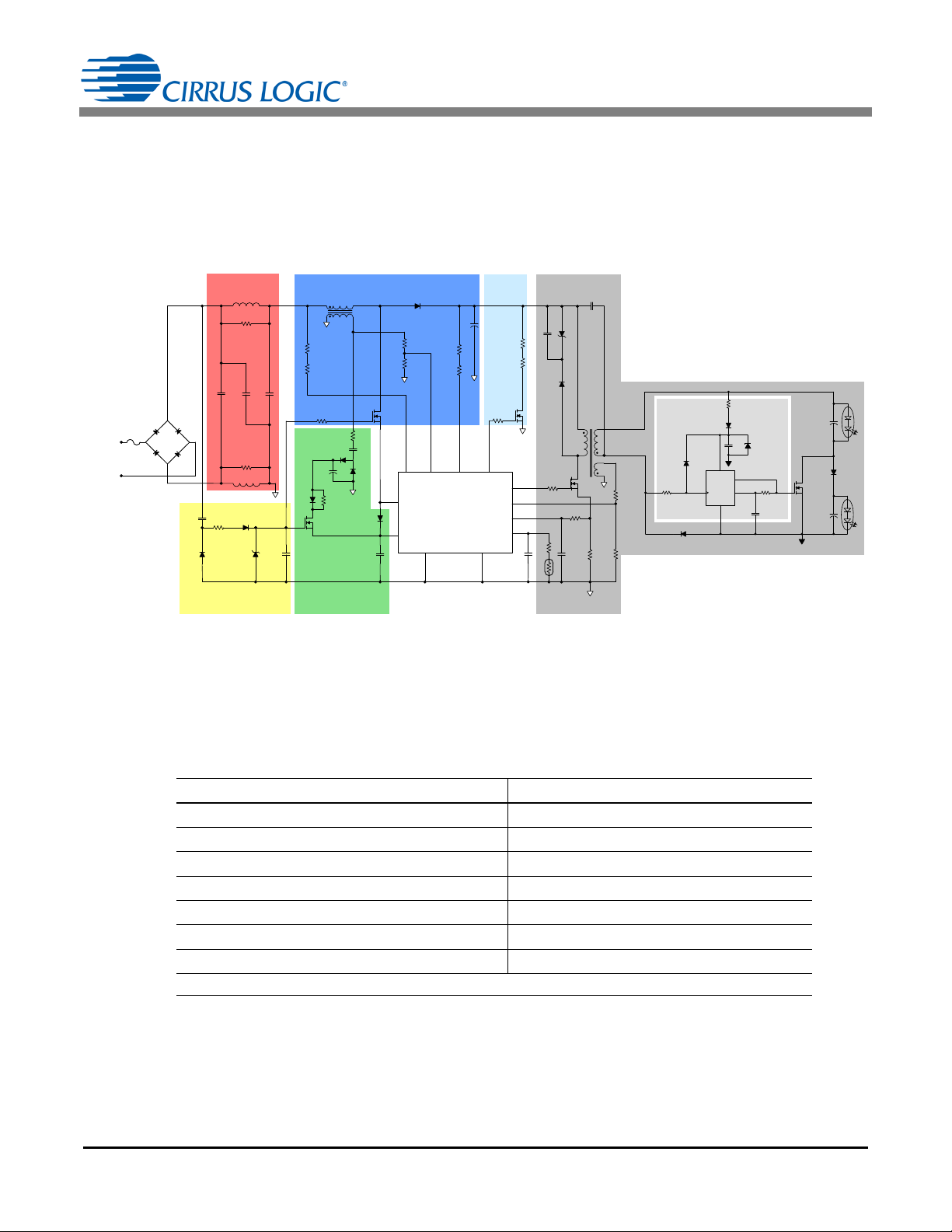

Figure 1. Diagram of CS1630 Design

Driving Two LED Strings in Series

3 Design Process

The design process for a two-stage power converter system can be partitioned into seven circuit blocks (see

Figure 1). The AC line voltage is passed through an electromagnetic interference (EMI) filter to prevent injection of

switching noise from the driver into the power line. The output of the EMI filter is then converted to the desired DC

output by a boost PFC followed by a flyback converter. The second stage is an isolated flyback circuit that requires

a phase synchronizer to control the two-channel output currents. The power converter system includes the Gate Bias, Steady State Supply, and Active Clamp support circuitry.

3.1 Operating Parameters

To initiate the design procedure, a set of operating parameters is required. Operating parameters required for

the analytical process are outlined in the table below. Parameters critical to the overall design, but not

specifically addressed in this document, include EMI compliance, efficiency, form factor, layout, and operating

temperature.

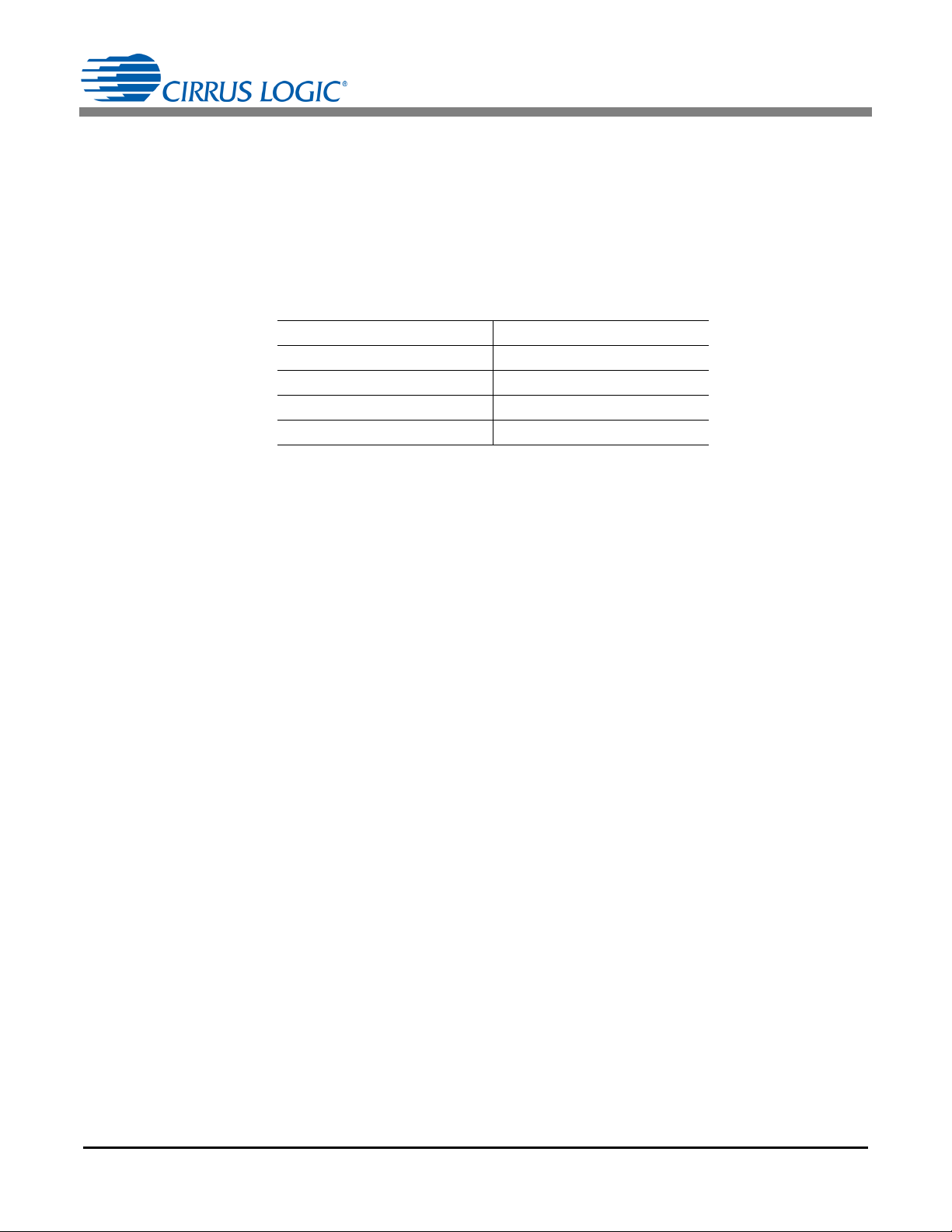

Parameter Symbol

Output Power

AC Line Input Voltage

Channel 1 Secondary Output Voltage

Channel 2 Secondary Output Voltage

Channel 1 Load Current

Channel 2 Load Current

Maximum Switching Frequency*

* Increasing Fsw may reduce the size of the magnetics but increases switching losses in the FET.

AN368REV2 9

P

OUT

V

IN

V

CH1

V

CH2

I

CH1

I

CH2

F

sw(max)

Page 10

3.2 Design Process

The design process requires a specification covering the required operating range, color temperature, dimmer

compatibility, form factor, and applicable standards. Once those specifications are defined, the recommended

design process is as follows:

Design the Flyback Stage

• Define power-stage components, such as the MOSFET and zener clamp, based on certain considerations,

including cost, performance, and space

• Calculate transformer parameters and remaining power-stage components

• Design transformer based on cost, size, and performance

• Design Synchronizer Circuit

• Specify protection thresholds

Design the Color System

Perform curve fit that meets target specifications for color and lumen output across the dimming range

Design the Boost Stage

• Pick power semiconductors for the boost stage based on input power required by flyback and nominal link

voltage

• Determine peak current in the boost stage during No-dimmer Mode

• Boost inductor design based on providing best-case tradeoff between efficiency, EMI, and size of

magnetics

AN368

Design of the Other Non-power Conversion Circuitry

• Design charge pump, auxiliary supply circuit for providing V

• Clamp circuit

Design the EMI Filter

• Design EMI filter to meet required compliance

Design Other Protections

• ZCD

• OCP, OLP, OVP, VDIFF, BOP, COP, LLP

• eOTP, iOTP

Layout the PCB

• Observe GND rules

• Sensitive traces

Optimize Output Regulation of Flyback Section

• Correct for actual ZCD offsets

• Compensate T2 commutation time

• I

Program the Device

• OTP memory

• Compute CRC

• OTP Verification

(T1) compensation

PK(FB)

to the IC

DD

Optimize EMI Filter

• Verify EMI filter meets dimmer compatibility

• Optimize EMI filter for compliance

10 AN368REV2

Page 11

3.3 Design Procedure

D2

R22

Z3

R21

R23

Q5

CS1630 /31

FBAUX

GND

13

GD

FBSEN SE

15

12

11

TX1

V

BST

R3

D6

U2

C10

C8

C15

D5

D

GND

_

Q

VCC

D15

R12 D10

Q3

R2

C16

Channel 1 LED

(White)

Channel 2 LED

(Red)

GND

IGND

I

MODE x

I

PRI

V

MODE x

D9

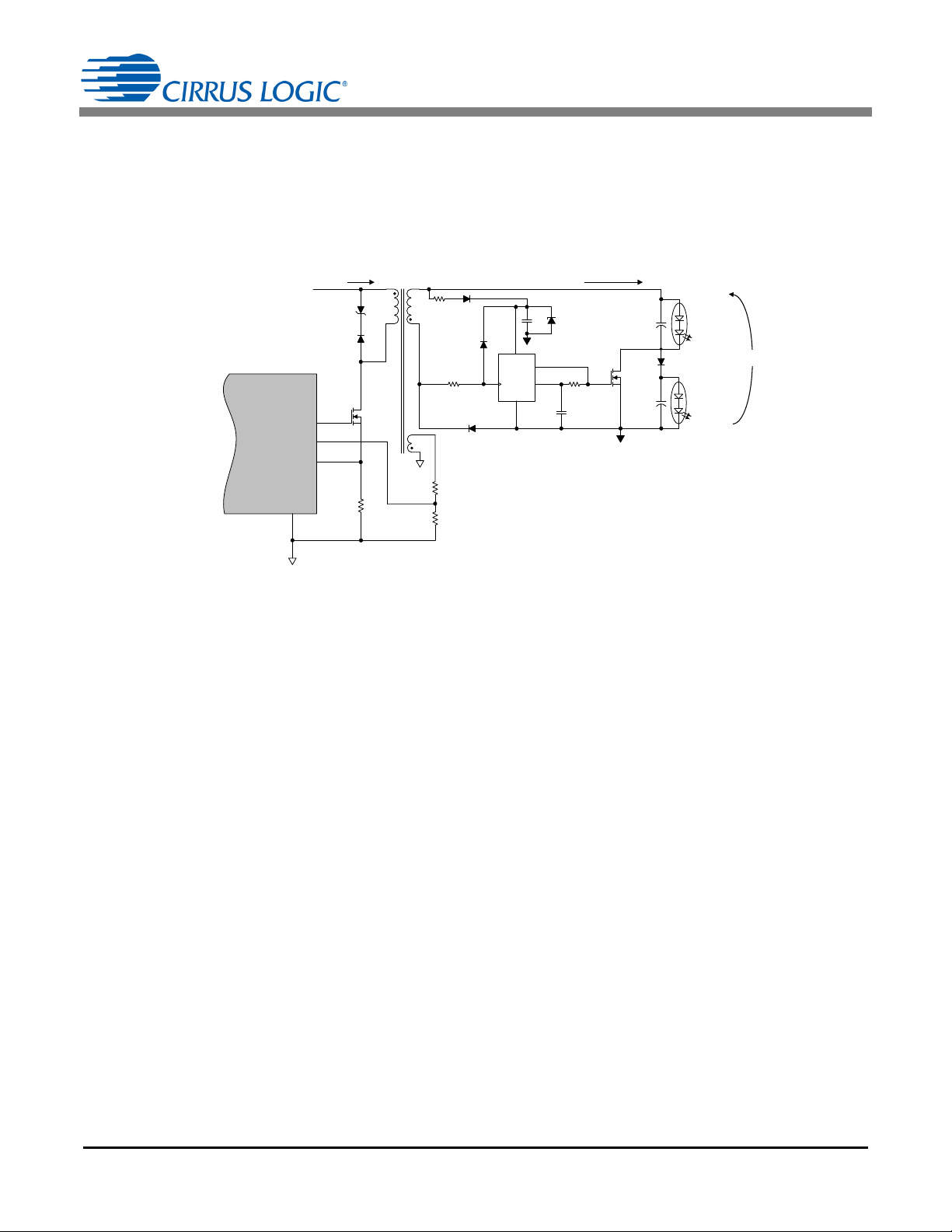

Figure 2. Flyback Series Output Model

Step 1) Select Input Voltage

The CS1630 is optimized for 120VAC line voltage applications and designs targeting 108 to 132 VAC markets.

Step 2) Design for a Flyback Topology

The light engine is defined for a flyback topology in a series configuration. Figure 2 illustrates a flyback

topology with a series lamp configuration.

AN368

This document focuses on designing and programming a driver with a flyback topology in a series

configuration. Cirrus Logic, Inc. and its affiliates and subsidiaries generally make no representations or

warranties that the combination of Cirrus Logic’s products with light-emitting diodes (“LEDs”), converter

materials, and/or other components will not infringe any third-party patents, including any patents related to

color mixing in LED lighting applications, such as, for example, U.S. Patent No. 7,213,940 and related patents

of Cree, Inc. For more information, please see Cirrus Logic’s Terms and Conditions of Sale, or contact a Cirrus

Logic sales representative.

a. Set OTP for a Series Configuration

The two LED strings are arranged in series so that current passes through either one or both LED strings. A

MOSFET is used to shunt current around one string on alternating switching cycles. In this configuration, one

string is required to have a larger output current than the other string.

When considering a series design, it is recommended that the current flowing through one of the LED channels

be 80% or lower than that of the other LED channel at all times. The LED string that has current flowing

continuously is referred to as channel 1 LED (I

channel 2 LED (I

CH2

); I

CH2

0.8I

. A good rule of thumb is that channel 2 LED must always have a forward

CH1

), while the string with the bypass FET is referred to as

CH1

voltage of 85% or lower than channel 1 LED.

The LED_ARG bit in register Config3 at Address 35 selects which channel is connected to the color LED string.

When bit LED_ARG is set to ‘1’, the color LED string is connected to channel 2.

The STRING bit in register Config3 at Address 35 selects the second-stage output channel configuration.

When bit STRING is set to ‘1’, a series configuration is selected.

b. Selecting a Flyback Topology

Flyback topology is enabled by setting bit S2CONFIG to ‘1’ in register Config12 at Address 44. The flyback

transformer input-to-output voltage ratio is used to determine the duty cycle and minimum turn ‘ON’ switching

period T1 for the power FET. The flyback transformer is designed as an isolated topology, and the digital

synchronization signal needs to be disabled. Set bit SYNC in register Config4 at Address 36 to ‘0’. Since bit

S2CONFIG is configured for a flyback topology, bits BUCK[3:0] in register Config10 at Address 42 are ignored

by the digital algorithm.

AN368REV2 11

Page 12

Step 3) Determine Second-stage Parameters for a Flyback Topology

Steps for the Flyback Design

1. Set the boost output voltage, V

BST

.

2. Select a MOSFET that aligns with the quality standards

of the designer’s company.

3. Determine the transformer turns ratio from the

V

BST

, FET

voltage, and reflected voltage, V

Reflected

.

4. Use the nominal switching frequency and an initial

estimate for time T3 to determine the value of time TT at

full brightness.

5. Use V

BST

, TT, and V

Reflected

to determine time T1 and

T2.

6. Use time T2 and TT, turns ratio N, and load current to

determine the value of the peak primary current, I

PK(FB)

.

7. Use I

PK(FB)

to determine R

Sense

.

8. Calculate the primary-side inductance using time T1.

9. Calculate flyback gain resistor R

FBGAIN

using full load

conditions. Ensure linearity of the load versus the dim

curve.

10. Calculate primary and secondary RMS currents using

I

PK(FB)

and duty cycle.

11. Select an output capacitor.

12. Determine the flyback transformer specifications.

13. Determine if the flyback transformer fits into specified

form factor after designing and constructing flyback

transformer. Repeat steps 3 to 12 until form factor

criteria is met.

14. Refinements to the circuit with final flyback transformer

design.

15. Validate that the system meets the operating criteria.

Second Stage

Flyback Specifications

Determine N, Fsw,

V

Reflec ted

, and V

CLAMP

Estimate T3

Calculate TT

fb

Calculate R

Sense

,

R

FBG AIN

, and Primary

Inductance

Color System

Parameters

Fit?

Yes

No

Calculate T1,

T2, and I

PK(FB)

Calculate RMS Current

and Output Capacitor

Transformer Core

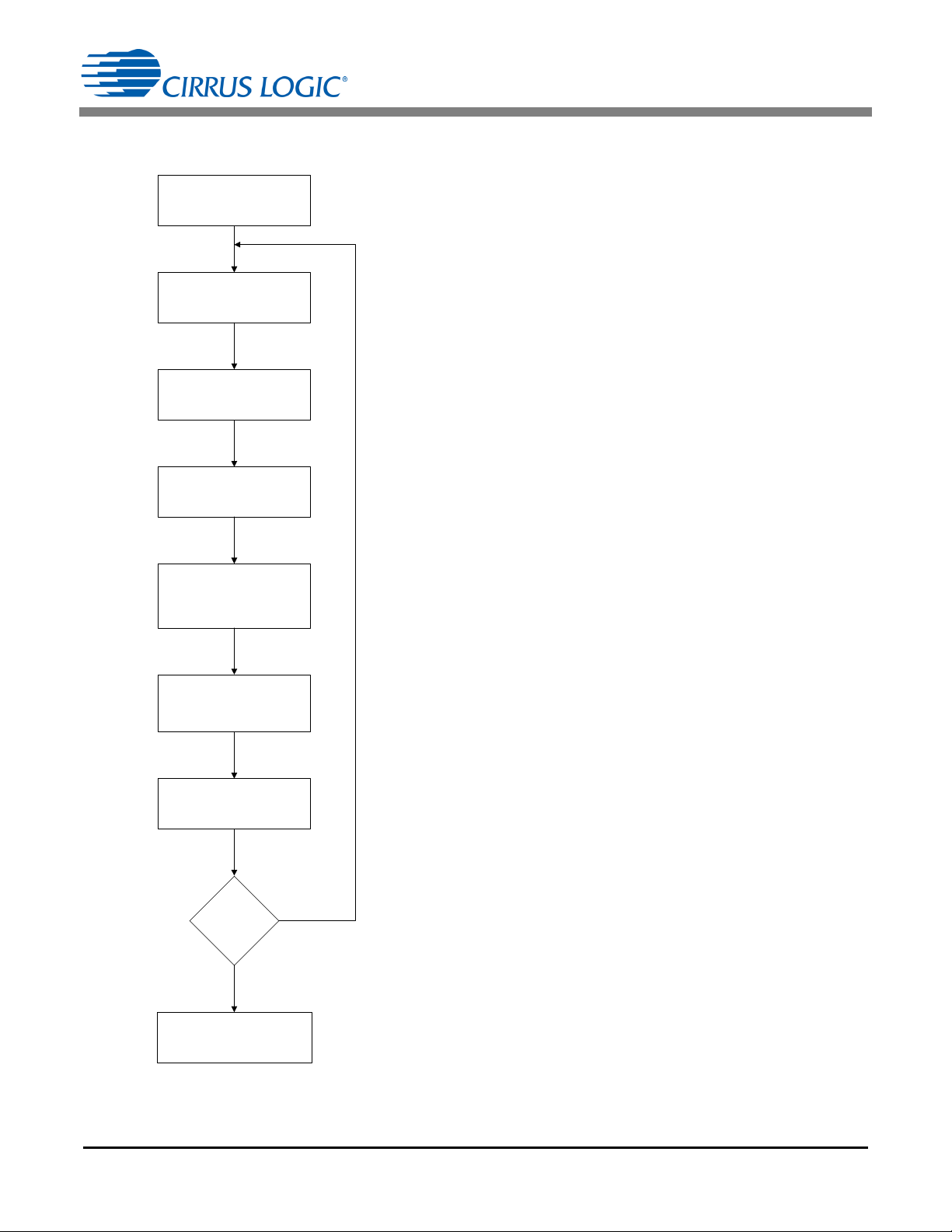

Figure 3. Flyback Stage Design

Figure 3 illustrates the steps for designing the second stage.

AN368

12 AN368REV2

Page 13

AN368

V

Drain maxVBST maxVZener max

+=

[Eq. 1]

V

Overshoot

V

ZenerVReflecteed

–=

[Eq. 2]

V

Margin

V

Zener

V

BST

V

Overshoot

V

Reflected

F

ET Breakdown

Voltage Rating

Clamp

Zener

Voltage

Boost Output

Voltage

Margin

Reflected

Voltage

Overshoot

Voltage

Overshoot is a brief condition above

V

Reflected

, required to quickly dissipate

the energy stored in the transformer

leakage inductance.

During this time, the primary current is

kept from transferring to the secondary, siphoning energy from the load to

the clamp zener (snubber).

Figure 3. FET Breakdown Voltage

a. Set the Value for Boost Output Voltage

The value of the boost output voltage V

maximum V

voltage V

BST

BST(max)

should be kept as low as possible to help keep the FET breakdown

requirement within economical constraints.

V

is determined by an internal parameter and changes slightly depending on the type of dimmer detected.

BST

With sense resistors R13, R14, R17, and R18 set to 750k each, the resulting V

for a 120V system. V

line-cycle. V

droops to its lowest value towards the end of each half line-cycle until the boosting process

BST

is regulated by charging the boost output capacitor to its nominal value each half

BST

starts again in the next half line-cycle.

b. Select an Appropriate FET

Determine the FET Q5 breakdown voltage V

drain voltage V

Drain(max)

is calculated using Equation 1.

The ringing associated with the transformer leakage inductance usually does not have enough energy to

cause a destructive avalanche breakdown. Voltages closely approaching the FET breakdown voltage are

acceptable. Alternatively, V

should be much greater than V

Zener

in the transformer leakage inductance.

The FET breakdown voltage is constrained by cost and performance. A compromise must be reached in

partitioning voltage between V

V

Zener

into V

Reflected

and a reasonable overshoot voltage portion, V

BST

, V

The losses caused by the leakage inductance are inversely proportional to V

Equation 2.

must be greater than the maximum input AC line voltage peak. The

BST

is approximately 200 V

BST

Zener

Breakdown

, and V

and reflected voltage V

Reflected

. A second compromise then determines how to divide

Margin

to rapidly discharge the energy stored

Overshoot

Reflected

.

Overshoot

. The FET maximum

, which is determined by

AN368REV2 13

Page 14

AN368

[Eq. 3]

V

Breakdown

V

BST maxVZenerVMinarg

++=

N

V

Reflected

V

CH1 maxVCH2 max

+

--------------------------------------------------------------

=

[Eq. 4]

i(t)

T1

CH1

T2

CH1

TT

CH1

No Current

T3

CH1

Secondary

Current

t

T1

CH2

T2

CH2

No Current

T3

CH2

Secondary

Current

TT

TT

CH2

Peak Primary Current 2, I

PK2(FB)

Primar y

Current

Peak Primary Current 1, I

PK1(FB)

Primar y

Current

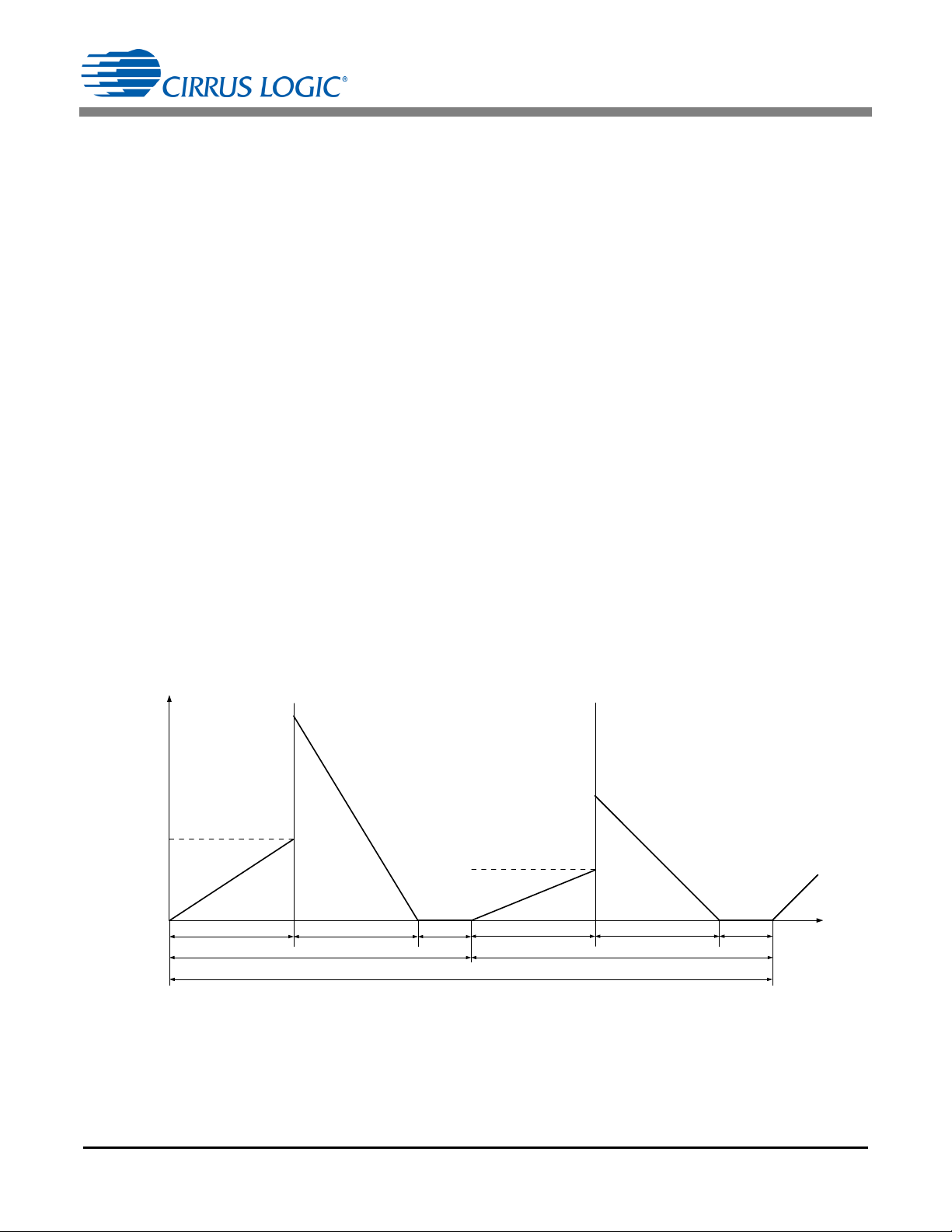

Figure 4. Timing Diagram for Switching Frequencies

1

F

sw max

---------------------

TTFREQ[7:0] 4 50ns=

[Eq. 5]

For optimum efficiency, the increase in transformer losses (created by an uneven duty cycle) must balance the

reduction of the losses caused by discharging the leakage inductance (obtained by increasing the overshoot

voltage). Equation 3 is used to balance all voltages contributing to the FET voltage drain and source.

where,

V

Overshoot

c. Determine the Flyback Transformer Turns Ratio

Select a turns ratio based on the channel output voltage, V

where,

V

CH1(max)

V

CH2(max)

d. Select the Full Brightness Switching Frequency

The CS1630 has two switching events with frequencies F

frequency F

1. Maximum channel-switching frequencies F

2. Maximum flyback stage switching frequency F

3. For EMI considerations, the higher switching frequency between the two channels should be less than

4. Switching frequency F

5. Switching frequencies F

= V

Zener

- V

Reflected

= Maximum channel 1 LED forward voltage V

= Maximum channel 2 LED forward voltage V

. Common criteria for determining the desired switching frequency include:

sw

sw1(max)

75kHz.

should be in audible range only at low power.

sw

sw1

and F

are selected such that the size of the flyback transformer meets

sw2

the converter system form factor requirements.

, V

CH1

at full current plus the rectifying diode voltage VF.

CH1

at full current plus the rectifying diode voltage VF.

CH2

and F

sw1

and F

sw2(max)

is less than 100kHz.

sw(max)

, and V

CH2

sw2

Reflected

that make up a complete switching

, using Equation 4.

are less than 200kHz.

14 AN368REV2

The maximum switching frequency F

Address 46. Bits TTFREQ[7:0] set the minimum allowable target period for the second-stage time TT:

sw(max)

for the second stage is configured using the TTFREQ register at

Page 15

AN368

1

F

sw min

--------------------

TT MAX[7:0] 128 127+50ns= [Eq. 6]

V

MODE1

V

CH1VCH2VD15VD5

+++=

[Eq. 7]

I

MODE1ICH2

=

[Eq. 8]

V

MODE2

V

CH1VD15

+=

[Eq. 9]

I

MODE2ICH1ICH2

–=

[Eq. 10]

The minimum switching frequency F

for the second stage is configured to provide good power

sw(min)

regulation. The minimum switching frequency should be set to the smallest possible value, but it should remain

outside of the audible frequency range. F

is configured using register TTMAX at Address 38. Bits

sw(min)

TTMAX[7:0] set the maximum allowable target period for the second-stage time TT:

The maximum second-stage switching period that is measured by the controller algorithm is set using bits

TT_MAX[1:0] in register Config3 at Address 35.

TT_MAX[1:0] Max Switching Period

0 51.15s

1 102.35s

2 153.55s

3 204.75s

Table 1. Maximum Measurable Switching Period

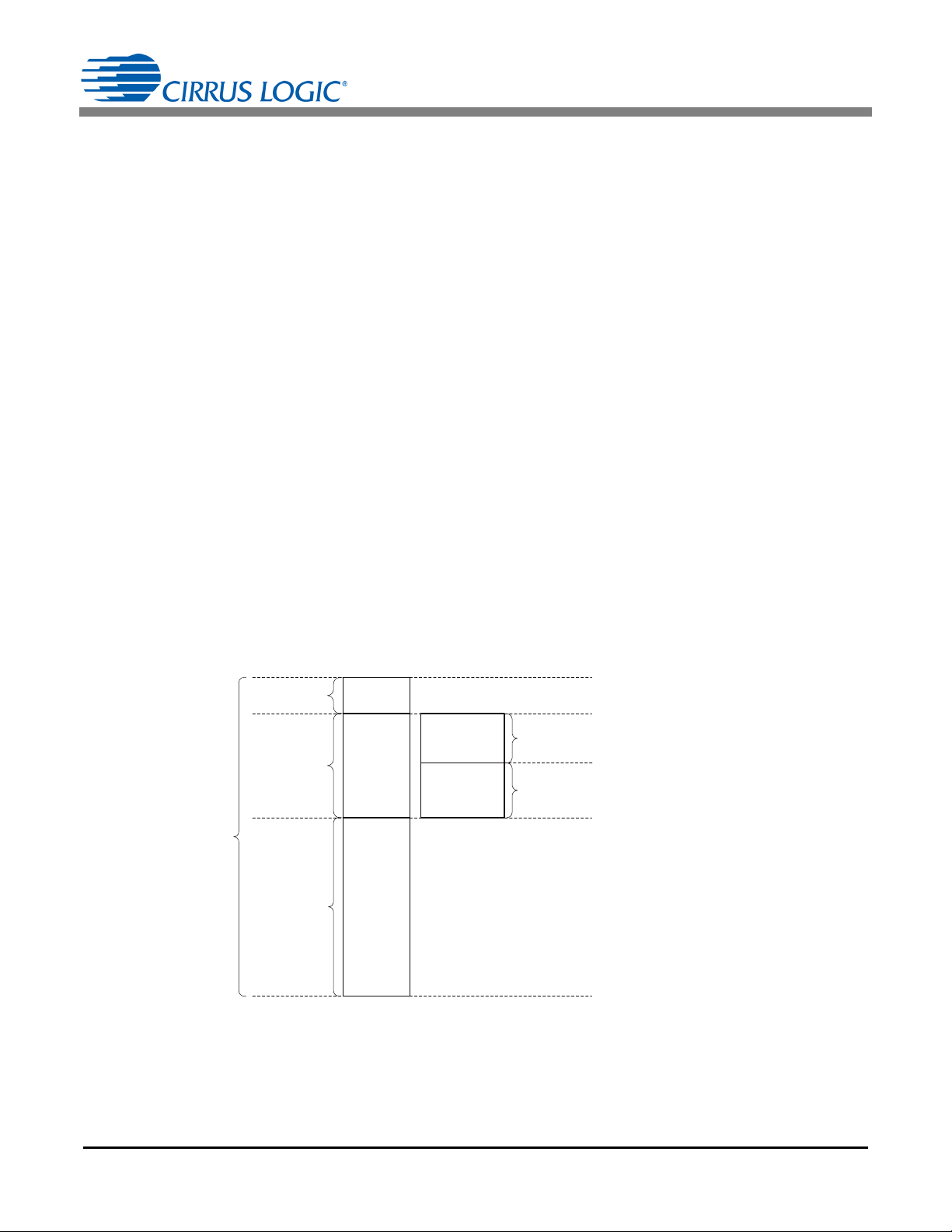

There are two modes of operation, and the output configuration in each of these modes is different.

Mode 1: Switching Event TT

In Mode 1 the phase synchronizer FET Q3 is switched ‘OFF’. Output voltage V

I

are calculated using Equations 7 and 8, respectively:

MODE1

CH1

and output current

MODE1

where,

V

= Channel 1 secondary output VDC (channel 1 LED string supply voltage)

CH1

V

= Channel 2 secondary output VDC (channel 2 LED string supply voltage)

CH2

V

= Forward bias voltage across diode D15

D15

V

= Forward bias voltage across diode D5

D5

I

= Channel 2 LED current

CH2

Mode 2: Switching Event TT

In Mode 2, phase synchronizer MOSFET Q3 is switched ‘ON’. Output voltage V

I

are calculated using Equations 9 and 10, respectively:

MODE2

CH2

and output current

MODE2

where,

I

= Channel 1 LED current

CH1

e. Determine the Flyback Nominal Timing T1 and T2

Assume that the power transferred in Mode 1 is greater than the power transferred in Mode 2. Select a Mode 1

switching frequency F

for optimal driver performance using the criteria described above.

sw1

AN368REV2 15

Page 16

AN368

[Eq. 11]

D

MODE1

NV

MODE1

V

BST

NV

MODE1

+

----------------------------------------------------------

=

[Eq. 12]

D

MODE2

NV

MODE2

V

BST

NV

MODE2

+

----------------------------------------------------------

=

TT

CH1

T1

CH1

T2

CH1

+

1

F

sw1

-----------

==

[Eq. 13]

F

sw2

F

sw1

V

BST

NV

MODE1

+

V

BST

NV

MODE2

+

----------------------------------------------------------

I

MODE1VMODE2

I

MODE2VMODE1

------------------------------------------

=

[Eq. 14]

TT

CH2

T1

CH2

T2

CH2

+

1

F

sw2

-----------

==

[Eq. 15]

TT

CH1

T= 1

CH1

T2

CH1

T3

CH1

++

[Eq. 16]

TT

CH2

T= 1

CH2

T2

CH2

T3

CH2

++

[Eq. 17]

TT TT

CH1

TT

CH2

+=

[Eq. 18]

F

sw

1

TT

-------

=

[Eq. 19]

[Eq. 20]

T1

CH1

TT

CH1

T3

CH1

–D

MODE1

=

[Eq. 21]

T1

CH2

TT

CH2

T3

CH2

–D

MODE2

=

Calculate Mode 1 duty ratio D

Assuming the resonant times T3

and Mode 2 duty ratio D

MODE1

and T3

CH1

CH2

using Equations 11 and 12, respectively:

MODE2

are zero, the remaining relevant flyback stage parameters can

be calculated using the turns ratio N calculated in Equation 4 and the switching frequency F

Mode 1. Calculate period TT

Calculate switching frequency F

Calculate period TT

using Equation 15:

CH2

using Equation 13:

CH1

using Equation 14:

sw2

selected for

sw1

The resonant times T3

CH1

and T3

are estimated for both channels. Deriving a more accurate value of the

CH2

resonant ringing time is discussed in Step 4g Automated Resonant Period Measurements on page 22. To

account for times T3

periods TT

CH1

and TT

and T3

CH1

using Equations 16 and 17, respectively.

CH2

that were neglected in the first approximation of Equation 13, recalculate

CH2

Calculate total period TT using Equation 18:

Calculate switching frequency Fsw using Equation 19:

Calculate the MOSFET ‘ON’ time T1

Calculate the MOSFET ‘ON’ time T1

in Mode 1 using Equation 20:

CH1

in Mode 2 using Equation 21:

CH2

16 AN368REV2

Page 17

AN368

[Eq. 22]

T2

CH1

TT

CH1

T1

CH1

– T3

CH1

–=

[Eq. 23]

T2

CH2

TT

CH2

T1

CH2

– T3

CH2

–=

[Eq. 24]

L

P

N2V

BST

2

V

MODE1

2V

BST

NV

MODE1

+

2

I

MODE1

TT F

sw1

2

-----------------------------------------------------------------------------------------------------------------------

=

[Eq. 25]

I

PK1 FBVBST

T1

CH1

L

P

----------------

=

[Eq. 26]

I

PK2 FBVBST

T1

CH2

L

P

----------------

=

[Eq. 27]

I

MODE1 avgIPK1 FB

N

T2

CH1

2TT

----------------

=

[Eq. 28]

I

MODE2 avgIPK2 FB

N

T2

CH2

2TT

----------------

=

[Eq. 29]

I

PRI RMSIPK1 FB

2

D

MODE1

3

--------------------

I

PK2 FB

2

D

MODE2

3

--------------------

+=

Calculate the MOSFET ‘OFF’ time T2

Calculate the MOSFET ‘OFF’ time T2

in Mode 1 using Equation 22:

CH1

in Mode 2 using Equation 23:

CH2

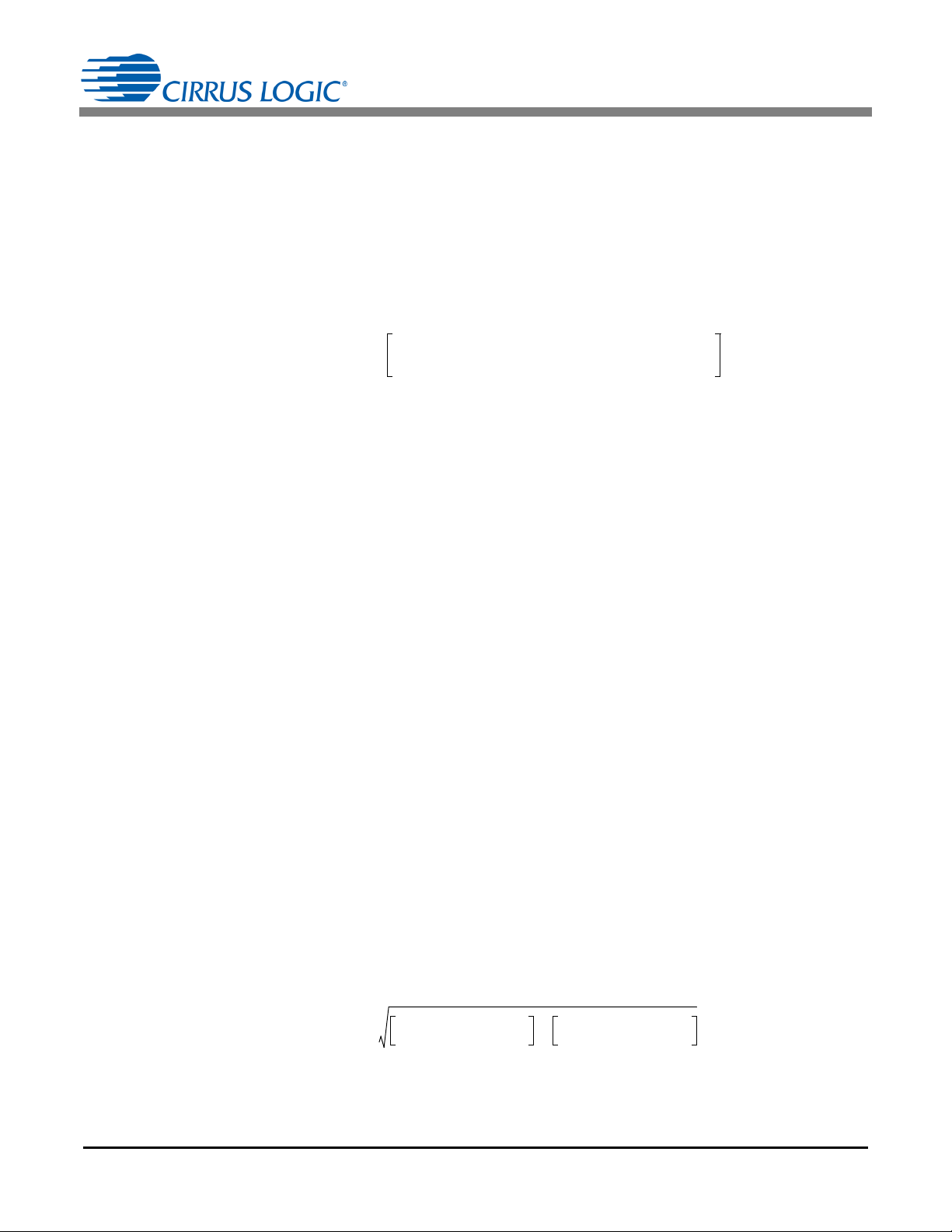

f. Calculate the Flyback Primary-side Inductance

Calculate the flyback transformer primary-side inductance L

g. Calculate Peak Current on the Flyback Primary-side

Calculate peak current I

Calculate peak current I

PK1(FB)

PK2(FB)

during Mode 1 using Equation 25:

during Mode 2 using Equation 26:

using Equation 24:

P

Calculate the average current I

Calculate the average current I

MODE1(avg)

MODE2(avg)

during Mode 1 using Equation 27:

during Mode 2 using Equation 28:

Equations 27 and 28 inherently assume that the IC generates the exact value for the FET ‘OFF’ time and the

peak currents. In practice, this is not always true due to the presence of parasitics in the system that cause

differences between the theoretical and measured value of peak current I

and time T2. Step 5 Optimize

PK(FB)

Output Current Regulation on page 24 describes in detail the way the CS1630 can compensate for these

differences.

h. Determine the RMS Current in the Winding

The CS1630 has a minimum required period T1 calculated in Equations 20 and 21 that is dependent on the

leading-edge blanking time T

. Blanking time T

LEB

is programmable from 150ns to 800ns and is used to

LEB

effectively disable the peak current comparator from turning off the gate drive too early due to spurious

switching noise. In applied systems, a good rule of thumb is to target a minimum duty cycle of 10% or greater.

The RMS current in the primary winding I

PRI(RMS)

is calculated using Equation 29:

AN368REV2 17

Page 18

AN368

[Eq. 30]

I

SEC RMS

N2I

PK1 FB

2

1D

MODE1

–

3

-----------------------------

N

2

I

PK2 FB

2

1D

MODE2

–

3

-----------------------------

+=

[Eq. 31]

R

Sense

1.4V

f

scale

I

PK1 FB

-------------------------------------=

[Eq. 32]

P

SenseIPRI RMS

2

R

Sense

=

Fir st Valley

Flyback FET

Voltage

V

CLAM P

V

BST

V

Reflected

Figure 5. Switching Waveform of Flyback FET Drain

[Eq. 33]

N

P

N

FBAUX

-------------------

2NV

OVP

R23

1.25V R22 R23+

------------------------------------------------------

=

The RMS current in the secondary winding I

i. Calculate R

Sense

(R21)

SEC(RMS)

is calculated using Equation 30:

A scaling factor is used to provide for a margin to account for manufacturing tolerances of external

components, such as inductance and resistance tolerance. Calculate sense resistor R

(R21) for flyback

Sense

using Equation 31:

where,

f

= Scaling factor

scale

R21 = R

Calculate the power P

Sense

in

dissipated by the sense resistor R

Sense

(R21) using Equation 32:

Sense

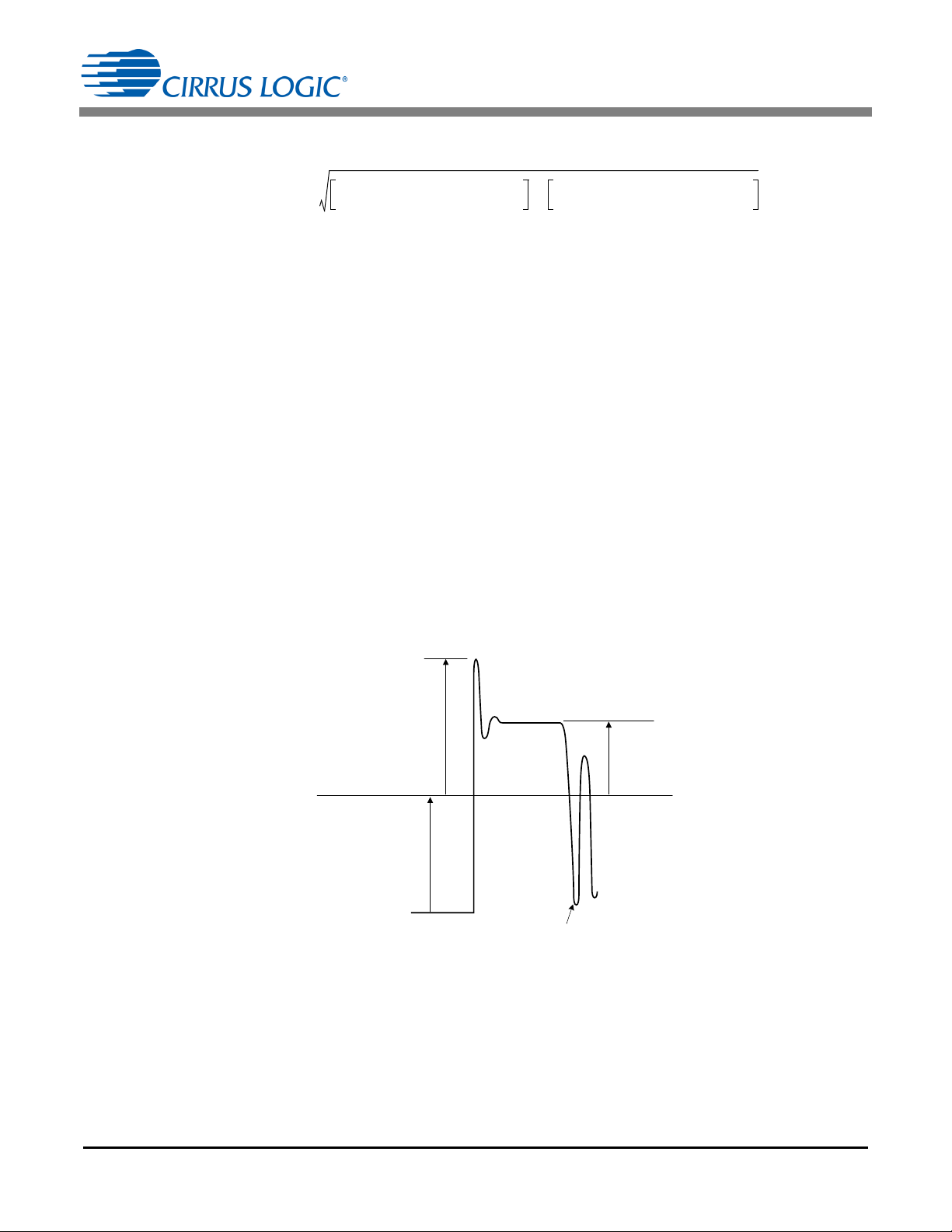

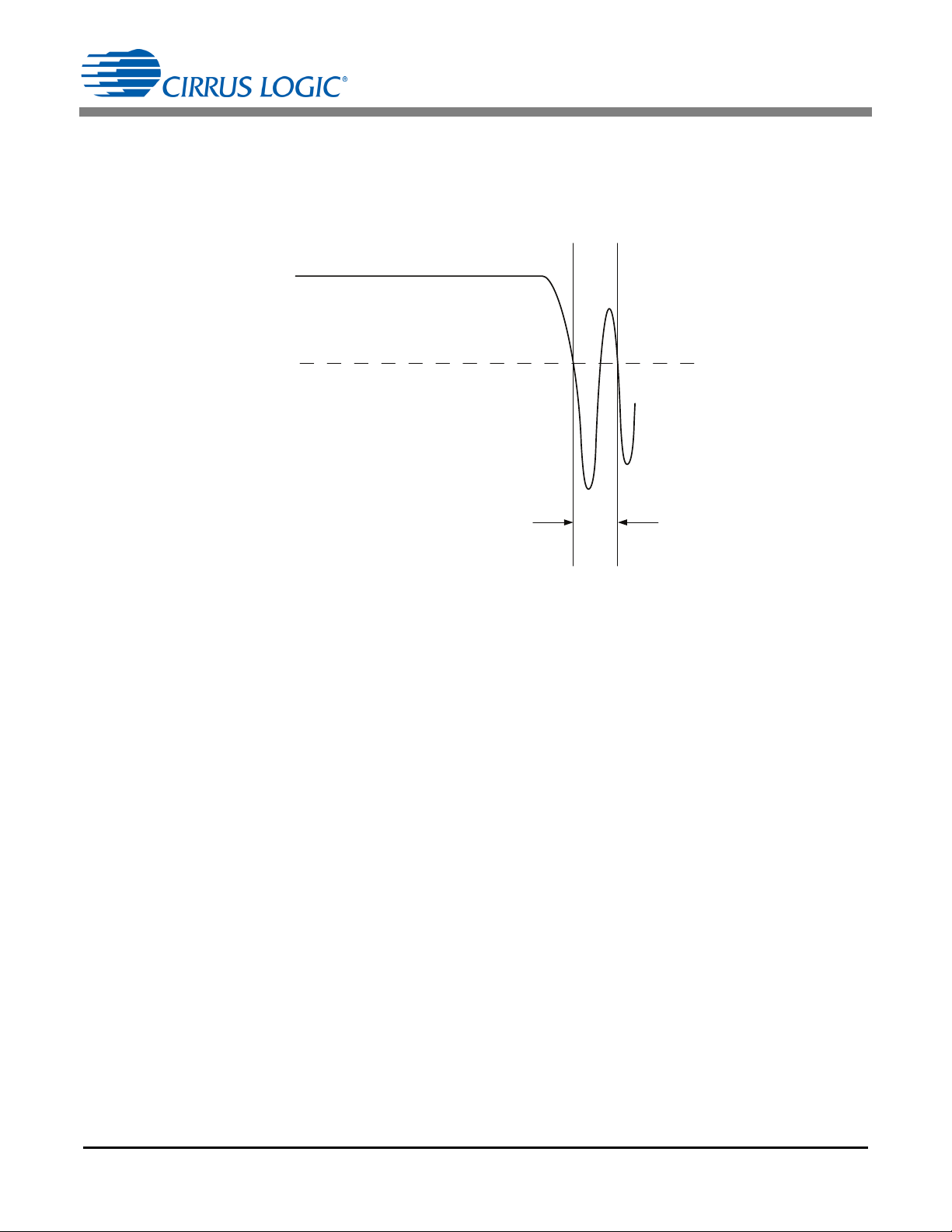

j. Calculate Flyback Zero-current Detection

The CS1630 uses zero-current detection (ZCD) to minimize switching losses. The ZCD algorithm is designed

to turn ‘ON’ the flyback FET Q5 when the resonant voltage across the FET is at a low point (see Figure 5).

Valley switching reduces the CV

2

power losses associated with the body capacitance of the FET. Pin FBAUX

is designed to monitor the resonant voltage from the auxiliary winding of the flyback transformer T1.

The auxiliary turns ratio must be designed such that the output voltage from the auxiliary winding is attenuated

by a resistor voltage divider that results in a 1.25V input to the FBAUX pin when the OVP threshold V

reached. In addition, the total current through the ZCD circuit should be limited to less than 1mA. The

transformer TX1 auxiliary winding turns ratio

is calculated using Equation 33:

OVP

is

18 AN368REV2

Page 19

AN368

[Eq. 34]

l

g

0.5 oL

P

I

PK1 FB

2

B

PK

2

Ae

--------------------------

=

[Eq. 35]N

P

L

P

I

PK1 FB

BPKAe

---------------------

=

N

S

N

P

N

-------

=

[Eq. 36]

The FBAUX pin current must be limited to less than 1mA. Resistor R22 plus resistor R23 should be chosen

such that current V

resistor of at least 22k must be used to limit the current. Bit VALLEYSW in register Config2 at Address 34

configures the quasi-resonant switching (valley switching) on the second stage. To enable valley switching,

set bit VALLEYSW to ‘1’. Bit POL_ZCD in register Config4 at Address 36 configures the polarity of the zerocurrent detection comparator output. It is recommended to set the ZCD comparator output to active-low by

setting bit POL_ZCD to ‘0’.

k. Determine Output Capacitors

The flyback output capacitors must provide a low impedance to the switching frequency. When using an

electrolytic capacitor, the choice is based on its ability to carry the ripple current so that it provides a long

service life. A capacitor that fulfills the ripple, voltage, temperature, and life requirements results in a capacitor

with a large capacitance that is often much greater than what is necessary to smooth the load current. In

flyback applications, the voltage ripple across the output electrolytic capacitor is determined mostly by the ESR

rather than the reactance.

l. Flyback Transformer Design

The following information is now available:

1. Maximum peak currents through the primary

2. Inductance

3. Turns ratio

4. RMS current through the winding

The core can be chosen using the transformer core data sheet, K

selecting the core, the gap and the number of turns can be calculated using Equations 34, 35, and 36.

The air gap length l

/(R22 + R23) is less than 1mA during the time when FET Q5 is ‘ON’ or ‘OFF’. A series

AUX

constant, or the area product. After

g

is calculated using Equation 34:

g

where,

= Permittivity of free space = 4 x 10-7 H/m

o

A

= Effective cross-sectional area of the core in mm

e

2

BPK = Peak flux density in Tesla

L

= Primary inductance in Henry

P

The primary turns N

The secondary turns N

Both N

and NP have to be an integer. Therefore, the actual flyback transformer turns ratio N may be

S

is calculated using Equation 35:

P

is calculated using Equation 36:

S

marginally different from the theoretical calculations. Hence the inductance needs to be re-calculated in order

to maintain the desired frequency spectrum. Circuit adjustments are required after the transformer has been

designed and constructed. Optimum efficiency, at full brightness, is obtained when the system is switching as

close to CRM as possible and turning on the first valley as illustrated in Figure 5. The ZCD delay can be

adjusted to hit the valley accurately, and this is demonstrated in Step 5b Tune Flyback ZCD Fixed Delays for

Optimum Valley-switching Performance on page 25.

AN368REV2 19

Page 20

AN368

CHxCUR

511 2 R

SenseICHx

NV

Sense

-------------------------------------------------------

=

[Eq. 37]

[Eq. 38]

T

LEB

LEB[3:0]= 2 50ns

m. Recalculate R

The flyback primary current is controlled by comparing the voltage across R

Sense

at pin FBSENSE to an

Sense

internal threshold of 1.4V. To guarantee the rated LED current under worst-case conditions, when the LED

string has maximum voltage, the V

R

to obtain the nominal LED current using Equations 31 and 32.

Sense

Once the current sense resistor R

is at its minimum point and R

BST

value is determined, the target output current CHxCUR for the channel

Sense

is at its highest tolerance. Adjust

Sense

can be calculated using Equation 37:

where,

V

= Voltage across sense resistor

Sense

I

= Current thought LED string

CHx

The target output current CHxCUR corresponds to a 9-bit OTP value and is programmed by bit CH1CURMSB

in register Config8 at Address 40 plus bits CH1CUR[7:0] at Address 41 for channel 1 and bit CH2CURMSB in

register Config10 at Address 42 plus bits CH2CUR[7:0] at Address 43 for channel 2.

Step 4) Tune Second-stage Performance and Limiting Parameters

The CS1630 LED controller provides a number of configurable parameters for controlling features of the

second-stage control. These features include leading- and falling-edge blanking times, configurable

deglitching of comparator outputs, dithering, resonant period probing, and phase synchronization. The optimal

values for many of the OTP general parameters not concerned with specific output design parameters have

been determined experimentally to cover the broadest design approaches. Unless there is a reason to change

them, these parameters are best set at their default values.

a. PID Feedback Controller

The maximum coefficient for the second-stage PID integrator is configured using register PID at Address 45.

The recommended value for a flyback topology that should be programmed in the PID register is ‘00000010’.

Bits RSHIFT[3:0] in register Config8 at Address 40 set the number of right shifts performed on the secondstage PID integrator value to generate a 10-bit threshold value for the peak control comparator. For peak

rectify mode, the threshold is calculated by a right shift of the integrator value. For example, setting

RSHIFT[3:0] to 12, the 24-bit integrator is shifted right 12 times, and the remaining bits represent the threshold

value provided to the peak control comparator. The recommended value that should be programmed in

RSHIFT[3:0] is ‘1100’.

b. Leading-edge Blanking

Configurable blanking time on the I

comparator provides protection to suppress potential false

Sense

comparator values caused by spurious noise induced by the power FET switching at the rising edge of the gate

drive. The controller ignores output from the comparator from the rising edge of the gate drive to the end of the

blanking time interval. The duration of the leading-edge blanking time T

is set using the LEB[3:0] bits in

LEB

register Config18 at Address 50.

A setting of LEB[3:0] = 2 results in a leading-edge blanking time of 200ns. In addition, the leading-edge

blanking sets the minimum gate drive duration or T1 time for the design. Since the I

comparator is ignored

Sense

during the leading-edge blanking time, the gate drive remains asserted throughout the leading-edge blanking

time.

20 AN368REV2

Page 21

AN368

[Eq. 39]

T

TEB

TEB[3:0]= 2 50ns

[Eq. 40]

T1

max

GD_DUR 87+= 50 ns

[Eq. 41]

V

IPK min

1.4

IPEAK[2:0] 1+1615+CL AMP[1:0] 8– 8 +

512

---------------------------------------------------------------------------------------------------------------------------------------------------

=

c. Trailing-edge Blanking

Configurable blanking time on the zero-current detection (ZCD) comparator provides protection to suppress

false comparator values due to noise at the falling edge of the gate drive. The controller suppresses any

comparator result from the falling edge of the gate drive to the end of the configurable trailing-edge blanking

time. The duration of the trailing-edge blanking time is set through the TEB[3:0] bits in register Config18 at

Address 50.

A setting of TEB[3:0] = 5 results in a trailing-edge blanking time of 500ns. In addition, the trailing-edge blanking

sets the minimum T2 time for the design since the ZCD comparator is ignored during the trailing-edge blanking

time.

d. Maximum Gate Drive Duration

The CS1630 controller provides configurable maximum gate duration to protect against a potential overstress

condition. The gate drive to the power FET is automatically disabled if the gate drive duration exceeds the

configurable limit in the absence of a trip of the I

T1

is configurable using the GD_DUR register at Address 33.

max

A setting of 65 for register GD_DUR provides a maximum gate drive duration time of 26.35s. The GD_DUR

register can be set to a percentage over the gate drive duration expected for the maximum peak current within

the system.

e. Minimum Measurable Peak Current

To achieve optimum output regulation at low dim values, the minimum measurable peak current must be set.

Voltage V

IPK(min)

corresponds to the minimum peak current measurement across sense resistor R

FET Q4 is turned ‘ON’ and is calculated using the minimum peak current level bits IPEAK[2:0] in register

Config3 at Address 35 and the offset adjustment bits CLAMP[1:0] in register Config2 at Address 34.

comparator output. The maximum gate drive duration

Sense

Sense

when

Setting the voltage V

V

IPK(min)

to be less than 0.2V can increase sensitivity to noise leading to a jittery control. For the CS1630,

IPK(min)

to be greater than 0.7V reduces the range of output regulation. Setting the voltage

0.25V should be considered the lower limit. For the CS1631, 0.35V should be considered the lower limit.

f. T2 Time-out Configuration

The CS1630 controller provides a T2 time out limit to ensure a minimum switching frequency for each channel.

The T2 duration is measured from the falling edge of the gate drive to the time at which the secondary current

equals zero. The controller uses the ZCD comparator output to locate the end of the T2 duration. If the T2

duration exceeds the T2 time out limit, the current switching cycle is terminated, and the gate drive for the next

channel switching cycle initiates.

The T2 time out limit is configurable through the TIMEOUT[1:0] bits in register Config12 at Address 44.

TIMEOUT[1:0] T2 Time-out Limit

045ms

170.6ms

296.2ms

3 121.8ms

Table 2. T2 Time-out Limits

AN368REV2 21

Page 22

AN368

T

RES

Figure 6. Waveforms of the Resonant Frequency

[Eq. 42]

TT

Cycles

16 P RCNT[3:0]15+=

[Eq. 43]

T

RES

4

---------------

2 PRCNT[3:0] 50ns=

g. Automated Resonant Period Measurements

To ensure accuracy of the T2 duration measurements within the CS1630 controller, the resonant period T

of the power train can be automatically measured during the T3 time (secondary current equals zero) of the

switching cycle. To enable the automated resonant period measurement, set the PROBE bit within register

Config7 at Address 39 to a value of ‘1’. To measure the resonant period, the controller forces DCM operation

at selected multiples of TT and measures the duration between the first and second zero-crossing detections.

RES

The frequency of the automated resonant period measurements is configurable through the PRCNT[3:0] bits

in register Config7 at Address 39. The number of channel 1 switching cycles TT

between resonant period

Cycles

measurements is set by Equation 42.

To force a resonant period measurement every 47 switching cycles, TT

, a value of 2 is programmed into

Cycles

the PRCNT[3:0] bits.

If the automated resonant period measurement is not desired, the controller supports the option to manually

program the resonant period. In this case, the PROBE bit is disabled with a value of ‘0’, and the value of onequarter of the resonant period T

If the resonant period T

is 800ns, a value of ‘2’ is programmed into bits PRCNT[3:0].

RES

is programmed using the PRCNT[3:0] bits in Equation 43.

RES

22 AN368REV2

Page 23

AN368

0

5

10

15

20

25

30

35

0.10 0.20 0.30 0.40 0.50 0.60 0.70 0.80 0.90 1.00

Frequency (kHz)

Dim

D

C

B

A

Figure 7. Dual Pulses Switching Frequency

TT

A

0.5 TT

dim1

TT

dim2

+ TT

dim1

TT

dim2

+

2

4T

res

++

2

=

[Eq. 44]

TT

dimx

2LdimI

MODEx

N2V

MODEx

1D

MODEx

–=

[Eq. 45]

TT

B

TT

FREQ

dim

--------------------

=

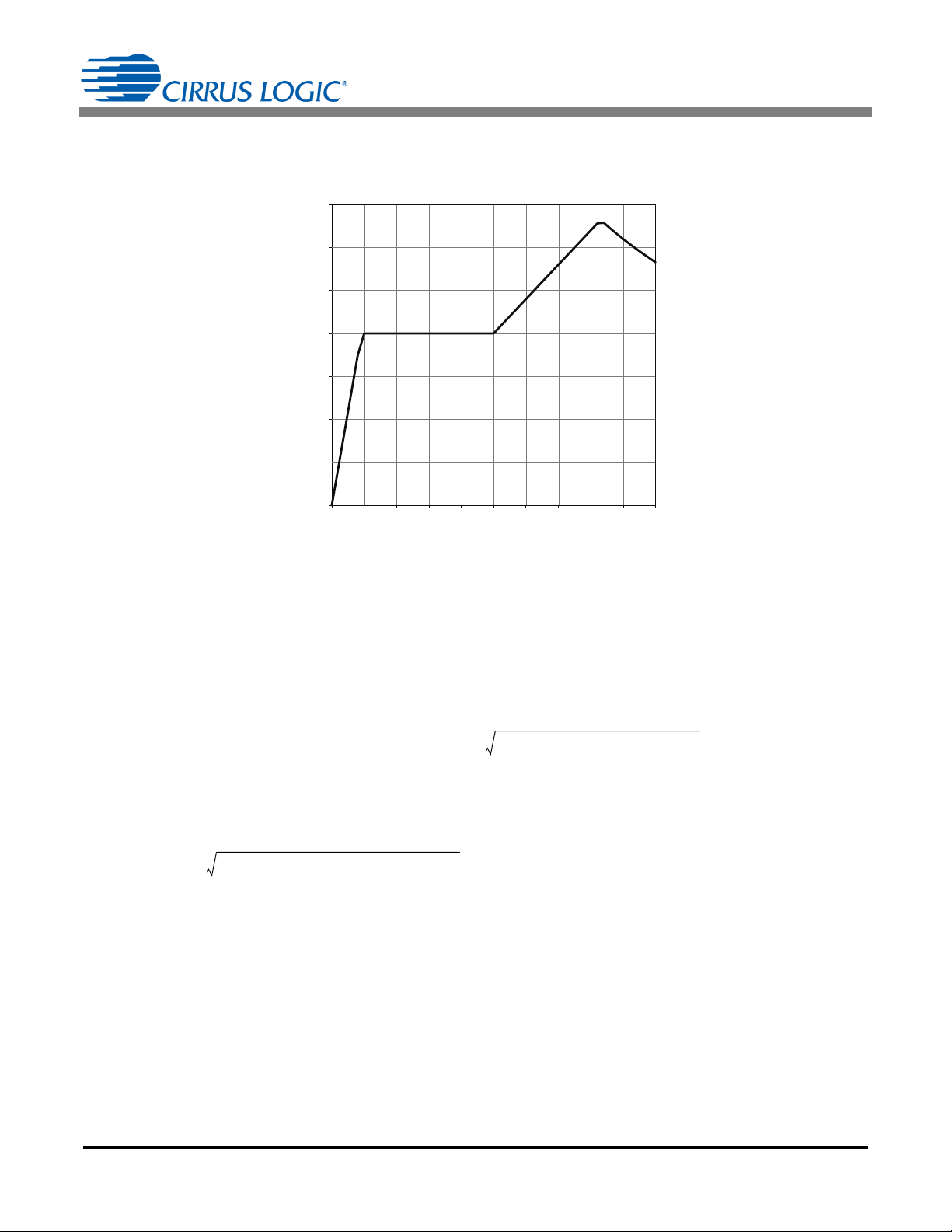

h. Switching Frequency Across Dim Range

From the equations below and setting the OTP registers as follows, the switching frequency across the dim

range can be calculated. A sample plot of the switching frequency across dim values is shown in Figure 7.

The frequencies in regions A, B, C, and D are governed by Equations 44, 45, 46 and 47, respectively.

Transitions between connecting regions are the result of simple inequalities. The following four equations do

not include the effect of a color system. Equations 44 through 47 must be adjusted after the color system has

been designed.

Frequency in Region A

In Region A, the system operates in CRM, and the period TT

is calculated using Equation 44:

A

where,

> TTB at the given dim level

TT

A

dim = The 12-bit dim level provided by the boost stage

Frequency in Region B

In Region B, the system operates in DCM, but the peak current remains the same. Period TT

using Equation 45:

where,

TT

< 50s

B

TT

> TT

B

A

is calculated

B

AN368REV2 23

Page 24

AN368

[Eq. 46]

TT

C

50s=

[Eq. 47]

TT

D

TT

DCM_2IPK min

2

L

2dimI

MODExVMODEx

-----------------------------------------------------------------

==

[Eq. 48]

I

CH1

I

CH1 fb

dim

4095

---------------------------------

=

I

CH2

I

CH2 fb

dim

4095

---------------------------------

=

[Eq. 49]

Frequency in Region C

In Region C, the switching frequency is kept constant, and the peak current I

TT

is calculated using Equation 46:

C

Frequency in Region D

Once the peak current I

reaches its minimum value, the switching frequency continues to reduce until

PK(FB)

the minimum peak current limit is reached, or the minimum switching frequency set by the maximum switching

period register TTMAX at Address 38. The period TT

is calculated using Equation 47:

D

where,

I

PKx(FB)

= I

PK(min)

TTD > TTC (50s)

TT

< TTMAX

D

starts to reduce. Period

PK(FB)

If the operating frequency is below TTMAX, the system stops regulating because the controller is out of range

to control the current I

PKx(FB)

or the frequency.

Step 5) Optimize Output Current Regulation

The CS1630 second-stage control loop achieves correct closed-loop output current regulation based on

measured values of time T1, current I

, and time T2. In practical systems, accurate measurements are

PK(FB)

limited due to circuit parasitics. Examples of circuit parasitics are leakage inductance, inter-winding

capacitance, and diode recoveries. The controller has the ability to compensate for these measurement errors

so that the control loop can maintain a tight current regulation across the corners. The following steps describe

the process of tuning these compensations accurately to minimize conversion error.

a. Definition and Scope of Second-stage Output Current Regulation

In a system where all the CS1630 second-stage compensation features have been tuned correctly and the

color system is disabled (for example, GAIN

and GAIN

DR

are forced to 1), the output current on the two

DTR

channels scales perfectly with the 12-bit dim level provided by the boost stage using Equations 48 and 49.

where,

dim = The 12-bit dim level provided by the boost stage

I

= Current at full brightness, when the dim is 4095 (full scale) provided that the color system is disabled

CH1(fb)

24 AN368REV2

Page 25

AN368

I

error

I

calculateImeasure

–

I

calculate

----------------------------------------------

100

=

[Eq. 50]