Cherry Semiconductor CS3845BGN8, CS3845BGDR8, CS3845BGDR14, CS3845BGD8, CS3845BGD14 Datasheet

1

Features

■

Optimized for Off-line Use

■

Temperature

Compensated Oscillator

■

50% Maximum Duty-cycle

Clamp

■ Low Start-up Current

(500µA max)

■ Pulse-by-pulse Current

Limiting

■ Undervoltage Active Pull

Down

■ Double Pulse Suppression

■ 1% Trimmed Bandgap

Reference

■ High Current Totem Pole

Output

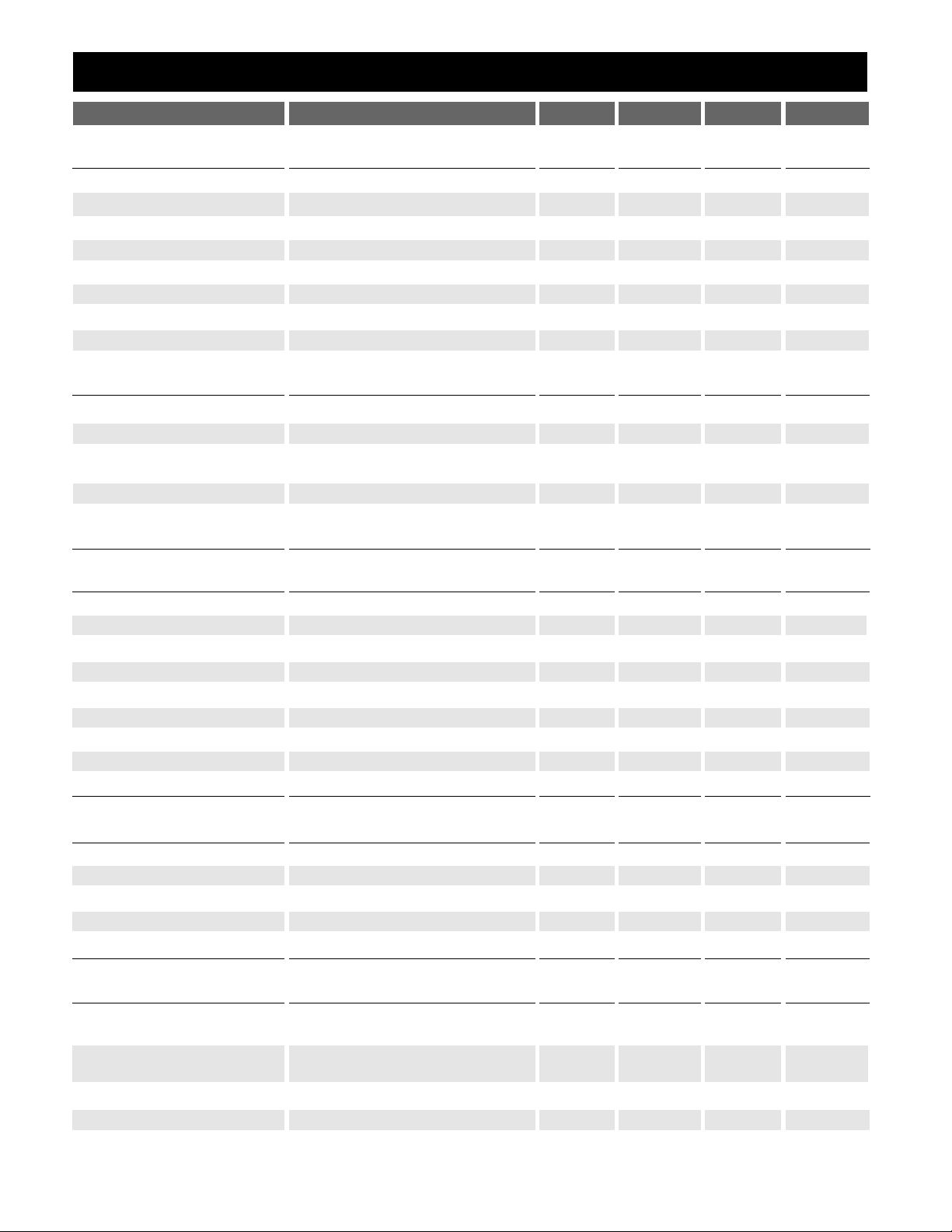

Package Options

CS3845B

Current Mode PWM

Control Circuit

with 50% Max Duty Cycle

CS3845B

Description

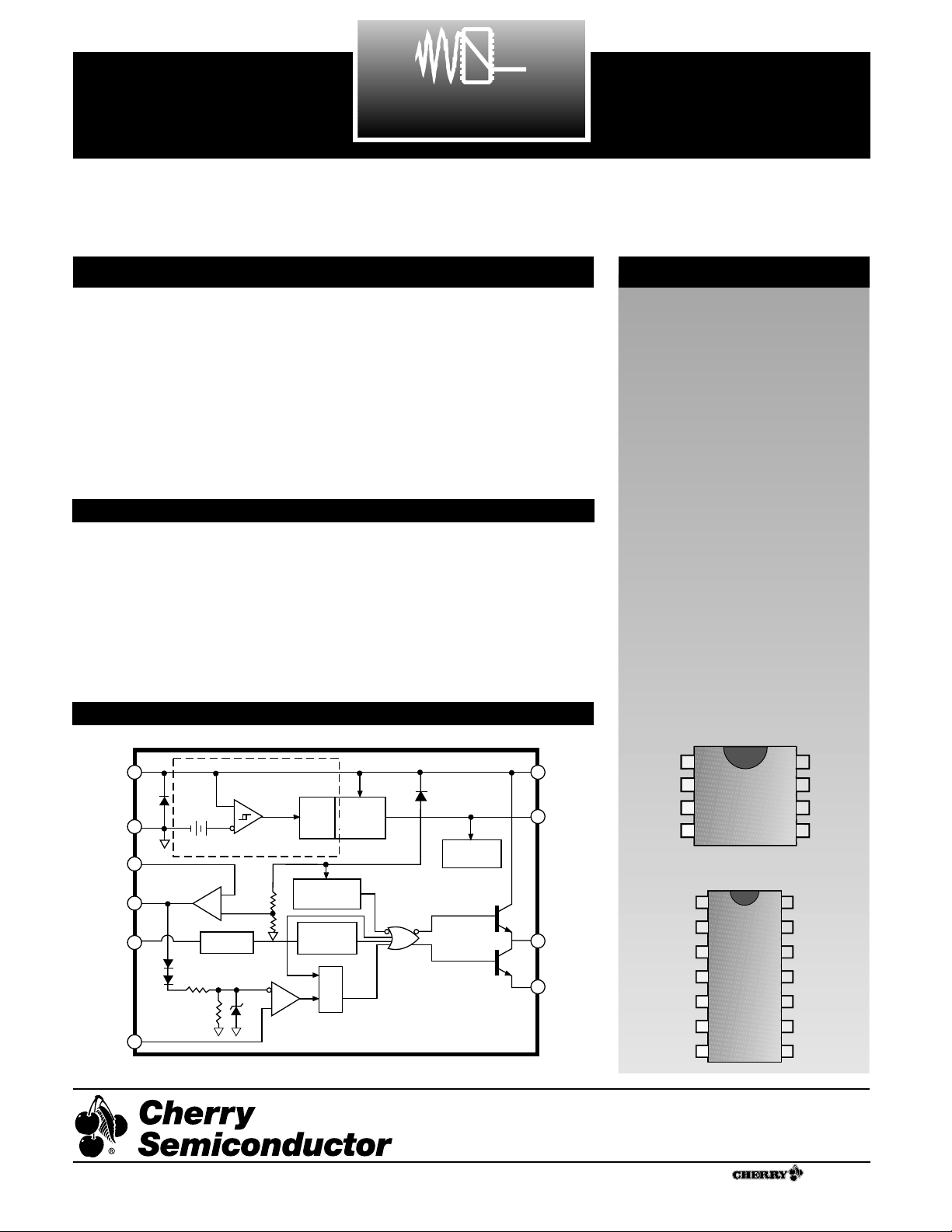

Block Diagram

Absolute Maximum Ratings

Supply Voltage (I

CC

<30mA) ..........................................................Self Limiting

Supply Voltage (Low Impedance Source)...................................................30V

Output Current ...............................................................................................±1A

Output Energy (Capacitive Load) .................................................................5µJ

Analog Inputs (VFB, V

SENSE

)...........................................................-0.3V to 5.5V

Error Amp Output Sink Current...............................................................10mA

Lead Temperature Soldering

Wave Solder (through hole styles only) ..........10 sec. max, 260°C peak

Reflow (SMD styles only)...........60 sec. max above 183°C, 230°C peak

1

COMP

2

3

4

V

FB

Sense

OSC

V

REF

V

CC

V

OUT

Gnd

8

7

6

5

8 Lead PDIP & SO

10

7

14

13

12

8

1

2

3

4

5

6

11

9

COMP

NC

V

FB

NC

Sense

NC

OSC

V

REF

NC

V

CC

VCC Pwr

V

OUT

Pwr Gnd

Gnd

14 Lead SO Narrow

The CS3845B provides all the necessary features to implement off-line

fixed frequency current-mode control

with a minimum number of external

components.

The CS3845B incorporates a precision

temperature-controlled oscillator to

minimize variations in frequency. An

internal toggle flip-flop, which blanks

the output off every other clock cycle,

ensures that the duty-cycle never

exceeds 50%. The undervoltage lockout feature ensures that V

REF

is stabilized within specification before the

output stage is enabled. The CS3845B

has been optimized for lower start up

current (500µA max).

Other features include 1% trimmed

band gap reference, pulse-by-pulse

current limiting, and a high-current

totem pole output for driving capacitive loads.

Rev. 11/19/98

Cherry Semiconductor Corporation

2000 South County Trail, East Greenwich, RI 02818

Tel: (401)885-3600 Fax: (401)885-5786

Email: info@cherry-semi.com

Web Site: www.cherry-semi.com

A Company

®

V

Undervoltage Lock-out

V

CC

CC

V

Pwr

CC

COMP

OSC

Sense

Gnd

V

34V

8.4V/7.6V

FB

Amplifier

2 R

Error

+

Oscillator

R

2.50V

1V

Reset

R

Undervoltage

R

Current

Sensing

Comparator

Set/

V

REF

Lockout

Toggle

Flip-Flop

S

R

PWM

Latch

5.0 Volt

Reference

NOR

Internal

Bias

V

REF

V

OUT

Pwr Gnd

2

Electrical Characteristics: 0≤TA≤70˚C, VCC=15V; RT=10kΩ, CT=3.3nF for sawtooth mode, unless otherwise stated

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

CS3845B

■ Reference Section

Output Voltage T

J

=25˚C, I

REF

=1mA 4.90 5.00 5.10 V

Line Regulation 12≤V

CC

≤25V 6 20 mV

Load Regulation 1≤I

REF

≤20mA 6 25 mV

Temperature Stability (Note 1) 0.2 0.4 mV/˚C

Total Output Variation Line, Load, Temp. (Note 1) 4.82 5.18 V

Output Noise Voltage 10Hz≤f≤10kHz, TJ=25˚C (Note 1) 50 µV

Long Term Stability TA=125˚C, 1000 Hrs. (Note 1) 5 25 mV

Output Short Circuit T

A

=25˚C -30 -100 -180 mA

■ Oscillator Section

Initial Accuracy Sawtooth Mode, TJ=25˚C 475257kHz

Voltage Stability 12≤V

CC

≤25V 0.2 1.0 %

Temperature Stability Sawtooth Mode T

MIN≤TA≤TMAX

(Note 1) 5 %

Amplitude V

OSC

(peak to peak)(Note 1) 17 V

Discharge TJ=25°C; (Note 1) 7.5 8.3 9.3 mA

T

MIN≤TA≤TMAX

(Note 1) 7.2 9.5 mA

■ Error Amp Section

Input Voltage V

COMP

=2.5V 2.42 2.50 2.58 V

Input Bias Current VFB=0V -0.3 -2.0 µA

AVOL 2≤V

OUT

≤4V 65 90 dB

Unity Gain Bandwidth (Note 1) 0.7 1.0 MHz

PSRR 12≤VCC≤25V 60 70 dB

Output Sink Current VFB=2.7V, V

COMP

=1.1V 2 6 mA

Output Source Current VFB=2.3V, V

COMP

=5V -0.5 -0.8 mA

V

OUT

HIGH VFB=2.3V, RL15kΩ to Gnd 5 6 V

V

OUT

LOW VFB=2.7V, RL=15kΩ to V

REF

0.7 1.1 V

■ Current Sense Section

Gain (Notes 2&3) 2.85 3.00 3.15 V/V

Maximum Input Signal V

COMP

=5V (Note 2) 0.9 1.0 1.1 V

PSRR 12≤V

CC

≤25V (Note 2) 70 dB

Input Bias Current V

Sense

=0V -2 -10 µA

Delay to Output TJ=25˚C (Note 1) 150 300 ns

■ Output Section

Output Low Level I

SINK

=20mA 0.1 0.4 V

I

SINK

=200mA 1.5 2.2 V

Output High Level I

SOURCE

=20mA 13.0 13.5 V

I

SOURCE

=200mA 12.0 13.5 V

Rise Time TJ=25˚C, CL=1nF (Note 1) 50 150 ns

Fall Time TJ=25˚C, CL=1nF (Note 1) 50 150 ns

Loading...

Loading...