Cherry Semiconductor CS2843ALN8, CS3843AGN8, CS3843AGDR8, CS3843AGDR14, CS3843AGD8 Datasheet

...

1

Features

■

Optimized for Off-line

Control

■

Internally Trimmed

Temperature

Compensated Oscillator

■

Maximum Duty-cycle

Clamp

■ V

REF

stabilized before

Output Stage is Enabled

■ Low Start-up Current

■ Pulse-by-pulse Current

Limiting

■ Improved Undervoltage

Lockout

■ Double Pulse Suppression

■ 1% Trimmed Bandgap

Reference

■ High Current Totem Pole

Output

Package Options

CS2842A/3843A SERIES

Off-Line Current Mode PWM

Control

Circuit with Undervoltage Lockout

CS2842A/CS3842A

CS2843A/CS3843A

Description

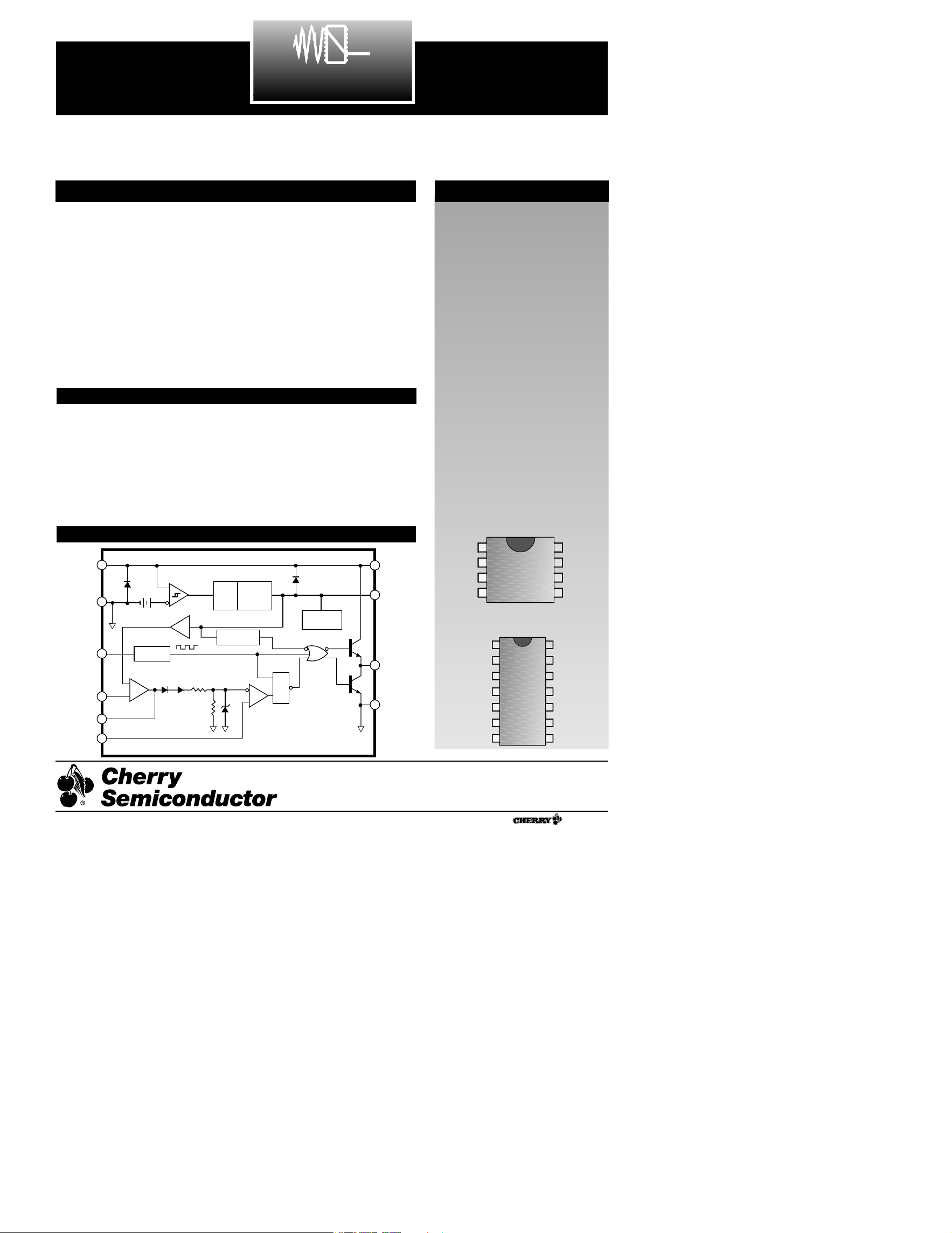

Block Diagram

Absolute Maximum Ratings

Supply Voltage (ICC<30mA).........................................................................Self Limiting

Supply Voltage (Low Impedance Source) .................................................................30V

Output Current..............................................................................................................±1A

Output Energy (Capacitive Load)................................................................................5µJ

Analog Inputs (V

FB

, Sense)...........................................................................-0.3V to 5.5V

Error Amp Output Sink Current .............................................................................10mA

Lead Temperature Soldering

Wave Solder (through hole styles only) ..........10 sec. max, 260°C peak

Reflow (SMD styles only)...........60 sec. max above 183°C, 230°C peak

1

COMP

2

3

4

V

FB

Sense

OSC

V

REF

V

CC

V

OUT

Gnd

8

7

6

5

8 Lead PDIP & SO Narrow

10

7

14

13

12

8

1

2

3

4

5

6

11

9

COMP

NC

V

FB

NC

Sense

NC

OSC

V

REF

NC

V

CC

VCC Pwr

V

OUT

Pwr Gnd

Gnd

14 Lead SO Narrow

The CS284XA, CS384XA provides all

the necessary features to implement

off-line fixed frequency current-mode

control with a minimum number of

external components.

The CS384XA family incorporates a

new precision temperature-controlled

oscillator with an internally trimmed

discharge current to minimize variations in frequency. A precision dutycycle clamp eliminates the need for an

external oscillator when a 50% dutycycle is used. Duty-cycles greater than

50% are also possible. On board logic

ensures that V

REF

is stabilized before

the output stage is enabled. Ion

implant resistors provide tighter control of undervoltage lockout.

Other features include low start-up

current, pulse-by-pulse current limiting, and a high-current totem pole output for driving capacitive loads, such

as the gate of power MOSFET. The output is LOW in the off state, consistent

with N-channel devices.

The CS384XA series of current-mode

control ICs are available in 8 and14

lead packages for surface mount (SO)

applications as well as 8 lead PDIP

packages.

A Company

®

Rev. 10/23/98

Cherry Semiconductor Corporation

2000 South County Trail, East Greenwich, RI 02818

Tel: (401)885-3600 Fax: (401)885-5786

Email: info@cherry-semi.com

Web Site: www.cherry-semi.com

V

CC

34V

Gnd

OSC

V

FB

COMP

Sense

(8.4V/7.6V)

+

–

Amplifier

16V/10V

2.50V

Oscillator

Error

Undervoltage

Lock-out Circuit

Set/

Reset

Reference

Output

Enable

2 R

V

C

R

1 V

( ) Indicates CS-2843A/3843A

5V

Current

Sensing

Comparator

Internal

Bias

NOR

S

PWM

R

Latch

VCC Pwr

V

REF

V

OUT

Pwr Gnd

2

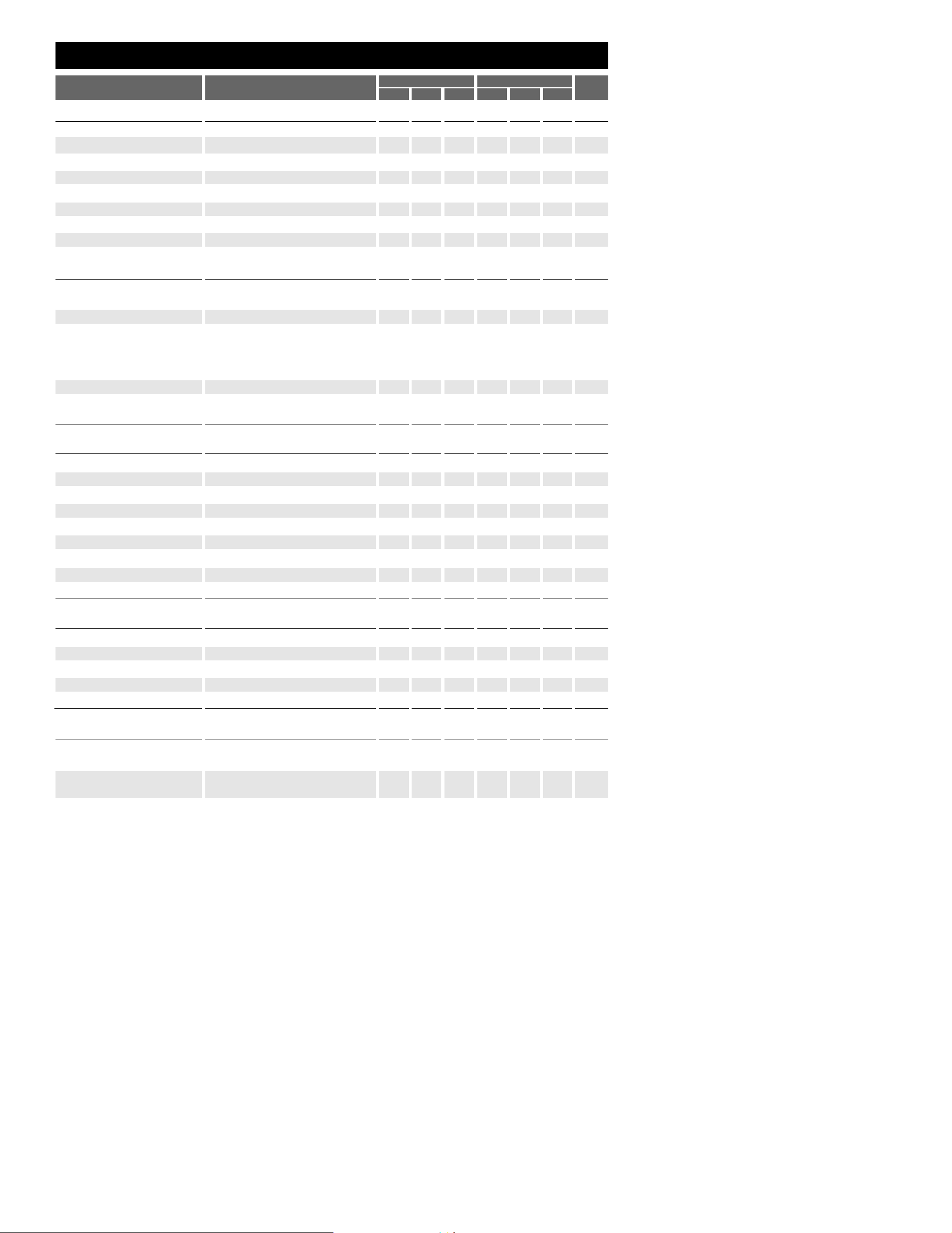

Electrical Characteristics: -25° ≤ T

A

≤ 85˚C for CS2842A/2843A, 0° ≤ TA≤ 70˚C for CS3842A/3843A. VCC= 15V (Note 1);

R

T

= 680Ω, CT= .022µF for triangular mode, RT= 10kΩ, CT= 3.3nF for sawtooth mode (see Figure 3), unless otherwise stated.

CS2842A/CS2843A CS3842A/CS3843A

PARAMETER TEST CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

CS2842A/3843A SERIES

■ Reference Section

Output Voltage T

J

= 25˚C, I

OUT

= 1mA 4.95 5.00 5.05 4.90 5.00 5.10 V

Line Regulation 12 ≤ V

IN

≤ 25V 6 20 6 20 mV

Load Regulation 1 ≤ I

OUT

≤ 20mA 6 25 6 25 mV

Temperature Stability (Note 2) 0.2 0.4 0.2 0.4 mV/˚C

Total Output Variation Line, Load, Temp. (Note 2) 4.90 5.10 4.82 5.18 V

Output Noise Voltage 10Hz ≤ f ≤ 10kHz, TJ= 25˚C (Note 2) 50 50 µV

Long Term Stability TA= 125˚C, 1kHrs. (Note 2) 5 25 5 25 mV

Output Short Circuit TA= 25˚C -30 -100 -180 -30 -100 -180 mA

■ Oscillator Section

Initial Accuracy Sawtooth Mode (see Fig. 3), T

J

= 25˚C475257475257kHz

Triangular Mode (see Fig. 3), T

J

= 25˚C475257445260kHz

Voltage Stability 12 ≤ VCC≤ 25V 0.2 1.0 0.2 1.0 %

Temp. Stability Sawtooth Mode T

MIN

≤ TA≤ T

MAX

(Note 2) 5 5 %

Triangular Mode T

MIN

≤ TA≤ T

MAX

(Note 2) 8 8 %

Amplitude OSC peak to peak 1.7 1.7 V

Discharge Current T

J

= 25˚C 7.5 8.3 9.3 7.5 8.3 9.3 mA

T

MIN

≤ TA≤ T

MAX

7.2 9.5 7.2 9.5 mA

■ Error Amp Section

Input Voltage V

COMP

= 2.5V 2.45 2.50 2.55 2.42 2.50 2.58 V

Input Bias Current VFB= 0 -0.3 -1.0 -0.3 -2.0 µA

A

VOL

2 ≤ V

OUT

≤ 4V 65 90 65 90 dB

Unity Gain Bandwidth (Note 2) 0.7 1.0 0.7 1.0 MHz

PSRR 12 ≤ VCC≤ 25V 60 70 60 70 dB

Output Sink Current VFB= 2.7V, V

COMP

= 1.1V 2 6 2 6 mA

Output Source Current VFB= 2.3V, V

COMP

= 5V -0.5 -0.8 -0.5 -0.8 mA

V

OUT

High VFB= 2.3V, RL= 15kΩ to ground 5 6 5 6 V

V

OUT

Low VFB= 2.7V, RL= 15kΩ to V

REF

0.7 1.1 0.7 1.1 V

■ Current Sense Section

Gain (Notes 3 & 4) 2.85 3.00 3.15 2.85 3.00 3.15 V/V

Maximum Input Signal V

COMP

= 5V (Note 3) 0.9 1.0 1.1 0.9 1.0 1.1 V

PSRR 12 ≤ VCC≤ 25V (Note 3) 70 70 dB

Input Bias Current V

Sense

= 0 -2 -10 -2 -10 µA

Delay to Output TJ= 25˚C (Note 2) 150 300 150 300 ns

■ Output Section

Output Low Level I

SINK

= 20mA 0.1 0.4 0.1 0.4 V

I

SINK

= 200mA 1.5 2.2 1.5 2.2 V

Output High Level I

SOURCE

= 20mA 13.0 13.5 13.0 13.5 V

I

SOURCE

= 200mA 12.0 13.5 12.0 13.5 V

Loading...

Loading...