Central CMLDM7003, CMLDM7003G, CMLDM7003J Schematic [ru]

CMLDM7003

CMLDM7003G*

CMLDM7003J

SURFACE MOUNT SILICON

DUAL N-CHANNEL

ENHANCEMENT-MODE

MOSFETS

DESCRIPTION:

These CENTRAL SEMICONDUCTOR devices

are dual N-Channel enhancement-mode MOSFETs,

www.centralsemi.com

manufactured by the N-Channel DMOS Process,

designed for high speed pulsed amplifier and driver

applications. The CMLDM7003 utilizes the USA pinout

configuration, while the CMLDM7003J utilizes the

Japanese pinout configuration. These devices offer low

r

DS(ON)

and ESD protection up to 2kV.

MARKING CODES: CMLDM7003: C30

SOT-563 CASE

Device is Halogen Free by design

*

MAXIMUM RATINGS: (TA=25°C) SYMBOL UNITS

Drain-Source Voltage VDS 50 V

Drain-Gate Voltage V

Gate-Source Voltage VGS 12 V

Continuous Drain Current ID 280 mA

Maximum Pulsed Drain Current IDM 1.5 A

Power Dissipation (Note 1) P

Power Dissipation (Note 2) P

Power Dissipation (Note 3) P

Operating and Storage Junction Temperature TJ, T

Thermal Resistance ΘJA 357 °C/W

CMLDM7003G*: C3G

CMLDM7003J: C3J

DG

D

D

D

-65 to +150 °C

stg

50 V

350 mW

300 mW

150 mW

ELECTRICAL CHARACTERISTICS PER TRANSISTOR: (TA=25°C unless otherwise noted)

SYMBOL TEST CONDITIONS MIN TYP MAX UNITS

I

GSSF, IGSSR

I

GSSF, IGSSR VGS

I

GSSF, IGSSR

I

V

DSS

BV

DSS

V

GS(th)

VSD V

r

DS(ON)

r

DS(ON)

r

DS(ON)

gFS V

C

rss

C

V

iss

C

V

oss

Notes: (1) Ceramic or aluminum core PC Board with copper mounting pad area of 4.0mm

(2) FR-4 Epoxy PC Board with copper mounting pad area of 4.0mm

(3) FR-4 Epoxy PC Board with copper mounting pad area of 1.4mm

VGS=5.0V 100 nA

=10V 2.0 μA

VGS=12V 2.0 μA

=50V, VGS=0 50 nA

V

V

V

V

DS

=0, ID=10μA 50 V

GS

VDS=VGS, ID=250μA 0.49 1.0 V

=0, IS=115mA 1.4 V

GS

=1.8V, ID=50mA 1.6 3.0 Ω

GS

=2.5V, ID=50mA 1.3 2.5 Ω

GS

=5.0V, ID=50mA 1.1 2.0 Ω

GS

=10V, ID=200mA 200 mS

DS

VDS=25V, VGS=0, f=1.0MHz 5.0 pF

=25V, VGS=0, f=1.0MHz 50 pF

DS

=25V, VGS=0, f=1.0MHz 25 pF

DS

2

2

2

R7 (28-January 2014)

CMLDM7003

CMLDM7003G*

CMLDM7003J

SURFACE MOUNT SILICON

DUAL N-CHANNEL

ENHANCEMENT-MODE

MOSFETS

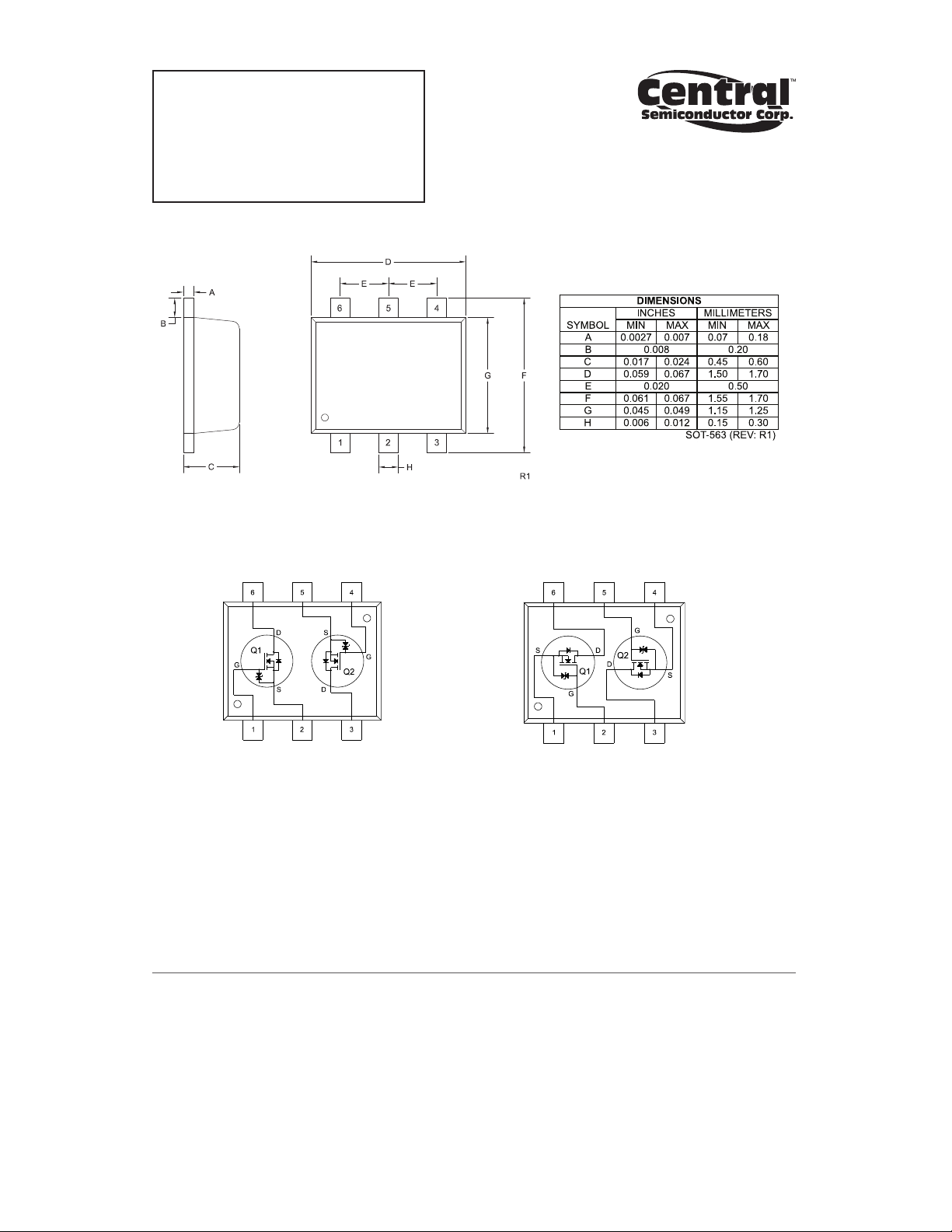

CMLDM7003 (USA Pinout)

CMLDM7003G*

SOT-563 CASE - MECHANICAL OUTLINE

PIN CONFIGURATIONS

CMLDM7003J (Japanese Pinout)

LEAD CODE:

1) Gate Q1

2) Source Q1

3) Drain Q2

4) Gate Q2

5) Source Q2

6) Drain Q1

MARKING CODES:

CMLDM7003: C30

CMLDM7003G*: C3G

Device is Halogen Free by design

*

www.centralsemi.com

LEAD CODE:

1) Source Q1

2) Gate Q1

3) Drain Q2

4) Source Q2

5) Gate Q2

6) Drain Q1

MARKING CODE: C3J

R7 (28-January 2014)

Loading...

Loading...