Page 1

5

4

3

2

1

D D

Topstar Digital technologies Co.,LTD

01. Title

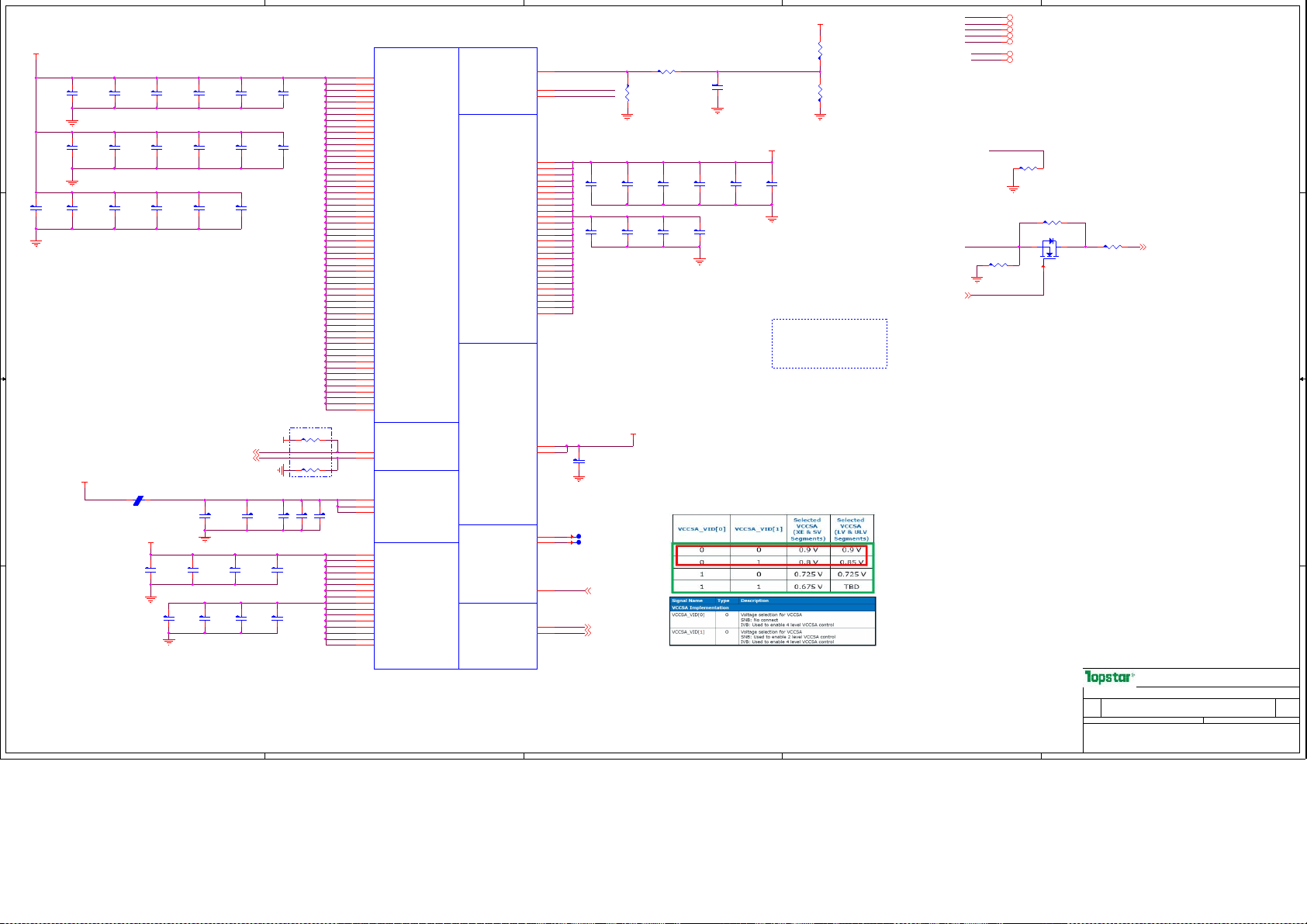

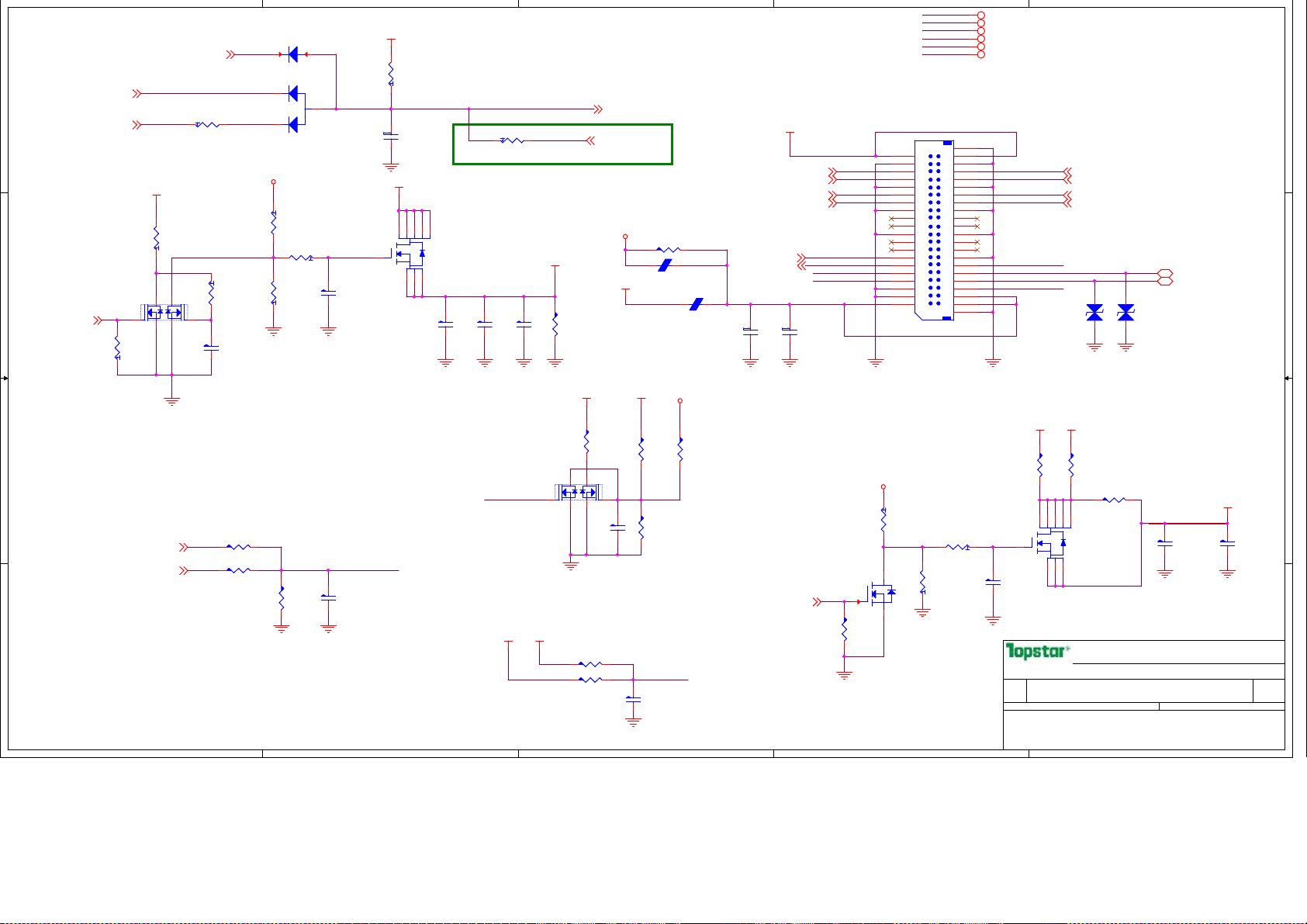

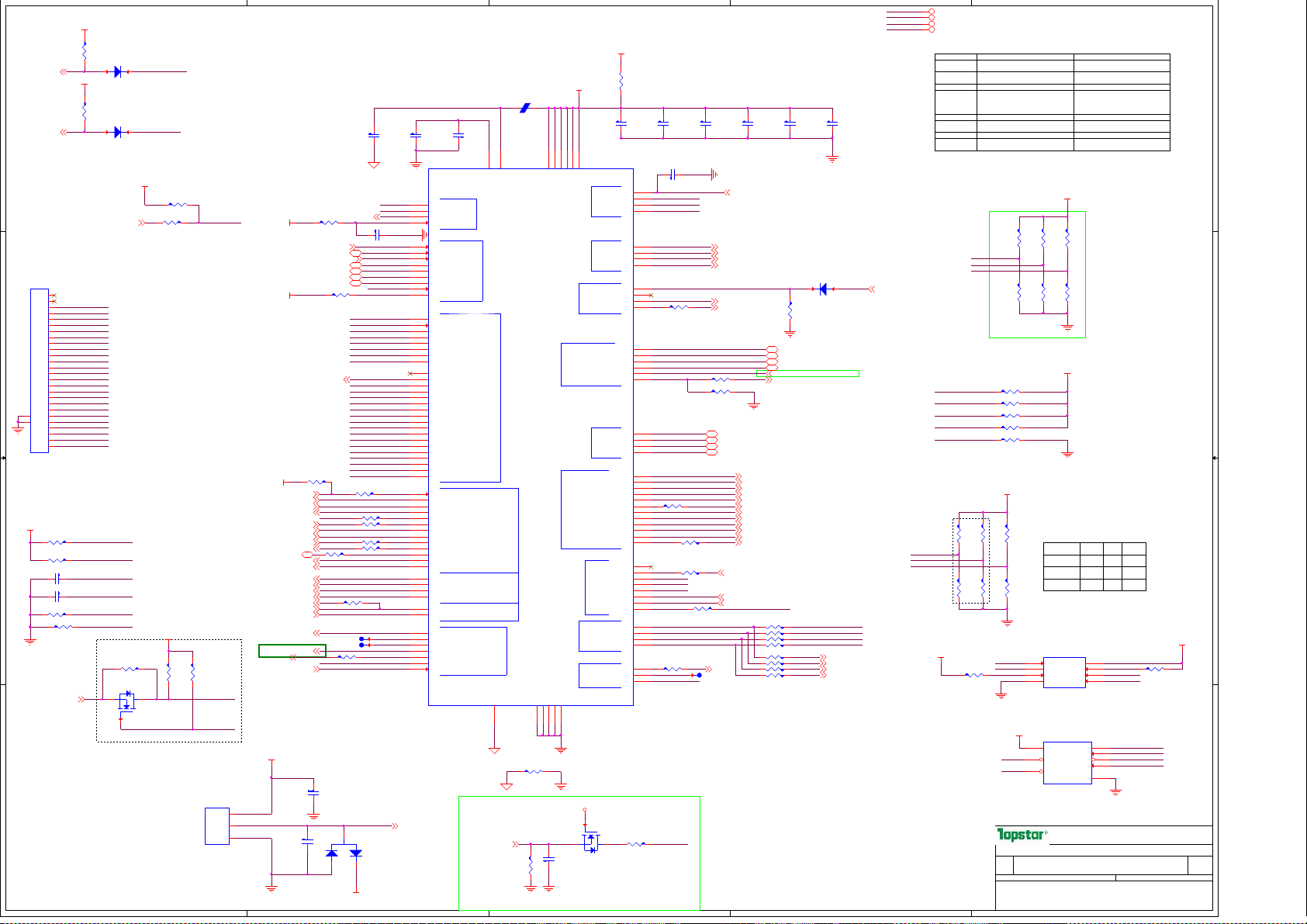

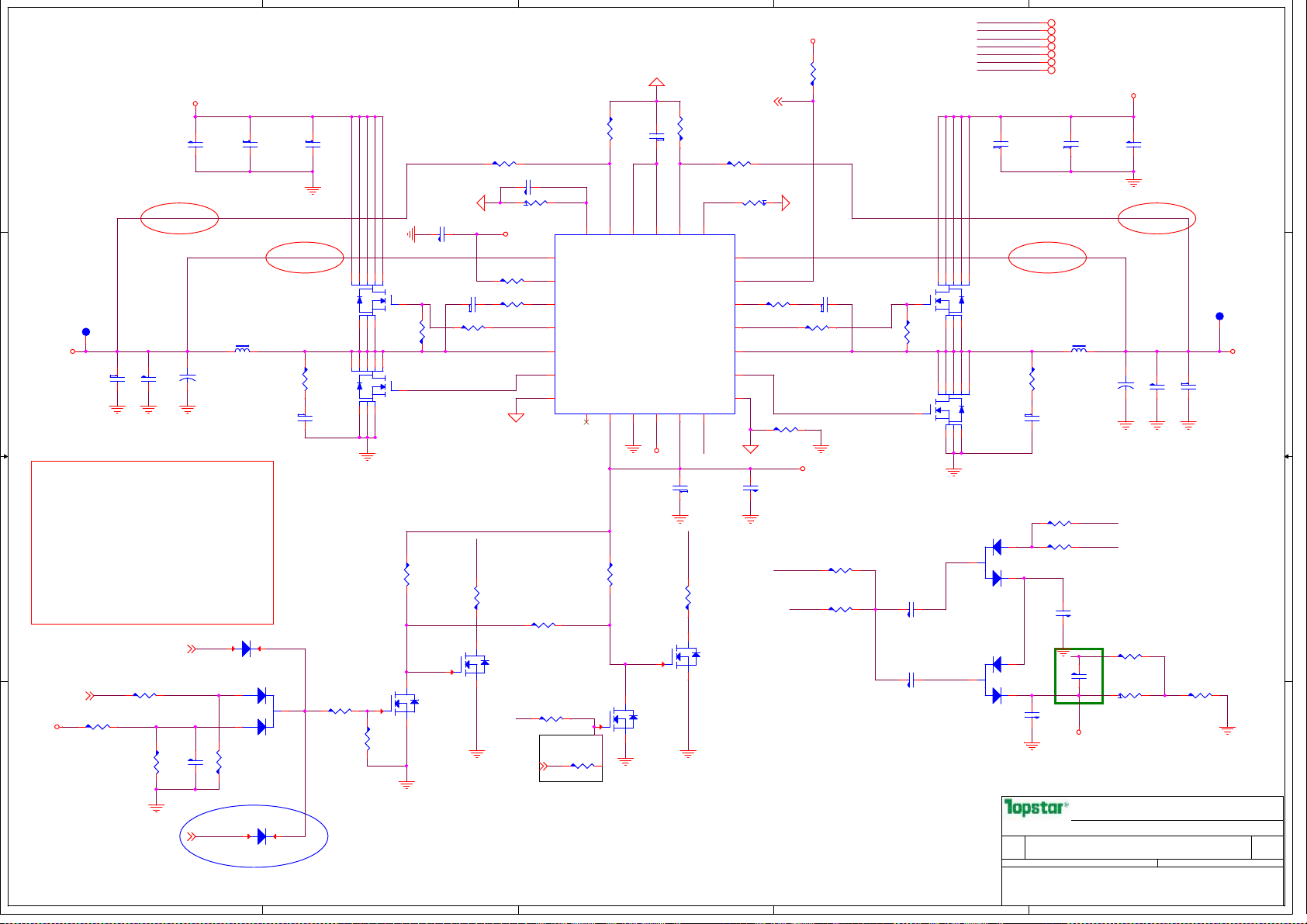

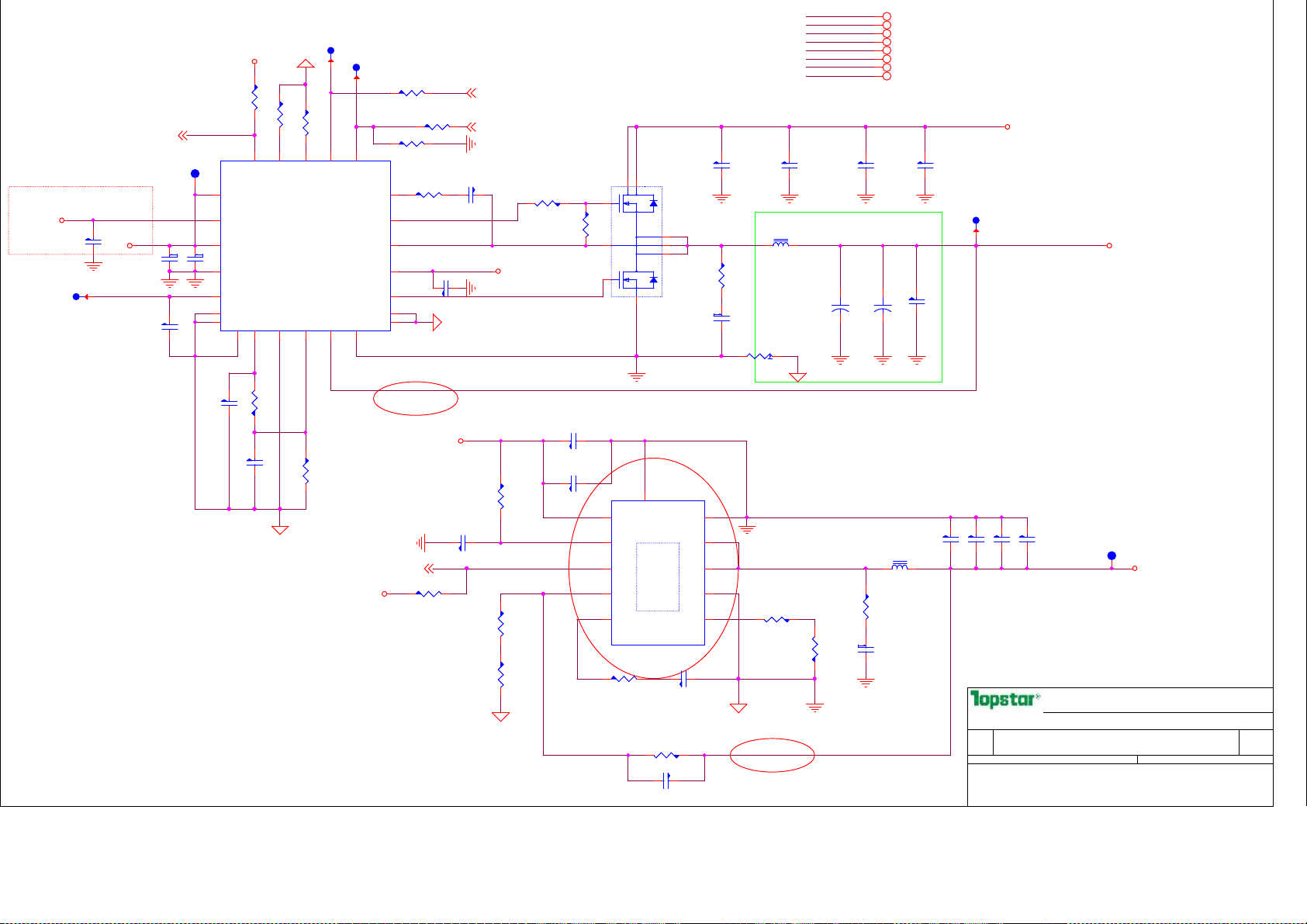

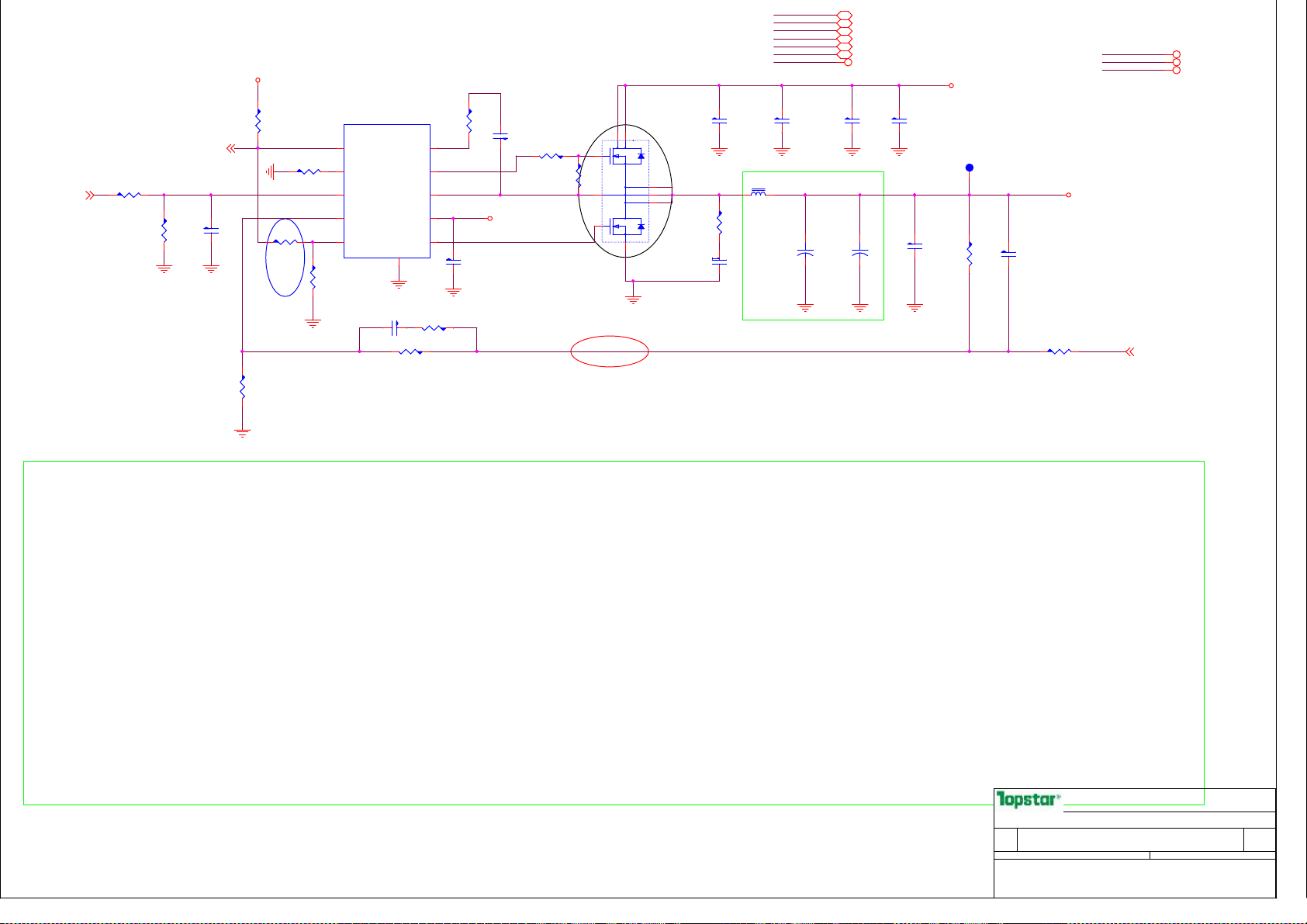

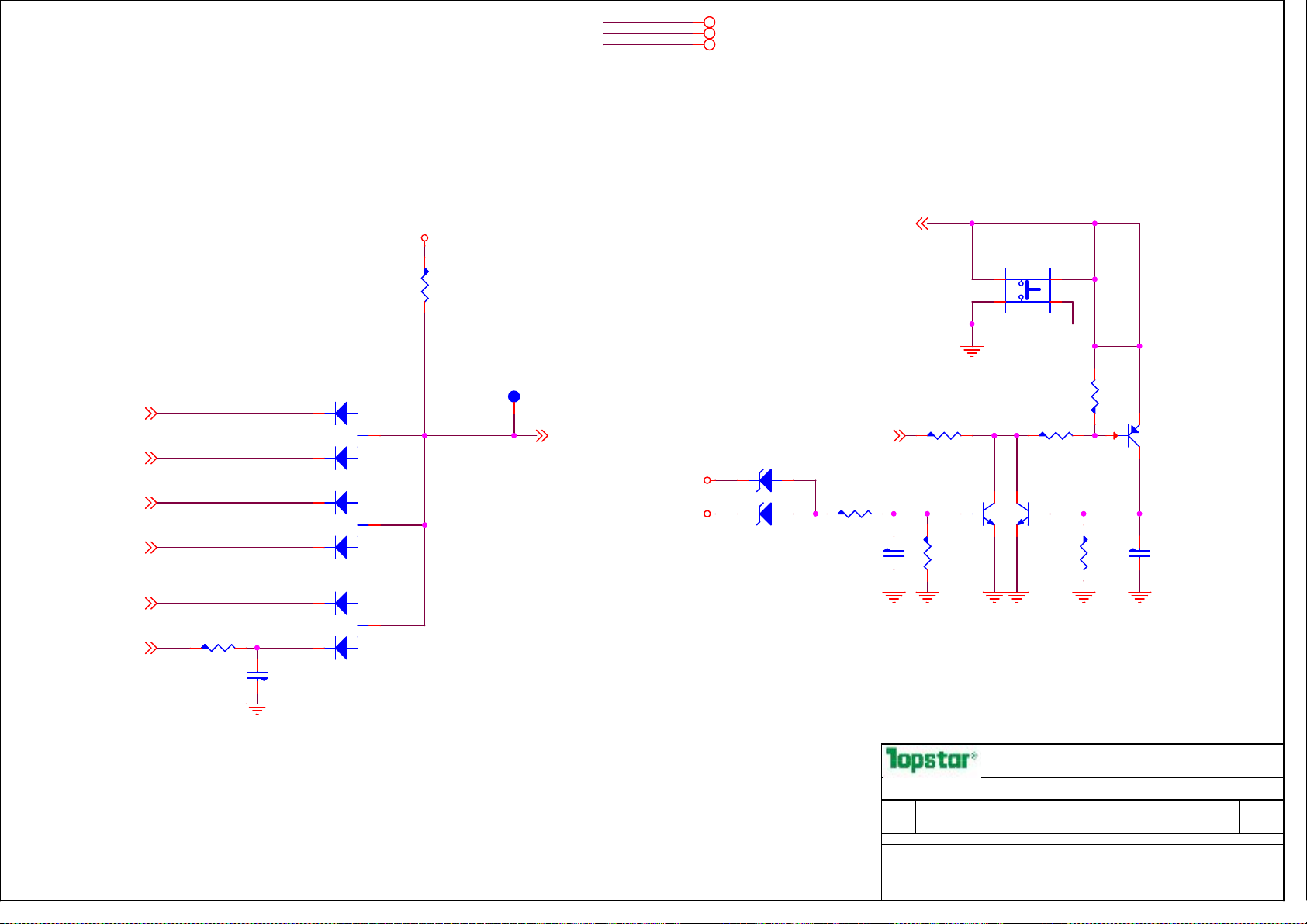

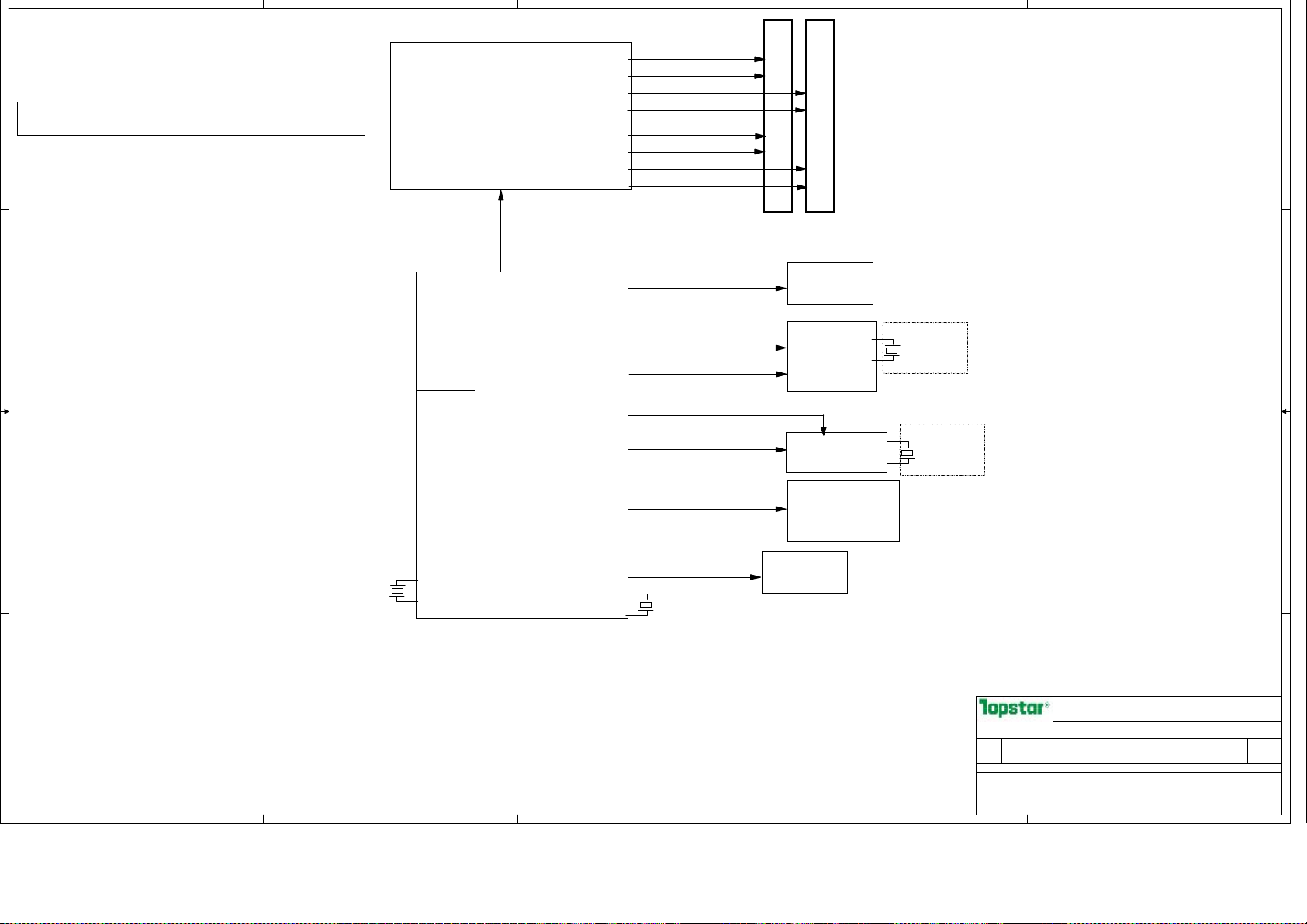

Board name: MotherBoard Schematic

Project name: F42

Version: VerC

Initial Date:

02. Sys block

03. PWR block

04. Notes

05. Modify and history

06. Ivy Bridge DMI/FDI/PCIE

07.Ivy Bridge CLK/MISC

08. Ivy Bridge DDR3

09. Ivy Bridge Vcore/VTT

10. Ivy Bridge VGFX/VDDQ

C C

11. Ivy Bridge GND

12. Ivy Bridge Reserved

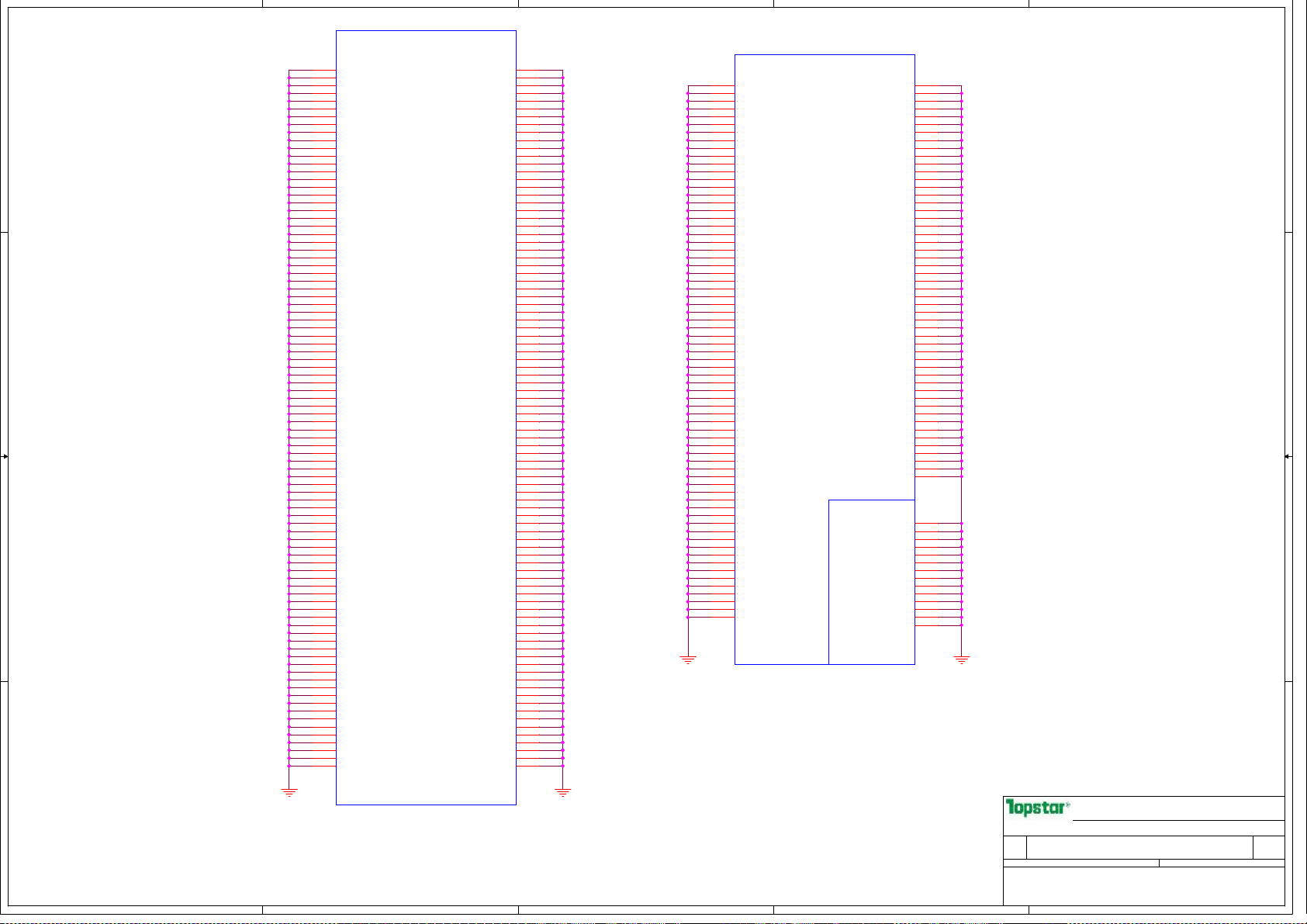

13. DDR3 CHA SODIMM0

14. DDR3 CHB SODIMM0

Topstar Confidential

Hardware drawing by: Hardware check by: EMI Check by:

15. PCH RTC/SATA/SPI/HDA/LPC

16. PCH PCIE/CLK/SMBUS

17. PCH DMI/FDI/PWRGD

18. PCH Display

19. PCH PCI/USB

20. PCH GPIO

21. PCH PWR 1/2

22. PCH PWR 2/2

23. PCH GND

24. LVDS&Inverter CONN

25. HDMI CONN

26. CRT Interface

27. SATA HDD&ODD

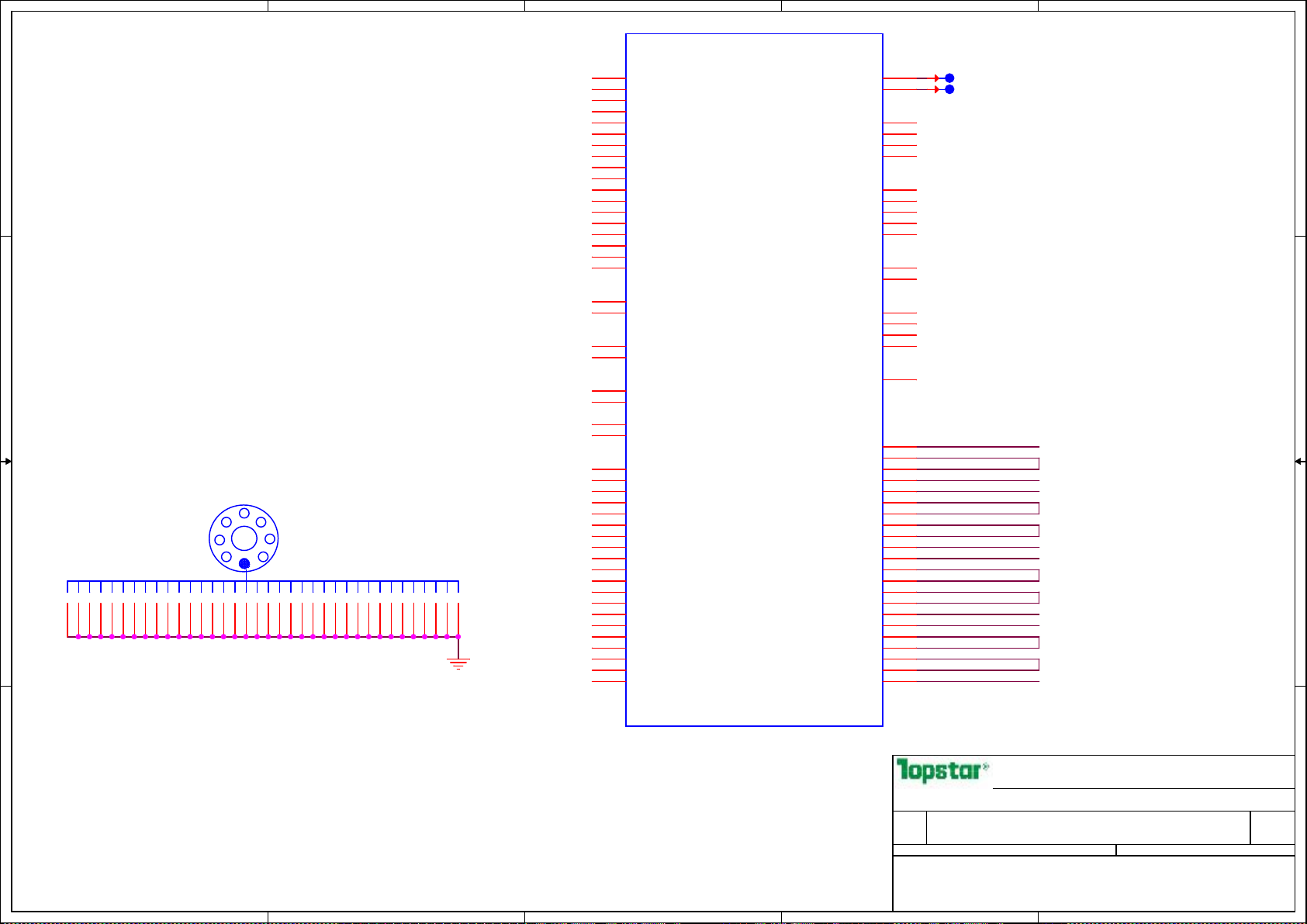

28. TP Module&BD CONN

B B

Power drawing by:

Power check by:

Manager Sign by:

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

杨华明

(Sky Yang)

杨华明

(Sky Yang)

杨华明

(Sky Yang)

Title(Cover Page)

Title(Cover Page)

Title(Cover Page)

CL42 EVT

CL42 EVT

CL42 EVT

1

A

A

1 51Sunday, April 07, 2013

1 51Sunday, April 07, 2013

1 51Sunday, April 07, 2013

A

Page 2

5

4

3

2

1

Topstar Confidential

ShenZhen Topstar Industry Co.,LTD

D D

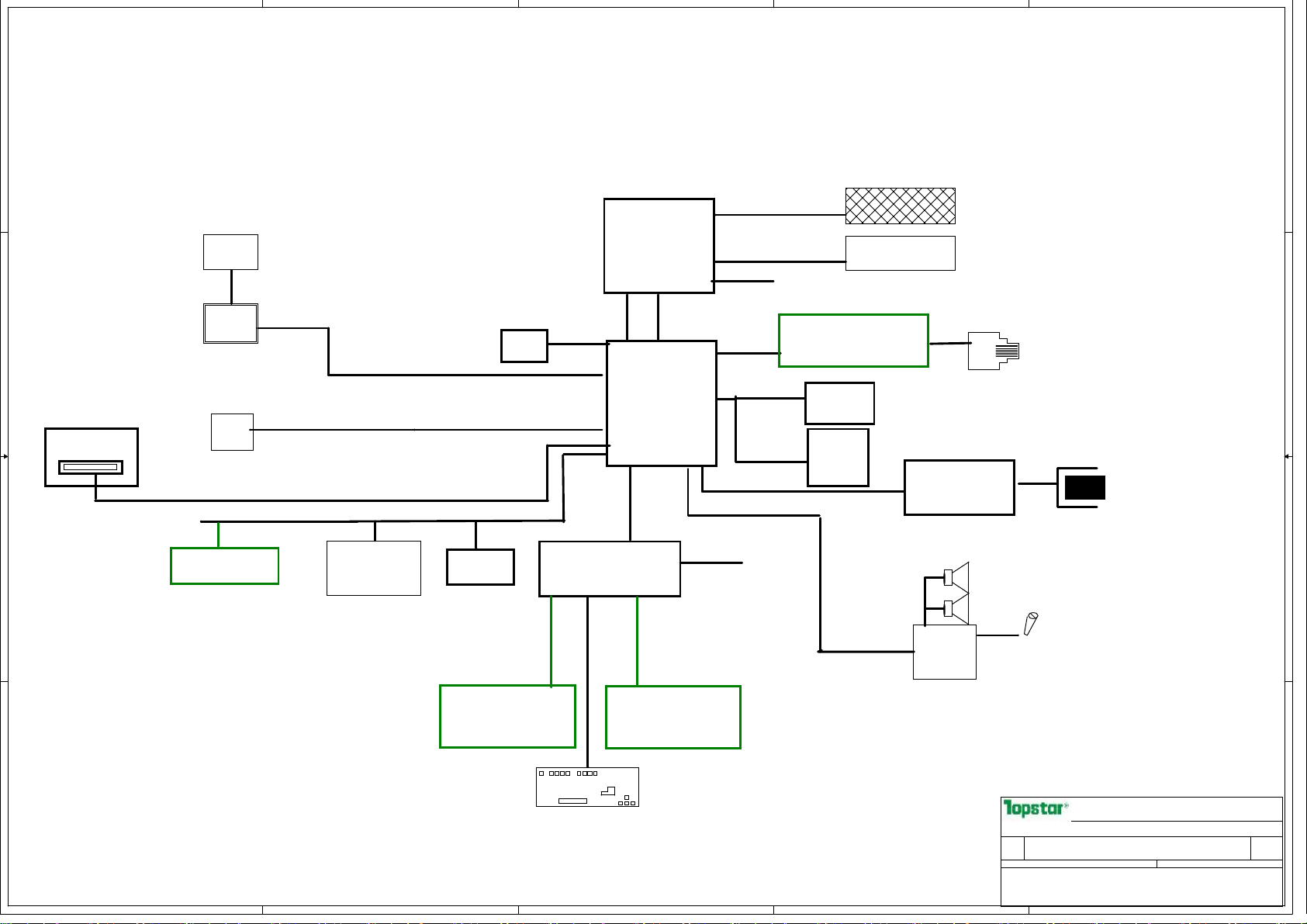

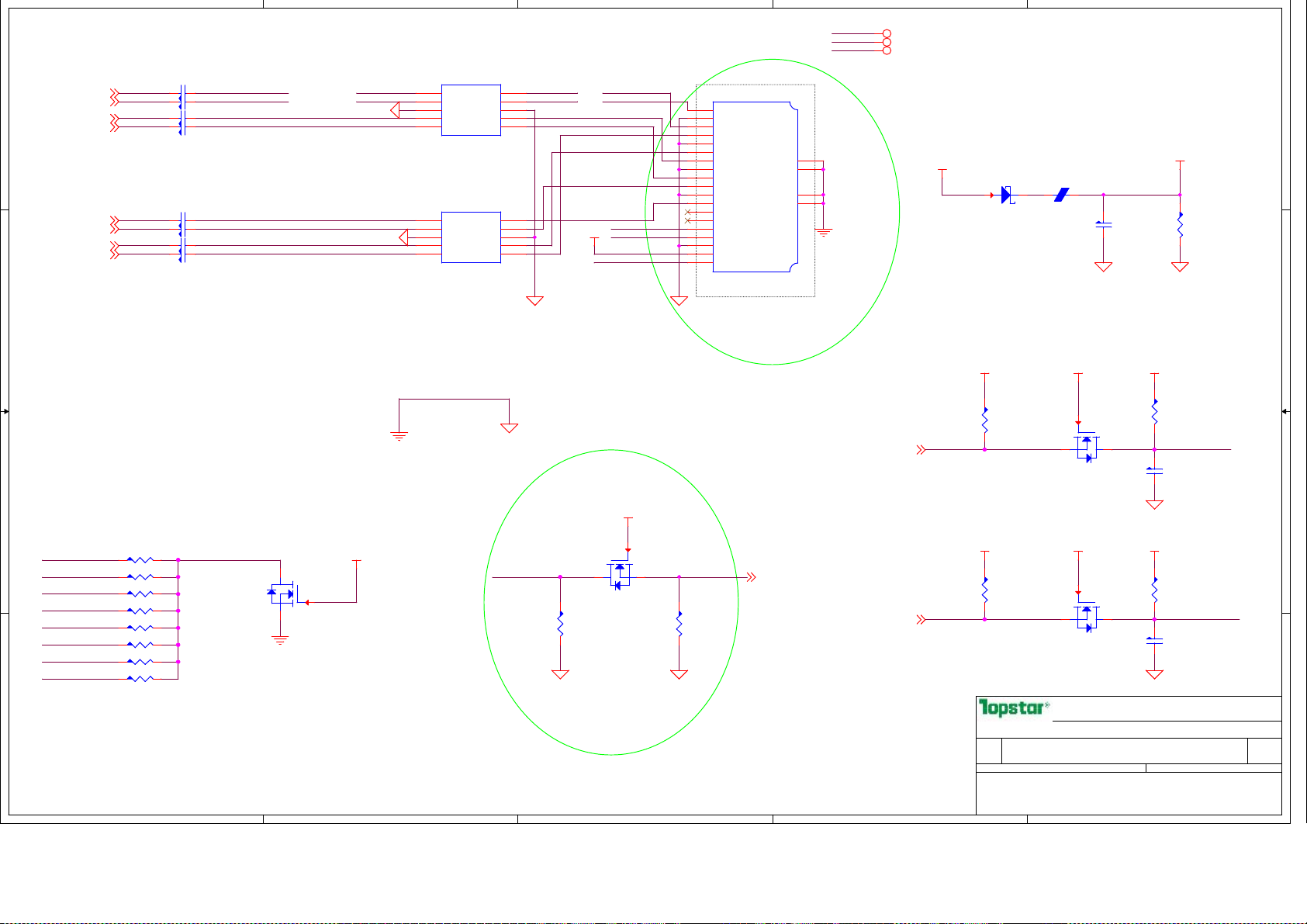

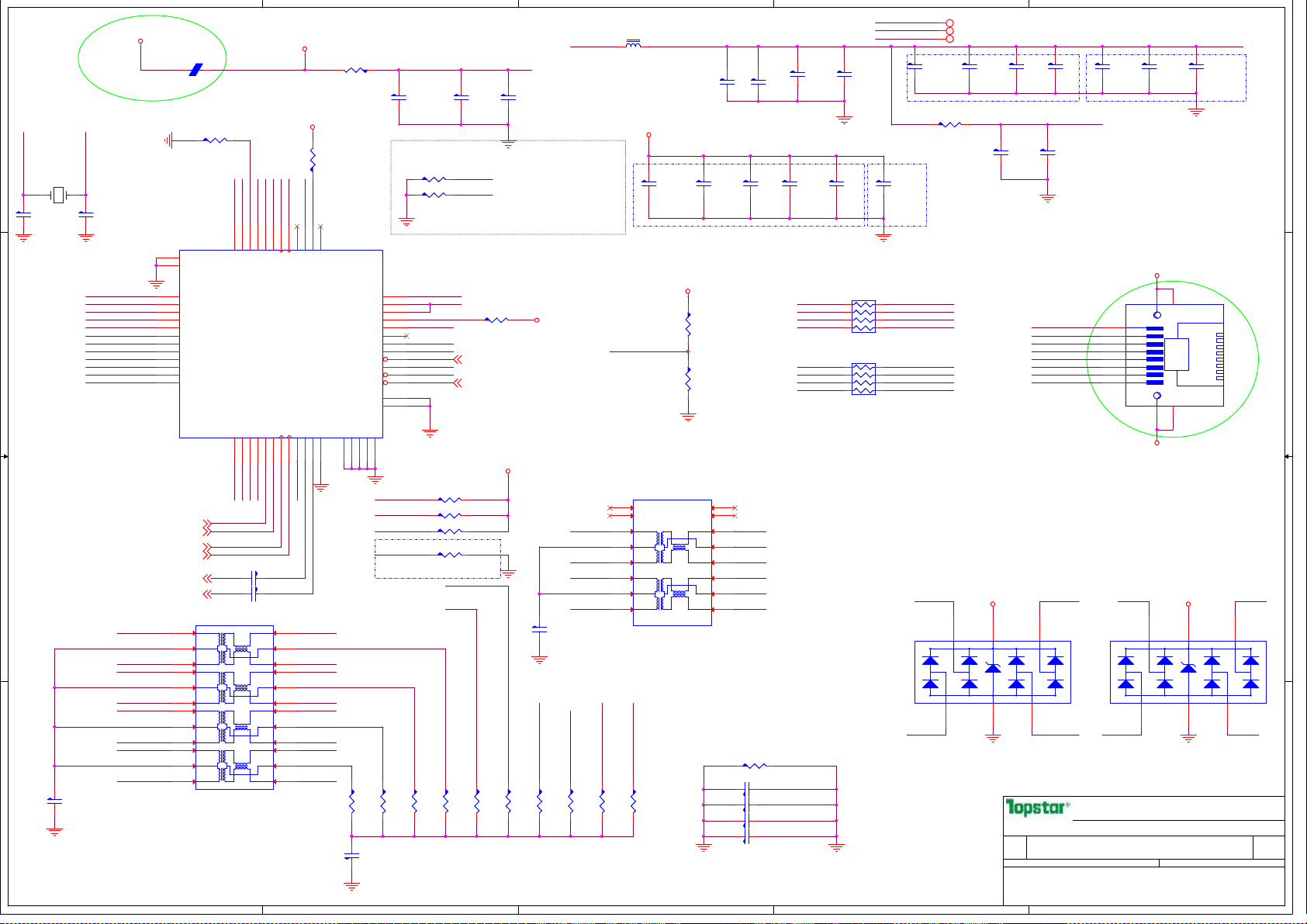

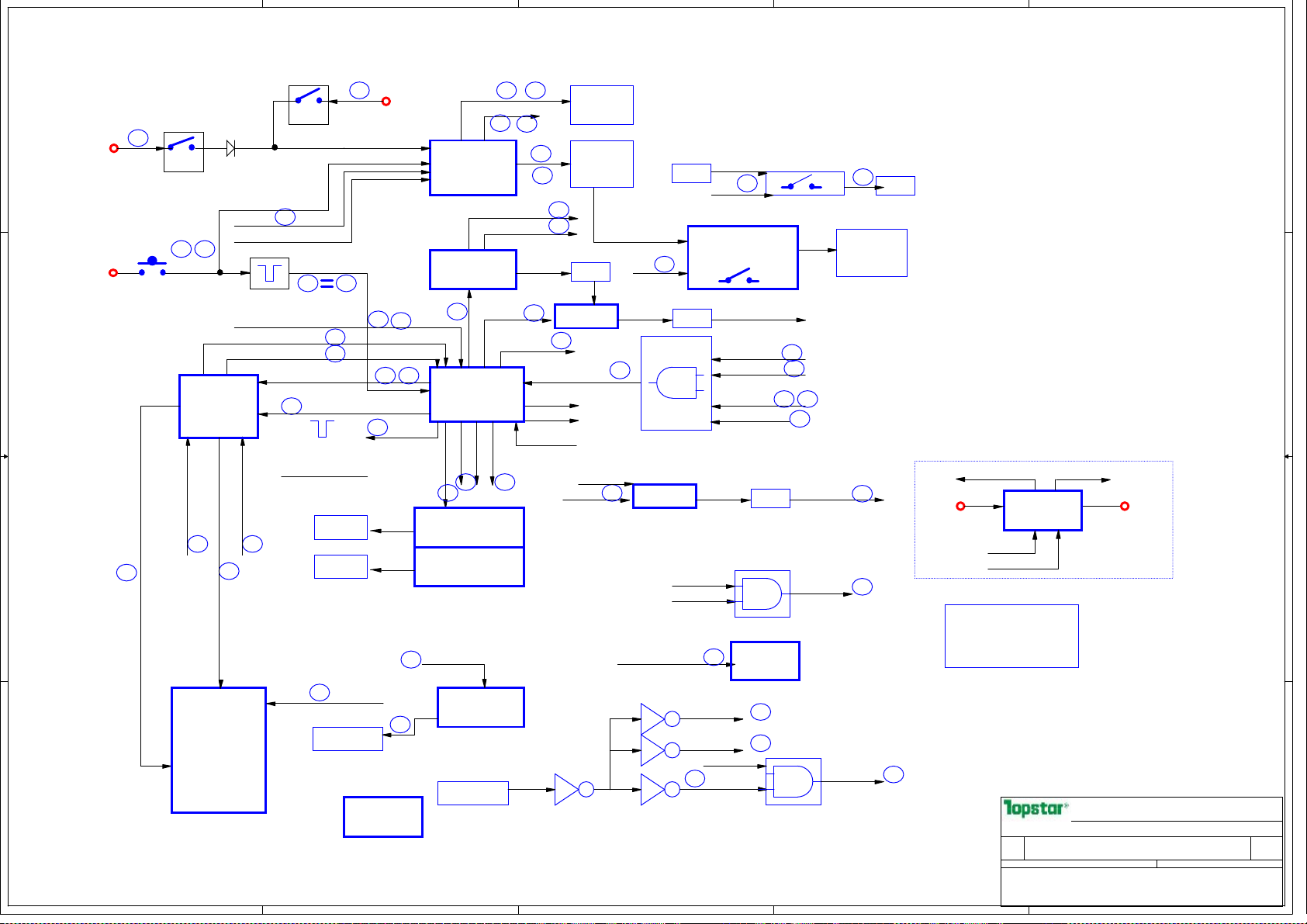

CL341 SYSTEM BLOCK Ver:C

CHA DDR3 SODIMM0

IVY Bridage

Backlight

Connector

+VDC

LED Panel

+V3.3S

C C

LVDS

BIOS

32Mbit

+V3.3S

SPI

BGA1023

+VCC_CORE,+VccGFX

+V1.5, +V1.8S,

+V1.05S

+VCCSA

FDI

GEN 2 DMI*4

Panther Point

989 FCBGA

+V3.3A,+V3.3S,+V1.5S,

+V1.05S,+V1.8S,

PCIE mini Card

HDMI

+V5S

PCIE 1X

+V5A,+V5S

LPC

USB1.1/2.0

DDR3 1333/1600

DDR3 1333/1600

PECI3.0

PCIE 1X

RTL8105E/RTL8111E

USB2.0

AZALIA

SATA ODD

NA

CHB DDR3 SODIMM1

1333/1600

+V0.75S,+V1.5,+V3.3S

+V0.75S,+V1.5,+V3.3S

RJ45

+V3.3S,+V3.3AL

+V5S

S-ATA

2.5" HDD

+V5S,+V3.3S

Card Reader

RTS5138-GR

+V3.3S,+V3.3AL

RJ45

SD/MMC/MS CARD

USB PORT0/1

B B

+V5AL

BLUE

TOOTH(V2.1)

BCM-2046/CCOM

+V3.3AL

+V3.3S

Camera

1.3M/2.0M

MODULE

KB Controller/EC

ENE 3930

+V3.3AL,+V3.3S

PECI3.0

L

R

AZALIA

ALC269

+V5S,+V3.3S

LED/TouchPAD/Button/

A A

5

4

KB Matrix

LID

DAUGHTER BOARD

3

2

MiC

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

杨华明

(Sky Yang)

杨华明

(Sky Yang)

杨华明

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

Sys block

Sys block

Sys block

CL42 EVT

CL42 EVT

CL42 EVT

(Sky Yang)

1

2 51Sunday, April 07, 2013

2 51Sunday, April 07, 2013

2 51Sunday, April 07, 2013

A

A

A

Page 3

5

D D

C C

4

3

2

1

B B

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

杨华明

(Sky Yang)

杨华明

(Sky Yang)

杨华明

(Sky Yang)

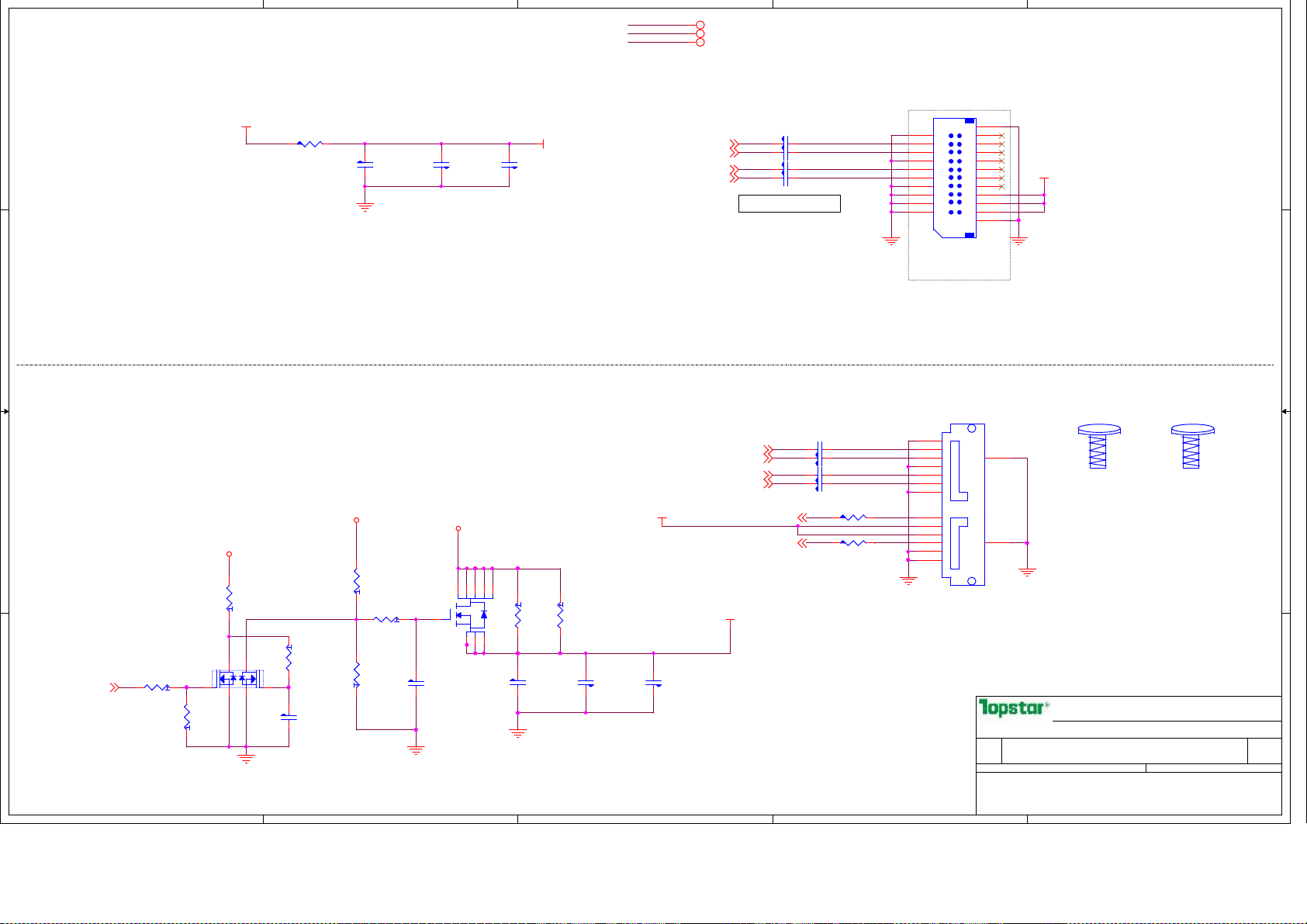

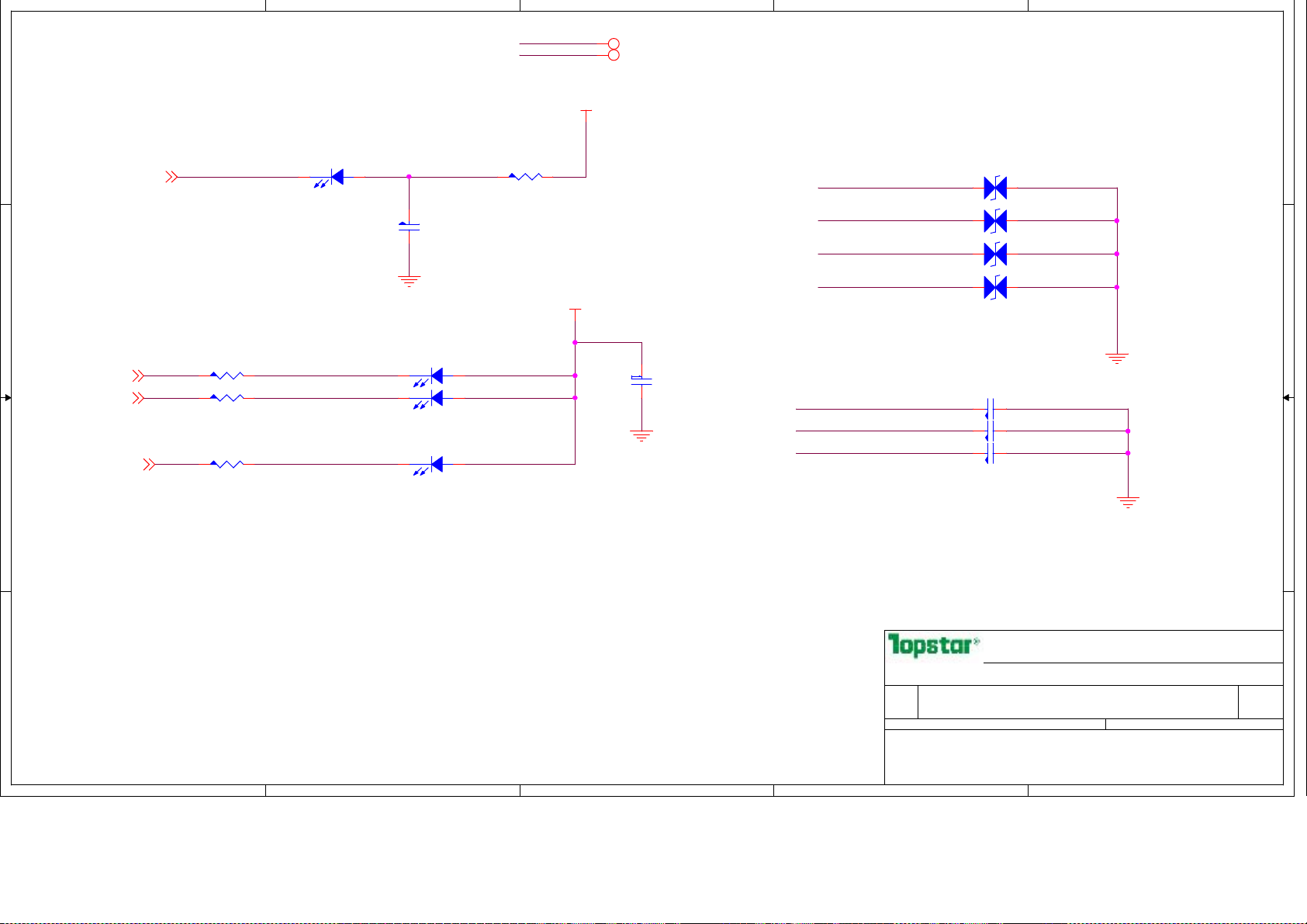

PWR Block

PWR Block

PWR Block

CL42 EVT

CL42 EVT

CL42 EVT

1

A

A

3 51Wednesday, January 09, 2013

3 51Wednesday, January 09, 2013

3 51Wednesday, January 09, 2013

A

Page 4

5

D D

C C

4

3

2

1

B B

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

杨华明

(Sky Yang)

杨华明

(Sky Yang)

杨华明

(Sky Yang)

Notes

Notes

Notes

CL42 EVT

CL42 EVT

CL42 EVT

1

A

A

4 51Wednesday, January 09, 2013

4 51Wednesday, January 09, 2013

4 51Wednesday, January 09, 2013

A

Page 5

5

4

3

2

1

2012-5-16 VerA First Release.

D D

C C

B B

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

杨华明

(Sky Yang)

杨华明

(Sky Yang)

杨华明

(Sky Yang)

Modify and history

Modify and history

Modify and history

CL42 EVT

CL42 EVT

CL42 EVT

1

A

A

5 51Wednesday, January 09, 2013

5 51Wednesday, January 09, 2013

5 51Wednesday, January 09, 2013

A

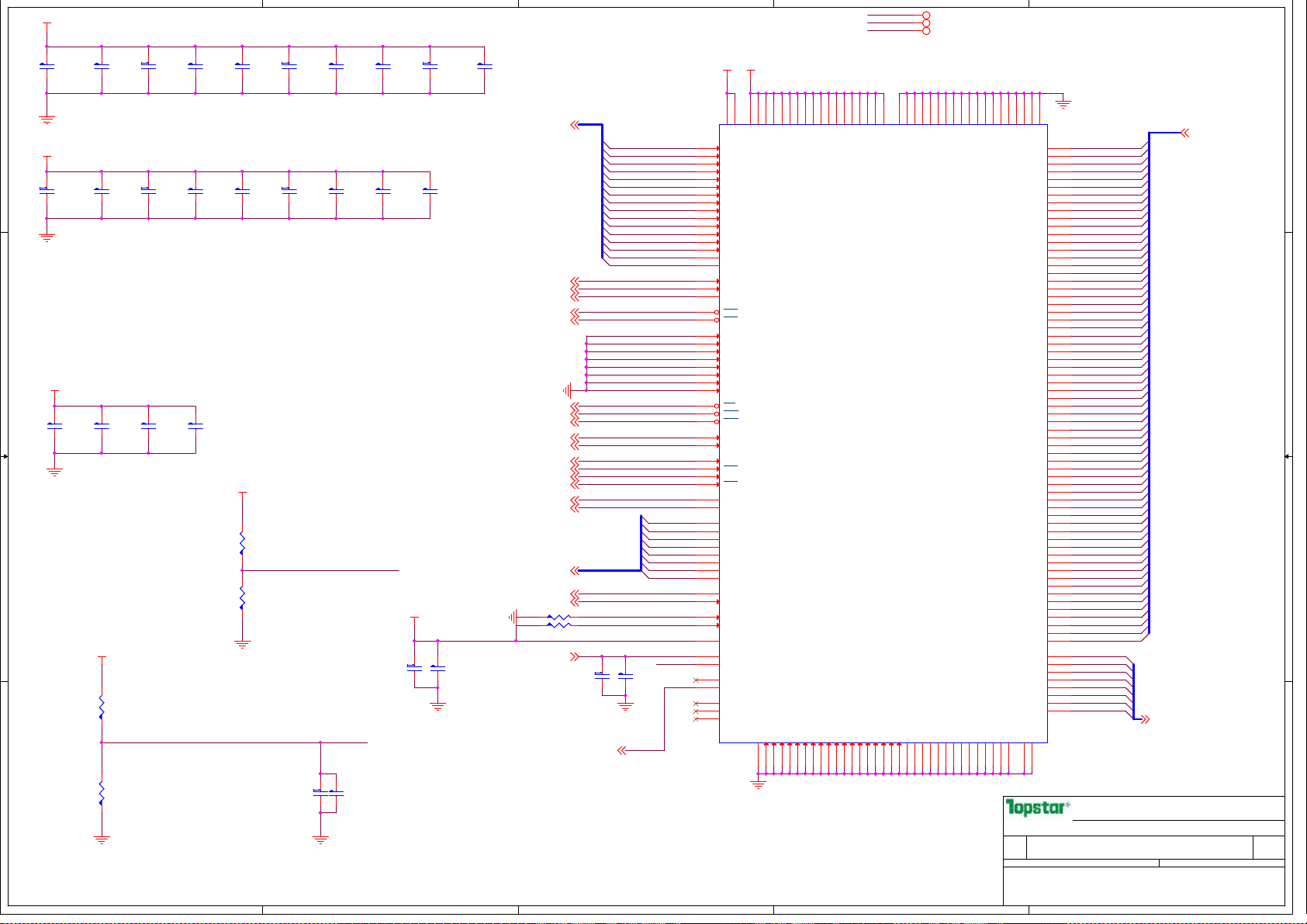

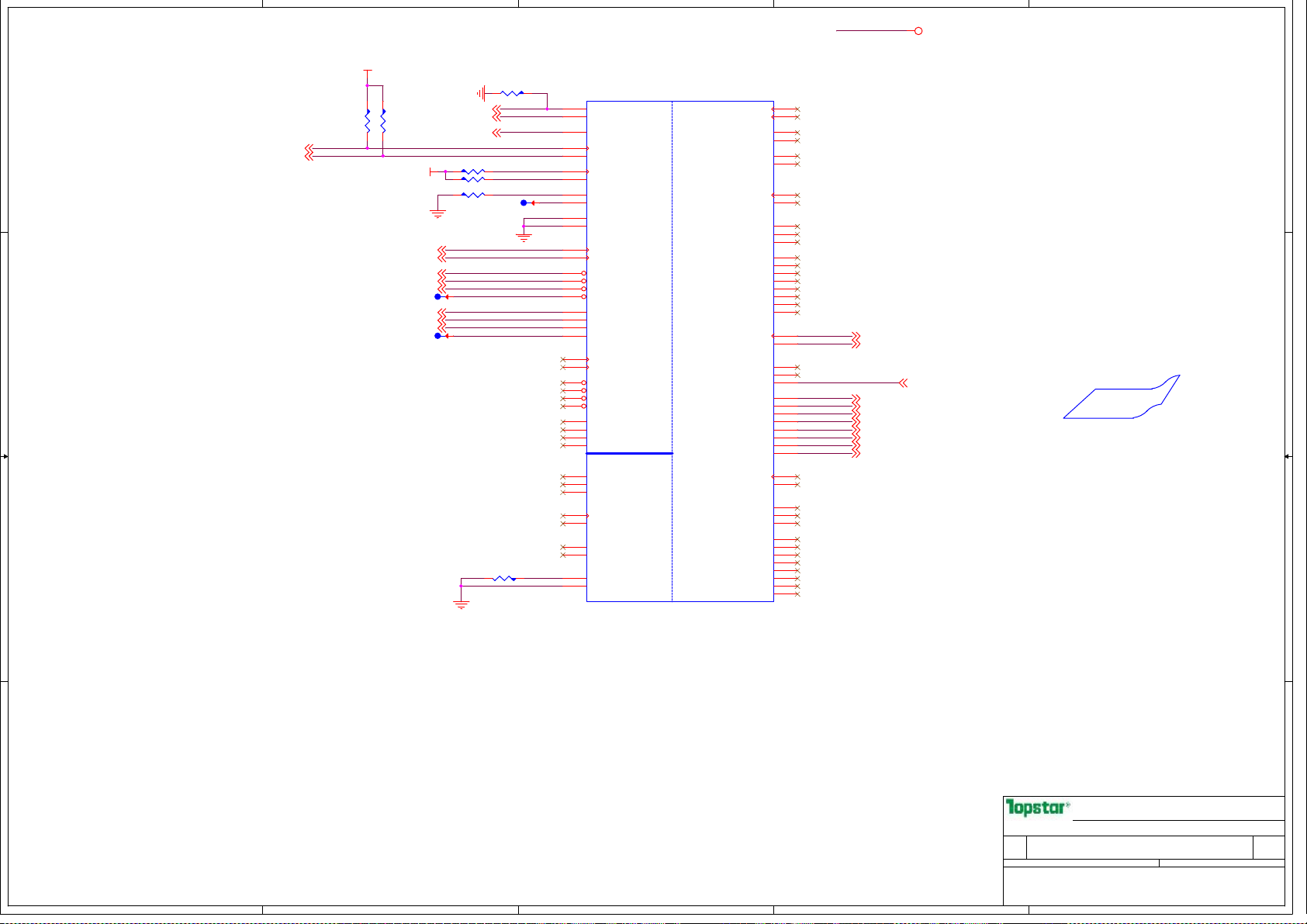

Page 6

5

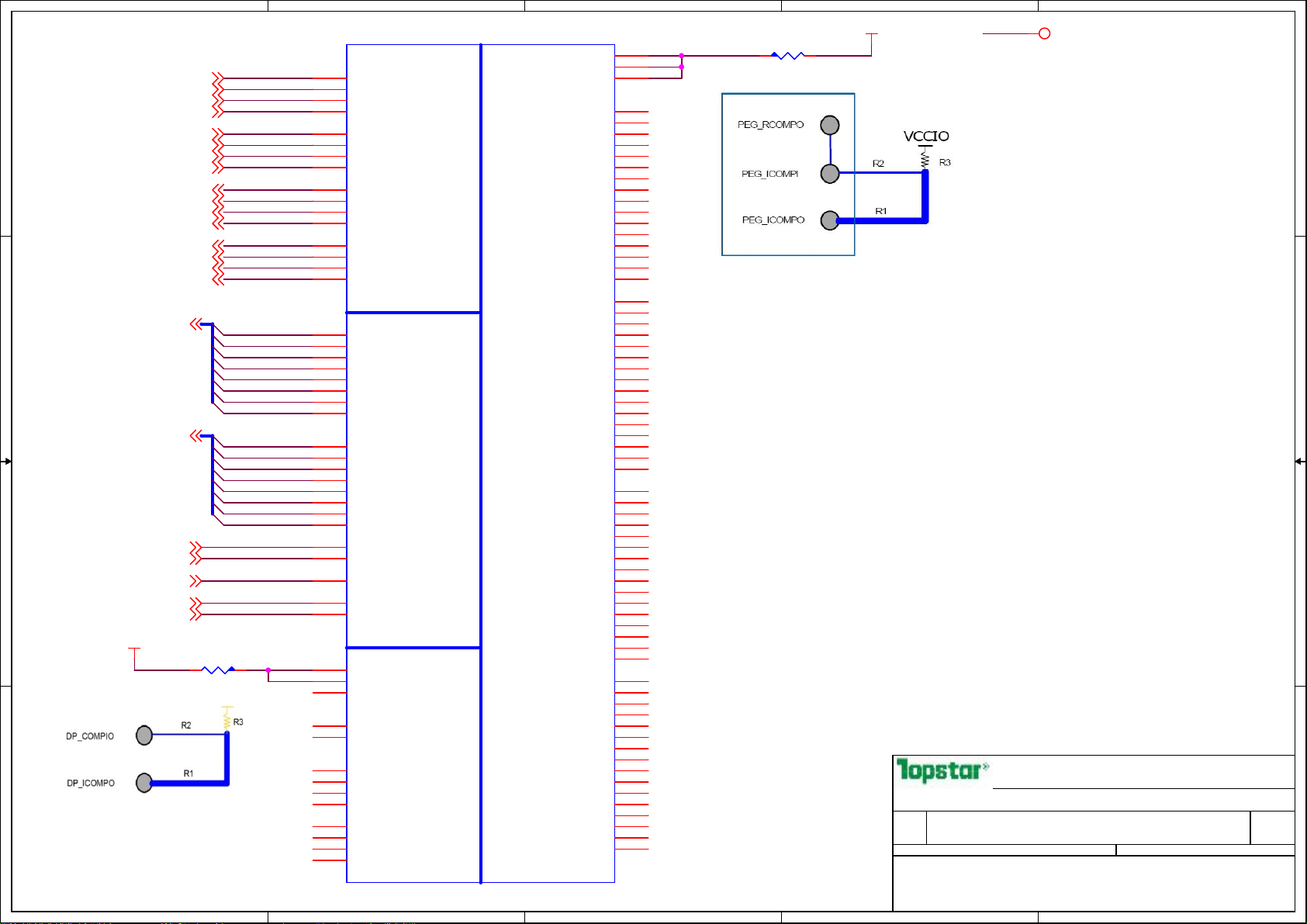

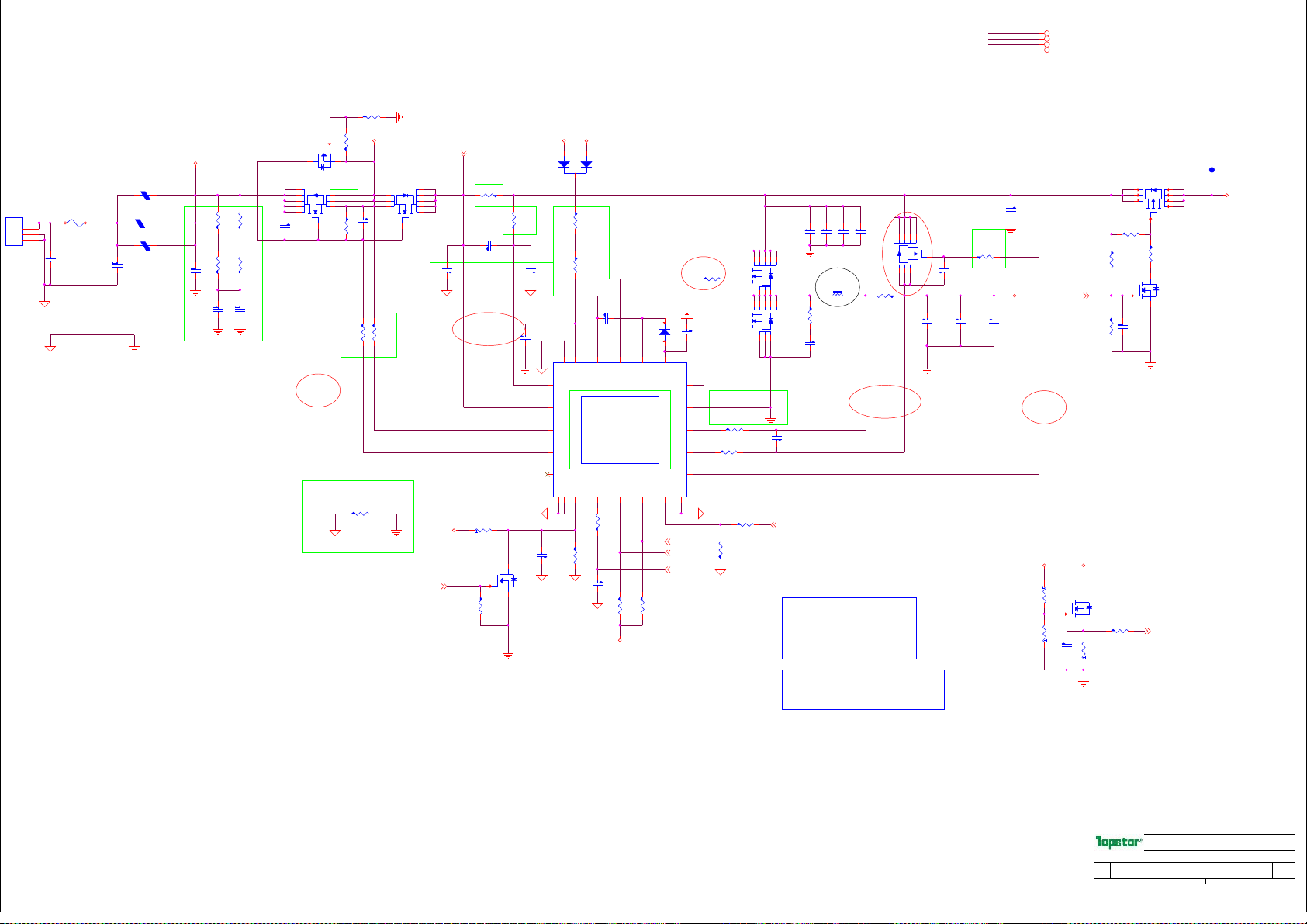

U16A

DMI_TXN017

DMI_TXN117

DMI_TXN217

FDI_TXN[7:0]17

FDI_TXP[7:0]17

FDI_FSYNC017

FDI_FSYNC117

FDI_LSYNC017

FDI_LSYNC117

+V1.05S

DMI_TXN317

DMI_TXP017

DMI_TXP117

DMI_TXP217

DMI_TXP317

DMI_RXN017

DMI_RXN117

DMI_RXN217

DMI_RXN317

DMI_RXP017

DMI_RXP117

DMI_RXP217

DMI_RXP317

FDI_INT17

R206

24.9,1%

R0402

5

D D

C C

B B

Layout notice:

A A

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

DP_COMP

M2

P6

P1

P10

N3

P7

P3

P11

K1

M8

N4

R2

K3

M7

P4

T3

U7

W11

W1

AA6

W6

V4

Y2

AC9

U6

W10

W3

AA7

W7

T4

AA3

AC8

AA11

AC12

U11

AA10

AG8

AF3

AD2

AG11

AG4

AF4

AC3

AC4

AE11

AE7

AC1

AA4

AE10

AE6

IC,IVB_2CBGA,0P7

BGA1023_31X24

4

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

FDI0_TX#[0]

FDI0_TX#[1]

FDI0_TX#[2]

FDI0_TX#[3]

FDI1_TX#[0]

FDI1_TX#[1]

FDI1_TX#[2]

FDI1_TX#[3]

FDI0_TX[0]

FDI0_TX[1]

FDI0_TX[2]

FDI0_TX[3]

FDI1_TX[0]

FDI1_TX[1]

FDI1_TX[2]

FDI1_TX[3]

FDI0_FSYNC

FDI1_FSYNC

FDI_INT

FDI0_LSYNC

FDI1_LSYNC

eDP_COMPIO

eDP_ICOMPO

eDP_HPD#

eDP_AUX#

eDP_AUX

eDP_TX#[0]

eDP_TX#[1]

eDP_TX#[2]

eDP_TX#[3]

eDP_TX[0]

eDP_TX[1]

eDP_TX[2]

eDP_TX[3]

4

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RX#[0]

PEG_RX#[1]

DMI Intel(R) FDI

eDP

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PCI EXPRESS -- GRAPHICS

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

3

G3

PEG_IRCOMP_R

G1

G4

H22

J21

B22

D21

A19

D17

B14

D13

A11

B10

G8

A8

B6

H8

E5

K7

K22

K19

C21

D19

C19

D16

C13

D12

C11

C9

F8

C8

C5

H6

F6

K6

G22

C23

D23

F21

H19

C17

K15

F17

F14

A15

J14

H13

M10

F10

D9

J4

F22

A23

D24

E21

G19

B18

K17

G17

E14

C15

K13

G13

K10

G10

D8

K4

3

R195 24.9,1%

R0402

Layout notice:

+V1.05S

2

+V1.05S 7,9,15,16,17,21,22,30,41,44,47

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Robin

Robin

Robin

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

Ivy Bridge DMI/FDI/PCIE

Ivy Bridge DMI/FDI/PCIE

Ivy Bridge DMI/FDI/PCIE

CL42 EVT

CL42 EVT

CL42 EVT

1

A

A

A

6 51Wednesday, January 09, 2013

6 51Wednesday, January 09, 2013

6 51Wednesday, January 09, 2013

1

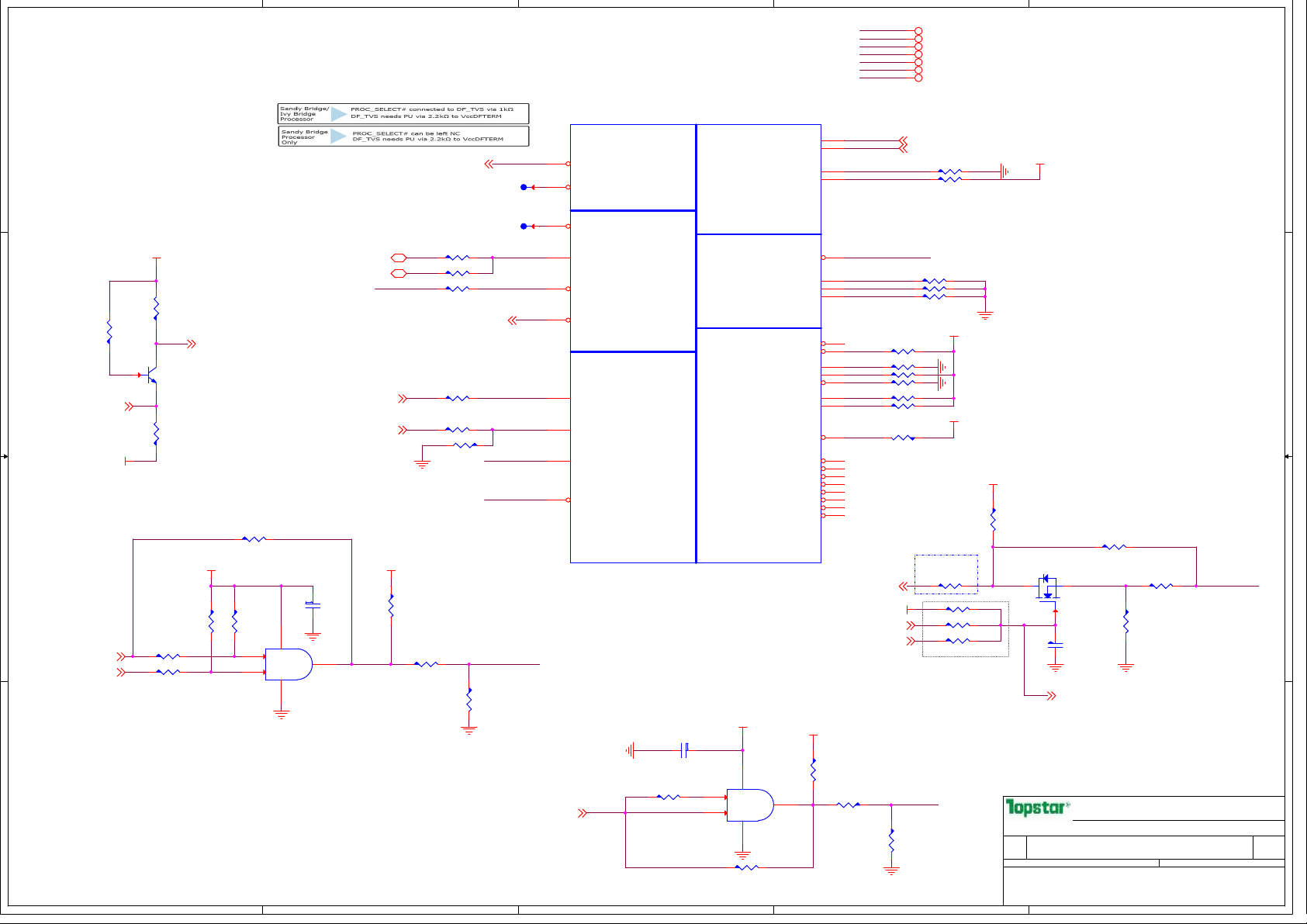

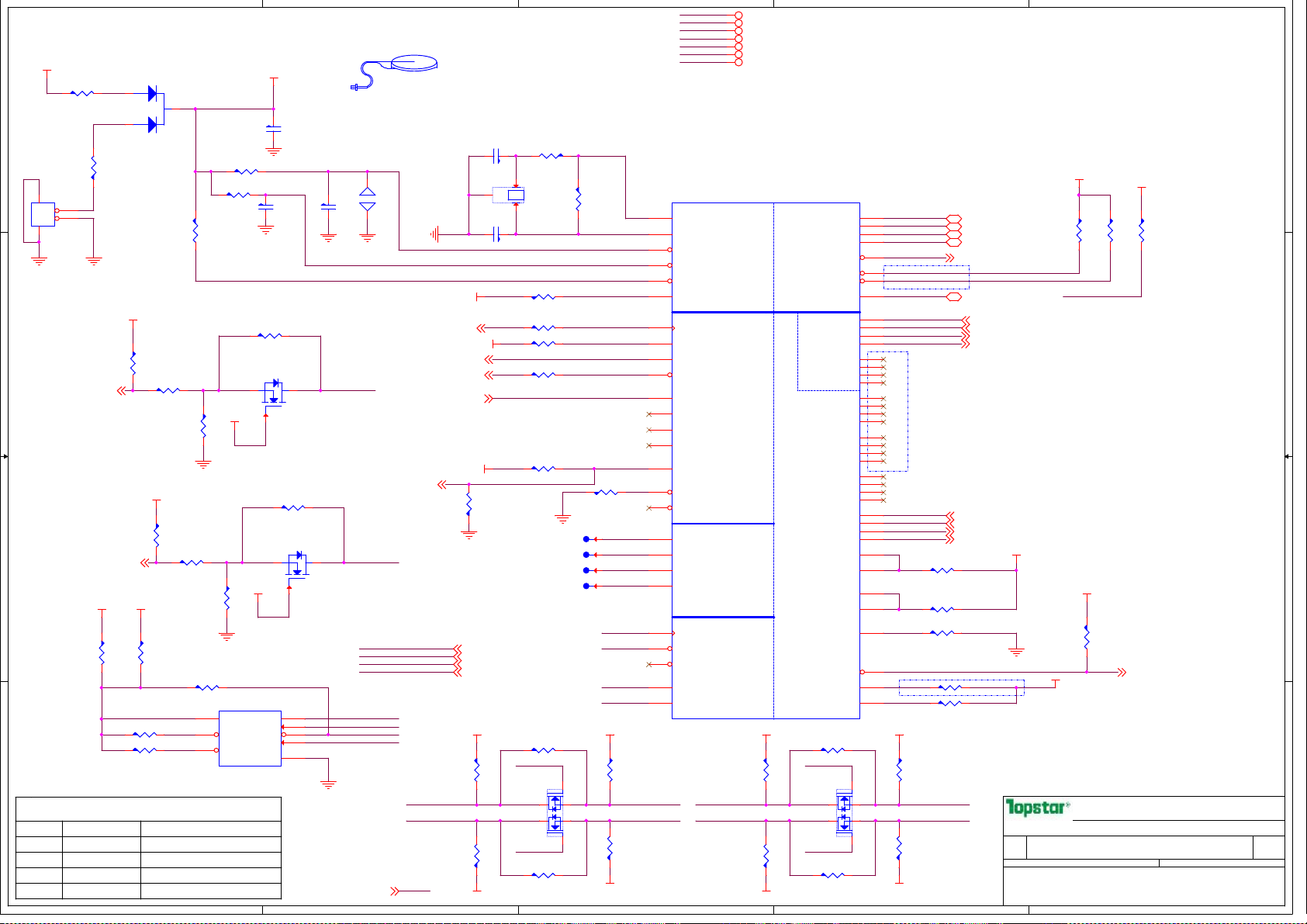

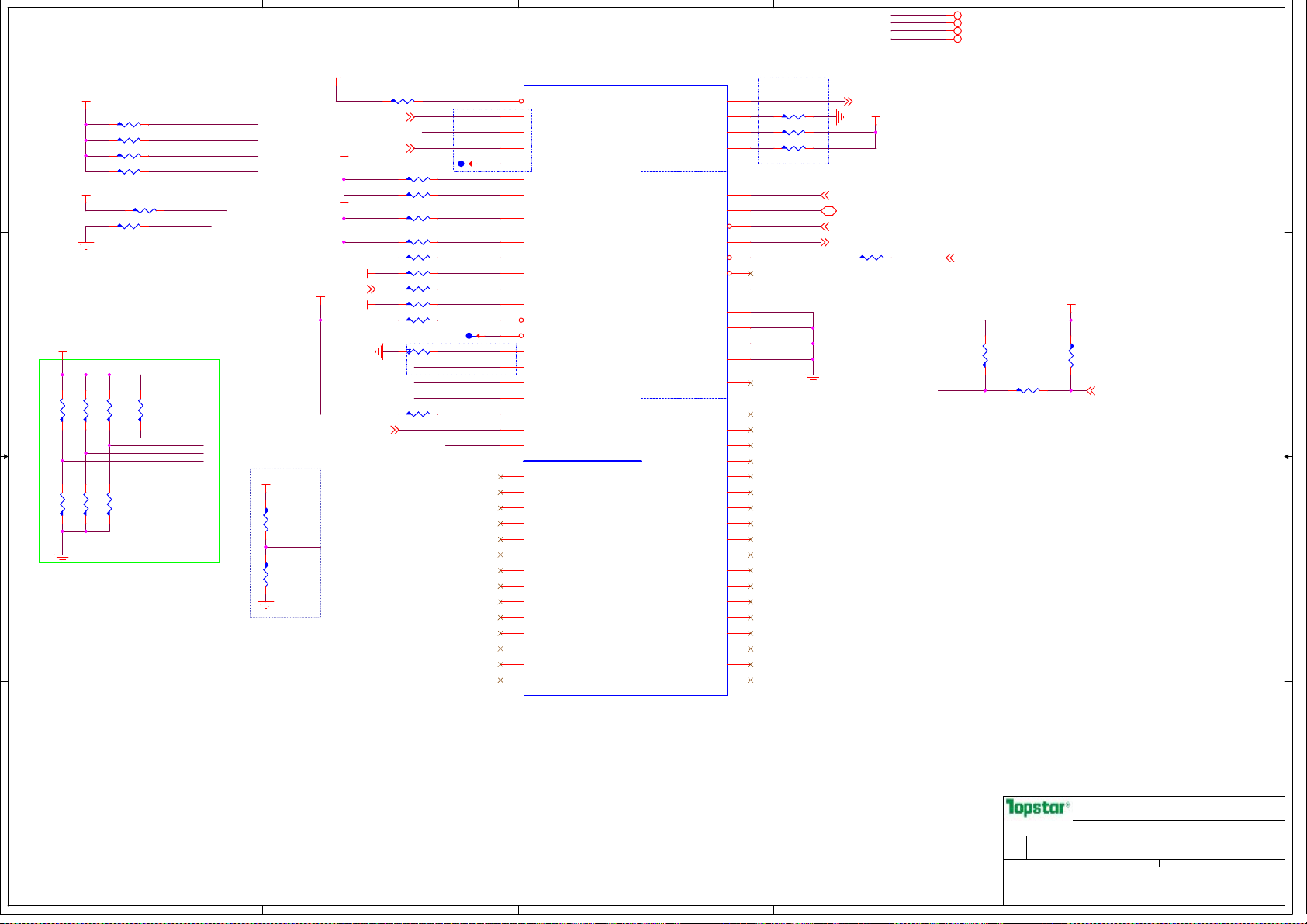

Page 7

5

4

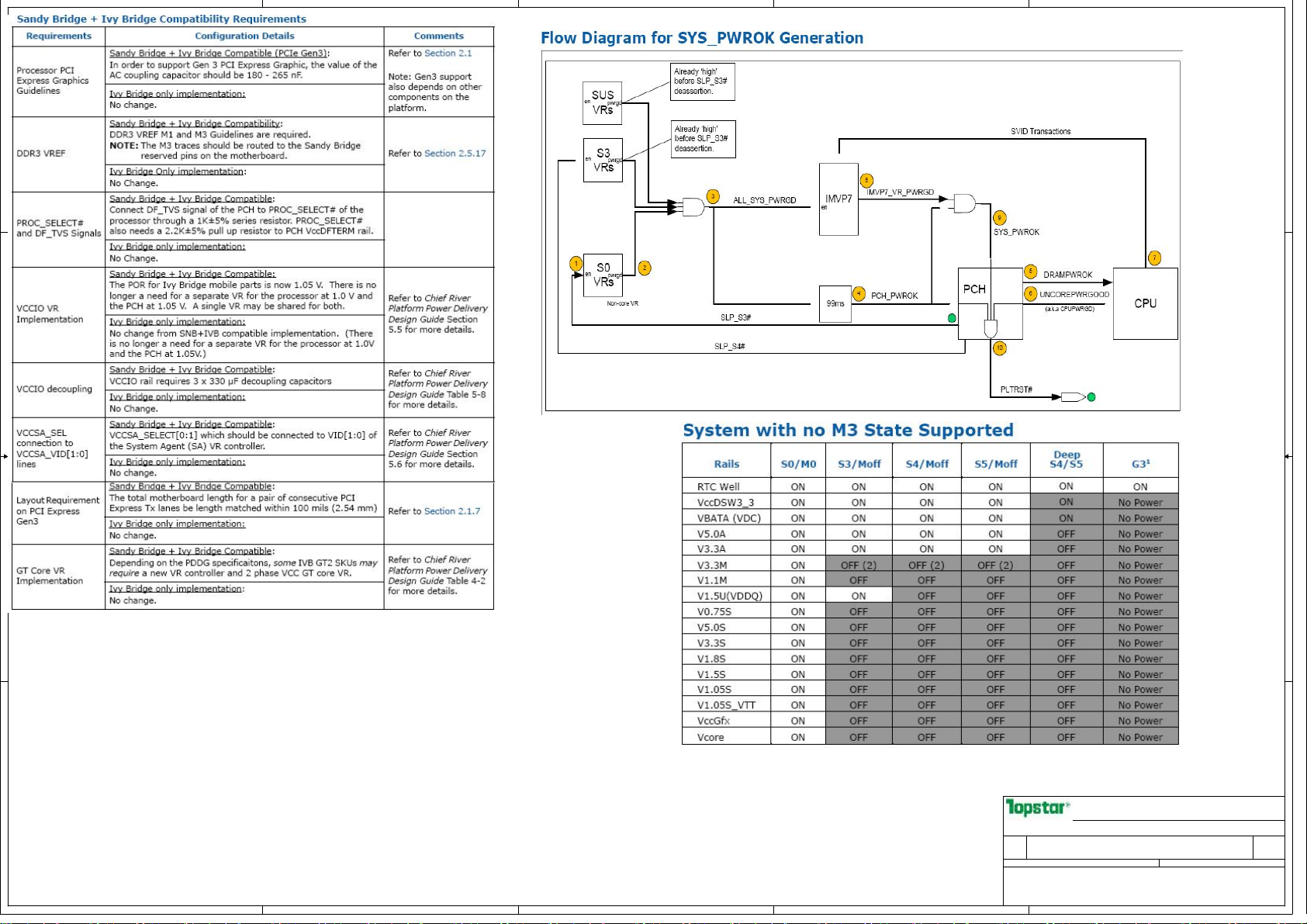

差异

1:Processor type

Sandy Bridge: Output High;

Ivy Bridge: Output low

3

2

+V3.3S 14,15,16,17,18,19,20,21,22,24,25,29,30,31,32,33,34,35,40,41,42,43,44,45,47

+V1.05S 6,9,15,16,17,21,22,30,41,44,47

+V1.5 14,40,45

+V3.3SB 15,17,20,22,28,31,33,35,37,38,39,45

+V3.3AL 15,16,17,19,20,22,24,28,31,33,40,43,45

+V1.5S_CPU_VDDQ

+V1.5S 10,21,31,45

1

BUF_PLT_RST#19,31,33,34

U16B

F49

PRO C_SELE CT#

C57

PRO C_DETE CT#

ICTP

C49

CAT ERR#

A48

ICTP

PEC I

C45

PRO CHOT#

D45

THER MTRIP#

C48

PM_SYNC

B46

UNCORE PWRG OOD

BE4 5

SM_DR AMPWR OK

D44

RES ET#

IC,IVB_2CBGA,0P7

BGA1023_31X24

MISC THERMAL PWR MANAGEMENT

CLOCKS

DDR3

JTAG & BPM

TU142 VerB: Changed R297 to 1k and ns R720 for DRAMRST#

isolate circuit control in Deep S3 2011-12-20

+V3.3AL

C0402

C177 0.1uF/10V,X7R

ns

R710 0

3

R0402

1

2

R363 0

DPL L_REF_ CLK

DPL L_REF_ CLK#

SM_DR AMRST#

SM_RC OMP[0]

SM_RC OMP[1]

SM_RC OMP[2]

MISC

U2

53

VCC

GND

SN74AHC1G08DBV

SOT23_5

R0402ns

4

BCL K

BCL K#

PRD Y#

PRE Q#

TCK

TMS

TRS T#

TDO

DBR #

BPM#[0 ]

BPM#[1 ]

BPM#[2 ]

BPM#[3 ]

BPM#[4 ]

BPM#[5 ]

BPM#[6 ]

BPM#[7 ]

+V1.05S

J3

H2

AG3

CLK_DP_P_R

AG1

CLK_DP_N_R

AT3 0

BF4 4

SM_RCOMP_0

BE4 3

SM_RCOMP_1

BG4 3

SM_RCOMP_2

N53

N55

PREQ#

L56

TCK

L55

TMS

J58

TRST#

M60

TDI

TDI

L59

TDO

K58

DBR#

G58

E55

E59

G55

G59

H60

J59

J61

DDR3_DRAMRST#14

DRAMRST_CNTRL_PCH16

EC_DRAMRST_CNTRL_PCH33

R246

75

R0402

ns

CPU_DRAMRST#

R185 51nsR0402

R190 51 R0402ns

R191 51 R0402ns

R193 51 R0402ns

R189 51 R0402ns

R194 51 R0402ns

R146 1K R0402

+V3.3AL

PLT_RST#_R

R247

2.2K

R0402

CLK_EXP_P 16

CLK_EXP_N 16

R492 1K R0402

R496 1K R0402

R244 140ohm 1%R0402

R243 25.5ohm 1%R0402

R236 200,1% R0402

+V1.05S

+V3.3S

Place near to DIMM

R267

1K

R0402

R720 1K R0402

R278 0 R0402

R297 1K

R0402

R238

1.05K 1%

R0402

2

+V1.05S

+V1.5

R268

1K

R0402

R265 0

Q13

L2N7002LT1G

SOT23

3

2

ns

Page Name

Page Name

Page Name

Size

Size

Size

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

1

C173

470pF/25V,X7R

C0402

DRAMRST_CNTRL 10

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

ns

R0402

R264 0

R262

4.99K,1%

R0402

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Robin

Robin

Robin

Ivy Bridge CLK/MISC

Ivy Bridge CLK/MISC

Ivy Bridge CLK/MISC

CL42 EVT

CL42 EVT

CL42 EVT

1

R0402

CPU_DRAMRST#

7 51Wednesday, January 09, 2013

7 51Wednesday, January 09, 2013

7 51Wednesday, January 09, 2013

A

A

A

D D

H_SNB_IVB#20

T17

ns

T69

ns

+V1.05S

R241

75

1

2 3

R531 0 R0402

R534 0 R0402

5

R0402

VR_PROCHOT# 44

Q11

LMBT3904LT1G

SOT23

R266

10K

R0402

R530

10K

R0402

ns

+V3.3AL

R695 0

R528

200,1%

R0402

1

2

R0402

ns

U20

53

VCC

GND

SN74AHC1G08DBV

SOT23_5

R248

1K

C C

EC_PROCHOT#33

B B

PM_DRAM_PWRGD17

MAIN_PWROK17,33,43

Note:

When implement S3 power save function, need to mount

S3_Power_Save option

A A

R0402

+V3.3SB

H_PM_SYNC17

H_CPUPWRGD20

C363

0.1uF/10V,X7R

C0402

4

H_PECI20

H_PECI_EC33

VR_PROCHOT#

+V1.5S

4

R696

200,1%

R0402

ns

R539 2.37K,1%

R0402

R154 0

R155 47

R147 56

R156 0

R171 0

H_PECI_R

ns

R0402

DG要求R147为43 ohm 5%

R0402

R0402

THERMTRIP#20,30

H_PM_SYNC_R

R0402

H_CPUPWRGD_R

R0402

10KR172

R0402

SM_DRAMPWROK

PLT_RST#_R

Note: Not mount R696 when S3 power save

Note:

S3 power save option: R539:2.37K, R234:2K

No S3 power save option: R539:0ohm, R234:ns

SM_DRAMPWROK

R234

2K,1%

R0402

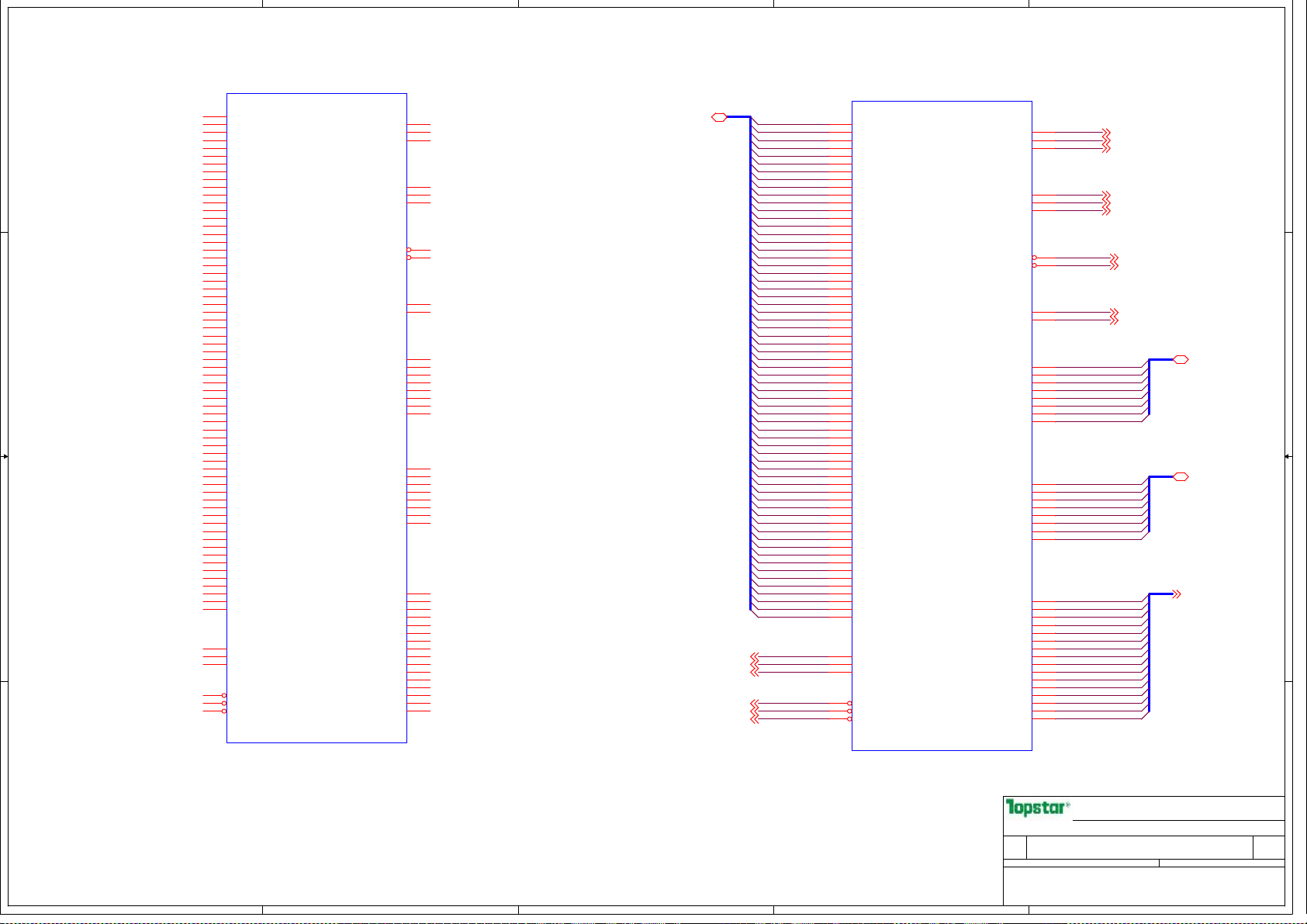

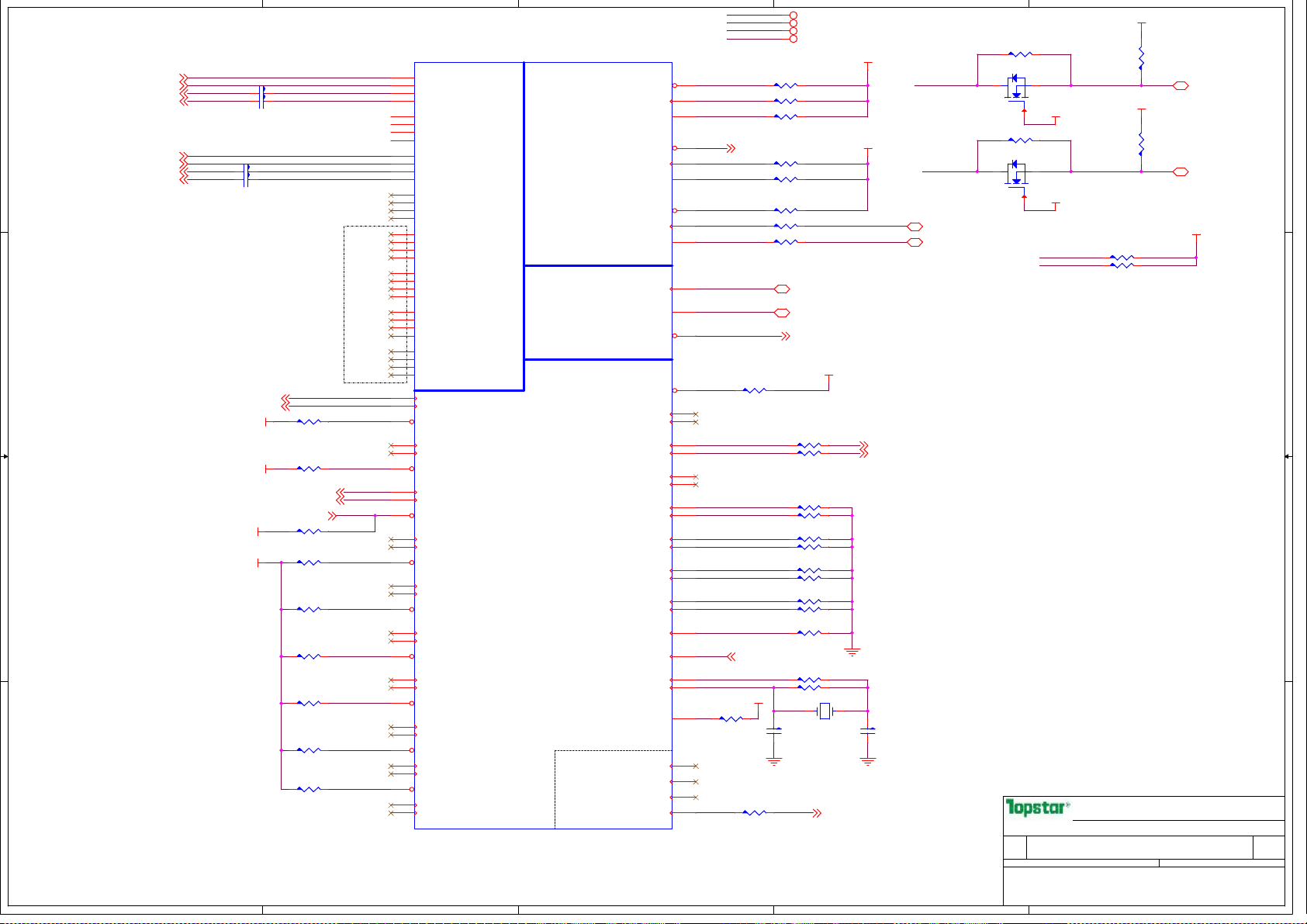

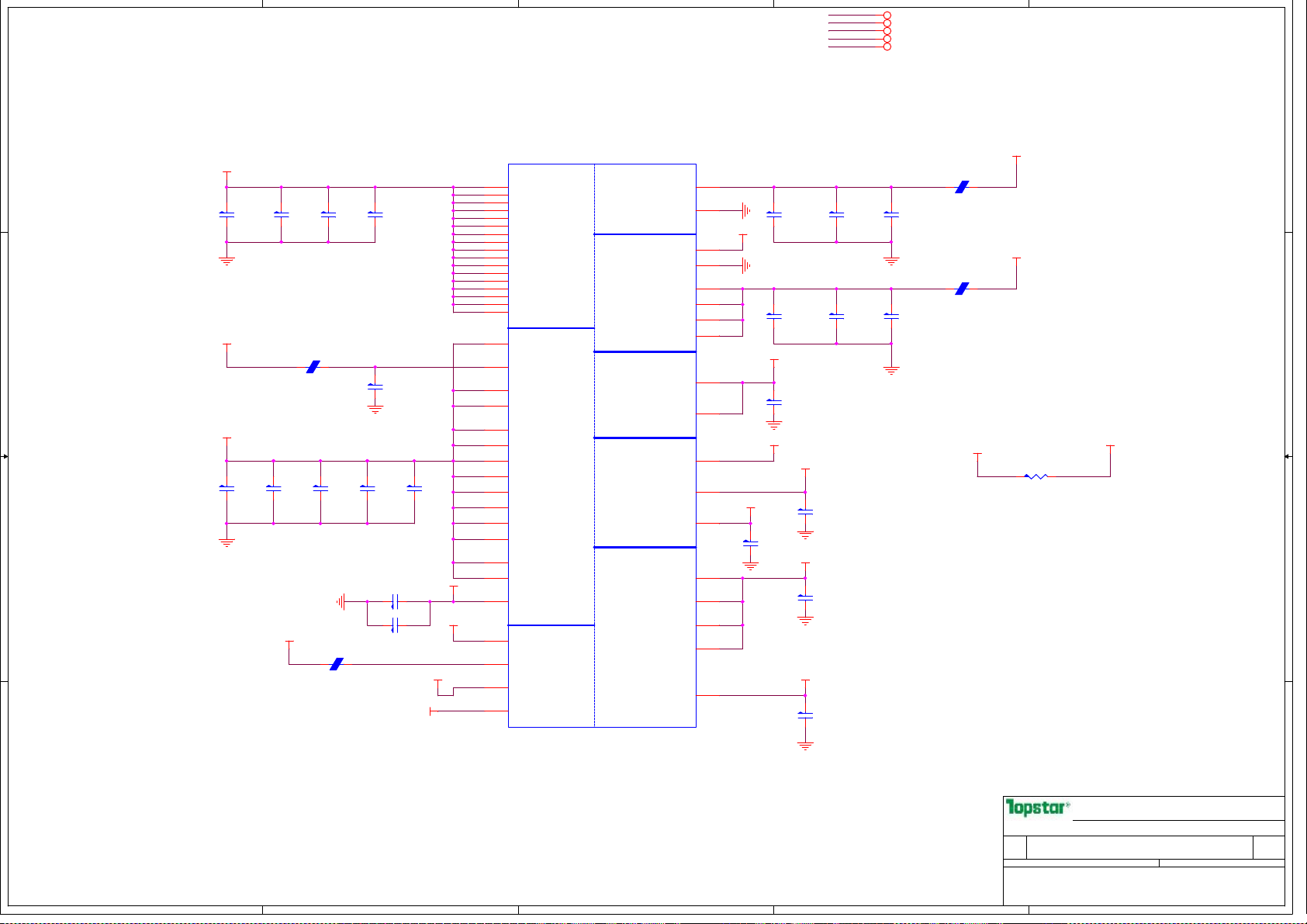

Page 8

5

4

3

2

1

U16C

AG6

SA_ DQ[0]

D D

C C

B B

AJ6

AP1 1

AL6

AJ1 0

AJ8

AL8

AL7

AR1 1

AP6

AU6

AV9

AR6

AP8

AT1 3

AU13

BC7

BB7

BA1 3

BB1 1

BA7

BA9

BB9

AY13

AV1 4

AR1 4

AY17

AR1 9

BA1 4

AU14

BB1 4

BB1 7

BA4 5

AR4 3

AW 48

BC4 8

BC4 5

AR4 5

AT4 8

AY48

BA4 9

AV4 9

BB5 1

AY53

BB4 9

AU49

BA5 3

BB5 5

BA5 5

AV5 6

AP5 0

AP5 3

AV5 4

AT5 4

AP5 6

AP5 2

AN57

AN53

AG5 6

AG5 3

AN55

AN52

AG5 5

AK5 6

BD3 7

BF3 6

BA2 8

BE3 9

BD3 9

AT4 1

SA_ DQ[1]

SA_ DQ[2]

SA_ DQ[3]

SA_ DQ[4]

SA_ DQ[5]

SA_ DQ[6]

SA_ DQ[7]

SA_ DQ[8]

SA_ DQ[9]

SA_ DQ[10]

SA_ DQ[11]

SA_ DQ[12]

SA_ DQ[13]

SA_ DQ[14]

SA_ DQ[15]

SA_ DQ[16]

SA_ DQ[17]

SA_ DQ[18]

SA_ DQ[19]

SA_ DQ[20]

SA_ DQ[21]

SA_ DQ[22]

SA_ DQ[23]

SA_ DQ[24]

SA_ DQ[25]

SA_ DQ[26]

SA_ DQ[27]

SA_ DQ[28]

SA_ DQ[29]

SA_ DQ[30]

SA_ DQ[31]

SA_ DQ[32]

SA_ DQ[33]

SA_ DQ[34]

SA_ DQ[35]

SA_ DQ[36]

SA_ DQ[37]

SA_ DQ[38]

SA_ DQ[39]

SA_ DQ[40]

SA_ DQ[41]

SA_ DQ[42]

SA_ DQ[43]

SA_ DQ[44]

SA_ DQ[45]

SA_ DQ[46]

SA_ DQ[47]

SA_ DQ[48]

SA_ DQ[49]

SA_ DQ[50]

SA_ DQ[51]

SA_ DQ[52]

SA_ DQ[53]

SA_ DQ[54]

SA_ DQ[55]

SA_ DQ[56]

SA_ DQ[57]

SA_ DQ[58]

SA_ DQ[59]

SA_ DQ[60]

SA_ DQ[61]

SA_ DQ[62]

SA_ DQ[63]

SA_ BS[0]

SA_ BS[1]

SA_ BS[2]

SA_ CAS#

SA_ RAS#

SA_ WE#

SA_ DQS#[0]

SA_ DQS#[1]

SA_ DQS#[2]

SA_ DQS#[3]

SA_ DQS#[4]

SA_ DQS#[5]

SA_ DQS#[6]

SA_ DQS#[7]

DDR SYSTEM MEMORY A

SA_ CK[0]

SA_ CK#[0]

SA_ CKE[0]

SA_ CK[1]

SA_ CK#[1]

SA_ CKE[1]

SA_ CS#[0]

SA_ CS#[1]

SA_ ODT[0]

SA_ ODT[1]

SA_ DQS[0]

SA_ DQS[1]

SA_ DQS[2]

SA_ DQS[3]

SA_ DQS[4]

SA_ DQS[5]

SA_ DQS[6]

SA_ DQS[7]

SA_ MA[0]

SA_ MA[1]

SA_ MA[2]

SA_ MA[3]

SA_ MA[4]

SA_ MA[5]

SA_ MA[6]

SA_ MA[7]

SA_ MA[8]

SA_ MA[9]

SA_ MA[10]

SA_ MA[11]

SA_ MA[12]

SA_ MA[13]

SA_ MA[14]

SA_ MA[15]

AU36

AV3 6

AY26

AT4 0

AU40

BB2 6

BB4 0

BC4 1

AY40

BA4 1

AL1 1

AR8

AV1 1

AT1 7

AV4 5

AY51

AT5 5

AK5 5

AJ1 1

AR1 0

AY11

AU17

AW 45

AV5 1

AT5 6

AK5 4

BG3 5

BB3 4

BE3 5

BD3 5

AT3 4

AU34

BB3 2

AT3 2

AY32

AV3 2

BE3 7

BA3 0

BC3 0

AW 41

AY28

AU26

MB_DATA[63:0]14

MB_B_BS014

MB_B_BS114

MB_B_BS214

MB_B_CAS#14

MB_B_RAS#14

MB_B_WE#14

MB_DATA0

MB_DATA1

MB_DATA2

MB_DATA3

MB_DATA4

MB_DATA5

MB_DATA6

MB_DATA7

MB_DATA8

MB_DATA9

MB_DATA10

MB_DATA11

MB_DATA12

MB_DATA13

MB_DATA14

MB_DATA15

MB_DATA16

MB_DATA17

MB_DATA18

MB_DATA19

MB_DATA20

MB_DATA21

MB_DATA22

MB_DATA23

MB_DATA25

MB_DATA24

MB_DATA27

MB_DATA26

MB_DATA28

MB_DATA29

MB_DATA30

MB_DATA31

MB_DATA32

MB_DATA33

MB_DATA34

MB_DATA35

MB_DATA36

MB_DATA37

MB_DATA38

MB_DATA39

MB_DATA40

MB_DATA41

MB_DATA42

MB_DATA43

MB_DATA44

MB_DATA45

MB_DATA46

MB_DATA47

MB_DATA48

MB_DATA49

MB_DATA50

MB_DATA51

MB_DATA52

MB_DATA53

MB_DATA54

MB_DATA55

MB_DATA56

MB_DATA57

MB_DATA58

MB_DATA59

MB_DATA60

MB_DATA61

MB_DATA62

MB_DATA63

AL4

AL1

AN3

AR4

AK4

AK3

AN4

AR1

AU4

AT2

AV4

BA4

AU3

AR3

AY2

BA3

BE9

BD9

BD1 3

BF1 2

BF8

BD1 0

BD1 4

BE1 3

BF1 6

BE1 7

BE1 8

BE2 1

BE1 4

BG1 4

BG1 8

BF1 9

BD5 0

BF4 8

BD5 3

BF5 2

BD4 9

BE4 9

BD5 4

BE5 3

BF5 6

BE5 7

BC5 9

AY60

BE5 4

BG5 4

BA5 8

AW 59

AW 58

AU58

AN61

AN59

AU59

AU61

AN58

AR5 8

AK5 8

AL5 8

AG5 8

AG5 9

AM60

AL5 9

AF6 1

AH60

BG3 9

BD4 2

AT2 2

AV4 3

BF4 0

BD4 5

U16D

SB_ DQ[0]

SB_ DQ[1]

SB_ DQ[2]

SB_ DQ[3]

SB_ DQ[4]

SB_ DQ[5]

SB_ DQ[6]

SB_ DQ[7]

SB_ DQ[8]

SB_ DQ[9]

SB_ DQ[10]

SB_ DQ[11]

SB_ DQ[12]

SB_ DQ[13]

SB_ DQ[14]

SB_ DQ[15]

SB_ DQ[16]

SB_ DQ[17]

SB_ DQ[18]

SB_ DQ[19]

SB_ DQ[20]

SB_ DQ[21]

SB_ DQ[22]

SB_ DQ[23]

SB_ DQ[24]

SB_ DQ[25]

SB_ DQ[26]

SB_ DQ[27]

SB_ DQ[28]

SB_ DQ[29]

SB_ DQ[30]

SB_ DQ[31]

SB_ DQ[32]

SB_ DQ[33]

SB_ DQ[34]

SB_ DQ[35]

SB_ DQ[36]

SB_ DQ[37]

SB_ DQ[38]

SB_ DQ[39]

SB_ DQ[40]

SB_ DQ[41]

SB_ DQ[42]

SB_ DQ[43]

SB_ DQ[44]

SB_ DQ[45]

SB_ DQ[46]

SB_ DQ[47]

SB_ DQ[48]

SB_ DQ[49]

SB_ DQ[50]

SB_ DQ[51]

SB_ DQ[52]

SB_ DQ[53]

SB_ DQ[54]

SB_ DQ[55]

SB_ DQ[56]

SB_ DQ[57]

SB_ DQ[58]

SB_ DQ[59]

SB_ DQ[60]

SB_ DQ[61]

SB_ DQ[62]

SB_ DQ[63]

SB_ BS[0]

SB_ BS[1]

SB_ BS[2]

SB_ CAS#

SB_ RAS#

SB_ WE#

BA3 4

SB_ CK[0]

AY34

SB_ CK#[0]

AR2 2

SB_ CKE[0]

BA3 6

SB_ CK[1]

BB3 6

SB_ CK#[1]

BF2 7

SB_ CKE[1]

BE4 1

SB_ CS#[0]

BE4 7

SB_ CS#[1]

AT4 3

SB_ ODT[0]

BG4 7

SB_ ODT[1]

AL3

SB_ DQS#[0]

SB_ DQS#[1]

SB_ DQS#[2]

SB_ DQS#[3]

SB_ DQS#[4]

SB_ DQS#[5]

SB_ DQS#[6]

SB_ DQS#[7]

SB_ DQS[0]

SB_ DQS[1]

SB_ DQS[2]

SB_ DQS[3]

SB_ DQS[4]

SB_ DQS[5]

SB_ DQS[6]

SB_ DQS[7]

AV3

BG1 1

BD1 7

BG5 1

BA5 9

AT6 0

AK5 9

AM2

AV1

BE1 1

BD1 8

BE5 1

BA6 1

AR5 9

AK6 1

MB_DQS#0

MB_DQS#1

MB_DQS#2

MB_DQS#3

MB_DQS#4

MB_DQS#5

MB_DQS#6

MB_DQS#7

MB_DQS0

MB_DQS1

MB_DQS2

MB_DQS3

MB_DQS4

MB_DQS5

MB_DQS6

MB_DQS7

DDR SYSTEM MEMORY B

SB_ MA[0]

SB_ MA[1]

SB_ MA[2]

SB_ MA[3]

SB_ MA[4]

SB_ MA[5]

SB_ MA[6]

SB_ MA[7]

SB_ MA[8]

SB_ MA[9]

SB_ MA[10]

SB_ MA[11]

SB_ MA[12]

SB_ MA[13]

SB_ MA[14]

SB_ MA[15]

BF3 2

BE3 3

BD3 3

AU30

BD3 0

AV3 0

BG3 0

BD2 9

BE3 0

BE2 8

BD4 3

AT2 8

AV2 8

BD4 6

AT2 6

AU22

MB_B_A0

MB_B_A1

MB_B_A2

MB_B_A3

MB_B_A4

MB_B_A5

MB_B_A6

MB_B_A7

MB_B_A8

MB_B_A9

MB_B_A10

MB_B_A11

MB_B_A12

MB_B_A13

MB_B_A14

MB_B_A15

M_CLK_DDR2 14

M_CLK_DDR#2 14

M_CKE2 14

M_CLK_DDR3 14

M_CLK_DDR#3 14

M_CKE3 14

M_CS#2 14

M_CS#3 14

M_ODT2 14

M_ODT3 14

MB_DQS#[7:0] 14

MB_DQS[7:0] 14

MB_B_A[15:0] 14

IC,IVB_2CBGA,0P7

BGA1023_31X24

A A

5

4

3

IC,IVB_2CBGA,0P7

BGA1023_31X24

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Robin

Robin

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

Robin

Ivy Bridge DDR3

Ivy Bridge DDR3

Ivy Bridge DDR3

CL42 EVT

CL42 EVT

CL42 EVT

A

A

8 51Sunday, April 07, 2013

8 51Sunday, April 07, 2013

8 51Sunday, April 07, 2013

1

A

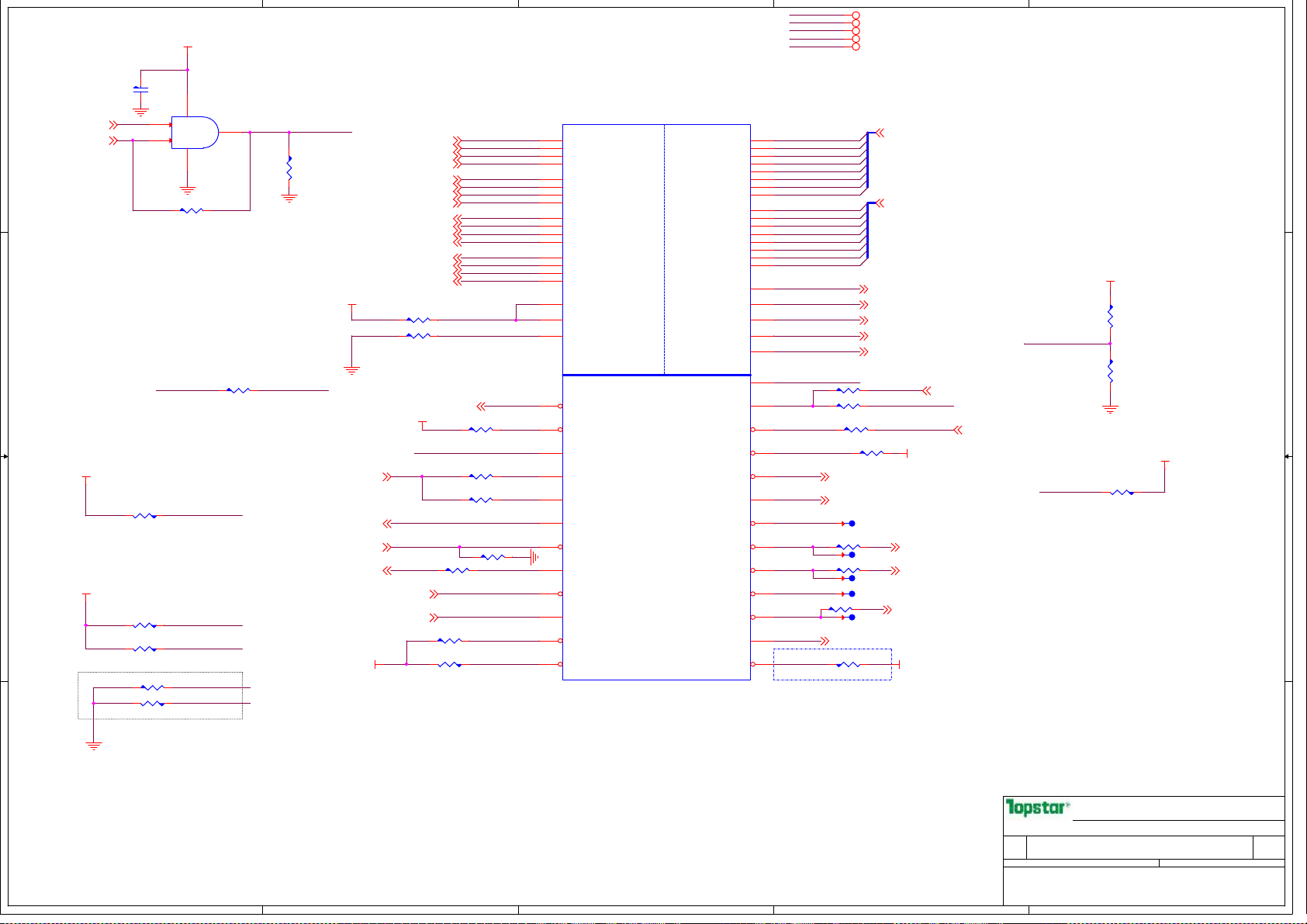

Page 9

5

U16F

ULV(17W):33A

LV(25W):43A

SV(35W):53A

A26

VCC[1]

A29

VCC[2]

A31

VCC[3]

G42

H25

H26

H28

H29

H32

H34

H35

H37

H38

H40

K26

K27

K29

K32

K34

K35

K37

K39

K42

N26

N30

N34

N38

A34

VCC[4]

A35

VCC[5]

A38

VCC[6]

A39

VCC[7]

A42

VCC[8]

C26

VCC[9]

C27

VCC[10]

C32

VCC[11]

C34

VCC[12]

C37

VCC[13]

C39

VCC[14]

C42

VCC[15]

D27

VCC[16]

D32

VCC[17]

D34

VCC[18]

D37

VCC[19]

D39

VCC[20]

D42

VCC[21]

E26

VCC[22]

E28

VCC[23]

E32

VCC[24]

E34

VCC[25]

E37

VCC[26]

E38

VCC[27]

F25

VCC[28]

F26

VCC[29]

F28

VCC[30]

F32

VCC[31]

F34

VCC[32]

F37

VCC[33]

F38

VCC[34]

F42

VCC[35]

VCC[36]

VCC[37]

VCC[38]

VCC[39]

VCC[40]

VCC[41]

VCC[42]

VCC[43]

VCC[44]

VCC[45]

VCC[46]

J25

VCC[47]

J26

VCC[48]

J28

VCC[49]

J29

VCC[50]

J32

VCC[51]

J34

VCC[52]

J35

VCC[53]

J37

VCC[54]

J38

VCC[55]

J40

VCC[56]

J42

VCC[57]

VCC[58]

VCC[59]

VCC[60]

VCC[61]

VCC[62]

VCC[63]

VCC[64]

VCC[66]

VCC[67]

L25

VCC[68]

L28

VCC[69]

L33

VCC[70]

L36

VCC[71]

L40

VCC[72]

VCC[73]

VCC[74]

VCC[75]

VCC[76]

D D

C C

B B

POWER

CORE SUPPLY

AF46

VCCIO[1]

AG48

VCCIO[3]

AG50

VCCIO[4]

AG51

VCCIO[5]

AJ17

VCCIO[6]

AJ21

VCCIO[7]

AJ25

VCCIO[8]

AJ43

VCCIO[9]

AJ47

VCCIO[10]

AK50

VCCIO[11]

AK51

VCCIO[12]

AL14

VCCIO[13]

AL15

VCCIO[14]

AL16

VCCIO[15]

AL20

VCCIO[16]

AL22

VCCIO[17]

AL26

VCCIO[18]

AL45

VCCIO[19]

AL48

VCCIO[20]

AM16

VCCIO[21]

AM17

VCCIO[22]

AM21

VCCIO[23]

AM43

VCCIO[24]

AM47

VCCIO[25]

AN20

VCCIO[26]

AN42

VCCIO[27]

AN45

VCCIO[28]

AN48

VCCIO[29]

AA14

VCCIO[30]

AA15

VCCIO[31]

AB17

VCCIO[32]

VCCIO[33]

VCCIO[34]

VCCIO[35]

VCCIO[36]

VCCIO[37]

VCCIO[38]

VCCIO[39]

VCCIO[40]

VCCIO[41]

VCCIO[42]

VCCIO[43]

VCCIO[44]

VCCIO[45]

VCCIO[46]

VCCIO[47]

VCCIO[48]

VCCIO[49]

VCCIO50

VCCIO51

VCCIO_SEL

VCCPQE[1]

VCCPQE[2]

AB20

AC13

AD16

AD18

AD21

AE14

AE15

AF16

AF18

AF20

AG15

AG16

AG17

AG20

AG21

AJ14

AJ15

W16

W17

BC22

AM25

AN22

PEG IO AND DDR IO

RAILS

A44

VIDALERT#

B43

VIDSCLK

C44

VIDSOUT

4

+V1.05S+VCC_CORE

C346

C0805

10uf/6.3V

+V1.05S

+V1.05S

C353

C0402

1uf/10V

8.5A

Max: 8.5A

C145

C0402

1uf/10V

R197 0

R0402

Processor 1.05V Quiet rail for DDR block,

BGA only

T84 ICTP ns

0.4A

C121

C0402

1uf/10V

R140 45.3 1% R0402

R722 0 R0402

R723 0 R0402

请注意走线

R721

75

R0402

+V1.05S

R148

130,1%

R0402

VR_SVID_ALERT# 44

VR_SVID_CLK 44

VR_SVID_DATA 44

C345

C0805

10uf/6.3V

C349

C0402

1uf/10V

+VCC_CORE

+VCC_CORE

C150

C0805

10uf/6.3V

C347

C0402

1uf/10V

3

C148

C0805

10uf/6.3V

C348

C0805

10uf/6.3V

CRB 上10个10uF,26个1uF,两个330uF

C275

C0402

1uf/10V

C273

C0402

1uf/10V

20*10uF+12*1uF

C129

C0805

10uf/6.3V

C138

C0402

1uf/10V

C157

C0402

1uf/10V

C135

C0805

10uf/6.3V

C341

C0402

1uf/10V

C170

C0402

1uf/10V

10uf/6.3V

1uf/10V

1uf/10V

C270

C0402

1uf/10V

C147

C0805

10uf/6.3V

C350

C0402

1uf/10V

C146

C0805

10uf/6.3V

C152

C0402

1uf/10V

CRB 上35个2.2uF,45个22uF,6个470uF

C115

C0805

C342

C0402

C171

C0402

C336

C0805

10uf/6.3V

C343

C0402

1uf/10V

C165

C0402

1uf/10V

C337

C0805

10uf/6.3V

C117

C0402

1uf/10V

2

C151

C0805

10uf/6.3V

1uf/10V

C338

C0805

10uf/6.3V

C118

C0402

1uf/10V

C274

C0402

+VCC_CORE 44

+V1.05S 6,7,15,16,17,21,22,30,41,44,47

C149

C0805

10uf/6.3V

1uf/10V

C141

C0805

10uf/6.3V

C122

C0402

1uf/10V

C344

C0402

1uf/10V

C111

C0805

10uf/6.3V

C328

C0402

1uf/10V

C267

C0805

10uf/6.3V

C276

C0402

10uf/6.3V

C123

C0402

1uf/10V

C131

C0805

C136

C0805

10uf/6.3V

C119

C0402

1uf/10V

1

C110

C0805

10uf/6.3V

C329

C0402

1uf/10V

C112

C0805

10uf/6.3V

C130

C0402

1uf/10V

R141

100,1%

F43

VCC_SENSE

A A

IC,IVB_2CBGA,0P7

BGA1023_31X24

5

VSS_SENSE

VCCIO_SENSE

VSS_SENSE_VCCIO

SENSE LINES SVID QUIET

VCCSENSE_R

G43

VSSSENSE_ R

+V1.05S

AN16

R204 0 R0402

AN17

R205 0 R0402

R149 0 R0402

R150 0 R0402

R741 10

R0402

4

VCCP_SENSE 41

VSSP_SE NSE

R742

10

R0402

R0402

R142

100,1%

R0402

VCCSENSE 44

VSSSENSE 44

3

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Robin

Robin

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

the expressed written consent of TOPSTAR

Robin

Ivy Bridge Vcore/VTT

Ivy Bridge Vcore/VTT

Ivy Bridge Vcore/VTT

CL42 EVT

CL42 EVT

CL42 EVT

1

A

A

9 51Wednesday, January 09, 2013

9 51Wednesday, January 09, 2013

9 51Wednesday, January 09, 2013

A

Page 10

5

+VGFX

D D

C C

B B

A A

C339

C0402

1uf/10V

C327

C0805

10uf/6.3 V

C409

C0805

10uf/6.3 V

C351

C0402

1uf/10V

+V1.8S

GT2: 33A

GT1: 20A

FB0805

CRB 6颗22uF,6颗10uF,11颗1uF,2颗470uF

C352

C127

C0805

C0805

10uf/6.3 V

10uf/6.3 V

C354

C358

C0402

C0805

0.22uF/ 10V,X7R

10uf/6.3 V

C326

C340

C0402

C0402

1uf/10V

1uf/10V

FB30

300ohm@10 0MHz,2A

CRB 1个10uF,2个1uF,1个330uF

Max: 1.2 A

12

C362

C0805

10uf/6.3 V

+VCCSA

C132

C0805

10uf/6.3 V

10uf/6.3 V

公版5颗

C359

C0402

1uf/10V

5

C134

C143

C0805

10uf/6.3 V

0.01uF/ 16V,X7R

Max: 6A

C120

C0805

C0805

10uf/6.3 V

C153

C356

C0805

C0402

10uf/6.3 V

C139

C133

C0402

C0402

1uf/10V

1uf/10V

Check list and CRB: 10ohm

Intel check change to 100ohm

C361

C0402

C478

C0805

10uf/6.3 V

1uf/10V

C360

C0402

+VGFX

VGFXVCCSEN4 4

VGFXVSSSEN44

1uf/10V

10uF,5颗1uF,1颗330uF

C357

C355

C0402

C0402

1uf/10V

1uf/10V

C144

C0805

10uf/6.3 V

C154

C0805

10uf/6.3 V

R743 100,1%

R744 100,1%

VCCPLLVCCPLL

C479

C0805

10uf/6.3 V

C277

C0402

1uf/10V

C472

R0402

R0402

ns

10uf/6.3 V

C473

ns

10uf/6.3 V

C0805

C0805

AC61

AD47

AD48

AD50

AD51

AD52

AD53

AD55

AD56

AD58

AD59

AA46

AB47

AB50

AB51

AB52

AB53

AB55

AB56

AB58

AB59

AE46

N45

P47

P48

P50

P51

P52

P53

P55

P56

P61

T48

T58

T59

T61

U46

V47

V48

V50

V51

V52

V53

V55

V56

V58

V59

W50

W51

W52

W53

W55

W56

W61

Y48

Y61

F45

G45

BB3

BC1

BC4

L17

L21

N16

N20

N22

P17

P20

R16

R18

R21

U15

V16

V17

V18

V21

W20

4

U16G

VAXG[1]

VAXG[2]

VAXG[3]

VAXG[4]

VAXG[5]

VAXG[6]

VAXG[7]

VAXG[8]

VAXG[9]

VAXG[10]

VAXG[11]

VAXG[12]

VAXG[13]

VAXG[14]

VAXG[15]

VAXG[16]

VAXG[17]

VAXG[18]

VAXG[19]

VAXG[20]

VAXG[21]

VAXG[22]

VAXG[23]

VAXG[24]

VAXG[25]

VAXG[26]

VAXG[27]

VAXG[28]

VAXG[29]

VAXG[30]

VAXG[31]

VAXG[32]

VAXG[33]

VAXG[34]

VAXG[35]

VAXG[36]

VAXG[37]

VAXG[38]

VAXG[39]

VAXG[40]

VAXG[41]

VAXG[42]

VAXG[43]

VAXG[44]

VAXG[45]

VAXG[46]

VAXG[47]

VAXG[48]

VAXG[49]

VAXG[50]

VAXG[51]

VAXG[52]

VAXG[53]

VAXG[54]

VAXG[55]

VAXG[56]

VAXG_SENSE

VSSAXG_SENSE

VCCPLL[1]

VCCPLL[2]

VCCPLL[3]

VCCSA[1]

VCCSA[2]

VCCSA[3]

VCCSA[4]

VCCSA[5]

VCCSA[6]

VCCSA[7]

VCCSA[8]

VCCSA[9]

VCCSA[10]

VCCSA[11]

VCCSA[12]

VCCSA[13]

VCCSA[14]

VCCSA[15]

VCCSA[16]

IC,IVB_2CBGA,0P7

BGA1023_3 1X24

4

POWER

VREF

DDR3 - 1.5V RAILS

GRAPHICS

SENSE

LINES

1.8V RAIL

SA RAIL

VCCSA VID

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

VDDQ[1]

VDDQ[2]

VDDQ[3]

VDDQ[4]

VDDQ[5]

VDDQ[6]

VDDQ[7]

VDDQ[8]

VDDQ[9]

VDDQ[10]

VDDQ[11]

VDDQ[12]

VDDQ[13]

VDDQ[14]

VDDQ[15]

VDDQ[16]

VDDQ[17]

VDDQ[18]

VDDQ[19]

VDDQ[20]

VDDQ[21]

VDDQ[22]

VDDQ[23]

VDDQ[24]

VDDQ[25]

VDDQ[26]

VCCDQ[1]

VCCDQ[2]

QUIET RAILS

VDDQ_SENSE

VSS_SENSE_VDDQ

VCCSA_SENSE

SENSE LINES

VCCSA_VID[0]

VCCSA_VID[1]

lines

3

AY43

BE7

DDR_WR_VREF0 1

BG7

DDR_WR_VREF0 2

AJ28

AJ33

AJ36

AJ40

AL30

AL34

AL38

AL42

AM33

AM36

AM40

AN30

AN34

AN38

AR26

AR28

AR30

AR32

AR34

AR36

AR40

AV41

AW26

BA40

BB28

BG33

AM28

AN26

BC43

BA43

U10

D48

D49

VID0:For Sandy Bridge processor the

output will be low, for Ivy Bridge processor the output will be high.

VID1:For Chief River platforms, this

pin must have a pull down resistor to ground.

CRB 8颗10uF,10颗1uF,1颗330uF

C174

C0805

10uf/6.3 V

C474

C0805

10uf/6.3 V

0.6A

C128

C0402

1uf/10V

T79 ICTP ns

T85 ICTP ns

VCCSA_SENSE 42

VCCSA_SELECT0 4 2

VCCSA_SELECT1 4 2

+V1.5S

R282 0 R04 02

R255

100K

R0402

ns

C175

C0805

10uf/6.3 V

C475

C0805

10uf/6.3 V

C178

C0402

0.1uF/1 0V,X7R

+V1.5S

Max: 5A

C167

C0402

1uf/10V

C477

C0805

10uf/6.3 V

C166

C0402

1uf/10V

TU142 VerB: Changed 0 ohm to open point for cost down 2011-12-20

CL341 VerC: Remove the open jump 1227

C168

C0402

1uf/10V

C476

C0805

10uf/6.3 V

差异

3:VCCSA_SEL[1:0] pins enable dynamic selection

3

SM_VREF_RSM_VREF

1uf/10V

C163

C0402

+V1.5S

R270

1K,1%

R0402

R269

1K,1%

R0402

2

DDR_WR_VREF0 2

DRAMRST_CNTRL7

2

DDR_WR_VREF0 1

R731 1K

R0402

DRAMRST_CNTRL

R728 1K

ns

+V1.5 7,14,40,45

+V1.5S_CPU_VDDQ

+VCCSA 42

+VDC 2 4,37,39,40 ,41,44,47

+VGFX 44

+V1.5S 7,21,31,45

+V1.8S 20,21,40,45

ns

R0402

R729 0 R0 402

ns

3

2

Q39

L2N7002LT 1G

SOT23

1

Page Name

Page Name

Page Name

Size

Size

Size

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: th is document con tains informatio n confidentia l and prop erty to

PROPERTY NOTE: th is document con tains informatio n confidentia l and prop erty to

PROPERTY NOTE: th is document con tains informatio n confidentia l and prop erty to

TOPSTAR an d shall not b e reprodu ced or tran sferred to other docu ments or disclos ed

TOPSTAR an d shall not b e reprodu ced or tran sferred to other docu ments or disclos ed

TOPSTAR an d shall not b e reprodu ced or tran sferred to other docu ments or disclos ed

to other s or used fo r any purp ose other t han that fo r which it was obtaine d without

to other s or used fo r any purp ose other t han that fo r which it was obtaine d without

to other s or used fo r any purp ose other t han that fo r which it was obtaine d without

the expresse d written conse nt of TOPSTAR

the expresse d written conse nt of TOPSTAR

the expresse d written conse nt of TOPSTAR

R730 0

R0402

Project Name Rev

Project Name Rev

Project Name Rev

Custom

Custom

Custom

1

DDR_WR_VREF0 1_D1 14

TOPSTAR T ECHNOLOGY

TOPSTAR T ECHNOLOGY

TOPSTAR T ECHNOLOGY

Robin

Robin

Robin

Ivy Bridge VGF X/VDDQ

Ivy Bridge VGF X/VDDQ

Ivy Bridge VGF X/VDDQ

CL42 EVT

CL42 EVT

CL42 EVT

1

A

A

10 51Wednesda y, January 09, 2013

10 51Wednesda y, January 09, 2013

10 51Wednesda y, January 09, 2013

A

Page 11

5

U16H

A13

VSS [1]

A17

VSS [2]

A21

VSS [3]

A25

VSS [4]

A28

VSS [5]

A33

VSS [6]

A37

VSS [7]

D D

C C

B B

A40

A45

A49

A53

AA1

AA1 3

AA5 0

AA5 1

AA5 2

AA5 3

AA5 5

AA5 6

AA8

AB1 6

AB1 8

AB2 1

AB4 8

AB6 1

AC1 0

AC1 4

AC4 6

AC6

AD1 7

AD2 0

AD4

AD6 1

AE1 3

AE8

AF1

AF1 7

AF2 1

AF4 7

AF4 8

AF5 0

AF5 1

AF5 2

AF5 3

AF5 5

AF5 6

AF5 8

AF5 9

AG1 0

AG1 4

AG1 8

AG4 7

AG5 2

AG6 1

AG7

AH4

AH58

AJ1 3

AJ1 6

AJ2 0

AJ2 2

AJ2 6

AJ3 0

AJ3 4

AJ3 8

AJ4 2

AJ4 5

AJ4 8

AJ7

AK1

AK5 2

AL1 0

AL1 3

AL1 7

AL2 1

AL2 5

AL2 8

AL3 3

AL3 6

AL4 0

AL4 3

AL4 7

AL6 1

AM13

AM20

AM22

AM26

AM30

AM34

VSS [8]

VSS [9]

VSS [10]

VSS [11]

A9

VSS [12]

VSS [13]

VSS [14]

VSS [15]

VSS [16]

VSS [17]

VSS [18]

VSS [19]

VSS [20]

VSS [21]

VSS [22]

VSS [23]

VSS [24]

VSS [25]

VSS [26]

VSS [27]

VSS [28]

VSS [29]

VSS [30]

VSS [31]

VSS [32]

VSS [33]

VSS [34]

VSS [35]

VSS [36]

VSS [37]

VSS [38]

VSS [39]

VSS [40]

VSS [41]

VSS [42]

VSS [43]

VSS [44]

VSS [45]

VSS [46]

VSS [47]

VSS [48]

VSS [49]

VSS [50]

VSS [51]

VSS [52]

VSS [53]

VSS [54]

VSS [55]

VSS [56]

VSS [57]

VSS [58]

VSS [59]

VSS [60]

VSS [61]

VSS [62]

VSS [63]

VSS [64]

VSS [65]

VSS [66]

VSS [67]

VSS [68]

VSS [69]

VSS [70]

VSS [71]

VSS [72]

VSS [73]

VSS [74]

VSS [75]

VSS [76]

VSS [77]

VSS [78]

VSS [79]

VSS [80]

VSS [81]

VSS [82]

VSS [83]

VSS [84]

VSS [85]

VSS [86]

VSS [87]

VSS [88]

VSS [89]

VSS [90]

4

VSS

VSS [91]

VSS [92]

VSS [93]

VSS [94]

VSS [95]

VSS [96]

VSS [97]

VSS [98]

VSS [99]

VSS [100]

VSS [101]

VSS [102]

VSS [103]

VSS [104]

VSS [105]

VSS [106]

VSS [107]

VSS [108]

VSS [109]

VSS [110]

VSS [111]

VSS [112]

VSS [113]

VSS [114]

VSS [115]

VSS [116]

VSS [117]

VSS [118]

VSS [119]

VSS [120]

VSS [121]

VSS [122]

VSS [123]

VSS [124]

VSS [125]

VSS [126]

VSS [127]

VSS [128]

VSS [129]

VSS [130]

VSS [131]

VSS [132]

VSS [133]

VSS [134]

VSS [135]

VSS [136]

VSS [137]

VSS [138]

VSS [139]

VSS [140]

VSS [141]

VSS [142]

VSS [143]

VSS [144]

VSS [145]

VSS [146]

VSS [147]

VSS [148]

VSS [149]

VSS [150]

VSS [151]

VSS [152]

VSS [153]

VSS [154]

VSS [155]

VSS [156]

VSS [157]

VSS [158]

VSS [159]

VSS [160]

VSS [161]

VSS [162]

VSS [163]

VSS [164]

VSS [165]

VSS [166]

VSS [167]

VSS [168]

VSS [169]

VSS [170]

VSS [171]

VSS [172]

VSS [173]

VSS [174]

VSS [175]

VSS [176]

VSS [177]

VSS [178]

VSS [179]

VSS [180]

AM38

AM4

AM42

AM45

AM48

AM58

AN1

AN21

AN25

AN28

AN33

AN36

AN40

AN43

AN47

AN50

AN54

AP1 0

AP5 1

AP5 5

AP7

AR1 3

AR1 7

AR2 1

AR4 1

AR4 8

AR6 1

AR7

AT1 4

AT1 9

AT3 6

AT4

AT4 5

AT5 2

AT5 8

AU1

AU11

AU28

AU32

AU51

AU7

AV1 7

AV2 1

AV2 2

AV3 4

AV4 0

AV4 8

AV5 5

AW 13

AW 43

AW 61

AW 7

AY14

AY19

AY30

AY36

AY4

AY41

AY45

AY49

AY55

AY58

AY9

BA1

BA1 1

BA1 7

BA2 1

BA2 6

BA3 2

BA4 8

BA5 1

BB5 3

BC1 3

BC5

BC5 7

BD1 2

BD1 6

BD1 9

BD2 3

BD2 7

BD3 2

BD3 6

BD4 0

BD4 4

BD4 8

BD5 2

BD5 6

BD8

BE5

BG1 3

3

U16I

BG1 7

VSS [181]

BG2 1

VSS [182]

BG2 4

VSS [183]

BG2 8

VSS [184]

BG3 7

VSS [185]

BG4 1

VSS [186]

BG4 5

VSS [187]

BG4 9

VSS [188]

BG5 3

VSS [189]

BG9

VSS [190]

C29

VSS [191]

C35

VSS [192]

C40

VSS [193]

D10

VSS [194]

D14

VSS [195]

D18

VSS [196]

D22

VSS [197]

D26

VSS [198]

D29

VSS [199]

D35

VSS [200]

D4

VSS [201]

D40

VSS [202]

D43

VSS [203]

D46

VSS [204]

D50

VSS [205]

D54

VSS [206]

D58

VSS [207]

D6

VSS [208]

E25

VSS [209]

E29

VSS [210]

E3

VSS [211]

E35

VSS [212]

E40

VSS [213]

F13

VSS [214]

F15

VSS [215]

F19

VSS [216]

F29

VSS [217]

F35

VSS [218]

F40

VSS [219]

F55

VSS [220]

G51

VSS [221]

G6

VSS [222]

G61

VSS [223]

H10

VSS [224]

H14

VSS [225]

H17

VSS [226]

H21

VSS [227]

H4

VSS [228]

H53

VSS [229]

H58

VSS [230]

J1

VSS [231]

J49

VSS [232]

J55

VSS [233]

K11

VSS [234]

K21

VSS [235]

K51

VSS [236]

K8

VSS [237]

L16

VSS [238]

L20

VSS [239]

L22

VSS [240]

L26

VSS [241]

L30

VSS [242]

L34

VSS [243]

L38

VSS [244]

L43

VSS [245]

L48

VSS [246]

L61

VSS [247]

M11

VSS [248]

M15

VSS [249]

IC,IVB_2CBGA,0P7

BGA1023_31X24

VSS

NCTF

VSS [250]

VSS [251]

VSS [252]

VSS [253]

VSS [254]

VSS [255]

VSS [256]

VSS [257]

VSS [258]

VSS [259]

VSS [260]

VSS [261]

VSS [262]

VSS [263]

VSS [264]

VSS [265]

VSS [266]

VSS [267]

VSS [268]

VSS [269]

VSS [270]

VSS [271]

VSS [272]

VSS [273]

VSS [274]

VSS [275]

VSS [276]

VSS [277]

VSS [278]

VSS [279]

VSS [280]

VSS [281]

VSS [282]

VSS [283]

VSS [284]

VSS [285]

VSS [286]

VSS [287]

VSS [288]

VSS [289]

VSS [290]

VSS [291]

VSS [292]

VSS [293]

VSS [294]

VSS [295]

VSS [296]

VSS [297]

VSS [298]

VSS [299]

VSS [300]

VSS _NCTF_1

VSS _NCTF_2

VSS _NCTF_3

VSS _NCTF_4

VSS _NCTF_5

VSS _NCTF_6

VSS _NCTF_7

VSS _NCTF_8

VSS _NCTF_9

VSS _NCTF_1 0

VSS _NCTF_1 1

VSS _NCTF_1 2

VSS _NCTF_1 3

VSS _NCTF_1 4

2

M4

M58

M6

N1

N17

N21

N25

N28

N33

N36

N40

N43

N47

N48

N51

N52

N56

N61

P14

P16

P18

P21

P58

P59

P9

R17

R20

R4

R46

T1

T47

T50

T51

T52

T53

T55

T56

U13

U8

V20

V61

W1 3

W1 5

W1 8

W2 1

W4 6

W8

Y4

Y47

Y58

Y59

A5

A57

BC6 1

BD3

BD5 9

BE4

BE5 8

BG5

BG5 7

C3

C58

D59

E1

E61

1

A A

5

IC,IVB_2CBGA,0P7

BGA1023_31X24

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

4

3

2

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Robin

Robin

Robin

Ivy Bridge GND

Ivy Bridge GND

Ivy Bridge GND

CL42 EVT

CL42 EVT

CL42 EVT

1

A

A

11 51Wednesday, January 09, 2013

11 51Wednesday, January 09, 2013

11 51Wednesday, January 09, 2013

A

Page 12

5

4

3

2

1

U16E

B50

CFG[0]

C51

CFG[1]

B54

CFG[2]

D53

CFG[3]

A51

D D

C C

BRACKET1

CPU_HOLE

ASSY

B B

1122334455667788991010111112121313141415151616171718181919202021212222232324242525262627272828292930303131323233333434353536

36

A A

5

4

CFG[4]

C53

CFG[5]

C55

CFG[6]

H49

CFG[7]

A55

CFG[8]

H51

CFG[9]

K49

CFG[10]

K53

CFG[11]

F53

CFG[12]

G53

CFG[13]

L51

CFG[14]

F51

CFG[15]

D52

CFG[16]

L53

CFG[17]

H43

VCC_VAL_SENSE

K43

VSS_VAL_SENSE

H45

VAXG_VAL_SENSE

K45

VSSAXG_VAL_SENSE

F48

VCC_DIE_SENSE

G48

RSVD47

H48

RSVD6

K48

RSVD7

BA19

RSVD8

AV19

RSVD9

AT21

RSVD10

BB21

RSVD11

BB19

RSVD12

AY21

RSVD13

BA22

RSVD14

AY22

RSVD15

AU19

RSVD16

AU21

RSVD17

BD21

RSVD18

BD22

RSVD19

BD25

RSVD20

BD26

RSVD21

BG22

RSVD22

BE22

RSVD23

BG26

RSVD24

BE26

RSVD25

BF23

RSVD26

BE24

RSVD27

IC,IVB_2CBGA,0P7

BGA1023_31X24

RESERVED

3

BCLK_ITP

BCLK_ITP#

RSVD30

RSVD31

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD37

RSVD38

RSVD39

RSVD40

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

DC_TEST_A4

DC_TEST_C4

DC_TEST_D3

DC_TEST_D1

DC_TEST_A58

DC_TEST_A59

DC_TEST_C59

DC_TEST_A61

DC_TEST_C61

DC_TEST_D61

DC_TEST_BD61

DC_TEST_BE61

DC_TEST_BE59

DC_TEST_BG61

DC_TEST_BG59

DC_TEST_BG58

DC_TEST_BG4

DC_TEST_BG3

DC_TEST_BE3

DC_TEST_BG1

DC_TEST_BE1

DC_TEST_BD1

N59

ns

N58

N42

L42

L45

L47

M13

M14

U14

W14

P13

AT49

K24

AH2

AG13

AM14

AM15

T70

T71

ICTP

ICTP

ns

N50

A4

DC_TEST_A4

C4

D3

DC_TEST_C4_D3

D1

DC_TEST_D1

A58

DC_TEST_A58

A59

C59

DC_TEST_A59_C59

A61

C61

DC_TEST_A61_C61

D61

DC_TEST_D61

BD61

DC_TEST_BD61

BE61

BE59

DC_TEST_BE59_BE61

BG61

BG59

DC_TEST_BG59_BG61

BG58

DC_TEST_BG58

BG4

DC_TEST_BG4

BG3

BE3

DC_TEST_BE3_BG3

BG1

BE1

DC_TEST_BE1_BG1

BD1

DC_TEST_BD1

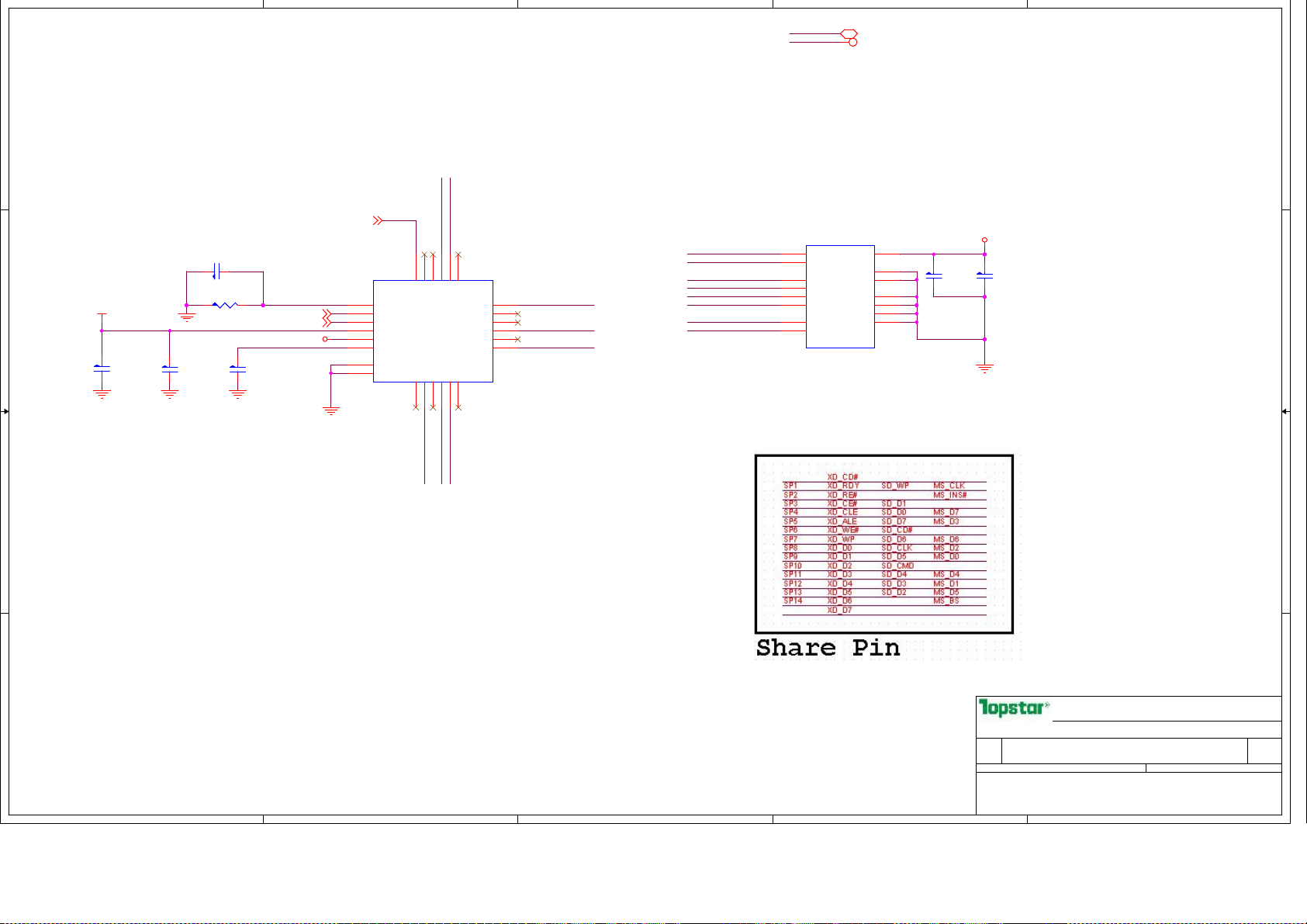

Daisy Chain, for solder joint reliability

and non-critical to function. BGA only.

Followed CRB connection.

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

Robin

Robin

Robin

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A4

A4

A4

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

2

Ivy Bridge Reserved

Ivy Bridge Reserved

Ivy Bridge Reserved

CL42 EVT

CL42 EVT

CL42 EVT

12 51Wednesday, January 09, 2013

12 51Wednesday, January 09, 2013

12 51Wednesday, January 09, 2013

1

A

A

A

Page 13

5

D D

C C

4

3

2

1

B B

A A

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

5

4

3

2

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

杨华明

(Sky Yang)

杨华明

(Sky Yang)

杨华明

(Sky Yang)

DDR3 CHA SODIMM0

DDR3 CHA SODIMM0

DDR3 CHA SODIMM0

CL42 EVT

CL42 EVT

CL42 EVT

1

A

A

13 51Wednesday, January 09, 2013

13 51Wednesday, January 09, 2013

13 51Wednesday, January 09, 2013

A

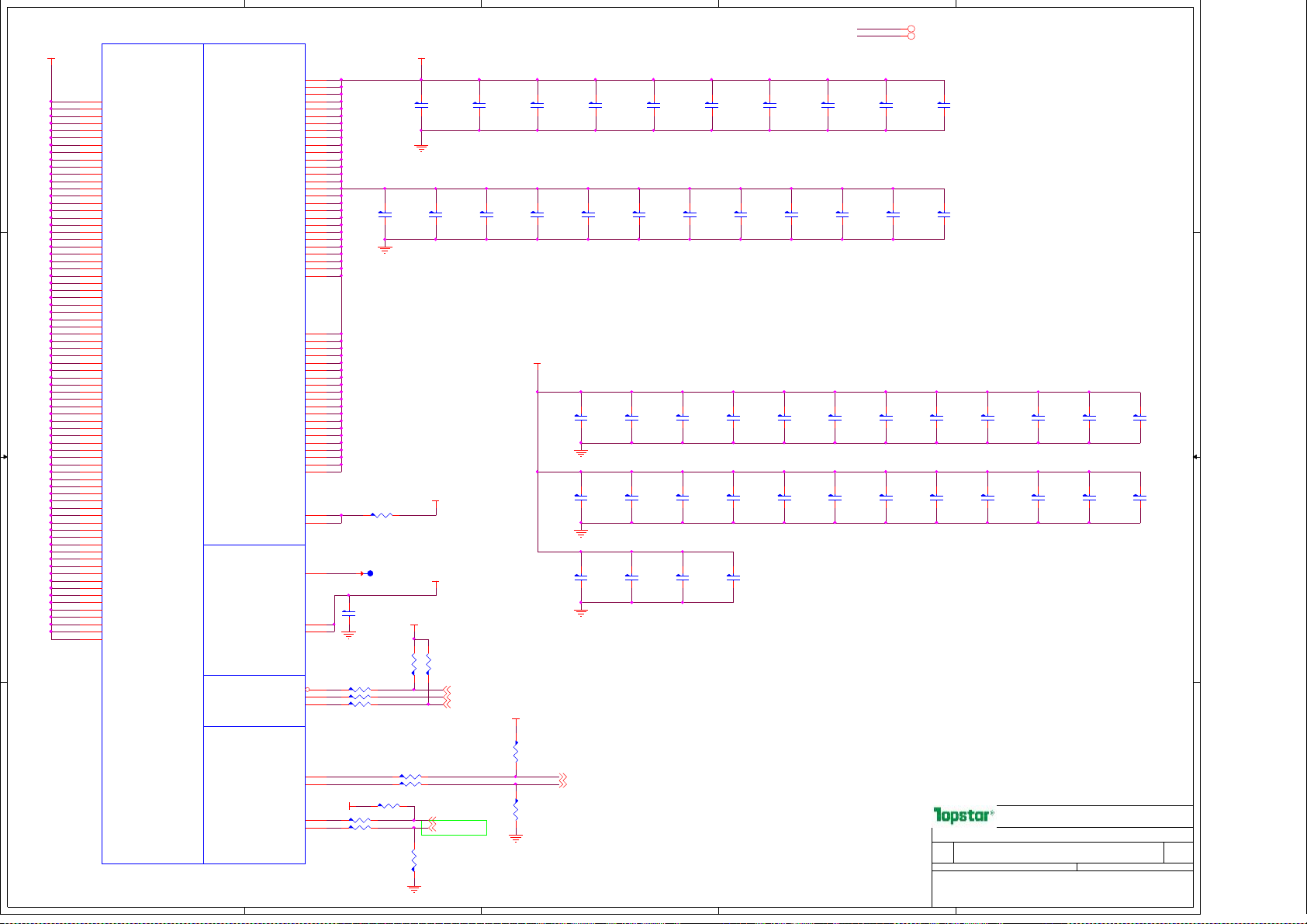

Page 14

+V1.5

5

4

3

2

+V3.3S 7,15,16,17,18,19,20,21,22,24,25,29,30,31,32,33,34,35,40,41,42,43,44,45,47

+V1.5 7,40,45

+V0.75S 40,45

1

2.2uf/10V

2.2uf/10V

1uf/10V

+V1.5

C217

C0603

C218

C0603

ns

C193

C0402

R303

1K,1%

R0402

C192

C0402

0.1UF/10V,X7R

ns

公版6颗

10uF,1颗330uF,4颗1uF

C216

C0402

0.1UF/10V,X7R

电容靠近

C227

C0402

1uf/10V

2.2uf/10V

2.2uf/10V

DDR slot VDD PIN

1uf/10V

C237

C0805

10uf/6.3V

D D

+V1.5

C235

C0402

0.1UF/10V,X7R

C C

B B

Layout note:

+V0.75S

C198

C0402

1uf/10V

C242

C0603

C220

C0603

C224

C0402

C241

C0603

2.2uf/10V

C184

C0603

2.2uf/10V

ns

+V1.5

VREFB_CA

R312

1K,1%

R0402

R310

1K,1%

R0402

C187

C0402

0.1UF/10V,X7R

ns

C234

C0402

0.1UF/10V,X7R

ns

DDR_WR_VREF01_D1

C238

C0603

2.2uf/10V

C214

C0603

2.2uf/10V

ns

C239

C0603

2.2uf/10V

C215

C0603

2.2uf/10V

C228

C0402

0.1UF/10V,X7R

+V3.3S

C236

C0402

0.1UF/10V,X7R

C203

10uf/6.3V

C0805

C226

C0603

2.2uf/10V

C219

10uf/6.3V

C0805

DDR_WR_VREF01_D110

MB_B_A[15:0]8

MB_B_BS08

MB_B_BS18

MB_B_BS28

M_CS#28

M_CS#38

MB_B_WE#8

MB_B_CAS#8

MB_B_RAS#8

M_CKE28

M_CKE38

M_CLK_DDR28

M_CLK_DDR#28

M_CLK_DDR38

M_CLK_DDR#38

M_ODT28

M_ODT38

MB_DQS[7:0]8

SMB_DATA_S16

SMB_CLK_S16

R318 10K R0402

R316 10K R0402

Note:

SO-DIMM1 SPD Address is 0xA4

C230

C0402

0.1UF/10V,X7R

DDR3_DRAMRST#7

C229

C0603

2.2uf/10V

MB_B_A0

MB_B_A1

MB_B_A2

MB_B_A3

MB_B_A4

MB_B_A5

MB_B_A6

MB_B_A7

MB_B_A8

MB_B_A9

MB_B_A10

MB_B_A11

MB_B_A12

MB_B_A13

MB_B_A14

MB_B_A15

MB_DQS0

MB_DQS1

MB_DQS2

MB_DQS3

MB_DQS4

MB_DQS5

MB_DQS6

MB_DQS7

VREFB_CA

+V1.5+V0.75S

203

204

VTT1

VTT2

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10 /AP

84

A11

83

A12 /BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

114

CS0

121

CS1

11

DQM0

28

DQM1

46

DQM2

63

DQM3

136

DQM4

153

DQM5

170

DQM6

187

DQM7

113

WE

115

CAS

110

RAS

73

CKE 0

74

CKE 1

101

CK0

103

CK0

102

CK1

104

CK1

116

ODT 0

120

ODT 1

12

DQS 0

29

DQS 1

47

DQS 2

64

DQS 3

137

DQS 4

154

DQS 5

171

DQS 6

188

DQS 7

200

SDA

202

SCL

197

SA0

201

SA1

199

VDD SPD

1

VRE F_DQ

126

VRE F_CA

198

EVE NT#

30

RES ET#

77

NC1

122

NC2

125

NCTE ST

DDR3_SODIMM204_0

99

100

105

106

111

112

117

118

VDD175VDD276VDD381VDD482VDD587VDD688VDD793VDD894VDD9

VSS23VSS38VSS49VSS513VSS614VSS719VSS820VSS925VSS1026VSS1131VSS1232VSS1337VSS1438VSS1543VSS1644VSS1748VSS1849VSS1954VSS2055VSS2160VSS2261VSS2365VSS2466VSS2571VSS2672VSS27

VSS1

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

151

145

150

123

VDD16

155

124

VSS36

VSS34

VSS35

VDD17

VDD18

2

156

161

162

167

168

172

173

178

179

184

185

189

190

195

196

DIMM1

5

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D60

D61

D62

D63

DQS #0

DQS #1

DQS #2

DQS #3

DQS #4

DQS #5

DQS #6

DQS #7

VSS29

VSS30

VSS31

VSS32

VSS28

VSS33

GND1

GND2

127

133

134

138

139

128

144

205

206

MB_DATA0

VSS52

7

MB_DATA1

15

MB_DATA2

17

MB_DATA3

4

MB_DATA4

6

MB_DATA5

16

MB_DATA6

18

MB_DATA7

21

MB_DATA8

23

MB_DATA9

33

MB_DATA10

35

MB_DATA11

22

MB_DATA12

24

MB_DATA13

34

MB_DATA14

36

MB_DATA15

39

MB_DATA16

41

MB_DATA17

51

MB_DATA18

53

MB_DATA19

40

MB_DATA20

42

MB_DATA21

50

MB_DATA22

52

MB_DATA23

57

MB_DATA24

59

MB_DATA25

67

MB_DATA26

69

MB_DATA27

56

MB_DATA28

58

MB_DATA29

68

MB_DATA30

70

MB_DATA31

129

MB_DATA32

131

MB_DATA33

141

MB_DATA34

143

MB_DATA35

130

MB_DATA36

132

MB_DATA37

140

MB_DATA38

142

MB_DATA39

147

MB_DATA40

149

MB_DATA41

157

MB_DATA42

159

MB_DATA43

146

MB_DATA44

148

MB_DATA45

158

MB_DATA46

160

MB_DATA47

163

MB_DATA48

165

MB_DATA49

175

MB_DATA50

177

MB_DATA51

164

MB_DATA52

166

MB_DATA53

174

MB_DATA54

176

MB_DATA55

181

MB_DATA56

183

MB_DATA57

191

MB_DATA58

193

MB_DATA59

180

MB_DATA60

182

MB_DATA61

192

MB_DATA62

194

MB_DATA63

10

MB_DQS#0

27

MB_DQS#1

45

MB_DQS#2

62

MB_DQS#3

135

MB_DQS#4

152

MB_DQS#5

169

MB_DQS#6

186

MB_DQS#7

MB_DATA[63:0] 8

MB_DQS#[7:0] 8

R302

A A

1K,1%

R0402

5

C213

C0402

0.1UF/10V,X7R

C222

C0603

2.2uf/10V

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

TOPSTAR TECHNOLOGY

杨华明

(Sky Yang)

杨华明

(Sky Yang)

杨华明

Page Name

Page Name

Page Name

Size

Size

Size

Project Name Rev

Project Name Rev

Project Name Rev

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

PROPERTY NOTE: this document contains information confidential and property to

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

TOPSTAR and shall not be reproduced or transferred to other documents or disclosed

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

to others or used for any purpose other than that for which it was obtained without

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

the expressed written consent of TOPSTAR

4

3

2

(Sky Yang)

DDR3 CHB SODIMM0

DDR3 CHB SODIMM0

DDR3 CHB SODIMM0

CL42 EVT

CL42 EVT

CL42 EVT

1

A

A

14 51Wednesday, January 09, 2013

14 51Wednesday, January 09, 2013

14 51Wednesday, January 09, 2013

A

Page 15

5

EC_RTC

D D

3

1

3

1

2

2

4

RTCCN1

4

Wafer

CNS2_V

HDA_SYNC:On-Die PLL Voltage Regulator Voltage Select

(Internal pull down 20K)

Low: 1.8V

High: 1.5V(Default)

C C

AZALIA_CODEC_SYNC29

VerC:HDA_SDO:

B B

A A

增加对声卡芯片的隔离电路,防止刷写ME是EC无法在S5下将

AZALIA_CODEC_SDOUT29

R0402

R334

1K

R0402

+V3.3S

R442

R0402

0

KB3930

D1

LBAT54CLT1G

sot23

1

3

2

+V3.3S

R706

1K

R0402

ns

R707 33 R0402

R708

1M

R0402

+V3.3S

R716

1K

R0402

R717 33 R0402

+V3.3SB

R440

R0402

0

KB9010

R444 10K R0402 ns

R447 3.3K R0402

R439 3.3K R0402

R718

1M

R0402

ns

R22

1M

R0402

8

3

7

PCH_EC_RTC

R24 20K R0402

R26 20K R0402

R705 0

Q36

L2N7002LT1G

2

+V5S

1

ME_LOCK#

+V5S

U13

VDD

CE#

WP #

SCK

HOLD#

VSS

W25Q32BVSSIG

SOIC8_50_208

C294

1uf/10V

C0402

C17

1uf/10V

C0402

nsR0402

3

SOT23

拉高

R715 0

Q37

L2N7002LT1G

2

SOT23