Calogic LLC DPAD50, DPAD5, DPAD20, DPAD2, DPAD100 Datasheet

...

Dual Pico Amp Diodes

DP AD1 / DPAD2 / DP AD5 / DP AD10 / DPAD2 0 / DPAD50 / DP AD100

SSTDP AD5 / SSTDP AD10 / SSTDP AD20 / SSTDP AD50 / SSTDP AD100

FEAT URES

••

High OFF Isolation. . . . . . . . . . . . . . . . . 1 pA max DP AD1

••

Excellent Isolation between diodes. . . . . . Typical 20 fA

••

Matched Capacitance

APPLICATIONS

••

Op Amp Protection Devices

••

Diode Switching

••

High Impeda nce Pr o tec tion

DESCRIPTION

Calogic’s ultra low leakage dual pico amp diodes out perform

conventional diodes for applications where reverse current

(leakage) is critical and must be kept at a minimum. The

devices have very low capacitance and are also fast

switching. Housed in a compact dual hermetic package and a

plastic surface mount SO-8 this product is also available in

chip form for h ybrid us es .

ORDERING INFORMATION

Part Package Tempe rature Range

DP AD1 Hermetic T O-78 -55 to +150

o

C

DP AD2 /50 Hermetic T O-71 -55 to +150

o

C

SSTDPAD5/100 Plastic SO-8 -55 to +150

o

C

XDPAD5/100 Sorted Chips in Carriers -55 to +150

o

C

CORPORATION

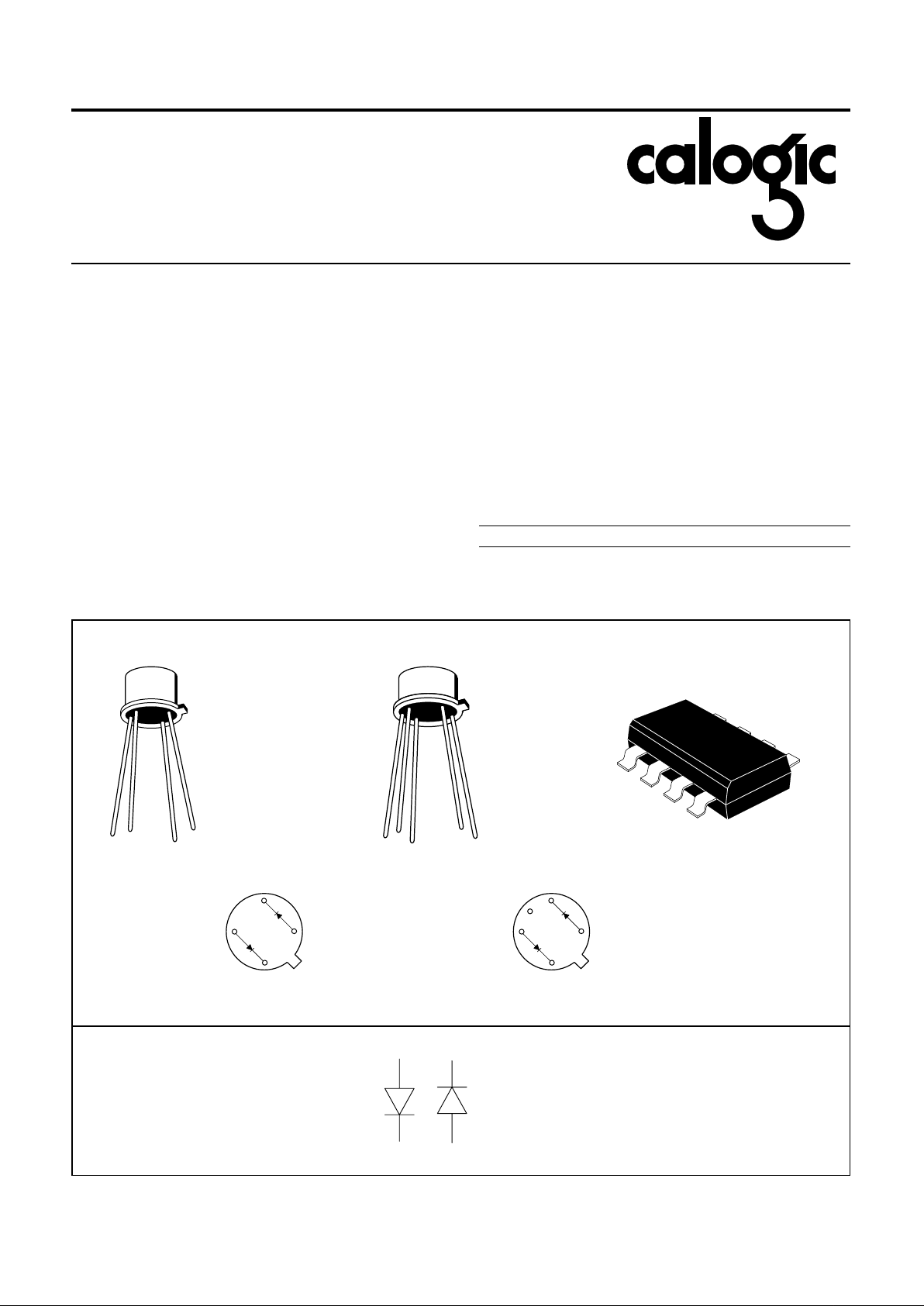

SCHEMATIC DIAGRAM

TO-71

(MODIFIED)

(PINS 2 AND

6 REMOVED)

A

1

A

2

C

2

C

1

C

C

1

C

2

A

1

A

2

TO-78

(MODIFIED)

(DPAD1 ONLY)

A

C

A

C

BOTTOM VIEW

(ALTERNATE)

1

A

1

C

1

A

2

C

2

2

3

4

1

A

1

C

1

A

2

C

2

C

BOTTOM VIEW

CASE

2

5

4

3

PIN CONFIGU RATION

SO-8

C1

A1

N/C

C2

A2

C1

N/C

C2

CJ1, CJ2, CJ4

DPAD1 / DPAD2 / DPAD5 / DPAD10 / DPAD20 / DPAD50 / DPAD100

SSTDPAD5 / SSTDP AD10 / SSTDPAD 20 / SSTDPAD50 / SSTDPAD 100

CORPORATION

ABSOLUTE MAXIMUM RATINGS (25oC)

Forward Gate Current, Each Side. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 mA

Total De vice Dissipat ion @ T

A

= 25oC

Derate 4.0 mW/

o

C to 125oC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400 mW

Storage Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -55 to +125

o

C

Lead Temperature (1/16" from case f or 1 0 seconds ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

o

C

ELECTRICAL CHARACTERI STICS (25

o

C unless otherwise noted )

SYMBOL CHARACTERISTICS MIN TYP MAX UNIT TEST CONDITIONS

STATIC

I

R

Reverse Current

-1

pA VR = -20 V

DPAD1

-2 DPAD2

-5 DPAD5

-10 DPAD10

-20 DPAD20

-50 DPAD50

-100 DPAD100

BV

R

Breakdown Voltage (Reverse)

-45 -120

V

I

R

= -1µA

DPAD1, 2, 5

-35 DPAD10, 20, 50, 100

V

F

Forward Voltage Drop 0.8 1.5 IF = 5 mA DPAD1, 2, 5, 10, 20, 50, 100

DYNAMIC

C

R

Capacitance

0.8

pF VR = -5 V, f = 1 MHz

DPAD1, 2, 5

2.0 DP AD10, 20, 50, 100

| CR1 - CR2 | Differential Capacitance 0.1 0.2 pF V

R1

= VR2 = -5 V, f = 1 MHz DPAD1, 2, 5, 10, 20, 50, 100

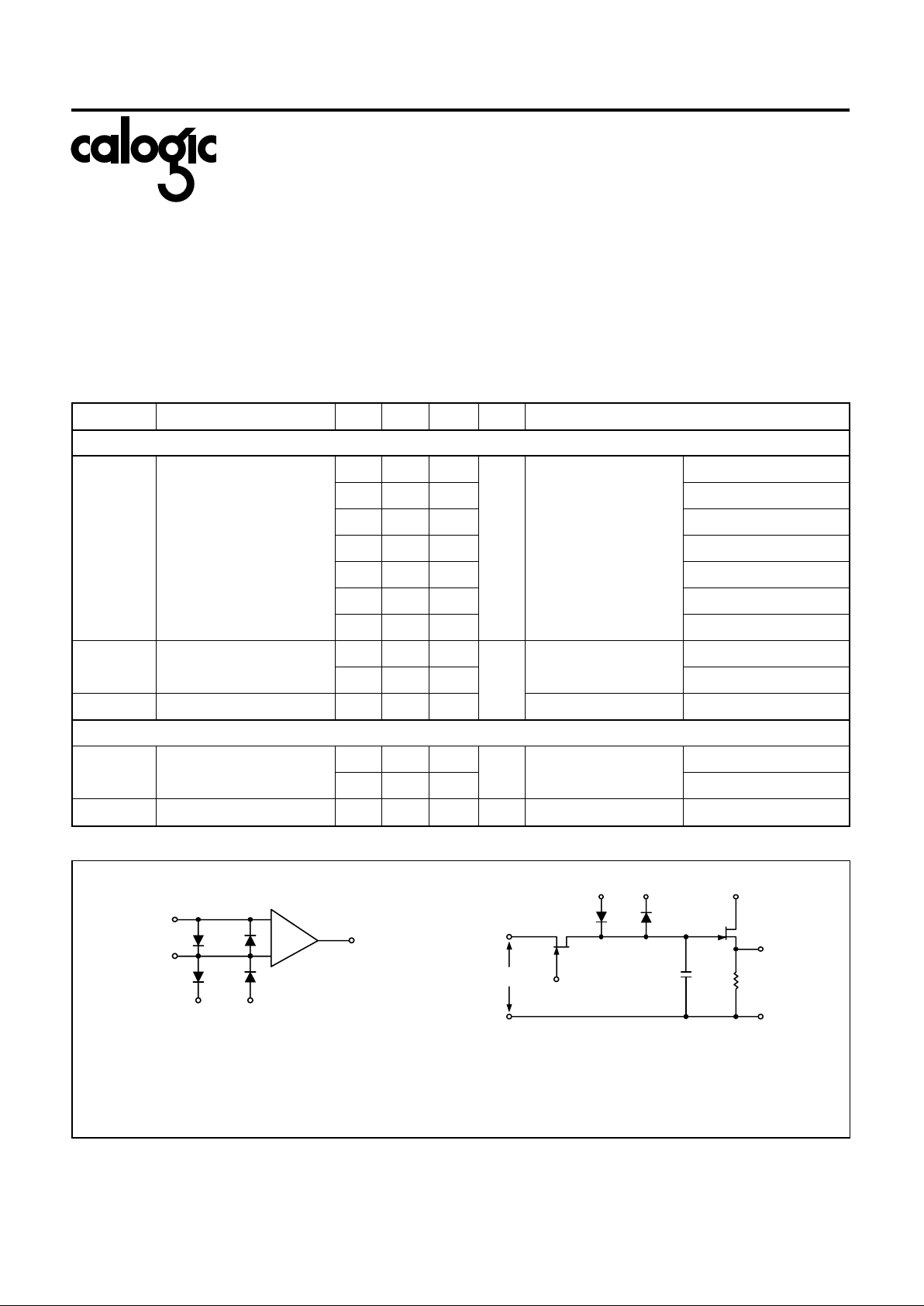

APPLICATION

Operational Amplifier Protection. Input Differential Voltage

limited to 0.8 V (typ) by DPADS D

1

and D2 Common mode

input voltage limit ed by D PADS D

3

and D4 to ±15V.

Typical sample and hold circuit with clipping, DPAD diodes

reduce offset voltages fed capacitively from the FET switch

gate.

DPAD10

D

1

D

4

+

1

-15V

+15V

_

D

2

D

3

I < 1 pA

R

+V

-V

DPAD1

V

OUT

C

CONTROL SIGNAL

e

in

+

DPAD1

J110

J210

Loading...

Loading...