Calogic SST5912 Datasheet

N-Channel JFET

Monolithic Dual

SST5912

CORPORATION

FEATURES

High Gain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . gfs > 6 mS

••

Low Leakage . . . . . . . . . . . . . . . . . . . . . . IG < 1pA typical

••

Low Noise

••

Surface Mou nt Package

••

APPLICATIONS

Differential Wi de band Amplifier

••

VHF/UHF Amplifie rs

••

T est and Measu rement

••

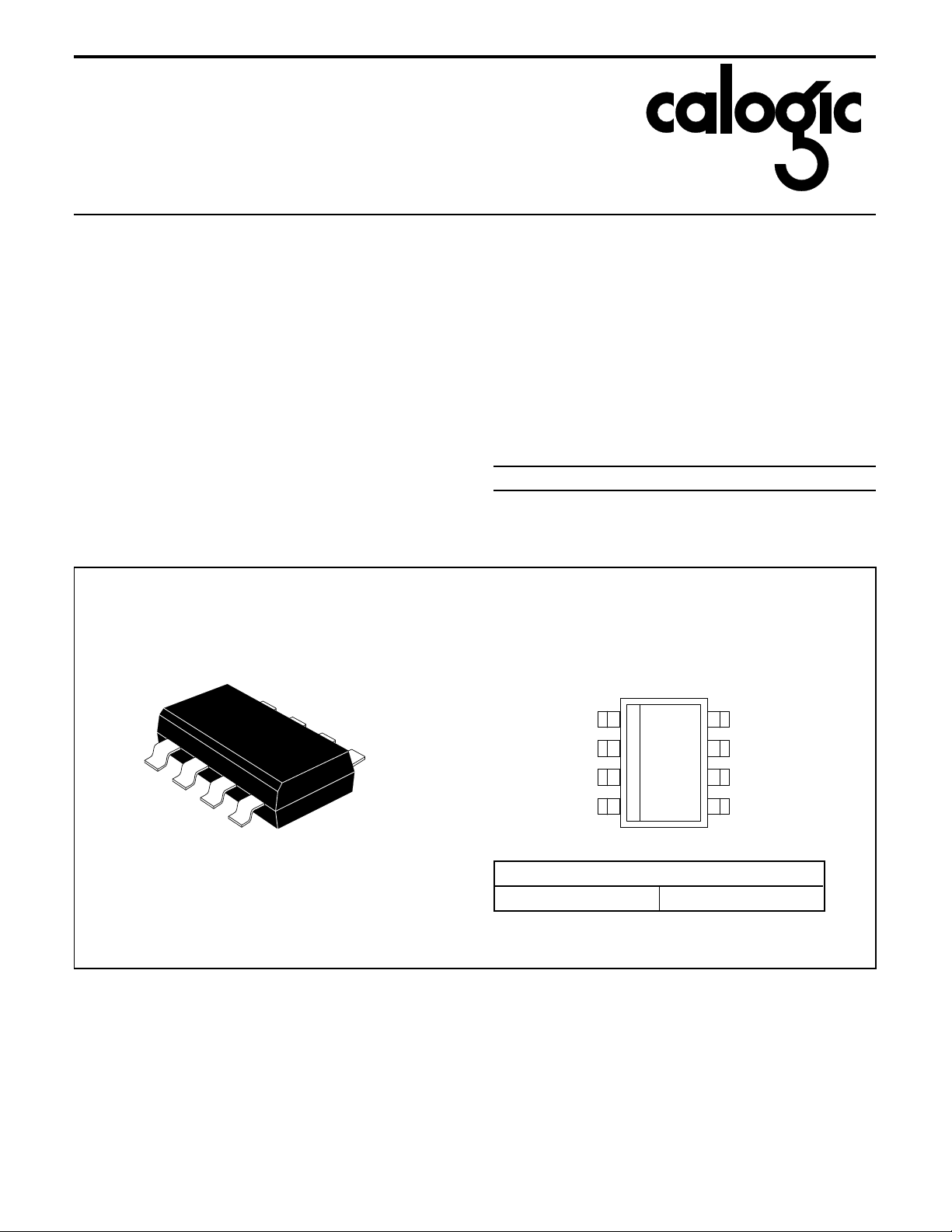

PIN CONFIGU R ATI O N

SO-8

DESCRIPTION

The SST5912 is a High Speed N-Channel Monolithic JFET

pair encapsulated in a surface mount plastic SO-8 package.

The device is designed for high gain (typically > 6000

mmhos), low leakage ( < 1pA typically) and low noise, The

SST5912 is an excellent choice for differential wideband

amplifiers, VHF/UHF amp lif iers and test and measur em e nt.

ORDERING INFORMATION

Part Package Temperature Range

o

SST5912 Plastic SO-8 Package -55

NOTE: For Sorted Chips in Carriers, See 2N5911 Series

TOP VIEW

(1) S1

(2) D1

C to +150oC

N/C (8)

G2 (7)

CJ1

(3) G1

(4) N/C

PRODUCT MARKING

SST5912 SST5912

D2 (6)

S2 (5)

SST5912

CORPORATION

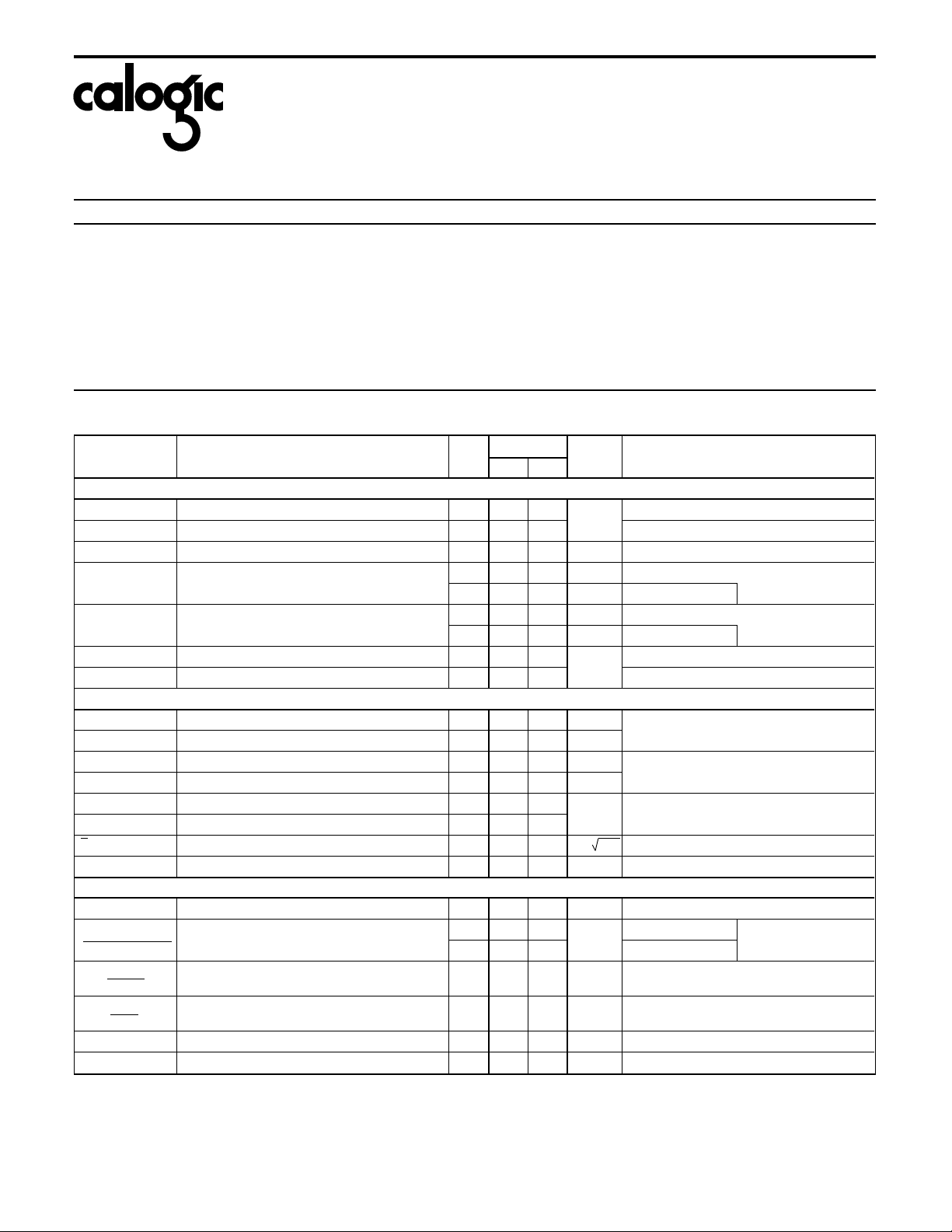

ABSOLUTE MAXIMUM RATINGS (TA = 25oC unless otherwise noted)

Parameter/Test Conditio n Symbol Limit Unit

Gate-Drain Voltage V

Gate-Source Voltage V

Forward Gate Cur r ent I

Power Dissipation (per side) P

GD

GS

G

D

(total) 500 mW

Power Derating (per side) 2.4 mW/

(total) 4 mW/

Operating J unct ion Temper at ur e T

Storage Tempera ture T

Lead Temperature (1/ 16 " fr om case for 10 seconds) T

J

stg

L

ELECTRICAL CHARACTERISTIC S (TA = 25oC unless otherwise note d)

SST5912

SYMBOL CHARACTERISTCS TYP

STATIC

V

(BR)GSS

) Gate-Source Cut off Voltage -3.5 -1 -5 VDS = 10V, ID = 1nA

V

GS(OFF

I

DSS

I

GSS

I

G

V

GS

V

GS(F)

Gate-Source Breakdown Voltage -35 -25

Saturation Drain Current

2

Gate Reverse Current

Gate Operating Current

Gate-Source Voltage -1.5 -0.3 -4

Gate-Source Forward Voltage 0 .7 IG = 1mA, VDS = 0V

DYNAMIC

g

fs

g

os

g

fs

g

os

C

iss

C

rss

e

n

Common-Source Forward Transconductance 6 5 10 mS

Common-Source Output Conductance 20 100 mS

Common-Source Forward Transconductance 6 5 10 mS

Common-Source Output Conductance 30 150 mS

Common-Source Input Capacitance 3.5 5

Common-Sourc e Revers e T rans f er Capac it anc e 1 1.2

Equivale nt Inp ut Noise Voltage 4 20 nV/ Hz VDG = 10V, ID = 5mA, f = 10kHz

NF Noise Figure 0.1 1 dB V

MATCHING

- V

| V

D | V

GS1

GS1

| Differential Gate Source Voltage 7 15 mV VDG = 10V, ID = 5mA

GS2

- V

|DTGate Source Voltage Differential Change with

GS2

Temperature

I

DSS1

I

DSS2

g

fs1

g

fs2

| I

- I

G1

G2

Saturation Drain Curre nt Rati o 0.98 0.95 1 VDS = 10V, VGS = 0V

Transconductance Ratio 0.98 0.95 1 VDG = 10V, ID = 5mA, f = 1kHz

| Differential Gate Current 0.01 20 nA VDG = 10V, ID = 5mA, TA = 125oC

CMRR Common Mode Rejection Ratio 90 dB V

NOTES: 1. For design aid only, not subject to production testing.

2. Pulse test; PW = 300ms, duty cycle â 3%.

1

MIN MAX

UNIT TEST CONDITIONS

V

15 7 40 mA VDS = 10V, VGS = 0V

-1 -100 pA V

-0.2 nA T

-1 -100 pA V

-0.2 nA T

V

pF

10 40

10 40 T = 25 to 125

mV/

o

-25 V

-25 V

50 mA

300 mW

-55 to 150

-65 to 150

300

IG = -1mA, VDS = 0V

= -15V, VDS = 0V

GS

= 125oC

A

= 10V, ID = 5mA

DG

= 125oC

A

VDG = 10V, ID = 5mA

V

= 10V, ID = 5mA

DG

f = 1kHz

V

= 10V, ID = 5mA

DG

f = 100MHz

V

= 10V, ID = 5mA

DG

f = 1MHz

= 10V, ID = 5mA, f = 10kHz, RG = 100W

DG

T = -55 to 25

C

= 5 to 10V, ID = 5mA

DD

o

C

V

= 10V

o

DG

I

= 5mA

D

C

o

C

o

C

o

C

o

C

o

C

Loading...

Loading...