California Micro Devices SN74S1051 Datasheet

CALIFORNIA MICRO DEVICES

D01

2

D06

7

D02

3

D07

10

D03

4

D08

11

D04

5

D09

12

D11

14

D05

6

D10

13

D12

15

8

GND9GND

116

VV

DD DD

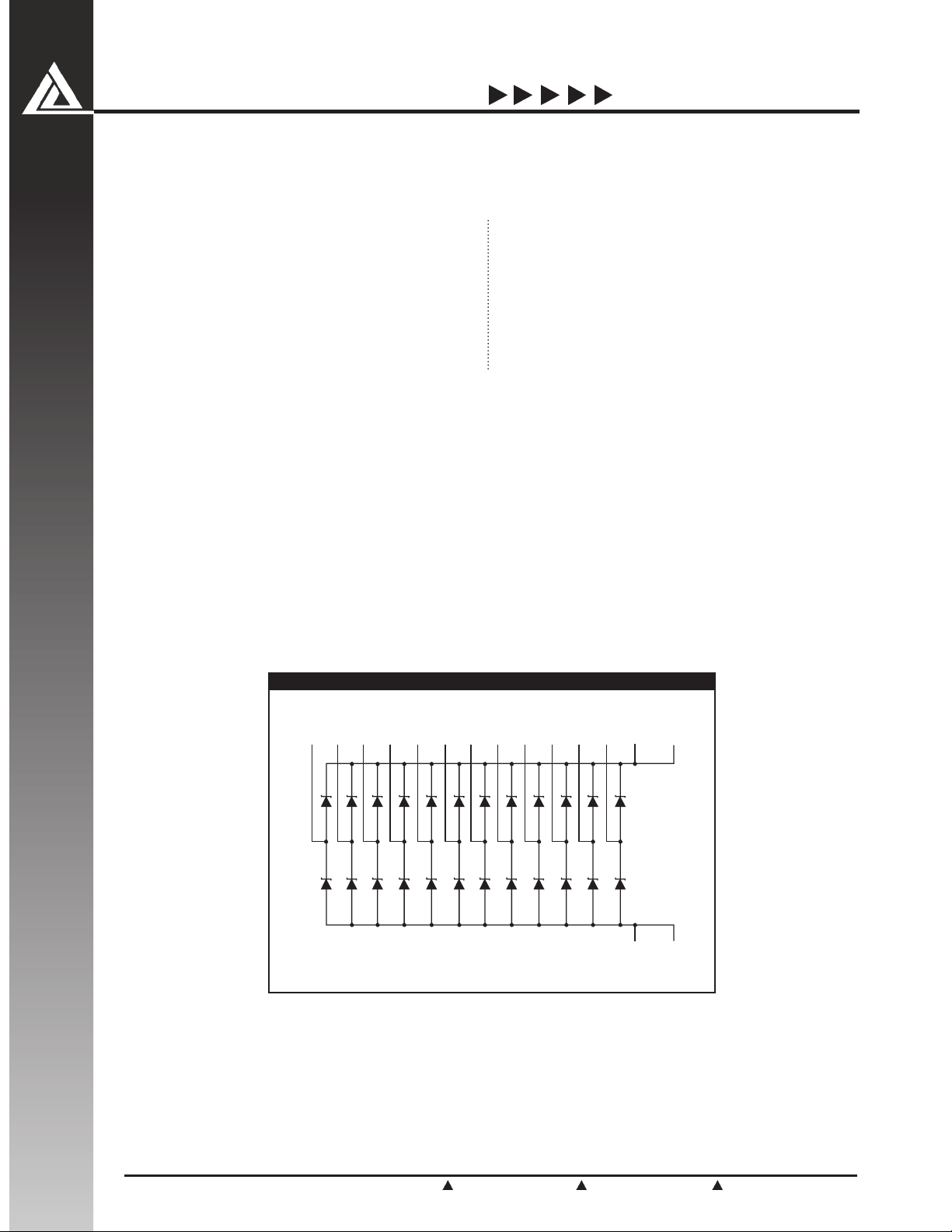

12-BIT SCHOTTKY BARRIER DIODE BUS TERMINATOR

SN 74S1051

Features

24 integrated diodes in a single package

offers 12 channel, dual rail clamping action

Provides proper bus termination independent of

external line or card loading conditions

Applications

Local high speed bus termination for all popular

RISC and embedded microprocessor applications

High speed memory and SDRAM memory

bus termination

Schottky diode technology; excellent forward

voltage and reverse recovery characteristics

Enhanced performance over existing device

16-pin SOIC package

Product Description

Reflections on high speed data lines lead to undershoot and overshoot disturbances which may result in improper

system operation. Resistor terminations, when used to terminate high speed data lines, increase power consumption

and degrade output (high) levels resulting in reduced noise immunity. Schottky diode termination is the best overall

solution for applications in which power consumption and noise immunity are critical considerations.

This integrated Schottky diode network provides very effective termination performance for high speed data lines

under variable loading conditions. The device supports up to 12 terminated lines per package each of which can

be simultaneously clamped to both ground and power supply rail.

SCHEMATIC CONFIGURATION

©1998 California Micro Devices Corp. All rights reserved.

®

is a registered trademark and PAC is a trademark of California Micro Devices.

P/Active

©1998 California Micro Devices Corp. All rights reserved.

4 / 98

4 / 98

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

C0220298D

1

CALIFORNIA MICRO DEVICES

SN 74S1051

STANDARD SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS

Parameter Symbol Rating

Supply Voltage V

Channel clamp current (continuous) I

Operating Temperature 0

Storage Temperature Tstg -65

DD -0.3V to +7V

clamp ±50mA

O

C to 70OC

O

C to +150OC

Package Power Rating 625mW, max.

The absolute maximum ratings are limiting values, to be applied individually, beyond which the device may be permanently damaged. Functional

operation under any of these conditions is not guaranteed. Exposing the device to its absolute maximum rating may

affect its reliability.

DIODE CHARACTERISTICS (TA = 0O to 70OC)

Parameter Conditions Min Typ Max

Diode foward voltage To V

Reverse Recovery Time (See Note 1) I

Channel leakage 0 ≤ V

Input Capacitance f = 1 MHz, V

DD IF = 16 mA 0.55V 0.70V

I

F = 50 mA 0.55V 0.70V 0.90V

From GND I

F = 50mA (estimated) <400pS

IN ≤ VDD 0.1µA 5µA

IN = 2.5V, TA = 25

F = 16 mA 0.50V 0.65V

I

F = 50 mA 0.50V 0.65V 0.85V

O

C, VDD = 5.0V 5pF

ESD Protection MIL-STD-883, Method 3015 4KV

NOITAMROFNIGNIREDROTRAPDRADNATS

egakcaPrebmuNtraPgniredrO

sniPelytSsebuTleeR&epaTgnikraMtraP

61worraNCIOST/1501S47NSR/1501S47NS1501S47NS

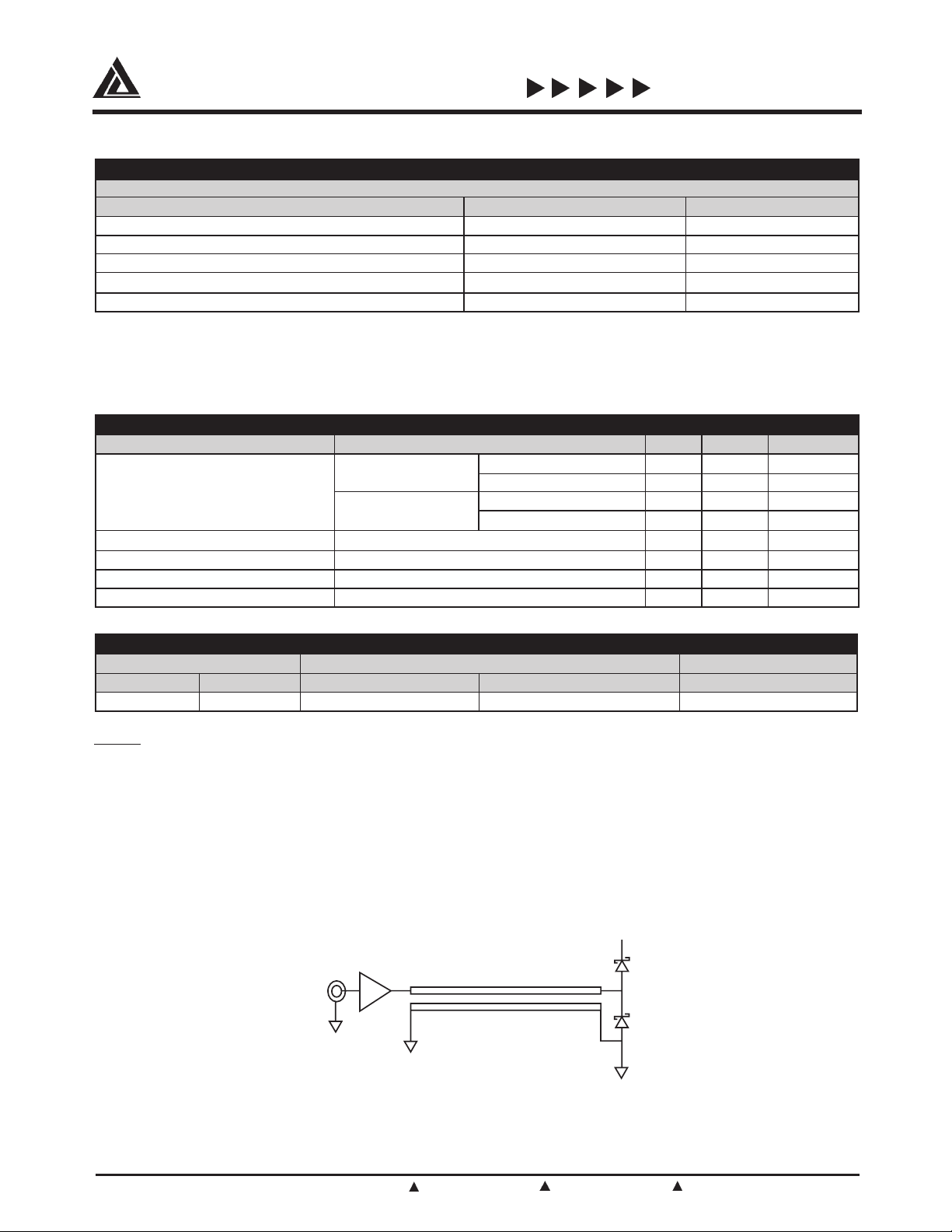

Note 1:

The test circuit depicts the Schottky diodes in their typical application. The impact of a reverse recovery time is measured

using a narrow pulse with 670- pS rise and fall times. This pulse propagates down a 60 cm, 54 ohm strip line fabricated

on a multi-layer, controlled impedance printed circuit board. In testing the ground clamp diode, the negative going edge

of the pulse causes a reflection which forces the diode under test to become forward biased. The positive going edge of

the pulse attempts to pull this diode out of forward conduction. A reverse recovery phenomenon would cause a delay

between the known arrival time of the positive edge and the observed edge due to the time it takes for the forward biased

diode to actually become reversed biased. In this measurement, however, there is no observable difference and therefore

no delay for the positive edge due to the presence of the diode. The waveforms are adjusted to individually test the

ground and V

DD clamps. See test circuit.

ABT16244A

Pulse

Generator

Z,L

0

V

DD

Diode

under

test

Test Circuit. Line length, pulse width and duty cycle are selected such as that only one reflection is involved

in the measurement.

©1998 California Micro Devices Corp. All rights reserved.

2

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

4 / 98

Loading...

Loading...