California Micro Devices PACVGA200Q Datasheet

CALIFORNIA MICRO DEVICES

VGA PORT COMPANION CIRCUIT

PACVGA200

Features

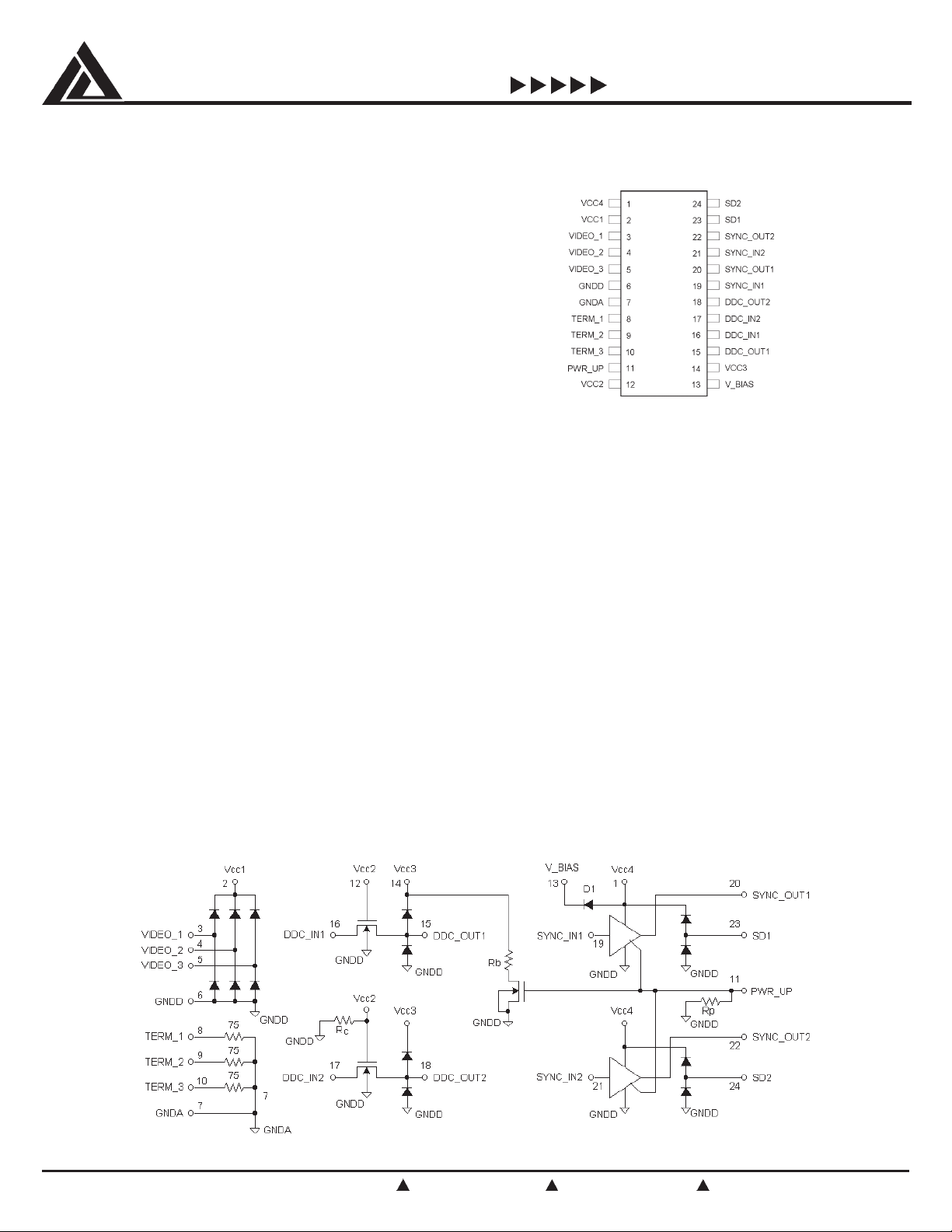

Pin Diagram

7 channels of ESD protection for all VGA port

connector pins meeting IEC-61000-4-2 Level-4 ESD

requirements (8KV contact discharge)

Very low loading capacitance from ESD protection

diodes on VIDEO lines, 4pF typical

TTL to CMOS level-translating buffers with power

down mode for HSYNC and VSYNC lines

75 Ω termination resistors for VIDEO lines (matched

to 1%typ.)

Bi-directional level shifting N-channel FETs provided for

DDC_CLK & DDC_DATA channels

Compact 24-pin QSOP package

24-PIN QSOP PACKAGE

Product Description

The PACVGA200 incorporates 7 channels of ESD protection for all signal lines commonly found in a VGA port. ESD protection

is implemented with current steering diodes designed to safely handle the high surge currents encountered with IEC-1000-4-

2 Level-4 ESD Protection (8KV contact discharge). When a channel is subjected to an electrostatic discharge, the ESD current

pulse is diverted via the protection diodes into the positive supply rail or ground where it may be safely dissipated.

Separate positive supply rails are provided for the VIDEO, DDC and SYNC channels to facilitate interfacing with low voltage

Video Controller ICs and provide design flexibility in multi-supply-voltage environments.

Two non-inverting drivers provide buffering for the HSYNC and VSYNC signals from the Video Controller IC (SYNC1, SYNC2).

These buffers accept TTL input levels and convert them to CMOS output levels that swing between Ground and V

drivers have nominal 60Ω output impedance to match the characteristic impedance of the HSYNC & VSYNC lines of the video

. These

CC4

cables typically used in PC applications.

Two N-channel FETs provide the level shifting function required when the DDC controller is operated at a lower supply voltage

than the monitor.

Three 75Ω termination resistors suitable for terminating the video signals from the video DAC are also provided. These

resistors have separate input pins to allow insertion of additional EMI filtering, if required, between the termination point and

the ESD protection diodes. These resistors are matched to better than 2% for excellent signal level matching for the R/G/B

signals.

When the PWR_UP input is driven LOW the SYNC inputs can be floated without causing the SYNC buffers to draw any current

from the V

An internal diode (D1 in schematic below) is also provided so that V

to V_BIAS. In applications where V

back to the powered down V

supply. When the PWR_UP input is LOW the SYNC outputs are driven LOW.

CC3

can be derived from V

may be powered down, diode D1 blocks any DC current paths from the DDC_OUT pins

CC4

rail via the top ESD protection diodes.

CC4

CC3

, if desired, by connecting V

CC4

CC3

Schematic Diagram

© 2000 California Micro Devices Corp. All rights reserved.

4/00

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

PACVGA200 is a trademark of California Micro Devices Corp.

C0641299

1

CALIFORNIA MICRO DEVICES

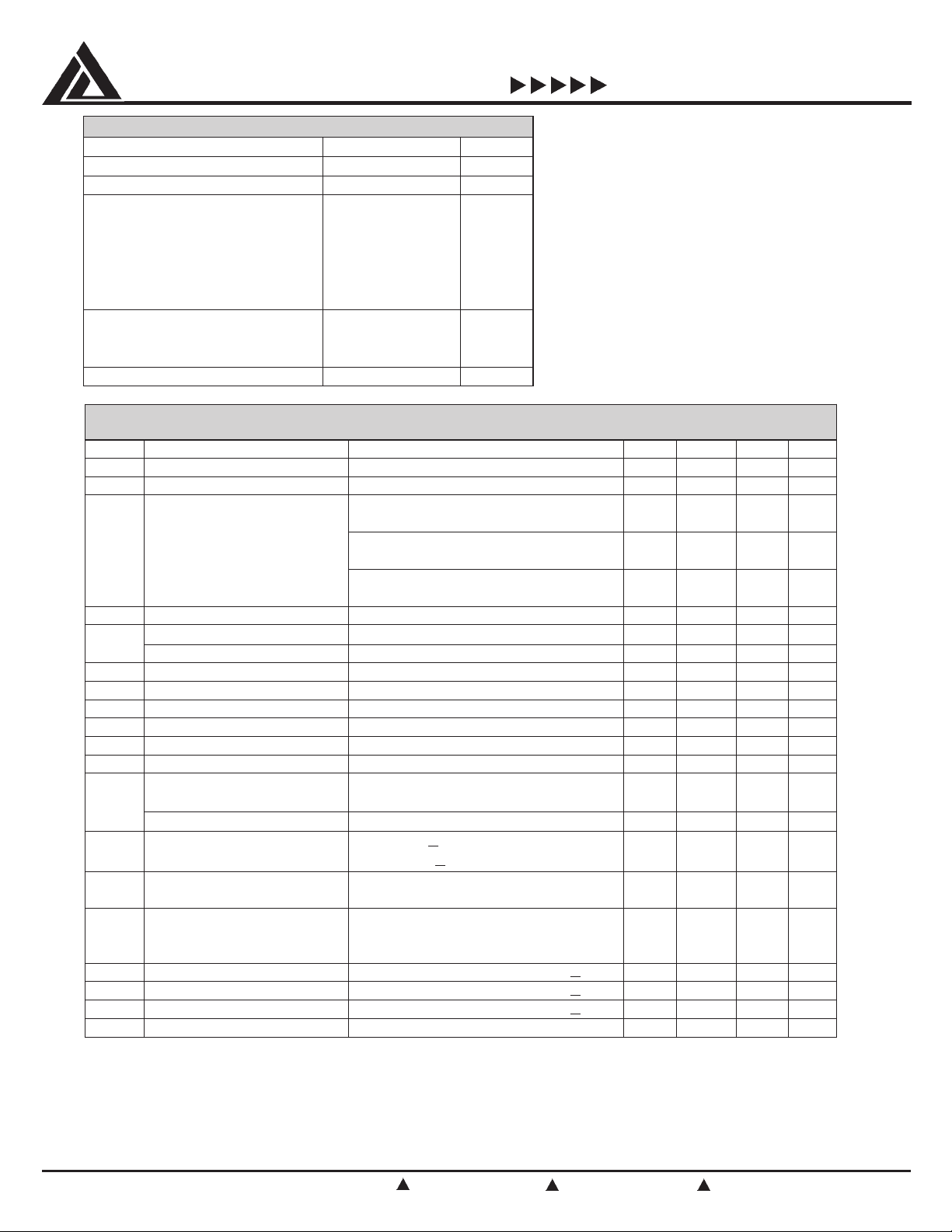

SGNITARMUMIXAMETULOSBA

retemaraPgnitaRtinU

V,

V,

V

1CC

2CC

V&

3CC

4CC

:stupnitaegatlovCD V

2NI_CDD,1NI_CDDV,5.0-DNG

2NI_CNYS,1NI_CNYSV,5.0-DNG

:erutarepmeT

egarotS051+ot04-

tneibmAgnitarepO07+ot0

noitapissidrewopegakcaP0.1W

lobmySretemaraPsnoitidnoCNIMPYTXAMTINU

I

1CC

I

I

4CC

V

R

T

V

HI

V

LI

V

V

LO

R

b

R

c

I

N

3,2CC

SAIB

HO

R,

p

V

1CC

V

V,

2CC

3CC

V

4CC

V

SAIB

R

T

V

2CC

eulavrotsiseRV,PU_RWP

tnerructupnI

stupniOEDIVV

I

FFO

TEFNgnitfihsV(

V

NO

C

NI

t

HLP

t

LHP

t,

t

r

f

V

DSE

Note 1: These parameter applies only to the HSYNC and VSYNC channels.

Note 2: Per the IEC-61000-4-2 International ESD Standard, Level 4 contact discharge method. V

to GND via a low impedance ground plane with a 0.2uF, low inductance, chip ceramic capacitor at each supply pin. ESD pulse

is applied between the applicable pins and GND. ESD pulse can be positive or negative with respect to GND. Applicable pins

are: VIDEO_1, VIDEO_2, VIDEO_3, SYNC_OUT1, SD1, SYNC_OUT2, SD2, DDC_OUT1 and DDC_OUT2. All other pins are ESD

protected to the industry standard 2kV per the Human Body model (MIL-STD-883, Method 3015).

Note 3: This parameter is guaranteed by design and characterization.

©2000 California Micro Devices Corp. All rights reserved.

2

215 Topaz Street, Milpitas, California 95035 Tel: (408) 263-3214 Fax: (408) 263-7846 www.calmicro.com

egatlovylppus0.6+,5.0-DNGV

tnerrucdrawrof1DedoiD001Au

3_OEDIV,2_OEDIV,1_OEDIVV,5.0-DNG

5.0+V

1CC

3_MRET,2_MRET,1_MRET0.6+,0.6-V

5.0+

2CC

2TUO_CDD,1TUO_CDDV,5.0-DNG

tnerrucylppusV

tnerrucylppusV

tnerrucylppusV

1CC

V=

2CC

4CC

V

4CC

Vtanip

V

4CC

5.0+V

3CC

5.0+V

4CC

o

C

o

C

tastupniOEDIV;V5=V

V5=01Au

3CC

VtanipPU_RWP

;4CC

4CC

dedaolnustuptuo

egatlovtiucricnepoVmorfnwardtnerruclanretxeoN

ecnatsisernoitanimretOEDIV 52.175757.87

gnihctamecnatsiser 12%

1

egatlovtupnihgiHcigoL

1

egatlovtupniwoLcigoL

1

egatlovtuptuohgiHcigoL

1

egatlovtuptuowoLcigoL

rotsisernwod-llupV

stupniCNYSV,CNYSHV

levelssorcapordegatloVV

V

V

I

HO

I

LO

level,tnerrucegakaeletatsFFOV(

V0.5=0.2V

4CC

V0.5=8.0V

4CC

V,Am4-=

V,Am4=

3CC

V0.3=5.05.13MΩ

2CC

V;V5=

1CC

4CC

2CC

2CC

2CC

NI

V;V5=

NI

V-

)< V;V4.0

NI_CDD

V-

)< V;V4.0

TUO_CDD

V;V5.2=

V0.5=4.4V

4CC

V0.5=4.0V

4CC

V0.5=5.012MΩ

V=

V=

S

DNGro1±

1CC

DNGro1±

4CC

CDD_TUO

CDD_NI

I,DNG=

SD

NOdenrutnehwTEFNgnitfihs

3

ecnaticapactupnI

3_OEDIV,2_OEDIV,1_OEDIVV

3,2

egatlovdnatshtiwDSE

1CC

V

1CC

yalednoitagaporpH-LsrevirdCNYSC

L

yalednoitagaporpL-HsrevirdCNYSC

L

semitllaf&esirtuptuosrevirdCNYSC

L

V

1CC

V;V0.5=

NI

V;V5.2=

NI

V;Fp05=

CC

V;Fp05=

CC

V;Fp05=

CC

V=

V=

3CC

V5=8±Vk

4CC

PACVGA200

SCITSIRETCARAHCGNITAREPOLACIRTCELE

)esiwrehtodeificepssselnusnoitidnocgnitareporevo(

DNGro01Au

1CC

VroDNGtastupniCNYS;V5=

;01Au

4CC

dedaolnustuptuoCNYS

PU_RWP;V0.3tastupniCNYS;V5=002Au

dedaolnustuptuoCNYS;

CNYS;DNGtatupniPU_RWP;V5=01Au

nipV

SAIB

V=

2CC

V=

2CC

Am3=51.0V

zHM1taderusaem;V5.2=0.4Fp

zHM1taderusaem;V52.1=5.4

ttupnI;V5=

tdna

<sn5821sn

r

f

ttupnI;V5=

tdna

<sn5821sn

r

f

ttupnI;V5=

tdna

<sn57sn

r

f

, V

and V

CC1

CC3

8.0-V

4CC

Ω

µA

µA

01

µA

01

µA

must be bypassed

CC4

4/00

Loading...

Loading...