Page 1

DATASHEET

ENCOUNTER

T

I

M

I

N

G

A

R

E

A

P

O

W

E

R

S

I

Y

I

E

L

D

STA

Test & Diagnostics

Power & SI Analysis

Constraint

Management

& Equivalence

Checking

Silicon Virtual Prototyping

Nanometer Routing

Manufacturing

RTL Synthesis

Global Physical Synthesis

G0001

ENCOUNTER CONFORMAL

LOW POWER

Cadence® Encounter® Conformal® Low Power, a key technology

of the Cadence Encounter digital IC design platform, enables

designers to verify and debug multimillion-gate designs optimized

for low power, without simulating test vectors. It combines

low power structural and functional checks with world-class

equivalence checking to provide superior performance, capacity,

and ease of use.

ENCOUNTER PLATFORM

To release innovative products in narrow

market windows, companies need to

focus precious engineering resources

on where they add the most value—

differentiating their designs. The Cadence

Encounter digital IC design platform

offers a full spectrum of technologies for

nanometer-scale SoC design, helping both

Logic Design and physical implementation

teams achieve high-quality silicon quickly.

As an integrated RTL-to-GDSII design

environment, the Encounter platform

provides a complete flow—from RTL

synthesis and test design, through silicon

virtual prototyping and partitioning, to

final timing and manufacturing closure.

It delivers the highest quality of silicon

(timing, area, and power with wires),

accurate verification, signal-integrity—

aware routing, and the latest yield and

low-power design capabilities that are

critical for advanced 65nm designs. With

Encounter technology, you can boost your

productivity, manage complexity, and get

your products to market faster.

Encounter platform products are available

in L, XL, and GXL offerings.

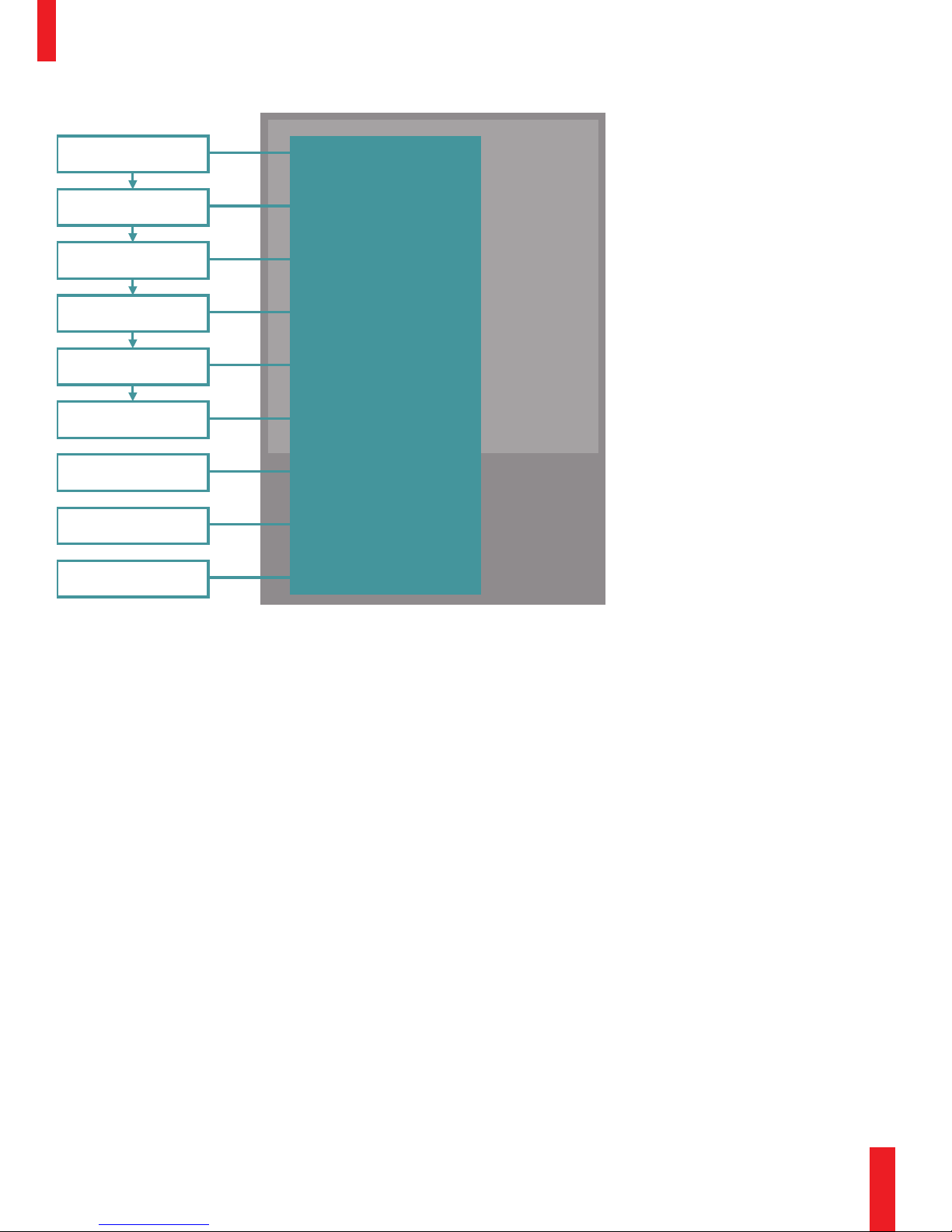

Figure 1: Encounter digital IC design platform

Page 2

Logic synthesis (area,

power, timing, yield)

RTL

Datapath and

test synthesis

Floorplanning and

physical synthesis

Place-and-route

ECO’s

Final layout

Custom memory design

Encounter

Conformal

Low Power XL

Encounter

Conformal

Low Power GXL

Custom circuit design

Logic equivalence checking

for low power design

Extended functional checks

Clock domain crossing checks

Semantic checks

Structural checks

Reachability and FSM checks

Equivalence checking support

for complex datapath and

final LVS netlist (SPICE)

Low power structural

and functional checks for

logical and power aware

design netlist

Equivalence checking

support for digital custom

logic, cell libraries, IO, and

embedded memories

Electrical verification of low

power transistor netlist

Figure 2: Encounter Conformal Low Power offers a complete solution—from RTL to final layout

ENCOUNTER CONFORMAL

LOW POWER

Consumers increasingly expect longer

battery life and higher performance in

their mobile devices. As these sometimes

conflicting demands force chips to

move into nanometer-scale processes,

power management becomes one of

the most critical design issues. Due to

increased leakage, devices created using

90-nanometer and smaller process nodes

consume as much power when they are

not in use as when they are being used.

Optimizing for leakage and dynamic power

helps designers reduce energy use and

lower cooling and packaging costs. While

advanced low power methods—such

as static and dynamic voltage/frequency

scaling, power gating, and state

retention—offer additional power savings,

they also complicate the verification task.

2 www.c a den c e.c om

ENC OU NTER CO NF ORMA L L OW POW ER

Verification complexity is amplified by

the fact that the majority of the low

power function is introduced into the

gate netlist during synthesis and physical

implementation. Full-chip, gate-level

simulation is not a practical or scalable

methodology for verifying the logic

function of the today’s designs due to their

size and complexity.

Encounter Conformal Low Power, which

combines proven equivalence checking and

functional checks, uses formal techniques

to address this challenge, enabling full-chip

low power verification.

Encounter Conformal Low Power is

available in XL and GXL offerings.

BENEFITS

• Minimizes silicon re-spin risk by providing

complete verification coverage

• Detects low power implementation

errors early in the design cycle

• Reduces verification time significantly by

verifying multimillion gate designs faster

(by orders of magnitude) than traditional

gate-level simulation

• Closes the RTL-to-layout verification gap

• Decreases risk of missing critical bugs

through independent verification

technology

FEATURES

ENCOUNTER CONFORMAL

LOW POWER XL

It combines logic equivalence checking

for the most complex low power SoC and

datapath-intensive designs, with functional

and structural checks for low power

designs, clock domain synchronization and

semantics.

EQUIVALENCE CHECKING FOR LOW

POWER DESIGN

During development, a low power design

undergoes numerous iterations prior to

final layout, and each step in this process

has the potential to introduce logical bugs.

Encounter Conformal Low Power XL checks

the functional equivalence of different

versions of a low power design at these

various stages and enables you to identify

and correct errors as soon as they are

introduced. It supports advanced dynamic

and static power synthesis optimizations

such as clock gating and signal gating,

Multi Vt libraries, as well as de-cloning and

re-cloning of gated clocks during clock tree

synthesis and optimization.

Encounter Conformal Low Power XL

supports the Common Power Format

(CPF) specification language. It uses CPF

as guidance to independently insert and

connect low-power cells—level shifters,

isolation, and state retention registers—into

an RTL design, thus enabling true low

power RTL to gate equivalence checking.

The tool can also model level shifters and

isolation cells as domain anchor points

during equivalence checking to detect

whether logic gates have erroneously

crossed domain boundaries from one

version of the netlist to another.

Page 3

Figure 4: Encounter Conformal Low Power debug

Environment

Figure 3: Illustrates power domain highlighting capability in Encounter Conformal Low Power XL

STRUCTURAL AND FUNCTIONAL

CHECKING FOR LOW POWER DESIGN

Encounter Conformal Low Power XL

supports multi-supply voltage island

(MSV), coarse grain power gating (PSO),

and coarse grain ground switching (GSO),

dynamic voltage and frequency scaling

(DVFS), and state retention power gating

design techniques. It also makes it possible

to perform power domain structural and

functional checks on an RTL design with

CPF, a logical gate netlist (typically postsynthesis), and a power aware physical

throughout the design hierarchy and

identifies all domain boundary crossings.

Finally, it reports:

• Power and ground domain assignment

related problems and floating connections

• Level shifter: Missing, redundant, wrong

domain location, or wrong connectivity

• Isolation cell: Missing, redundant, wrong

gate type, or wrong location, wrong

isolation enable polarity

• Control signals that are not powered

appropriately

gate netlist (post-place and route).

Encounter Conformal Low Power XL

For RTL and logical gate netlist checking

using a non-CPF based implementation

flow, the user manually defines, using

Encounter Conformal commands, the

power domains, ground domains, voltages,

supports dedicated and non-dedicated

isolation cells, as well as combination

isolation and level shifter cells. It also

performs isolation and state retention

functional checks using formal methods.

standby conditions, power modes, and

power associations, along with the lowpower cells being used. For a CPF-based

implementation flow, the tool derives all

the setup information directly from CPF.

The software then propagates domains

For physical netlist checking, the tool

accepts a Verilog® power-aware netlist LEF,

and simulation or Liberty models. It uses

top-level power pins, power and ground

nets, power switches (MTCMOS), ground

switches, island voltages, power

pin associations, and low power cells to

automatically derive the power domains

and domain crossings in the design.

The entire tool setup for physical netlist

checking can also be derived from CPF.

It then reports:

• Incorrect power and ground connectivity,

including shorts and opens

• Instances with undefined power

domains, or mixed power domains

• Missing, redundant, incorrect power

connection, wrong level shifter type

• Missing, redundant, incorrect isolation

cell power connectivity

• Power control signals to power switches,

isolation cells, state retention, that are

not powered

• Incorrect power connection to state

retention registers

Encounter Conformal Low Power XL also

performs isolation functional checks on userdefined isolation cells, as well as standard

cell-based isolation. It also runs sleep and

wake sequence functional checks on state

retention registers using formal methods.

www.c a den c e.c om 3

ENC OU NTER CO NF ORMA L L OW POW ER

Page 4

INTEGRATED ENVIRONMENT

An intuitive and interactive graphical user

interface (GUI) is provided for setup and

debugging, allowing the user to quickly

operate the tool and pinpoint the cause of

failed checks. Included are:

PLATFORMS

• Linux (32-bit, 64-bit)

• Sun Solaris (32-bit, 64-bit)

• HP-UX (32-bit, 64-bit)

• IBM AIX (32-bit, 64-bit)

• Graphical debugging via integrated

schematic viewer

• Automatic error candidate identification

for equivalence checking with assigned

and weighted percentages

• Low Power Manager GUI to help users

debug failed checks

• Waveform viewer and automatic counter

example generation for failed isolation

and state retention properties

ENCOUNTER CONFORMAL

LOW POWER GXL

Encounter Conformal Low Power GXL

combines all the features in Encounter

Conformal Low Power XL and offers

transistor circuit analysis, abstraction,

and equivalence checking for custom

designs, standard cell libraries, IO pads, and

embedded memories. It also offers unique

checks for circuit integrity such as drive

strength checking via the transistor stacks

and checking for circuit problems across

power domain boundaries such as sneaky

DC paths during power down.

Figure 5: Demonstrates structural checking for

missing isolation

Encounter Conformal Low Power GXL can

also abstract from a transistor cdl/spice

netlist accurate power aware Verilog

models of level shifters and isolation cells.

This allows the user to identify inconsistencies between simulation, Liberty, spice, and

LEF models. It can also help validate that

the isolation cells used in the low power

design are appropriate.

LANGUAGE SUPPORT

• Verilog (1995, 2001)

• SystemVerilog

• VHDL (87, 93)

• SPICE (traditional, LVS)

• EDIF

• Liberty

• Mixed languages

For more information Email

us at icinfo@cadence.com

or visit www.cadence.com.

Cadence Design Systems, Inc.

Corporate Headquarters

2655 Seely Avenue San Jose, CA 95134

United States 800.746.6223

+408.943.1234 (outside U.S.)

www.cadence.com

© 2007 Cadence Design Systems, Inc. All rights reserved.

Cadence, Conformal, Encounter, and Verilog are registered trademarks, and the Cadence logo is a trademark of Cadence

Design Systems, Inc. All others are properties of their respective holders.

6846B 01/07 MK/FLD/JA/PDF

Loading...

Loading...