Burr Brown Corporation DDC112U, DDC112UK-1K, DDC112UK, DDC112U-1K Datasheet

DDC112

®

1

DDC112

®

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

Twx: 910-952-1111 • Internet: http://www.burr-brown.com/ • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

DDC112

Dual Current Input 20-Bit

ANALOG-TO-DIGITAL CONVERTER

FEATURES

● MONOLITHIC CHARGE MEASUREMENT ADC

● DIGITAL FILTER NOISE REDUCTION:

3.2ppm, rms

● INTEGRAL LINEARITY:

±0.005% Reading ±0.5ppm FSR

● HIGH PRECISION, TRUE INTEGRATING

FUNCTION

● PROGRAMMABLE FULL SCALE

● SINGLE SUPPLY

● CASCADABLE OUTPUT

APPLICATIONS

● DIRECT PHOTOSENSOR DIGITIZATION

● CT SCANNER DAS

● INFRARED PYROMETER

● PRECISION PROCESS CONTROL

● LIQUID/GAS CHROMATOGRAPHY

● BLOOD ANALYSIS

DESCRIPTION

The DDC112 is a dual input, wide dynamic range,

charge-digitizing analog-to-digital converter (ADC) with

20-bit resolution. Low level current output devices,

such as photosensors, can be directly connected to its

inputs. Charge integration is continuous as each input

uses two integrators; while one is being digitized, the

other is integrating.

For each of its two inputs, the DDC112 combines

current-to-voltage conversion, continuous integration,

programmable full-scale range, A/D conversion, and

digital filtering to achieve a precision, wide dynamic

range digital result. In addition to the internal programmable full-scale ranges, external integrating capacitors

allow an additional user-settable full-scale range of up

to 1000pC.

To provide single-supply operation, the internal ADC

utilizes a differential input, with the positive input tied

to V

REF

. When the integration capacitor is reset at the

beginning of each integration cycle, the capacitor

charges to V

REF

. This charge is removed in proportion

to the input current. At the end of the integration cycle,

the remaining voltage is compared to V

REF

.

The high-speed serial shift register which holds the

result of the last conversion can be configured to allow

multiple DDC112 units to be cascaded, minimizing

interconnections. The DDC112 is available in a SO-28

package and is offered in two performance grades.

Protected by US Patent #5841310

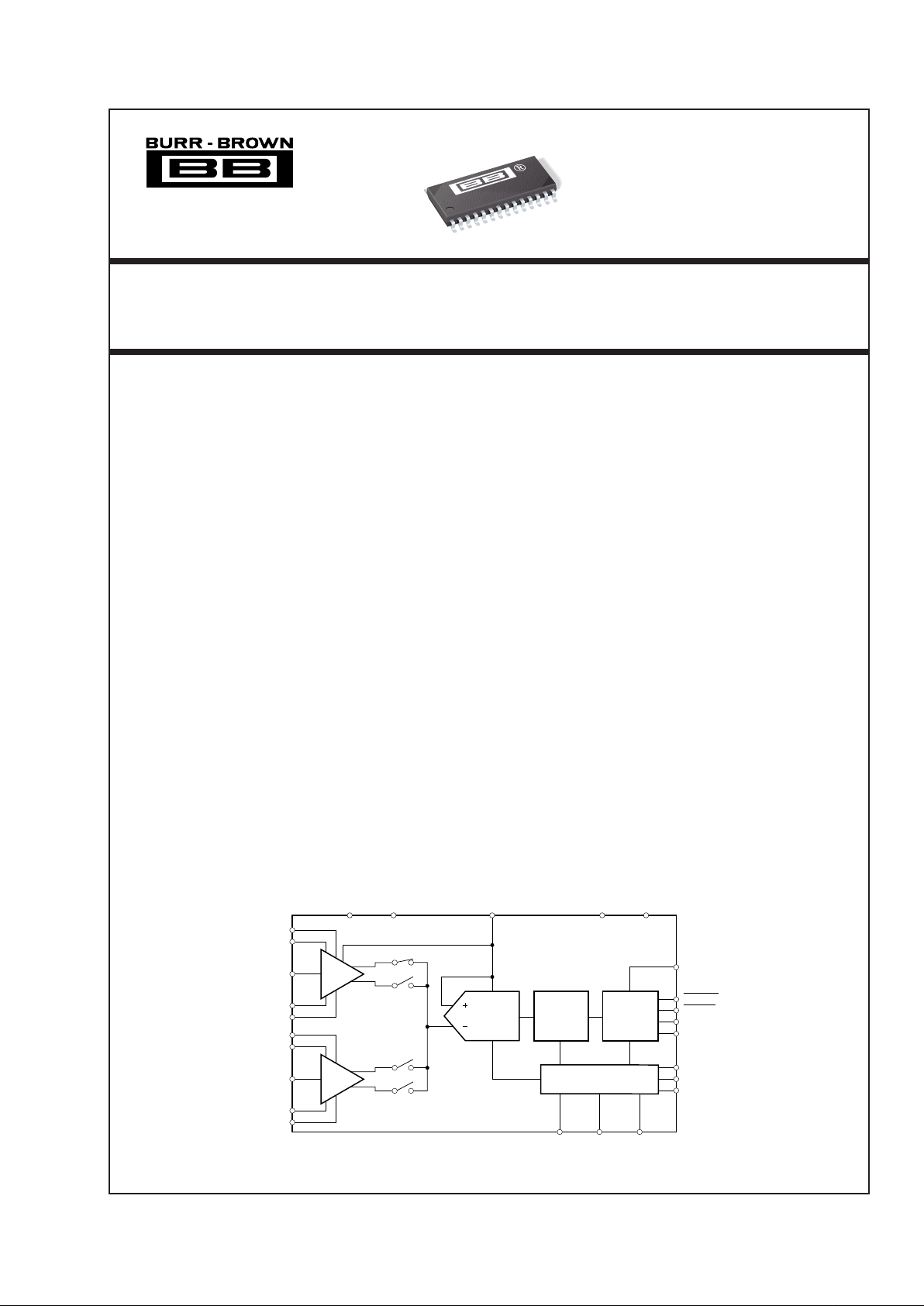

Dual

Switched

Integrator

Dual

Switched

Integrator

∆Σ

Modulator

Digital

Filter

Control

Digital

Input/Output

DVALID

DXMIT

DOUT

DIN

DCLK

RANGE2

RANGE1

RANGE0

TEST

CONV

CLK

CAP1A

CAP1A

CAP1B

CAP1B

CAP2A

CAP2A

CAP2B

CAP2B

IN2

IN1

V

REF

DGNDDV

DD

AGNDAV

DD

CHANNEL 1

CHANNEL 2

©

1997 Burr-Brown Corporation PDS-1421D Printed in U.S.A. January, 2000

For most current data sheet and other product

information, visit www.burr-brown.com

®

2

DDC112

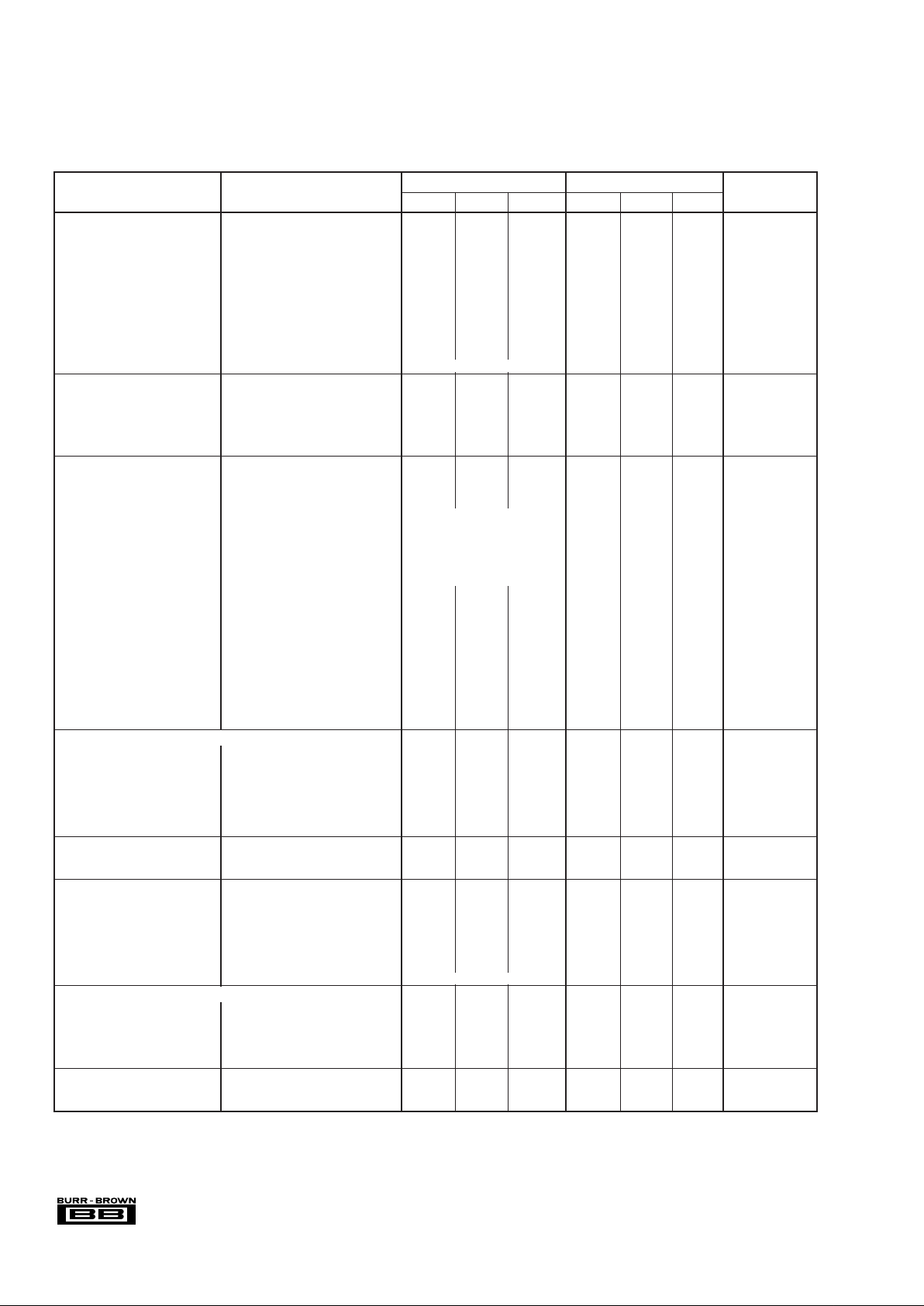

SPECIFICATIONS

At TA = +25°C, AVDD = DVDD = +5V, DDC112U: T

INT

= 500µs, CLK = 10MHz, DDC112UK: T

INT

= 333.3µs, CLK = 15MHz, V

REF

= +4.096V, continuous mode

operation, and internal integration capacitors, unless otherwise noted.

NOTES: (1) Input is less than 1% of full scale. (2) C

SENSOR

is the capacitance seen at the DDC112 inputs from wiring, photodiode, etc. (3) FSR is Full-Scale Range.

(4) A best-fit line is used in measuring linearity. (5) Matching between side A and side B, not input 1 to input 2. (6) Voltage produced by the DDC112 at its input which

is applied to the sensor. (7) Range drift does not include external reference drift. (8) Input reference current decreases with increasing T

INT

(see text). (9) Data format

is Straight Binary with a small offset (see text). (10) Guaranteed but not tested.

DDC112U DDC112UK

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

ANALOG INPUTS

External, Positive Full-Scale

Range 0 C

EXT

= 250pF 1000 ✻ pC

Internal, Positive Full-Scale

Range 1 47.5 50 52.5 ✻✻✻ pC

Range 2 95 100 105 ✻✻✻ pC

Range 3 142.5 150 157.5 ✻✻✻ pC

Range 4 190 200 210 ✻✻✻ pC

Range 5 237.5 250 262.5 ✻✻✻ pC

Range 6 285 300 315 ✻✻✻ pC

Range 7 332.5 350 367.5 ✻✻✻ pC

Negative Full-Scale Input

–0.4% of Positive FS

✻ pC

DYNAMIC CHARACTERISTICS

Conversion Rate 2 3 kHz

Integration Time, T

INT

Continuous Mode 500 1,000,000 333.3 ✻ µs

Integration Time, T

INT

Non-continuous Mode 50 ✻ µs

System Clock Input (CLK) 1 10 12 ✻✻15 MHz

Data Clock (DCLK) 12 15 MHz

ACCURACY

Noise, Low Level Current Input

(1)

C

SENSOR

(2)

= 0pF, Range 5 (250pC) 3.2 ✻

ppm of FSR

(3)

, rms

C

SENSOR

= 25pF, Range 5 (250pC) 3.8 ✻ ppm of FSR, rms

C

SENSOR

= 50pF, Range 5 (250pC) 4.2 6.0 ✻ 7 ppm of FSR, rms

Differential Linearity Error ±0.005% Reading ±0.5ppm

FSR, max ✻

Integral Linearity Error

(4)

±0.005% Reading ±0.5ppm

FSR, typ ✻

±0.025% Reading ±1.0ppm

FSR, max ✻

No Missing Codes 20 ✻ Bits

Input Bias Current T

A

= +25°C 0.1 10 ✻✻ pA

Range Error Range 5 (250pC) 5 ✻ % of FSR

Range Error Match

(5)

All Ranges 0.1 0.5 ✻✻% of FSR

Range Sensitivity to V

REF

V

REF

= 4.096 ±0.1V 1:1 ✻

Offset Error Range 5, (250pC) ±200 ✻ ±600 ppm of FSR

Offset Error Match

(5)

±100 ✻ ppm of FSR

DC Bias Voltage

(6)

(Input VOS) ±0.05 ±2 ✻✻ mV

Power Supply Rejection Ratio ±25 ±200 ✻✻ppm of FSR/V

Internal Test Signal 13 ✻ pC

Internal Test Accuracy ±10 ✻ %

PERFORMANCE OVER TEMPERATURE

Offset Drift ±0.5 ±3

(10)

ppm of FSR/°C

Offset Drift Stability ±0.2 ✻ ±0.7

(10)

ppm of FSR/minute

DC Bias Voltage Drift Applied to Sensor Input 3 ±1 µV/°C

Input Bias Current Drift +25°C to +45°C 0.01 1

(10)

✻✻ pA/°C

Input Bias Current T

A

= +75°C250

(10)

✻✻ pA

Range Drift

(7)

Range 5 (250pC) 25 0 25 50

(10)

ppm/°C

Range Drift Match

(5)

Range 5 (250pC) ±0.05 ✻ ppm/°C

REFERENCE

Voltage 4.000 4.096 4.200 ✻✻✻ V

Input Current

(8)

T

INT

= 500µs 150 225 275 µA

DIGITAL INPUT/OUTPUT

Logic Levels

V

IH

4.0

DV

DD

+ 0.3

✻✻V

V

IL

–0.3 +0.8 ✻✻V

V

OH

IOH = –500µA 4.5 ✻ V

V

OL

IOL = 500µA 0.4 ✻ V

Input Current, I

IN

–10 +10 ✻✻µA

Data Format

(9)

Straight Binary ✻

POWER SUPPLY REQUIREMENTS

Power Supply Voltage AV

DD

and DV

DD

4.75 5.25 ✻✻V

Supply Current

Analog Current AV

DD

= +5V 14.8 15.2 mA

Digital Current DV

DD

= +5V 1.2 1.8 mA

Total Power Dissipation 80 100 85 130 mW

TEMPERATURE RANGE

Specified Performance –40 +85 0 +70 °C

Storage –60 +100 ✻✻°C

DDC112

®

3

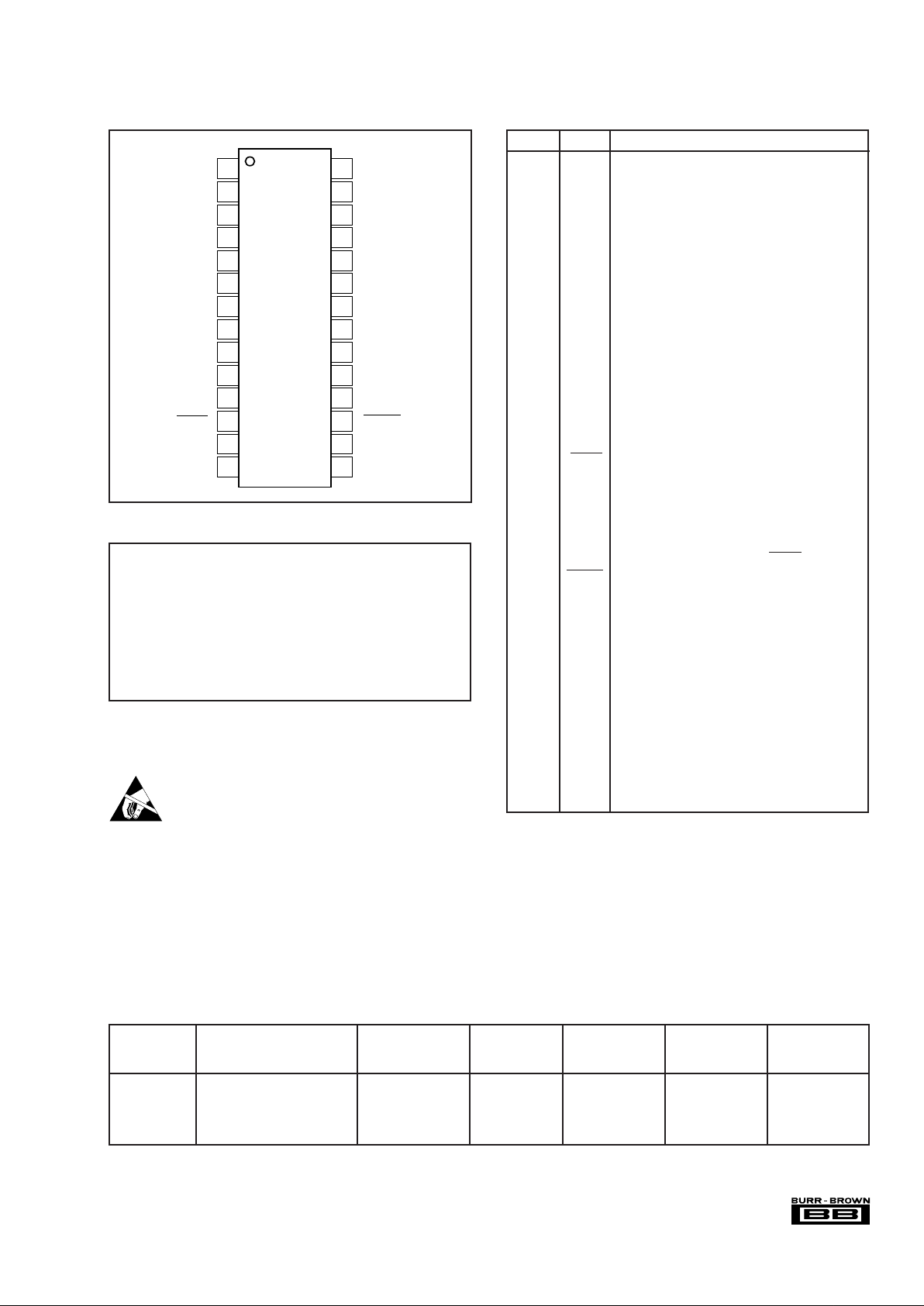

PIN DESCRIPTIONS

PIN LABEL DESCRIPTION

1 IN1 Input 1: analog input for Integrators 1A and 1B. The

integrator that is active is set by the CONV input.

2 AGND Analog Ground.

3 CAP1B External Capacitor for Integrator 1B.

4 CAP1B External Capacitor for Integrator 1B.

5 CAP1A External Capacitor for Integrator 1A.

6 CAP1A External Capacitor for Integrator 1A.

7AV

DD

Analog Supply, +5V nominal.

8 TEST Test Control Input. When HIGH, a test charge is

applied to the A or B integrators on the next CONV

transition.

9 CONV Controls which side of the integrator is connected to

input. In continuous mode; CONV HIGH → side A is

integrating, CONV LOW → side B is integrating.

CONV must be synchronized with CLK (see text).

10 CLK System Clock Input, 10MHz nominal.

11 DCLK Serial Data Clock Input. This input operates the

serial I/O shift register.

12 DXMIT Serial Data Transmit Enable Input. When LOW, this

input enables the internal serial shift register.

13 DIN Serial Digital Input. Used to cascade multiple

DDC112s.

14 DV

DD

Digital Supply, +5V nominal.

15 DGND Digital Ground.

16 DOUT Serial Data Output, Hi-Z when DXMIT is HIGH.

17 DVALID Data Valid Output. A LOW value indicates valid data

is available in the serial I/O register.

18 RANGE0 Range Control Input 0 (least significant bit).

19 RANGE1 Range Control Input 1.

20 RANGE2 Range Control Input 2 (most significant bit).

21 AGND Analog Ground.

22 V

REF

External Reference Input, +4.096V nominal.

23 CAP2A External Capacitor for Integrator 2A.

24 CAP2A External Capacitor for Integrator 2A.

25 CAP2B External Capacitor for Integrator 2B.

26 CAP2B External Capacitor for Integrator 2B.

27 AGND Analog Ground.

28 IN2 Input 2: analog input for Integrators 2A and 2B. The

integrator that is active is set by the CONV input.

The information provided herein is believed to be reliable; however, BURR-BROWN

assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no

responsibility for the use of this information, and all use of such information shall be

entirely at the user’s own risk. Prices and specifications are subject to change without

notice. No patent rights or licenses to any of the circuits described herein are implied or

granted to any third party. BURR-BROWN does not authorize or warrant any BURRBROWN product for use in life support devices and/or systems.

AVDD to DVDD....................................................................... –0.3V to +6V

AV

DD

to AGND .....................................................................–0.3V to +6V

DV

DD

to DGND ..................................................................... –0.3V to +6V

AGND to DGND ............................................................................... ±0.3V

V

REF

Voltage to AGND ............................................ –0.3V to AVDD +0.3V

Digital Input Voltage to DGND ................................ –0.3V to DV

DD

+0.3V

Digital Output Voltage to DGND ............................. –0.3V to DV

DD

+0.3V

Package Power Dissipation ............................................. (T

JMAX

– TA)/

θ

JA

Maximum Junction Temperature (T

JMAX

) ...................................... +150°C

Thermal Resistance,

θ

JA

............................................................. 150°C/W

Lead Temperature (soldering, 10s) ............................................... +300°C

NOTE: (1) Stresses above those listed under “Absolute Maximum Ratings”

may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

ABSOLUTE MAXIMUM RATINGS

(1)

PIN CONFIGURATION

Top View SO

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

IN2

AGND

CAP2B

CAP2B

CAP2A

CAP2A

V

REF

AGND

RANGE2 (MSB)

RANGE1

RANGE0 (LSB)

DVALID

DOUT

DGND

IN1

AGND

CAP1B

CAP1B

CAP1A

CAP1A

AV

DD

TEST

CONV

CLK

DCLK

DXMIT

DIN

DV

DD

DDC112

PACKAGE/ORDERING INFORMATION

MAXIMUM SPECIFICATION PACKAGE

INTEGRAL TEMPERATURE DRAWING ORDERING TRANSPORT

PRODUCT LINEARITY ERROR RANGE PACKAGE NUMBER NUMBER

(1)

MEDIA

DDC112U

±0.025% Reading ±1.0ppm% FSR

–40°C to +85°C SO-28 217 DDC112U Rails

"""""DDC112U/1K Tape and Reel

DDC112UK

±0.025% Reading ±1.0ppm% FSR

0°C to +70°C SO-28 217 DDC112UK Rails

"""""DDC112UK/1K Tape and Reel

NOTES: (1) Models with a slash (/) are available only in Tape and Reel in the quantities indicated (e.g., /1K indicates 1000 devices per reel). Ordering 1000 pieces

of “DDC112U/1K” will get a single 1000-piece Tape and Reel.

ELECTROSTATIC

DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown

recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and

installation procedures can cause damage.

ESD damage can range from subtle performance degradation to

complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes

could cause the device not to meet its published specifications.

®

4

DDC112

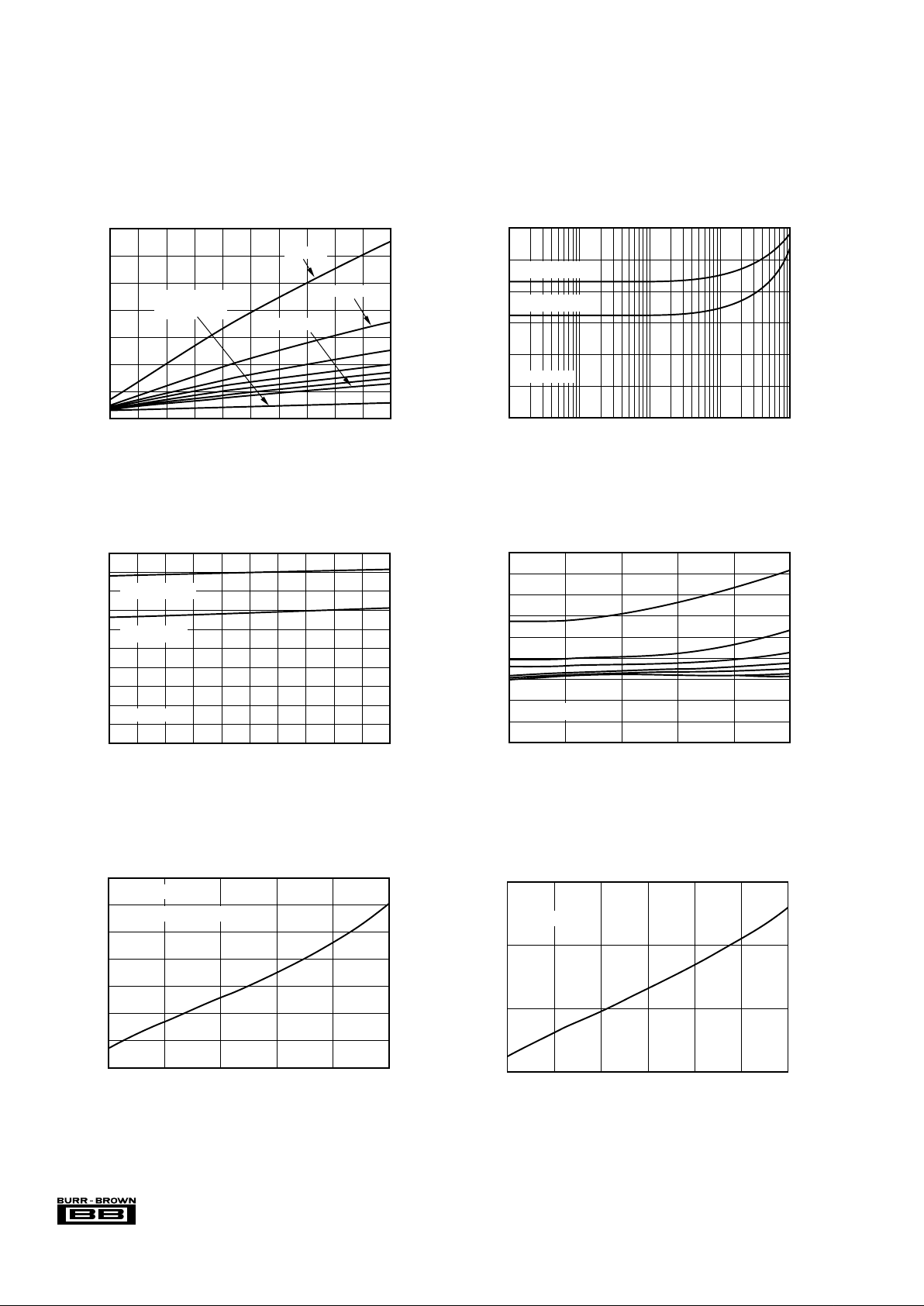

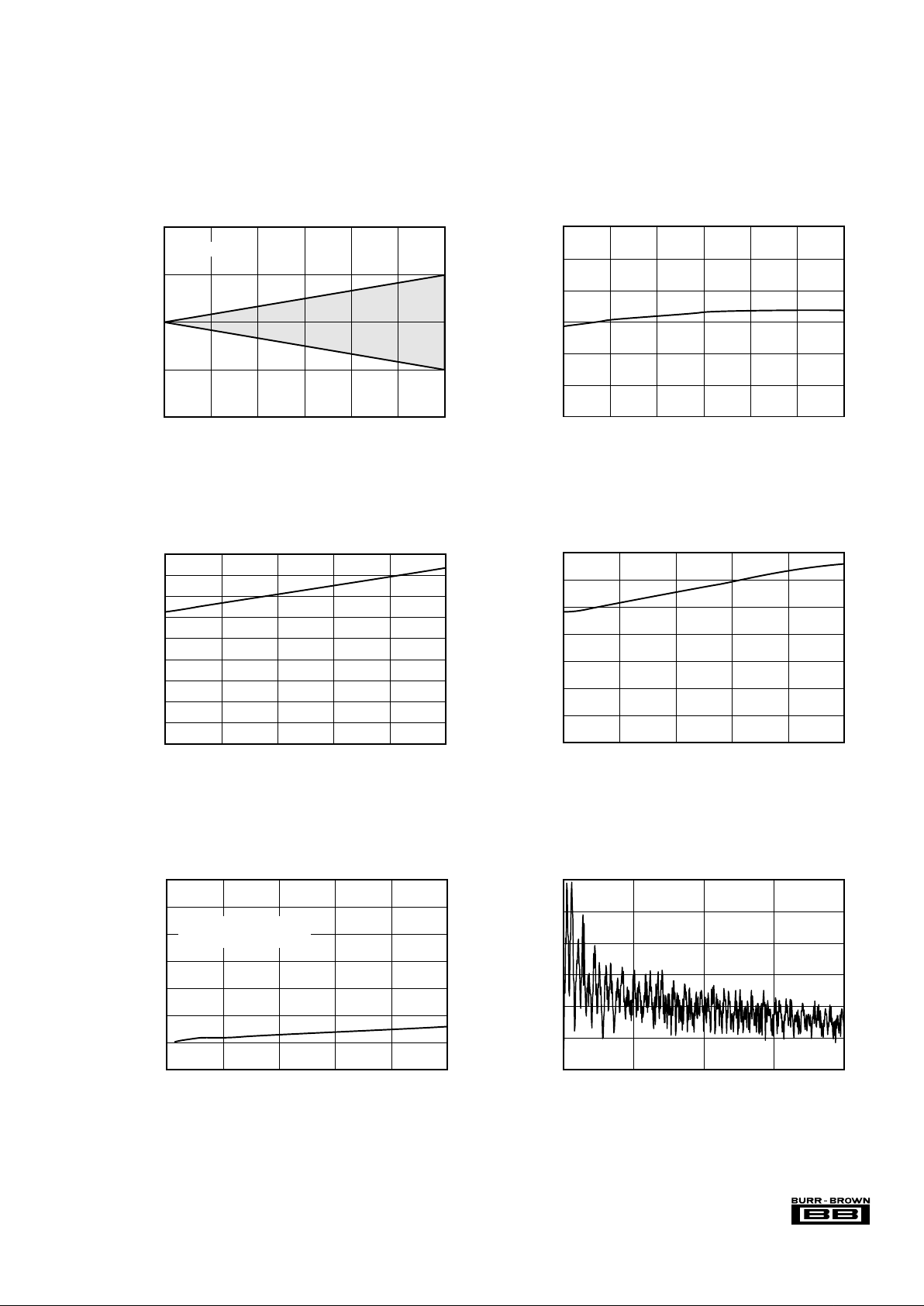

NOISE vs T

INT

1 10000.1 10010

T

INT

(ms)

Noise (ppm of FSR, rms)

0

1

2

3

4

5

6

C

SENSOR

= 50pF

C

SENSOR

= 0pF

Range 5

TYPICAL PERFORMANCE CURVES

At TA = +25°C, characterization done with Range 5 (250pC), T

INT

= 500µs, V

REF

= +4.096, AVDD = DVDD = +5V, and CLK = 10MHz, unless otherwise noted.

NOISE vs C

SENSOR

200 8000 1000600400

C

SENSOR

(pF)

Noise (ppm of FSR, rms)

0

10

20

30

40

50

60

70

Range 7

Range 2

Range 1

Range 0

(C

EXT

= 250pF)

NOISE vs INPUT LEVEL

30 4020 9010 10070 80 1050 60

Input Level (% of Full-Scale)

Noise (ppm of FSR, rms)

5

4.5

4

3.5

3

2.5

2

1.5

1

0.5

0

C

SENSOR

= 50pF

C

SENSOR

= 0pF

Range 5

NOISE vs TEMPERATURE

9

8

7

6

5

4

3

2

1

0

–40 –15 10 35 60 85

Temperature (°C)

Noise (ppm of FSR, rms)

Range 1

Range 2

Range 7

Range 3

C

SENSOR

= 0pF

RANGE DRIFT vs TEMPERATURE

–40 –15 10 35 60 85

Temperature (°C)

Range Drift (ppm)

Ranges 1 - 7

(Internal Integration Capacitor)

2000

1500

1000

500

0

–500

–1000

–1500

IB vs TEMPERATURE

25 35 45 55 65 75 85

Temperature (°C)

I

B

(pA)

All Ranges

10

1

0.1

0.01

DDC112

®

5

TYPICAL PERFORMANCE CURVES (Cont.)

At TA = +25°C, characterization done with Range 5 (250pC), T

INT

= 500µs, V

REF

= +4.096, AVDD = DVDD = +5V, and CLK = 10MHz, unless otherwise noted.

600

POWER SUPPLY REJECTION RATIO vs FREQUENCY

0 10025 7550

Frequency (KHz)

PSRR (ppm of FSR/V)

0

100

200

300

400

500

INPUT VOS vs RANGE

36

35

34

33

32

31

30

1234567

Range

V

OS

(µV)

DIGITAL SUPPLY CURRENT vs TEMPERATURE

1.4

1.2

1.0

0.8

0.6

0.4

0.2

0

–40 –15 10 35 60 85

Temperature (°C)

Current (mA)

ANALOG SUPPLY CURRENT vs TEMPERATURE

18

16

14

12

10

8

6

4

2

0

–40 –15 10 35 60 85

Temperature (°C)

Current (mA)

OFFSET DRIFT vs TEMPERATURE

25 35 45 55 65 75 85

Temperature (°C)

Offset Drift (ppm of FSR)

100

50

0

–50

–100

All Ranges

CROSSTALK vs FREQUENCY

0

–20

–40

–60

–80

–100

–120

–140

0 100 200 300 400 500

Frequency (Hz)

Separation (dB)

Separation Measured

Between Inputs 1 and 2

®

6

DDC112

THEORY OF OPERATION

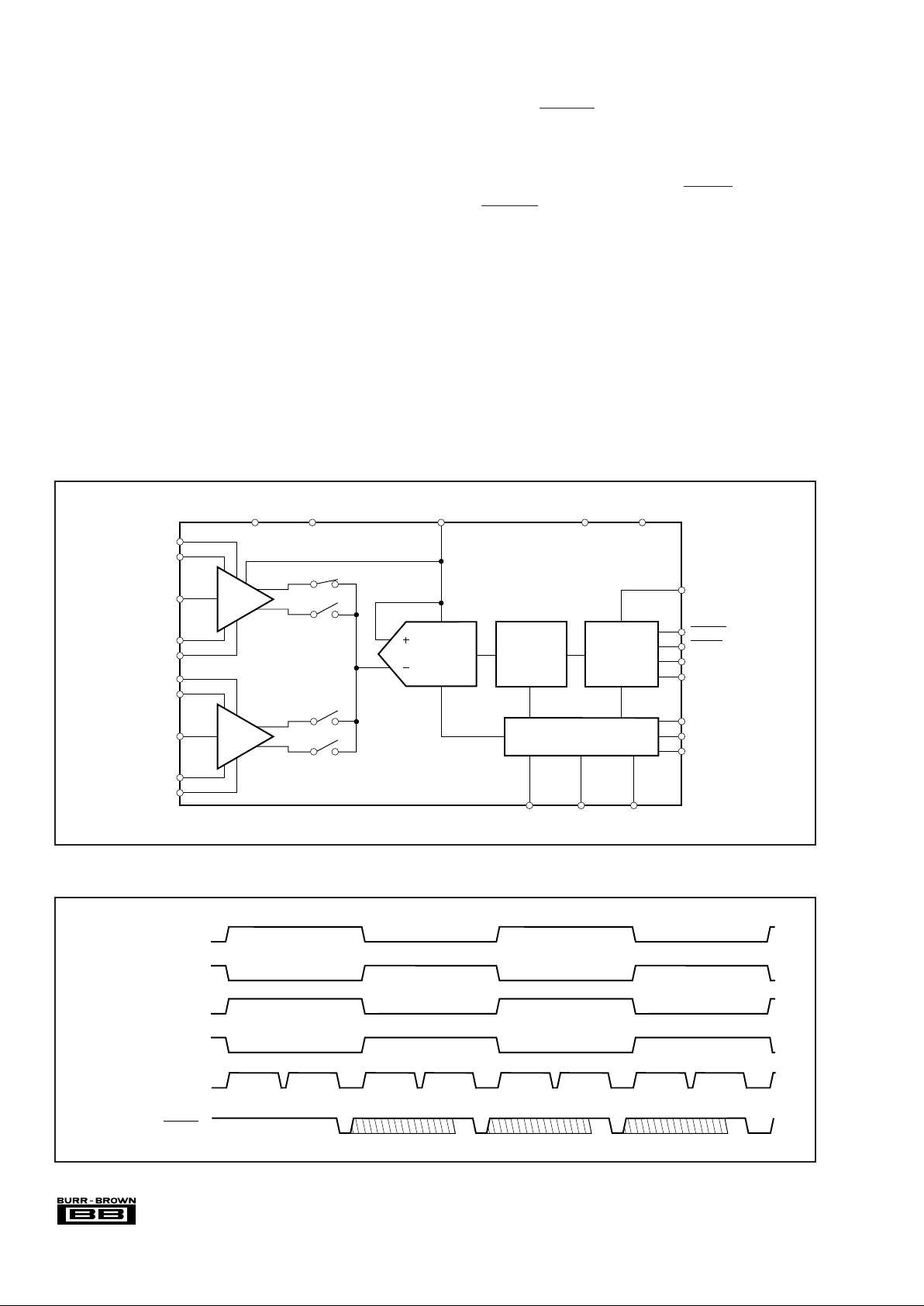

The basic operation of the DDC112 is illustrated in

Figure 1.

The device contains two identical input channels where each

performs the function of current-to-voltage integration followed by a multiplexed analog-to-digital (A/D) conversion.

Each input has two integrators so that the current-to-voltage

integration can be continuous in time. The output of the four

integrators are switched to one delta-sigma converter via a

four input multiplexer. With the DDC112 in the continuous

integration mode, the output of the integrators from one side

of both of the inputs will be digitized while the other two

integrators are in the integration mode as illustrated in the

timing diagram in Figure 2. This integration and A/D conversion process is controlled by the system clock, CLK.

With a 10MHz system clock, the integrator combined with

the delta-sigma converter accomplishes a single 20-bit conversion in approximately 220µs. The results from side A and

side B of each signal input are stored in a serial output shift

register. The DVALID output goes LOW when the shift

register contains valid data.

The digital interface of the DDC112 provides the digital

results via a synchronous serial interface consisting of a data

clock (DCLK), a transmit enable pin (DXMIT), a valid data

pin (DVALID), a serial data output pin (DOUT), and a serial

data input pin (DIN). The DDC112 contains only one A/D

converter, so the conversion process is interleaved between

the two inputs, as shown in Figure 2. The integration and

conversion process is fundamentally independent of the data

retrieval process. Consequently, the CLK frequency and

DCLK frequencies need not be the same. DIN is only used

when multiple converters are cascaded and should be tied to

DGND otherwise. Depending on T

INT

, CLK, and DCLK, it

is possible to daisy chain over 100 converters. This greatly

simplifies the interconnection and routing of the digital

outputs in those cases where a large number of converters

are needed.

Dual

Switched

Integrator

Dual

Switched

Integrator

∆Σ

Modulator

Digital

Filter

Control

Digital

Input/Output

DVALID

DXMIT

DOUT

DIN

DCLK

RANGE2

RANGE1

RANGE0

TEST

CONV

CLK

CAP1A

CAP1A

CAP1B

CAP1B

CAP2A

CAP2A

CAP2B

CAP2B

IN2

IN1

V

REF

DGNDDV

DD

AGNDAV

DD

Input 1

Input 2

IN1, Integrator A

IN1, Integrator B

IN2, Integrator A

IN2, Integrator B

Conversion in Progress

DVALID

IN1B IN2B IN1A

Integrate

Integrate

Integrate

Integrate

Integrate

Integrate

Integrate

Integrate

IN2A IN1B IN2B IN1A

IN2A

FIGURE 2. Basic Integration and Conversion Timing for the DDC112 (continuous mode).

FIGURE 1. DDC112 Block Diagram.

DDC112

®

7

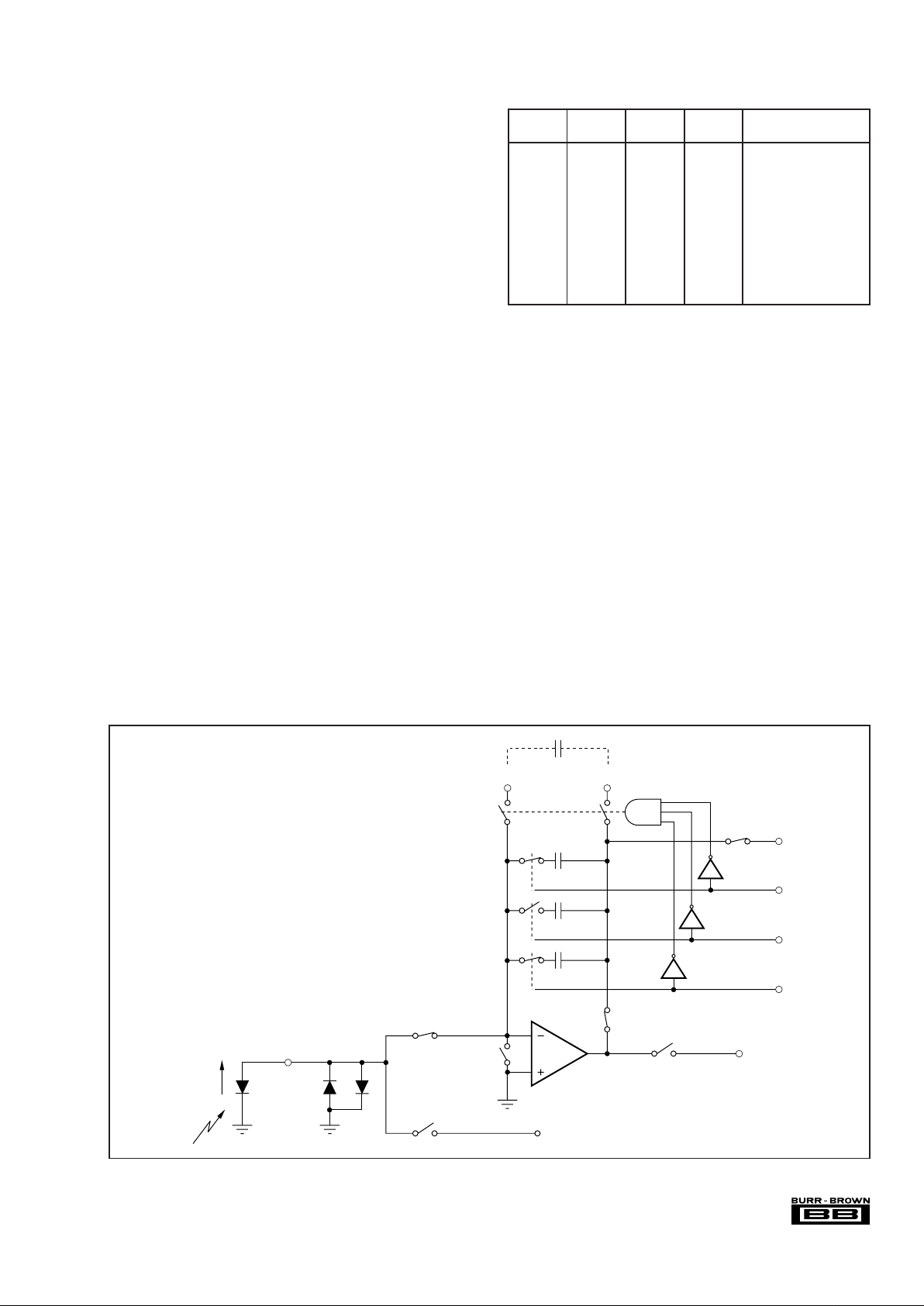

DEVICE OPERATION

Basic Integration Cycle

The fundamental topology of the front end of the DDC112

is a classical analog integrator as shown in Figure 3. In this

diagram, only Input 1 is shown. This representation of the

input stage consists of an operational amplifier, a selectable

feedback capacitor network (CF), and several switches that

implement the integration cycle. The timing relationships of

all of the switches shown in Figure 3 are illustrated in Figure

4. Figure 4 is used to conceptualize the operation of the

integrator input stage of the DDC112 and should not be used

as an exact timing tool for design. Block diagrams of the

reset, integrate, converter and wait states of the integrator

section of the DDC112 are shown in Figure 5. This internal

switching network is controlled externally with the convert

command (CONV), range selection pins (RANGE0RANGE2), and the system clock (CLK). For the best noise

performance, CONV must be synchronized with the rising

edge of CLK. It is recommended CONV toggle within

±10ns of the rising edge of CLK.

The non-inverting inputs of the integrators are internally

referenced to ground. Consequently, the DDC112 analog

ground should be as clean as possible. The range switches,

along with the internal and external capacitors (CF) are

shown in parallel between the inverting input and output of

the operational amplifier. Table I shows the value of the

integration capacitor (CF) for each range. At the beginning

of a conversion, the switches S

A/D

, S

INTA

, S

INTB

, S

REF1

,

S

REF2

, and S

RESET

are set (see Figure 4).

At the completion of an A/D conversion, the charge on the

integration capacitor (CF) is reset with S

REF1

and

C

F

INPUT RANGE

RANGE2 RANGE1 RANGE0 (pF, typ) (pC, typ)

0 0 0 External Up to 1000

12.5 to 250

0 0 1 12.5 –0.2 to 50

0 1 0 25 –0.4 to 100

0 1 1 37.5 –0.6 to 150

1 0 0 50 –0.8 to 200

1 0 1 62.5 –0.1 to 250

1 1 0 75 –1.2 to 300

1 1 1 87.5 –1.4 to 350

TABLE I. Range Selection of the DDC112.

FIGURE 3. Basic Integrator Configuration for Input 1 Shown with a 250pC (CF = 62.5pF) Input Range.

S

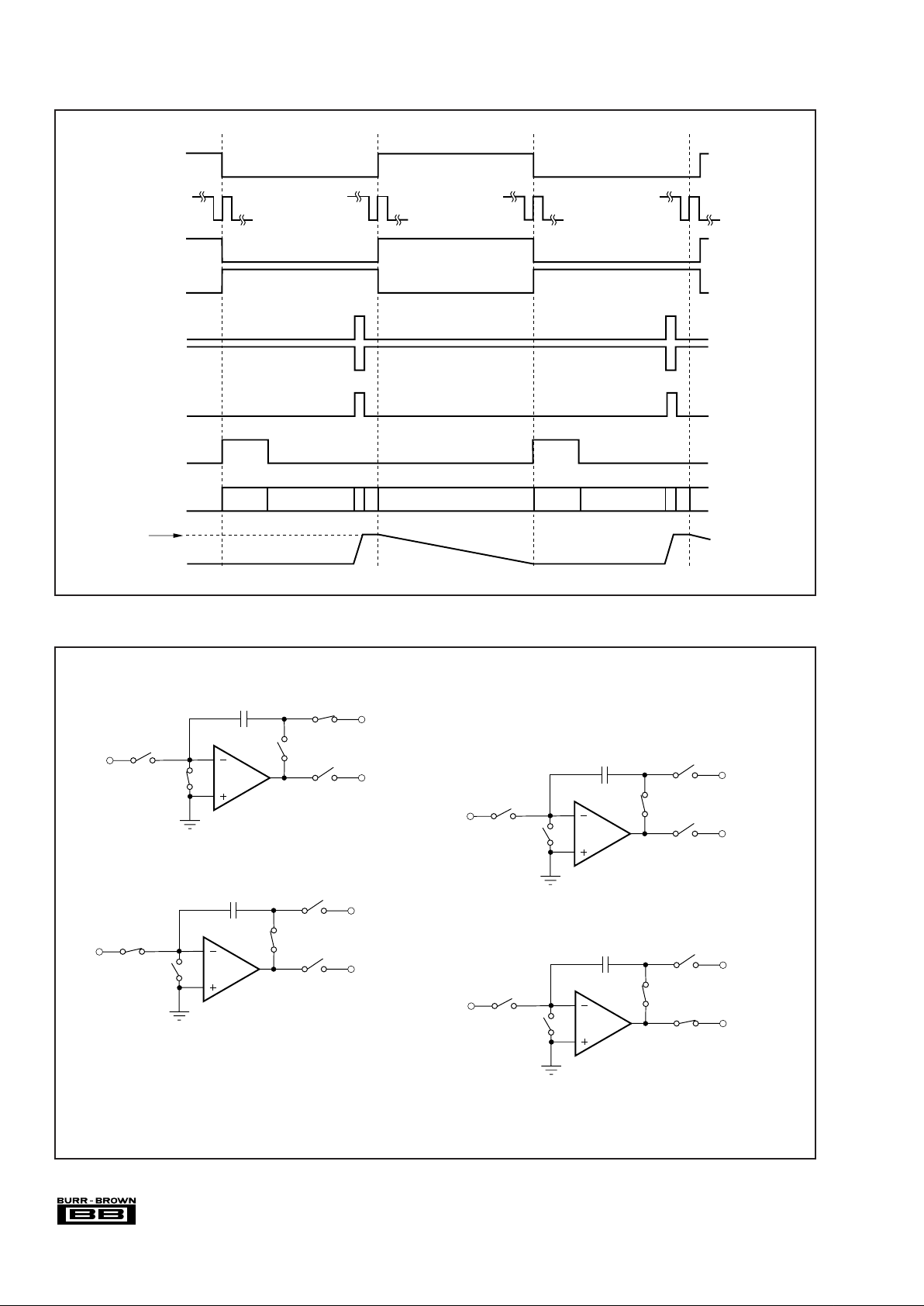

RESET

(see Figures 4 and 5a). This is done during the reset

time. In this manner, the selected capacitor is charged to the

reference voltage, V

REF

. Once the integration capacitor is

charged, S

REF1

, and S

RESET

are switched so that V

REF

is no

longer connected to the amplifier circuit while it waits to

begin integrating (see Figure 5b). With the rising edge on

CONV, S

INTA

closes which begins the integration of Channel A. This puts the integrator stage into its integrate mode

(see Figure 5c).

Charge from the input signal is collected on the integration

capacitor causing the voltage output of the amplifier to

decrease. A falling edge CONV stops the integration by

switching the input signal from side A to side B (S

INTA

and

S

INTB

). Prior to the falling edge of CONV, the signal on side

B was converted by the A/D converter and reset during the

time that side A was integrating. With the falling edge of

CONV, side B starts integrating the input signal. Now the

output voltage of side A’s operational amplifier is presented

to the input of the ∆Σ A/D converter (see Figure 5d).

50pF

CAP1ACAP1A

25pF

12.5pF

V

REF

RANGE2

RANGE1

RANGE0

To Converter

S

RESET

S

REF2

S

A/D1A

S

INTA

S

REF1

S

INTB

IN1

ESD

Protection

Diode

Input

Current

Integrator A

Integrator B (same as A)

Photodiode

®

8

DDC112

FIGURE 5. Diagrams for the Four Configurations of the Front End Integrators of the DDC112.

FIGURE 4. Basic Integrator Timing Diagram as Illustrated in Figure 3.

To Converter

S

RESET

S

REF2

S

A/D

V

REF

S

REF1

S

INT

IN

C

F

a) Reset Configuration

To Converter

S

RESET

S

REF2

S

A/D

V

REF

S

REF1

S

INT

IN

C

F

c) Integrate Configuration

To Converter

S

RESET

S

REF2

S

A/D

V

REF

S

REF1

S

INT

IN

C

F

d) Convert Configuration

To Converter

S

RESET

S

REF2

S

A/D

V

REF

S

REF1

S

INT

IN

C

F

b) Wait Configuration

S

A/D1A

V

REF

Integrator A

Voltage Output

Configuration of

Integrator A

WaitConvert WaitConvertIntegrate

S

REF1

S

REF2

S

INTA

S

INTB

S

RESET

CONV

CLK

Wait

Reset

Wait

Reset

Loading...

Loading...