Burr Brown Corporation DAC7802LU, DAC7802LP, DAC7802KU, DAC7800KP, DAC7802KP Datasheet

...

®

1

DAC7800, 01, 02

DAC7800

DAC7801

DAC7802

DESCRIPTION

The DAC7800, DAC7801 and DAC7802 are members of a new family of monolithic dual 12-bit CMOS

multiplying digital-to-analog converters. The digital

interface speed and the AC multiplying performance

are achieved by using an advanced CMOS process

optimized for data conversion circuits. High stability

on-chip resistors provide true 12-bit integral and differential linearity over the wide industrial temperature

range of –40oC to +85oC.

DAC7800 features a serial interface capable of clocking-in data at a rate of at least 10MHz. Serial data is

clocked (edge triggered) MSB first into a 24-bit shift

register and then latched into each D/A separately or

simultaneously as required by the application. An

asynchronous CLEAR control is provided for poweron reset or system calibration functions. It is packaged

in a 16-pin 0.3" wide plastic DIP.

DAC7801 has a 2-byte (8 + 4) double-buffered

interface. Data is first loaded (level transferred) into

the input registers in two steps for each D/A. Then

both D/As are updated simultaneously. DAC7801 features an asynchronous CLEAR control. DAC7801 is

packaged in a 24-pin 0.3" wide plastic DIP.

DAC7802 has a single-buffered 12-bit data word interface. Parallel data is loaded (edge triggered) into the

single D/A register for each D/A. DAC7802 is packaged in a 24-pin 0.3" wide plastic DIP.

FEATURES

● TWO D/As IN A 0.3" WIDE PACKAGE

● SINGLE +5V SUPPLY

● HIGH SPEED DIGITAL INTERFACE:

Serial—DAC7800

8 + 4-Bit Parallel—DAC7801

12-Bit Parallel—DAC7802

● MONOTONIC OVER TEMPERATURE

● LOW CROSSTALK: –94dB min

● FULLY SPECIFIED OVER –40

O

C TO +85OC

APPLICATIONS

● PROCESS CONTROL OUTPUTS

● ATE PIN ELECTRONICS LEVEL SETTING

● PROGRAMMABLE FILTERS

● PROGRAMMABLE GAIN CIRCUITS

● AUTO-CALIBRATION CIRCUITS

Dual Monolithic CMOS 12-Bit Multiplying

DIGITAL-TO-ANALOG CONVERTERS

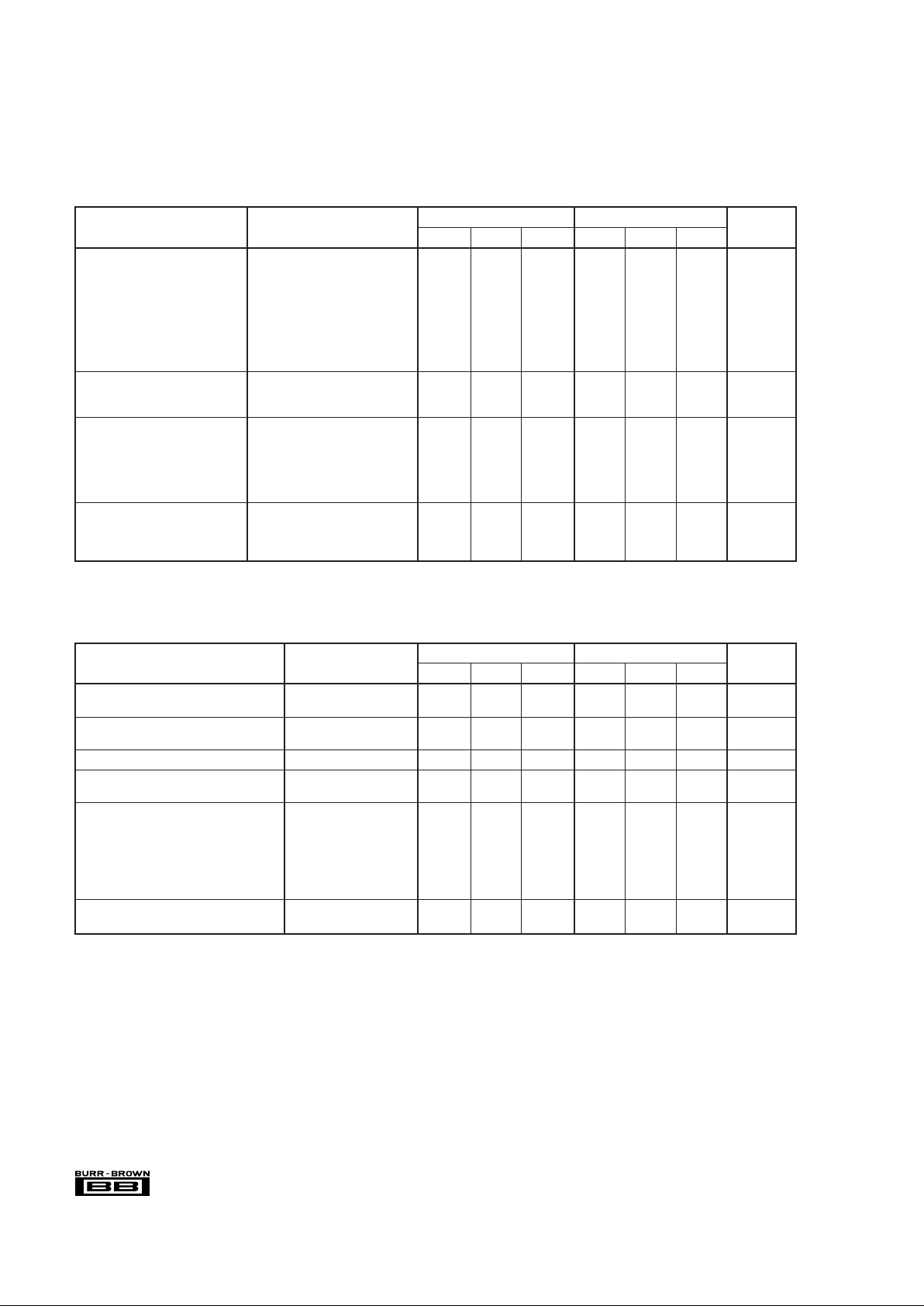

Serial Interface

8-Bit Interface

8 Bits + 4 Bits

Serial

DAC7801

DAC7800

12-Bit MDAC

DAC A

FB B

I

OUT B

CLR

WR

A0CSA1

UPD

UPD A

UPD B

CS

CLK

CLR

12-Bit MDAC

DAC B

R

12-Bit Interface

DAC7802

CSA

WR

12

8

CSB

12

12

AGND B

REF B

V

FB A

I

OUT A

R

AGND A

REF A

V

®

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111 • Twx: 910-952-1111

Internet: http://www.burr-brown.com/ • FAXLine: (800) 548-6133 (US/Canada Only) • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

© 1990 Burr-Brown Corporation PDS-1079G Printed in U.S.A. January, 1998

2

®

DAC7800, 01, 02

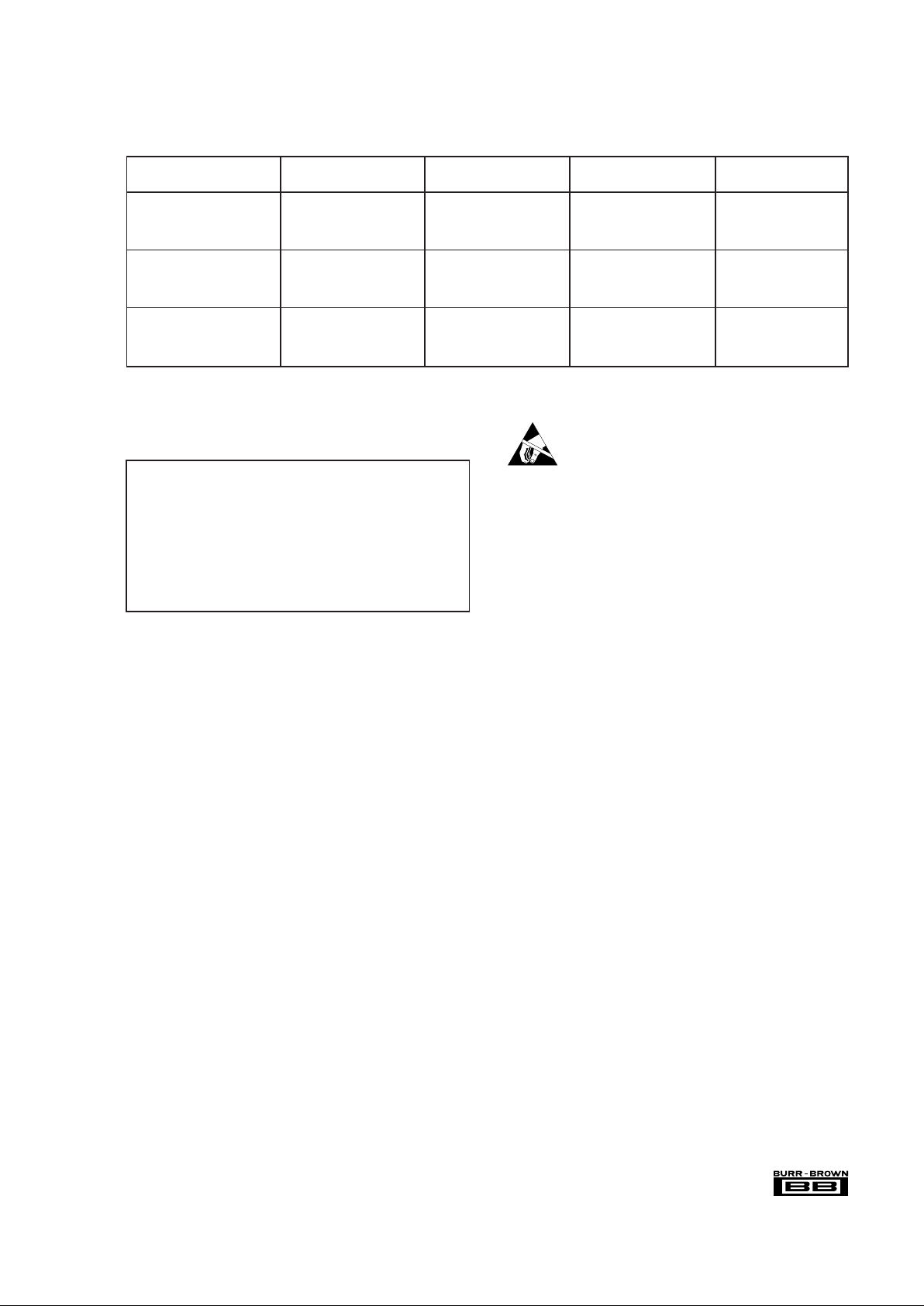

SPECIFICA TIONS

ELECTRICAL

At VDD = +5VDC, V

REF A

= V

REF B

= +10V, TA = –40°C to +85°C, unless otherwise noted.

DAC7800, 7801, 7802K DAC7800, 7801, 7802L

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

ACCURACY

Resolution 12 ✻ Bits

Relative Accuracy ±1 ±1/2 LSB

Differential Nonlinearity ±1 ✻ LSB

Gain Error Measured Using R

FB A

and R

FB B

. ±3 ±1 LSB

All Registers Loaded with All 1s.

Gain Temperature Coefficient

(1)

25 ✻✻ppm/°C

Output Leakage Current T

A

= +25°C 0.005 10 ✻✻ nA

T

A

= –40°C to +85°C 3 150 ✻✻ nA

REFERENCE INPUT

Input Resistance 6 10 14 ✻✻✻ kΩ

Input Resistance Match 0.5 3 ✻ 2%

DIGITAL INPUTS

V

IH

(Input High Voltage) 2 ✻ V

V

IL

(Input Low Voltage) 0.8 ✻ V

I

IN

(Input Current) TA = +25°C ±1 ✻ µA

T

A

= –40°C to +85°C ±10 ✻ µA

C

IN

(Input Capacitance) 0.8 10 ✻✻ pF

POWER SUPPLY

V

DD

4.5 5.5 ✻✻V

I

DD

0.2 2 ✻✻ mA

Power Supply Rejection V

DD

from 4.5V to 5.5V 0.002 ✻ %/%

✻ Same specification as for DAC7800, 7801, 7802K.

AC PERFORMANCE

OUTPUT OP AMP IS OPA602.

At V

DD

= +5VDC, V

REF A

= V

REF B

= +10V, TA = +25°C, unless otherwise noted. These specifications are fully characterized but not subject to test.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes

no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change

without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant

any BURR-BROWN product for use in life support devices and/or systems.

NOTE: (1) Guaranteed but not tested.

DAC7800, 7801, 7802K DAC7800, 7801, 7802L

PARAMETER CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

OUTPUT CURRENT SETTLING TIME To 0.01% of Full Scale 0.4 0.8 ✻✻ µs

R

L

= 100Ω, CL = 13pF

DIGITAL-TO-ANALOG GLITCH IMPULSE V

REF A

= V

REF B

= 0V 0.9 ✻ nV-s

R

L

= 100Ω, CL = 13pF

AC FEEDTHROUGH f

VREF

= 10kHz –75 –72 ✻✻ dB

OUTPUT CAPACITANCE DAC Loaded with All 0s 30 50 ✻✻ pF

DAC Loaded with All 1s 70 100 ✻✻ pF

CHANNEL-TO-CHANNEL ISOLATION

V

REF A

to I

OUT B

f

VREF A

= 10kHz –90 –94 ✻✻ dB

V

REF B

= 0V,

Both DACs Loaded with 1s

V

REF B

to I

OUT A

f

VREF B

= 10kHz –90 –101 ✻✻ dB

V

REF A

= 0V,

Both DACs Loaded with 1s

DIGITAL CROSSTALK Full Scale Transition 0.9 ✻ nV-s

R

L

= 100Ω, CL = 13pF

✻ Same specification as for DAC7800, 7801, 7802K.

®

3

DAC7800, 01, 02

PACKAGE DRAWING

PRODUCT PACKAGE NUMBER

(1)

RELATIVE ACCURACY GAIN ERROR

DAC7800KP 16-Pin PDIP 180 ±1LSB ±3LSB

DAC7800LP 16-Pin PDIP 180 ±1/2LSB ±1LSB

DAC7800KU 16-Lead SOIC 211

DAC7800LU 16-Lead SOIC 211

DAC7801KP 24-Pin DIP 243 ±1LSB ±3LSB

DAC7801LP 24-Pin DIP 243 ±1/2LSB ±1LSB

DAC7801KU 24-Lead SOIC 239

DAC7801LU 24-Lead SOIC 239

DAC7802KP 24-Pin DIP 243-3 ±1LSB ±3LSB

DAC7802LP 24-Pin DIP 243-3 ±1/2LSB ±1LSB

DAC7802KU 24-Lead SOIC 239

DAC7802LU 24- Lead SOIC 239

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

PACKAGE/ORDERING INFORMATION

VDD to AGND ................................................................................. 0V, +7V

V

DD

to DGND................................................................................. 0V, +7V

AGND to DGND .......................................................................... –0.3, V

DD

Digital Input to DGND ......................................................... –0.3, VDD + 0.3

V

REF A

, V

REF B

to AGND ..................................................................... ±20V

V

REF A

, V

REF B

to DGND ..................................................................... ±20V

I

OUT A

, I

OUT B

to AGND................................................................. –0.3, V

DD

Storage Temperature Range........................................... –55°C to +125°C

Operating Temperature Range .......................................... –40°C to +85°C

Lead Temperature (soldering, 10s) ................................................ +300°C

Junction Temperature ...................................................................... +175°C

ABSOLUTE MAXIMUM RATINGS

At TA = +25°C, unless otherwise noted.

ELECTROSTATIC

DISCHARGE SENSITIVITY

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure.

Burr-Brown Corporation recommends that all integrated circuits be handled and stored using appropriate ESD protection

methods.

Digital Inputs: All digital inputs of the DAC780X family

incorporate on-chip ESD protection circuitry. This protection

is designed and has been tested to withstand five 2500V

positive and negative discharges (100pF in series with 1500Ω)

applied to each digital input.

Analog Pins: Each analog pin has been tested to Burr-Brown’s

analog ESD test consisting of five 1000V positive and negative discharges (100pF in series with 1500Ω) applied to each

pin. AGND, I

OUT

, and R

FB

show some sensitivity. Failure to

observe ESD handling procedures could result in catastrophic

device failure.

4

®

DAC7800, 01, 02

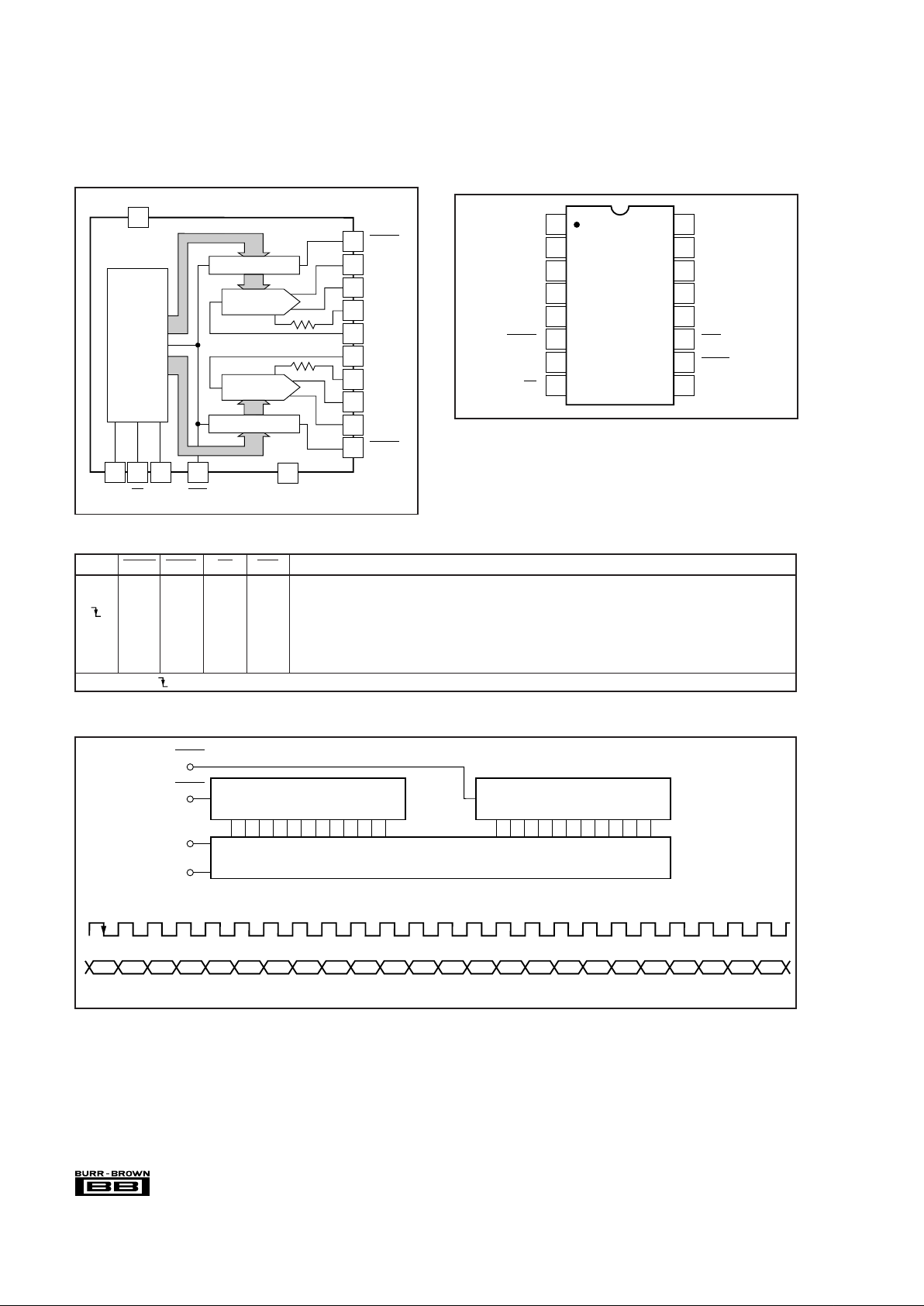

DAC7800

BLOCK DIAGRAM

DAC A

DAC B

DAC A Register

12

12

12

UPD B

I

AGND B

R

V

V

R

I

AGND A

UPD A

OUT B

FB B

REF B

REF A

FB A

OUT A

12

V

DD

9

DGND

10

15

16

14

13

4

3

2

1

6

DAC B Register

Bit 0

Bit 11

Bit 12

Bit 23

Control Logic and Shift Register

7 11

CLR

12

DAC7800

Data

In

5

CLK8CS

PIN CONFIGURATION

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

AGND A

CLK

UPD A

Data In

CS

AGND B

I

R

V

V

CLR

UPD B

DGND

OUT A

FB A

REF A

OUT B

DAC7800

Top View

DIP

I

R

V

FB B

REF B

DD

Data In

Bit 0 Bit 23Bit 22Bit 21Bit 20Bit 19Bit 18Bit 17Bit 16Bit 15Bit 14Bit 13Bit 12Bit 11Bit 10Bit 9Bit 8Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1

LSB

DAC A

MSB

DAC A

LSB

DAC B

MSB

DAC B

DAC7800 Data Input Sequence

DAC7800 Digital Interface Block Diagram

24-Bit

Shift Register

DAC A Register

UPD A

Data In

CLK

UPD B

LSB MSB

DAC B Register

LSB MSB

Bit

23

Bit

12

Bit

11

Bit

0

CLK

DATA INPUT FORMAT

CLK UPD A UPD B CS CLR FUNCTION

X X X X 0 All register contents set to 0’s (asynchronous).

X X X 1 X No data transfer.

X X 0 1 Input data is clocked into input register (location Bit 23) and previous data shifts.

X 0 1 0 1 Input register bits 23 (LSB)—12 (MSB) are loaded into DAC A.

X 1 0 0 1 Input register bits 11 (LSB)—0 (MSB) are loaded into DAC B.

X 0 0 0 1 Input register bits 23 (LSB)—12 (MSB) are loaded into DAC A, and input register bits 11 (LSB)—0 (MSB)

are loaded into DAC B.

X = Don’t care.

means falling edge triggered.

LOGIC TRUTH TABLE

Loading...

Loading...